#### ISL6721

Flexible Single-Ended Current Mode PWM Controller

FN9110 Rev 9.00 May 20, 2016

The ISL6721 is a low power, single-ended Pulse Width Modulating (PWM) current mode controller designed for a wide range of DC/DC conversion applications including Boost, Flyback and isolated output configurations. Peak current mode control effectively handles power transients and provides inherent overcurrent protection. Other features include a low power mode where the supply current drops to less than 200µA during overvoltage and overcurrent shutdown faults.

This advanced BiCMOS design features low operating current, adjustable operating frequency up to 1MHz, adjustable soft-start, and a bidirectional SYNC signal that allows the oscillator to be locked to an external clock for noise sensitive applications.

# **Applications**

- · Telecom and datacom power

- · Wireless base station power

- · File server power

- · Industrial power systems

- · Isolated buck and Flyback regulators

- · Boost regulators

#### **Features**

- · 1A MOSFET gate driver

- 100µA start-up current

- · Fast transient response with peak current mode control

- · Adjustable switching frequency up to 1MHz

- · Bidirectional synchronization

- · Low power disable mode

- · Delayed restart from OV and OC shutdown faults

- · Adjustable slope compensation

- · Adjustable soft-start

- · Adjustable overcurrent shutdown threshold

- · Adjustable UV and OV monitors

- · Leading edge blanking

- · Integrated thermal shutdown

- 1% tolerance voltage reference

- · Pb-free available (RoHS compliant)

#### **Related Literature**

- AN1384, "ISL6841EVAL3Z Evaluation Board for General Purpose Industrial Applications"

- AN1491, "ISL6721EVAL3Z: Resonant Reset Forward Converters for Low Power"

# **Ordering Information**

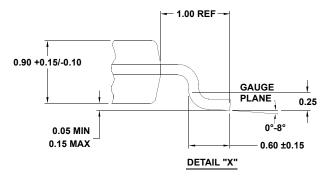

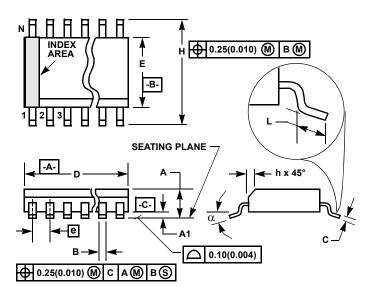

| PART NUMBER<br>(Notes 1, 2, 3)                                                 | PART<br>MARKING  | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|--------------------------------------------------------------------------------|------------------|---------------------|-----------------------------|----------------|

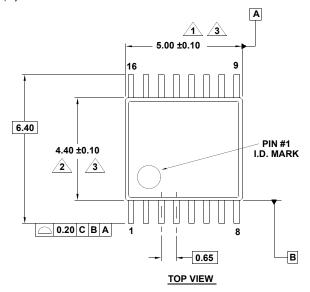

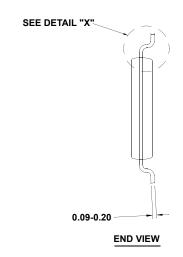

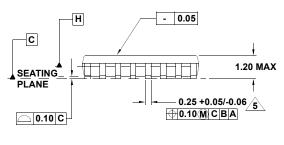

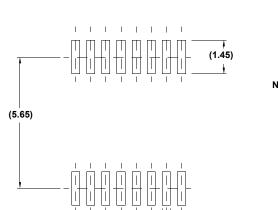

| ISL6721ABZ                                                                     | 6721ABZ          | -40 to +105         | 16 Ld SOIC (150 mil)        | M16.15         |

| ISL6721AV-T<br>(No longer available, recommended<br>replacement: ISL6721AVZ-T) | ISL67 21AV       | -40 to +105         | 16 Ld TSSOP (4.4mm)         | M16.173        |

| ISL6721AVZ                                                                     | ISL67 21AVZ      | -40 to +105         | 16 Ld TSSOP (4.4mm)         | M16.173        |

| ISL6721EVAL3Z                                                                  | Evaluation Board |                     |                             |                |

#### NOTES:

- 1. Add "-T" suffix for 2.5k unit for Tape and Reel options. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials and 100% matte tin

plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL6721</u>. For more information on MSL please see techbrief <u>TB363</u>.

**TABLE 1. KEY DIFFERENCES BETWEEN FAMILY OF PARTS**

| PART NUMBER                      | ISL6721   | ISL6721A  |

|----------------------------------|-----------|-----------|

| UVLO thresholds (start/stop) (V) | 8.25/7.70 | 6.80/6.20 |

| UV threshold (V)                 | 1.45      | 1.93      |

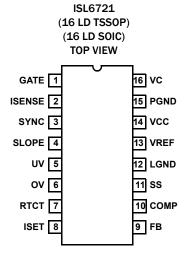

# **Functional Block Diagram**

FIGURE 1. FUNCTIONAL BLOCK DIAGRAM

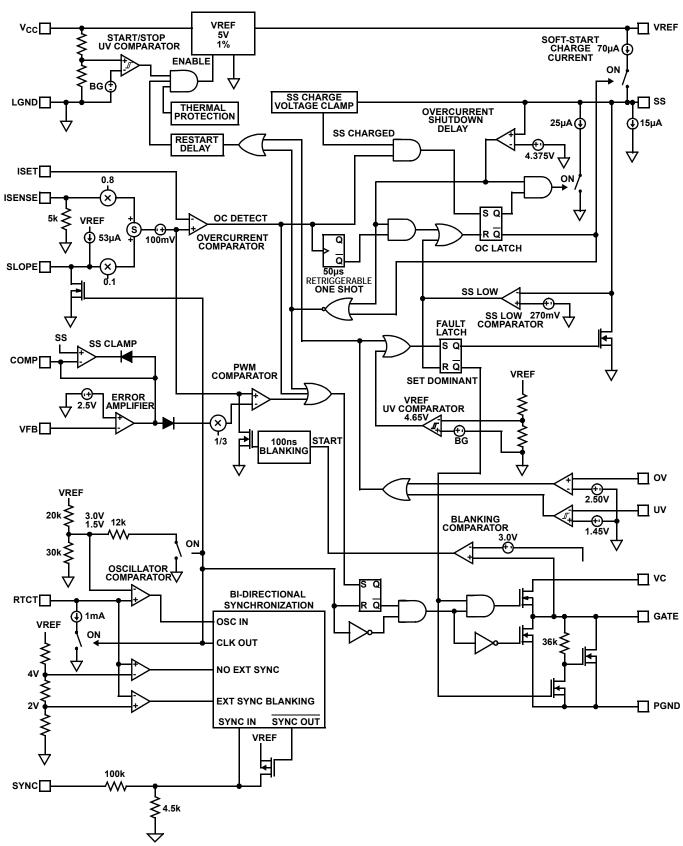

# Typical Application - 48V Input Dual Output Flyback, 3.3V at 2.5A, 1.8V at 1.0A

FIGURE 2. TYPICAL APPLICATION - 48V INPUT DUAL OUTPUT FLYBACK, 3.3V AT 2.5A, 1.8V AT 1.0A

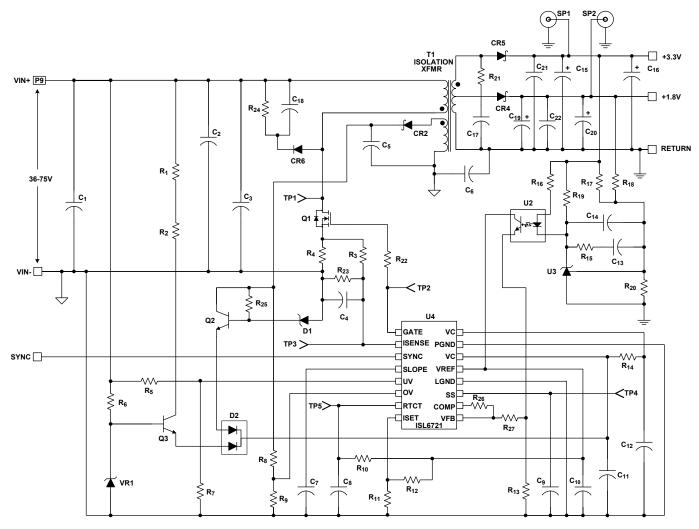

# **Typical Boost Converter Application Schematic**

FIGURE 3. TYPICAL BOOST CONVERTER APPLICATION SCHEMATIC

#### **Absolute Maximum Ratings**

| Supply Voltage, VCC. VC | (GND -0.3V) to +20.0V                     |

|-------------------------|-------------------------------------------|

| GATE                    | (GND - 0.3V) to Gate Output Limit Voltage |

| PGND to LGND            | ±0.3V                                     |

| VREF                    | (GND - 0.3V) to 5.3V                      |

| Signal Pins             | (GND - 0.3V) to VREF                      |

| Peak GATE Current       | 1Δ                                        |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4) | θ <sub>JA</sub> (°C/W) |

|--------------------------------------|------------------------|

| 16 Ld SOIC                           | 80                     |

| 16 Ld TSSOP                          | 105                    |

| Maximum Junction Temperature         | 5°C to +150°C          |

| Maximum Storage Temperature Range65  | 5°C to +150°C          |

| Pb-Free Reflow Profile               | see <u>TB493</u>       |

### **Operating Conditions**

| Temperature Range                      |                |

|----------------------------------------|----------------|

| ISL6721Ax                              | 40°C to +105°C |

| Supply Voltage Range (Typical, Note 5) | 9VDC to 18VDC  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4.  $\theta_{\text{JA}}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 5. All voltages are with respect to GND.

**Electrical Specifications** Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 3 and "Typical Boost Converter Application Schematic" on page 5. 9V <  $V_{CC}$  = VC < 20V,  $R_T$  = 11k $\Omega$ ,  $C_t$  = 330 pF,  $T_A$  = -40°C to +105°C (Note 6), Typical values are at  $T_A$  = +25°C.

| PARAMETER                                      | TEST CONDITIONS                                                                                             | MIN  | TYP  | MAX  | UNIT |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|------|

| UNDERVOLTAGE LOCKOUT                           | ·                                                                                                           |      |      |      | '    |

| START Threshold                                |                                                                                                             | 7.95 | 8.25 | 8.55 | V    |

| STOP Threshold                                 |                                                                                                             | 7.40 | 7.70 | 8.20 | V    |

| Hysteresis                                     |                                                                                                             | 0.50 | 0.55 | 1.00 | V    |

| Start-Up Current, I <sub>CC</sub>              | V <sub>CC</sub> < START Threshold                                                                           | -    | 100  | 175  | μΑ   |

| OC/OV Fault Operating Current, I <sub>CC</sub> |                                                                                                             | -    | 200  | 300  | μΑ   |

| Operating Current, I <sub>CC</sub>             |                                                                                                             | -    | 4.5  | 10.0 | mA   |

| Operating Supply Current, I <sub>C</sub>       | Includes 1nF GATE loading                                                                                   | -    | 8.0  | 12.0 | mA   |

| REFERENCE VOLTAGE                              |                                                                                                             |      | •    | •    | •    |

| Overall Accuracy                               | Line, load, 0°C to +105°C                                                                                   | 4.95 | 5.00 | 5.05 | V    |

|                                                | Line, load, -40 °C to +105 °C                                                                               | 4.90 | 5.00 | 5.05 | ٧    |

| Long Term Stability                            | T <sub>A</sub> = +125°C, 1000 hours ( <u>Note 8</u> )                                                       | -    | 5    | -    | mV   |

| Fault Voltage                                  |                                                                                                             | 4.50 | 4.65 | 4.75 | V    |

| V <sub>REF</sub> Good Voltage                  |                                                                                                             | 4.65 | 4.80 | 4.95 | ٧    |

| Hysteresis                                     |                                                                                                             | 75   | 165  | 250  | mV   |

| Operational Current                            |                                                                                                             | -10  | -    | -    | mA   |

| Current Limit                                  |                                                                                                             | -20  | -    | -    | mA   |

| CURRENT SENSE                                  |                                                                                                             |      |      |      |      |

| Input Impedance                                |                                                                                                             | -    | 5    | -    | kΩ   |

| Offset Voltage                                 |                                                                                                             | 0.08 | 0.10 | 0.11 | ٧    |

| Input Voltage Range                            |                                                                                                             | 0    | -    | 1.5  | V    |

| Blanking Time                                  | (Note 8)                                                                                                    | 30   | 60   | 100  | ns   |

| Gain, A <sub>CS</sub>                          | $V_{SLOPE} = 0V$ , $V_{FB} = 2.3V$ , $V_{ISET} = 0.35V$ , $1.5V$ $A_{CS} = \triangle ISET/\triangle ISENSE$ | 0.77 | 0.79 | 0.81 | V/V  |

**Electrical Specifications** Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 3 and "Typical Boost Converter Application Schematic" on page 5. 9V <  $V_{CC}$  = VC < 20V,  $R_T$  = 11k $\Omega$ ,  $C_t$  = 330 pF,  $T_A$  = -40°C to +105°C (Note 6), Typical values are at  $T_A$  = +25°C.

| PARAMETER                                      | TEST CONDITIONS                                                                      | MIN                    | TYP          | MAX          | UNIT |

|------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|--------------|--------------|------|

| ERROR AMPLIFIER                                |                                                                                      |                        |              |              |      |

| Open Loop Voltage Gain                         | ( <u>Note 8</u> )                                                                    | 60                     | 90           | -            | dB   |

| Gain-Bandwidth Product                         | ( <u>Note 8</u> )                                                                    | -                      | 15           | -            | MHz  |

| Reference Voltage Initial Accuracy             | V <sub>FB</sub> = COMP, T <sub>A</sub> = +25°C ( <u>Note 8</u> )                     | 2.465                  | 2.515        | 2.565        | V    |

| Reference Voltage                              | V <sub>FB</sub> = COMP                                                               | 2.440                  | 2.515        | 2.590        | V    |

| COMP to PWM Gain, A <sub>COMP</sub>            | COMP = 4V, T <sub>A</sub> = +25 °C                                                   | 0.31                   | 0.33         | 0.35         | V/V  |

| COMP to PWM Offset                             | COMP = 4V (Note 8)                                                                   | 0.51                   | 0.75         | 0.88         | V    |

| FB Input Bias Current                          | V <sub>FB</sub> = 0V                                                                 | -2                     | 0.1          | 2            | μΑ   |

| COMP Sink Current                              | COMP = 1.5V, V <sub>FB</sub> = 2.7V                                                  | 2                      | 6            | -            | mA   |

| COMP Source Current                            | COMP = 1.5V, V <sub>FB</sub> = 2.3V                                                  | -0.25                  | -0.50        | -            | mA   |

| COMP V <sub>OH</sub>                           | V <sub>FB</sub> = 2.3V                                                               | 4.25                   | 4.40         | 5.00         | V    |

| COMP V <sub>OL</sub>                           | V <sub>FB</sub> = 2.7V                                                               | 0.4                    | 0.8          | 1.2          | V    |

| PSRR                                           | Frequency = 120Hz (Note 8)                                                           | 60                     | 80           | -            | dB   |

| SS Clamp, V <sub>COMP</sub>                    | SS = 2.5V, V <sub>FB</sub> = 0V, ISET = 2V                                           | 2.4                    | 2.5          | 2.6          | v    |

| OSCILLATOR                                     |                                                                                      | 1                      |              | 1            | 1    |

| Frequency Accuracy                             |                                                                                      | 289                    | 318          | 347          | kHz  |

| Frequency Variation with V <sub>CC</sub>       | T = +105°C (f20V - f9V)/f9V<br>T = -40°C (f20V -f9V)/f9V                             | -                      | 2<br>2       | 3            | %    |

| Temperature Stability                          | ( <u>Note 8</u> )                                                                    | -                      | 8            | -            | %    |

| Maximum Duty Cycle                             | ( <u>Note 9</u> )                                                                    | 68                     | 75           | 81           | %    |

| Comparator High Threshold - Free Running       |                                                                                      | -                      | 3.00         | -            | V    |

| Comparator High Threshold - with External SYNC | ( <u>Note 8</u> )                                                                    | -                      | 4.00         | -            | V    |

| Comparator Low Threshold                       |                                                                                      | -                      | 1.50         | -            | V    |

| Discharge Current                              | 0°C to +105°C<br>-40°C to +105°C                                                     | 0.75<br>0.70           | 1.00<br>1.00 | 1.20<br>1.20 | mA   |

| SYNCHRONIZATION                                |                                                                                      |                        |              |              |      |

| nput High Threshold                            |                                                                                      | -                      | -            | 2.5          | V    |

| nput Pulse Width                               |                                                                                      | 25                     | -            | -            | ns   |

| Input Frequency Range                          | ( <u>Note 8</u> )                                                                    | 0.65 x Free<br>Running | -            | 1.0          | MHz  |

| nput Impedance                                 |                                                                                      | -                      | 4.5          | -            | kΩ   |

| v <sub>он</sub>                                | $R_{LOAD} = 4.5k\Omega$                                                              | 2.5                    | -            | -            | V    |

| V <sub>OL</sub>                                | R <sub>LOAD</sub> = open                                                             | -                      | -            | 0.1          | ٧    |

| SYNC Advance                                   | SYNC rising edge to GATE falling edge, C <sub>GATE</sub> = C <sub>SYNC</sub> = 100pF | -                      | 25           | 55           | ns   |

| Output Pulse Width                             | C <sub>SYNC</sub> = 100pF                                                            | 50                     | -            | -            | ns   |

**Electrical Specifications** Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 3 and "Typical Boost Converter Application Schematic" on page 5. 9V <  $V_{CC}$  = VC < 20V,  $R_T$  = 11k $\Omega$ ,  $C_t$  = 330 pF,  $T_A$  = -40°C to +105°C (Note 6), Typical values are at  $T_A$  = +25°C.

| PARAMETER                              | TEST CONDITIONS                                                                                                              | MIN        | TYP        | MAX        | UNIT |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------|

| SOFT-START                             |                                                                                                                              |            |            |            |      |

| Charging Current                       | SS = 2V                                                                                                                      | -40        | -55        | -70        | μΑ   |

| Charged Threshold Voltage              |                                                                                                                              | 4.26       | 4.50       | 4.74       | V    |

| Initial Overcurrent Discharge Current  | Sustained OC Threshold < SS < Charged Threshold                                                                              | 30         | 40         | 55         | μА   |

| Overcurrent Shutdown Threshold Voltage | Charged Threshold minus,<br>T <sub>A</sub> = +25 °C                                                                          | 0.095      | 0.125      | 0.155      | V    |

| Fault Discharge Current                | SS = 2V                                                                                                                      | 0.25       | 1.00       | -          | mA   |

| Reset Threshold Voltage                | T <sub>A</sub> = +25°C                                                                                                       | 0.22       | 0.27       | 0.31       | V    |

| SLOPE COMPENSATION                     | ,                                                                                                                            | 1          | ll .       | 1          | 1    |

| Charge Current                         | SLOPE = 2V, 0°C to +105°C<br>-40°C to +105°C                                                                                 | -45<br>-41 | -53<br>-53 | -65<br>-65 | μА   |

| Slope Compensation Gain                | Fraction of slope voltage added to I <sub>SENSE</sub> , T <sub>A</sub> = +25°C                                               | 0.097      | -          | 0.103      | V/V  |

|                                        | Fraction of slope voltage added to I <sub>SENSE</sub> (Note 6)                                                               | 0.082      | -          | 0.118      | V/V  |

| Discharge Voltage                      | V <sub>RTCT</sub> = 4.5V                                                                                                     | -          | 0.1        | 0.2        | V    |

| GATE OUTPUT                            | ,                                                                                                                            | l          | l          |            |      |

| Gate Output Limit Voltage              | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF,<br>I <sub>OUT</sub> = 0mA                                                     | 11.0       | 13.5       | 16.0       | V    |

| Gate V <sub>OH</sub>                   | $V_C$ - GATE, $V_C$ = 10V,<br>$I_{OUT}$ = 150mA                                                                              | -          | 1.5        | 2.2        | V    |

| Gate V <sub>OL</sub>                   | GATE - PGND, IOUT = 150mA<br>I <sub>OUT</sub> = 10mA                                                                         | -          | 1.2<br>0.6 | 1.5<br>0.8 | V    |

| Peak Output Current                    | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF ( <u>Note 8</u> )                                                              | -          | 1.0        | -          | Α    |

| Output "Faulted" Leakage               | V <sub>C</sub> = 20V, UV = 0V, GATE = 2V                                                                                     | 1.2        | 2.6        | -          | mA   |

| Rise Time                              | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF<br>1V < GATE < 9V                                                              | -          | 60         | 100        | ns   |

| Fall Time                              | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF<br>1V < GATE < 9V                                                              | -          | 15         | 40         | ns   |

| Minimum ON-Time                        | ISET = 0.5V; $V_{FB}$ = 0V; $V_{C}$ = 11V<br>ISENSE to GATE $w/10$ :1 Divider<br>RTCT = 4.75V through $1k\Omega$<br>(Note 8) | -          | -          | 110        | ns   |

| OVERCURRENT PROTECTION                 |                                                                                                                              |            |            |            |      |

| Minimum ISET Voltage                   |                                                                                                                              | -          | -          | 0.35       | V    |

| Maximum ISET Voltage                   |                                                                                                                              | 1.2        | -          | -          | V    |

| SET Bias Current                       | V <sub>ISET</sub> = 1.00V                                                                                                    | -1.0       | -          | 1.0        | μΑ   |

| Restart Delay                          | T <sub>A</sub> = +25°C                                                                                                       | 150        | 295        | 445        | ms   |

| OV AND UV VOLTAGE MONITOR              |                                                                                                                              |            |            |            |      |

| Overvoltage Threshold                  |                                                                                                                              | 2.4        | 2.5        | 2.6        | V    |

| Undervoltage Fault Threshold           |                                                                                                                              | 1.38       | 1.45       | 1.52       | V    |

| Undervoltage Clear Threshold           |                                                                                                                              | 1.41       | 1.53       | 1.62       | V    |

**Electrical Specifications** Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 3 and "Typical Boost Converter Application Schematic" on page 5. 9V <  $V_{CC}$  = VC < 20V,  $R_T$  = 11k $\Omega$ ,  $C_t$  = 330 pF,  $T_A$  = -40°C to +105°C (Note 6), Typical values are at  $T_A$  = +25°C.

| PARAMETER                       | TEST CONDITIONS         | MIN  | TYP | MAX | UNIT |  |

|---------------------------------|-------------------------|------|-----|-----|------|--|

| Undervoltage Hysteresis Voltage |                         | 20   | 50  | 100 | mV   |  |

| UV Bias Current                 | V <sub>UV</sub> = 2.00V | -1.0 | -   | 1.0 | μΑ   |  |

| OV Bias Current                 | V <sub>OV</sub> = 2.00V | -1.0 | -   | 1.0 | μΑ   |  |

| THERMAL PROTECTION              | THERMAL PROTECTION      |      |     |     |      |  |

| Thermal Shutdown                | ( <u>Note 8</u> )       | 120  | 130 | 140 | °C   |  |

| Thermal Shutdown Clear          | (Note 8)                | 105  | 120 | 135 | °C   |  |

| Hysteresis                      | ( <u>Note 8</u> )       | -    | 10  | -   | °C   |  |

#### NOTES:

- 6. Specifications at -40  $^{\circ}$ C and +105  $^{\circ}$ C are guaranteed by +25  $^{\circ}$ C test with margin limits.

- 7. This is the V<sub>CC</sub> current consumed when the device is active but not switching. Does not include gate drive current.

- 8. Limits should be considered typical and are not production tested.

- 9. This is the maximum duty cycle achievable using the specified values of R<sub>T</sub> and C<sub>T</sub>. Larger or smaller maximum duty cycles may be obtained using other values for R<sub>T</sub> and C<sub>T</sub>. See Equations 1, 2, 3 and 4.

### **Typical Performance Curves**

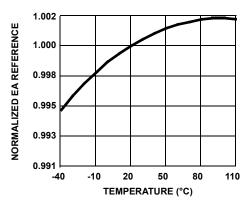

FIGURE 4. EA REFERENCE VOLTAGE VS TEMPERATURE

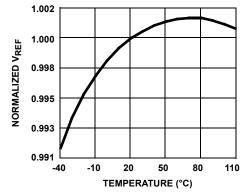

FIGURE 5. V<sub>REF</sub> REFERENCE VOLTAGE vs TEMPERATURE

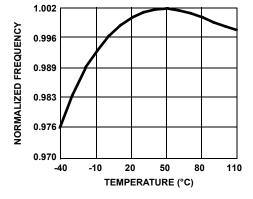

FIGURE 6. OSCILLATOR FREQUENCY vs TEMPERATURE

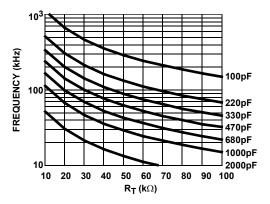

FIGURE 7. RESISTANCE FOR  $C_{\mbox{\scriptsize T}}$  CAPACITOR VALUES GIVEN

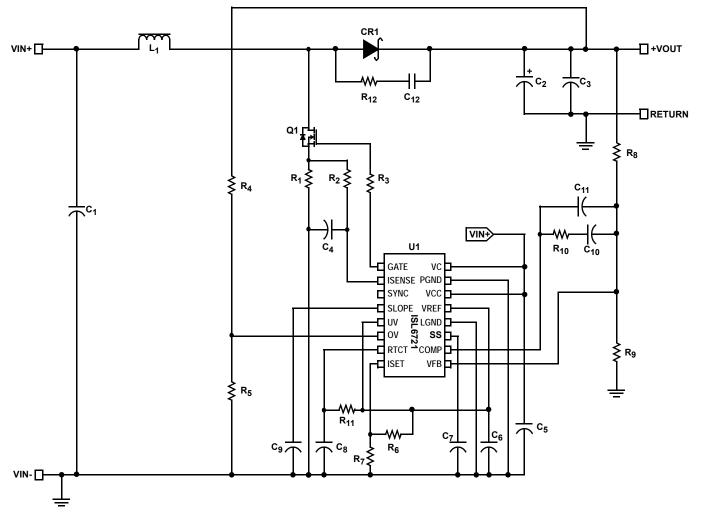

# **Pin Descriptions**

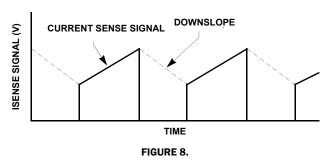

**SLOPE** - Means by which the ISENSE ramp slope may be increased for improved noise immunity or improved control loop stability for duty cycles greater than 50%. An internal current source charges an external capacitor to GND during each switching cycle. The resulting ramp is scaled and added to the ISENSE signal.

**RTCT** - This is the oscillator timing control pin. The operational frequency and maximum duty cycle are set by connecting a resistor,  $R_T$ , between  $V_{REF}$  and this pin and a timing capacitor,  $C_T$ , from this pin to LGND. The oscillator produces a sawtooth waveform with a programmable frequency range of 100kHz to 1.0MHz. The charge time,  $t_C$ , the discharge time,  $t_D$ , the switching frequency,  $f_{SW}$ , and the maximum duty cycle, Dmax, can be calculated from Equations 1, 2, 3 and 4:

$$t_{C} \approx 0.655 \bullet R_{T} \bullet C_{T} \qquad S \tag{EQ. 1}$$

$$t_{D} \approx -R_{T} \bullet C_{T} \bullet LN \left( \frac{0.001 \bullet R_{T} - 3.6}{0.001 \bullet R_{T} - 1.9} \right) \qquad S \tag{EQ. 2}$$

$$f_{sw} = \frac{1}{t_D + t_C} \qquad \text{Hz}$$

(EQ. 3)

$$Dmax = t_{C} \bullet f_{sw}$$

(EQ. 4)

<u>Figure 7</u> may be used as a guideline in selecting the capacitor and resistor values required for a given frequency.

**COMP** - COMP is the output of the error amplifier and the input of the PWM comparator. The control loop frequency compensation network is connected between the COMP and FB pins.

The ISL6721 features a built-in full cycle soft-start. Soft-start is implemented as a clamp on the maximum COMP voltage.

**FB** - Feedback voltage input connected to the inverting input of the error amplifier. The noninverting input of the error amplifier is internally tied to a reference voltage. Current sense leading edge blanking is disabled when the FB input is less than 2.0V.

**OV** - Overvoltage monitor input pin. This signal is compared to an internal 2.5V reference to detect an overvoltage condition.

UV - Undervoltage monitor input pin. This signal is compared to an internal 1.45V reference to detect an undervoltage condition.

ISENSE - This is the input to the current sense comparators. The IC has two current sensing comparators, a PWM comparator for peak current mode control, and an overcurrent protection comparator. The overcurrent comparator threshold is adjustable through the ISET pin.

Exceeding the overcurrent threshold will start a delayed shutdown sequence. Once an overcurrent condition is detected, the soft-start charge current source is disabled and a discharge current source is enabled. The soft-start capacitor begins discharging, and if it discharges to less than 4.375V (sustained overcurrent threshold), a shutdown condition occurs and the GATE output is forced low. See "Overcurrent Operation" on page 12 for more details. The GATE output remains low until the reset threshold is attained. At this point, a soft-start cycle begins.

If the overcurrent condition ceases, and then an additional 50µs period elapses before the shutdown threshold is reached, no shutdown occurs and the soft-start voltage is allowed to recharge.

**LGND** - LGND is a small signal reference ground for all analog functions on this device.

**PGND** - This pin provides a dedicated ground for the output gate driver. The LGND and PGND pins should be connected externally using a short printed circuit board trace close to the IC. This is imperative to prevent large, high frequency switching currents flowing through the ground metallization inside the IC. (Decouple VC to PGND with a low ESR 0.1μF or larger capacitor.)

**GATE** - This is the device output. It is a high current power driver capable of driving the gate of a power MOSFET with peak currents of 1.0A. This GATE output is actively held low when VCC is below the UVLO threshold.

The output high voltage is clamped to ~13.5V. Voltages exceeding this clamp value should not be applied to the GATE pin. The output stage provides very low impedance to overshoot and undershoot.

VC - This pin is for separate collector supply to the output gate drive. Separate VC and PGND helps decouple the IC's analog circuitry from the high power gate drive noise. (Decouple VC to PGND with a low ESR  $0.1\mu F$  or larger capacitor.)

$\mbox{VCC}$  - VCC is the power connection for the device. Although quiescent current,  $\mbox{I}_{CC},$  is low, it is dependent on the frequency of operation. To optimize noise immunity, bypass VCC to LGND with a ceramic capacitor as close to the VCC and LGND pins as possible.

The total supply current ( $I_C$  plus  $I_{CC}$ ) will be higher, depending on the load applied to GATE. Total current is the sum of the quiescent current and the average gate current. Knowing the operating frequency,  $f_{SW}$ , and the MOSFET gate charge, Qg, the average GATE output current can be calculated in Equation 5:

Igate =

$$Qg \bullet f_{SW}$$

A (EQ. 5)

VREF - The 5V reference voltage output. Bypass to LGND with a  $0.01\mu\text{F}$  or larger capacitor to filter this output as needed. Using capacitance less than this value may result in unstable operation.

**SS** - Connect the soft-start capacitor between this pin and LGND to control the duration of soft-start. The value of the capacitor determines both the rate of increase of the duty cycle during start-up, and also controls the overcurrent shutdown delay.

ISET - A DC voltage between 0.35V and 1.2V applied to this input sets the pulse-by-pulse overcurrent threshold. When overcurrent inception occurs, the SS capacitor begins to discharge and starts the overcurrent delayed shutdown cycle.

# **Functional Description**

#### **Features**

The ISL6721 current mode PWMs make an ideal choice for low-cost Flyback and Forward topology applications requiring enhanced control and supervisory capability. With adjustable overvoltage and undervoltage thresholds, overcurrent threshold, and hiccup delay, a highly flexible design with minimal external components is possible. Other features include peak current mode control, adjustable soft-start, slope compensation, adjustable oscillator frequency, and a bidirectional synchronization clock input.

#### **Oscillator**

The ISL6721 has a sawtooth oscillator with a programmable frequency range to 1MHz, which can be programmed with a resistor and capacitor on the RTCT pin. (Please refer to Figure 7 on page 9 for the resistance and capacitance required for a given frequency.)

#### **Implementing Synchronization**

The oscillator can be synchronized to an external clock applied at the SYNC pin or by connecting the SYNC pins of multiple ICs together. If an external master clock signal is used, it must be at least 65% of the free running frequency of the oscillator for proper synchronization. The external master clock signal should have a pulse width greater than 20ns. If no master clock is used, the first device to assert SYNC assumes control of the SYNC signal. An external SYNC pulse is ignored if it occurs during the first 1/3 of the switching cycle.

During normal operation the RTCT voltage charges from 1.5V to 3.0V and back during each cycle. Clock and SYNC signals are generated when the 3.0V threshold is reached. If an external clock signal is detected during the latter 2/3 of the charging cycle, the oscillator switches to external synchronization mode and relies upon the external SYNC signal to terminate the oscillator cycle. The generation of a SYNC signal is inhibited in this mode. If the RTCT voltage exceeds 4.0V (i.e., no external SYNC signal terminates the cycle), the oscillator reverts to the internal clock mode and a SYNC signal is generated.

#### **Soft-Start Operation**

The ISL6721 features soft-start using an external capacitor in conjunction with an internal current source. Soft-start is used to reduce voltage stresses and surge currents during start-up.

Upon start-up, the soft-start circuitry clamps the error amplifier output (COMP pin) to a value proportional to the soft-start

voltage. The error amplifier output rises as the soft-start capacitor voltage rises. This has the effect of increasing the output pulse width from zero to the steady state operating duty cycle during the soft-start period. When the soft-start voltage exceeds the error amplifier voltage, soft-start is completed. Soft-start forces a controlled output voltage rise. Soft-start occurs during start-up and after recovery from a fault condition or overcurrent shutdown. The soft-start voltage is clamped to 4.5V.

#### **Gate Drive**

The ISL6721 is capable of sourcing and sinking 1A peak current. Separate collector supply (VC) and power ground (PGND) pins help isolate the IC's analog circuitry from the high power gate drive noise. To limit the peak current through the IC, an external resistor may be placed between the totem-pole output of the IC (GATE pin) and the gate of the MOSFET. This small series resistor also damps any oscillations caused by the resonant tank of the parasitic inductances in the traces of the board and the FET's input capacitance.

#### **Slope Compensation**

For applications where the maximum duty cycle is less than 50%, slope compensation may be used to improve noise immunity, particularly at lighter loads. The amount of slope compensation required for noise immunity is determined empirically, but is generally about 10% of the full scale current feedback signal. For applications where the duty cycle is greater than 50%, slope compensation is required to prevent instability. Slope compensation is a technique in which the current feedback signal is modified by adding additional slope to it. The minimum amount of slope compensation required corresponds to 1/2 the inductor downslope. However, adding excessive slope compensation results in a control loop that behaves more as a voltage mode controller than as current mode controller.

The minimum amount of capacitance to place at the SLOPE pin is calculated in <u>Equation 6</u>:

$$C_{SLOPE} = 4.24 \times 10^{-6} \bullet \frac{t_{ON}}{V_{SLOPE}} \qquad F \qquad (EQ. 6)$$

Where  $t_{ON}$  is the On time and  $V_{SLOPE}$  is the amount of voltage to be added as slope compensation to the current feedback signal. In general, the amount of slope compensation added is 2 to 3 times the minimum required.

#### Example:

Assume the inductor current signal presented at the ISENSE pin decreases 125mV during the Off period, and:

Switching frequency, f<sub>sw</sub> = 250kHz

Duty Cycle, D = 60%

$$t_{ON} = D/f_{SW} = 0.6/250E3 = 2.4 \mu s$$

$$t_{OFF} = (1 - D)/fsw = 1.6 \mu s$$

Determine the downslope:

Downslope =  $0.125V/1.6\mu s = 78mV/\mu s$ . Now determine the amount of voltage that must be added to the current sense signal by the end of the On time.

$$V_{SLOPE} = \frac{1}{2} \cdot 0.078 \cdot 2.4 = 94 \text{mV}$$

(EQ. 7)

Therefore.

$$C_{SLOPE(MIN)} = 4.24 \times 10^{-6} \bullet \frac{2.4 \times 10^{-6}}{0.094} \approx 110 \text{ pF}$$

(EQ. 8)

An appropriate slope compensation capacitance for this example would be 1/2 to 1/3 the calculated value, or between 68pF and 33pF.

#### **Overvoltage and Undervoltage Monitor**

The OV and UV signals are inputs to a window comparator used to monitor the input voltage level to the converter. If the voltage falls outside of the user designated operating range, a shutdown fault occurs. For OV faults, the supply current,  $I_{CC}$ , is reduced to  $200\,\mu\text{A}$  for ~295ms at which time recovery is attempted. If the fault is cleared, a soft-start cycle begins. Otherwise another shutdown cycle occurs. A UV condition also results in a shutdown fault, but the device does not enter the low power mode and no restart delay occurs when the fault clears.

A resistor divider between  $\rm V_{IN}$  and LGND to each input determines the operational thresholds. The UV threshold has a fixed hysteresis of 75mV nominal.

#### **Overcurrent Operation**

The overcurrent threshold level is set by the voltage applied at the ISET pin. Setting the overcurrent level may be accomplished by using a resistor divider network from VREF to LGND. The ISET threshold should be set at a level that corresponds to the desired peak output inductor current plus the additive effects of slope compensation.

Overcurrent delayed shutdown is enabled once the soft-start cycle is complete. If an overcurrent condition is detected, the soft-start charging current source is disabled and the discharging current source is enabled. The soft-start capacitor is discharged at a rate of  $40\mu A$ . At the same time, a  $50\mu s$  retriggerable one-shot timer is activated and it remains active for  $50\mu s$  after the overcurrent condition stops. The soft-start discharge cycle cannot be reset until the one-shot timer becomes inactive. If the soft-start capacitor discharges by more than 0.125V to 4.375V, the output is disabled and the soft-start capacitor is discharged. The output remains disabled

and  $I_{CC}$  drops to 200 $\mu$ A for approximately 295ms. A new soft-start cycle is then initiated. The shutdown and restart behavior of the OC protection is often referred to as hiccup operation due to its repetitive start-up and shutdown characteristic.

If the overcurrent condition ceases at least 50µs prior to the soft-start voltage reaching 4.375V, the soft-start charging and discharging currents revert to normal operation and the soft-start voltage is allowed to recover.

Hiccup OC protection may be defeated by setting ISET to a voltage that exceeds the Error Amplifier current control voltage, or about 1.5V.

#### **Leading Edge Blanking**

The initial 100ns of the current feedback signal input at ISENSE is removed by the leading edge blanking circuitry. The blanking period begins when the GATE output leading edge exceeds 3.0V. Leading edge blanking prevents current spikes from parasitic elements in the power supply from causing false trips of the PWM comparator and the overcurrent comparator.

#### **Fault Conditions**

A Fault condition occurs if VREF falls below 4.65V, the OV input exceeds 2.50V, the UV input falls below 1.45V, or the junction temperature of the die exceeds ~+130°C. When a Fault is detected the GATE output is disabled and the soft-start capacitor is quickly discharged. When the Fault condition clears and the soft-start voltage is below the reset threshold, a soft-start cycle begins.

#### **Ground Plane Requirements**

Careful layout is essential for satisfactory operation of the device. A good ground plane must be employed. A unique section of the ground plane must be designated for high di/dt currents associated with the output stage. Power ground (PGND) can be separated from the Logic Ground (LGND) and connected at a single point. VC should be bypassed directly to PGND with good high frequency capacitors. The return connection for input power and the bulk input capacitor should be connected to the PGND ground plane.

# **Reference Design**

The <u>"Typical Boost Converter Application Schematic" on page 5</u> features the ISL6721 in a conventional dual output 10W discontinuous mode Flyback DC/DC converter. The ISL6721EVAL1 demonstration unit implements this design and is available for evaluation.

The input voltage range is from 36VDC to 75VDC, and the two outputs are 3.3V at 2.5A and 1.8V at 1.0A. Cross regulation is achieved using the weighted sum of the two outputs.

#### **Circuit Element Descriptions**

The converter design may be broken down into the following functional blocks:

• Input storage and filtering capacitor: C1, C2, C3

• Isolation transformer: T<sub>1</sub>

Primary voltage clamp: C<sub>R6</sub>, R<sub>24</sub>, C<sub>18</sub>

• Start bias regulator: R<sub>1</sub>, R<sub>2</sub>, R<sub>6</sub>, Q<sub>3</sub>, V<sub>R1</sub>

Operating bias and regulator: R<sub>25</sub>, Q<sub>2</sub>, D<sub>1</sub>, C<sub>5</sub>, C<sub>R2</sub>, D<sub>2</sub>

• Main MOSFET power switch: Q1

• Current sense network: R4, R3, R23, C4

• Feedback network: R<sub>13</sub>, R<sub>15</sub>, R<sub>16</sub>, R<sub>17</sub>, R<sub>18</sub>, R<sub>19</sub>, R<sub>20</sub>, R<sub>26</sub>, R<sub>27</sub>, C<sub>13</sub>, C<sub>14</sub>, U<sub>2</sub>, U<sub>3</sub>

• Control circuit:  $C_7$ ,  $C_8$ ,  $C_9$ ,  $C_{10}$ ,  $C_{11}$ ,  $C_{12}$ ,  $R_5$ ,  $R_6$ ,  $R_8$ ,  $R_9$ ,  $R_{10}$ ,  $R_{11}$ ,  $R_{12}$ ,  $R_{14}$ ,  $R_{22}$

Output rectification and filtering: C<sub>R4</sub>, C<sub>R5</sub>, C<sub>15</sub>, C<sub>16</sub>, C<sub>19</sub>,

C<sub>20</sub>, C<sub>21</sub>, C<sub>22</sub>

• Secondary snubber: R21, C17

#### **Design Criteria**

The following design requirements were selected:

Switching frequency, f<sub>sw</sub>: 200kHz

V<sub>IN</sub>: 36V to 75V

V<sub>OUT(1)</sub>: 3.3V at 2.5A

V<sub>OUT(2)</sub>: 1.8V at 1.0A

V<sub>OUT(BIAS)</sub>: 12V at 50mA

• P<sub>OUT</sub>: 10W

• Efficiency: 70%

• Maximum duty cycle, D<sub>MAX</sub>: 0.45

#### **Transformer Design**

The design of a Flyback transformer is a non-trivial affair. It is an iterative process, which requires a great deal of experience to achieve the desired result. It is a process of many compromises, and even experienced designers will produce different designs when presented with identical requirements. The iterative design process is not presented here for clarity.

The abbreviated design process follows:

- Select a core geometry suitable for the application.

Constraints of height, footprint, mounting preference, and operating environment will affect the choice.

- · Select suitable core material(s).

- Select maximum flux density desired for operation.

- Select core size. Core size will be dictated by the capability

of the core structure to store the required energy, the

number of turns that have to be wound and the wire gauge

needed. Often the window area (the space used for the

windings) and power loss determine the final core size. For

Flyback transformers, the ability to store energy is the

critical factor in determining the core size. The cross sectional area of the core and the length of the air gap in the magnetic path determine the energy storage capability.

- Determine maximum desired flux density. Depending on the frequency of operation, the core material selected, and the operating environment, the allowed flux density must be determined. The decision of what flux density to allow is often difficult to determine initially. Usually the highest flux density that produces an acceptable design is used, but often the winding geometry dictates a larger core than is required based on flux density and energy storage calculations.

- . Determine the number of primary turns.

- · Determine the turns ratio.

- · Select the wire gauge for each winding.

- · Determine winding order and insulation requirements.

- · Verify the design.

Input Power:

- P<sub>OUT</sub>/efficiency = 14.3W (use 15W)

- Max On time:  $t_{ON(MAX)} = D_{MAX}/f_{SW} = 2.25 \mu s$

- Average input current: I<sub>AVG(IN)</sub> = P<sub>IN</sub>/V<sub>IN(MIN)</sub> = 0.42A

**Peak Primary Current:**

$$I_{PPK} = \frac{2 \bullet I_{AVG(IN)}}{f_{sw} \bullet t_{ON(MAX)}} = 1.87 \qquad A$$

(EQ. 9)

**Maximum Primary Inductance:**

$$Lp(max) = \frac{V_{IN(MIN)} \bullet t_{ON(MAX)}}{I_{PPK}} = 43.3 \qquad \mu H$$

(EQ. 10)

Choose desired primary inductance to be 40µH.

The core structure must be able to deliver a certain amount of energy to the secondary on each switching cycle in order to maintain the specified output power.

$$\Delta w = P_{OUT} \bullet \frac{\langle V_{OUT} + Vd \rangle}{f_{sw} \bullet V_{OUT}}$$

joules (EQ. 11)

Where  $\Delta w$  is the amount of energy required to be transferred each cycle and Vd is the drop across the output rectifier.

The capacity of a gapped ferrite core structure to store energy is dependent on the volume of the airgap and can be expressed in Equation 12:

$$Vg = Aeff \bullet Ig = \frac{2 \bullet \mu_0 \bullet \Delta w}{\Delta B^2} \qquad m^3$$

(EQ. 12)

Where Aeff is the effective cross sectional area of the core in  $m^2$ , lg is the length of the airgap in meters,  $\mu_0$  is the permeability of free space  $(4\pi \bullet 10^{-7})$  and  $\Delta B$  is the change in flux density in Tesla.

A core structure having less airgap volume than calculated will be incapable of providing the full output power over some portion of its operating range. On the other hand, if the length of the airgap becomes large, magnetic field fringing around the

gap occurs. This has the effect of increasing the airgap volume. Some fringing is usually acceptable, but excessive fringing can cause increased losses in the windings around the gap resulting in excessive heating. Once a suitable core and gap combination are found, the iterative design cycle begins. A design is developed and checked for ease of assembly and thermal performance. If the core does not allow adequate space for the windings, then a core with a larger window area is required. If the transformer runs hot, it may be necessary to lower the flux density (more primary turns, lower operating frequency), select a less lossy core material, change the geometry of the windings (winding order), use heavier gauge wire or multi-filar windings, and/or change the type of wire used (Litz wire, for example).

For simplicity, only the final design is further described.

An EPCOS EFD 20/10/7 core using N87 material gapped to an  $A_L$  value of 25nH/ $N^2$  was chosen. It has more than the required air gap volume to store the energy required, but was needed for the window area it provides.

Aeff =

$$31 \cdot 10^{-6}$$

m<sup>2</sup>

$lg = 1.56 \cdot 10^{-3}$  m

The flux density  $\Delta \textbf{B}$  is only 0.069T or 690 gauss, a relatively low value.

Since:

$$L_{p} = \frac{\mu_{o} \cdot N_{p}^{2} \cdot Aeff}{Ig} \qquad \mu H$$

(EQ. 13)

The number of primary turns,  $N_p$ , may be calculated. The result is  $N_p = 40$  turns. The secondary turns may be calculated as follows:

$$N_{s} \leq \frac{Ig \bullet \langle Vout + Vd \rangle \bullet tr}{N_{p} \bullet Ippk \bullet \mu_{o} \bullet Aeff}$$

(EQ. 14)

Where tr is the time required to reset the core. Since discontinuous MMF mode operation is desired, the core must completely reset during the off time. To maintain discontinuous mode operation, the maximum time allowed to reset the core is  $t_{\text{SW}}$ -  $t_{\text{ON}(\text{MAX})}$  where  $t_{\text{SW}}$  =  $1/f_{\text{SW}}$ . The minimum time is application dependent and at the designers discretion knowing that the secondary winding RMS current and ripple current stress in the output capacitors increases with decreasing reset time. The calculation for maximum  $N_{\text{S}}$  for the 3.3 V output using t =  $t_{\text{SW}}$ -  $t_{\text{ON}\;(\text{MAX})}$  = 2.75 $\mu$ s is 5.52 turns.

The determination of the number of secondary turns is also dependent on the number of outputs and the required turns ratios required to generate them. If Schottky output rectifiers are used and we assume a forward voltage drop of 0.45V, the required turns ratio for the two output voltages, 3.3V and 1.8V, is 5:3.

With a turns ratio of 5:3 for the secondary windings, we will use  $N_{s1}=5$  turns and  $N_{s2}=3$  turns. Checking the reset time using these values for the number of secondary turns yields a duration of Tr = 2.33 $\mu$ s or about 47% of the switching period, an acceptable result.

The bias winding turns may be calculated similarly, only a diode forward drop of 0.7V is used. The rounded off result is 17 turns for a 12V bias.

The next step is to determine the wire gauge. The RMS current in the primary winding may be calculated using <u>Equation 15</u>:

$$I_{P(RMS)} = I_{PPK} \bullet \sqrt{\frac{t_{ON(MAX)}}{3 \bullet t_{SW}}}$$

A (EQ. 15)

The peak and RMS current values in the remaining windings may be calculated using <u>Equations 16</u> and <u>17</u>:

$$I_{SPK} = \frac{2 \cdot I_{OUT} \cdot t_{sw}}{Tr} \qquad A$$

(EQ. 16)

$$I_{RMS} = 2 \bullet I_{OUT} \bullet \sqrt{\frac{t_{SW}}{3 \bullet Tr}}$$

A (EQ. 17)

The RMS current for the primary winding is 0.72A, for the 3.3V output, 4.23A, for the 1.8V output, 1.69A, and for the bias winding, 85mA.

To minimize the transformer leakage inductance, the primary was split into two sections connected in parallel and positioned such that the other windings were sandwiched between them. The output windings were configured so that the 1.8V winding is a tap off of the 3.3V winding. Tapping the 1.8V output requires that the shared portion of the secondary conduct the combined current of both outputs. The secondary wire gauge must be selected accordingly.

The determination of current carrying capacity of wire is a compromise between performance, size, and cost. It is affected by many design constraints such as operating frequency (harmonic content of the waveform) and the winding proximity/geometry. It generally ranges between 250 and 1000 circular mils per ampere. A circular mil is defined as the area of a circle 0.001" (1 mil) in diameter. As the frequency of operation increases, the AC resistance of the wire increases due to skin and proximity effects. Using heavier gauge wire may not alleviate the problem. Instead multiple strands of wire in parallel must be used. In some cases, Litz wire is required.

The winding configuration selected is:

Primary #1: 40T, 2 #30 bifilar

Secondary: 5T, 0.003" (3 mil) copper foil tapped at 3T

Bias: 17T #32

Primary #2: 40T, 2 #30 bifilar

The internal spacing and insulation system was designed for 1500VDC dielectric withstand rating between the primary and secondary windings.

#### **Power MOSFET Selection**

Selection of the main switching MOSFET requires consideration of the voltage and current stresses that will be encountered in the application, the power dissipated by the device, its size, and its cost.

The input voltage range of the converter is 36VDC to 75VDC. This suggests a MOSFET with a voltage rating of 150V

is required due to the Flyback voltage likely to be seen on the primary of the isolation transformer.

The losses associated with MOSFET operation may be divided into three categories: conduction, switching and gate drive.

The conduction losses are due to the MOSFETs ON-resistance.

Pcond =

$$r_{DS(ON)} \cdot lprms^2$$

W (EQ. 18)

Where  $r_{DS(ON)}$  is the ON-resistance of the MOSFET and Iprms is the RMS primary current. Determining the conduction losses is complicated by the variation of  $r_{DS(ON)}$  with temperature. As junction temperature increases, so does  $r_{DS(ON)}$ , which increases losses and raises the junction temperature more, and so on. It is possible for the device to enter a thermal runaway situation without proper heatsinking. As a general rule of thumb, doubling the +25 °C  $r_{DS(ON)}$  specification yields a reasonable value for estimating the conduction losses at +125 °C junction temperature.

The switching losses have two components, capacitive switching losses and voltage/current overlap losses. The capacitive losses occur during turn-on of the device and may be calculated in <u>Equation 19</u>:

$$Pswcap = \frac{1}{2} \bullet Cfet \bullet V_{1N}^{2} \bullet f_{sw} \qquad W$$

(EQ. 19)

Where Cfet is the equivalent output capacitance of the MOSFET. Device output capacitance is specified on datasheets as Coss and is non-linear with applied voltage. To find the equivalent discrete capacitance, Cfet, a charge model is used. Using a known current source, the time required to charge the MOSFET drain to the desired operating voltage is determined and the equivalent capacitance may be calculated in Equation 20:

$$Cfet = \frac{lchg \cdot t}{V} \qquad F \tag{EQ. 20}$$

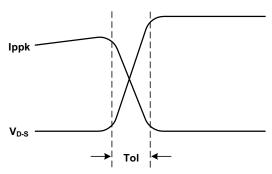

The other component of the switching loss is due to the overlap of voltage and current during the switching transition. A switching transition occurs when the MOSFET is in the process of either turning on or off. Since the load is inductive, there is no overlap of voltage and current during the turn-on transition, so only the turn-off transition is of significance. The power dissipation may be estimated using Equation 21:

$$P_{SW} \approx \frac{1}{x} \bullet I_{PPK} \bullet V_{IN} \bullet t_{OL} \bullet f_{SW}$$

(EQ. 21)

Where  $t_{OL}$  is the duration of the overlap period and x ranges from about 3 through 6 in typical applications and depends on where the waveforms intersect. This estimate may predict higher dissipation than is realized because a portion of the turn-off drain current is attributable to the charging of the device output capacitance (Coss) and is not dissipative during this portion of the switching cycle.

FIGURE 9. SWITCHING CYCLE

The final component of MOSFET loss is caused by the charging of the gate capacitance through the device gate resistance. Depending on the relative value of any external resistance in the gate drive circuit, a portion of this power will be dissipated externally.

Pgate =

$$Qg \cdot Vg \cdot f_{SW}$$

W (EQ. 22)

Once the losses are known, the device package must be selected and the heatsinking method designed. Since the design requires a small surface mount part, an 8 Ld SOIC package was selected. A Fairchild FDS2570 MOSFET was selected based on these criteria. The overall losses are estimated at 400mW.

#### **Output Filter Design**

In a Flyback design, the primary concern for the design of the output filter is the capacitor ripple current stress and the ripple and noise specification of the output.

The current flowing in and out of the output capacitors is the difference between the winding current and the output current. The peak secondary current,  $I_{SPK}$ , is 10.73A for the 3.3V output and 4.29A for the 1.8V output. The current flowing into the output filter capacitor is the difference between the winding current and the output current. Looking at the 3.3V output, the peak winding current is  $I_{SPK}$  = 10.73A. The capacitor must store this amount minus the output current of 2.5A, or 8.23A. The RMS ripple current in the 3.3V output capacitor is about 3.5A  $_{RMS}$ . The RMS ripple current in the 1.8V output capacitor is about 1.4A  $_{RMS}$ .

Voltage deviation on the output during the switching cycle (ripple and noise) is caused by the change in charge of the output capacitor, the Equivalent Series Resistance (ESR), and Equivalent Series Inductance (ESL). Each of these components must be assigned a portion of the total ripple and noise specification. How much to allow for each contributor is dependent on the capacitor technology used.

For purposes of this discussion, we will assume the following:

- 3.3V output: 100mV total output ripple and noise

- ESR: 60mV

- Capacitor ∆Q: 10mV

- ESL: 30mV

- 1.8V output: 50mV total output ripple and noise

- ESR: 30mV

- Capacitor ∆Q: 5mV

- ESL: 15mV

#### For the 3.3V output:

$$ESR \le \frac{\Delta V}{I_{SPK} - I_{OUT}} = \frac{0.060}{10.73 - 2.5} = 7.3 \text{m}\Omega$$

(EQ. 23)

The change in voltage due to the change in charge of the output capacitor,  $\Delta Q$ , determines how much capacitance is required on the output.

$$C \ge \frac{(Ispk-Iout) \bullet Tr}{2 \bullet \Delta V} = \frac{(10.73-2.5) \bullet 2.33 \times 10^{-6}}{2 \bullet 0.010} = 960 \mu F \tag{EQ. 24}$$

ESL adds to the ripple and noise voltage in proportion to the rate of change of current into the capacitor (V = L  $\bullet$  di/dt).

$$L \le \frac{V \cdot dt}{di} = \frac{0.030 \cdot 200 \times 10^{-9}}{10.73} = 0.56 \text{nH}$$

(EQ. 25)

Capacitors having high capacitance usually do not have sufficiently low ESL. High frequency capacitors such as surface mount ceramic or film are connected in parallel with the high capacitance capacitors to address the effects of ESL. A combination of high frequency and high ripple capability capacitors is used to achieve the desired overall performance. The analysis of the 1.8V output is similar to that of the 3.3V output and is omitted for brevity. Two OSCON 4SEP560M (560µF) electrolytic capacitors and a 22µF X5R ceramic 1210 capacitor were selected for both the 3.3 and 1.8V outputs. The 4SEP560M electrolytic capacitors are each rated at 4520mA ripple current and 13m $\Omega$  of ESR. The ripple current rating of just one of these capacitors is adequate, but two are needed to meet the minimum ESR and capacitance values.

The bias output is of such low power and current that it places negligible stress on its filter capacitor. A single  $0.1\mu F$  ceramic capacitor was selected.

#### **Control Loop Design**

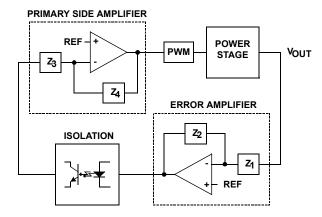

The major components of the feedback control loop are a programmable shunt regulator, an opto-coupler, and the inverting amplifier of the ISL6721. The opto-coupler is used to transfer the error signal across the isolation barrier. The opto-coupler offers a convenient means to cross the isolation barrier, but it adds complexity to the feedback control loop. It adds a pole at about 10kHz and a significant amount of gain variation due the Current Transfer Ratio (CTR). The CTR of the opto-coupler varies with initial tolerance, temperature, forward current and age.

A block diagram of the feedback control loop is shown in Figure 10.

FIGURE 10. FEEDBACK CONTROL LOOP

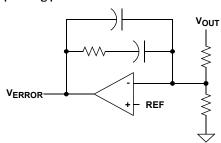

The loop compensation is placed around the Error Amplifier (EA) on the secondary side of the converter. The primary side amplifier located in the control IC is used as a unity gain inverting amplifier and provides no loop compensation. A Type 2 error amplifier configuration was selected as a precaution in case operation in continuous mode should occur at some operating point.

FIGURE 11. TYPE 2 ERROR AMPLIFIER

Development of a small signal model for current mode control is rather complex. The method of reference (1) was selected for its ability to accurately predict loop behavior. To further simplify the analysis, the converter will be modeled as a single output supply with all of the output capacitance reflected to the 3.3V output. Once the "single" output system is compensated, adjustments to the compensation will be required based on actual loop measurements.

The first parameter to determine is the peak current feedback loop gain. Since this application is low power, a resistor in series with the source of the power switching MOSFET is used for the current feedback signal. For higher power applications, a resistor would dissipate too much power and current transformer would be used instead.

There is limited flexibility to adjust the current loop behavior due to the need to provide overcurrent protection. Current limit and the current loop gain are determined by the current sense resistor and the ISET threshold. ISET was set at 1.0V, near its maximum, to minimize noise effects. When determining ISET, the internal gain and offset of the ISENSE signal in the control IC must be taken into account. The maximum peak primary current was determined earlier to be 1.87A, so a choice of

2.25A peak primary current for current limit is reasonable. A current gain, AFXT, of 0.5V/A was selected to achieve this.

ISET =

$$2.25 \cdot 0.8 \cdot 0.5 + 0.100 = 1.00$$

V (EQ. 26)

The control to output transfer function may be represented as Equation 27. (see reference 2):

$$\frac{v_o}{v_c} = K \bullet \sqrt{\frac{R_o \bullet L_s \bullet f_{sW}}{2}} \bullet \frac{1 + \frac{s}{\omega_z}}{1 + \frac{s}{\omega_p}}$$

(EQ. 27)

If we ignore the current feedback sampled-data effects:

$$K = \frac{I_{spk(max)}}{V_{c(max)}}$$

(EQ. 28)

$$R_0 = Load Resistance$$

(EQ. 29)

$$L_s$$

= Secondary Inductance (EQ. 30)

$$\omega_{p} = \frac{2}{R_{o} \cdot C_{o}} \qquad \text{or} \qquad f_{p} = \frac{1}{\pi \cdot R_{o} \cdot C_{o}}$$

$$\omega_{z} = \frac{1}{R_{c} \cdot C_{o}} \qquad \text{or} \qquad f_{z} = \frac{1}{2 \cdot \pi \cdot R_{c} \cdot C_{o}}$$

(EQ. 31)

$$\omega_z = \frac{1}{R_c \cdot C_o}$$

or  $f_z = \frac{1}{2 \cdot \pi \cdot R_c \cdot C_o}$  (EQ. 32)

$$C_0$$

= Output Capacitance (EQ. 33)

$$R_c = \text{Output Capacitor ESR}$$

(EQ. 34)

$$V_{c(max)} = Control Voltage Range$$

(EQ. 35)

The value of K may be determined by assuming all of the output power is delivered by the 3.3V output at the threshold of current limit. The maximum power allowed was determined earlier as 15W, therefore:

$$I_{spk(max)} = \frac{2 \cdot \frac{P_{out}}{V_{out}} \cdot t_{sw}}{Tr} = \frac{2 \cdot \frac{15}{3.3} \cdot 5 \times 10^{-6}}{2.33 \times 10^{-6}} = 19.5$$

(EQ. 36)

$$v_{c(max)} = V_{ISENSE} \bullet A_{EXT} \bullet A_{CS} \bullet \frac{1}{A_{COMP}} = 2.93$$

V (E0. 37)

Where A<sub>EXT</sub> is the external gain of the current feedback network,  $A_{\mbox{\footnotesize{CS}}}$  is the IC internal gain, and  $A_{\mbox{\footnotesize{COMP}}}$  is the gain between the error amplifier and the PWM comparator.

The Type 2 compensation configuration has two poles and one zero. The first pole is at the origin, and provides the integration characteristic which results in excellent DC regulation. Referring to the Typical Application Schematic on page 5, the remaining pole and zero for the compensator are located at:

$$f_{pc} = \frac{C_{13} + C_{14}}{2 \bullet \pi \bullet R_{15} \bullet C_{14} \bullet C_{13}} \approx \frac{1}{2 \bullet \pi \bullet R_{15} \bullet C_{14}}$$

(EQ. 38)

$$f_{zc} = \frac{1}{2 \cdot \pi \cdot R_{15} \cdot C_{13}}$$

(EQ. 39)

The ratio of  $R_{15}$  to the parallel combination of  $R_{17}$  and  $R_{18}$ determine the mid band gain of the error amplifier.

$$A_{midband} = \frac{R_{15} \bullet (R_{17} + R_{18})}{R_{17} \bullet R_{18}}$$

(EQ. 40)

From Equation 27, it can be seen that the control to output transfer function frequency dependence is a function of the output load resistance, the value of output capacitance, and the output capacitor ESR. These variations must be considered when compensating the control loop. The worst case small signal operating point for the converter is at minimum VIN, maximum load, maximum COLIT and minimum ESR.

The higher the desired bandwidth of the converter, the more difficult it is to create a solution that is stable over the entire operating range. A good rule of thumb is to limit the bandwidth to about f<sub>sw</sub>/4. For this example, the bandwidth will be further limited due to the low GBWP of the LM431-based Error Amplifier and the opto-coupler. A bandwidth of approximately 5kHz was selected.

For the EA compensation, the first pole is placed at the origin by default (C<sub>14</sub> is an integrating capacitor). The first zero is placed below the crossover frequency,  $f_{\text{co}}$ , usually around 1/3fco. The second pole is placed at the lower of the ESR zero or at one half of the switching frequency. The midband gain is then adjusted to obtain the desired crossover frequency. If the phase margin is not adequate, the crossover frequency may have to be reduced.

Using this technique to determine the compensation, the following values for the EA components were selected.

$$R_{17} = R_{18} = R_{15} = 1k\Omega$$

$$C_{13} = 100 nF$$

$$C_{14} = 100pF$$

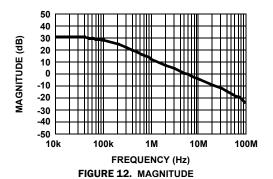

A Bode plot of the system at low line, maximum load appears in Figures 12 and 13.

200 150 100 50 -50 -100 10k 100k 1M 10M 100M FREQUENCY (Hz)

FIGURE 13. PHASE

#### **Regulation Performance**

TABLE 2. OUTPUT LOAD REGULATION,  $V_{IN} = 48V$

| I <sub>OUT</sub> (A), 3.3V | I <sub>OUT</sub> (A), 1.8V | V <sub>OUT</sub> (V), 3.3V | V <sub>OUT</sub> (V), 1.8V |

|----------------------------|----------------------------|----------------------------|----------------------------|

| 0                          | 0.030                      | 3.351                      | 1.825                      |

| 0.39                       | 0.030                      | 3.281                      | 1.956                      |

| 0.88                       | 0.030                      | 3.251                      | 1.988                      |

| 1.38                       | 0.030                      | 3.223                      | 2.014                      |

| 1.87                       | 0.030                      | 3.204                      | 2.029                      |

| 2.39                       | 0.030                      | 3.185                      | 2.057                      |

| 2.89                       | 0030                       | 3.168                      | 2.084                      |

| 3.37                       | 0.030                      | 3.153                      | 2.103                      |

| 0                          | 0.52                       | 3.471                      | 1.497                      |

| 0.39                       | 0.52                       | 3.283                      | 1.800                      |

| 0.88                       | 0.52                       | 3.254                      | 1.836                      |

| 1.38                       | 0.52                       | 3.233                      | 1.848                      |

| 1.87                       | 0.52                       | 3.218                      | 1.855                      |

| 2.39                       | 0.52                       | 3.203                      | 1.859                      |

| 2.89                       | 0.52                       | 3.191                      | 1.862                      |

| 0                          | 1.05                       | 3.619                      | 1.347                      |

| 0.39                       | 1.05                       | 3.290                      | 1.730                      |

| 0.88                       | 1.05                       | 3.254                      | 1.785                      |

TABLE 2. OUTPUT LOAD REGULATION, V<sub>IN</sub> = 48V (Continued)

| I <sub>OUT</sub> (A), 3.3V | I <sub>OUT</sub> (A), 1.8V | V <sub>OUT</sub> (V), 3.3V | V <sub>OUT</sub> (V), 1.8V |

|----------------------------|----------------------------|----------------------------|----------------------------|

| 1.38                       | 1.05                       | 3.235                      | 1.805                      |

| 1.87                       | 1.05                       | 3.220                      | 1.814                      |

| 2.39                       | 1.05                       | 3.207                      | 1.820                      |

| 0                          | 1.55                       | 3.699                      | 1.265                      |

| 0.39                       | 1.55                       | 3.306                      | 1.682                      |

| 0.88                       | 1.55                       | 3.260                      | 1.750                      |

| 1.38                       | 1.55                       | 3.239                      | 1.776                      |

| 1.87                       | 1.55                       | 3.224                      | 1.789                      |

| 0                          | 2.07                       | 3.762                      | 1.201                      |

| 0.39                       | 2.07                       | 3.329                      | 1.645                      |

| 0.88                       | 2.07                       | 3.270                      | 1.722                      |

| 1.38                       | 2.07                       | 3.245                      | 1.752                      |

| 0                          | 2.62                       | 3.819                      | 1.142                      |

| 0.39                       | 2.62                       | 3.355                      | 1.612                      |

| 0.88                       | 2.62                       | 3.282                      | 1.697                      |

| 0                          | 3.14                       | 3.869                      | 1.091                      |

| 0.39                       | 3.14                       | 3.383                      | 1.581                      |

#### **Waveforms**

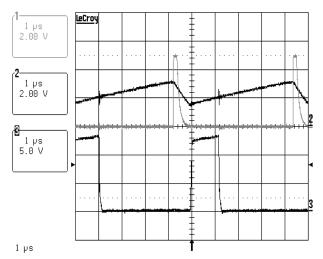

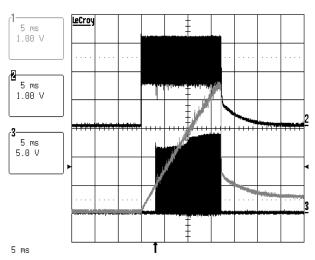

Typical waveforms can be found in Figures 14 through 16. Figure 14 shows the steady state operation of the sawtooth oscillator waveform at RTCT (Trace 2) the SYNC output pulse (Trace 1) and the GATE output to the converter FET (Trace 3). Figure 15 shows the converter behavior while operating in an overcurrent fault condition. Trace 1 is the soft-start voltage, which increases from OV to 4.5V, at which point the OC fault function is enabled. The OC condition is detected and the soft-start capacitor is discharged to the 4.375V OC fault threshold at which point the IC enters the fault shutdown mode. Trace 2 shows the behavior of the timing capacitor voltage during a shutdown fault. Most of the functions of the IC are depowered during a fault, and the oscillator is among those functions. During a fault, the IC is turned off until the restart delay has timed out. After the delay, power is restored and the IC resumes normal operation. Trace 3 is the GATE output during the soft-start cycle and OC fault.

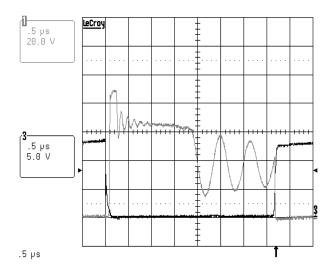

<u>Figure 16</u> shows the switching FET waveforms during steady state operation. Trace 1 is drain-source voltage and Trace 2 is gate-source voltage

NOTE:

Trace 1: SYNC Output

Trace 2: RTCT Sawtooth

Trace 3: GATE Output

FIGURE 14. TYPICAL WAVEFORMS

NOTE:

Trace 1: SS

Trace 2: RTCT Sawtooth Trace 3: GATE Output

FIGURE 15. SOFT-START WITH OVERCURRENT FAULT

NOTE:

Trace 1: VD-S

Trace 3: VG-S

FIGURE 16. GATE AND DRAIN-SOURCE WAVEFORMS

### References

- Ridley, R., "A New Continuous-Time Model for Current Mode Control", IEEE Transactions on Power Electronics, Vol. 6, No. 2, April 1991.

- Dixon, Lloyd H., "Closing the Feedback Loop", Unitrode Power Supply Design Seminar, SEM-700, 1990.

# **Component List**

| REFERENCE DESIGNATOR                                                                                      | VALUE  | DESCRIPTION                               |

|-----------------------------------------------------------------------------------------------------------|--------|-------------------------------------------|

| c <sub>1</sub> , c <sub>2</sub> , c <sub>3</sub>                                                          | 1.0µF  | Capacitor, 1812, X7R, 100V, 20%           |

| C <sub>5</sub> , C <sub>13</sub>                                                                          | 0.1µF  | Capacitor, 0603, X7R, 25V, 10%            |

| C <sub>15</sub> , C <sub>16</sub> , C <sub>19</sub> , C <sub>20</sub>                                     | 560µF  | Capacitor, Radial, SANYO 4SEP560M         |

| C <sub>17</sub>                                                                                           | 470pF  | Capacitor, 0603, COG, 50V, 5%             |

| C <sub>18</sub>                                                                                           | 0.01μF | Capacitor, 0805, X7R, 50V, 10%            |

| C <sub>21</sub> , C <sub>22</sub>                                                                         | 22µF   | Capacitor, 1210, X5R, 10V, 20%            |

| C <sub>4</sub> , C <sub>14</sub>                                                                          | 100pF  | Capacitor, 0603, COG, 50V, 5%             |

| C <sub>6</sub>                                                                                            | 1500pF | Capacitor, Disc, Murata DE1E3KX152MA5BA01 |

| C <sub>7</sub>                                                                                            |        | 0Ω Jumper, 0603                           |

| c <sub>8</sub>                                                                                            | 330pF  | Capacitor, 0603, COG, 50V, 5%             |

| C <sub>9</sub> , C <sub>10</sub> , C <sub>11</sub> , C <sub>12</sub>                                      | 0.22µF | Capacitor, 0603, X7R, 16V, 10%            |

| C <sub>R2</sub> , C <sub>R6</sub>                                                                         |        | Diode, Fairchild ES1C                     |

| C <sub>R4</sub> , C <sub>R5</sub>                                                                         |        | Diode, IR 12CWQ03FN                       |

| D <sub>1</sub>                                                                                            |        | Zener, 18V, Zetex BZX84C18                |

| D <sub>2</sub>                                                                                            |        | Diode, Schottky, BAT54C                   |

| Q <sub>1</sub>                                                                                            |        | FET, Fairchild FDS2570                    |

| Q <sub>2</sub>                                                                                            |        | Transistor, Zetex FMMT491A                |

| Q <sub>3</sub>                                                                                            |        | Transistor, ON MJD31C                     |

| R <sub>1</sub> , R <sub>2</sub>                                                                           | 1.00k  | Resistor, 1206, 1%                        |

| R <sub>10</sub>                                                                                           | 20.0k  | Resistor, 0603, 1%                        |

| R <sub>7</sub> , R <sub>9</sub> , R <sub>11</sub> , R <sub>26</sub> , R <sub>27</sub>                     | 10.0k  | Resistor, 0603, 1%                        |

| R <sub>12</sub>                                                                                           | 38.3k  | Resistor, 0603, 1%                        |