### ISL68200DEMO1Z

### Demonstration Board User Guide

UG067 Rev.2.00 Aug 23, 2017

The <u>ISL68200</u> is a single-phase synchronous buck PWM controller featuring Intersil's proprietary R4<sup>™</sup> Technology, which has extremely fast transient performance, accurately regulated frequency control, and all internal compensation. The ISL68200 supports a wide 4.5V to 24V input voltage range and a wide 0.5V to 5.5V output range. It includes programmable functions and telemetries for easy use and high system flexibility using SMBus, PMBus, or I<sup>2</sup>C interface. See the ISL68200 datasheet for more details.

The ISL68200DEM01Z is a 6-layer board demonstrating a compact 17mmx17mm 20A synchronous buck converter. Transient performance, fault protections, DC/AC regulations, PMBus programming, power sequencing, margining, and other features can be evaluated using this board.

The PMBus dongle (ZLUSBEVAL3Z USB-to-PMBus adapter) and USB cable are included with the demonstration board. Intersil's evaluation software can be installed from Intersil's website and be used to evaluate the full PMBus functionality of the part using a PC running Microsoft Windows.

## **Related Literature**

- · For a full list of related documents, visit our website

- ISL68200 product page

- Intersil's <u>PowerNavigator</u> User Guide

### **Key Features**

- 20A synchronous buck converter with PMBus control

- · On-board transient load with adjustable di/dt

- Configurable through resistor pins

- Cascadeable PMBus connectors

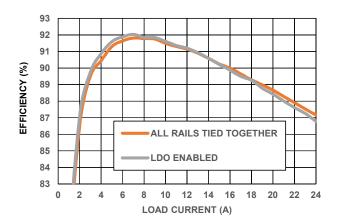

- Integrated LDOs for a single rail solution

- · Enable switch and power-good indicator

- · All ceramics solution with SP capacitor footprint option

### **Target Specifications**

- V<sub>IN</sub> = 4.75V to 14.5V

- V<sub>OUT</sub> = 1V/20A full load

- f<sub>SW</sub> = 400kHz

- Peak efficiency:

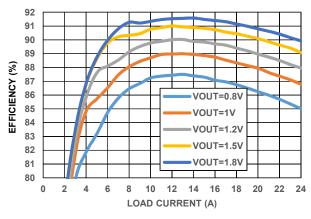

- 89% at 12A/1V<sub>OUT</sub>/12V<sub>IN</sub>

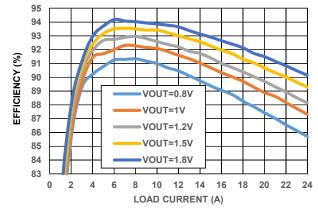

- 94% at 6A/1.8V<sub>OUT</sub>/5V<sub>IN</sub>

- Output regulation: 1V ±8mV

- I/O capacitor rating: C<sub>IN</sub> 16V; C<sub>OUT</sub> 4V

- Compact size: 17mmx17mm

- With or without PMBus, SMBus, and I<sup>2</sup>C Capability

## **Ordering Information**

| PART NUMBER | DESCRIPTION                                                                             |  |

|-------------|-----------------------------------------------------------------------------------------|--|

|             | ISL68200 Demonstration Board (Items shipped:<br>Demonstration board, dongle, USB cable) |  |

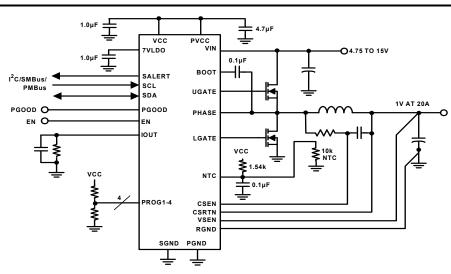

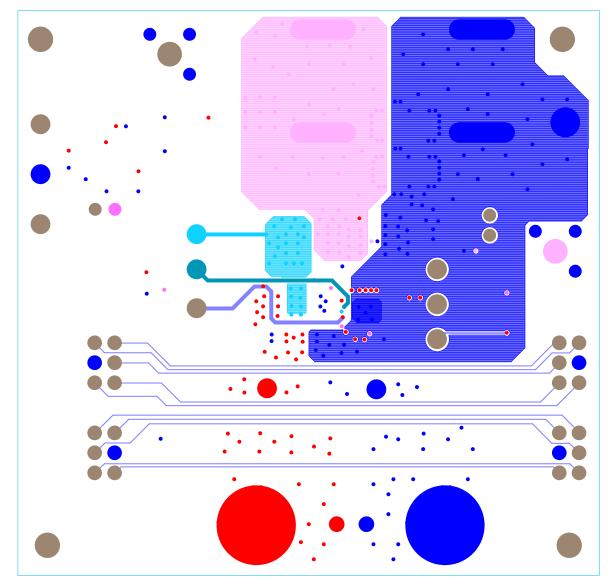

FIGURE 1. ISL68200DEM01Z SIMPLIFIED SCHEMATIC

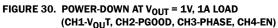

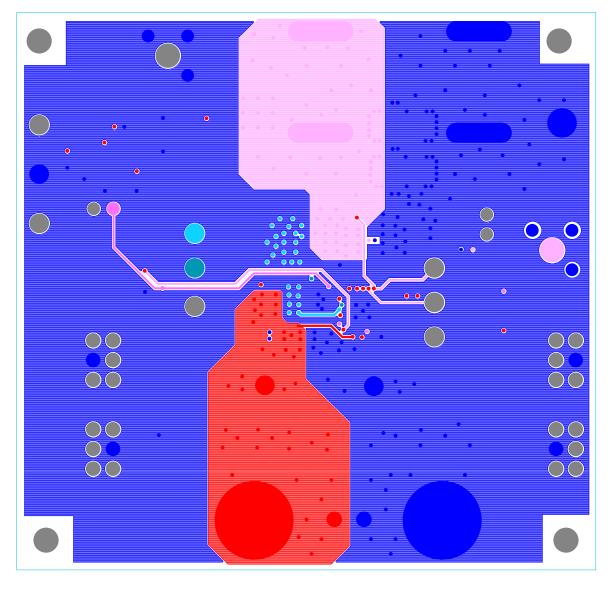

FIGURE 2. DEMONSTRATION BOARD TOP VIEW

### Demonstration Board Description

The ISL68200DEM01Z provides all circuitry required to demonstrate the key features of the ISL68200. A majority of the features of the ISL68200, such as optimal transient response with Intersil's R4 Modulator, 8-bit programmable boot voltage levels, selectable switching frequency in continuous conduction mode, selectable PFM operation option for improved light-load efficiency, power-good monitor for soft-start and fault detection, over-temperature protection, output overcurrent and short-circuit protection, and output overvoltage protection are available on this demonstration board.

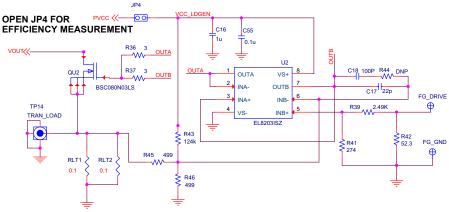

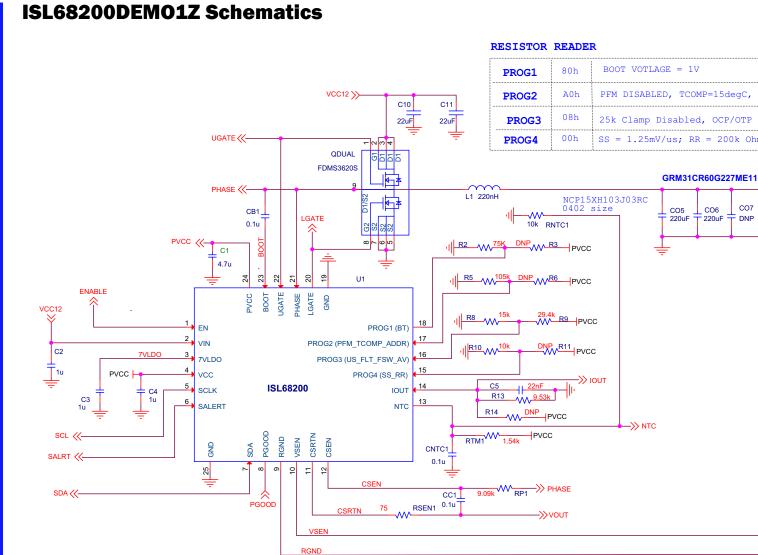

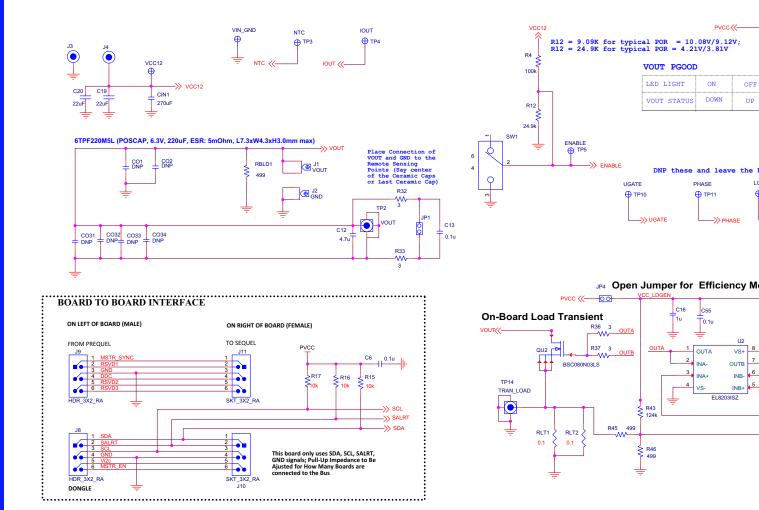

Figure 1 shows a simplified schematic diagram of the ISL68200DEMO1Z board. Figure 6 shows the detailed 20A buck solution schematics, while Figure 7 shows the I/O connectors, auxiliary circuits and on-board transient circuits. Figures 8 through 30 show typical performance data and Figures 31 through 36 show the PCB board layout. The default programming pins setting is given on the upper right corner of Figure 7, and the Bill of Materials (BOM) is included for reference beginning on page 9.

The ISL68200DEMO1Z board can run by itself without a serial bus communication. The operational configuration is fully programmable using programming pins (PROG1-4).

The ISL68200 however, uses the PMBus/SMBus/I<sup>2</sup>C protocol and provides the flexibility for digital power management and performance optimization before finalizing the hardware configuration on the programming pins.

The buck regulator in the ISL68200DEM01Z board is a single input rail design, that is, everything is biased by the input supply (typically 12V). The resistor divider on the EN pin ( $R_4$  and  $R_{12}$ ) can set the input supply undervoltage protection level and its hysteresis. The "ENABLE" switch is a hardware operational control, alternately, the serial bus ON\_OFF\_CONFIG and OPERATION commands can be used for software operational control.

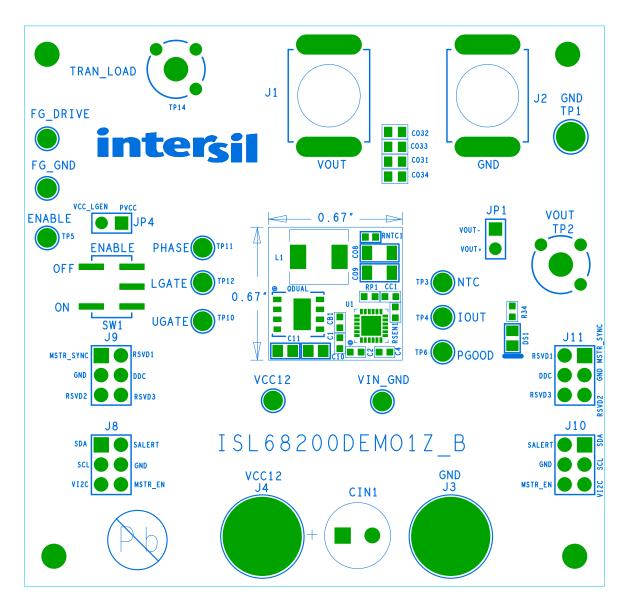

FIGURE 3. DEMONSTRATION BOARD BOTTOM VIEW

Furthermore, an on-board transient load, as shown in Figure 7, with both di/dt and load step amplitude is controlled by a function generator. Because this auxiliary circuit draws more than 10A of bias current, the jumper on JP5 should be removed for accurate efficiency measurement.

Intersil's PowerNavigator evaluation software is compatible with Windows operating systems and can be used to evaluate the serial bus functionality of the ISL68200. The software and user guide can be found at: <u>http://www.intersil.com/powernavigator</u>

# **Quick Start Guide**

### Stand-Alone Operation

- 1. Set the ENABLE switch to the "OFF" position.

- 2. Connect a power supply (off) to input connectors (J4-VIN and J3-GND).

- 3. Set the input power supply voltage level (no more than 15V) and current limiting (no more than 1A for 0A load).

- 4. Turn the power supply on.

- 5. Set the ENABLE switch to the "ON" position.

- 6. Increase the power supply current limit enough to support more than the full load.

- 7. Apply load to the output connectors (J1-VOUT and J2-SGND).

- 8. Monitor operation using an oscilloscope.

#### **PMBus Operation**

- 1. Connect the supplied dongle to J8.

- 2. Connect the supplied USB cable from the computer to the dongle.

- 3. After the input power supply turns on, open the PowerNavigator™ evaluation software.

- 4. Select the detected ISL68200 device (Address 60h) and follow Intersil's PowerNavigator operation guide.

- 5. Monitor and configure the board using PMBus commands in the evaluation software.

## Configuration

The default programming pins setting of the ISL68200DEM01Z board can be found at the resistor reader table on the upper right corner of <u>"ISL68200DEM01Z Schematics" on page 7</u> or read back using the PowerNavigator software. Each PMBus command can be loaded or programmed through the PowerNavigator software. Note that ISL68200 does not have NVM to store the operational configuration, which can however be set by the resistor programming pins (PROG1-4) or programmed by the serial bus master before powering up. If a serial bus master is available in the system, the ISL68200-based rail can be fully controlled using the software for the power-up/down sequencing and operational configuration without a soldering iron.

### **Load Transient**

The on-board transient load can be controlled by a function generator, whose inputs are connected to FG\_DRIVE2 and FG\_GND2. The function generator's output is terminated by R42 at the input terminal, while its amplitude and dV/dt set the load amplitude and di/dt on the 50m $\Omega$  load (R<sub>LT1</sub>//R<sub>LT2</sub>). The transient load can be monitored with a scope probe on TP15. Note that the duty cycle of applied load should be less than 10% duty cycle with <10ms pulse width to keep the average power of R<sub>LT1</sub>//R<sub>LT2</sub> less than its power rating.

FIGURE 4. LOAD TRANSIENT

FIGURE 5. ISL68200 DEMONSTRATION BOARD SETUP

# **Design Modifications**

Any modifications to the design will require new L/DCR matching for a different inductor, a divider on the PROG pins for a different operational configuration, RSEN1 for OCP, and an IOUT network for accurate digital IOUT, a higher input capacitor rating to support higher than 16V input, and a higher output capacitor rating to support higher than 4V output. Refer to the ISL68200 datasheet and PowerNavigator software for proper design modifications including L/DCR matching, thermal compensation, OCP, and digital I<sub>OUT</sub> fine-tuning.

Two examples are provided in <u>Table 1</u>, showing the recommended design modifications to accommodate the application cases with 5V and 3.3V output voltages. Some

fine-tuning might be needed depending upon the rework and final layout design.

For the 5V input voltage applications with 4.5V < V<sub>IN</sub> < 5.5V requirement, the VIN, VCC, PVCC, and 7VLDO pins should be shorted together, to connect with the input supply for optimal performance;  $R_{12}$  should be removed as well.

Note that all devices in the same bus should set different addresses for unique identification and proper communication. JP2, JP3, JP9, and JP10 connectors are designed to cascade many Intesil's solutions for easy communication and system evaluation before the system integration and design.

| REFERENCE<br>DESIGNATOR | 5.0V AT 16A                                                          | 3.3V AT 16A     | 3.3V AT 30A                                                           | COMMENTS                                                                                                                                                    |  |

|-------------------------|----------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L1                      | 680nH, 1.72mΩ<br>Vendor: Wurth Electronic;<br>Part Number: 744334006 |                 | 470nH, 0.165mΩ<br>Vendor: Wurth Electronic;<br>Part Number: 744309047 | Reduce Output ripple current; typically higher voltage output needs higher inductance.                                                                      |  |

| C05, C06, C08,<br>C09   | Vendor: Murata;                                                      |                 |                                                                       | Increase C <sub>OUT</sub> rating to support higher V <sub>OUT</sub> .<br>Also capacitance of ceramic capacitors<br>decreases with increased output voltage. |  |

| PROG1 (DC)              | DFh                                                                  | BFh             | BFh                                                                   | Set correct V <sub>BOOT</sub> = V <sub>OUT</sub>                                                                                                            |  |

| R <sub>3</sub>          | 147k, 1%                                                             | 105k, 1%        | 105k, 1%                                                              |                                                                                                                                                             |  |

| PROG2 (DD)              | AOh                                                                  | BFh             | BFh                                                                   | Set Different PMBus Addresses as needed                                                                                                                     |  |

| R <sub>5</sub>          | 105k, 1%                                                             | DNP             | DNP                                                                   | T <sub>COMP</sub> = 15<br>PFM DISABLED                                                                                                                      |  |

| R <sub>6</sub>          | DNP                                                                  | 105k, 1%        | 105k, 1%                                                              |                                                                                                                                                             |  |

| PROG3 (DE)              | 0Dh                                                                  | 0Dh             | ODh                                                                   | Set AV = 13                                                                                                                                                 |  |

| R <sub>8</sub>          | 24.3k, 1%                                                            | 24.3k, 1%       | 24.3k, 1%                                                             | f <sub>SW</sub> = 500kHz<br>OCP = Retry                                                                                                                     |  |

| R <sub>9</sub>          | 16.9k, 1%                                                            | 16.9k, 1%       | 16.9k, 1%                                                             | 25kHz Clamp Disabled                                                                                                                                        |  |

| PROG4 (DF)              | 08h                                                                  | 08h             | 08h                                                                   | Set RR = 400k                                                                                                                                               |  |

| R <sub>10</sub>         | 15k, 1%                                                              | 15k, 1%         | 15k, 1%                                                               | SS = 1.25mV/µs<br>AVMLTI = 1 x                                                                                                                              |  |

| R <sub>11</sub>         | 29.4k, 1%                                                            | 29.4k, 1%       | 29.4k, 1%                                                             |                                                                                                                                                             |  |

| R <sub>P1</sub>         | 4.99k, 1%                                                            | 4.99k, 1%       | 3.57k, 1%                                                             | L/DCR Matching                                                                                                                                              |  |

| R <sub>SEN1</sub>       | 536, 1%                                                              | 536, 1%         | 62, 1%                                                                | Set OCP                                                                                                                                                     |  |

| R <sub>13</sub>         | 11k, 1%                                                              | <b>11</b> k, 1% | 15k, 1%                                                               | Set I <sub>OUT</sub> to 1A/1A Slope                                                                                                                         |  |

| R <sub>14</sub>         | TBD                                                                  | TBD             | TBD                                                                   | Pull-up value depends upon final layout design                                                                                                              |  |

#### TABLE 1. DESIGN EXAMPLES

NOTE:

1. Some fine-tuning might be needed depending upon the rework and final layout design.

### Design and Layout Considerations

To ensure a first pass design, the schematics design must be done correctly and the board must be carefully laid out.

As a general rule, power layers should be close together, either on the top or bottom of the board, with the weak analog or logic signal layers on the opposite side of the board or internal layers. The ground-plane layer should be in between the power layers and the signal layers to provide shielding, often the layer below the top and the layer above the bottom should be the ground layers.

There are two sets of components in a DC/DC converter, the power components and the small signal components. The power components are the most critical because they switch large amount of energy. The small signal components connect to sensitive nodes or supply critical bypassing current and signal coupling.

The power components should be placed first and these include MOSFETs, input and output capacitors, and the inductor. Keeping the distance between the power train and the control IC short helps keep the gate drive traces short. These drive signals include the LGATE, UGATE, GND, PHASE, and BOOT.

When placing MOSFETs, try to keep the source of the upper MOSFETs and the drain of the lower MOSFETs as close as thermally possible. Input high frequency capacitors should be placed close to the drain of the upper MOSFETs and the source of the lower MOSFETs. Place the output inductor and output capacitors between the MOSFETs and the load. High frequency output decoupling capacitors (ceramic) should be placed as close as possible to the decoupling target, making use of the shortest connection paths to any internal planes. Place the components in such a way that the area under the IC has less noise traces with high dV/dt and di/dt, such as gate signals, phase node signals, and the VIN plane.

Tables 2 and 3 provide design and layout checklist that the designer must pay attention to.

#### TABLE 2. DESIGN AND LAYOUT CHECKLIST

| PIN<br>NAME | NOISE<br>SENSITIVITY | DESCRIPTION                                                                                                                                              |

|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN          | Yes                  | There is an internal 1µs filter. Decoupling the capacitor is NOT needed, but if needed, use a low time constant one to avoid too large a shutdown delay. |

| VIN         | Yes                  | Place 16V+ X7R 1µF in close proximity to the VIN pin and the system ground plane.                                                                        |

| 7VLDO       | Yes                  | Place 10V+ X7R 1µF in close proximity to the 7VLDO pin and the system ground plane.                                                                      |

| VCC         | Yes                  | Place X7R 1µF in close proximity to the VCC pin and the system ground plane.                                                                             |

#### TABLE 2. DESIGN AND LAYOUT CHECKLIST (Continued)

| IABLE 2. DESIGN AND LAYOUT CHECKLIST (Continued) |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN<br>NAME                                      | NOISE<br>SENSITIVITY | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SCL, SDA                                         | Yes                  | 50kHz to 1.25MHz signal when the SMBus,<br>PMBus, or I <sup>2</sup> C is sending commands. Pairing<br>up with SALERT and routing carefully back to<br>SMBus, PMBus, or I <sup>2</sup> C master. 20 mils spacing<br>within SDA, SALERT, and SCL; and more than<br>30 mils to all other signals. Refer to the<br>SMBus, PMBus, or I <sup>2</sup> C design guidelines and<br>place proper terminated (pull-up) resistance<br>for impedance matching. Tie them to GND<br>when not used.          |  |  |

| SALERT                                           | No                   | Open-drain and high dv/dt pin during<br>transitions. Route it in the middle of SDA and<br>SCL. Tie it to GND when not used.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PGOOD                                            | No                   | Open-drain pin. Tie it to ground when not used.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RGND,<br>VSEN                                    | Yes                  | Differential pair routed to the remote sensing<br>points with sufficient decoupling ceramics<br>capacitors and not across or go above/under<br>any switching nodes (BOOT, PHASE, UGATE,<br>LGATE) or planes (VIN, PHASE, VOUT) even<br>though they are not in the same layer. At least<br>20 mils spacing from other traces. DO NOT<br>share the same trace with CSRTN.                                                                                                                      |  |  |

| CSRTN                                            | Yes                  | Connect to the output rail side of the output inductor or current sensing resistor pin with series resistor in close proximity to the pin. Th series resistor sets the current gain and shou be within $40\Omega$ and $3.5k\Omega$ . Decoupling (~ $0.1\mu$ F/X7R) on the output end (not the pin is optional and might be required for long sense trace and a poor layout.                                                                                                                  |  |  |

| CSEN                                             | Yes                  | Connect to the phase node side of the output<br>inductor or current sensing resistor pin with<br>L/DCR or ESL/R <sub>SEN</sub> matching network in close<br>proximity to the CSEN and CSRTN pins.<br>Differentially routing back to the controller<br>with at least 20 mils spacing from other<br>traces. Should NOT cross or go above/under<br>the switching nodes [BOOT, PHASE, UGATE,<br>LGATE] and power planes (VIN, PHASE, VOUT)<br>even though they are not in the same layer.        |  |  |

| NTC                                              | Yes                  | Place NTC 10k (Murata, NCP15XH103J03RC,<br>$\beta$ = 3380) in close proximity to the output<br>inductor's output rail, not close to MOSFET<br>side; the return trace should be 20 mils away<br>from other traces. Place 1.54k $\Omega$ pull-up and<br>decoupling capacitor (typically 0.1µF) in close<br>proximity to the controller. The pull-up resiston<br>should be exactly tied to the same point as the<br>VCC pin, not through an RC filter. If not used,<br>connect this pin to VCC. |  |  |

| IOUT                                             | Yes                  | Scale R such that the IOUT pin voltage is 2.5V<br>at 63.875A load. Place R and C in general<br>proximity to the controller. The time constant<br>of RC should be sufficient as an averaging<br>function for the digital IOUT. An external<br>pull-up resistor to VCC is recommended to<br>cancel the IOUT offset at OA load.                                                                                                                                                                 |  |  |

#### TABLE 2. DESIGN AND LAYOUT CHECKLIST (Continued)

| PIN<br>NAME    | NOISE<br>SENSITIVITY | DESCRIPTION                                                                                                                                                                                      |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROG1-4        | No                   | Resistor divider must be referenced to the VCC<br>pin and the system ground; they can be placed<br>anywhere. DO NOT use decoupling capacitors<br>on these pins.                                  |

| GND            | Yes                  | Directly connect to low noise area of the system ground. The GND PAD should use at least four vias. Separate analog ground and power ground with a $0\Omega$ resistor is highly NOT recommended. |

| LGATE          | No                   | Low-side driver output and short and wide<br>trace in between this pin and the MOSFET gate<br>pin as possible. High dV/dt signals should not<br>be close to any sensitive signals.               |

| UGATE          | No                   | High-side driver output and short and wide<br>trace in between this pin and the MOSFET gate<br>pin as possible. High dV/dt signals should not<br>be close to any sensitive signals.              |

| BOOT,<br>PHASE | Yes                  | Place X7R 0.1µF or 0.22µF in proximity to the<br>BOOT and PHASE pins. High dV/dt signals<br>should not be close to any sensitive signals.                                                        |

| PVCC           | Yes                  | Place X7R 4.7µF in proximity to the PVCC pin and the system ground plane.                                                                                                                        |

#### TABLE 3. TOP LAYOUT TIPS

| NUMBER | DESCRIPTION                                                                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | The layer next to controller (top or bottom) should be a ground layer. Separate analog ground and power ground with a $0\Omega$ resistor is highly NOT recommended. Directly connect GND PAD to low noise area of the system ground with at least four vias. |

| 2      | Never place controller and its external components above or under the VIN plane or any switching nodes.                                                                                                                                                      |

| 3      | Never share CSRTN and VSEN on the same trace.                                                                                                                                                                                                                |

| 4      | Place the input rail decoupling ceramic capacitors closely to<br>the high-side FET. Never use only one via and a trace to<br>connect the input rail decoupling ceramics capacitors; must<br>connect to the VIN and GND planes.                               |

| 5      | Place all decoupling capacitors in close proximity to the<br>controller and the system ground plane.                                                                                                                                                         |

| 6      | Connect remote sense (VSEN and RGND) to the load and ceramic decoupling capacitors nodes; never run this pair below or above switching noise plane.                                                                                                          |

| 7      | Always double check critical component pinout and their respective footprints.                                                                                                                                                                               |

FIGURE 6. ISL68200DEM01Z 1V AT 20A BUCK SOLUTION SCHEMATICS

Page 7 of 22

A Renesas Company

FIGURE 7. I/O CONNECTORS, AUXILIARY CIRCUITS AND ON-BOARD TRANSIENT LOAD SCHEMATICS

ISL68200DEM01Z Schematics (Continued)

A Renesas Company

Page 8 of 22

## **Bill of Materials**

| QTY | REFERENCE<br>DESIGNATOR | DESCRIPTION                          | PCB FOOTPRINT         | MANUFACTURER                    | PART NUMBER        |

|-----|-------------------------|--------------------------------------|-----------------------|---------------------------------|--------------------|

| 1   | U1                      | R4 Wrapper with Driver               | QFN24_157X157_197_EPC | INTERSIL                        | ISL68200IRZ-REVD   |

| 1   | CIN1                    | 270µF/16V/8x9/10mΩ                   | CAPR_315X275_150_P    | SANYO                           | 16SEPC270MX        |

| 1   | C1                      | 4.7µF/6.3V/X5R                       | SM0603                | VENKEL                          | C0603X5R6R3-475KNE |

| 2   | C2, C3                  | 1.0µF/16V/X7R                        | SM0603                | трк                             | C1608X7R1C105K     |

| 1   | C4                      | 1µF/6.3V/X5R                         | SM0603                | PANASONIC                       | ECJ1VB0J105K       |

| 1   | C5                      | 22nF/50V/X7R                         | SM0603                | VENKEL                          | C0603X7R500-223KNE |

| 4   | C6, CB1, CC1, CNTC1     | 0.1µF/16V/X7R                        | SM0603                | MURATA                          | GRM39X7R104K016AD  |

| 4   | C10, C11, C19, C20      | 22µF/16V/X5R                         | SM0805                | VENKEL                          | C0805X5R160-226KNE |

| 4   | C05, C06, C08, C09      | 220µF/4V/X5R                         | SM1206                | MURATA                          | GRM31CR60G227ME11  |

| 1   | L1                      | 220nH, 0.29mΩ                        | ind_we_744302010      | Wurth Electronics               | 744307022          |

| 1   | QDUAL                   | Dual FET                             | pqfn_5x6_dual         | INFINEON                        | BSC0910NDI         |

| 1   | R2                      | 75kΩ, 1%                             | SM0603                | VENKEL                          | CR0603-10W-7502FT  |

| 1   | R4                      | 100kΩ, 1%                            | SM0603                | VENKEL                          | CR0603-10W-1003FT  |

| 1   | R5                      | 105kΩ, 1%                            | SM0603                | PANASONIC                       | ERJ-3EKF1053V      |

| 1   | R8                      | <b>15kΩ, 1%</b>                      | SM0603                | PANASONIC                       | ERJ-3EKF1502V      |

| 1   | R9                      | 29.4kΩ, 1%                           | SM0603                | YAGEO                           | RC0603FR-0729K4L   |

| 4   | R10, R15, R16, R17      | 10kΩ, 1%                             | SM0603                | VENKEL                          | CR0603-10W-1002FT  |

| 1   | R12                     | 24.9kΩ, 1%                           | SM0603                | PANASONIC                       | ERJ-3EKF2492V      |

| 1   | R13                     | 9.53kΩ, 1%                           | SM0603                | YAGEO                           | 9C06031A9531FKHFT  |

| 2   | R30, R31                | ΟΩ                                   | SM0603                | VENKEL                          | CR0603-10W-000T    |

| 1   | RBLD1                   | 121Ω, 1%                             | SM0603                | VISHAY/DALE                     | CRCW0603121RFKTA   |

| 1   | RNTC1                   | 10k $\Omega$ NTC, 5%, $\beta$ = 3380 | SM0402                | MURATA                          | NCP15XH103J03RC    |

| 1   | RP1                     | 9.09kΩ, 1%                           | SM0603                | YAGEO                           | RC0603FR-079K09L   |

| 1   | RSEN1                   | 75Ω, 1%                              | SM0603                | PANASONIC                       | ERJ-3EKF75R0V      |

| 1   | RTM1                    | 1.54kΩ, 1%                           | SM0603                | YAGEO                           | RC0603FR-071K54L   |

| )EM | ONSTRATION BOARD S      | PECIFIC AUXILIARY PARTS BILL O       | F MATERIALS           |                                 |                    |

| 1   | U2                      | Dual Amp/500MHz/5V                   | SOIC8                 | INTERSIL                        | EL8203ISZ          |

| 1   | QU2                     | 8mΩ N-MOSFET                         | LFPAK                 | INFINEON                        | BSC080N03LS G      |

| 1   | DS1                     | LED/RED/0805/CLEAR                   | SM0805                | WURTH ELEKTRONIK                | 150080RS75000      |

| 1   | SW1                     | Enable Switch                        | GT11SC                | C&K DIVISION                    | GT11MSCBE          |

| 1   | C12                     | 4.7µF/6.3V/X5R                       | SM0603                | VENKEL                          | C0603X5R6R3-475KNE |

| 2   | C13, C55                | 0.1µF/16V/X7R                        | SM0603                | MURATA                          | GRM39X7R104K016AD  |

| 1   | C16                     | 1µF/6.3V/X5R                         | SM0603                | PANASONIC                       | ECJ1VB0J105K       |

| 1   | C17                     | 22pF/50V/C0G                         | SM0603                | VENKEL                          | C0603C0G500-220JNE |

| 1   | C18                     | 100pF/50V/C0G                        | SM0603                | PANASONIC                       | ECJ-1VC1H101J      |

| 2   | J1, J2                  | Screw Terminal                       | В2С-РСВ               | INTERNATIONAL<br>HYDRAULICS INC | В2С-РСВ            |

| 1   | J3                      | Female Banana Jack, Black            | 111-07xx-001          | JOHNSON<br>COMPONENTS           | 111-0703-001       |

# Bill of Materials (Continued)

| QTY | REFERENCE<br>DESIGNATOR | DESCRIPTION                             | PCB FOOTPRINT   | MANUFACTURER          | PART NUMBER       |

|-----|-------------------------|-----------------------------------------|-----------------|-----------------------|-------------------|

| 1   | J4                      | Female Banana Jack, Red                 | 111-07xx-001    | JOHNSON<br>COMPONENTS | 111-0702-001      |

| 2   | J8, J9                  | CONN-HEADER, 2X3, BRKAWY,<br>2.54mm,TIN | CONN6           | SAMTEC                | TSW-103-08-T-D-RA |

| 2   | J10, J11                | CONN-SOCKET STRIP,TH,2X3,<br>2.54mm,TIN | CONN6           | SAMTEC                | SSQ-103-02-T-D-RA |

| 2   | JP1, JP4                | 2-pin 0.1" spacing Jumper               | CONN2           | BERG/FCI              | 69190-202HLF      |

| 1   | TP1                     | Probe Ground                            | TP-150C100P-RTP | KEYSTONE              | 1514-2            |

| 2   | TP2, TP14               | Probe Jack                              | TEK131-4353-00  | TEKTRONIX             | 131-4353-00       |

| 4   | TP3, TP4, TP5, TP6      | Test Point                              | MTP500x         | KEYSTONE              | 5002              |

| 2   | VCC12, FG_DRIVE         | Test Point RED                          | MTP500x         | KEYSTONE              | 5000              |

| 2   | VIN_GND, FG_GND         | Test Point BLACK                        | MTP500x         | KEYSTONE              | 5001              |

| 4   | R32, R33, R36, R37      | 3Ω, 1%                                  | SM0603          | VENKEL                | CR0603-10W-03R0FT |

| 1   | R34                     | 2kΩ, 1%                                 | SM0603          | КОА                   | RK73H1JTTD2001F   |

| 1   | R39                     | 2.49kΩ, 1%                              | SM0603          | КОА                   | RK73H1JTTD2491F   |

| 1   | R42                     | 52.3Ω, 1%                               | SM0603          | PANASONIC             | ERJ-3EKF52R3V     |

| 1   | R41                     | 274Ω, 1%                                | SM0603          | VENKEL                | CR0603-10W-2740FT |

| 1   | R43                     | 124kΩ, 1%                               | SM0603          | YAGEO                 | 9C06031A1243FKHFT |

| 2   | R45, R46                | 499Ω, 1%                                | SM0603          | VENKEL                | CR0603-10W-4990FT |

| 2   | RLT1, RLT2              | 0.1Ω, 1%                                | SM2512          | CTS RESISTOR          | 73L7R10J          |

# **Measured Data** The following data was acquired using a ISL68200DEM01Z board.

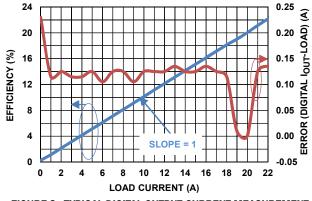

FIGURE 8. TYPICAL DIGITAL OUTPUT CURRENT MEASUREMENT

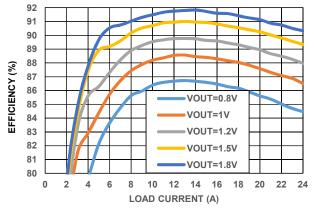

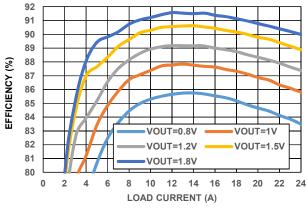

FIGURE 9. EFFICIENCY,  $V_{IN} = 12V$ ,  $f_{SW} = 400$ kHz

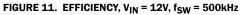

Measured Data The following data was acquired using a ISL68200DEM01Z board. (Continued)

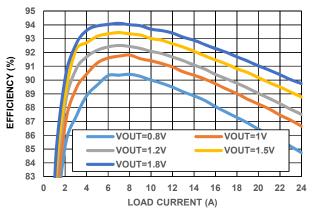

FIGURE 13. EFFICIENCY, VIN = 12V, fSW = 600kHz

FIGURE 14. EFFICIENCY,  $V_{IN} = 5V$ ,  $f_{SW} = 600$ kHz

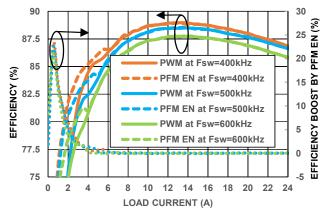

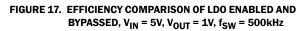

FIGURE 15. EFFICIENCY COMPARISON OF PWM MODE AND PFM ENABLED MODE, VIN = 12V, VOUT = 1V

FIGURE 16. EFFICIENCY COMPARISON OF PWM MODE AND PFM ENABLED MODE, VIN = 5V, VOUT = 1V

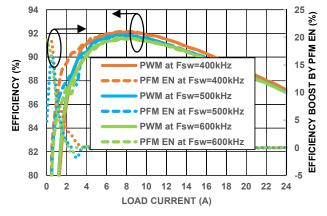

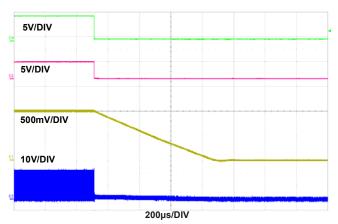

FIGURE 18. POWER-UP WITH/WITHOUT PRECHARGE AT 1A LOAD

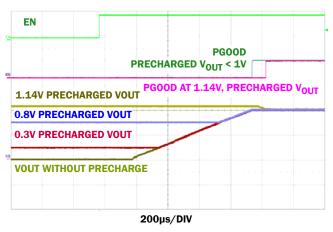

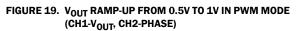

Measured Data The following data was acquired using a ISL68200DEM01Z board. (Continued)

100µs/DIV

100µs/DIV

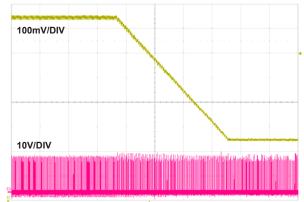

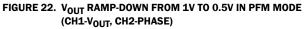

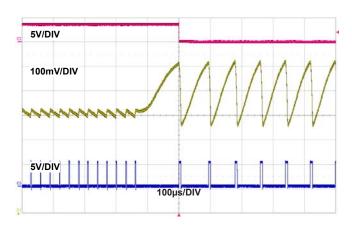

FIGURE 21.  $V_{\mbox{OUT}}$  RAMP-UP FROM 0.5V TO 1V IN PFM MODE (CH1-V<sub>OUT</sub>, CH2-PHASE)

100µs/DIV

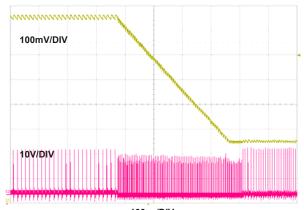

FIGURE 20. V<sub>OUT</sub> RAMP-DOWN FROM 1V TO 0.5V IN PWM MODE (CH1-V<sub>OUT</sub>, CH2-PHASE)

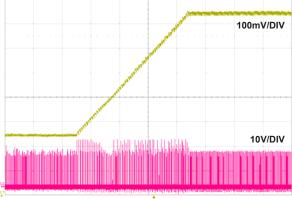

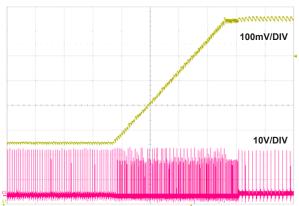

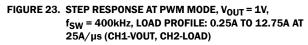

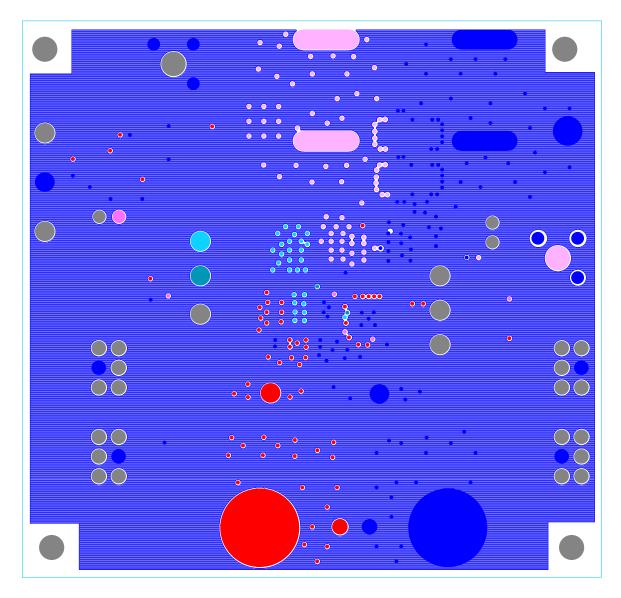

# Measured Data The following data was acquired using a ISL68200DEM01Z board. (Continued)

5µs/DIV

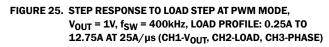

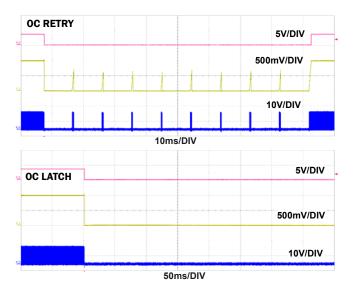

FIGURE 27. OVERCURRENT PROTECTION (CH1-V<sub>OUT</sub>, CH2-PGOOD, CH3-PHASE)

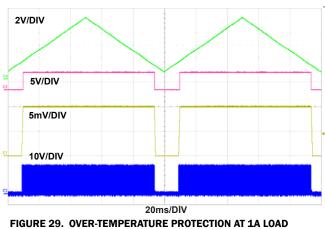

JRE 29. OVER-TEMPERATURE PROTECTION AT 1A LOAD (CH1-V<sub>OUT</sub>, CH2-LOAD, CH3-PHASE, CH4-NTC)

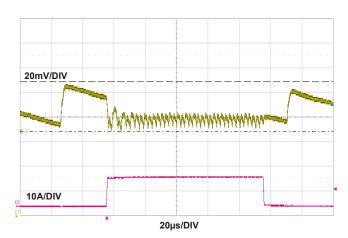

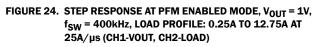

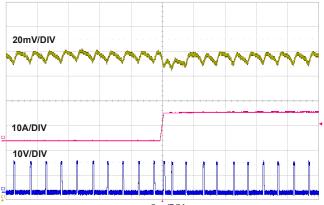

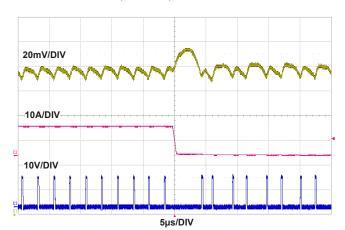

FIGURE 26. STEP RESPONSE TO LOAD RELEASE AT PWM MODE,  $V_{OUT} = 1V$ ,  $f_{SW} = 400$ kHz, LOAD PROFILE: 0.25A TO 12.75A AT 25A/µs (CH1-V<sub>OUT</sub>, CH2-LOAD, CH3-PHASE)

FIGURE 28. OVERVOLTAGE PROTECTION (CH1-V<sub>OUT</sub>, CH2-PGOOD, CH3-LGATE)

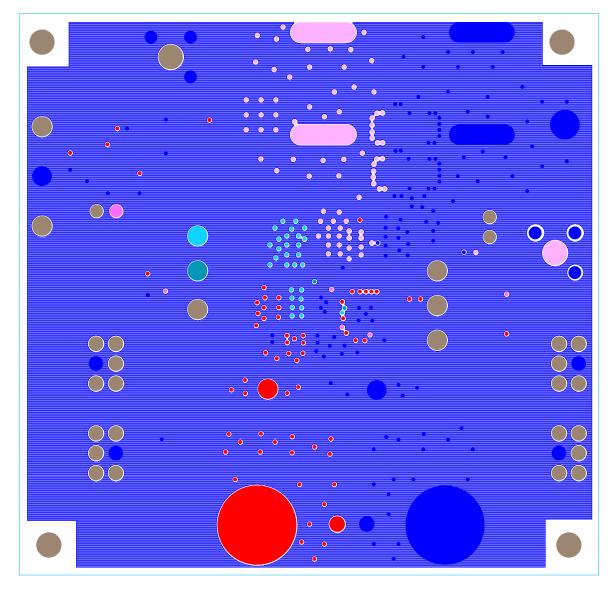

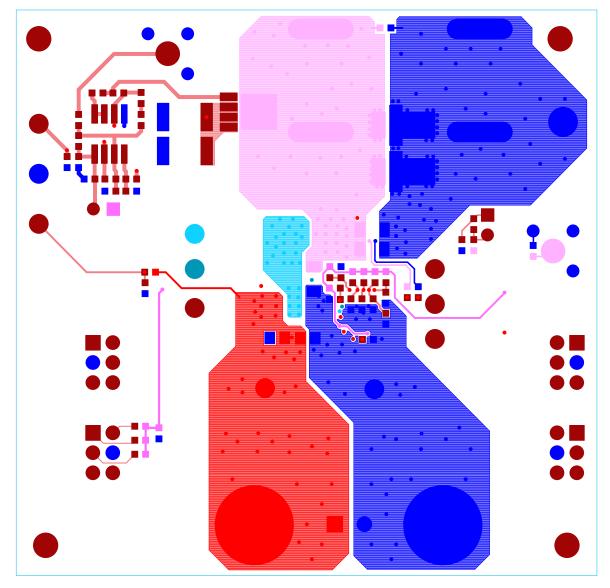

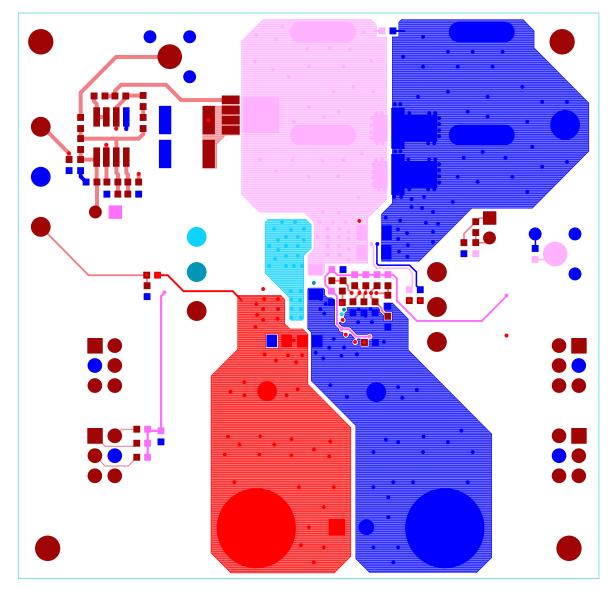

ISL68200DEM01Z Board Layout

FIGURE 31. PCB - TOP ASSEMBLY

FIGURE 32. PCB - TOP LAYER

FIGURE 33. PCB - INNER LAYER 2 (TOP VIEW)

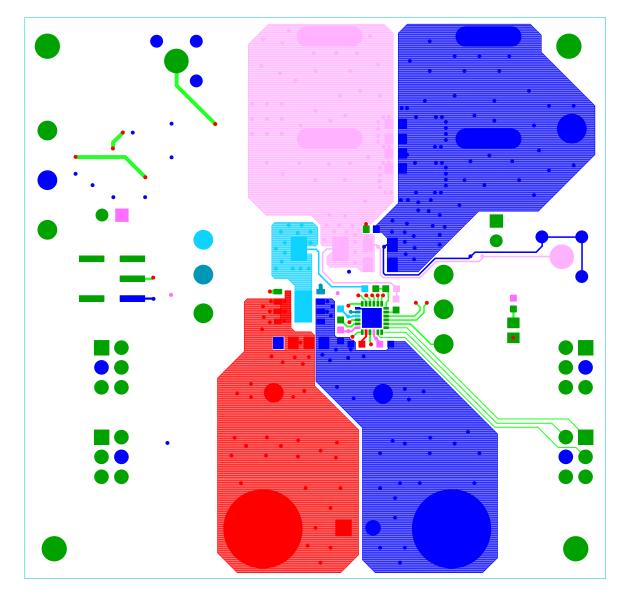

FIGURE 34. PCB - INNER LAYER 3 (TOP VIEW)

FIGURE 35. PCB - INNER LAYER 4 (TOP VIEW)

FIGURE 36. PCB - INNER LAYER 5 (TOP VIEW)

FIGURE 37. PCB - BOTTOM LAYER (TOP VIEW)

FIGURE 38. PCB - BOTTOM ASSEMBLY (TOP VIEW)

© Copyright Intersil Americas LLC 2016-2017. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.

For information regarding Intersil Corporation and its products, see <u>www.intersil.com</u>

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

EVAL-ADM1168LQEBZ EVB-EP5348UI MIC23451-AAAYFLEV MIC5281YMMEEV DA9063-EVAL ADP122-3.3-EVALZ ADP130-0.8-EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP1714-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM3691TL-1.8EV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV EVAL-ADM1186-1MBZ EVAL-ADM1186-2MBZ