# RENESAS

# DATASHEET

#### ISL78226

6-Phase 12V/48V Bidirectional Synchronous PWM Controller

FN8887 Rev.2.00 Oct 19, 2017

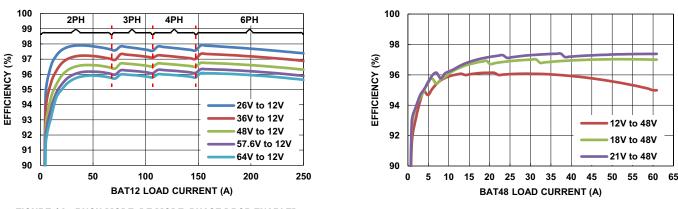

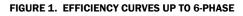

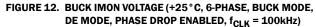

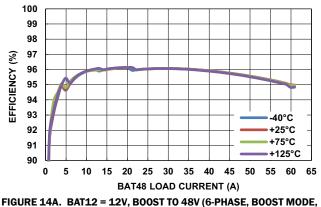

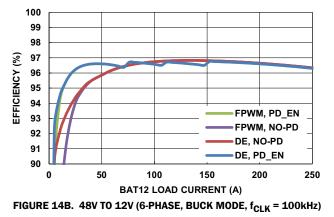

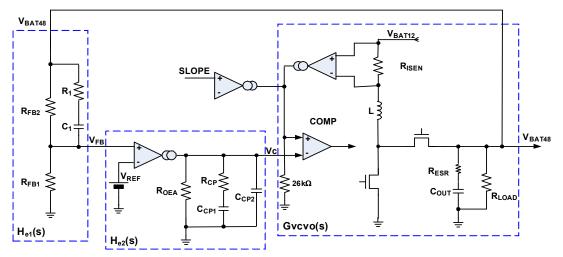

The <u>ISL78226</u> is a 6-phase, bidirectional, synchronous PWM controller designed to perform power conversion between 12V and 48V buses up to 3.75kW at >95% conversion efficiency. One ISL78226 supports both Buck and Boost power conversion enabling a compact and robust design with minimum components.

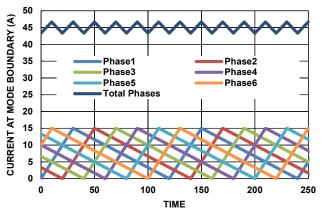

ISL78226 regulates both voltage and current to control power transfer from bus to bus. The multiphase architecture uses interleaved timing to support up to six parallel power stages per ISL78226. By interleaving the power stages, the ripple frequency is multiplied, reducing input and output ripple voltage and current. Lower ripple results in fewer input/output capacitors and therefore, lower component cost and smaller circuit implementation.

The IC is designed to be interleaved in a master/slave architecture to be scaleable for higher power. Also integrated within the device is a dual-output Flyback controller that generates both a 12V supply for the power stage FET drivers as well as a 6V supply for the ISL78226 from either of the two buses. A 200mA auxiliary linear regulator is provided to supply a local microcontroller or interface devices.

A PMBus interface provides system control and diagnostics to support functional safety requirements. This digital interface offers the system controller the ability to program operating modes, voltage and current limit warning, protection thresholds, individual fault response, and rapid fault condition detection.

# **Related Literature**

- For a full list of related documents, visit our website

- ISL78226 product page

#### **Features**

- 6-phase bidirectional synchronous 12V to 48V controller

- · Master/slave architecture supports up to 4 ICs in parallel

- Voltage and current regulation

- · Phase dropping facilitated with companion FET driver

- · Average phase-to-phase current balancing

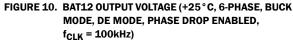

- 2% current monitor gain accuracy from 0 to full load

- Supply and clock redundancy for functional safety

- Cycle-by-cycle peak current limiting

- · Cycle-by-cycle negative current limiting

- · Digitally programmable average current limit

- · Analog/digital control of output voltage

- PMBus for status monitoring and fault response control

- Selectable phase dropping and diode emulation for light-load efficiency improvement

- Comprehensive protection with selectable hiccup or latch-off fault responses

- · Digitally programmable warning and fault thresholds

- Dual-output Flyback controller

- · 200mA adjustable output linear regulator

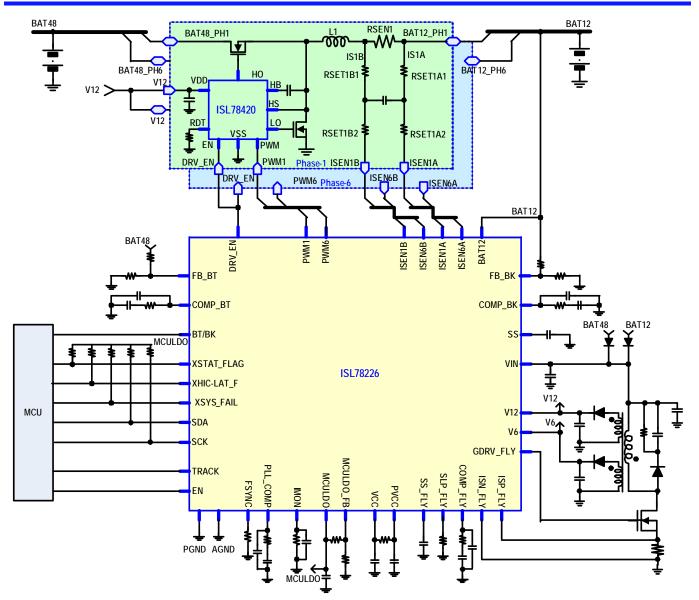

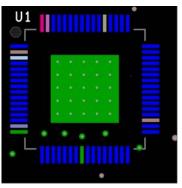

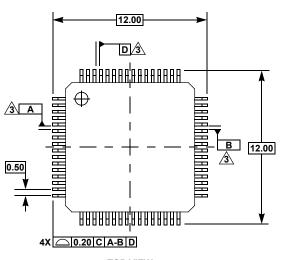

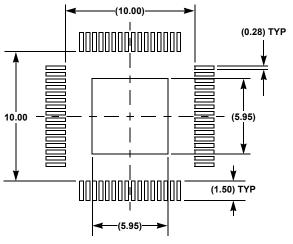

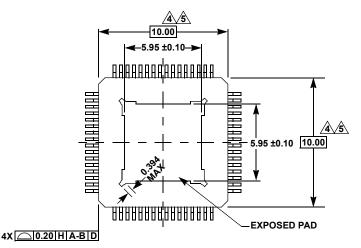

- 10mmx10mm 64 Ld TQFP with exposed pad thermal interface

- <u>AEC-Q100</u> Grade 1

#### Applications

- · Automotive bidirectional DC/DC converter

- Bidirectional DC/DC for smart grid

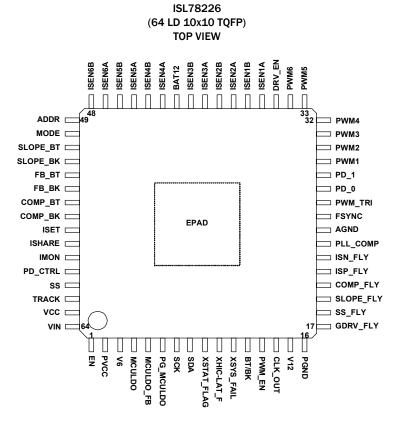

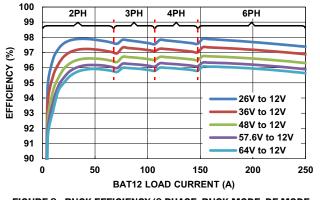

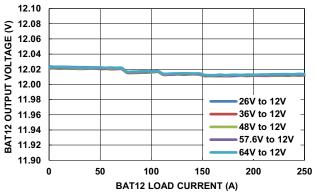

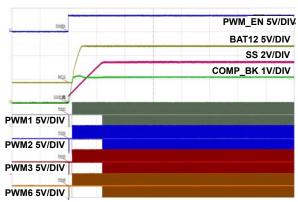

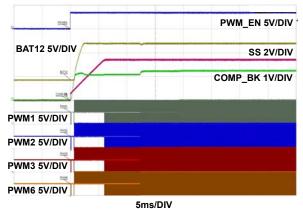

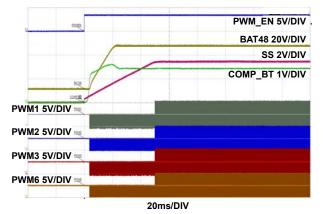

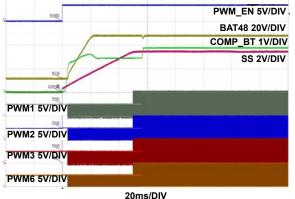

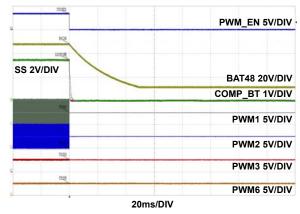

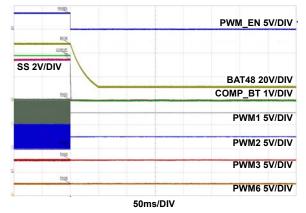

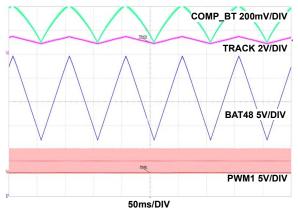

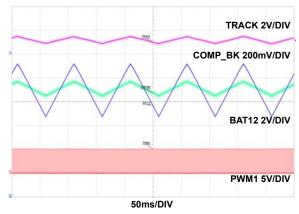

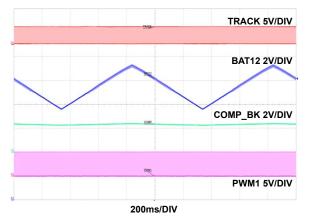

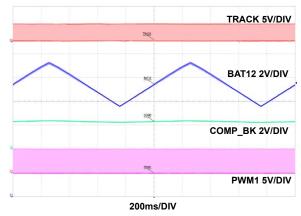

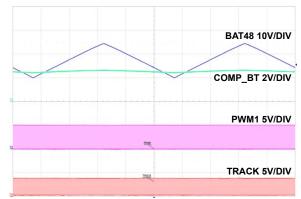

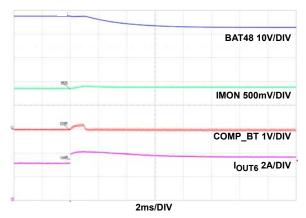

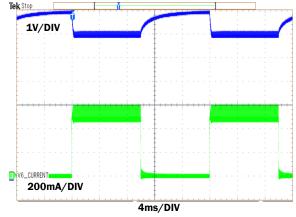

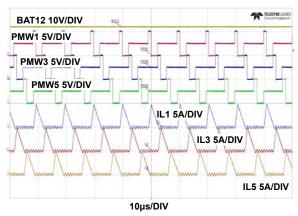

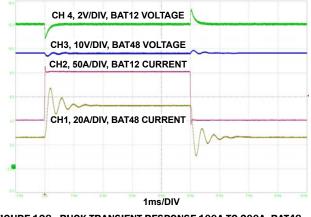

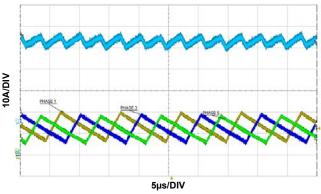

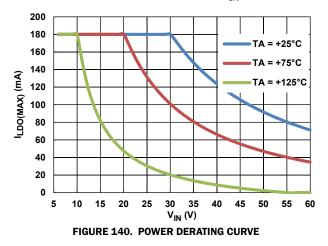

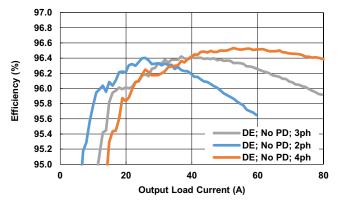

FIGURE 1A. BUCK MODE, DE MODE, PHASE-DROP ENABLED

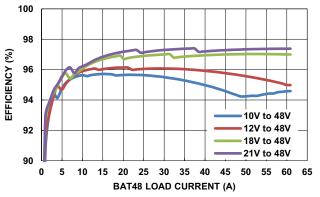

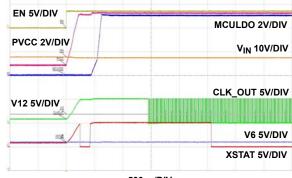

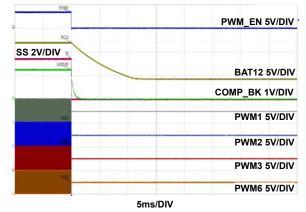

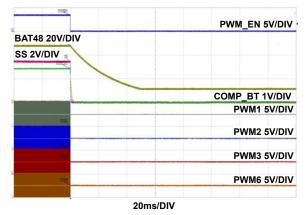

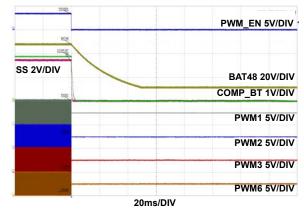

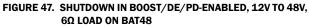

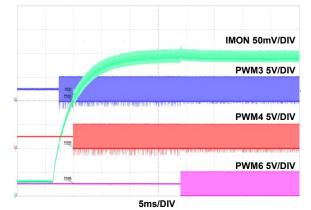

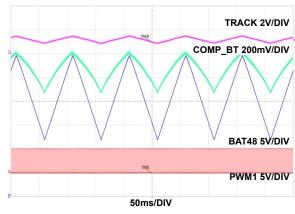

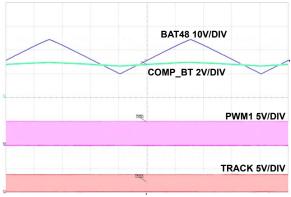

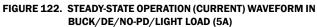

FIGURE 1B. BOOST MODE, DE MODE, PHASE-DROP ENABLED

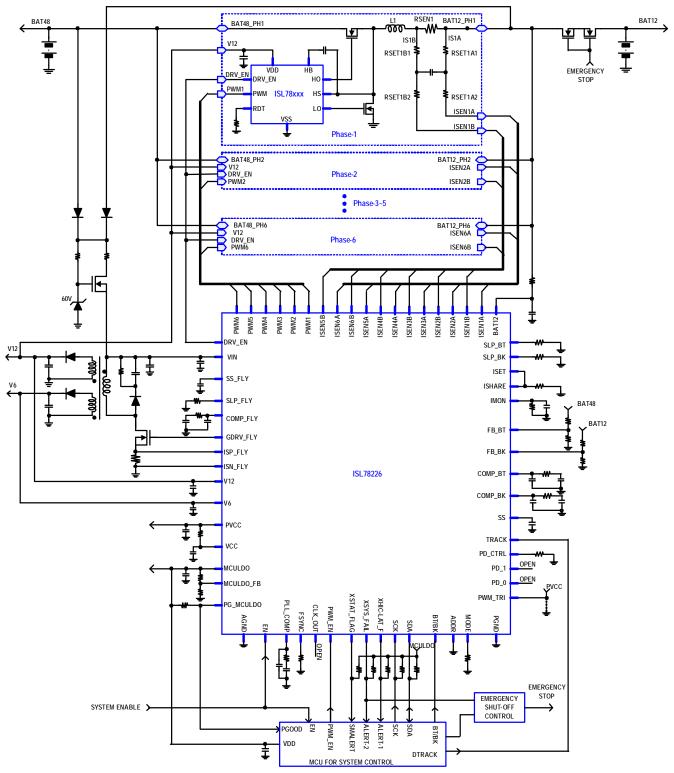

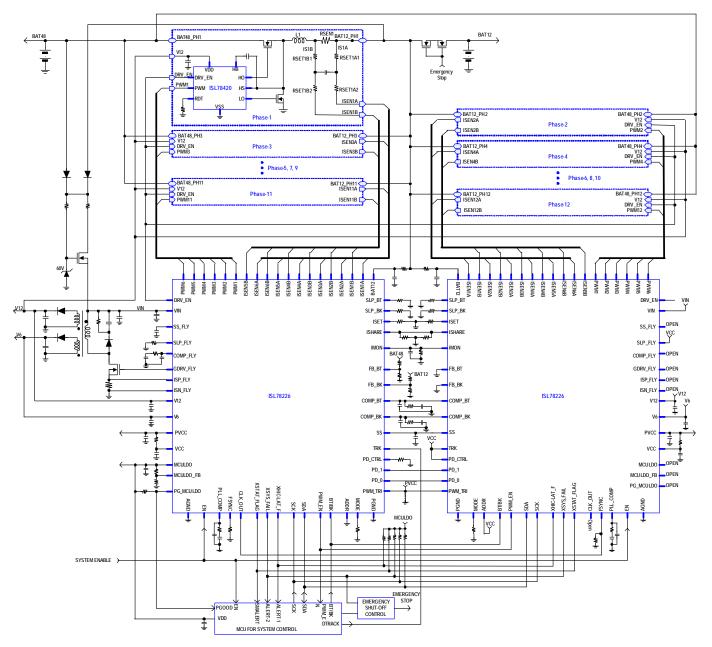

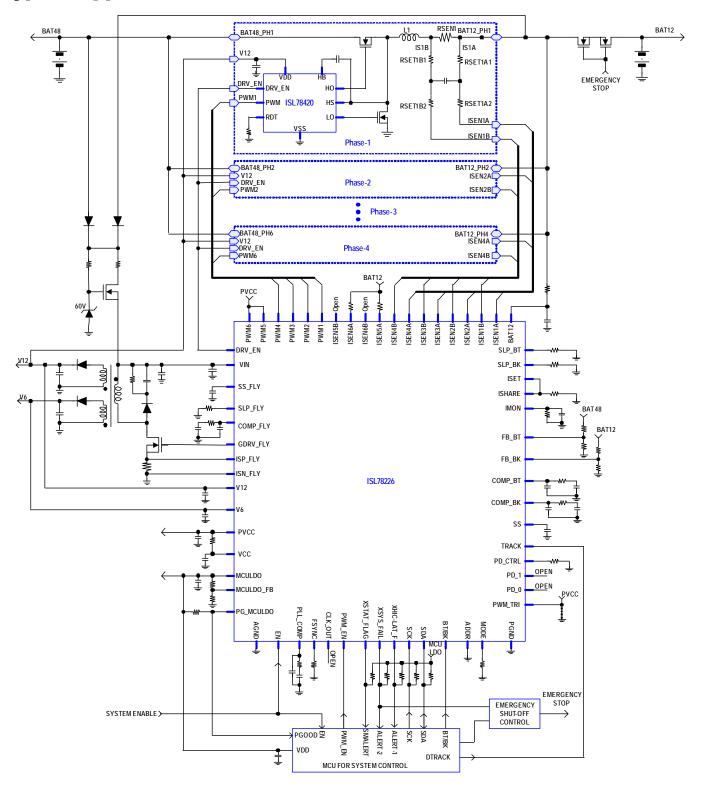

FIGURE 2. SIMPLIFIED TYPICAL APPLICATION SCHEMATIC

#### **Table of Contents**

| Pin Configuration                                                                   | 5    |

|-------------------------------------------------------------------------------------|------|

| Pin Description                                                                     | 5    |

| Ordering Information                                                                | . 10 |

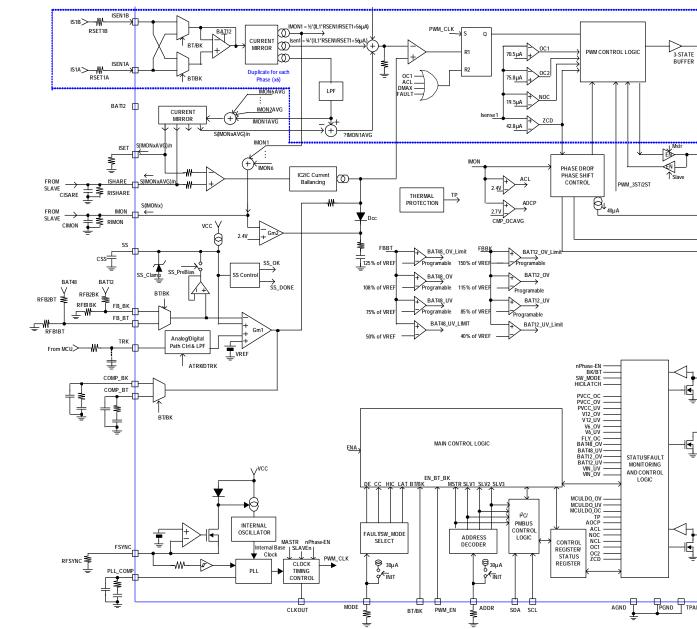

| Block Diagram                                                                       | .11  |

| Typical Application Schematics                                                      |      |

| Absolute Maximum Ratings                                                            |      |

| _                                                                                   |      |

| Thermal Information                                                                 |      |

| Recommended Operating Conditions                                                    |      |

| Electrical Specifications                                                           |      |

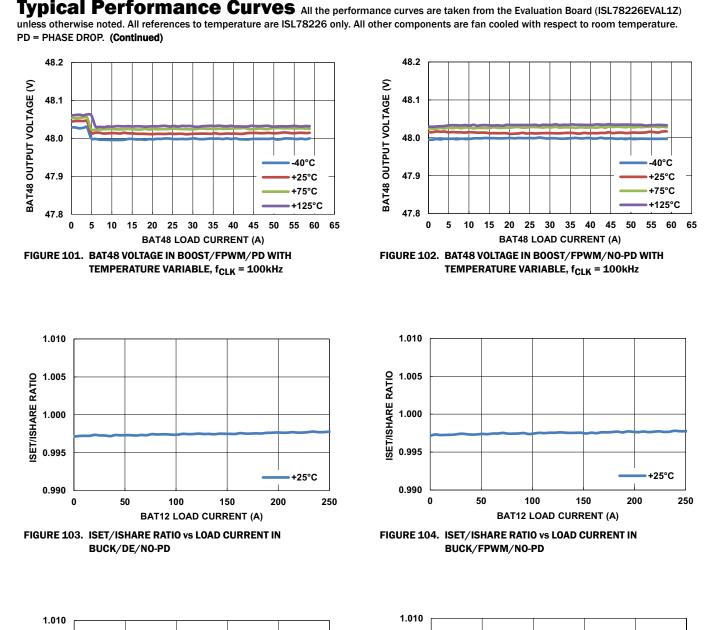

| Typical Performance Curves                                                          | .29  |

| Operation Description                                                               |      |

| Bidirectional Power Conversion                                                      |      |

| Multiphase Interleaving Control<br>Oscillator and Clock Synchronization             |      |

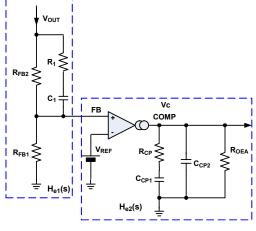

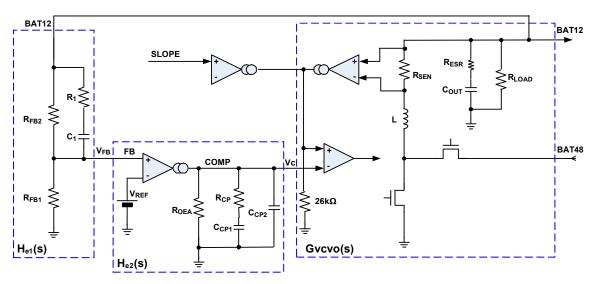

| Output Voltage Regulation Loop                                                      |      |

| Peak Current Mode Control                                                           | . 52 |

| 3-State PWM Control Output                                                          |      |

| Boot Refreshing                                                                     | . 53 |

| Current Sharing between Phases                                                      |      |

| Tracking                                                                            |      |

| Current Sense                                                                       |      |

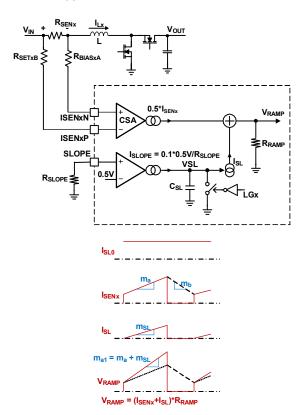

| Adjustable Slope Compensation                                                       | 55   |

| Light-Load Efficiency Enhancement                                                   |      |

| Diode Emulation at Light-Load Condition                                             |      |

| Pulse Skipping at Deep Light-Load Condition                                         |      |

| Automatic Phase Dropping/Adding                                                     |      |

| Average Current Control                                                             |      |

| Average Constant Current Control Loop (CCL)                                         |      |

| Average Overcurrent Protection (AOCP)                                               |      |

| Power Supply to the Device                                                          |      |

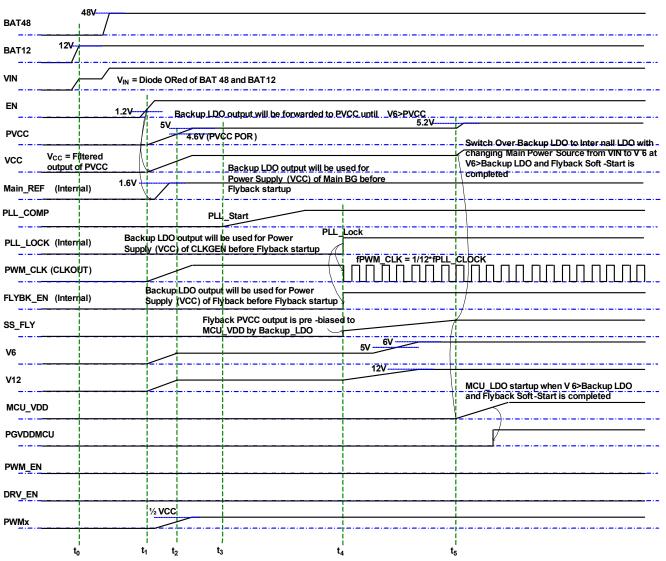

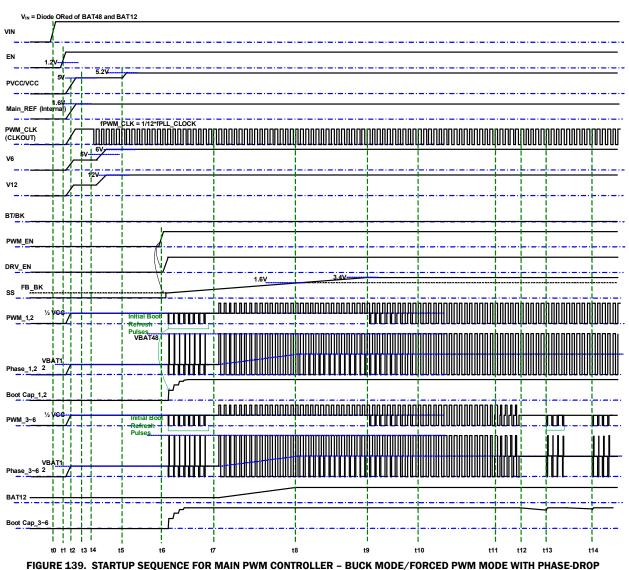

| Initialization and Startup Sequence                                                 |      |

| Initialization and Internal Bias Circuit Startup                                    |      |

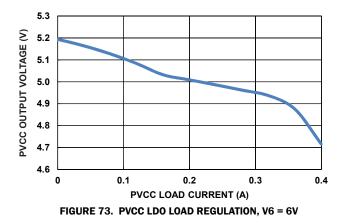

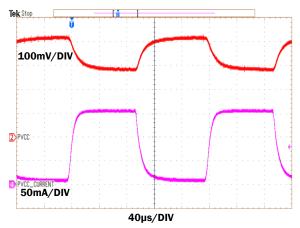

| LDOs                                                                                | . 60 |

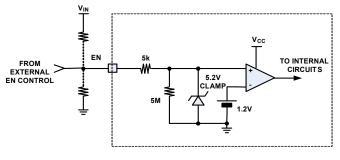

| Backup LDO                                                                          |      |

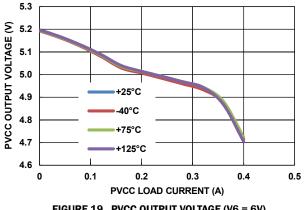

| Internal 5.2V LDO                                                                   |      |

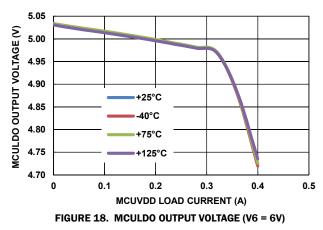

| MCULDO                                                                              |      |

| Flyback Controller                                                                  |      |

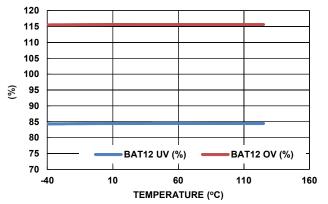

| 12V/48V (BAT12/BAT48) Rail Input/Output Overvoltag                                  |      |

| and Undervoltage Fault                                                              |      |

| VIN Overvoltage Protection                                                          |      |

| Flyback Output (V12/V6) Over/Undervoltage Detection a                               | and  |

| Protection                                                                          |      |

| Flyback Overcurrent Protection                                                      |      |

| Overcurrent Protection                                                              |      |

| Cycle-by-Cycle Overcurrent Limiting (OC1)                                           |      |

| Inductor Peak Current Overcurrent Protection (OC2)                                  |      |

| Average Overcurrent Protection (AOCP)                                               |      |

| Negative Overcurrent Protection (NOC)           Fault Phase Removal (Phase-Disable) |      |

| Overriding Individual Fault Responses                                               |      |

| Operation Mode Setting                                                              |      |

| Converter Direction Selection                                                       |      |

| PWM Output Mode Selection                                                           |      |

| Switching Mode and Fault Response Selection                                         |      |

| Master Controller and Slave Controller Setting 6                                                          |          |

|-----------------------------------------------------------------------------------------------------------|----------|

| Operating Phase Count Setting and Phase Shifting 6                                                        |          |

| I <sup>2</sup> C/PMBus Communication 6                                                                    |          |

| Monitor Faults and Configure Fault Responses 6                                                            |          |

| Set Operation/Fault Thresholds via I <sup>2</sup> C/PMBus 6                                               |          |

| Accessible Timing for I <sup>2</sup> C/PMBus Registers Status 6                                           | 55       |

| Control and Status Registers 6                                                                            | 6        |

| Control Registers 6                                                                                       |          |

| Control Register 1 (0xB0) 6                                                                               | 6        |

| Individual Fault Response Control Register 1 (0xB1) 6                                                     | 57       |

| Individual Fault Response Control Register 2 (0xB2) 7                                                     | '0       |

| Individual Fault Response Control Register 3 (0xB3) 7                                                     |          |

| Individual Fault Response Control Register 4 (0xB4) 7                                                     |          |

| Individual Fault Response Control Register 6 (0xB6) 7                                                     |          |

| Individual Fault Response Control Register 6 (0xB7) 7                                                     |          |

| Individual Fault Response Control Register 7 (0xB8) 7                                                     |          |

|                                                                                                           |          |

| BAT12 Overvoltage Threshold Setting Register (0xB9) . 8<br>BAT12 and BAT48 Undervoltage Threshold Setting | 2        |

| Register (0xBA) 8                                                                                         | 33       |

| BAT48 Overvoltage Threshold Setting Register (0xBB) . 8                                                   | 34       |

| Individual Phase Removal Control Register (0xBC) 8                                                        |          |

| Serious Fault Response Control Register (0xBD) 8                                                          |          |

| Minimum On-Time, Current Balancing Setting                                                                | -        |

| Register (0xBE)                                                                                           | 28       |

| Maximum On-Duty Setting Register (0xBF)                                                                   |          |

| Boot Refresh Control Register (0xEC)                                                                      |          |

| - · · ·                                                                                                   |          |

| CCL/ACL Threshold Control Register (0xED)                                                                 |          |

| WRITE_PROTECT (10h)                                                                                       |          |

| Status Registers                                                                                          | )3<br>)3 |

| Fault Status Register-1 (0xD2)                                                                            |          |

| Fault Status Register-2 (0xD3)                                                                            |          |

| Fault Status Register-3 (0xD4)                                                                            |          |

| Fault Status Register-4 (0xD5)                                                                            |          |

| Fault Status Register-5 (0xD6)                                                                            |          |

| Fault Status Register-6 (0xD7)                                                                            |          |

| Fault Status Register-7 (0xD8)                                                                            |          |

| Fault Status Register-8 (0xD9)                                                                            |          |

| Fault Status Register-9 (0xD4)                                                                            |          |

|                                                                                                           |          |

| System Status Register-1 (0xDC)                                                                           |          |

| System Status Register-2 (0xDD) 10                                                                        |          |

| System Status Register-3 (0xDF) 10                                                                        |          |

| Device ID (0xAD) 10                                                                                       |          |

| Chip Revision (0xAE) 10                                                                                   |          |

| Application Information 11                                                                                |          |

| Operation Mode Setting 11                                                                                 | .0       |

| Converter Boost or Buck Mode Selection                                                                    |          |

| PWM Output Mode Selection                                                                                 |          |

| Switching Mode and Fault Response Selection 11                                                            | 0.       |

| Master Controller and Slave Controller Setting 11                                                         | 0        |

| Soft-Start Capacitor Selection                                                                            |          |

| Output Voltage Setting 11                                                                                 | 1        |

| Switching Frequency 11                                                                                    | 1        |

| Inductor Selection                                                                                        | 1        |

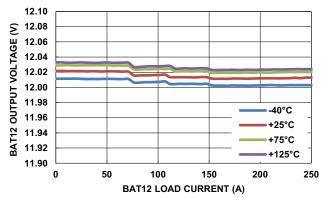

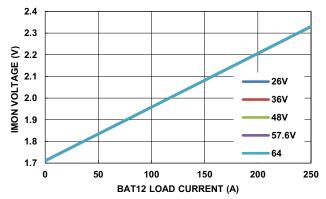

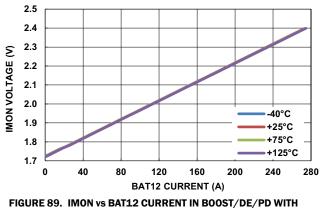

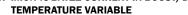

| Current Monitor Setting 11                                                                                | 2        |

| IMON Resistor and Average Constant Current Loop (CCL)                                                     |          |

| Threshold Setting                                                                                         |          |

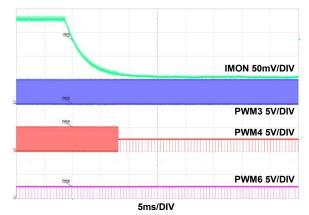

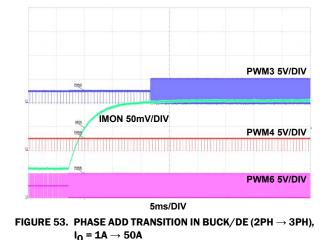

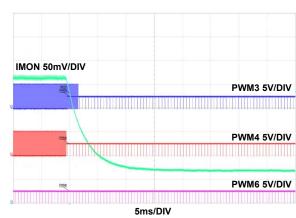

| Phase Drop/Add Control                                                                                    |          |

| V <sub>IN</sub> Input Capacitor 11                                                                        | .3       |

| PVCC and VCC Filter Capacitor                |

|----------------------------------------------|

| MCULDO Setting                               |

| External Flyback Converter Setup             |

| Capacitor Selection for BAT48 and BAT12114   |

| FET Driver IC Selection                      |

| Power MOSFET Selection114                    |

| Driver Bootstrap Capacitor Selection114      |

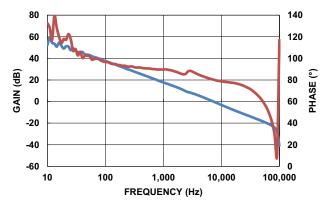

| Loop Compensation Design - Boost             |

| BOOST POWERSTAGE Transfer Function           |

| Compensation Design - Boost                  |

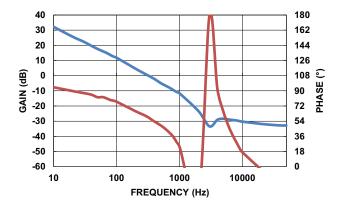

| Loop Compensation Design - Buck              |

| BUCK POWERSTAGE Transfer Function            |

| Compensation Design - Buck                   |

| Loop Compensation Design, Boost and Buck     |

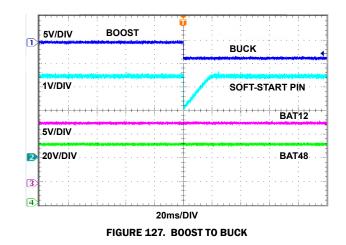

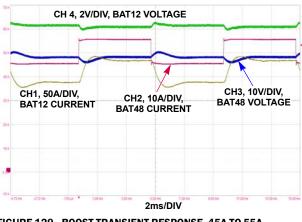

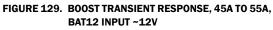

| Buck to Boost and Boost to Buck Operation118 |

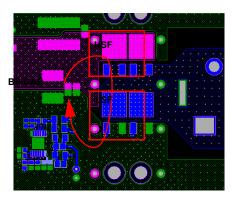

| Layout Considerations118                     |

| Layout Philosophy119                         |

| Revision History120                          |

| About Intersil                               |

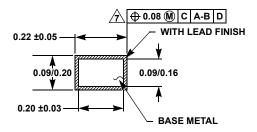

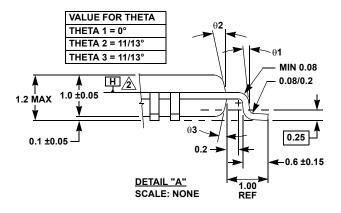

| Package Outline Drawing121                   |

## **Pin Configuration**

## **Pin Description**

| PIN NAME   | I/O    | PIN # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN         | I      | 1     | Device Enable/shut-off control pin. When EN pin is driven above 1.4V, the ISL78226 is active. The operating mode depends<br>on the configurations of the mode setting pins, control registers, and fault register status. The fault status will be kept while<br>the EN pin is high unless internal Power-On Reset (POR) becomes low. When the EN pin is driven below 0.7V the device<br>clears all fault statuses and goes into shutdown mode. While in shutdown mode, the current consumption of the device will<br>be less than 1µA. |  |

| PVCC       | PS (0) | 2     | put of the internal linear regulator that provides bias for internal analog and logic circuits. The PVCC operating range is<br>to 5.4V. A ceramic capacitor of 4.7μF minimum is recommended between PVCC and PGND for noise decoupling. This<br>acitor should be connected as close as possible to PVCC and PGND.                                                                                                                                                                                                                       |  |

| V6         | I      | 3     | V6 is biased by an external ~6V source and is also one of the control loop feedback inputs for the Flyback converter.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MCULDO     | 0      | 4     | e output of MCULDO to supply the MCU or an external general purpose circuit. The output voltage of MCULDO can be<br>justed with an external feedback resistor network which is connected between this output, MCULDO_FB, and AGND.                                                                                                                                                                                                                                                                                                      |  |

| MCULDO_FB  | I      | 5     | edback for the MCULDO output. The midpoint of a resistor voltage divider between MCULDO and AGND is connected to s pin and is compared with the internal reference voltage (1.2V) to regulate the MCULDO output voltage.                                                                                                                                                                                                                                                                                                                |  |

| PG_MCULDO  | 0      | 6     | An open-drain output for MCULDO voltage power-good indication. Pull this pin up with a resistor to supply voltage of M<br>I/F. When the output voltage is within the regulation limit and soft-start is complete, the internal pull down of this pin<br>released and this pin will be pulled high by the external resistor. This pin will be pulled low when the output OV or UV<br>condition is detected.                                                                                                                              |  |

| SCK        | I      | 7     | C/SMBus communication clock input. Requires external pull up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SDA        | I/0    | 8     | I <sup>2</sup> C/SMBus communication data input/output. Requires external pull up.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| XSTAT_FLAG | 0      | 9     | n open-drain output to indicate any status changes at the internal status register. Pull up this pin with a resistor to VCC of<br>apply voltage of MCU I/F. This is including both fault condition detection and warning condition detection. To recognize the<br>atus, MCU should read the status registers via I <sup>2</sup> C/PMBUS.                                                                                                                                                                                                |  |

| PIN NAME   | I/0 | PIN # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XHIC-LAT_F | I/0 | 10    | XHIC-LAT_F is an open-drain output used to indicate Hiccup or Latch-Off fault and also to communicate hiccup or latch<br>fault status between the multiple ISL78226 devices when used in parallel. This node is required to be pulled up to VCC<br>an external resistor. If one of the devices detects Hiccup or Latch-Off fault, the pin of the fault detected device will be dr<br>low and it will pull down the pins of all the other devices connected in parallel. All devices connected in parallel devices<br>all PWM outputs and DRV_EN pins will be driven low. When Hiccup mode is selected, the device tries to restart from s<br>start at 500ms intervals until the fault condition is removed. When Latch-Off mode is selected, the device requires th<br>toggling of the EN or PWM_EN pins for restart.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| XSYS_FAIL  | 0   | 11    | n open-drain output to indicate a potential serious system failure condition. Pull up this pin with a resistor to VCC or th<br>ICU I/F supply voltage.<br>Netects cases where the high-side transistor is shorted, low-side transistor is shorted, the BAT48 is shorted to GND, or a<br>bnormally large current is sensed at the current-sense resistor. When this abnormal condition (continuous Overcurrent<br>ICC2) or Negative Overcurrent (NOC) in both on and off cycles) continues for three switching cycles, the device detects the<br>erious failure condition and pulls the XSYS_FAIL pin low. It is recommended that the system have an emergency protection<br>ircuit to disconnect the battery from the system using a fuse or an external path switch when this signal is pulled low.<br>IOTE: This flag indicates a potential serious system failure such as high-side or low-side transistor short. This flag does n<br>etect all of the serious failure conditions, such as when the high-side or low-side transistor is shorted with some resistance<br>he combination of fault detection information and an additional external failure detection system is recommended to<br>uild robust failure detection. |  |

| BT/BK      | I   | 12    | The converter direction selector pin. When this pin is high, the device operates in Boost mode. When this pin is low, the device operates in Buck mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWM_EN     | I   | 13    | Bidirectional PWM controller enable/disable control signal. While this pin is Low, the bidirectional PWM controller will be turned off. When this pin becomes High, the bidirectional PWM controller will start up from the initialized condition. If latch-<br>off occurs, toggling this pin will restart the bidirectional PWM output.<br>NOTE: This pin does not affect the Flyback converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| CLK_OUT    | 0   | 14    | his pin provides a clock signal to synchronize with another ISL78226. The rising edge signal on the CLKOUT pin is the same ming of rising edge of PWM1 output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| V12        | 1   | 15    | /12 is used to monitor the bridge driver power supply voltage which is generated by the Flyback regulator. The Flyback<br>regulator output voltage for the bridge driver is set to 12V internally. Also, this pin is used as the power supply for the gather<br>drive of Flyback MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PGND       | GND | 16    | Power and digital ground pin. This pin is a reference of internal digital blocks and is connected to the PWMx output buff<br>and Flyback gate driver that generates noisy peak current. Any sensitive analog signal trace should not share common<br>traces with this driving return path. Connect this pin directly to the ground copper plane and put several vias as close as<br>possible to this pin. The PGND and AGND should be connected at common solid ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GDRV_FLY   | 0   | 17    | PWM output to drive the gate of primary side switching NMOS of Flyback regulator. At the startup of the system, this driver will be powered by internal backup LDO output (5V typical) and will be switched over to V12 when V12 voltage exceeds internal backup LDO output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| SS_FLY     | I   | 18    | Use this pin to set the soft-start time of Flyback regulator output. A capacitor placed from SS_FLY to GND will set up the soft-start ramp rate and in turn determine the soft-start time. For details, refer to the <u>"Flyback Controller"</u> section on <u>page 61</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| SLOPE_FLY  | I   | 19    | This pin programs the slope compensation for the Flyback controller. A resistor should be connected from the SLOPE_FLY pin to GND. For details, refer to the <u>"Flyback Controller"</u> section on <u>page 61</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| COMP_FLY   | I/O | 20    | The output of the transconductance amplifier of the Flyback controller. Place the compensation network between the COMP_FLY pin and GND for compensation loop design of Flyback regulator. For details, refer to the <u>"Flyback Controller"</u> section on <u>page 61</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ISP_FLY    | I   | 21    | Connect this pin to the positive node of the current-sense resistor, which is connected to the source of the primary side switching NMOS of the Flyback regulator. For details, refer to the <u>"Flyback Controller"</u> section on <u>page 61</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| ISN_FLY    | I   | 22    | Connect this pin to the GND side of the current-sense resistor, which is connected to the source of the primary side switching NMOS of the Flyback regulator. For details, refer to the <u>"Flyback Controller"</u> section on <u>page 61</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PLL_COMP   | I/O | 23    | PLL_COMP is used as the compensation node for the PLL. A second order passive-loop filter connected between the PLL_COMP pin and GND compensates the PLL feedback loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| AGND       | GND | 24    | Analog ground pin; the reference of internal analog circuits. Connect this pin to a large, quiet copper ground plane. In PCB layout planning, avoid having switching current flowing into the AGND area. The PGND and AGND should be connected at common solid ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

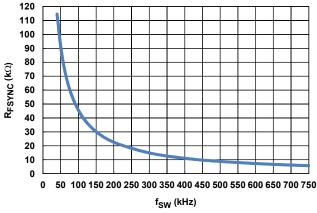

| FSYNC      | I   | 25    | FSYNC pin is used to adjust the internal oscillator frequency or external synchronous clock input.<br>The oscillator switching frequency is adjusted with a resistor from this pin to GND.<br>If the external synchronous clock is applied to this pin, the internal oscillator locks to the rising edge. There is a 25ns<br>(typical) delay from the FSYNC pin's input clock rising edge to PWM1 rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| PIN NAME | I/0 | PIN # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PWM_TRI  | I   | 26    | This pin enables the Tri-Level of the PWM output signal. Pulling the PWM_TRI to VCC enables Tri-Level PWM output signals<br>then the PWM output can be at the 2.5V tri-level condition. To use the Tri-Level output, the external driver needs to be<br>applicable to this function. ISL78420 is an example.<br>Pulling this pin to GND forces the PWM output to be two-level logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| PD_0     | I/0 | 27    | f the ISL78226 is used standalone then PD_0 and PD_1 should not be connected. PD_0 and PD_1 are used to control t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| PD_1     | I/O | 28    | phase dropping between the multiple ISL78226 in parallel. If the controller is configured as Master Controller, the PD_0<br>and PD_1 are configured as output to indicate the number of the operation phases of the system to slave devices.<br>The Slave Controller receives the phase dropping indicator signal from PD_0 and PD_1 pins. The relation between the phase<br>dropping and PD_0 and PD_1 levels are described in <u>Table 1 on page 57</u> .<br>Phases are dropped or added three switching cycles after the changes of PD_0 and PD_1 signal for both master and slave<br>controllers.<br>The PD_0 and PD_1 signals are also used to indicate the Boot-Refresh timing to the slave devices from the master device.<br>When the master detects the Boot-Refreshing timing while operating in Buck mode, the PD_0 and/or PD_1 pins will be<br>toggled to low level for one PLL-Clock period (1/12 of PWM clock cycle), which initializes the boot refresh timing of the slave<br>devices. |  |  |  |  |  |

| PWM1     | 0   | 29    | Pulse Width Modulation (PWM) output for Phase 1. Connect this output to the PWM input of an external driver IC of Phase 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PWM2     | 0   | 30    | Pulse Width Modulation (PWM) output for Phase 2. Connect this output to the PWM input of an external driver IC of Phase 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PWM3     | 0   | 31    | Pulse Width Modulation (PWM) output for Phase 3. Connect this output to the PWM input of an external driver IC of Phase 3 If this pin is connected to VCC, the device operates in 2-phase mode and PWM3 to PWM6 output will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PWM4     | 0   | 32    | Pulse Width Modulation (PWM) output for Phase 4. Connect this output to the PWM input of an external driver IC of Phase 4. If this pin is connected to VCC, the device operates in 3-phase mode and PWM4 to PWM6 output will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PWM5     | 0   | 33    | Pulse Width Modulation (PWM) output for Phase 5. Connect this output to the PWM input of an external driver IC of Phase 5. If this pin is connected to VCC, the device operates in 4-phase mode and PWM5 and PWM6 output will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| PWM6     | 0   | 34    | Pulse Width Modulation (PWM) output for Phase 6. Connect this output to the PWM input of an external driver IC of Phas<br>If this pin is connected to VCC, the device operates in 4-phase mode and PWM5 and PWM6 output will be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| DRV_EN   | 0   | 35    | Driver Enable signal output pin. This pin will be connected to the Enable pin of the driver. When the ISL78226 is read output the PWM signal, this DRV_EN signal goes high. If the ISL78226 is disabled, the hiccup/latch-off fault condition occurs, or the MCU overrides the DRV_EN register to be low (disabled), then this output will be pulled low and disable drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

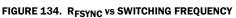

| ISEN1A   | I   | 36    | Current-Sense Amplifier (CSA) 1 input. With a combination of ISEN1B and gain setting resistor R <sub>SET1A</sub> and R <sub>SET1B</sub> , the current flowing at Current-Sense Resistor-1 will be converted to the sensed current signal and forwarded into the device. Connect ISEN1A at the negative side of Current-Sense Resistor-1 in Buck mode configuration. Ultimately senses the BAT12 voltage side of the current-sensing shunt through the filter, refer to Figure 4 on page 12. The resistive shunt MUST be Kelvir connected, do not allow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used for peak current mode control, average current control, and overcurrent protections.                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ISEN1B   | I   | 37    | The other side of Current-Sense Amplifier (CSA) 1 input. With a combination of ISEN1A and gain setting resistors, $R_{SET1A}$ and $R_{SET1B}$ , the current flowing at Current-Sense Resistor-1 will be converted to the sensed current signal and forwarded into the device. Connect ISEN1B at the positive side of Current-Sense Resistor-1 in Buck mode configuration. Ultimately senses the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvir connected. The sensed current information is used for peak current mode control, average current control, and overcurrent protections.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| ISEN2A   | I   | 38    | Current-Sense Amplifier (CSA) 2 input. With a combination of ISEN2B and gain setting resistors, R <sub>SET2A</sub> and R <sub>SET2B</sub> , the current flowing at Current Sense Resistor-2 will be converted to the sensed current signal and forwarded into the device. Connect ISEN2A at the negative side of Current-Sense Resistor-2 in Buck mode configuration. Ultimately senses the BAT12 voltage side of the current-sensing shunt through the filter, refer to Figure 4 on page 12. The resistive shunt MUST be Kelvir connected, do not allow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used for peak current mode control, average current control, and overcurrent protections.                                                                                                                                                                                                                                                   |  |  |  |  |  |

| ISEN2B   | I   | 39    | The other side of Current-Sense Amplifier (CSA) 2 input. With a combination of ISEN2A and gain setting resistors, $R_{SET2A}$ and $R_{SET2B}$ , the current flowing at Current-Sense Resistor-2 will be converted to the sensed current signal and forwarded into the device. Connect ISEN2B at the positive side of Current-Sense Resistor-2 in Buck mode configuration. Ultimately senses the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvir connected. The sensed current information is used for peak current mode control, average current control, and overcurrent protections.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PIN NAME | I/0 | PIN # | # DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ISEN3A   | 1   | 40    | Current-Sense Amplifier (CSA) 3 input. With a combination of ISEN3B and gain setting resistors, R <sub>SET3A</sub> and R <sub>SET3B</sub> , th current flowing at Current-Sense Resistor-3 will be converted to the sensed current signal and forwarded into the device Connect ISEN3A at the negative side of Current-Sense Resistor-3 in Buck mode configuration. Ultimately senses the BAT: voltage side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected do not allow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used for peak current mode control, average current control, and overcurrent protections. If this phase is not used, connect the ISEN3A to BAT12.                     |  |  |  |

| ISEN3B   | 1   | 41    | The other side of Current-Sense Amplifier (CSA) 3 input. With a combination of ISEN3A and gain setting resistors, R <sub>SET3A</sub> and R <sub>SET3B</sub> , the current flowing at Current-Sense Resistor-3 will be converted to the sensed current signal and forwarded not the device. Connect ISEN3B at the positive side of Current-Sense Resistor-3 in Buck mode configuration. Ultimately enses the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected. The sensed current information is used for peak current mode control, average current control, and overcurrent protections. If this phase is not used, float or do not connect the ISEN3B pin.                                                                        |  |  |  |

| BAT12    | I   | 42    | Power supply for internal current-sense amplifier. Connect to 12V side of current sense resistor with an RC filter (10 $\Omega$ resistor and 0.1 $\mu$ F ceramic capacitor).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ISEN4A   | I   | 43    | Current-Sense Amplifier (CSA) 4 input. With a combination of ISEN4B and gain setting resistors, R <sub>SET4A</sub> and R <sub>SET4B</sub> , the<br>current flowing at Current-Sense Resistor-4 will be converted to the sensed current signal and forwarded into the device.<br>Connect ISEN4A at the negative side of Current-Sense Resistor-4 in Buck mode configuration. Ultimately senses the BAT12<br>roltage side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected<br>to not allow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used for<br>beak current mode control, average current control, and overcurrent protections. If this phase is not used, connect the<br>SEN4A to BAT12. |  |  |  |

| ISEN4B   | I   | 44    | The other side of Current-Sense Amplifier (CSA) 4 input. With a combination of ISEN4A and gain setting resistors, R <sub>SET4</sub> , and R <sub>SET4B</sub> , the current flowing at Current-Sense Resistor-4 will be converted to the sensed current signal and forwarded into the device. Connect ISEN4B at the positive side of Current-Sense Resistor-4 in Buck mode configuration. Ultimately senses the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvi connected. The sensed current information is used for peak current mode control, average current control, and overcurrer protections. If this phase is not used, float or do not connect the ISEN4B pin.                                                                       |  |  |  |

| ISEN5A   | I   | 45    | Current-Sense Amplifier (CSA) 5 input. With a combination of ISEN5B and gain setting resistors, R <sub>SET5A</sub> and R <sub>SET5B</sub> , th current flowing at Current-Sense Resistor-5 will be converted to the sensed current signal and forwarded into the device Connect ISEN5A at the negative side of Current Sense Resistor-5 in Buck mode configuration. Ultimately senses the BAT: voltage side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected do not allow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used f peak current mode control, average current control, and overcurrent protections. If this phase is not used, connect the ISEN5A to BAT12.                       |  |  |  |

| ISEN5B   | I   | 46    | The other side of Current-Sense Amplifier (CSA) 5 input. With a combination of ISEN5A and gain setting resistor R <sub>SET5A</sub> at R <sub>SET5B</sub> , the current flowing at Current-Sense Resistor-5 will be converted to the sensed current signal and forwarded in the device. Connect ISEN5B at the positive side of Current-Sense Resistor-5 in Buck mode configuration. Ultimately sense the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected. The sensed current information is used for peak current mode control, average current control, and overcurrent protections. If this phase is not used, float or do not connect the ISEN5B pin.                                                                            |  |  |  |

| ISEN6A   | 1   | 47    | Current-Sense Amplifier (CSA) 6 input. With a combination of ISEN6B and gain setting resistors, R <sub>SET6A</sub> and R <sub>SET6B</sub> , th current flowing at Current-Sense Resistor-6 will be converted to the sensed current signal and forwarded into the device Connect ISEN6A at the negative side of Current-Sense Resistor-6 in Buck mode configuration. Ultimately senses the BAT1 voltage side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelvin connected on tallow this connection to take place anywhere else on the BAT12 plane. The sensed current information is used for peak current mode control, average current control, and overcurrent protections. If this phase is not used, connect the ISEN6A to BAT12.                        |  |  |  |

| ISEN6B   | I   | 48    | The other side of Current-Sense Amplifier (CSA) 6 input. With a combination of ISEN6A and gain setting resistors, R <sub>SET6</sub> and R <sub>SET6B</sub> , the current flowing at Current-Sense Resistor-6 will be converted to the sensed current signal and forwarde into the device. Connect ISEN6B at the positive side of Current-Sense Resistor-6 in Buck mode configuration. Ultimately senses the inductor side of the current-sensing shunt through the filter, refer to Figure 4. The resistive shunt MUST be Kelv connected. The sensed current information is used for peak current mode control, average current control, and overcurrent protections. If this phase is not used, float or do not connect the ISEN6B pin.                                                                          |  |  |  |

| ADDR     | I   | 49    | Controller address configuration pin. At the initialization phase, the device forces 30μA constant current at this pin and determines the order of the device (master, slave-1, salve-2, slave-3) by the setting of this pin.<br>If this pin is connected to GND directly, the device operates as Master.<br>If this pin is connected to VCC directly, the device operates as Slave-1.<br>If a 33.2kΩ or 68.1kΩ resistor is connected between this pin and GND, the device operates as Slave-2 and Slave-3, respectively.                                                                                                                                                                                                                                                                                         |  |  |  |

| PIN NAME | I/O | PIN # | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE     | I   | 50    | The MODE pin determines the operation switching mode (Diode Emulation (DE) mode or Forced PWM mode) and fault response (hiccup or latch-off) at the initialization period of device startup. To select the proper operation mode, connect a resistor between this pin to GND or directly connect to VCC or GND. This pin sources 30µA current while in initialization period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|          |     |       | If the pin is connected to GND directly, the device operates in DE mode and has Hiccup fault response.<br>If a $33.2k\Omega$ resistor is connected between this pin and GND, the device operates in PWM mode and has Hiccup fault response.<br>If a $68.1k\Omega$ resistor is connected between this pin and GND, the device operates in DE mode and has Latch-Off fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|          |     |       | response. If this pin is directly connected to VCC, the device operates in Forced PWM mode and Latch-Off fault response. DE and Forced PWM mode cannot be changed by internal register options once selected at EN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SLOPE_BT | I   | 51    | This pin programs the slope of the internal slope compensation for Boost mode operation. A resistor should be connected from the SLOPE_BT pin to GND. When BT/BK pin is high, this pin is activated. Slope resistor value setting and selection guidance is provided in the <u>"Loop Compensation Design - Boost"</u> section on <u>page 114</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SLOPE_BK | I   | 52    | This pin programs the slope of the internal slope compensation for Buck mode operation. A resistor should be connected from the SLOPE_BK pin to GND. When BT/BK pin is low, this pin is activated. Slope resistor value setting and selection guidance is provided in the <u>"Loop Compensation Design - Buck"</u> section on <u>page 117</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| FB_BT    | I   | 53    | The inverting input of the transconductance amplifier for Boost mode operation and the input for BAT48 rail monitoring. A resistor voltage divider must be placed between the FB_BT pin, the BAT48 rail, and GND to set the Boost mode output voltage and to monitor the BAT48 rail voltage. When configured as Master and BT/BK pin is high, this function will be activated.<br>When configured as slave device, the combination of FB_BT and FB_BK determines the total slave device count for the                                                                                                                                                                                                                                                                                                                                                                    |  |

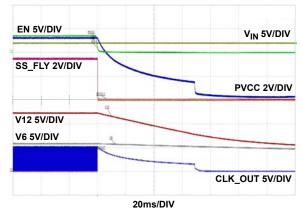

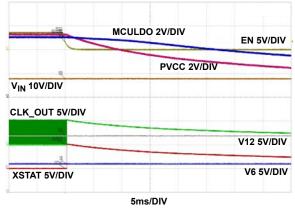

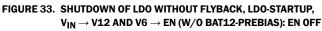

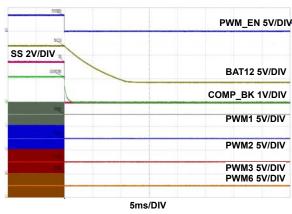

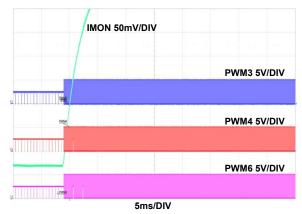

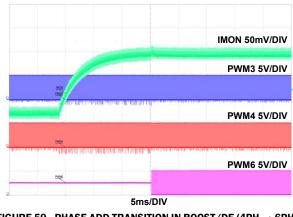

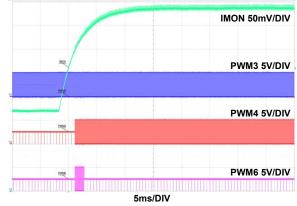

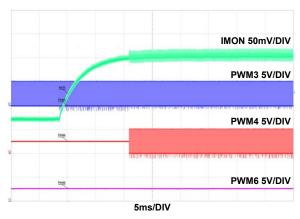

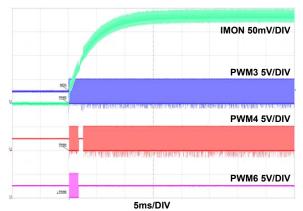

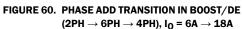

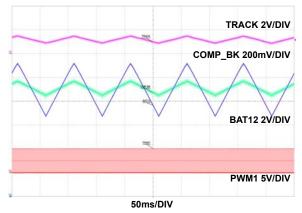

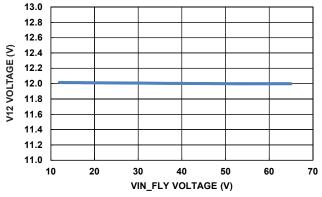

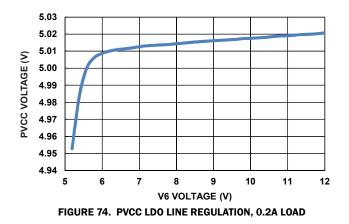

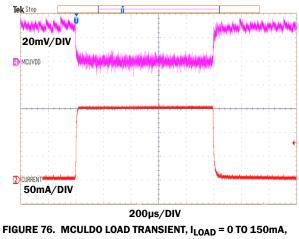

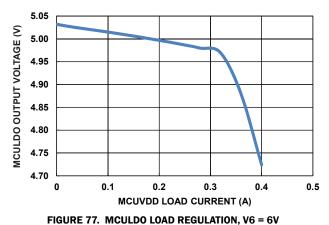

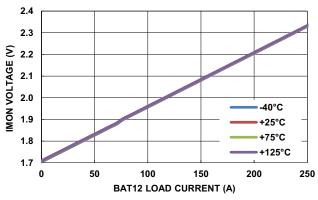

|          |     |       | proper phase shifting. If the system is configured as 1-master/1-slave operation, connect FB_BT and FB_BK pins of slave device to GND. If the system is configured as 1-master/2-slave operation, connect FB_BT and FB_BK pins of slave devices to VCC. And if the system is configured as 1-master/3-slave operation, connect FB_BT and FB_BK pins of slave devices to GND and VCC, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |