## ISL78227

2-Phase Boost Controller with Integrated Drivers

FN8808 Rev.6.00 Oct 22, 2021

The ISL78227 is an automotive grade (AEC-Q100 Grade 1), 2-phase, 55V synchronous boost controller that simplifies the design of high power boost applications. It integrates strong half-bridge drivers, an analog/digital tracking input, and comprehensive protection functions.

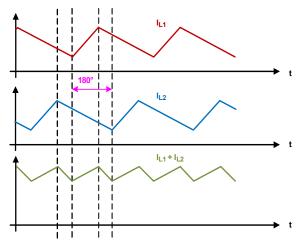

The ISL78227 enables a simple, modular design for systems requiring power and thermal scalability. It offers peak-current mode control for fast line response and simple compensation. Its synchronous 2-phase architecture enables it to support higher current while reducing the size of input and output capacitors. The integrated drivers feature programmable adaptive dead time control offering flexibility in power stage design. The ISL78227 offers a 90° output clock and supports 1-, 2-, and 4-phases.

The ISL78227 offers a highly robust solution for the most demanding environments. Its unique soft-start control prevents large negative current even in extreme cases, such as a restart under high output pre-bias on high volume capacitances. It also offers two levels of cycle-by-cycle overcurrent protection, average current limiting, input OVP, output UVP/OVP, and internal OTP. In the event of a fault, the fault protection response can be selected to be latch-off or hiccup recovery.

Also integrated are several functions that ease system design. A unique tracking input controls the output voltage, allowing it to track either a digital duty cycle (PWM) signal or an analog reference. The ISL78227 provides input average current limiting so the system can deliver transient bursts of high load current while limiting the average current to avoid overheating.

## **Features**

- Input/output voltage range: 5V to 55V, withstands 60V transients

- · Supports synchronous or standard boost topology

- Peak current mode control with adjustable slope compensation

- · Secondary average current control loop

- Integrated 5V 2A sourcing/3A sinking N-channel MOSFET drivers

- Switching frequency: 50kHz to 1.1MHz per phase

- External synchronization

- · Programmable minimum duty cycle

- · Programmable adaptive dead time control

- · Optional diode emulation and phase dropping

- · PWM and analog track function

- · Forced PWM operation with negative current limiting and protection

- · Comprehensive fault protections

- Selectable hiccup or latch-off fault response

- AEC-Q100 qualified, Grade 1: -40°C to +125°C

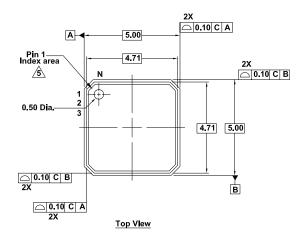

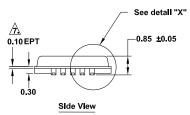

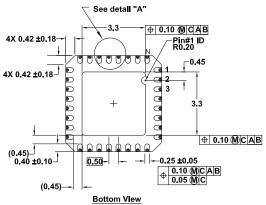

- 5mmx5mm 32 Ld Wettable Flank QFN (WFQFN) package

## Applications

- · Automotive power systems (12V to 24V, 12V to 48V, etc.)

- Trunk audio amplifiers

- Start-stop systems

- Automotive boost applications

- · Industrial and telecommunication power supplies

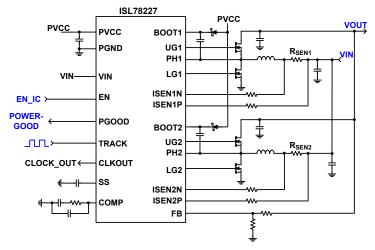

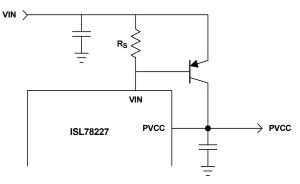

FIGURE 1. SIMPLIFIED APPLICATION SCHEMATIC, 2-PHASE **SYNCHRONOUS BOOST**

NOTE: (See Typical Application in Figure 4 on page 8.)

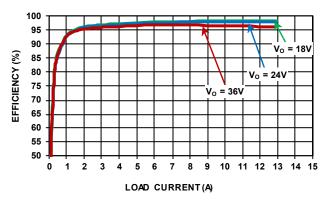

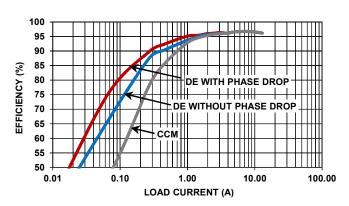

FIGURE 2. EFFICIENCY CURVES,  $V_{IN} = 12V$ ,  $T_A = +25$  °C

## **Table of Contents**

| Pin Configuration3                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional Pin Description                                                                                                                                                                                                                                                                                                      |

| Ordering Information 6                                                                                                                                                                                                                                                                                                          |

| Block Diagram 7                                                                                                                                                                                                                                                                                                                 |

| Typical Application - 2-Phase Synchronous Boost                                                                                                                                                                                                                                                                                 |

| Absolute Maximum Ratings9                                                                                                                                                                                                                                                                                                       |

| Thermal Information                                                                                                                                                                                                                                                                                                             |

| Recommended Operating Conditions 9                                                                                                                                                                                                                                                                                              |

| Electrical Specifications 9                                                                                                                                                                                                                                                                                                     |

| Performance Curves                                                                                                                                                                                                                                                                                                              |

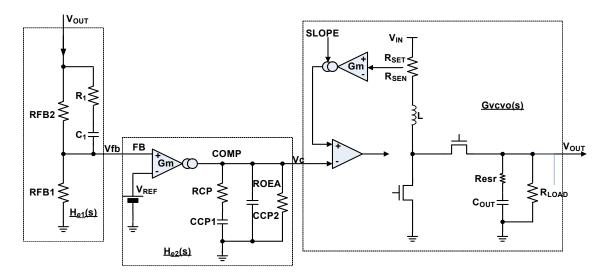

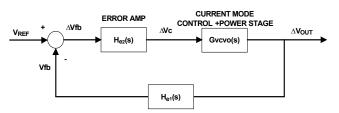

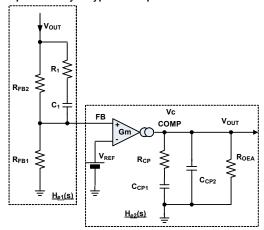

| Operation Description                                                                                                                                                                                                                                                                                                           |

| Synchronous Boost                                                                                                                                                                                                                                                                                                               |

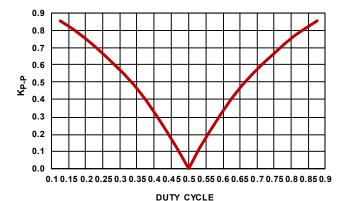

| Multiphase Power Conversion   26     Oscillator and Synchronization   27                                                                                                                                                                                                                                                        |

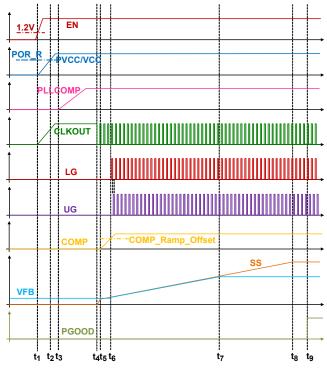

| Operation Initialization and Soft-Start. 29 Enable 30                                                                                                                                                                                                                                                                           |

| Soft-Start                                                                                                                                                                                                                                                                                                                      |

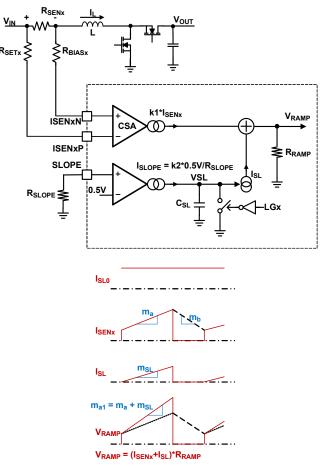

| Adjustable Slope Compensation                                                                                                                                                                                                                                                                                                   |

| Application Information                                                                                                                                                                                                                                                                                                         |

| Output Voltage Setting       37         Switching Frequency       37         Input Inductor Selection       37         Output Capacitor       38         Input Capacitor       38         Power MOSFET       38         Bootstrap Capacitor       38         Loop Compensation Design       38         Valuable Filter       40 |

| V <sub>CC</sub> Input Filter       40         Current Sense Circuit       40         Configuration to Support Single Phase Boost       40                                                                                                                                                                                       |

| Layout Considerations                                                                                                                                                                                                                                                                                                           |

| Revision History42                                                                                                                                                                                                                                                                                                              |

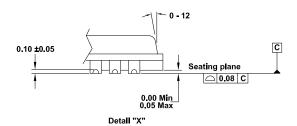

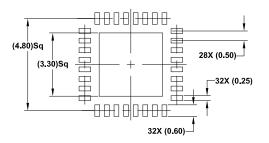

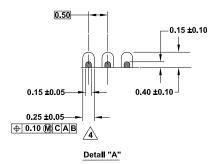

| Package Outline Drawing                                                                                                                                                                                                                                                                                                         |

## **Pin Configuration**

## **Functional Pin Description**

| PIN NAME | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vcc      | 1    | IC bias power input pin for the internal analog circuitry. Use a minimum 1μF ceramic capacitor between VCC and ground for noise decoupling purposes. VCC is typically biased by PVCC or an external bias supply with voltage ranging from 4.75V to 5.5V. Because PVCC provides pulsing drive current, a small resistor (10Ω or smaller) between PVCC and VCC can help filter out the noises from PVCC to VCC.                                                                                                                                       |

| SLOPE    | 2    | Programs the slope of the internal slope compensation. A resistor should be connected from the SLOPE pin to GND. Refer to "Adjustable Slope Compensation" on page 32 for information about how to select this resistor value.                                                                                                                                                                                                                                                                                                                       |

| FB       | 3    | The inverting input of the error amplifier for the voltage regulation loop. A resistor network must be placed between the FB pin and the output rail to set the boost converter's output voltage. Refer to "Output Voltage Setting" on page 37 for more details. Output overvoltage and undervoltage comparators also monitor this pin. Refer to "Output Overvoltage Fault Protection" and "Output Undervoltage Indication" on page 34 for more details.                                                                                            |

| СОМР     | 4    | The output of the transconductance error amplifier (Gm1) for the output voltage regulation loop. Place the compensation network between the COMP pin and ground. Refer to "Output Voltage Regulation Loop" on page 25 for more details. The COMP pin voltage can also be controlled by the constant current control loop error amplifier (Gm2) output through a diode (D <sub>CC</sub> ) when the constant current control loop is used to control the input average current. Refer to "Constant Current Control (CC)" on page 35 for more details. |

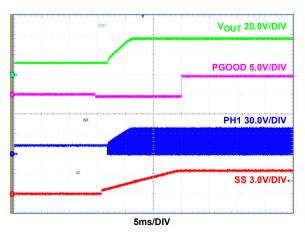

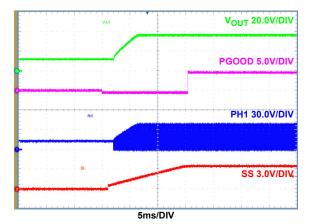

| SS       | 5    | A capacitor placed from SS to ground sets up the soft-start ramp rate and in turn, determines the soft-start time. Refer to "Soft-Start" on page 30 for more details.                                                                                                                                                                                                                                                                                                                                                                               |

## Functional Pin Description (Continued)

| PIN NAME  | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

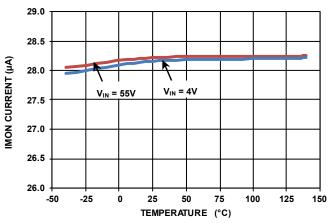

| IMON      | 6    | The average current monitor pin for the sum of the two phases' inductor currents. It is used for average current limiting and average current protection functions.  The sourcing current from the IMON pin is the sum of the two CSA outputs plus a fixed 17µA offset current. With each CSA sensing individual phase's inductor current, the IMON signal represents the sum of the two phases' inductor currents and is the input current for the boost. Place a resistor in parallel with a capacitor from IMON to ground. The IMON pin output current signal builds up the average voltage signal representing the average current sense signals.  A constant average current-limiting function and an average current protection are implemented based on the IMON signal.  • Constant Current Control: A Constant Current (CC) control loop controls the IMON average current signal equal to a 1.6V reference (VREF_CC), which ultimately limits the total input average current to a constant level. |

|           |      | <ul> <li>Average Current Protection: If the IMON pin voltage is higher than 2V, the part goes into either Hiccup or Latch-off fault<br/>protection depending on the HIC/LATCH pin configuration.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |      | Refer to "Average Current Sense for Two Phases - IMON" on page 31 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

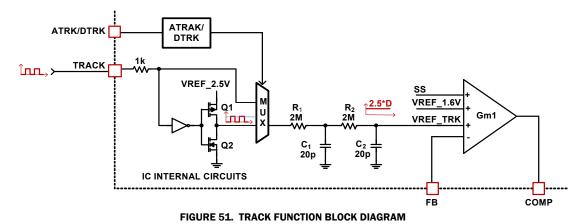

| TRACK     | 7    | External reference input pin for the IC output voltage regulation loop to follow. The input reference signal can be either a digital or analog signal selected by the ATRK/DTRK pin configuration. If the TRACK function is not used, connect the TRACK pin to VCC and the internal VREF_1.6V works as the reference. Refer to "Digital/Analog Track Function" on page 25 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

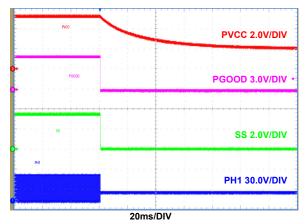

| PGOOD     | 8    | Provides an open-drain, power-good signal. Pull up this pin with a resistor to this IC's VCC for proper function. When the output voltage is within OV/UV thresholds and soft-start is completed, the internal PGOOD open-drain transistor is open and PGOOD is pulled HIGH. It is pulled low when output UV/OV or input OV conditions are detected. Refer to "PGOOD Signal" on page 30 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

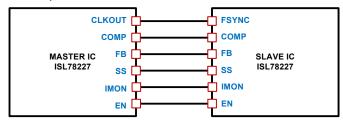

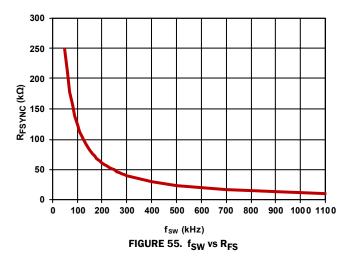

| FSYNC     | 9    | Dual-function pin for switching frequency setting and synchronization is defined as follows:.  • The PWM switching frequency can be programmed by a resistor R <sub>FSYNC</sub> from this pin to ground. PWM frequency refers to a single-phase switching frequency in this datasheet. The typical programmable frequency range is 50kHz to 1.1MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

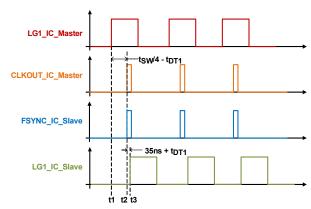

|           |      | The PWM switching frequency can also be synchronized to an external clock applied on the FSYNC pin. The FSYNC pin detects the input clock signal's rising edge that it is to be synchronized with. The typical detectable minimum pulse width of the input clock is 20ns. The rising edge of LG1 is delayed by 35ns from the rising edge of the input clock signal at the FSYNC pin. When the internal clock is locked to the external clock, it latches to the external clock. If the external clock on the FSYNC pin is removed, the switching frequency oscillator shuts down. The part then detects PLL_LOCK fault and goes to either Hiccup mode or Latch-off mode, depending on the HIC/LATCHOFF pin configuration. If the part is set in Hiccup mode, it restarts with frequency set by RFSYNC.                                                                                                                                                                                                       |

|           |      | The typical synchronization frequency range is 50kHz to 1.1MHz. The phase dropping mode is <b>not allowed</b> with external synchronization. Refer to "Oscillator and Synchronization" on page 27 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HIC/LATCH | 10   | Select either Hiccup or Latch-off response to faults including output overvoltage (monitoring the FB pin), output undervoltage (monitoring the FB pin, default inactive), V <sub>IN</sub> overvoltage (monitoring the FB pin), peak overcurrent protection (OC2_PEAK), and average current protection (monitoring the IMON pin), etc.  Set HIC/LATCH = HIGH to activate the Hiccup fault response.  Set HIC/LATCH = LOW to activate the Latch-off fault response. Either toggling the EN pin or recycling VCC POR resets the IC from Latch-off status. Refer to "Selectable Hiccup or Latch-Off Fault Response" on page 33 for more details.                                                                                                                                                                                                                                                                                                                                                                 |

| DE/PHDRP  | 11   | Selects Diode Emulation mode (DE), Phase Dropping (PH_DROP) mode, or Continuous Conduction Mode (CCM). The three configurable modes are: DE mode, DE plus PH_DROP mode, and CCM mode.  Refer to Table 2 on page 33 for the three configurable options. PD_DROP mode is <b>not allowed</b> with external synchronization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

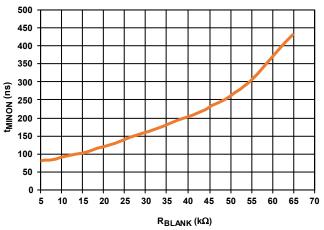

| RBLANK    | 12   | A resistor from this pin to ground programs the blanking time for current sensing after the PWM is ON (LG is ON). This blanking time is also called t <sub>MINON</sub> time, meaning the minimum ON-time when a PWM pulse is ON. Refer to <u>"Minimum On-Time (Blank Time) Consideration" on page 28</u> for the selection of R <sub>BLANK</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

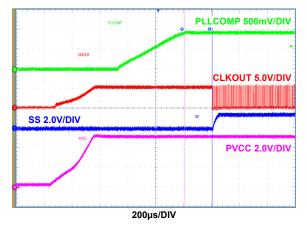

| PLLCOMP   | 13   | Compensation node for the switching frequency clock's PLL (Phase Lock Loop). A second order passive loop filter connected between this pin and ground compensates the PLL. Refer to "Oscillator and Synchronization" on page 27 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EN        | 14   | Threshold-sensitive enable input for the controller. When the EN pin is driven above 1.21V (typical), the ISL78227 is enabled and the internal LDO is activated to power up PVCC followed by a start-up procedure. Driving the EN pin below 0.95V disables the IC and clears all fault states. Refer to "Enable" on page 30 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKOUT    | 15   | Outputs a clock signal with same frequency to one phase's switching frequency. The rising edge signal on the CLKOUT pin is delayed by 90° from the rising edge of LG1 of the same IC. With CLKOUT connected to the FSYNC pin of the second ISL78227, a 4-phase interleaving operation can be achieved. Refer to "Oscillator and Synchronization" on page 27 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Functional Pin Description (Continued)

| PIN NAME  | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ВООТ2     | 16   | Provides bias voltage to the Phase 2 high-side MOSFET driver. A bootstrap circuit creates a voltage suitable to drive the external N-channel MOSFET. A $0.47\mu F$ ceramic capacitor in series with a $1.5\Omega$ resistor is recommended between the BOOT2 and PH2 pins. In the typical configuration, PVCC provides the bias to BOOT2 through a fast switching diode. In applications in which a high-side driver is not needed (for example, standard boost applications), BOOT2 is recommended to be connected to ground. The ISL78227 IC can detect BOOT2 being grounded during start-up and both the Phase 1 and Phase 2 high-side drivers are disabled. In addition, PH1 and PH2 should also be tied to ground. |

| UG2       | 17   | Phase 2 high-side gate driver output. Disable this output by tying either BOOT1 and PH1 to ground or BOOT2 and PH2 to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PH2       | 18   | Represents the return path for the Phase 2 high-side gate drive. Connect this pin to the source of the Phase 2 high-side MOSFETs and the drain of the low-side MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LG2       | 19   | Phase 2 low-side gate driver output. It should be connected to the Phase 2 low-side MOSFETs' gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PGND      | 20   | Provides the return path for the low-side MOSFET drivers. This pin carries a noisy driving current, so traces connecting from this pin to the low-side MOSFET source and PVCC decoupling capacitor ground pad should be as short as possible. All sensitive analog signal traces should not share common traces with this driver return path. Connect this pin to the ground copper plane (wiring away from the IC instead of connecting through the IC bottom PAD) through several vias as close as possible to the IC.                                                                                                                                                                                               |

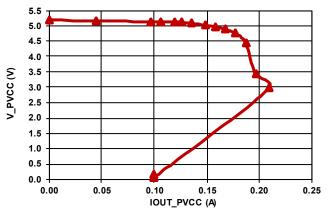

| PVCC      | 21   | Output of the internal linear regulator that provides bias for the low-side driver, high-side driver (PVCC connected to BOOTx through diodes), and VCC bias (PVCC and VCC are typically connected through a small resistor like $10\Omega$ or smaller, which helps to filter out the noises from PVCC to VCC). The PVCC operating range is 4.75V to 5.5V. A minimum $10\mu$ F decoupling ceramic capacitor should be used between PVCC and PGND. Refer to "Internal 5.2V LDO" on page 36 for more details.                                                                                                                                                                                                             |

| LG1       | 22   | Phase 1 low-side gate driver output. It should be connected to the Phase 1 low-side MOSFETs' gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PH1       | 23   | Represents the return path for the Phase 1 high-side gate drive. Connect this pin to the source of the Phase 1 high-side MOSFETs and the drain of the low-side MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UG1       | 24   | Phase 1 high-side MOSFET gate drive output. Disable this output by tying either BOOT1 and PH1 to ground or BOOT2 and PH2 to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B00T1     | 25   | Provides bias voltage to the Phase 1 high-side MOSFET driver. A bootstrap circuit creates a voltage suitable to drive the external N-channel MOSFET. A 0.47μF ceramic capacitor in series with a 1.5Ω resistor are recommended between BOOT1 and PH1 pins. In a typical configuration, PVCC provides the bias to BOOT1 through a fast switching diode.  In applications in which a high-side driver is not needed (for example, standard boost applications), BOOT1 is recommended to be connected to ground. The ISL78227 IC can detect BOOT1 being grounded during start-up and both the Phase 1 and Phase 2 high-side drivers are disabled. In addition, PH1 and PH2 should also be tied to ground.                 |

| VIN       | 26   | Connect the supply rail to this pin. Typically, connect the boost input voltage to this pin. The VIN pin can also be supplied by a separate input source independent from the boost power stage input source. This pin is connected to the input of the internal linear regulator, generating the power necessary to operate the chip. The DC voltage applied to VIN should not exceed 55V during norma operation. VIN can withstand transients up to 60V, but in this case, the device's overvoltage protection stops it from switching to protect itself. Refer to "Input Overvoltage Fault Protection" on page 34 for more details.                                                                                 |

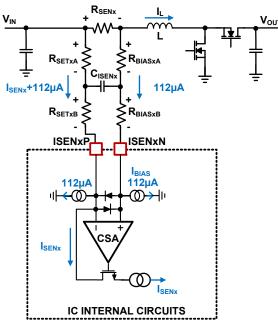

| ISEN1N    | 27   | The ISEN1N pin is the negative potential input to the Phase 1 current sense amplifier. This amplifier continuously senses the Phase 1 inductor current through a power current sense resistor in series with the inductor. The sensed current signal is used for current mode control, peak current limiting, average current limiting, and diode emulation.                                                                                                                                                                                                                                                                                                                                                           |

| ISEN1P    | 28   | Positive potential input to the Phase 1 current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ISEN2N    | 29   | Negative potential input to the Phase 2 current sense amplifier. This amplifier continuously senses the Phase 2 inductor current through a power current sense resistor in series with the inductor. The sensed current signal is used for current mode control, peak current limiting, average current limiting, and diode emulation.                                                                                                                                                                                                                                                                                                                                                                                 |

| ISEN2P    | 30   | Positive phase input to the Phase 2 current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ATRK/DTRK | 31   | Logic input pin to select the input signal format options for the TRACK pin. Pull this pin HIGH for the TRACK pin to accept analog input signals. Pull this pin LOW for the TRACK pin to accept digital input signals. Refer to "Digital/Analog Track Function" on page 25 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                           |

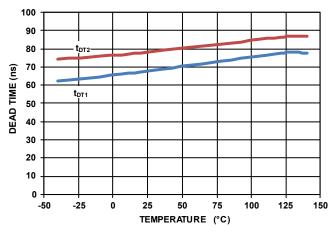

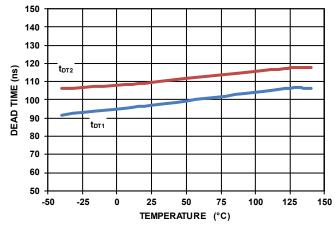

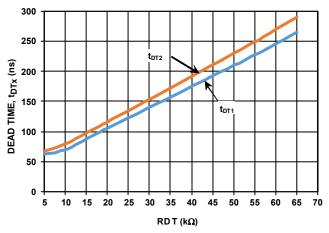

| RDT       | 32   | A resistor connected from this pin to ground programs the dead times between UGx OFF to LGx ON and LGx OFF to UGx ON to prevent shoot-through. Refer to "Driver Configuration" on page 24 for the selection of RDT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SGND      | -    | Signal ground bottom pad to which to refer the internal sensitive analog circuits. Also serves as thermal pad. Connect this pad to a large ground plane. Put as many vias as possible in this pad connecting to the ground copper plane to help reduce the IC's $\theta_{JA}$ . In layout power flow planning, avoid noisy, high frequency pulse current flow through the SGND area.                                                                                                                                                                                                                                                                                                                                   |

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART MARKING     | PACKAGE DESCRIPTION<br>(ROHS COMPLIANT) | PKG.<br>DWG. # | CARRIER TYPE<br>(Note 1) | TEMP. RANGE   |

|-----------------------------|------------------|-----------------------------------------|----------------|--------------------------|---------------|

| ISL78227ARZ                 | ISL7822          | 32 Ld 5x5 WFQFN                         | L32.5x5H       | Tube                     | -40 to +125°C |

| ISL78227ARZ-T               | 7ARZ             |                                         |                | Reel, 6k                 |               |

| ISL78227ARZ-T7A             |                  |                                         |                | Reel, 250                |               |

| ISL78227EV1Z                | Evaluation Board |                                         |                |                          |               |

#### NOTES:

- 1. See TB347 for details about reel specifications.

- These Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu-Ag plate e4

termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified

at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the ISL78227 product information page. For more information about MSL, see TB363.

#### **TABLE 1. KEY DIFFERENCES BETWEEN FAMILY OF PARTS**

| PART<br>NUMBER | TOPOLOGY                 | PMBus™ | NTC | TRACK FUNCTION | PACKAGE         |

|----------------|--------------------------|--------|-----|----------------|-----------------|

| ISL78229       | 2-Phase Boost Controller | Yes    | Yes | Yes            | 40 Ld 6x6 WFQFN |

| ISL78227       | 2-Phase Boost Controller | No     | No  | Yes            | 32 Ld 5x5 WFQFN |

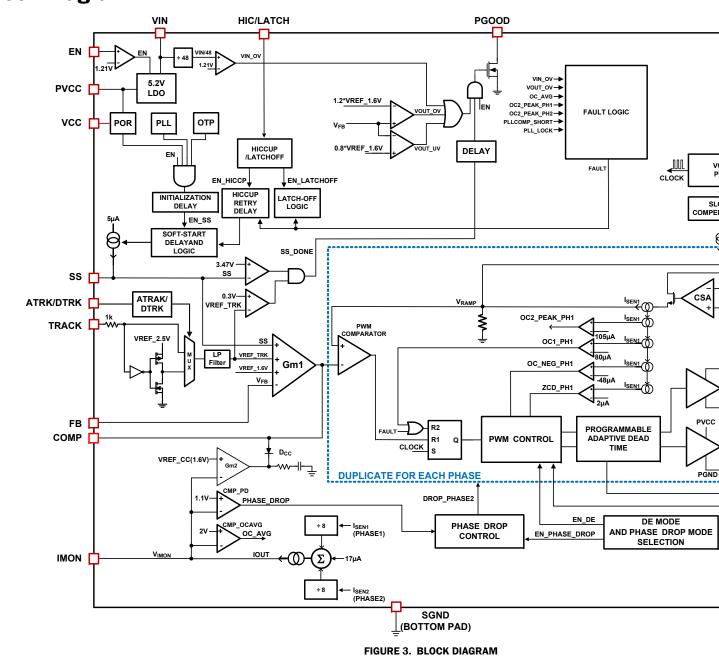

## **Block Diagram**

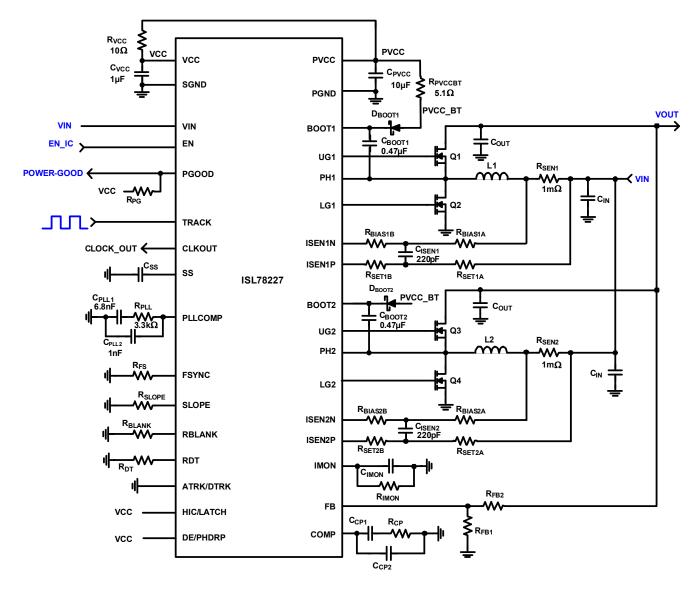

## **Typical Application - 2-Phase Synchronous Boost**

ATRK/DTRK:

- = VCC to track analog signal = GND to track digital signal

Q1, Q2, Q3, Q4: 2 BUK9Y6R0-60E in parallel

#### HIC/LATCH:

- = VCC for HICCUP mode

- = GND for LATCHOFF mode

### DE/PHDRP:

- = VCC for DE mode

- = FLOAT for DE and Phase-Drop mode = GND for CCM mode

FIGURE 4. TYPICAL APPLICATION 2-PHASE SYNCHRONOUS BOOST

## **Absolute Maximum Ratings**

| VIN<br>PH1, PH2                              |                             |

|----------------------------------------------|-----------------------------|

| 10                                           | OV(<20ns Pulse Width, 25µJ) |

| BOOT1, BOOT2, UG1, UG2                       | 0.3V to +65V                |

| Upper Driver Supply Voltage, VBOOTx - VPHx . | 0.3V to +6.5V               |

|                                              |                             |

| PVCC, VCC                                    | 0.3V to +6.5V               |

| ISEN1P, ISEN1N, ISEN2P, ISEN2N               | 0.3V to +60V                |

| V <sub>ISENXP</sub> - V <sub>ISENXN</sub>    | ±0.6V                       |

| All Other Pins                               | 0.3V to VCC + 0.3V          |

| ESD Rating                                   |                             |

| Human Body Model (Tested per AEC-Q100        | -002)2kV                    |

| Charged Device Model (Tested per AEC-Q1      | .00-011)                    |

| Latch-Up Rating (Tested per AEC-Q100-004)    | 100mA                       |

|                                              |                             |

### **Thermal Information**

| Thermal Resistance                         | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}(^{\circ}C/W)$ |

|--------------------------------------------|----------------------------|----------------------------|

| 32 Ld 5x5 WFQFN Package (Notes 4, 5)       | 30                         | 1.2                        |

| Maximum Junction Temperature (Plastic Pack | age)                       | +150°C                     |

| Maximum Storage Temperature Range          | <del>.</del> 6             | 55°C to +150°C             |

| Pb-Free Reflow Profile                     |                            | see <u>TB493</u>           |

### **Recommended Operating Conditions**

| VIN 5V to +55V                                                      |

|---------------------------------------------------------------------|

| PVCC, VCC                                                           |

| PH1, PH20.3V to +55V                                                |

| Upper Driver Supply Voltage, V <sub>BOOTx</sub> - V <sub>PHx</sub>  |

| ISEN1P to ISEN1N and ISEN2P to ISEN2N Differential Voltage ±0.3V    |

| ISEN1P, ISEN1N, ISEN2P, ISEN2N Common-Mode Voltage 4V to 55V        |

| Operational Junction Temperature Range (Automotive)40 °C to +125 °C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>IA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

- 5. For  $\theta_{\mbox{\scriptsize JC}},$  the case temperature location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Refer to Figure 3 on page 7 and Typical Application Schematics (page 8). Operating conditions unless otherwise noted:  $V_{IN}$  = 12V,  $V_{PVCC}$  = 5.2V and  $V_{VCC}$  = 5.2V,  $T_A$  = -40°C to +125°C (Note 7). Typical values are at  $T_A$  = +25°C. **Boldface limits apply across** the operating temperature range, -40°C to +125°C.

| PARAMETER                                                                    | SYMBOL                 | TEST CONDITIONS                                                                                                                                             | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNIT |

|------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| SUPPLY INPUT                                                                 |                        |                                                                                                                                                             |                 |      | •               |      |

| Input Voltage Range                                                          | V <sub>IN</sub>        | Switching, under the condition of internal LDO having dropout (V <sub>IN</sub> - PVCC) less than 0.25V                                                      | 5               |      | 55              | V    |

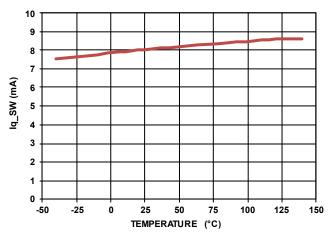

| Input Supply Current to the VIN Pin (IC Enabled)                             | I <sub>Q_SW</sub>      | EN = 5V, V <sub>IN</sub> = 12V, PVCC = VCC, BOOT1 and BOOT2 supplied by PVCC, R <sub>FSYNC</sub> = 40.2k (f <sub>SW</sub> = 300kHz), LGx = OPEN, UGx = OPEN |                 | 8.0  | 10.0            | mA   |

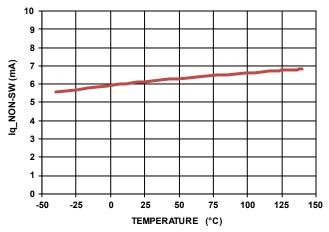

|                                                                              | I <sub>Q_NON</sub> -sw | EN = 5V, V <sub>IN</sub> = 12V, PVCC = VCC, BOOT1 and BOOT2 supplied by PVCC, non-switching, LGx = OPEN, UGx = OPEN                                         |                 | 6.0  | 8.5             | mA   |

| Input Supply Current to the VIN Pin (IC Shutdown)                            | I_SD_VIN_55V           | EN = GND, V <sub>IN</sub> = 55V                                                                                                                             |                 | 0.2  | 1.0             | μΑ   |

| Input Bias Current (IC Shutdown) to Each of ISEN1P/ISEN1N/ISEN2P/ISEN2N Pins | I_SD_ISENxP/N          | EN = GND, V <sub>IN</sub> = 55V<br>ISEN1P (or<br>ISEN1N/ISEN2P/ISEN2N) = 55V                                                                                | -1              | 0    | 1               | μA   |

| INPUT OVERVOLTAGE PROTECTION                                                 |                        |                                                                                                                                                             |                 |      | 1               |      |

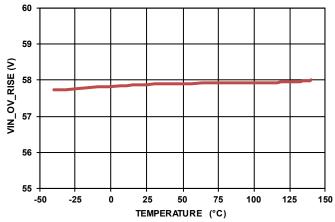

| V <sub>IN</sub> OVP Rising Threshold (Switching Disable)                     |                        | EN = 5V, V <sub>IN</sub> rising                                                                                                                             | 56.5            | 58.0 | 59.5            | ٧    |

| V <sub>IN</sub> OVP Trip Delay                                               |                        | EN = 5V, V <sub>IN</sub> rising                                                                                                                             |                 | 5    |                 | μs   |

| INTERNAL LINEAR REGULATOR                                                    |                        |                                                                                                                                                             |                 |      |                 |      |

| LDO Voltage (PVCC Pin)                                                       | V <sub>PVCC</sub>      | V <sub>IN</sub> = 6V to 55V, C <sub>PVCC</sub> = 4.7μF,<br>I <sub>PVCC</sub> = 10mA                                                                         | 5.0             | 5.2  | 5.4             | ٧    |

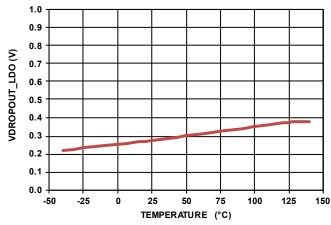

| LDO Saturation Dropout Voltage (PVCC Pin)                                    | V <sub>DROPOUT</sub>   | V <sub>IN</sub> = 4.9V, C <sub>PVCC</sub> = 4.7μF, I_PVCC = 80mA                                                                                            |                 | 0.3  |                 | ٧    |

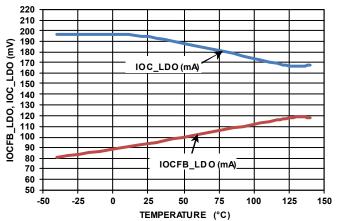

| LDO Current Limit (PVCC Pin)                                                 | I <sub>OC_LDO</sub>    | V <sub>IN</sub> = 6V, V <sub>PVCC</sub> = 4.5V                                                                                                              | 130             | 195  | 250             | mA   |

| LDO Output Short Current Limit (PVCC Pin)                                    | I <sub>OCFB_LDO</sub>  | V <sub>IN</sub> = 6V, V <sub>PVCC</sub> = 0V                                                                                                                | 50              | 100  | 160             | mA   |

| PARAMETER                                        | SYMBOL                   | TEST CONDITIONS                                                                                                                                                                               | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNIT |

|--------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

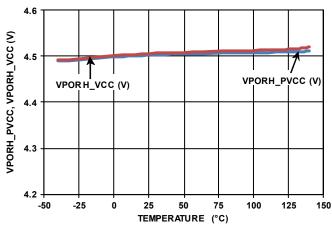

| POWER-ON RESET (For both PVCC and VCC)           |                          |                                                                                                                                                                                               |                 |      |                 | l    |

| Rising V <sub>VCC</sub> POR Threshold            | V <sub>PORH_VCC</sub>    |                                                                                                                                                                                               | 4.35            | 4.50 | 4.75            | ٧    |

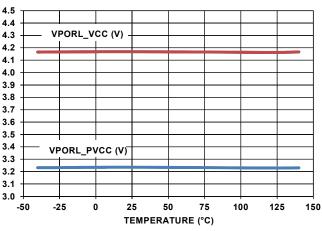

| Falling V <sub>VCC</sub> POR Threshold           | V <sub>PORL_VCC</sub>    |                                                                                                                                                                                               | 4.05            | 4.15 | 4.25            | ٧    |

| V <sub>VCC</sub> POR Hysteresis                  | V <sub>PORHYS_VCC</sub>  |                                                                                                                                                                                               |                 | 0.4  |                 | ٧    |

| Rising V <sub>PVCC</sub> POR Threshold           | V <sub>PORH_PVCC</sub>   |                                                                                                                                                                                               | 4.35            | 4.50 | 4.75            | V    |

| Falling V <sub>PVCC</sub> POR Threshold          | V <sub>PORL_PVCC</sub>   |                                                                                                                                                                                               | 3.0             | 3.2  | 3.4             | ٧    |

| V <sub>PVCC</sub> POR Hysteresis                 | V <sub>PORHYS_PVCC</sub> |                                                                                                                                                                                               |                 | 1.3  |                 | ٧    |

| Soft-Start Delay                                 | t <sub>SS_DLY</sub>      | From POR rising to initiation of soft-start.<br>$R_{FSYNC}$ = 61.9k, $f_{SW}$ = 200kHz, PLLCOMP pin network of $R_{PLL}$ = 3.24k, $C_{PLL1}$ = 6.8nF, and $C_{PLL2}$ = 1nF                    |                 | 0.85 |                 | ms   |

| EN                                               |                          | 1                                                                                                                                                                                             | 1               |      |                 |      |

| Enable Threshold                                 | V <sub>ENH</sub>         | EN Rising                                                                                                                                                                                     | 1.13            | 1.21 | 1.33            | V    |

|                                                  | V <sub>ENL</sub>         | EN Falling                                                                                                                                                                                    | 0.85            | 0.95 | 1.10            | V    |

|                                                  | V <sub>EN_HYS</sub>      | Hysteresis                                                                                                                                                                                    |                 | 250  |                 | m۷   |

| Input Impedance                                  |                          | EN = 4V                                                                                                                                                                                       | 2               | 6    |                 | МΩ   |

| PWM SWITCHING FREQUENCY                          |                          |                                                                                                                                                                                               |                 |      |                 | ı    |

| PWM Switching Frequency (Per Phase)              | Fosc                     | $R_{FSYNC} = 249 \mathrm{k}\Omega  (0.1\%)$                                                                                                                                                   | 46.0            | 50.2 | 54.5            | kHz  |

|                                                  |                          | $R_{FSYNC} = 82.5k\Omega (0.1\%)$                                                                                                                                                             | 142             | 150  | 156             | kHz  |

|                                                  |                          | $R_{FSYNC} = 40.2k\Omega (0.1\%)$                                                                                                                                                             | 290             | 300  | 310             | kHz  |

|                                                  |                          | $R_{FSYNC} = 10k\Omega (0.1\%)$                                                                                                                                                               | 990             | 1100 | 1170            | kHz  |

| Minimum Adjustable Switching Frequency           |                          |                                                                                                                                                                                               |                 | 50   |                 | kHz  |

| Maximum Adjustable Switching Frequency           |                          |                                                                                                                                                                                               |                 | 1100 |                 | kHz  |

| FSYNC Pin Voltage                                |                          |                                                                                                                                                                                               |                 | 0.5  |                 | ٧    |

| Minimum ON-Time (Blanking Time) on LGx           | t <sub>MINON_1</sub>     | Minimum duty cycle, $C_{UG} = C_{LG} = OPEN$<br>$R_{BLANK} = 80k\Omega (0.1\%)$                                                                                                               | 315             | 410  | 525             | ns   |

|                                                  | t <sub>MINON_2</sub>     | Minimum duty cycle, $C_{UG} = C_{LG} = OPEN$<br>$R_{BLANK} = 50kΩ (0.1%)$                                                                                                                     | 175             | 260  | 325             | ns   |

|                                                  | t <sub>MINON</sub> 3     | Minimum duty cycle, $C_{UG} = C_{LG} = OPEN$<br>$R_{BLANK} = 25k\Omega (0.1\%)$                                                                                                               | 100             | 140  | 180             | ns   |

|                                                  | t <sub>MINON_4</sub>     | Minimum duty cycle, C <sub>UG</sub> = C <sub>LG</sub> = OPEN<br>R <sub>BLANK</sub> = 10k                                                                                                      | 75              | 90   | 105             | ns   |

| Maximum Duty Cycle                               | D <sub>MAX</sub>         | $\begin{split} &D_{MAX} = T\_LG\_ON/t_{SW}, \ V_{COMP} = 3.5V, \\ &f_{SW} = 300 \text{kHz}, \ \text{RDT} = 18.2 \text{k}\Omega, \ C_{UG} = \text{OPEN}, \\ &C_{LG} = \text{OPEN} \end{split}$ | 88.5            | 89.0 | 90.5            | %    |

| SYNCHRONIZATION (FSYNC PIN)                      | I                        | ı                                                                                                                                                                                             | ı L             |      | 1               | l .  |

| Minimum Synchronization Frequency at FSYNC Input |                          |                                                                                                                                                                                               |                 | 50   |                 | kHz  |

| Maximum Synchronization Frequency at FSYNC Input |                          |                                                                                                                                                                                               |                 | 1100 |                 | kHz  |

| Input High Threshold                             | V <sub>IH</sub>          |                                                                                                                                                                                               | 3.5             |      |                 | ٧    |

| Input Low Threshold                              | V <sub>IL</sub>          |                                                                                                                                                                                               |                 |      | 1.5             | V    |

| PARAMETER                                                                                 | SYMBOL               | TEST CONDITIONS                                                                                                                                                        | MIN<br>(Note 6)       | TYP                    | MAX<br>( <u>Note 6</u> ) | UNIT |

|-------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--------------------------|------|

| Input Minimum Pulse Width - Rise-to-Fall                                                  |                      |                                                                                                                                                                        | 20                    |                        |                          | ns   |

| Input Minimum Pulse Width - Fall-to-Rise                                                  |                      |                                                                                                                                                                        | 20                    |                        |                          | ns   |

| Delay Time from Input Pulse Rising to LG1<br>Rising Edge Minus Dead Time t <sub>DT1</sub> |                      | $C_{LG}$ = OPEN, RDT = $50k\Omega$                                                                                                                                     |                       | 35                     |                          | ns   |

| Input Impedance                                                                           |                      | Input impedance before synchronization mode                                                                                                                            |                       | 1                      |                          | kΩ   |

|                                                                                           |                      | Input impedance after synchronization mode                                                                                                                             |                       | 200                    |                          | МΩ   |

| CLKOUT                                                                                    |                      |                                                                                                                                                                        |                       | 11                     | •                        |      |

| CLKOUTH                                                                                   |                      | I <sub>CLKOUT</sub> = 500μA                                                                                                                                            | V <sub>CC</sub> - 0.5 | V <sub>CC</sub> - 0.1  |                          | V    |

| CLKOUTL                                                                                   |                      | I <sub>CLKOUT</sub> = -500μA                                                                                                                                           |                       | 0.1                    | 0.4                      | V    |

| Output Pulse Width                                                                        |                      | C <sub>CLKOUT</sub> = 100pF, t <sub>SW</sub> is each phase's switching period                                                                                          |                       | 1/12 * t <sub>SW</sub> |                          |      |

| Phase Shift from LG1 Rising Edge to CLKOUT Pulse Rising Edge                              |                      | C <sub>LG1</sub> = OPEN, C <sub>CLKOUT</sub> = OPEN,<br>f <sub>SW</sub> = 300kHz, t <sub>DT1</sub> = 60ns (refer to<br>Figure 56 on page 28 for the timing<br>diagram) |                       | 87                     |                          | o    |

| SOFT-START                                                                                |                      |                                                                                                                                                                        |                       | 11                     | •                        |      |

| Soft-Start Current                                                                        | I <sub>SS</sub>      |                                                                                                                                                                        | 4.5                   | 5.0                    | 5.5                      | μΑ   |

| Minimum Soft-Start Pre-Bias Voltage                                                       |                      |                                                                                                                                                                        |                       | 0                      |                          | V    |

| Maximum Soft-Start Pre-Bias Voltage                                                       |                      |                                                                                                                                                                        |                       | 1.6                    |                          | V    |

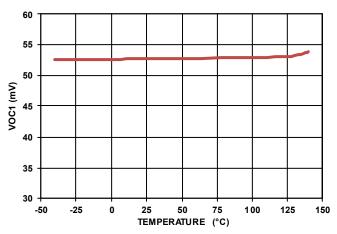

| Soft-Start Pre-bias Voltage Accuracy                                                      |                      | V <sub>FB</sub> = 500mV                                                                                                                                                | -25                   | 0                      | 25                       | mV   |

| Soft-Start Clamp Voltage                                                                  | V <sub>SSCLAMP</sub> |                                                                                                                                                                        | 3.25                  | 3.47                   | 3.70                     | V    |

| HICCUP RETRY DELAY (Refer to "Selectable H                                                | liccup or Latch-Of   | f Fault Response" on page 33 for details)                                                                                                                              |                       | 11                     | •                        |      |

| Hiccup Retry Delay                                                                        |                      | If Hiccup fault response selected                                                                                                                                      |                       | 500                    |                          | ms   |

| REFERENCE VOLTAGE FOR OUTPUT VOLTAGE                                                      | REGULATION           |                                                                                                                                                                        |                       | I .                    |                          | .1   |

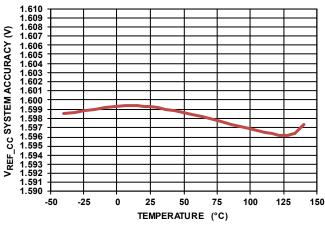

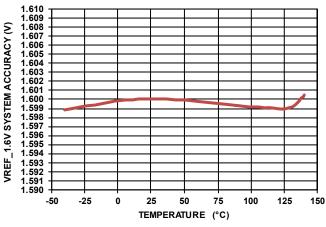

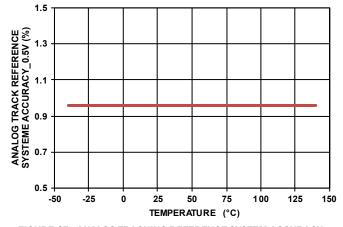

| System Reference Accuracy                                                                 |                      | Measured at the FB pin                                                                                                                                                 | 1.576                 | 1.600                  | 1.620                    | V    |

| FB Pin Input Bias Current                                                                 |                      | V <sub>FB</sub> = 1.6V, TRACK = Open                                                                                                                                   | -0.05                 | 0.01                   | 0.05                     | μΑ   |

| ERROR AMPLIFIER FOR OUTPUT VOLTAGE RE                                                     | GULATION (Gm1)       |                                                                                                                                                                        |                       | 11                     | •                        |      |

| Transconductance Gain                                                                     |                      |                                                                                                                                                                        |                       | 2                      |                          | mA/V |

| Output Impedance                                                                          |                      |                                                                                                                                                                        |                       | 7.5                    |                          | МΩ   |

| Unity Gain Bandwidth                                                                      |                      | C <sub>COMP</sub> = 100pF from COMP pin to GND                                                                                                                         |                       | 3.3                    |                          | MHz  |

| Slew Rate                                                                                 |                      | C <sub>COMP</sub> = 100pF from COMP pin to GND                                                                                                                         |                       | ±3                     |                          | V/µs |

| Output Current Capability                                                                 |                      |                                                                                                                                                                        |                       | ±300                   |                          | μΑ   |

| Maximum Output Voltage                                                                    |                      |                                                                                                                                                                        | 3.5                   | 3.7                    |                          | V    |

| Minimum Output Voltage                                                                    |                      |                                                                                                                                                                        |                       | 0.1                    | 0.3                      | ٧    |

| PWM CORE                                                                                  | <u> </u>             | 1                                                                                                                                                                      |                       | L                      | 1                        | 1    |

| SLOPE Pin Voltage                                                                         |                      |                                                                                                                                                                        | 480                   | 500                    | 520                      | m۷   |