## ISL78268

55V Synchronous Buck Controller with Integrated 3A Driver

FN8657 Rev 3.00 December 12, 2014

The ISL78268 is a grade 1, automotive, synchronous buck controller with integrated high/low side MOSFET drivers. It supports a wide operating input voltage range of 5V to 55V and up to 60V at  $V_{\rm IN}$  when not switching. The integrated driver offers adaptive dead-time control and is capable of supplying up to 2A sourcing and 3A sinking current, allowing the ISL78268 to support power stages designed for a wide range of loads, from under 1A to over 25A.

ISL78268's fully synchronous architecture enables power conversion with very high efficiency and improved thermal performance over standard buck converters. The ISL78268 also offers diode emulation mode for improved light load efficiency.

While ISL78268 is a peak current mode PWM controller, it also includes a dedicated average output current modulation loop, which achieves constant output current limiting for applications such as battery charging, super-cap charging, and temperature control systems where a constant current must be provided.

The ISL78268 supports switching frequencies from 50kHz to 1.1MHz allowing the user the flexibility to trade-off switching frequency and efficiency against the size of external components.

The ISL78268 offers comprehensive protection features. It includes robust current protection with cycle-by-cycle peak current limiting, average current limiting, and a selectable hiccup or latch-off fault responses. In addition, it offers protection against over-temperature, as well as input and output overvoltages.

## **Features**

- Wide input range 5V to 55V (switching); withstand 60V (non-switching)

- . Integrated 2A sourcing, 3A sinking MOSFET drivers

- Constant current regulation/limiting dedicated average current control loop

- Adjustable switching frequency or external synchronization from 50kHz up to 1.1MHz

- Low shutdown current, I<sub>O</sub> <1μA

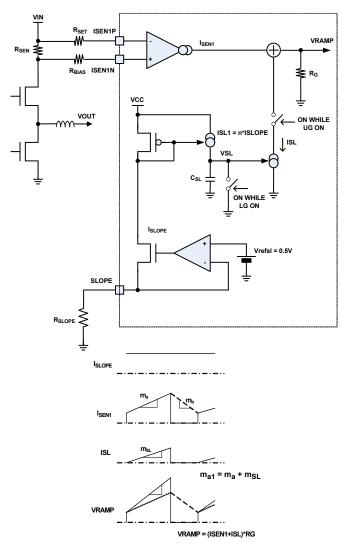

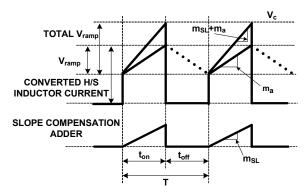

- Peak current mode control with adjustable slope compensation

- Selectable diode emulation mode for high efficiency at light load

- Input and output OVP, cycle-by-cycle current limiting, average current OCP, OTP

- · Selectable hiccup or latch-off fault responses

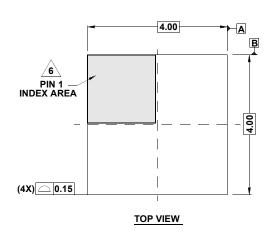

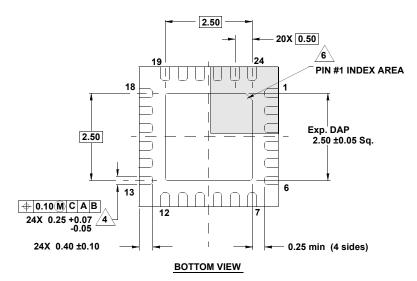

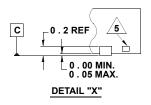

- Pb-free 24 Ld 4x4 QFN package (RoHS compliant)

- · AEC-Q100 qualified

## **Applications**

- · Automotive power

- · Telecom and industrial power supplies

- General purpose power

- · Supercap charging

## **Related Literature**

AN1946, "ISL78268EVAL1Z Evaluation Board User Guide"

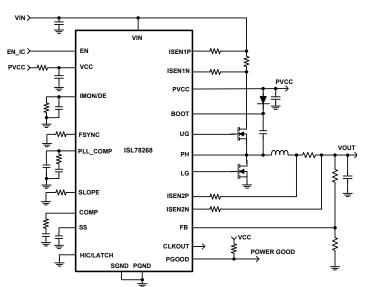

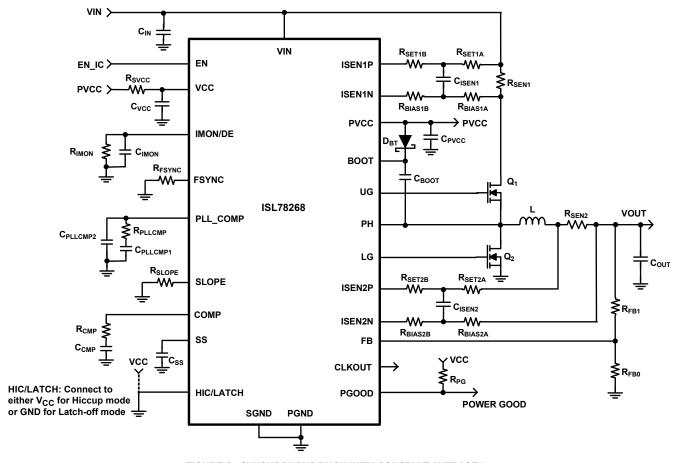

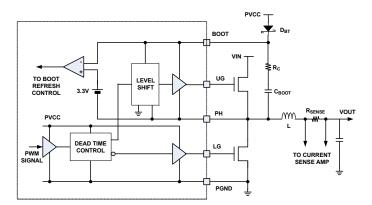

FIGURE 1. SIMPLIFIED TYPICAL APPLICATION SCHEMATIC

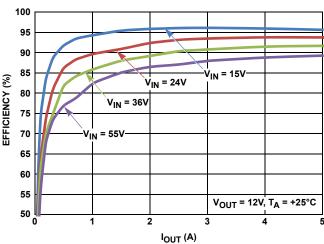

FIGURE 2. EFFICIENCY CURVES (ISL78268EVAL1Z/DE MODE)

## **Table of Contents**

| Related Literature                       |     |

|------------------------------------------|-----|

| Pin Configuration                        | . 3 |

| Functional Pin Description               | . 3 |

| Ordering Information                     | . 5 |

| Block Diagram                            | . 6 |

| Typical Application Schematics           | . 7 |

| Absolute Maximum Ratings                 | 10  |

| Thermal Information                      | 10  |

| Recommended Operating Conditions         | 10  |

| Electrical Specifications                | 10  |

| Typical Performance                      | 14  |

| Operation Description                    | 20  |

| Synchronous Buck                         |     |

| Adaptive Dead-Time Control.              |     |

| Operation Initialization and Soft-Start. |     |

| Enable                                   |     |

| Clock Generator and Synchronization      |     |

| Soft-Start                               |     |

| Bootstrap for High-side NMOS Drive       | 22  |

| PWM Operation                            | 23  |

| Current Sensing                          |     |

| Adjustable Slope Compensation            |     |

| Light Load Efficiency Enhancement        |     |

| Average Constant Current Control         |     |

| Fault Monitoring and Protection          |     |

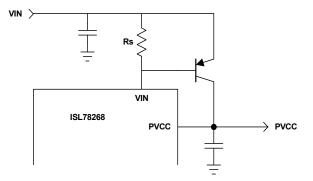

| Internal 5.2V LDO                        |     |

| Application Information                  |     |

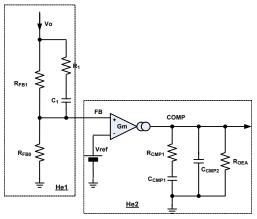

| Output Voltage Setting                   |     |

| Switching Frequency                      |     |

| Output Inductor Selection                |     |

| Output Capacitor                         | _   |

| Input Capacitor                          | _   |

| Power MOSFETBootstrap Capacitor          |     |

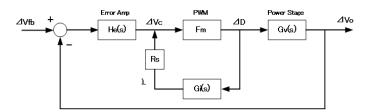

| Loop Compensation Design                 |     |

| VCC Input Filter                         |     |

| Current Sense Circuit                    |     |

| Layout Consideration                     | 31  |

| Revision History                         | 32  |

| About Intersil                           | 32  |

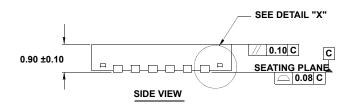

| Package Outline Drawing                  | 33  |

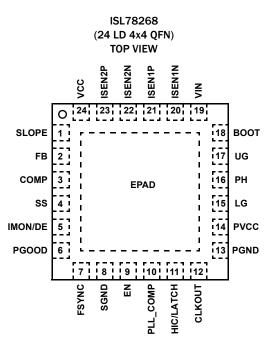

# **Pin Configuration**

# **Functional Pin Description**

| PIN NAME | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLOPE    | 1    | This pin programs the slope of the internal slope compensation. A resistor should be connected from the SLOPE pin to GND. Please refer to "Adjustable Slope Compensation" on page 24 for how to choose this resistor value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FB       | 2    | The inverting input of the transconductance amplifier. A resistor divider must be placed between the FB pin and the output rail to set the output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COMP     | 3    | The output of the transconductance amplifier. Place the compensation network between the COMP pin and GND for compensation loop design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

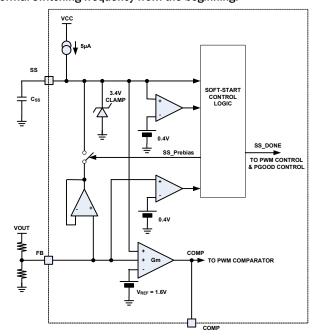

| SS       | 4    | Use this pin to set up the desired soft-start time. A capacitor placed from SS to GND will set up the soft-start ramp rate and in turn determine the soft-start time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IMON/DE  | 5    | <ol> <li>IMON/DE is a bifunctional pin as either the average current monitor/protection or switching mode selection (Diode Emulation (DE) mode or Forced PWM mode).</li> <li>If IMON/DE pin is connected to VCC (higher than VCC - 0.7V), the device operates in Forced PWM mode and the average current monitoring/limiting feature is disabled.</li> <li>If a resistor (and a filter capacitor in parallel) is connected between IMON/DE and GND, the device operates in DE mode and the average current monitoring/limiting feature is enabled. A current which is proportional to the current sensed at I<sub>SEN2</sub> is sourced from the IMON/DE pin. With an R/C network at the IMON/DE pin to GND, the voltage at IMON/DE pin describes average output current.</li> <li>When average current monitoring/limiting feature is enabled and DE mode is selected;</li> <li>If IMON/DE is higher than 2V, the device enters Average Current Protection mode with the hiccup/latch-off as the fault response.</li> <li>If IMON/DE reaches to 1.6V, the device enters the Average Constant Current control loop.</li> <li>If the IMON/DE pin voltage is lower than 1.6V (typ), the device operates as a normal buck regulator in DE mode.</li> </ol> |

| PG00D    | 6    | Provides an open-drain Power-Good signal. When the output voltage is within +15/-12% of the nominal output regulation point and soft-start is completed, the internal PGOOD open-drain transistor is open. It will be pulled low once output UV/OV or input OV conditions are detected. Requires pull-up resistor connecting to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

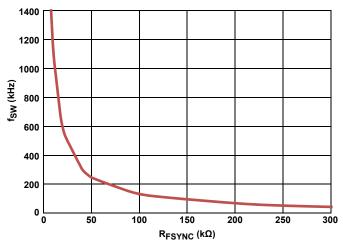

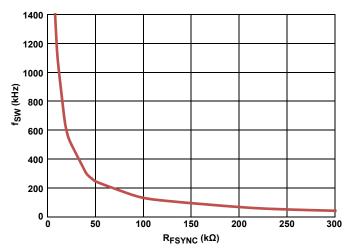

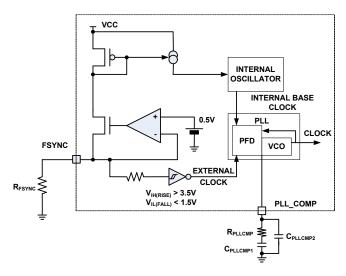

| FSYNC    | 7    | The oscillator switching frequency is adjusted with a resistor from this pin to GND. The internal oscillator locks to the rising edge of a square pulse waveform if this pin is driven by an external clock. There is a 325ns delay from the FSYNC pin's input clock rising edge to UG rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SGND     | 8    | Signal ground pin; the reference of internal analog circuits. Connect this pin to a large quiet copper ground plane. In PCB layout planning, avoid having switching current flowing into the SGND area (including the IC PAD that is connected to the quiet large copper ground plane also).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Functional Pin Description (Continued)

| PIN NAME  | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

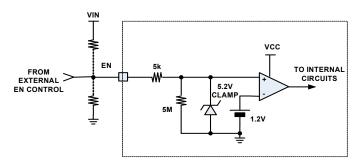

| EN        | 9    | This pin is a threshold-sensitive enable input for the controller. Connecting the power supply input to the EN pin through an appropriate resistor divider provides a means to have input voltage UVLO. When EN pin is driven above 1.2V, the ISL78268 is active depending on status of the internal POR, and pending fault states. Driving the EN pin below 1.1V will clear all fault states and the ISL78268 will soft-start when reenabled.                                                                     |

| PLL_COMP  | 10   | This pin serves as the compensation node for the PLL. A second order passive loop filter connected between the PLL_COMP pin and GND compensates the PLL feedback loop.                                                                                                                                                                                                                                                                                                                                             |

| HIC/LATCH | 11   | This pin is used to select either HICCUP or LATCHOFF response for faults including output overvoltage, V <sub>IN</sub> overvoltage, peak overcurrent protection (OC2) and average overcurrent protection.  HIC/LATCH = HIGH to activate HICCUP fault response,  HIC/LATCH = LOW to have LATCHOFF fault response.  Either toggling EN pin or recycling VCC POR can reset the IC from LATCHOFF status.                                                                                                               |

| CLKOUT    | 12   | This pin provides a clock signal to synchronize with another ISL78268. The rising edge signal on the CLKOUT pin is delayed 180° from the rising edge of UG to facilitate 2-phase interleaved operation using two ICs.                                                                                                                                                                                                                                                                                              |

| PGND      | 13   | This Power GND pin provides the return path for the low-side MOSFET drive. Note this pin carries the noisy driving current and the trace connected to the low-side MOSFET and PVCC decoupling capacitors should be as short as possible. Any sensitive analog signal trace should not share common traces with this driving return path. Connect this pin directly to the ground copper plane and put several vias as close as possible to this pin.                                                               |

| PVCC      | 14   | Output of the internal linear regulator that provides bias for both high-side and low-side drives. The PVCC operating range is 4.75V to 5.5V. A minimum 4.7µF ceramic capacitor should be used between PVCC and PGND for noise decoupling purpose. This capacitor provides a noisy driving current and its ground pad should have several vias connecting to the ground copper plane.                                                                                                                              |

| LG        | 15   | The low-side MOSFET gate drive output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PH        | 16   | Phase node. Connect this pin to the source of the high-side MOSFETs and the drain of the low-side MOSFETs. This pin represents the return path for the high-side gate drive.                                                                                                                                                                                                                                                                                                                                       |

| UG        | 17   | High-side MOSFET gate drive output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| воот      | 18   | This pin provides bias voltage to the high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive the external N-channel MOSFET. Place a 1µF ceramic capacitor between the BOOT and PH pins, and a switching diode from PVCC to BOOT.                                                                                                                                                                                                                                               |

| VIN       | 19   | Connect input rail to this pin. This pin is connected to the input of the internal linear regulator, generating the power necessary to operate the chip. It is recommended the DC voltage applied to the VIN pin does not exceed 55V when the IC is switching. VIN can stand up to 60V when IC is not switching.                                                                                                                                                                                                   |

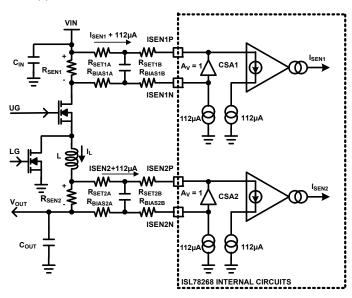

| ISEN1N    | 20   | The ISEN1N pin is a negative potential input pin of the first current sense amplifier (CSA1). This amplifier senses the signal on the current-sense resistor placed in series with the high-side MOSFET. The sensed current information is used for peak current mode control and overcurrent protection.                                                                                                                                                                                                          |

| ISEN1P    | 21   | The ISEN1P pin is a positive potential input pin of the first current sense amplifier (CSA1).                                                                                                                                                                                                                                                                                                                                                                                                                      |

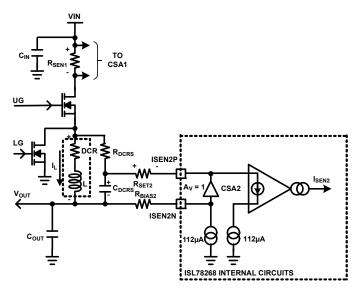

| ISEN2N    | 22   | The ISEN2N pin is a negative potential input pin of the second current sense amplifier (CSA2). This amplifier senses the continuous output inductor current either by DCR sensing method or using a sense resistor in series with the inductor for more accurate sensing. The sensed current signal is used for 3 functions:  - Accurately limiting the average output current for constant output current control  - Achieve diode emulation  - Achieve average OCP (comparator at IMON/DE pin with 2V reference) |

| ISEN2P    | 23   | The ISEN2P pin is a positive potential input pin of the second current-sense amplifier (CSA2).                                                                                                                                                                                                                                                                                                                                                                                                                     |

| vcc       | 24   | This pin provides bias power for the IC analog circuitry. An RC filter is recommended between this pin and the bias supply (range of 4.75V to 5.5V, typically from PVCC). A minimum 1µF ceramic capacitor should be used between VCC and GND for noise decoupling purposes.                                                                                                                                                                                                                                        |

| EPAD      |      | Bottom thermal pad. It is not connected to any electrical potential of the IC. In layout it must be connected to a PCB large ground copper plane that doesn't contain noisy power flows. Put multiple vias (as many as possible) in this pad connecting to the ground copper plane to help reduce the IC's $\theta_{JA}$ .                                                                                                                                                                                         |

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING  | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|--------------------------------|------------------|---------------------|-----------------------------|----------------|

| ISL78268ARZ                    | 782 68ARZ        | -40 to +125         | 24 Ld 4x4 QFN               | L24.4x4H       |

| ISL78268EVAL1Z                 | Evaluation Board |                     |                             |                |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL78268. For more information on MSL please see techbrief TB363.

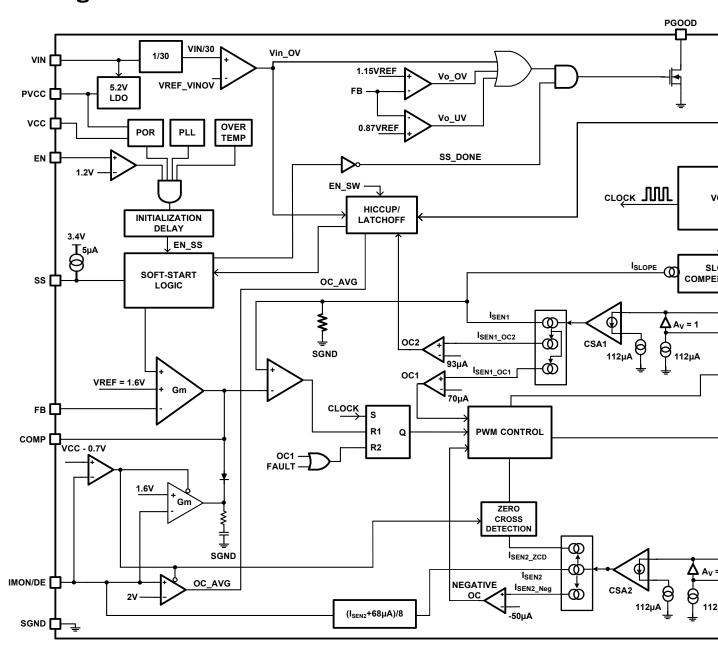

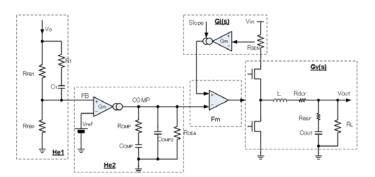

# **Block Diagram**

## **Typical Application Schematics**

FIGURE 3. SYNCHRONOUS BUCK WITH CONSTANT AVERAGE  $\mathbf{I}_{\text{OUT}}$

Page 7 of 34

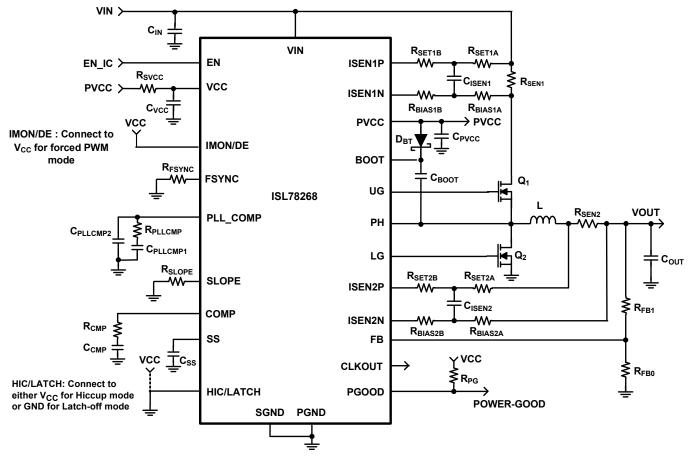

## Typical Application Schematics (Continued)

FIGURE 4. SYNCHRONOUS BUCK (FORCED PWM)

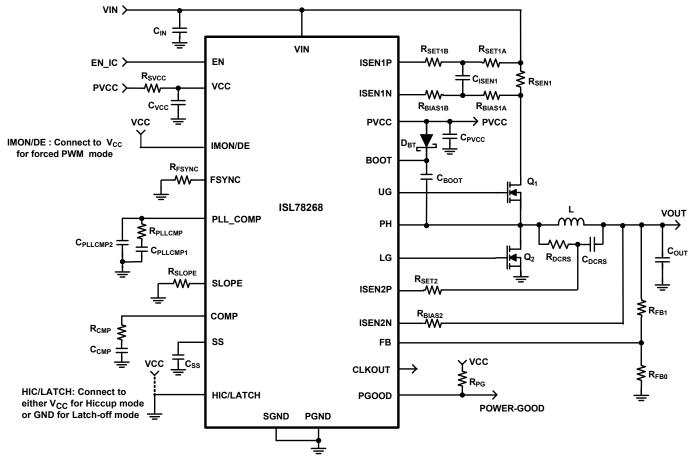

## Typical Application Schematics (Continued)

FIGURE 5. SYNCHRONOUS BUCK WITH DCR SENSING

## **Absolute Maximum Ratings**

| VIN                                             | 0.3V to +60V         |

|-------------------------------------------------|----------------------|

| PH                                              | 0.3V to +60V         |

| BOOT, UG                                        | 0.3V to +65V         |

| Upper Driver Supply Voltage, VBOOT - VPH        | 0.3V to +6.5V        |

| PVCC, VCC                                       |                      |

| VISENXP - VISENXP                               | ±0.6V                |

| ISEN1P, ISEN1N, ISEN2P, ISEN2N                  |                      |

| All Other Pins                                  | - 0.3V to VCC + 0.3V |

| ESD Rating                                      |                      |

| Human Body Model (Tested per AEC-Q100-002)      | 2kV                  |

| Machine Model (Tested per AEC-Q100-003)         | 200V                 |

| Charged Device Model (Tested per AEC-Q100-011). | 750V                 |

| Latchup Rating (Tested per AEC-Q100-004)        | 100mA                |

|                                                 |                      |

#### **Thermal Information**

| Thermal Resistance                          | $\theta_{JA}$ (°C/W) | $\theta_{\text{JC}}$ (°C/W) |

|---------------------------------------------|----------------------|-----------------------------|

| 24 Ld 4x4 QFN Package (Notes 4, 5)          | 39                   | 3.5                         |

| Maximum Junction Temperature (Plastic Packa | age)                 | +150°C                      |

| Maximum Storage Temperature Range           | 6                    | 55°C to +150°C              |

| Pb-Free Reflow Profile                      |                      | see <u>TB493</u>            |

### **Recommended Operating Conditions**

| VIN 5V to 55V                                                         |

|-----------------------------------------------------------------------|

| PH                                                                    |

| PVCC, VCC                                                             |

| Upper Driver Supply Voltage, V <sub>BOOT</sub> - V <sub>PH</sub>      |

| ISEN1P, ISEN1N, ISEN2P, ISEN2N Common Mode Voltage 4V to 55V          |

| ISEN1P to ISEN1N and ISEN2P to ISEN2N Differential Voltage $\pm$ 0.3V |

| Operational Ambient Temperature Range (Automotive)40 °C to +125 °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>18379</u>.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 6. Unless otherwise noted, all voltages specified in this specification are refer to GND.

**Electrical Specifications** Refer to the Block Diagram (page 6) and Typical Application Schematics (page 7). Operating conditions unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{PVCC} = 5.2V$  and  $V_{VCC} = 5.2V$ , EN = 5.0V,  $T_A = -40$ °C to +125°C. Typicals are at  $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40°C to +125°C.

| PARAMETER                                                                         | SYMBOL                     | TEST CONDITIONS                                                                     | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNITS |

|-----------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| SUPPLY INPUT                                                                      | 1                          |                                                                                     | "               |      | <u>'</u>        |       |

| Input Voltage Range                                                               | VIN                        | For V <sub>IN</sub> = 5V, the internal LDO dropout (V <sub>IN</sub> - PVCC) <0.25V  | 5               |      | 55              | V     |

| Input Supply Current (ENABLED Mode) to VIN Pin                                    | I <sub>Q_SW</sub>          | $R_{FSYNC}$ = 40.2k $\Omega$ (f <sub>SW</sub> = 300kHz), LG = OPEN, UG = OPEN       |                 | 5    | 7               | mA    |

|                                                                                   | IQ_NON-SW                  | FSYNC = 5V, LG = OPEN, UG = OPEN                                                    |                 | 2.7  | 3.5             | mA    |

| Input Supply Current (Shutdown Mode) to VIN                                       | I <sub>Q_SD_VIN</sub>      | EN = GND, V <sub>IN</sub> = 12V                                                     |                 | 0.15 | 0.5             | μΑ    |

| Pin                                                                               |                            | EN = GND, V <sub>IN</sub> = 55V                                                     |                 | 0.2  | 1               | μΑ    |

| Input Leakage Current (Shutdown Mode) to each of ISEN1P/ISEN1N/ISEN2P/ISEN2N Pins | I <sub>Q_SD_ISENxP/N</sub> | EN = GND, ISEN1P<br>(or ISEN1N/ISEN2P/ISEN2N) = 55V, V <sub>IN</sub> = 55V          | -1              | 0    | 1               | μА    |

| INPUT OVERVOLTAGE PROTECTION                                                      | 1                          | ,                                                                                   | - 1             |      | 1               |       |

| V <sub>IN</sub> Switching-Disabled Threshold                                      |                            | EN = 5V, V <sub>IN</sub> rising                                                     | 56              | 57.5 | 59.5            | ٧     |

| V <sub>IN</sub> Overvoltage Recovery Threshold                                    |                            |                                                                                     | 52.5            | 54.5 | 57              | ٧     |

| V <sub>IN</sub> Switching-Disabled Threshold Hysteresis                           |                            |                                                                                     |                 | 3    |                 | ٧     |

| V <sub>IN</sub> Overvoltage Hiccup Retry Delay                                    |                            | From the time fault is removed to initiation of soft-start                          |                 | 500  |                 | ms    |

| INTERNAL LINEAR REGULATOR                                                         | II.                        |                                                                                     |                 |      |                 |       |

| LDO Output Voltage (PVCC Pin)                                                     | V <sub>PVCC</sub>          | $V_{IN}$ = 6V to 55V, $C_{PVCC}$ = 4.7 $\mu$ F from PVCC to PGND, $I_{PVCC}$ = 10mA | 5               | 5.2  | 5.4             | V     |

| LDO Dropout Voltage (PVCC pin)                                                    | V <sub>DROPOUT</sub>       | $V_{IN}$ = 4.9V, $C_{PVCC}$ = 4.7 $\mu$ F from PVCC to PGND, $I_{VCC}$ = 80mA       |                 | 0.3  |                 | V     |

| LDO Current Foldback Limit (PVCC Pin)                                             | I <sub>OC_LDO</sub>        | $V_{IN}$ = 6V, $C_{PVCC}$ = 4.7 $\mu$ F from PVCC to PGND $V_{PVCC}$ = 2.5 V        | 150             | 230  | 280             | mA    |

| LDO Output Short Current (PVCC pin)                                               | I <sub>OCFB_LDO</sub>      | $V_{IN}$ = 6V, $C_{PVCC}$ = 4.7 $\mu$ F from PVCC to PGND $V_{PVCC}$ = 0V           | 100             | 150  | 220             | mA    |

**Electrical Specifications** Refer to the Block Diagram (page 6) and Typical Application Schematics (page 7). Operating conditions unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{PVCC} = 5.2V$  and  $V_{VCC} = 5.2V$ , EN = 5.0V,  $T_A = -40\,^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . Typicals are at  $T_A = +25\,^{\circ}\text{C}$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . (Continued)

| PARAMETER                                                   | SYMBOL                 | TEST CONDITIONS                                                                                                                     | MIN<br>( <u>Note 7</u> ) | TYP     | MAX<br>(Note 7) | UNITS |

|-------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|-----------------|-------|

| POWER-ON RESET (for both PVCC and VCC)                      |                        |                                                                                                                                     |                          |         | 1.              | ,L    |

| Rising V <sub>PVCC/VCC</sub> POR Threshold                  | V <sub>PORH_RISE</sub> |                                                                                                                                     | 4.35                     | 4.55    | 4.75            | V     |

| Falling V <sub>PVCC/VCC</sub> POR Threshold                 | V <sub>PORL_FALL</sub> |                                                                                                                                     | 4.1                      | 4.15    | 4.3             | V     |

| V <sub>PVCC/VCC</sub> POR Hysteresis                        | V <sub>PORL_HYS</sub>  |                                                                                                                                     |                          | 0.4     |                 | V     |

| Phase Lock Loop Locking Time                                | t <sub>PLL_DLY</sub>   | From POR to Initiation of soft-start.  RPLLCMP = 3.24k, CPLLCMP1 = 6.8nF,  CPLLCMP2 = 1nF, RFSYNC = 40.2k, f <sub>SW</sub> = 300kHz |                          | 0.8     |                 | ms    |

| EN                                                          |                        |                                                                                                                                     |                          |         |                 | 1     |

| Enable Threshold                                            | V <sub>ENH</sub>       | Rising                                                                                                                              | 1.1                      | 1.2     | 1.3             | V     |

|                                                             | V <sub>ENL</sub>       | Falling                                                                                                                             | 1.04                     | 1.14    | 1.24            | V     |

|                                                             | V <sub>EN_HYS</sub>    | Hysteresis                                                                                                                          |                          | 60      |                 | m۷    |

| Input Resistance                                            |                        | EN = 4V                                                                                                                             | 3000                     | 5000    | 8000            | kΩ    |

|                                                             |                        | EN = 6V                                                                                                                             |                          | 5       |                 | kΩ    |

| OSCILLATOR                                                  |                        | 1                                                                                                                                   | I .                      | 1       | 1               | 1     |

| PWM Switching Frequency                                     | Fosc                   | $R_{FSYNC} = 249k\Omega (0.1\%)$                                                                                                    | 47.5                     | 50      | 52.5            | kHz   |

| 3 34,4 3,                                                   | 030                    | $R_{\text{FSYNC}} = 40.2 \text{k}\Omega (0.1\%)$                                                                                    | 285                      | 300     | 315             | kHz   |

|                                                             |                        | $R_{\text{FSYNC}} = 10 \text{k}\Omega  (0.1\%)$                                                                                     | 1036                     | 1100    | 1155            | kHz   |

| Switching Frequency Range                                   |                        | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 12V                                                                                       | 50                       |         | 1100            | kHz   |

| Synchronization Range at FSYNC                              |                        | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 12V                                                                                       | 50                       |         | 1100            | kHz   |

| CLKOUT                                                      |                        | 14 125 6, TIN 121                                                                                                                   |                          |         |                 | 12    |

| High Level CLKOUT Output Voltage                            | CLKOUTH                | I <sub>CLKOUT</sub> = 500μA                                                                                                         | VCC-0.4                  | VCC-0 1 |                 | ٧     |

| Low Level CLKOUT Output Voltage                             | CLKOUTL                | I <sub>CLKOUT</sub> = -500µA                                                                                                        | 100-0.4                  | 0.1     | 0.4             | V     |

| Output Pulse Width                                          | CEROUTE                |                                                                                                                                     |                          | 270     | 0.4             |       |

| •                                                           |                        | C <sub>CLKOUT</sub> = 100pF                                                                                                         |                          | 180     |                 | ns    |

| Phase Shift from UG Rising Edge to CLKOUT Pulse Rising Edge |                        | UG = OPEN, C <sub>CLKOUT</sub> = OPEN                                                                                               |                          | 180     |                 |       |

| SYNCHRONIZATION (FSYNC pin)                                 |                        | 1                                                                                                                                   | 1                        |         | П               |       |

| Input High Threshold                                        | VIH                    |                                                                                                                                     | 3.5                      |         |                 | V     |

| Input Low Threshold                                         | VIL                    |                                                                                                                                     |                          |         | 1.5             | V     |

| Input Pulse Width - Rise_To_Fall                            |                        |                                                                                                                                     | 20                       |         | 20,000          | ns    |

| Input Pulse Width - Fall_To_Rise                            |                        |                                                                                                                                     | 20                       |         | 20,000          | ns    |

| Delay from Input Pulse Rising to UG Rising Edge             |                        | UG = OPEN                                                                                                                           |                          | 325     |                 | ns    |

| SOFT-START                                                  |                        |                                                                                                                                     | 1                        |         |                 |       |

| Soft-Start Current                                          | I <sub>SS</sub>        | V <sub>SS</sub> = 0V                                                                                                                | 4.5                      | 5       | 5.5             | μΑ    |

| Soft-Start Pin PreBias Voltage Range                        | V <sub>SS_PRE</sub>    | In prebias output condition; V <sub>SS PRE</sub> = V <sub>FB</sub>                                                                  | 0                        |         | 1.6             | V     |

| Soft-Start PreBias Voltage Accuracy                         | <u> </u>               | V <sub>FB</sub> = 500mV                                                                                                             | -25                      |         | 25              | mV    |

| Soft-Start Clamp Voltage                                    | V <sub>SSCLAMP</sub>   |                                                                                                                                     | 3                        | 3.4     | 3.8             | V     |

| REFERENCE VOLTAGE                                           | JOOLAINI               |                                                                                                                                     |                          |         |                 |       |

| Reference Accuracy                                          |                        | Measured at FB pin                                                                                                                  | 1.584                    | 1.6     | 1.616           | V     |

| FB Pin Input Bias Current                                   |                        | V <sub>FB</sub> = 1.6V                                                                                                              | -0.05                    |         | 0.05            | μA    |

| ERROR AMPLIFIER                                             |                        | 110                                                                                                                                 |                          |         | 3               |       |

| Transconductance Gain                                       |                        |                                                                                                                                     |                          | 2       |                 | ms    |

| COMP Output Impedance                                       |                        |                                                                                                                                     |                          | 10      |                 | MΩ    |

| Oom Output impouding                                        |                        |                                                                                                                                     |                          |         |                 | 17122 |

**Electrical Specifications** Refer to the Block Diagram (page 6) and Typical Application Schematics (page 7). Operating conditions unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{PVCC} = 5.2V$  and  $V_{VCC} = 5.2V$ , EN = 5.0V,  $T_A = -40\,^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . Typicals are at  $T_A = +25\,^{\circ}\text{C}$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . (Continued)

| PARAMETER                                              | SYMBOL                 | TEST CONDITIONS                                                                                                                                                                      | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNITS  |

|--------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|--------|

| Slew Rate                                              |                        | C <sub>CMP</sub> = 100pF from COMP pin to GND                                                                                                                                        |                 | ±2.5 |                 | V/µs   |

| COMP Output Current Capability                         |                        |                                                                                                                                                                                      |                 | ±300 |                 | μΑ     |

| COMP Output Voltage High                               |                        |                                                                                                                                                                                      | 3.5             | 3.7  | 3.9             | ٧      |

| COMP Output Voltage Low                                |                        |                                                                                                                                                                                      |                 |      | 0.3             | ٧      |

| SLOPE COMPENSATION SETTING                             |                        |                                                                                                                                                                                      |                 |      |                 |        |

| SLOPE Pin Voltage                                      |                        |                                                                                                                                                                                      |                 | 500  |                 | m۷     |

| SLOPE Accuracy                                         |                        | R <sub>SLOPE</sub> = 20k (0.1%)                                                                                                                                                      | -30             |      | 30              | %      |

|                                                        |                        | R <sub>SLOPE</sub> = 40.2k (0.1%)                                                                                                                                                    | -30             |      | 30              | %      |

| CURRENT SENSE AMPLIFIER                                |                        |                                                                                                                                                                                      |                 | 1    | 1               |        |

| ISENxN, ISENxP Common Mode Voltage Range               | 9                      |                                                                                                                                                                                      | 4               |      | 55              | ٧      |

| ISENxN, ISENxP Bias Current                            | ISENXBIAS              | Sinking into pin, EN = 5V,<br>V <sub>ISENXN</sub> = V <sub>ISENXP</sub> = 4V to 55V                                                                                                  | 90              | 112  | 130             | μΑ     |

| ZERO CROSSING DETECTION                                |                        |                                                                                                                                                                                      |                 |      |                 |        |

| Zero Crossing Detection (ZCD) Threshold                | V <sub>ZCD_TH</sub>    | $R_{SEN}$ Differential Voltage<br>$R_{SET2A} + R_{SET2B} = 665\Omega (0.1\%)$<br>$R_{BIAS2A} + R_{BIAS2B} = 665\Omega (0.1\%)$<br>See page 7 for $R_{SET}$ resistors                 |                 | 1.3  |                 | mV     |

| OVERCURRENT PROTECTION                                 |                        |                                                                                                                                                                                      |                 | •    |                 |        |

| Peak Current Cycle-by-Cycle Limit Voltage<br>Threshold | V <sub>OC1</sub>       | $R_{SEN}$ Differential Voltage<br>$R_{SET1A} + R_{SET1B} = 665\Omega (0.1\%)$<br>$R_{BIAS2A} + R_{BIAS2B} = 665\Omega (0.1\%)$<br>See page 7 for $R_{SET}$ resistors                 | 32              | 47   | 60              | mV     |

| Peak Current Cycle-by-Cycle Limit Delay                |                        | UG = OPEN, from V <sub>OC1</sub> threshold to UG falling                                                                                                                             |                 | 50   |                 | ns     |

| Peak Current Hiccup/Latch-off Voltage<br>Threshold     | V <sub>OC2</sub>       | $R_{SEN}$ Differential Voltage<br>$R_{SET1A} + R_{SET1B} = 665Ω$ (0.1%)<br>$R_{BIAS2A} + R_{BIAS2B} = 665Ω$ (0.1%)<br>See page 7 for $R_{SET}$ resistors                             | 45              | 62   | 75              | mV     |

| OC2 Hiccup/Latch-off Blanking Time                     |                        | Consecutive OC2 switching cycles                                                                                                                                                     |                 | 3    |                 | cycles |

| OC2 Hiccup Retry Delay                                 |                        |                                                                                                                                                                                      |                 | 500  |                 | ms     |

| AVERAGE OVERCURRENT PROTECTION AND                     | CONSTANT CU            | RRENT LIMITING LOOP                                                                                                                                                                  |                 |      | •               |        |

| IMON Offset Current                                    |                        | $\begin{split} &V_{RSEN-CSA2} = 0 mV,  V_{ISEN2N} = 4V \text{ to } 55V, \\ &R_{SET2A} + R_{SET2B} = 665\Omega  (0.1\%) \\ &R_{BIAS2A} + R_{BIAS2B} = 665\Omega  (0.1\%) \end{split}$ | 7.0             | 8.5  | 10.0            | μΑ     |

| IMON Current Accuracy                                  | IMON <sub>CSA2</sub>   | $V_{RSEN-CSA2}$ = 25mV, $V_{ISEN2N}$ = 4V to 55V, $R_{SET2A} + R_{SET2B}$ = 665 $\Omega$ (0.1%) $R_{BIAS2A} + R_{BIAS2B}$ = 665 $\Omega$ (0.1%)                                      | 12              | 13.2 | 15              | μA     |

|                                                        | IMON <sub>CSA2</sub>   | $V_{RSEN-CSA2} = 76 \text{mV}, V_{ISEN2N} = 4 \text{V to } 55 \text{V},$ $R_{SET2A} + R_{SET2B} = 665 \Omega (0.1\%)$ $R_{BIAS2A} + R_{BIAS2B} = 665 \Omega (0.1\%)$                 | 21              | 22.8 | 26              | μΑ     |

| Fault Threshold at IMON/DE Pin                         |                        | Selected LATCHOFF/HICCUP response                                                                                                                                                    | 1.9             | 2.0  | 2.1             | V      |

| OC_AVG Hiccup Retry Delay                              |                        |                                                                                                                                                                                      |                 | 500  |                 | ms     |

| Constant Current Limit Reference Accuracy              | VREFCC                 |                                                                                                                                                                                      | 1.584           | 1.6  | 1.616           | ٧      |

| PWM CONTROLLER                                         |                        |                                                                                                                                                                                      |                 |      |                 | -      |

| Minimum UGATE ON Time                                  | t <sub>MINON_UG</sub>  | UGATE pulse width, UG = OPEN, LG = OPEN                                                                                                                                              | 240             | 300  | 360             | ns     |

| Minimum UGATE OFF Time                                 | t <sub>MINOFF_UG</sub> | V <sub>COMP</sub> = 3.5V, UG = OPEN, LG = OPEN                                                                                                                                       |                 | 285  |                 | ns     |

| Minimum LGATE ON Time                                  | t <sub>MINON_LG</sub>  | V <sub>COMP</sub> = 3.5V, UG = OPEN, LG = OPEN                                                                                                                                       | 140             | 175  | 210             | ns     |

**Electrical Specifications** Refer to the Block Diagram (page 6) and Typical Application Schematics (page 7). Operating conditions unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{PVCC} = 5.2V$  and  $V_{VCC} = 5.2V$ , EN = 5.0V,  $T_A = -40\,^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . Typicals are at  $T_A = +25\,^{\circ}\text{C}$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}\text{C}$  to +125 $^{\circ}\text{C}$ . (Continued)

| PARAMETER                                            | SYMBOL                | TEST CONDITIONS                                                                                        | MIN<br>(Note 7) | ТҮР      | MAX<br>(Note 7) | UNITS |

|------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------|-----------------|----------|-----------------|-------|

| GATE DRIVERS                                         |                       |                                                                                                        |                 |          |                 |       |

| UG Source Resistance                                 | R <sub>UGSRC</sub>    | 50mA source current; V <sub>BOOT</sub> - V <sub>PH</sub> = 4.5V                                        |                 | 1.2      |                 | Ω     |

| UG Source Current                                    | IUGSRC                | UG - PH = 2.5V; V <sub>BOOT</sub> - V <sub>PH</sub> = 4.5V                                             |                 | 2.0      |                 | Α     |

| UG Sink Resistance                                   | R <sub>UGPD</sub>     | 100mA sink current; V <sub>BOOT</sub> - V <sub>PH</sub> = 4.5V                                         |                 | 0.65     |                 | Ω     |

| UG Sink Current                                      | I <sub>UGPD</sub>     | UG - PH = 2.5V; V <sub>BOOT</sub> - V <sub>PH</sub> = 4.5V                                             |                 | 3.0      |                 | Α     |

| LG Source Resistance                                 | R <sub>LGSRC</sub>    | 50mA source current                                                                                    |                 | 1.0      |                 | Ω     |

| LG Source Current                                    | I <sub>LGSRC</sub>    | LG - PGND = 2.5V                                                                                       |                 | 2.0      |                 | Α     |

| LG Sink Resistance                                   | R <sub>LGPD</sub>     | 100mA sink current                                                                                     |                 | 0.55     |                 | Ω     |

| LG Sink Current                                      | I <sub>LGPD</sub>     | LG - PGND = 2.5V                                                                                       |                 | 3.0      |                 | Α     |

| UG to PH Pull-Down Resistance                        |                       |                                                                                                        |                 | 50       |                 | kΩ    |

| LG to PGND Pull-Down Resistance                      |                       |                                                                                                        |                 | 50       |                 | kΩ    |

| BOOT-PH Refreshing Detection Threshold               |                       |                                                                                                        | 3.1             | 3.3      | 3.5             | V     |

| BOOT-PH Refreshing Detection Threshold<br>Hysteresis |                       |                                                                                                        | 100             | 150      | 250             | mV    |

| Dead-Time Delay - UG Falling to LG Rising            | t <sub>DT1</sub>      | UG = OPEN, LG = OPEN                                                                                   | 45              | 55       | 65              | ns    |

| Dead-Time Delay - LG Falling to UG Rising            | t <sub>DT2</sub>      | UG = OPEN, LG = OPEN                                                                                   | 45              | 55       | 65              | ns    |

| OUTPUT OVERVOLTAGE DETECTION/PROTECTION              | CTION (NOTE: FB       | _OVP response is selectable to be LATCHOFF or I                                                        | HICCUP)         |          | I.              | 1     |

| FB Overvoltage Rising Trip Threshold                 | V <sub>FBOV_REF</sub> | Percentage of Reference Point, VFB = 1.6V<br>Selected LATCHOFF/HICCUP response.                        | 111             | 115      | 118             | %     |

| FB Overvoltage Recovery Threshold                    |                       |                                                                                                        | 108             | 112      | 115             | %     |

| Overvoltage Threshold Hysteresis                     |                       |                                                                                                        |                 | 3        |                 | %     |

| FB Overvoltage Protection Delay                      |                       | Overvoltage detection filter                                                                           |                 | 1        |                 | μs    |

| FB_OV Hiccup Retry Delay                             |                       |                                                                                                        |                 | 500      |                 | ms    |

| OUTPUT UNDERVOLTAGE DETECTION                        |                       |                                                                                                        |                 |          |                 | 1     |

| FB Undervoltage Falling Threshold                    | V <sub>FBUV_REF</sub> | Percentage of reference point, VFB = 1.6V                                                              | 85              | 87.5     | 90              | %     |

| FB Undervoltage Recovery Threshold                   | _                     |                                                                                                        | 88              | 90.5     | 93              | %     |

| Undervoltage Hysteresis                              |                       |                                                                                                        |                 | 3        |                 | %     |

| POWER-GOOD MONITOR (OUTPUT OVERVOI                   | TAGE, OUTPUT          | UNDERVOLTAGE, VIN OVERVOLTAGE)                                                                         |                 |          |                 | 1     |

| PGOOD Leakage Current                                |                       | PGOOD HIGH, V <sub>PGOOD</sub> = 5V                                                                    |                 |          | 1               | μΑ    |

| PGOOD Low Voltage                                    |                       | PGOOD LOW, I <sub>PGOOD</sub> = 0.5mA                                                                  |                 | 0.20     | 0.4             | ٧     |

| PGOOD Rising Delay -1                                |                       | From V <sub>SS</sub> = 0.95*VREF to V <sub>SS</sub> = V <sub>SSCLAMP</sub> ,<br>C <sub>SS</sub> = 15nF |                 | 5.6      |                 | ms    |

| PGOOD Rising Delay -2                                |                       | From V <sub>SS</sub> = V <sub>SSCLAMP</sub> to PGOOD HIGH                                              |                 | 0.5      |                 | ms    |

| PGOOD Falling Delay                                  |                       | Blanking filter time before transition                                                                 |                 | 10       |                 | us    |

| HIC/LATCH Pin                                        |                       | -                                                                                                      | I               |          | I               |       |

| HIC/LATCH Input Pull-Down Current                    |                       | V <sub>HIC/LATCH</sub> = 5V                                                                            | 0.8             | 1        | 2               | μΑ    |

| HIC/LATCH Input High Threshold                       |                       | , i                                                                                                    | 2               |          |                 | ٧     |

| HIC/LATCH Input Low Threshold                        |                       |                                                                                                        |                 |          | 0.8             | ٧     |

| OVER-TEMPERATURE PROTECTION                          |                       |                                                                                                        |                 | <u> </u> | <u> </u>        |       |

| Over-Temperature Threshold                           |                       |                                                                                                        |                 | 160      |                 | °C    |

| Over-Temperature Recovery Threshold                  |                       |                                                                                                        |                 | 145      |                 | °C    |

#### NOTE:

<sup>7.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

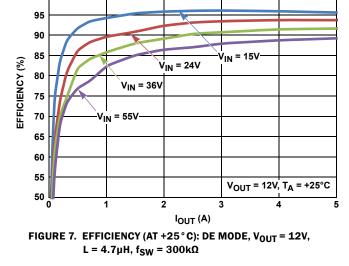

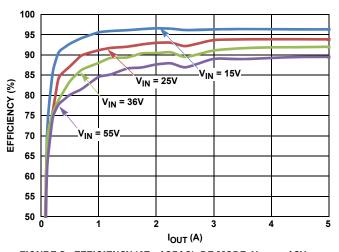

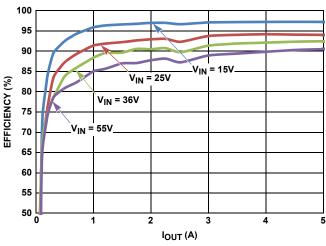

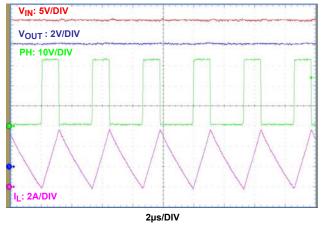

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted.

FIGURE 6. FREQUENCY SETTING (AT +25°C), VIN = 36V

FIGURE 8. EFFICIENCY (AT +125  $^{\circ}$  C): DE MODE,  $V_{OUT}$  = 12V, L = 4.7  $\mu$ H,  $f_{SW}$  = 300k $\Omega$

FIGURE 9. EFFICIENCY (AT -40  $^{\circ}$  C), DE MODE, V<sub>OUT</sub> = 12V, L = 4.7  $\mu$ H, f<sub>SW</sub> = 300 k $\Omega$

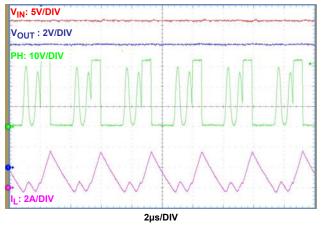

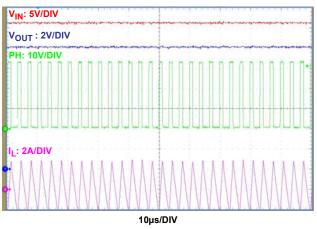

FIGURE 10. DE MODE:  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 2.5A, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz (CONTINUOUS CONDUCTION OPERATION)

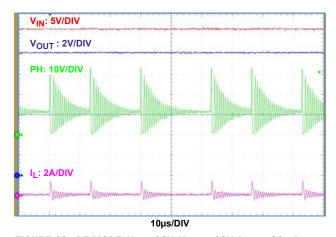

FIGURE 11. DE MODE:  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 1.0A, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz (DISCONTINUOUS CONDUCTION OPERATION)

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted. (Continued)

FIGURE 12. DE MODE:  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 30mA, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz (PULSE SKIP OPERATION)

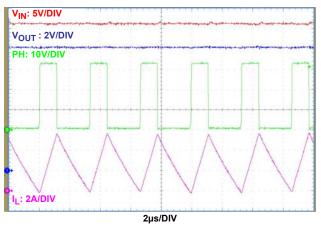

FIGURE 13. FORCED PWM MODE, V $_{IN}$ =36V, V $_{OUT}$  = 12V, I $_{OUT}$  = 2.5A, L = 4.7 $\mu$ H, C $_{OUT}$  = 98 $\mu$ F, f $_{SW}$  = 300kHz

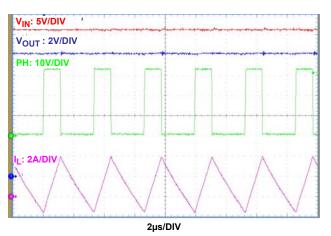

FIGURE 14. FORCED PWM MODE,  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 1.0A, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz

FIGURE 15. FORCED PWM MODE,  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 30mA, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz

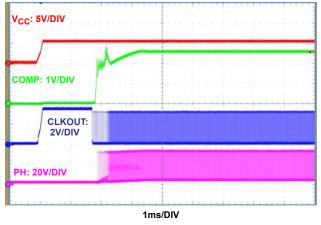

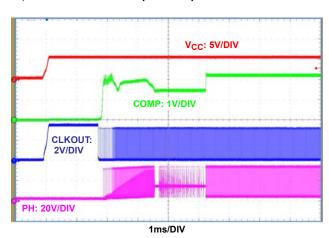

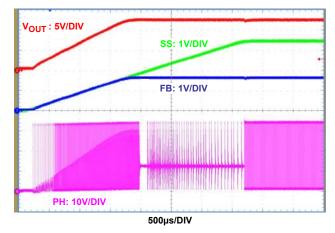

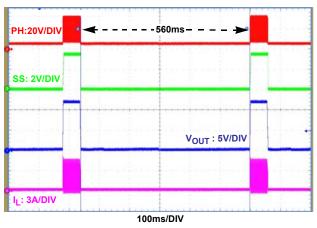

FIGURE 16. INITIALIZATION TO START-UP: DE MODE,  $V_{IN}=36V$ ,  $V_{OUT}=12V$ ,  $I_{OUT}=2.5A$ ,  $L=4.7\mu H$ ,  $C_{OUT}=98\mu F$ ,  $f_{SW}=300kHz$

FIGURE 17. INITIALIZATION TO START-UP: DE MODE,  $V_{IN}=36V$ ,  $V_{OUT}=12V$ ,  $I_{OUT}=0A$ ,  $L=4.7\mu H$ ,  $C_{OUT}=98\mu F$ ,  $f_{SW}=300 kHz$

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted. (Continued)

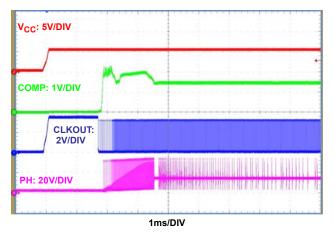

FIGURE 18. INITIALIZATION TO START-UP: FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=2.5A,\,L=4.7\mu H,\\ C_{OUT}=98\mu F,\,f_{SW}=300kHz$

FIGURE 19. INITIALIZATION TO START-UP: FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=0A,\,L=4.7\mu H,\\ C_{OUT}=98\mu F,\,f_{SW}=300kHz$

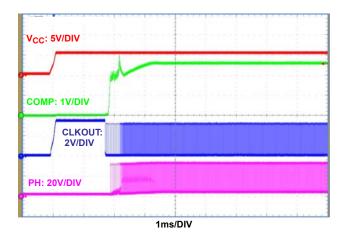

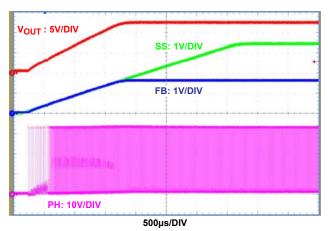

FIGURE 20. SOFT-START (NON-PREBIASED): DE MODE,  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 2.5A, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz

FIGURE 21. SOFT-START (NON-PREBIASED): DE MODE,  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 0A, L = 4.7 $\mu$ H,  $C_{OUT}$  = 98 $\mu$ F,  $f_{SW}$  = 300kHz

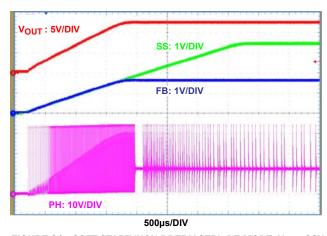

FIGURE 22. SOFT-START (NON-PREBIASED): FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=2.5A,\,L=4.7\mu H,\\ C_{OUT}=98\mu F,\,f_{SW}=300kHz$

FIGURE 23. SOFT-START (NON-PREBIASED): FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=0A,\,L=4.7\mu\text{H},\\ C_{OUT}=98\mu\text{F},\,f_{SW}=300\text{kHz}$

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted. (Continued)

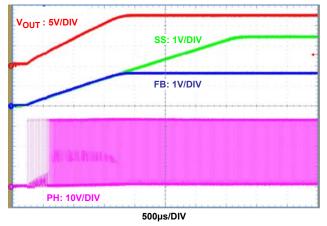

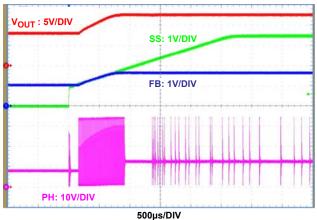

FIGURE 24. SOFT-START (PREBIASED): DE MODE, VIN = 36V,  $V_{OUT} = 12V$ ,  $I_{OUT} = 0A$ ,  $L = 4.7\mu H$ ,  $C_{OUT} = 98\mu F$ , f<sub>SW</sub> = 300kHz

V<sub>OUT</sub> : 5V/DIV

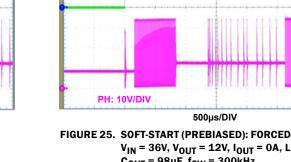

FIGURE 25. SOFT-START (PREBIASED): FORCED-PWM MODE,  $V_{IN} = 36V$ ,  $V_{OUT} = 12V$ ,  $I_{OUT} = 0A$ ,  $L = 4.7\mu H$ ,  $C_{OUT} = 98\mu F$ ,  $f_{SW} = 300kHz$

SS: 1V/DIV

FB: 1V/DIV

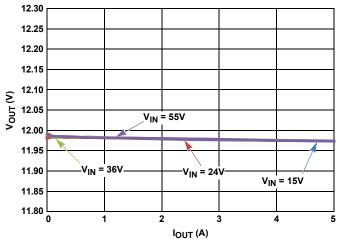

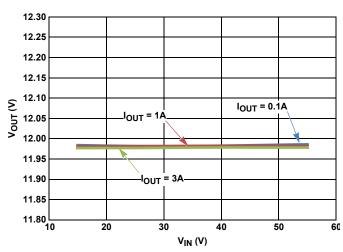

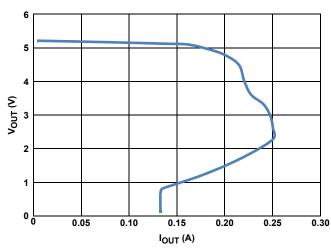

**FIGURE 26. LOAD REGULATION**

FIGURE 27. LINE REGULATION

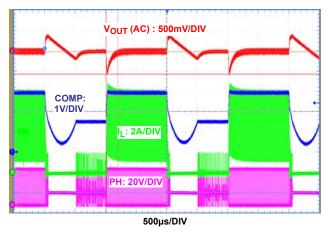

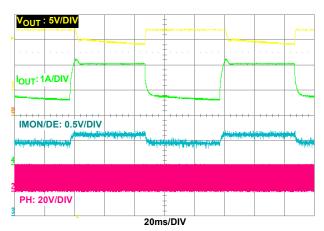

FIGURE 28. TRANSIENT RESPONSE: DE MODE,  $V_{\text{IN}}$  = 36V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 0.1A TO 4.5A, L = 4.7 $\mu$ H,  $C_{OUT} = 98\mu F$

FIGURE 29. TRANSIENT RESPONSE: DE MODE,  $V_{\text{IN}}$  = 36V,  $V_{OUT} = 12V$ ,  $I_{OUT} = 1A$  TO 3A,  $L = 4.7\mu H$ ,  $C_{OUT} = 98\mu F$

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted. (Continued)

FIGURE 30. TRANSIENT RESPONSE: FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=0.1A\ TO\ 4.5A,\,L=4.7\mu H,\\ C_{OUT}=98\mu F$

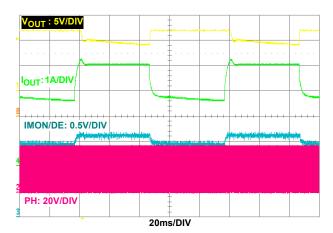

FIGURE 32. HICCUP: ACL,  $V_{IN}$  = 30V,  $V_{OUT}$  = 12V,  $R_{IMON}$  = 156k $\Omega$

FIGURE 34. AVERAGE CONSTANT OUTPUT CURRENT CONTROL,  $V_{IN}=20V,\,V_{OUT}\,(\text{SETTING})=12V,\,C_{IMON}=1nF,\\ R_{IMON}=130k\Omega,\,\text{ACL}=4.05A,\,R_L=5.0\Omega\,\,\text{TO}\,\,2.0\Omega,\\ F_{LOAD}=10\text{Hz},\,\text{DUTY}\,\,\text{OF}\,\,\text{LOAD}\,\,\text{CHANGE}=50\%$

FIGURE 31. TRANSIENT RESPONSE: FORCED-PWM MODE,  $V_{IN}=36V,\,V_{OUT}=12V,\,I_{OUT}=1A\ TO\ 3A,\,L=4.7\mu H,\\ C_{OUT}=98\mu F$

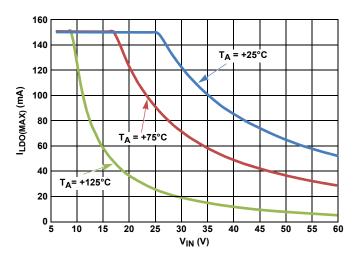

FIGURE 33. INTERNAL LDO LOAD REGULATION:  $V_{IN}$  = 36V,  $T_A$  = +25 °C

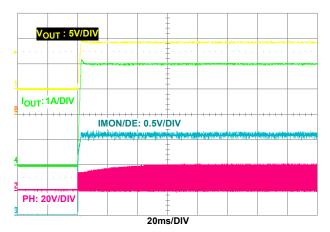

FIGURE 35. AVERAGE CONSTANT OUTPUT CURRENT CONTROL,  $V_{IN}=36V,\,V_{OUT}\,(\text{SETTING})=12V,\,C_{IMON}=1nF,\\ R_{IMON}=130k\Omega,\,\text{ACL}=4.05\text{A},\,R_L=5.0\Omega\,\text{TO}\,\,2.0\Omega,\\ F_{LOAD}=10\text{Hz},\,\text{DUTY}\,\,\text{OF}\,\,\text{LOAD}\,\,\text{CHANGE}=50\%$

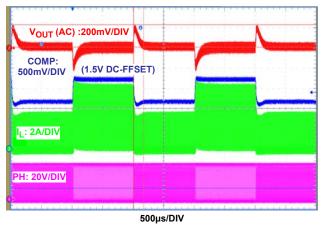

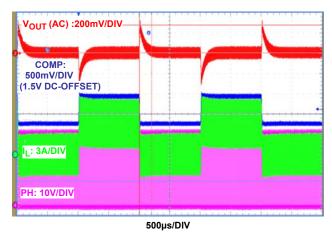

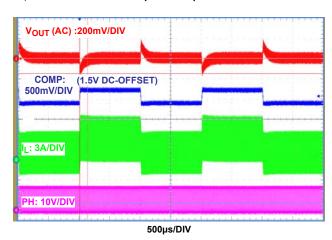

All the performance curves are taken from the Evaluation Board (ISL78268EVAL1Z) unless otherwise noted. (Continued)

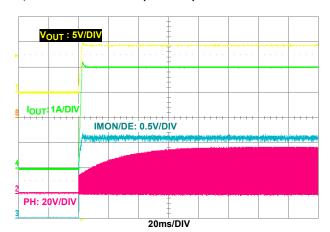

FIGURE 36. AVERAGE CONSTANT OUTPUT CURRENT CONTROL,  $V_{IN}=20V,\,V_{OUT}\,(\text{SETTING})=12V,\,C_{IMON}=1nF,\\ R_{IMON}=130k\Omega,\,\text{ACL}=4.05\text{A},\,R_L=2.3\Omega,\,\text{START-UP}\\ \text{WITH FIXED }R_L$

FIGURE 37. AVERAGE CONSTANT OUTPUT CURRENT CONTROL,  $V_{IN}=36V,\,V_{OUT}\,(\text{SETTING})=12V,\,C_{IMON}=1nF,\\ R_{IMON}=130k\Omega,\,\text{ACL}=4.05\text{A},\,R_L=2.3\Omega,\,\text{START-UP}\\ \text{WITH FIXED }R_L$

## **Operation Description**

The ISL78268 is an automotive graded (AEC-Q100 Grade-1) single-phase synchronous buck controller with integrated high/low side 2/3A MOSFET drivers. It supports a wide operating input voltage range of 5V to 55V and up to 60V at  $V_{IN}$  when not switching. The device also provides the features of selectable Diode Emulation mode for the higher efficiency operation in light load conditions, average constant output current controls, and several protection features such as input overvoltage protection, output overvoltage protection, cycle-by-cycle current limit and protections, and thermal protection. Details of the functions are described in the following.

### **Synchronous Buck**

In order to improve the efficiency, the ISL78268 employs synchronous buck architecture. In a synchronous buck, the LG output drives the synchronous low-side MOSFET, which replaces the freewheeling diode and improves the power losses by the voltage drop of the freewheeling diode while the high-side MOSFET is off. The LG signal is complementary to the UG signal.

The UG signal is powered from a charge pump that generates a voltage between BOOT and PH. An external diode from PVCC to BOOT charges an external capacitor between BOOT and PH when LG is high and PH is low. The capacitor provides the power to drive UG high. BOOT rises with PH and maintains the voltage to drive UG as the bootstrap diode is reverse biased.

### **Adaptive Dead-Time Control**

The UG and LG drivers are designed to have an adaptive dead-time algorithm that optimizes operation with varying MOSFET conditions. In this algorithm, the device detects the off timing of external MOSFETs which is turning off via the gate driver output voltage. The ISL78268 adds internally fixed 55ns dead-time before turning on the target gate driver. This algorithm helps to prevent shoot-through current at the switching of external MOSFETs and also optimizes the total dead-time to maximize the efficiency.

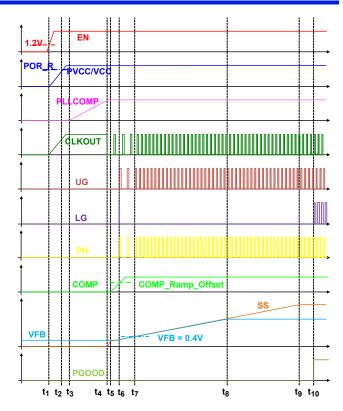

### **Operation Initialization and Soft-Start**