## ISL85009

9A, 3.8V to 18V Input, Synchronous Buck Regulator

FN8918 Rev.1.00 Mar 28, 2017

The <u>ISL85009</u> is a highly efficient, monolithic, synchronous buck regulator that can deliver 9A of continuous output current from a 3.8V to 18V input supply. The device uses current mode control architecture with a fast transient response and excellent loop stability.

The ISL85009 integrates very low ON-resistance high-side and low-side FETs to maximize efficiency and minimize external component count. The minimum BOM and easy layout footprint are extremely friendly to space constraint systems.

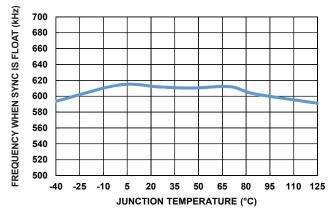

The operation frequency of this device can be set using the FREQ pin: 600kHz (FREQ = float) and 300kHz (FREQ = GND). The device can also be synchronized to an external clock up to 1MHz.

Both high-side and low-side MOSFET current limit along with reverse current limit, fully protect the regulator in an overcurrent event. Selectable OCP schemes can fit various applications. Other protections, such as input/output overvoltage and over-temperature, are also integrated into the device which give required system level safety in the event of fault conditions.

The ISL85009 is offered in a space saving 15 Ld 3.5mmx3.5mm Pb-free TQFN package with great thermal performance and 0.8mm maximum height.

## **Related Literature**

- · For a full list of related documents please visit our web page

- ISL85009 product page

## **Features**

- · Power input voltage range variable 3.8V to 18V

- PWM output voltage adjustable from 0.6V

- · Up to 9A output load

- · Prebias start-up, fixed 3ms soft-start

- Selectable f<sub>SW</sub> of 300kHz, 600kHz, and external synchronization up to 1MHz

- · Peak current mode control

- DCM/CCM

- Thermally compensated current limit

- Internal/external compensation

- · Open-drain PG window comparator

- · Output overvoltage and thermal protection

- · Input overvoltage protection

- · Integrated boot diode with undervoltage detection

- · Selectable OCP schemes

- Hiccup OCP

- Latch-off

- Compact size 3.5mmx3.5mm, 15 Ld TQFN

## **Applications**

- · Servers and cloud infrastructure POLs

- . IPCs, factory automation, and PLCs

- · Telecom and networking systems

- Storage systems

- · Test measurement

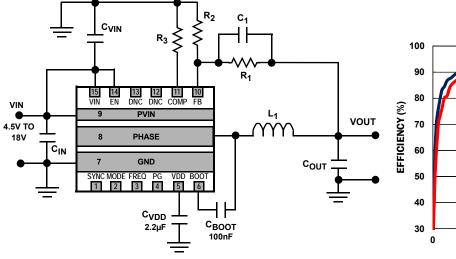

FIGURE 1. TYPICAL APPLICATION SCHEMATIC FOR INTERNAL COMPENSATION

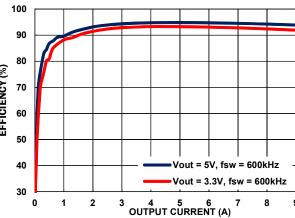

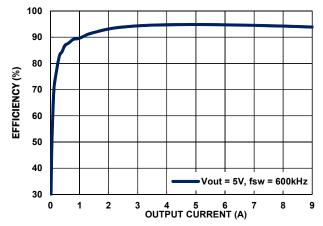

FIGURE 2. EFFICIENCY (VIN = 12V)

## **Typical Application Schematic**

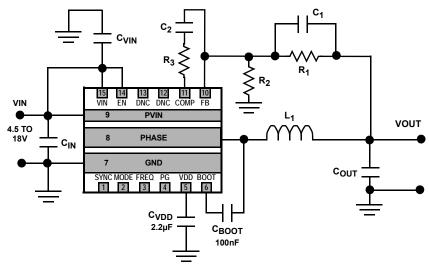

FIGURE 3. TYPICAL APPLICATION SCHEMATIC FOR EXTERNAL COMPENSATION

TABLE 1. DESIGN TABLE FOR DIFFERENT OUTPUT VOLTAGE USING INTERNAL COMPENSATION (See Figure 1)

| V <sub>OUT</sub> (V)  | 1           | 1.2         | 1.8       | 3.3       | 5        |

|-----------------------|-------------|-------------|-----------|-----------|----------|

| V <sub>IN</sub> (V)   | 4.5 to 18   | 4.5 to 18   | 4.5 to 18 | 4.5 to 18 | 6 to 18  |

| FREQ (kHz)            | 300         | 300         | 600       | 600       | 600      |

| Compensation          | Internal    | Internal    | Internal  | Internal  | Internal |

| C <sub>IN</sub> (μF)  | 3x22        | 3x22        | 3x22      | 3x22      | 3x22     |

| C <sub>OUT</sub> (μF) | 560 + 3x100 | 560 + 3x100 | 3x100     | 4x47      | 4x47     |

| L <sub>1</sub> (μΗ)   | 1           | 1           | 1         | 1.5       | 1.5      |

| R <sub>1</sub> (kΩ)   | 100         | 147         | 200       | 365       | 365      |

| R <sub>2</sub> (kΩ)   | 150         | 147         | 100       | 80.6      | 49.9     |

| C <sub>1</sub> (pF)   | DNP         | DNP         | 4.7       | 3.3       | 3.3      |

#### NOTES:

- 1. The design table is referencing the schematic shown in Figure 1.

- 2. Ceramic capacitors are selected for  $22\mu F$ ,  $47\mu F$ , and  $100\mu F$  in the table.

- 3.  $560\mu F$  (4.5m $\Omega$ ) low ESR conductive polymer aluminum solid capacitors are selected.

- 4. Recommend to keep the inductor peak-to-peak current to less than 5A.

# **Ordering Information**

| PART NUMBER<br>( <u>Notes 5, 6, 7</u> ) | PART<br>MARKING  | TEMP. RANGE<br>(°C) | TAPE AND REEL<br>(UNITS) | PACKAGE<br>(Rohs Compliant) | PKG.<br>DWG.# |

|-----------------------------------------|------------------|---------------------|--------------------------|-----------------------------|---------------|

| ISL85009FRZ-T                           | 5009             | -40 to +125         | 6k                       | 15 Ld 3.5mmx3.5mm TQFN      | L15.3.5x3.5   |

| ISL85009FRZ-T7A                         | 5008             |                     | 250                      |                             |               |

| ISL85009EVAL1Z                          | Evaluation Board |                     |                          |                             | ·             |

#### NOTES:

- 5. Refer to TB347 for details on reel specifications.

- 6. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 7. For Moisture Sensitivity Level (MSL), please see product information page for ISL85009. For more information on MSL, see tech brief TB363.

**TABLE 2. KEY DIFFERENCES BETWEEN FAMILY OF PARTS**

| PART NUMBER | BER INTERNAL/EXTERNAL COMPENSATION EXTERNAL FREQUENCY SYNC |     | CURRENT RATING |

|-------------|------------------------------------------------------------|-----|----------------|

| ISL85009    | Yes                                                        | Yes | 9A             |

| ISL85012    | Yes                                                        | Yes | 12A            |

| ISL85014    | Yes                                                        | Yes | 14A            |

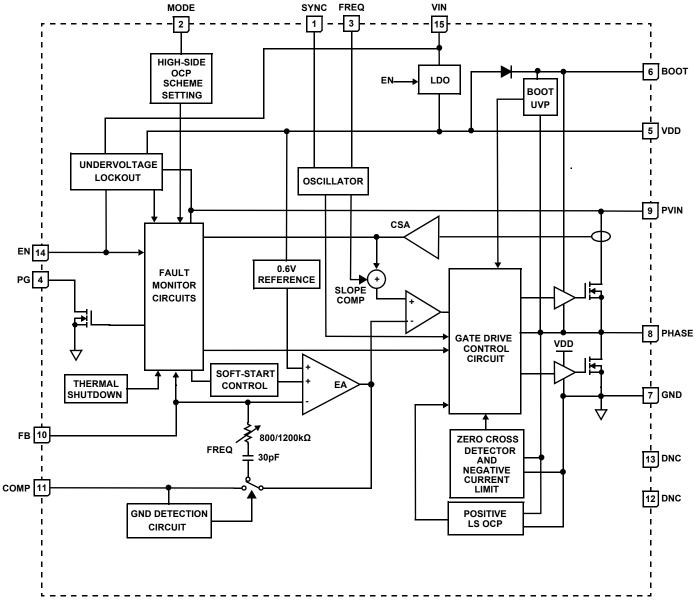

# **Functional Block Diagram**

FIGURE 4. FUNCTIONAL BLOCK DIAGRAM

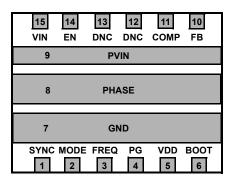

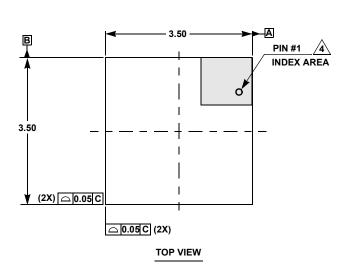

# **Pin Configuration**

ISL85009 (15 LD 3.5mmx3.5mm TQFN) TOP VIEW

# **Pin Descriptions**

| PIN#   | PIN<br>NAME                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SYNC                                                                                                                                                                                                                                                                                                                                                                     | Synchronization and FCCM/DEM selection pin. Connect to VDD or float for Forced Continuous Conduction Mode. Connect to GND for Diode Emulation Mode in the light-load condition. Connect to an external clock signal for synchronization with the rising edge trigger. |

| 2      | MODE                                                                                                                                                                                                                                                                                                                                                                     | OCP scheme select pin. Short it to GND for Latch-Off mode. Float it for Hiccup mode.                                                                                                                                                                                  |

| 3      | FREQ                                                                                                                                                                                                                                                                                                                                                                     | Default frequency selection pin. Short it to GND for 300kHz. Float it for 600kHz.                                                                                                                                                                                     |

| 4      | PG                                                                                                                                                                                                                                                                                                                                                                       | Power-good open-drain output. It requires a pull-up resistor ( $10k\Omega$ to $100k\Omega$ ) between PG and VDD or a voltage not exceeding 5.5V. PG pulls high when FB is in the range of ~90% to ~116% of its intended value.                                        |

| 5      | 5 VDD Low dropout linear regulator decoupling pin. The VDD is the internally generated 5V supply voltage and is derived from VDD is used to power all the internal core analog control blocks and drivers. Connect a 2.2µF capacitor from VDD to the ground plane. If the V <sub>IN</sub> is between 3V to 5.5V, then connect VDD directly to VIN to improve efficiency. |                                                                                                                                                                                                                                                                       |

| 6      | воот                                                                                                                                                                                                                                                                                                                                                                     | BOOT is the floating bootstrap supply pin for the high-side power MOSFET gate driver. A bootstrap capacitor, usually 0.1µF, is required between BOOT and PHASE.                                                                                                       |

| 7      | GND                                                                                                                                                                                                                                                                                                                                                                      | Reference of the power circuit. For thermal relief, this pin should be connected to the ground plane by vias.                                                                                                                                                         |

| 8      | PHASE                                                                                                                                                                                                                                                                                                                                                                    | Switch node connection to the internal power MOSFETs (source of upper FET and drain of lower FET) and the external output inductor.                                                                                                                                   |

| 9      | PVIN                                                                                                                                                                                                                                                                                                                                                                     | Input supply for the PWM regulator power stage. A decoupling capacitor, typically ceramic, is required to be connected between this pin and GND.                                                                                                                      |

| 10     | FB                                                                                                                                                                                                                                                                                                                                                                       | Inverting input to the voltage loop error amplifier. The output voltage is set by an external resistor divider connected to FB.                                                                                                                                       |

| 11     | COMP                                                                                                                                                                                                                                                                                                                                                                     | Output of the error amplifier. Compensation network between COMP and FB to configure external compensation. Place a $200\Omega$ resistor between COMP and GND for internal compensation, which is used to meet most applications.                                     |

| 12, 13 | DNC                                                                                                                                                                                                                                                                                                                                                                      | Do Not Connect to pin. Float the pins in the design.                                                                                                                                                                                                                  |

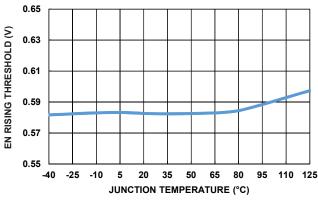

| 14     | EN                                                                                                                                                                                                                                                                                                                                                                       | Enable input. The regulator is held off when this pin is pulled to ground. The device is enabled when the voltage on this pin rises to about 0.6V.                                                                                                                    |

| 15     | VIN                                                                                                                                                                                                                                                                                                                                                                      | Input supply for the control circuit and the source for the internal linear regulator that provides bias for the IC.  A decoupling capacitor, typically 1µF ceramic, is required between VIN and GND.                                                                 |

## **Absolute Maximum Ratings**

| VIN, EN to GND                                                             |

|----------------------------------------------------------------------------|

| •                                                                          |

| PVIN to GND0.3V to +24V                                                    |

| PHASE to GND0.7V to +24V (DC)                                              |

| PHASE to GND2V to +24V (40ns)                                              |

| BOOT to PHASE0.3V to +7V                                                   |

| VDD, COMP, SYNC, PG, FB, MODE, FREQ, SS, IOCP to GND $\ldots$ -0.3V to +7V |

| ESD Rating                                                                 |

| Human Body Model (Tested per JS-001-2014)2.5kV                             |

| Charged Device Model (Tested per JS-002-2014) 1kV                          |

| Latch-Up (Tested per JESD78E; Class 2, Level A, +125°C)100mA               |

### **Thermal Information**

| Thermal Resistance                | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------|----------------------|----------------------|

| TQFN Package (Notes 8, 9)         | 33                   | 1.2                  |

| Maximum Storage Temperature Range | 6                    | 5°C to +150°C        |

| Junction Temperature Range        |                      | 5°C to +150°C        |

| Pb-Free Reflow Profile            |                      | see <u>TB493</u>     |

## **Recommended Operating Conditions**

| VIN Supply Voltage Range  | 4.5V to 18V |

|---------------------------|-------------|

| PVIN Supply Voltage Range | 3.8V to 18V |

| Load Current Range        | 0A to 9A    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features, except with

three vias under the GND EPAD strip contacting the GND plane and two vias under the VIN EPAD strip contacting the VIN plane. See Tech Brief <u>TB379</u>.

- 9. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Unless otherwise noted, all parameter limits are established over the recommended operating conditions and the typical specifications are measured at the following conditions:  $T_J = -40$  °C to +125 °C,  $V_{IN} = 4.5$ V to 18V, unless otherwise noted. Typical values are at  $T_A = +25$  °C. Boldface limits apply across the operating temperature range, -40 °C to +125 °C.

| PARAMETER                           | SYMBOL           | TEST CONDITIONS                                             | MIN<br>( <u>Note 10</u> )                    | TYP | MAX<br>( <u>Note 10</u> ) | UNIT |

|-------------------------------------|------------------|-------------------------------------------------------------|----------------------------------------------|-----|---------------------------|------|

| SUPPLY VOLTAGE                      | <u> </u>         |                                                             | <u>'</u>                                     |     |                           |      |

| PVIN Voltage Range                  | PVIN             |                                                             | 3.8                                          |     | 18                        | ٧    |

| VIN Voltage Range                   | VIN              |                                                             | 4.5                                          |     | 18                        | ٧    |

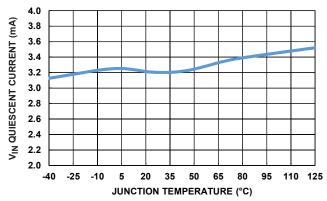

| VIN Quiescent Supply Current        | lQ               | EN = 2V, FB = 0.64V                                         |                                              | 3   | 5                         | mA   |

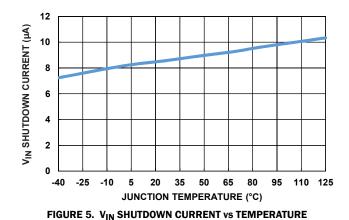

| VIN Shutdown Supply Current         | I <sub>SD</sub>  | EN = GND                                                    |                                              | 8   | 13                        | μΑ   |

| POWER-ON RESET                      |                  |                                                             | <u>,                                    </u> | I.  |                           |      |

| PVIN POR Threshold                  |                  | Rising edge                                                 |                                              |     | 2.9                       | ٧    |

|                                     |                  | Falling edge                                                | 1.9                                          |     |                           | ٧    |

| VIN POR Threshold                   |                  | Rising edge                                                 |                                              |     | 4.49                      | ٧    |

|                                     |                  | Falling edge                                                | 3.4                                          |     |                           | ٧    |

| EN POR Threshold                    |                  | Rising edge                                                 | 0.5                                          | 0.6 | 0.7                       | ٧    |

|                                     |                  | Hysteresis                                                  |                                              | 100 |                           | m۷   |

| VDD POR Threshold                   |                  | Rising edge                                                 |                                              |     | 3.6                       | ٧    |

|                                     |                  | Falling edge                                                | 2.4                                          |     |                           | ٧    |

| INTERNAL VDD LDO                    | -                |                                                             | <u> </u>                                     |     | 1                         |      |

| VDD Output Voltage Regulation Range |                  | V <sub>IN</sub> = 6V to 18V, I <sub>VDD</sub> = 0mA to 30mA | 4.3                                          | 5.0 | 5.5                       | ٧    |

| VDD Output Current Limit            |                  |                                                             |                                              | 80  |                           | mA   |

| LDO Dropout Voltage                 |                  | V <sub>IN</sub> = 5V, I <sub>VDD</sub> = 30mA               |                                              |     | 0.65                      | ٧    |

| OSCILLATOR                          |                  |                                                             |                                              |     | 1                         |      |

| Nominal Switching Frequency         | f <sub>SW1</sub> | FREQ = float                                                | 540                                          | 600 | 660                       | kHz  |

| Nominal Switching Frequency         | f <sub>SW2</sub> | FREQ = GND                                                  | 250                                          | 280 | 310                       | kHz  |

| Minimum On-Time                     | t <sub>ON</sub>  | I <sub>OUT</sub> = 0mA                                      |                                              | 90  | 150                       | ns   |

| Minimum Off-Time                    | t <sub>OFF</sub> |                                                             |                                              | 140 | 170                       | ns   |

| Synchronization Range               |                  |                                                             | 100                                          |     | 1000                      | kHz  |

| SYNC Logic Input Low                |                  |                                                             |                                              |     | 0.5                       | ٧    |

| SYNC Logic Input High               |                  |                                                             | 1.2                                          |     |                           | ٧    |

**Electrical Specifications** Unless otherwise noted, all parameter limits are established over the recommended operating conditions and the typical specifications are measured at the following conditions:  $T_J = -40 \,^{\circ}\text{C}$  to  $+125 \,^{\circ}\text{C}$ ,  $V_{IN} = 4.5 \,^{\circ}\text{C}$  to  $+18 \,^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}\text{C}$ . Boldface limits apply across the operating temperature range,  $-40 \,^{\circ}\text{C}$  to  $+125 \,^{\circ}\text{C}$ . (Continued)

| PARAMETER                                 | SYMBOL            | TEST CONDITIONS                                         | MIN<br>(Note 10) | TYP   | MAX<br>( <u>Note 10</u> ) | UNIT    |

|-------------------------------------------|-------------------|---------------------------------------------------------|------------------|-------|---------------------------|---------|

| ERROR AMPLIFIER                           | -II               |                                                         | I.               |       | I.                        |         |

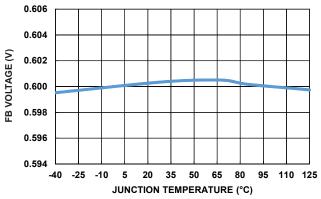

| FB Regulation Voltage                     | V <sub>FB</sub>   |                                                         | 0.588            | 0.6   | 0.612                     | ٧       |

| FB Leakage Current                        |                   | V <sub>FB</sub> = 0.6V                                  |                  |       | 10                        | nA      |

| Open Loop Bandwidth                       | BW                |                                                         |                  | 5.5   |                           | MHz     |

| Gain                                      |                   |                                                         |                  | 70    |                           | dB      |

| Output Drive                              |                   | High-side clamp = 1.5V, low-side clamp = 0.4V           |                  | ±100  |                           | μA      |

| Current Sense Gain                        | RT                |                                                         | 0.05             | 0.055 | 0.063                     | Ω       |

| Slope Compensation                        | Se                | Tested at 600kHz                                        |                  | 470   |                           | mV/μs   |

| SOFT-START                                | П                 | ,                                                       | 1                |       | I.                        |         |

| Default Soft-Start Time                   |                   |                                                         | 1.9              | 3     | 4.7                       | ms      |

| PG                                        | 1                 |                                                         |                  |       | l                         | Ш       |

| Output Low Voltage                        |                   | I <sub>PG</sub> = 5mA                                   |                  | 0.3   |                           | ٧       |

| PG Pin Leakage Current                    |                   |                                                         |                  | 0.01  |                           | μA      |

| PG Lower Threshold                        |                   | Percentage of output regulation                         | 81               | 87    | 92                        | %       |

| PG Upper Threshold                        |                   | Percentage of output regulation                         | 110              | 116   | 121                       | %       |

| PG Thresholds Hysteresis                  |                   | SYNC is short-to-GND                                    |                  | 3     |                           | %       |

| Delay Time                                |                   | Rising edge                                             |                  | 1.5   |                           | ms      |

|                                           |                   | Falling edge                                            |                  | 23    |                           | μs      |

| FAULT PROTECTION                          |                   |                                                         | -                |       |                           | Ш       |

| VIN/PVIN Overvoltage Lockout              |                   | Rising edge                                             | 19               | 20.5  | 22                        | ٧       |

|                                           |                   | Falling edge                                            | 18               | 19.5  | 21                        | ٧       |

|                                           |                   | Hysteresis                                              |                  | 1     |                           | ٧       |

| Positive Overcurrent Protection Threshold | I <sub>POCP</sub> | High-side OCP                                           | 12.5             | 15    | 16.5                      | Α       |

|                                           |                   | Low-side OCP                                            |                  | 21    |                           | Α       |

| Negative Overcurrent Protection Threshold | I <sub>NOCP</sub> | Current forced into PHASE node, high-side MOSFET is off | -10.8            | -7.5  | -5.5                      | Α       |

| Hiccup Blanking Time                      |                   |                                                         |                  | 150   |                           | ms      |

| FB Overvoltage Threshold                  |                   |                                                         | 110              | 116   | 121                       | %       |

| Thermal Shutdown Temperature              | T <sub>SD</sub>   | Rising threshold                                        |                  | 160   |                           | °C      |

|                                           | T <sub>HYS</sub>  | Hysteresis                                              |                  | 10    |                           | °C      |

| POWER MOSFET                              | •                 |                                                         |                  |       | •                         | <u></u> |

| High-Side                                 | R <sub>HDS</sub>  | IPHASE = 900mA                                          |                  | 17    |                           | mΩ      |

| Low-Side                                  | R <sub>LDS</sub>  | IPHASE = 900mA                                          |                  | 8.5   |                           | mΩ      |

| PHASE Pull-Down Resistor                  |                   | EN = GND                                                |                  | 22.5  |                           | kΩ      |

#### NOTE:

10. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

# **Typical Characteristics**

FIGURE 6. VIN QUIESCENT CURRENT VS TEMPERATURE

FIGURE 7. FEEDBACK VOLTAGE vs TEMPERATURE

FIGURE 8. ENABLE THRESHOLD vs TEMPERATURE

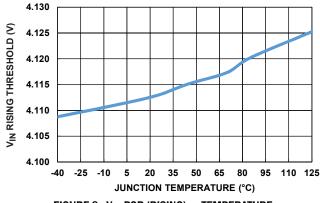

FIGURE 9. VIN POR (RISING) vs TEMPERATURE

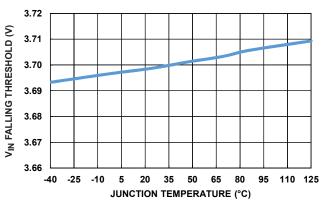

FIGURE 10. VIN POR (FALLING) vs TEMPERATURE

# Typical Characteristics (Continued)

FIGURE 11. FREQUENCY (600kHz DEFAULT) vs TEMPERATURE

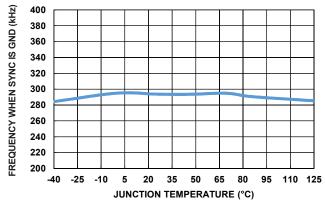

FIGURE 12. FREQUENCY (300kHz DEFAULT) vs TEMPERATURE

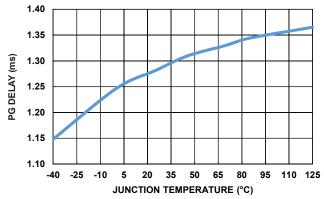

FIGURE 13. PG DELAY vs TEMPERATURE

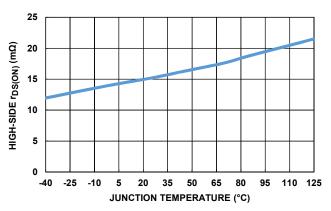

FIGURE 14. HIGH-SIDE  $r_{DS(ON)}$  vs TEMPERATURE

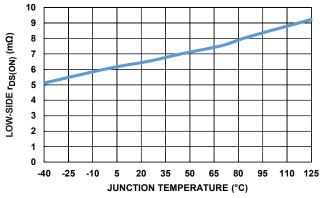

FIGURE 15. LOW-SIDE  $r_{DS(ON)}$  vs TEMPERATURE

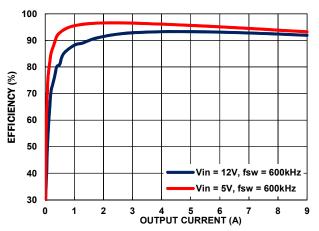

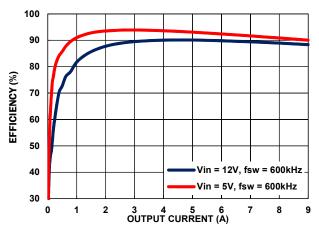

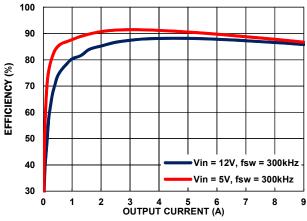

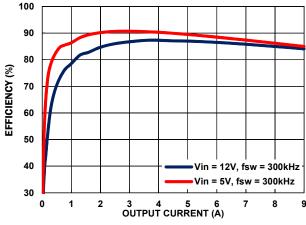

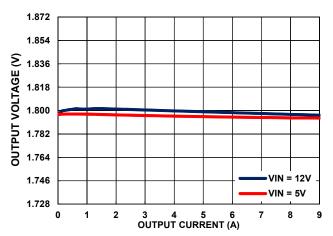

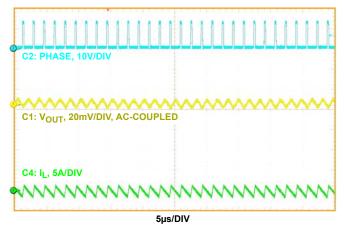

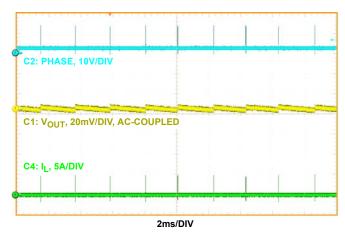

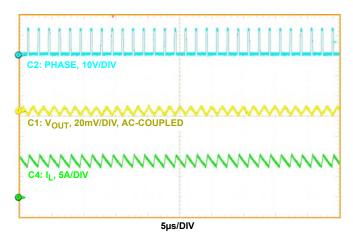

**Typical Performance Curves** Circuit of Figure 3. Design table on page 2 shows the components value for different output voltages. Plots are captured from ISL85009EVAL1Z boards.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ , FREQ = 600kHz, CCM,  $T_J = -40$  °C to +125 °C unless otherwise noted. Typical values are at  $T_A = +25$  °C.

FIGURE 16. EFFICIENCY vs LOAD ( $V_{OUT} = 5V$ ,  $f_{SW} = 600$ kHz)

FIGURE 17. EFFICIENCY vs LOAD ( $V_{OUT} = 3.3V$ ,  $f_{SW} = 600$ kHz)

FIGURE 18. EFFICIENCY vs LOAD ( $V_{OUT} = 1.8V$ ,  $f_{SW} = 600kHz$ )

FIGURE 19. EFFICIENCY vs LOAD ( $V_{OUT} = 1.2V$ ,  $f_{SW} = 300kHz$ )

FIGURE 20. EFFICIENCY vs LOAD (V<sub>OUT</sub> = 1.0V, f<sub>SW</sub> = 300kHz)

FIGURE 21.  $V_{OUT}$  REGULATION vs LOAD ( $V_{OUT}$  = 1.8V,  $f_{SW}$  = 600kHz)

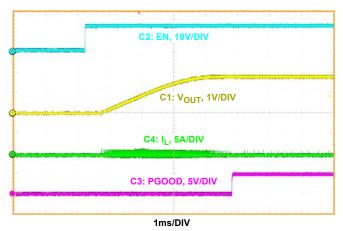

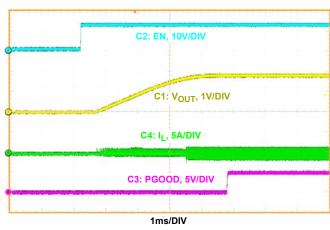

**Typical Performance Curves** Circuit of <u>Figure 3</u>. Design table on <u>page 2</u> shows the components value for different output voltages. Plots are captured from ISL85009EVAL1Z boards.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ , FREQ = 600kHz, CCM,  $T_J = -40$  °C to +125 °C unless otherwise noted. Typical values are at  $T_A = +25$  °C. (Continued)

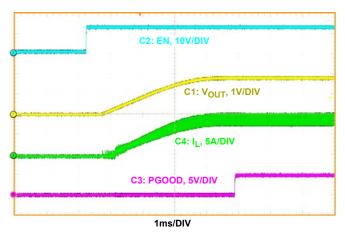

FIGURE 22. START-UP BY EN ( $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$  AT 0A, 600kHz, DCM)

FIGURE 23. START-UP BY EN ( $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$  AT 0A, 600kHz, FCCM)

FIGURE 24. START-UP BY EN ( $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$  AT 9A, 600kHz)

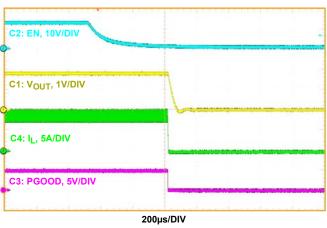

FIGURE 25. SHUT DOWN BY EN (V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 1.8V AT 9A, 600kHz)

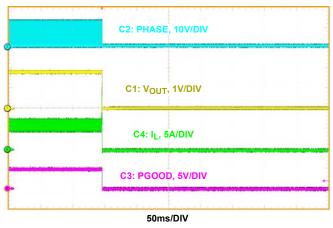

FIGURE 26. LATCH-OFF OCP ( $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ , 600kHz)

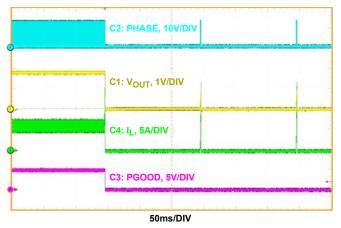

FIGURE 27. HICCUP OCP ( $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ , 600kHz)

**Typical Performance Curves** Circuit of Figure 3. Design table on page 2 shows the components value for different output voltages. Plots are captured from ISL85009EVAL1Z boards.  $V_{IN} = 12V$ ,  $V_{OUT} = 1.8V$ , FREQ = 600kHz, CCM,  $T_J = -40$  °C to +125 °C unless otherwise noted. Typical values are at  $T_A = +25$  °C. (Continued)

FIGURE 28. OUTPUT VOLTAGE RIPPLE ( $V_{IN}$  = 12V,  $V_{OUT}$  = 1.8V AT 0A, 600kHz, FCCM)

FIGURE 29. OUTPUT VOLTAGE RIPPLE ( $V_{IN} = 12V, V_{OUT} = 1.8V$  AT OA, 600kHz, DEM)

FIGURE 30. OUTPUT VOLTAGE RIPPLE (VIN = 12V, VOUT = 1.8V AT 9A, 600kHz)

## **Detailed Description**

The ISL85009 combines a synchronous buck controller with a pair of integrated switching MOSFETs. The buck controller drives the internal high-side and low-side N-channel MOSFETs to deliver load currents up to 9A. The buck regulator can operate from an unregulated DC source, such as a battery, with a voltage ranging from +3.8V to +18V. An internal 5V LDO voltage regulator is used to bias the controller. The converter output voltage is programmed using an external resistor divider and will generate regulated voltages down to 0.6V. These features make the regulator suited for a wide range of applications.

The controller uses a current mode loop, which simplifies the loop compensation and permits fixed frequency operation over a wide range of input and output voltages. The internal feedback loop compensation option allows for simple circuit design. 600kHz (FREQ = float) and 300kHz (FREQ = GND) can be selected as the default switching frequency. The regulator can be synchronized from 100kHz to 1MHz by the SYNC pin as well.

The buck regulator is equipped with a lossless current limit scheme. The current in the output stage is derived from temperature compensated measurements of the drain-to-source voltage of the internal power MOSFETs.

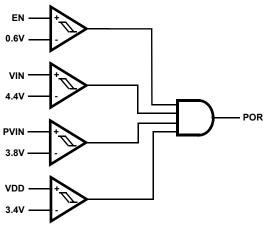

## **Operation Initialization**

The power-on reset circuitry and enable inputs prevent false start-up of the PWM regulator output. Once all the input criteria are met (see <a href="Figure 31">Figure 31</a>), the controller soft-starts the output voltage to the programmed level.

FIGURE 31. POR CIRCUIT

## **Enable and Soft-Start**

Chip operation begins after V<sub>IN</sub>, PVIN, and V<sub>DD</sub> exceed their rising POR trip points. If EN is held low externally, nothing happens until this pin is released. Once the voltage on the EN pin is above 0.6V, the LDO powers up and soft-start control begins. The ISL85009 operates with Diode Emulation Mode (DEM) during soft-start regardless the setting on SYNC pin. The soft-start time is 3ms (typical).

The part is designed to support start-up into a prebiased load (the prebiased voltage is required to be less than the output voltage setting). Both high-side and low-side switches are disabled until the internal SS voltage exceeds the FB voltage during start-up. It is recommended to connect an RC filter between an external EN input and the EN pin if a long trace or pull-up to VIN is used. An RC filter of  $100 \mathrm{k}\Omega$  and  $1\mathrm{nF}$  is recommended.

#### **PWM Control Scheme**

The ISL85009 employs the current-mode Pulse-Width Modulation (PWM) control scheme for fast transient response. The current loop consists of the oscillator, the PWM comparator, current-sensing circuit, and the slope compensation circuit. The gain of the current-sensing circuit is typically 55mV/A and the slope compensation is  $780\text{mV/t}_{SS}$  ( $t_{SS}$  = period). The control reference for the current loop comes from the Error Amplifier's (EA) output, which compares the feedback signal at FB pin to the integrated 0.6V reference.

To use internal compensation, connect COMP to ground via a  $200\Omega$  resistor. When the default frequency 600kHz is used, either by floating the FREQ pin, or by applying a 600kHz square wave at the SYNC pin, the voltage loop is internally compensated with a 30pF and  $800k\Omega$  RC network. When the frequency is set to 300kHz, the voltage loop is internally compensated with a 30pF and  $1200k\Omega$  RC network. A 30pF and  $1200k\Omega$  RC network is implemented for internal compensation when It works at default 300kHz (FREQ = GND).

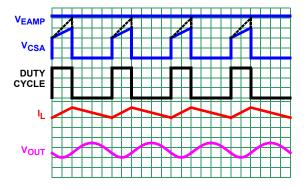

The PWM operation is initialized by the clock from the oscillator. The high-side MOSFET is turned on at the beginning of a PWM cycle and the current in the MOSFET starts to ramp-up. When the sum of the current amplifier (CSA) and the slope compensation (780mV/t<sub>SS</sub>) reaches the control reference of the current loop (COMP), the PWM comparator sends a signal to the PWM logic to turn off the upper MOSFET and turn on the lower MOSFET. The lower MOSFET stays on until the end of the PWM cycle. Figure 32 shows the typical operating waveforms during Continuous Conduction Mode (CCM) operation. The dotted lines illustrate the sum of the compensation ramp and the current sense amplifier's output.

FIGURE 32. PWM OPERATION WAVEFORMS

## **Light-Load Operation**

The ISL85009 monitors both the current in the low-side MOSFET and the voltage of the FB node for regulation. Pulling the SYNC pin low allows the regulator to enter discontinuous operation when lightly loaded by operating the low-side MOSFET in Diode Emulation Mode (DEM). In this mode, reverse current is not allowed in the inductor and the output falls naturally to the regulation voltage before the high-side MOSFET is switched for the next cycle. In CCM mode, the boundary is set by Equation 1:

$$I_{OUT} = \frac{V_{OUT}(1-D)}{2Lf_{SW}}$$

(EQ. 1)

where D = duty cycle,  $f_{SW}$  = switching frequency, L = inductor value,  $I_{OUT}$  = output loading current,  $V_{OUT}$  = output voltage. Table 3 shows the operating modes determined by the SYNC pin.

**TABLE 3. OPERATION MODE SETTING**

| SYNC PIN SETTING | LIGHT-LOAD OPERATION |

|------------------|----------------------|

| Float            | Forced CCM           |

| GND              | DEM                  |

## Switching Frequency Setting and Synchronization

The ISL85009's switching frequency can be set by the FREQ pin. Floating the FREQ pin sets the switching frequency to 600kHz, while shorting the FREQ pin to ground sets the switching frequency to 300kHz. The ISL85009 can also be synchronized from 100kHz to 1MHz by an external signal applied to the SYNC pin. The rising edge on the SYNC triggers the rising edge of the PHASE pulse. Make sure the on-time of the SYNC pulse is longer than 100ns.

When floating the FREQ pin for 600kHz switching frequency, or using synchronizing to an external clock on the SYNC pin, along with the internal compensation option (COMP short to GND through a  $200\Omega$  resistor), the voltage loop is internally compensated with a 30pF and  $800k\Omega$  RC network. A 30pF and  $1200k\Omega$  RC network is implemented for internal compensation when It works with FREQ = GND ( $f_{SW}$  = 300kHz).

In applications, the minimum on-time requirement of the regulator limits the range of the switching frequency. The maximum switching frequency can be calculated using Fountion 2:

$$f_{SW(Max)} = \frac{V_{OUT}}{V_{IN(MAX)} \cdot mint_{on}}$$

(EQ. 2)

ISL85009 requires a minimum on-time of 150ns (maximum) for proper output regulation. For example, with 1V output voltage and 18V maximum input voltage, the switching frequency must be less than 370kHz.

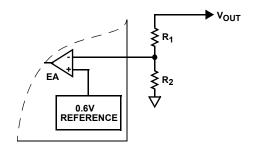

#### **Output Voltage Selection**

The regulator output voltages can be programmed using external resistor dividers that scale the voltage feedback relative to the internal reference voltage. The scaled voltage is fed back to the inverting input of the error amplifier; refer to Figure 33.

The output voltage programming resistor,  $R_2$ , will depend on the value chosen for the feedback resistor,  $R_1$ , and the desired output voltage,  $V_{OUT}$ ; see Equation 3. The  $R_1$  value will determine the gain of the feedback loop. See "Loop Compensation Design" on page 16 for more details. The value for the feedback resistor is typically between  $1k\Omega$  and  $370k\Omega$ .

$$R_2 = \frac{R_1 \cdot 0.6V}{V_{OUT} - 0.6V}$$

(EQ. 3)

If the desired output voltage is 0.6V, then  $\rm R_2$  is left unpopulated.  $\rm R_1$  is still required to set the low frequency pole of the modulator compensation.

FIGURE 33. EXTERNAL RESISTOR DIVIDER

## **Protection Features**

The regulator limits current in all on-chip power devices. Overcurrent limits are applied to the two output switching MOSFETs as well as to the LDO linear regulator that feeds  $V_{DD}$ . The output overvoltage protection circuitry on the switching regulator provides a second layer of protection.

## **High-Side MOSFET Overcurrent Protection**

Current flowing through the internal high-side switching MOSFET is monitored during on-time. The current, which is temperature compensated, will compare to a default 15A overcurrent limit. The ISL85009 offers two OCP schemes to implement the on-time overcurrent protection, which can be configured by the MODE pin (see Table 4).

**TABLE 4. OCP SCHEME SETTING**

| MODE PIN SETTING | OCP SCHEME                                                                               |

|------------------|------------------------------------------------------------------------------------------|

| Float            | Enter Hiccup mode after eight consecutive cycle-by-cycle limits. Blanking time is 150ms. |

| GND              | Enter Latch-Off mode after eight consecutive cycle-by-cycle limits.                      |

If the measured current exceeds the overcurrent limit, the high-side MOSFET is immediately turned off and will not turn on again until the next switching cycle. After eight consecutive cycles of overcurrent events detected, the converter will operate at the selected OCP scheme according to the MODE pin configuration. A cycle where an overcurrent condition is not detected will reset the counter.

The switching frequency will be folded back if the OCP is tripped and the on-time of the PWM is less than 250ns to lower down the average inductor current.

## **Low-Side MOSFET Overcurrent Protection**

Low-side current limit consists of forward current limit (from GND to PHASE) and reverse current limit (from PHASE to GND).

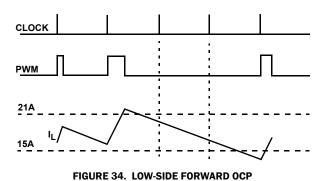

Current through the low-side switching MOSFET is sampled during off time. The low-side OCP comparator is flagged if the low-side MOSFET current exceeds 21A (forward). It resets the flag when the current falls below 15A. The PWM will skip cycles when the flag is set, allowing the inductor current to decay to a safe level before resuming switching (see Figure 34).

Similar to the forward overcurrent, the reverse current protection is realized by monitoring the current across the low-side MOSFET. When the low-side MOSFET current reaches -7.5A, the synchronous rectifier is turned off. This limits the ability of the regulator to actively pull-down on the output.

# Output Overvoltage Protection The overvoltage protection triggers when triggers when the overvoltage protection trigge

The overvoltage protection triggers when the output voltage exceeds 116% of the set voltage. In this condition, high-side and low-side MOSFETs are off until the output drops to within the regulation band. Once the output is in regulation, the controller will restart under internal SS control.

## **Input Overvoltage Protection**

The input overvoltage protection system prevents operation of the switching regulator whenever the input voltage is higher than 20V. The high-side and low-side MOSFETs are off and the converter will restart under internal SS control when the input voltage returns to normal.

## **Thermal Overload Protection**

Thermal overload protection limits the maximum die temperature, and thus the total power dissipation in the regulator. A sensor on the chip monitors the junction temperature. A signal is sent to the fault monitor circuits whenever the junction temperature (T<sub>J</sub>) exceeds +160 °C, which causes the switching regulator and LDO to shut down.

The switching regulator turns on again and soft-starts after the IC's junction temperature cools by 10 °C. The switching regulator exhibits hiccup mode operation during continuous thermal overload conditions. For continuous operation, do not exceed the +125 °C junction temperature rating.

## **BOOT Undervoltage Detection**

The internal driver of the high-side FET is equipped with a BOOT Undervoltage (UV) detection circuit. In the event the voltage difference between BOOT and PHASE falls below 2.8V, the UV detection circuit allows the low-side MOSFET on for 250ns to recharge the bootstrap capacitor.

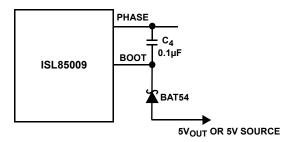

While the ISL85009 includes an internal bootstrap diode, efficiency can be improved by using an external supply voltage and bootstrap Schottky diode. The external diode is then sourced from a fixed external 5V supply or from the output of the switching regulator if this is at 5V. The bootstrap diode can be a low cost type, such as the BAT54 (see Figure 35).

#### **Power-Good**

ISL85009 has a Power-Good (PG) indicator which is an open drain of a MOSFET. It requires pull-up to VDD or other voltage source lower than 5.5V through a resistor (usually from 10k to  $100 \mathrm{k}\Omega$ ). The PG is asserted 1.5ms after the FB voltage reaches 90% of the reference voltage in soft-start. It pulls low if the FB voltage drops to 87% of the reference voltage or exceeds 116% of the reference voltage during the normal operation. Disabling the part also pulls the PG low. The PG will reassert when the FB voltage drops back to 113% (100%) of the reference voltage after tripping the overvoltage protection when SYNC is low (float/high).

FIGURE 35. EXTERNAL BOOTSTRAP DIODE

## **Application Guidelines**

## **Buck Regulator Output Capacitor Selection**

An output capacitor is required to filter the inductor current and supply the load transient current. The filtering requirements are a function of the switching frequency, the ripple current, and the required output ripple. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitor types and careful layout.

High frequency ceramic capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the Equivalent Series Resistance (ESR) and voltage rating requirements rather than actual capacitance requirements.

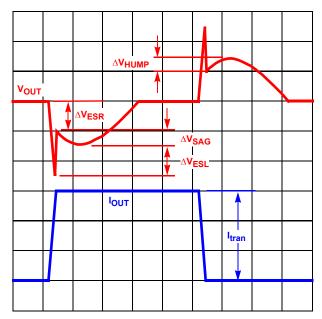

FIGURE 36. TYPICAL TRANSIENT RESPONSE

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements.

The shape of the output voltage waveform during a load transient that represents the worst case loading conditions will ultimately determine the number of output capacitors and their type. When this load transient is applied to the converter, most of the energy required by the load is initially delivered from the output capacitors. This is due to the finite amount of time required for the inductor current to slew up to the level of the output current required by the load. This phenomenon results in a temporary dip in the output voltage. At the very edge of the transient, the Equivalent Series Inductance (ESL) of each capacitor induces a spike that adds on top of the existing voltage drop due to the Equivalent Series Resistance (ESR).

After the initial spike, attributable to the ESR and ESL of the capacitors, the output voltage experiences sag. This sag is a direct consequence of the amount of capacitance on the output.

During the removal of the same output load, the energy stored in the inductor is dumped into the output capacitors. This energy dumping creates a temporary hump in the output voltage. This hump, as with the sag, can be attributed to the total amount of capacitance on the output. Figure 36 shows a typical response to a load transient.

The amplitudes of the different types of voltage excursions can be approximated using Equations 4, 5, 6, and 7:

$$\Delta V_{ESR} = ESR \bullet I_{TRAN}$$

(EQ. 4)

$$\Delta V_{ESL} = ESL \cdot \frac{I_{TRAN}}{dt}$$

(EQ. 5)

$$\Delta V_{SAG} = \frac{L_{out} \bullet I_{TRAN}^{2}}{2C_{OUT} \bullet (V_{IN} - V_{OUT})}$$

(EQ. 6)

$$\Delta V_{HUMP} = \frac{L_{out} \cdot I_{TRAN}^{2}}{2C_{OUT} \cdot V_{OUT}}$$

(EQ. 7)

where  $I_{TRAN}$  = Output Load Current Transient and  $C_{OUT}$  = Total Output Capacitance.

In a typical converter design, the ESR of the output capacitor bank dominates the transient response. The ESR and the ESL are typically the major contributing factors in determining the output capacitance. The number of output capacitors can be determined by using Equation 8, which relates the ESR and ESL of the capacitors to the transient load step and the tolerable output voltage excursion during load transient  $(\Delta V_{\rm O})$ :

Number of Capacitors =

$$\frac{ESL \bullet I_{TRAN}}{dt} + ESR \bullet I_{TRAN}$$

$$\frac{\Delta V_0}{\Delta V_0}$$

(EQ. 8)

If  $\Delta V_{SAG}$  and/or  $\Delta V_{HUMP}$  are found to be too large for the output voltage limits, then the amount of capacitance may need to be increased. In this situation, a trade-off between output inductance and output capacitance may be necessary.

The ESL of the capacitors, which is an important parameter in the previous equations, is not usually listed in the specification. Practically, it can be approximated using Equation 9 if an Impedance vs Frequency curve is given for a specific capacitor:

$$ESL = \frac{1}{C(2 \bullet \pi \bullet f_{res})^2}$$

(EQ. 9)

where f<sub>res</sub> is the frequency where the lowest impedance is achieved (resonant frequency).

The ESL of the capacitors becomes a concern when designing circuits that supply power to loads with high rates of change in the current.

#### **Output Inductor Selection**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage and current are approximated by Equations 10 and 11:

$$\Delta I = \frac{(V_{IN} - V_{OUT})}{f_{SW} \cdot L} \cdot \frac{V_{OUT}}{V_{IN}}$$

(EQ. 10)

$$\Delta V_{OLLT} = \Delta I \bullet ESR$$

(EQ. 11)

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient. It is recommended to set the ripple inductor current to approximately 30% of the maximum output current for optimized performance. It is recommend that the design of the inductor ripple current does not exceed 5A in the applications of ISL85009.

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the ISL85009 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval, the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

The response time to a transient is different for the application of load and the removal of load. <u>Equations 12</u> and <u>13</u> give the approximate response time interval for application and removal of a transient load:

$$t_{RISE} = \frac{L \times I_{TRAN}}{V_{IN} - V_{OUT}}$$

(EQ. 12)

$$t_{\text{FALL}} = \frac{L \times I_{\text{TRAN}}}{VOUT}$$

(EQ. 13)

where  $I_{TRAN}$  is the transient load current step,  $t_{RISE}$  is the response time to the application of load, and  $t_{FALL}$  is the response time to the removal of load. The worst case response time can be either at the application or removal of load. Be sure to check both of these equations at the minimum and maximum output levels for the worst case response time.

With the overcurrent protection thresholds of 15A (typical) on the high-side MOSFET and 21A(typical) on the low-side MOSFET, it is recommended to use the inductor with saturated current higher than 21A. Metal Alloy Powder material core inductors are typically recommended due to their better saturation characteristics.

#### **Input Capacitor Selection**

Use a mix of input bypass capacitors to control the input voltage ripple. Use ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time the switching MOSFET turns on. Place the ceramic capacitors physically close to the MOSFET VIN pins (switching MOSFET drain) and PGND.

The important parameters for the bulk input capacitance are the voltage rating and the RMS current rating. For reliable operation, select bulk capacitors with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. Their voltage rating should be at least 1.25x greater than the maximum input voltage, while a voltage rating of 1.5x is a conservative guideline. For most cases, the RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

The maximum RMS current required by the regulator may be closely approximated through **Equation 14**:

$$I_{RMS_{MAX}} = \sqrt{\frac{V_{OUT}}{V_{IN}} \bullet \left(I_{OUT_{MAX}}^2 + \frac{1}{12} \bullet \left(\frac{V_{IN} - V_{OUT}}{L \bullet f_{SW}} \bullet \frac{V_{OUT}}{V_{IN}}\right)^2\right)}$$

(EQ. 14)

For a through-hole design, several electrolytic capacitors may be needed, especially at temperatures less than -25 °C. The electrolytic's ESR can increase ten times higher than at room

temperature and cause input line oscillation. In this case, a more thermally stable capacitor such as X7R ceramic should be used. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. Some capacitor series available from reputable manufacturers are surge current tested.

## **Loop Compensation Design**

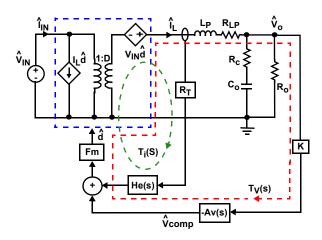

When COMP is not connected to GND through a  $200\Omega$  resistor, the COMP pin is active for external loop compensation. The regulator uses constant frequency peak current mode control architecture to achieve a fast loop transient response. An accurate current sensing pilot device in parallel with the high-side switch is used for peak current control signal and overcurrent protection. The inductor is not considered as a state variable since its peak current is constant, and the system becomes a single order system. It is much easier to design a Type II compensator to stabilize the loop than to implement voltage mode control. Peak current mode control has an inherent input voltage feed-forward function to achieve good line regulation. Figure 37 shows the small signal model of the synchronous buck regulator.

FIGURE 37. SMALL SIGNAL MODEL OF SYNCHRONOUS BUCK REGULATOR

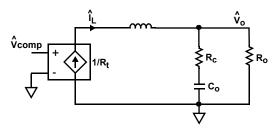

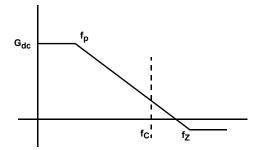

To simplify the analysis, sample and hold effect block He(s) and slope compensation are not taken into account. Assume  $V_{comp}$  is equal to the current sense signal  $I_L$  x  $R_t$  and ignore the DCR of the inductor. The power train can be approximated by a voltage controlled current source supplying current to the output capacitor and load resistor (see Figure 38). The transfer function frequency response is presented in Figure 39.

FIGURE 38. POWER TRAIN SMALL SIGNAL MODEL

FIGURE 39. POWER TRAIN SMALL FREQUENCY RESPONSE

The simplified transfer function is derived in Equation 15.

$$Gp(S) = \frac{\hat{v}_0}{\hat{v}_{comp}} = Gdc \frac{1 + \frac{S}{\omega_z}}{1 + \frac{S}{\omega_p}}$$

(EQ. 15)

where:

$$Gdc = \frac{R_o}{R_t}; \omega_z = 2\pi fz = \frac{1}{R_c x C_o}; \omega_p = 2\pi fp = \frac{1}{(R_o + R_c) x C_o}$$

(E0. 16)

Note that  $\mathrm{C}_{\mathrm{O}}$  is the actual capacitance seen by the regulator, which may include ceramic high frequency decoupling and bulk output capacitors. Ceramic may have to be derated by approximately 40% depending on dielectric, voltage stress, and temperature.

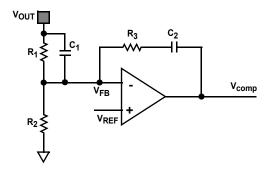

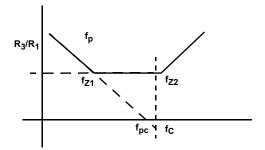

Usually, a Type II compensation network is used to compensate the peak current mode control converter. Figure 40 shows a typical Type II compensation network and its transfer function is expressed in Equation 17. The frequency response is shown in Figure 41.

FIGURE 40. TYPE II COMPENSATION NETWORK

$$A_{v}(S) = \frac{\hat{v}_{comp}}{\hat{v}_{o}} = \frac{\left(1 + \frac{S}{\omega_{cz1}}\right)\left(1 + \frac{S}{\omega_{cz2}}\right)}{SC_{2}R_{1}}$$

(EQ. 17)

where

$$\omega_{cz1} = 2\pi f_{z1} = \frac{1}{R_3 C_2}, \omega_{cz2} = 2\pi f_{z2} = \frac{1}{R_1 C_1}, f_{pc} = \frac{1}{2\pi R_1 C_2}$$

FIGURE 41. TYPE II COMPENSATION FREQUENCY RESPONSE

Design example:  $V_{IN}$  = 12V,  $V_{O}$  = 1.8V,  $I_{O}$  = 9A,  $f_{SW}$  = 600kHz,  $R_{1}$  = 200k $\Omega$ ,  $R_{2}$  = 100k $\Omega$ ,  $C_{O}$  = 3x100 $\mu$ F/3m $\Omega$  6.3V ceramic (actually ~150 $\mu$ F), L = 0.68 $\mu$ H.

Select  $f_c = 80kHz$ . The gain of the Gp(s)xAv(s) should have a unity gain at crossover frequency. Thus,  $R_3$  can be derived as:

$$R_3 = 2\pi f_c C_0 R_t R_1 = 829 k\Omega$$

(EQ. 18)

Select  $800k\Omega$  for  $R_3$ . Place the zero  $f_{z1}$  around the pole  $f_p$  to achieve -20db/dec roll off

$$C_2 = \frac{(Ro + Rc)xC_0}{R_3} = 38pF$$

(EQ. 19)

where Rc is the ESR of the output capacitor.

Select 30pF for  $C_2$ . Zero  $f_{z2}$  is a phase boost zero to increase the phase margin. Place it between  $f_c$  and 1/2 switching frequency. In this case, 4.7pF capacitor is selected and the zero is placed at  $f_{z2}$ :

$$f_{z2} = \frac{1}{2\pi R_1 C_1} = 169 \text{kHz}$$

(EQ. 20)

The calculated values for R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, C<sub>1</sub>, and C<sub>2</sub> match with the 1.8V output application in the recommended design with internal compensation shown in Table 1 on page 2. Do not select resistance higher than 370k $\Omega$  for R<sub>1</sub> in real applications, since it will result in a very small C<sub>1</sub>, which might be overwhelmed by parasitic capacitances.

In practice, it is recommended to select lower resistance for  $R_1/R_2$  and  $R_3$  in the external compensation applications. Usually, 10 times lower compared with the internal compensation is a good start.

# **Layout Considerations**

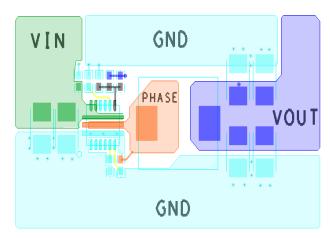

The layout is very important in high frequency switching converter design. With power devices switching efficiently at 600kHz, the resulting current transitions from one device to another causes voltage spikes across the devices and other circuit elements. These voltage spikes can degrade efficiency, radiate noise into the circuit, and lead to device overvoltage stress. Careful component layout and printed circuit board design minimizes these voltage spikes.

As an example, consider the turn-off transition of the upper MOSFET. Prior to turn-off, the MOSFET is carrying the full load current. During turn-off, current transfers from the MOSFET to the

internal body diode of the adjacent MOSFET. Any parasitic inductance in the switched current path generates a large voltage spike during the switching interval. Careful component selection, tight layout of the critical components, and short, wide traces minimize the magnitude of voltage spikes.

A multilayer printed circuit board is recommended. Figures 42 and 43 show the recommended layout of the top layer and the inner layer 1 of the schematic in Figure 1 on page 1.

- Place the input ceramic capacitors between PVIN and GND pins. Put them as close to the pins as possible.

- 2. A 1µF decoupling input ceramic capacitor is recommended. Place it as close to the VIN pin as possible.

- 3. A 2.2µF decoupling ceramic capacitor is recommended for the VDD pin. Place it as close to the VDD pin as possible.

- 4. The entire inner layer 1 is recommended to be the GND plane in order to reduce the noise coupling.

- The switching node (PHASE) plane needs to be kept away from the feedback network. Place the resistor divider close to the IC.

- 6. Put three to five vias on the GND pin to connect the GND plane of other layers for better thermal performance. This allows the heat to move away from the IC. Keep the vias small enough to prevent solder wicking through the holes during reflow. An 8 mil hole with 15 mil diameter vias are used on the evaluation board. Do not use "thermal relief" patterns to connect the vias. It is important to have a complete connection of the plated-through hole to each plane.

FIGURE 42. RECOMMENDED TOP LAYER LAYOUT

FIGURE 43. SOLID GND PLANE OF INNER LAYER 1

**Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure that you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                  |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Mar 28, 2017 | FN8918.1 | In "Power-Good" on page 14, updated 88% to 87% and 114% to 113%. Updated verbiage above Equation 8. Updated verbiage after Equation 19. |

| Feb 13, 2017 | FN8918.0 | Initial Release                                                                                                                         |

## **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing, and high-end consumer markets.

For the most updated datasheet, application notes, related documentation, and related parts, see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

For a listing of definitions and abbreviations of common terms used in our documents, visit: www.intersil.com/glossary.

You can report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at <a href="www.intersil.com/support">www.intersil.com/support</a>.

© Copyright Intersil Americas LLC 2017. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

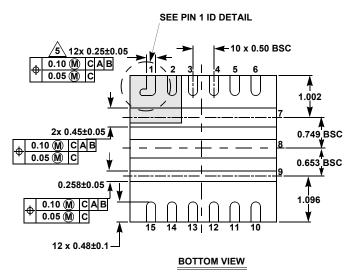

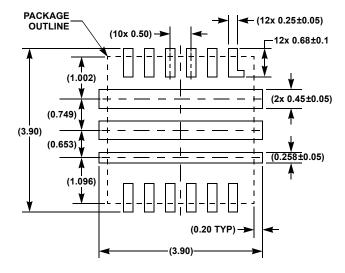

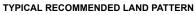

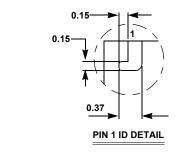

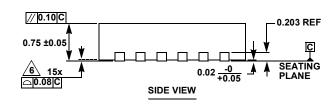

# **Package Outline Drawing**

L15.3.5x3.5

15 LEAD THIN QUAD FLAT NO-LEAD PACKAGE (TQFN)

Rev 1, 9/14

For the most recent package outline drawing, see <u>L15.3.5x3.5</u>.

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 2. All dimensions are in millimeters.

- 3. N is the total number of terminals.

The location of the marked terminal #1 identifier is within the hatched area.

Dimension applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has a radius on the other end of it, dimension b should not be measured in that radius area.

6 Coplanarity applies to the terminals and all other bottom surface metallization.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

EVAL-ADM1168LQEBZ EVB-EP5348UI MIC23451-AAAYFL EV MIC5281YMME EV DA9063-EVAL ADP122-3.3-EVALZ ADP1300.8-EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP1714-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM

BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM

NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM3691TL1.8EV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV EVAL-ADM1186-1MBZ EVAL-ADM1186-2MBZ