## ISL94202

Standalone 3 to 8 Cell Li-Ion Battery Pack Monitor

The <u>ISL94202</u> is a battery pack monitor IC that supports from three to eight series connected cells. It provides complete battery monitoring and pack control. The ISL94202 provides automatic shutdown and recovery from out-of-bounds conditions and automatically controls pack cell balancing.

The ISL94202 is highly configurable as a stand-alone unit, but can be used with an optional external Microcontroller (MCU), which communicates to the ISL94202 through an I<sup>2</sup>C interface.

The ISL94202 supersedes the ISL94203 for all future designs, as the ISL94202 operates in both parallel and series power FET configurations.

#### **Applications**

- · Power tools

- · Battery back-up systems

- · Light electric vehicles

- · Portable equipment

- · Energy storage systems

- · Solar farms

- Medical equipment

- · Hospital beds

- · Monitoring equipment

- Ventilators

#### **Features**

- Eight cell voltage monitors support Li-ion CoO<sub>2</sub>,

Li-ion Mn<sub>2</sub>O<sub>4</sub>, Li-ion FePO<sub>4</sub>, and other chemistries

- · Stand-alone pack control no MCU needed

- Multiple voltage protection options (each programmable to 4.8V; 12-bit digital value) and selectable overcurrent protection levels

- Programmable detection/recovery times for overvoltage, undervoltage, overcurrent, and short-circuit conditions

- Configuration/calibration registers maintained in EEPROM

- · Open Wire battery connection detection

- Integrated charge/discharge FET drive circuitry with built-in charge pump supports high-side N-channel FETs

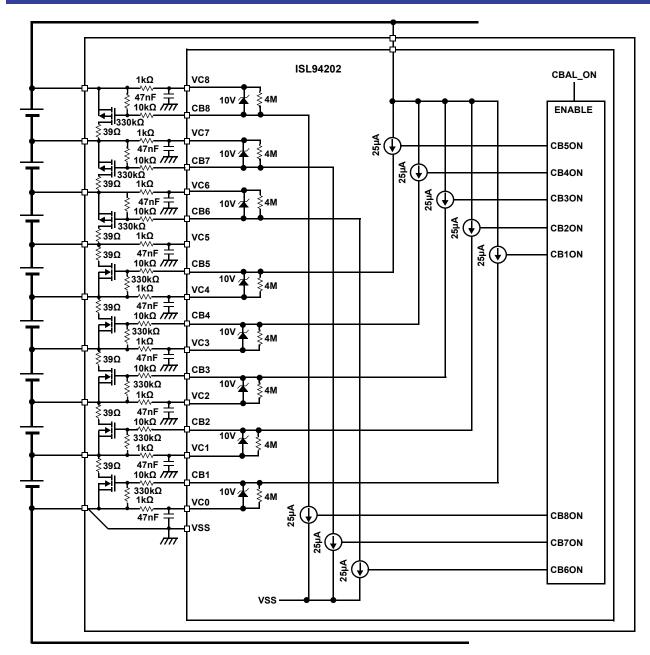

- Cell balancing uses external FETs with internal state machine or an optional external MCU

- · Enters low power states after periods of inactivity

- Charge or discharge current detection resumes normal scan rates

#### Related Literature

For a full list of related documents, visit our website:

• ISL94202 device page

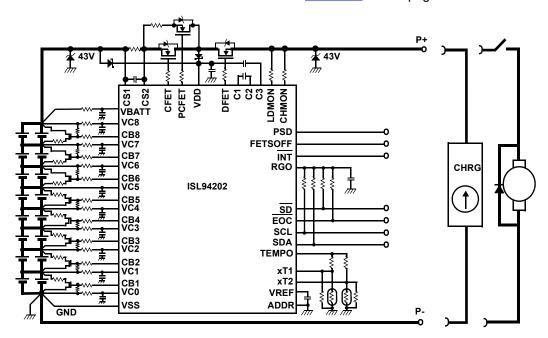

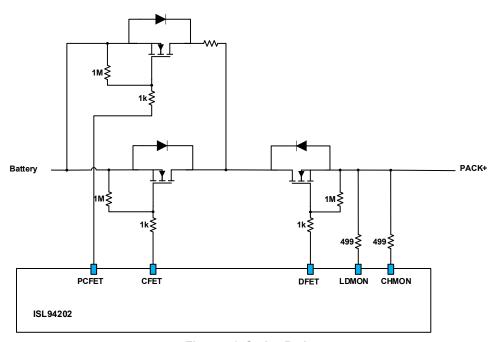

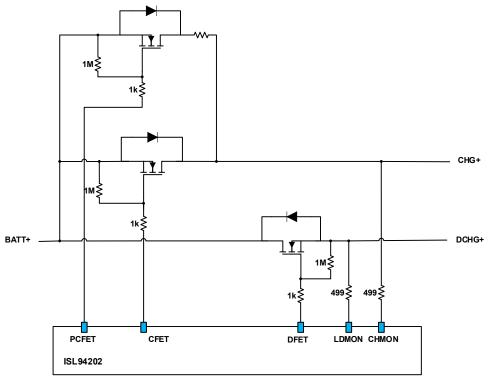

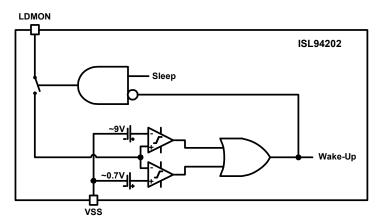

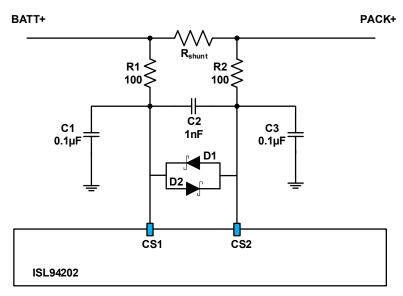

**Figure 1. Typical Application Diagram**

# **Contents**

| 1.  | Overview                                 | 8    |

|-----|------------------------------------------|------|

| 1.1 | Block Diagram                            | 8    |

| 1.2 |                                          |      |

| 1.3 | Pin Configuration                        | . 10 |

| 1.4 | · ·                                      |      |

| 2.  | Specifications                           | . 12 |

| 2.1 | ·                                        |      |

| 2.2 | · · · · · · · · · · · · · · · · · · ·    |      |

| 2.3 |                                          |      |

| 2.4 | , -                                      |      |

| 2.5 | ·                                        |      |

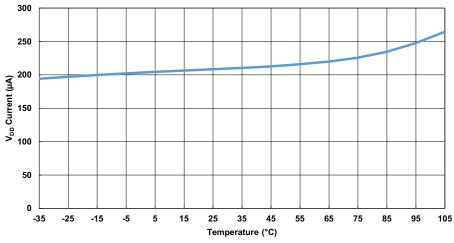

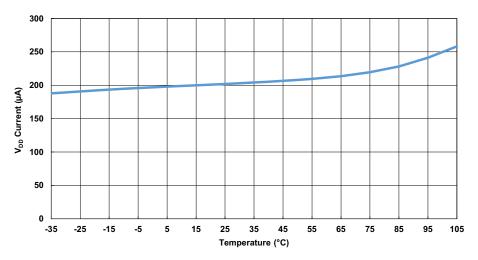

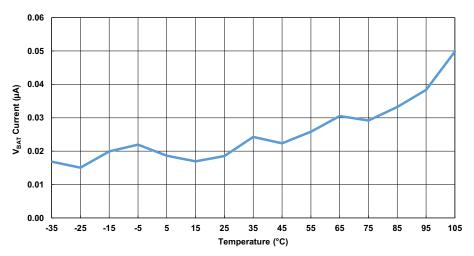

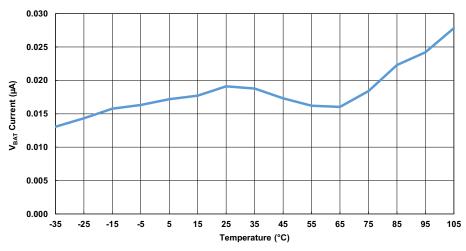

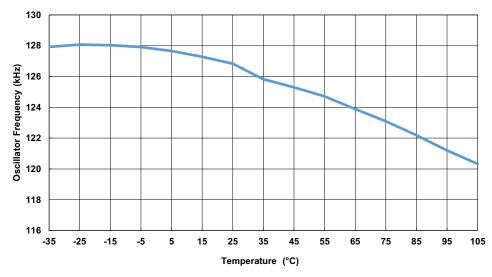

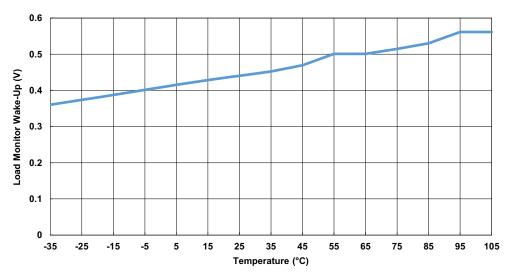

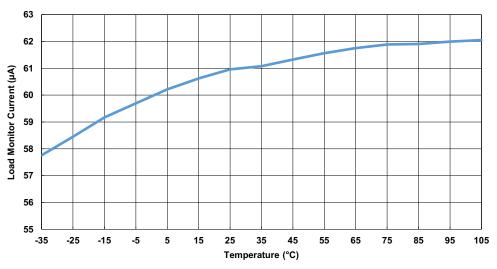

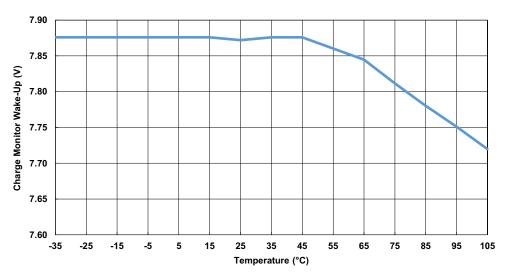

| 3.  | Typical Performance Curves               |      |

| 4.  | System Registers                         |      |

|     |                                          |      |

| 4.1 | 3                                        |      |

| 4.  | .1.1 0x00-01 CDPW & V <sub>CELL</sub> OV |      |

|     | 4.1.1.1 V <sub>CELL</sub> OV             |      |

| 1   | 4.1.1.2 0x01.7.4 CDPW                    |      |

|     | .1.3 0x04-05 LDPW & V <sub>CELL</sub> UV |      |

| т.  | 4.1.3.1 V <sub>CFLI</sub> UV             |      |

|     | 4.1.3.2 0x05.7:4 LDPW                    |      |

| 4.  | .1.4 0x06-07 V <sub>CELL</sub> UVR       |      |

| 4.  | .1.5 0x08-09 V <sub>CFLI</sub> OVLO      |      |

| 4.  | .1.6 0x0A-0B V <sub>CFLI</sub> UVLO      |      |

| 4.  | .1.7 0x0C-0D V <sub>CELL</sub> EOC       |      |

| 4.  | .1.8 0x0E-0F V <sub>CFI</sub> LVCL       |      |

|     | .1.9 0x10-11 V <sub>CFLI</sub> OV Timer  |      |

|     | 4.1.9.1 V <sub>CFLI</sub> OVDTU          |      |

|     | 4.1.9.2 V <sub>CFLI</sub> OVDT           |      |

| 4.  | .1.10 0x12-13 V <sub>CELL</sub> UV Timer | . 42 |

|     | 4.1.10.1 V <sub>CELL</sub> UVDTU         | . 42 |

|     | 4.1.10.2 V <sub>CELL</sub> UVDT          | . 42 |

| 4.  | .1.11 0x14-15 OWT                        |      |

|     | 4.1.11.1 OWTU                            |      |

| 1   | 4.1.11.2 OWT                             |      |

| 4.  |                                          |      |

|     | 4.1.12.1 0x17.[6:4] DOC                  |      |

|     | 4.1.12.3 0x16-17 DOCT                    |      |

|     | 4.1.12.4 DOCR                            |      |

| 4.  | .1.13 0x18-19 COC & COCT                 | . 46 |

|     | 4.1.13.1 0x19.[6:4] COC                  |      |

|     | 4.1.13.2 0x19.[3:2] COCTU                |      |

|     | 4.1.13.3 0x18-19 COCT                    |      |

| 4   | 4.1.13.4 COCR                            |      |

| 4.  |                                          |      |

|     | 4.1.14.1 0x1B.[6:4] DSC                  |      |

|     | T.1.17.2 0.1 15.[0.2] D0010              | . 40 |

| 4.1.14.3 0x1B.[1:0] - 0x1A.[7:0] DSCT |      |

|---------------------------------------|------|

| 4.1.14.4 DSCR                         |      |

|                                       |      |

| 4.1.16 0x1E-1F CBMAX                  |      |

| 4.1.17 0x20-21 CBMINDV                |      |

| 4.1.18 0x22-23 CBMAXDV                |      |

| 4.1.19 0x24-25 CBON Timer             |      |

| 4.1.19.1 0x25.[3:2] CBONU             |      |

| 4.1.19.2 0x24-25 CBON                 |      |

|                                       |      |

| 4.1.20.1 CBOFFU                       |      |

| 4.1.21 0x28-29 CBUT                   |      |

| 4.1.22 0x2A-2B CBUTR                  |      |

| 4.1.23 0x2C-2D CBOT                   |      |

| 4.1.24 0x2E-2F CBOTR                  |      |

|                                       |      |

|                                       |      |

| 4.1.26 0x32-33 COTR                   |      |

| 4.1.27 0x34-35 CUT                    |      |

| 4.1.28 0x36-37 CUTR                   |      |

| 4.1.29 0x38-39 DOT                    |      |

| 4.1.30 0x3A-3B DOTR                   |      |

| 4.1.31 0x3C-3D DUT                    |      |

| 4.1.32 0x3E-3F DUTR                   |      |

| 4.1.33 0x40-41 IOT                    |      |

| 4.1.34 0x42-43 IOTR                   |      |

| 4.1.35 0x44-45 SLV                    | . 64 |

| 4.1.36 0x46-47 WDT & SLT              | . 64 |

| 4.1.36.1 0x47.[7:3] WDT               | . 65 |

| 4.1.36.2 0x47.[2:1] SLTU              |      |

| 4.1.36.3 0x47.[0] - 0x46.[7:0] SLT    |      |

| 4.1.37 0x48 Mode Timers               |      |

| 4.1.37.1 0x48.[3:0] IDLE/DOZE Timer   |      |

| 4.1.37.2 0x48.[7:4] SLEEP Timer       |      |

| 4.1.39 0x4A Setup 0                   |      |

| 4.1.39                                |      |

| 4.1.39.1 0x4A.7 CELLF PSD             |      |

| 4.1.39.3 0x4A.4 TGAIN                 |      |

| 4.1.39.4 0x4A.2 PCFETE                |      |

| 4.1.39.5 0x4A.1 DOWD                  |      |

| 4.1.39.6 0x4A.0 OWPSD                 | . 68 |

| 4.1.40 0x4B Setup 1                   |      |

| 4.1.40.1 0x4B.7 CBDD                  |      |

| 4.1.40.2 0x4B.6 CBDC                  |      |

| 4.1.40.3 0x4B.5 DFODUV                |      |

| 4.1.40.4 0x4B.4 CFODOV                |      |

| 4.1.40.6 0x4B.0 CB EOC.               |      |

| 4.2 0x80-89 Other Registers           |      |

| 4.2.1 0x4C-4F RSV                     |      |

| 4.2.2 0x50-57 User EEPROM             |      |

| 4.3 0x80-89 Operations Registers      |      |

|                     |                              | _  |

|---------------------|------------------------------|----|

| 4.3.1 0x            | x80 Status 0 (R)             | 71 |

| 4.3.1.1             | 0x80.7 CUTF                  | 71 |

| 4.3.1.2             | 0x80.6 COTF                  |    |

| 4.3.1.3             | 0x80.5 DUTF                  |    |

| 4.3.1.4             | 0x80.4 DOTF                  | 72 |

| 4.3.1.5             | 0x80.3 UVLOF                 | 72 |

| 4.3.1.6             | 0x80.2 UVF                   | 72 |

| 4.3.1.7             | 0x80.1 OVLOF                 | 73 |

| 4.3.1.8             | 0x80.0 OVF                   | 73 |

| 4.3.2 0x            | د81 - Status 1 (R)           | 73 |

| 4.3.2.1             | 0x81.7 VEOC                  | 73 |

| 4.3.2.2             | 0x81.5 OWF                   |    |

| 4.3.2.3             | 0x81.4 CELLF                 |    |

| 4.3.2.4             | 0x81.3 DSCF                  |    |

| 4.3.2.5             | 0x81.2 DOCF                  |    |

| 4.3.2.6             | 0x81.1 COCF                  |    |

| 4.3.2.7             | 0x81.0 IOTF                  |    |

|                     | (82 - Status 2 (R)           |    |

| 4.3.3.1             | 0x82.7 LVCHG                 |    |

| 4.3.3.2             | 0x82.6 INT_SCAN              |    |

| 4.3.3.3             | 0x82.5,4 ECC_FAIL & ECC_USED |    |

| 4.3.3.4             | 0x82.3 DCHING                |    |

| 4.3.3.5             | 0x82.2 CHING                 |    |

| 4.3.3.6             | 0x82.1 CH_PRSNT              |    |

| 4.3.3.7             | 0x82.0 LD_PRSNT              |    |

|                     | :83 - Status 3 (R)           |    |

| 4.3.4.1             | 0x83.6 IN_SLEEP              |    |

| 4.3.4.2             | 0x83.5 IN_DOZE               |    |

| 4.3.4.3             | 0x83.4 IN_IDLE               |    |

| 4.3.4.4             | 0x83.3 CBUV                  |    |

| 4.3.4.5             | 0x83.2 CBOV                  |    |

| 4.3.4.6             | 0x83.1 CBUTF                 |    |

| 4.3.4.7<br>4.3.5 0x | 0x83.0 CBOTF                 |    |

|                     | 84 CBFC (R/W)                |    |

|                     | 85 Control 0 (R/W)           |    |

|                     | 0x85.6 ADCSTRT               |    |

| 4.3.6.2             | 0x85.[5:4] CG                |    |

| 4.3.6.3             | 0x85.[3:0] AO                |    |

|                     | 86 Control 1 (R/W)           |    |

| 4.3.7.1             | 0x86.7 CLR_LERR              |    |

| 4.3.7.2             | 0x86.6 LMON_EN               |    |

| 4.3.7.3             | 0x86.5 CLR_CERR              |    |

| 4.3.7.4             | 0x86.4 CMON_EN               |    |

| 4.3.7.5             | 0x86.3 PSD                   |    |

| 4.3.7.6             | 0x86.2 PCFET                 |    |

| 4.3.7.7<br>4.3.7.8  |                              |    |

|                     | 0x86.0 DFET                  |    |

|                     |                              |    |

| 4.3.8.1             | 0x87.6 μCFET                 |    |

| 4.3.8.2             | 0x87.5 μCCBAL                |    |

| 4.3.8.3             | 0x87.4 µCLMON                |    |

| 4.3.8.4<br>4.3.8.5  | 0x87.3 μCCMON                |    |

| 4.3.8.5<br>4.3.8.6  | 0x87.1 OW_STRT               |    |

| 4.3.8.7             | 0x87.0 CBAL ON               |    |

|                     |                              | 84 |

| 4.3          | .9.1 0x88.3 PDWN            | 84         |

|--------------|-----------------------------|------------|

| 4.3          | .9.2 0x88.2 SLEEP           |            |

|              | .9.3 0x88.1 DOZE            |            |

|              | .9.4 0x88.0 IDLE            |            |

|              | 0 0x89 - EEPROM Enable      |            |

| 4.3<br>4.4   | .10.1 0x89.0 EEEN           |            |

| 4.4          | Conversion Constants        |            |

|              | .1.1 Threshold Setting      |            |

|              | .1.1 Threshold Setting      |            |

|              | .1.3 Cell Voltage Formula   |            |

| 4.4.2        | 0x8A-8B CELMIN              |            |

| 4.4.3        | 0x8C-8D CELMAX              | 89         |

| 4.4.4        | 0x8E-8F IPACK               | 90         |

| 4.4.5        | 0x90-9F VCELL1-8            | 90         |

| 4.4.6        | 0xA0-A1 ITEMP               | 91         |

| 4.4.7        | 0xA2-A5 XT1-2               | 91         |

| 4.4.8        | 0xA6-A7 VBATT               |            |

| 4.4.9        | 0xA8-A9 VRGO                | 92         |

| 4.4.10       |                             |            |

|              |                             |            |

| 5. Pir       | n Function                  | 94         |

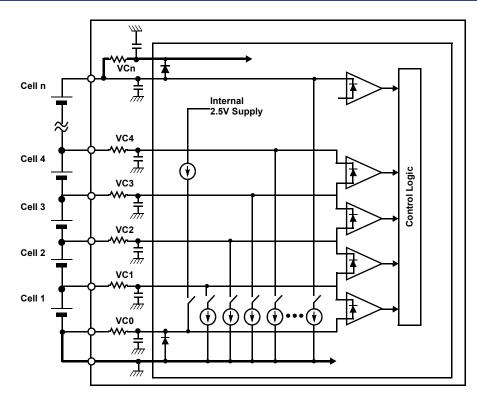

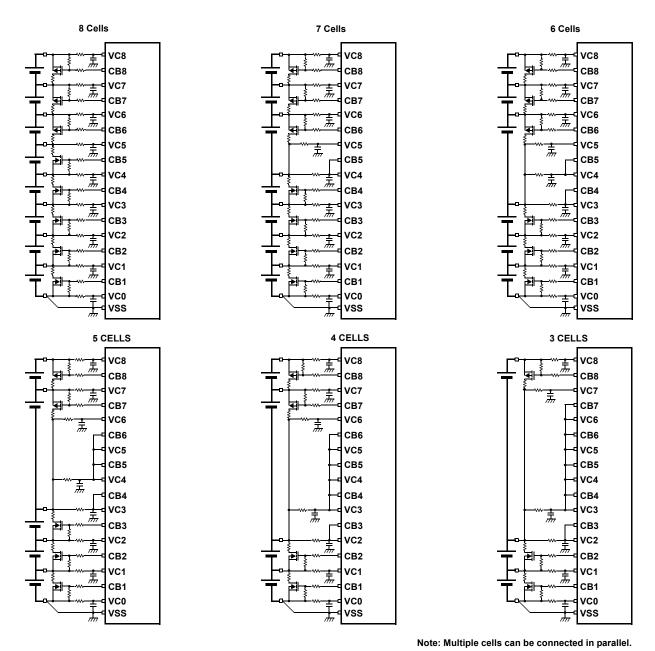

| 5.1          | VCn Pins                    | 94         |

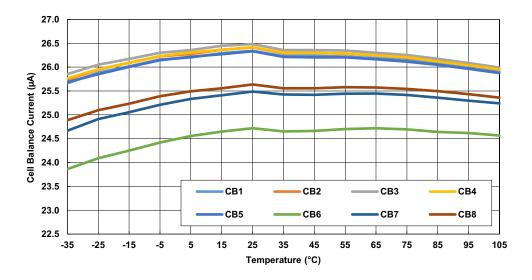

| 5.2          | CBn Pins                    | 94         |

| 5.3          | VSS Pin (18, 28, 29)        | 95         |

| 5.4          | VREF Pin (19)               | 95         |

| 5.5          | Thermistor Pins (20-22)     | 96         |

| 5.6          | ADDR Pin (24)               | 97         |

| 5.7          | SCL Pin (25)                | 97         |

| 5.8          | SDAI/O Pins (26, 27)        | 97         |

| 5.9          | <u>INT</u> Pin (31)         | 97         |

| 5.10         | PSD Pin (32)                | 98         |

| 5.11         | FETSOFF Pin (33)            | 98         |

| 5.12         | SD Pin (34)                 | 99         |

| 5.13         | EOC Pin (35)                | 99         |

| 5.14         | RGO Pin (36)                | 99         |

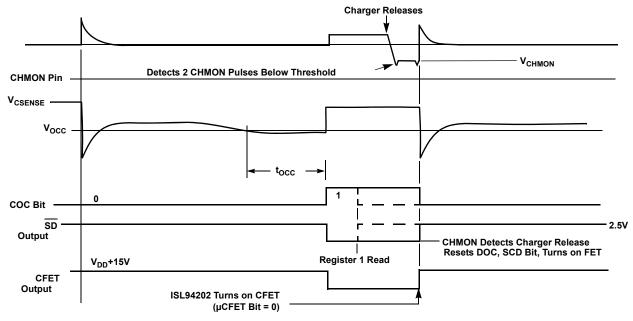

| 5.15         | CHMON Pin (37)              | 99         |

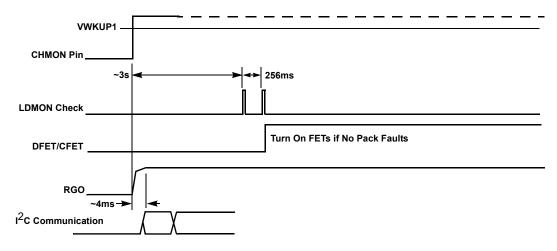

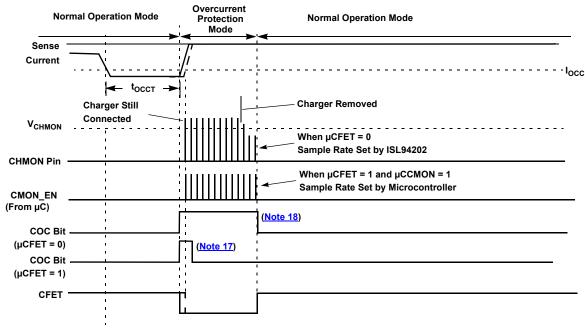

| 5.15.        | 1 COC Recovery              | 00         |

| 5.1          | 5.1.1 Automatic CHMON       | 101        |

|              | 5.1.2 MCU CHMON             |            |

|              | 2 Charger Detection         |            |

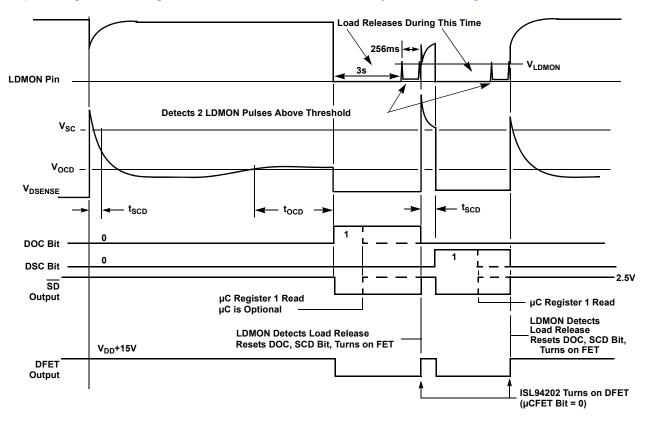

| 5.16         | LDMON Pin (38)              |            |

| 5.16.        | ,                           |            |

|              | 6.1.1 Automatic LDMON       |            |

|              | 6.1.2 MCU LDMON             |            |

|              | 2 Load Detection            |            |

| 5.17<br>5.10 | Cn Pins (39-41)             |            |

| 5.18<br>5.10 | VDD Pin (43)                |            |

| 5.19         | Power FET Pins (42, 44, 45) |            |

| 5.19.        |                             |            |

| 5.19.        |                             | 108<br>108 |

|              |                             |            |

| 5.19.4       | 4 Automatic FET Control         | 109 |

|--------------|---------------------------------|-----|

| 5.19.5       | 5 MCU FET Control               | 110 |

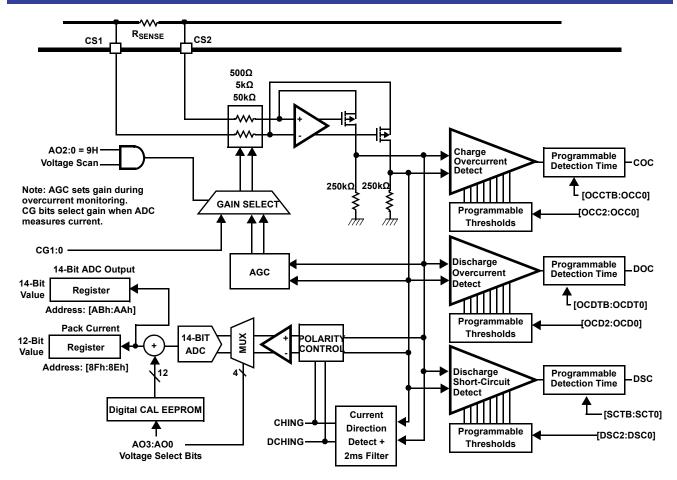

| 5.20         | CSI1-2 Pins (47, 48)            | 111 |

| 5.21         | VBATT Pin (48)                  | 113 |

|              |                                 |     |

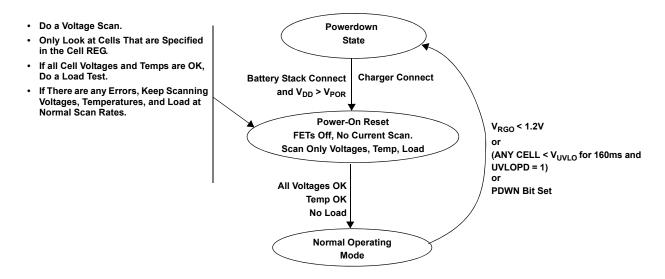

| 6. Sys       | stem Operation                  |     |

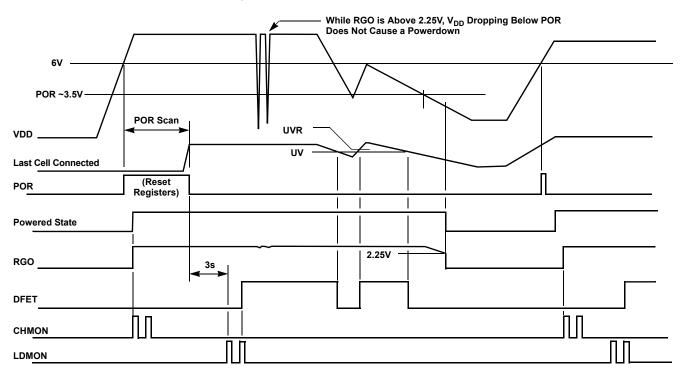

| 6.1          | Power Up                        |     |

| 6.2          | Wake Up                         |     |

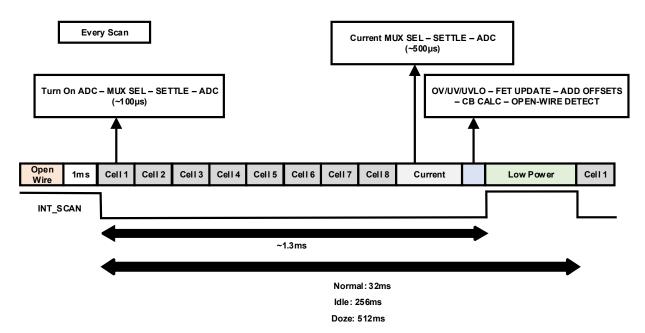

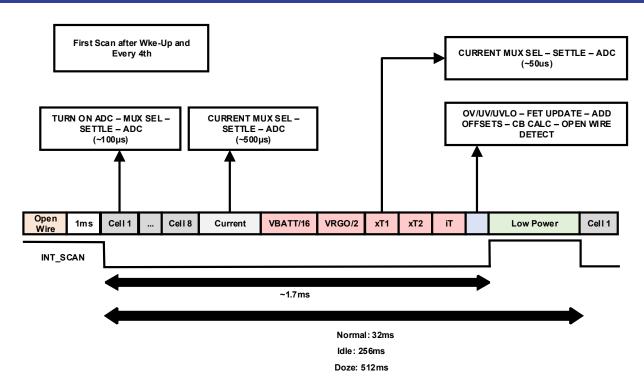

| 6.3          | System Scans                    |     |

| 6.3.1        | Automatic V & I Scan            |     |

| 6.3.2        | Automatic V, I, & T Scan        |     |

| 6.3.3        | MCU Scan                        |     |

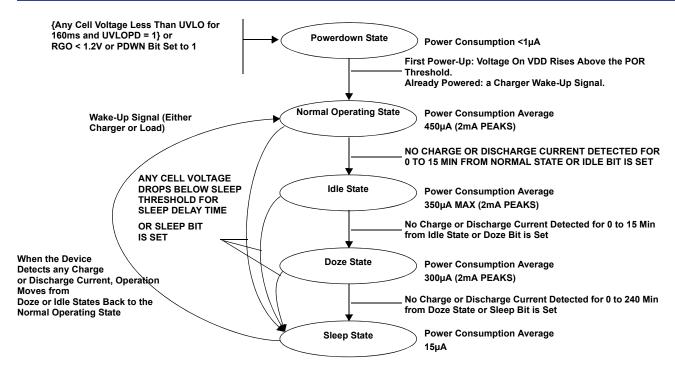

| 6.4          | System Modes                    |     |

| 6.4.1        | Powerdown State                 |     |

| 6.4.2        | NORMAL Mode                     |     |

| 6.4.3        | IDLE Mode                       |     |

| 6.4.4        | DOZE Mode                       |     |

| 6.4.5        | SLEEP Mode                      |     |

| 6.4.6<br>6.5 | Mode Exceptions                 |     |

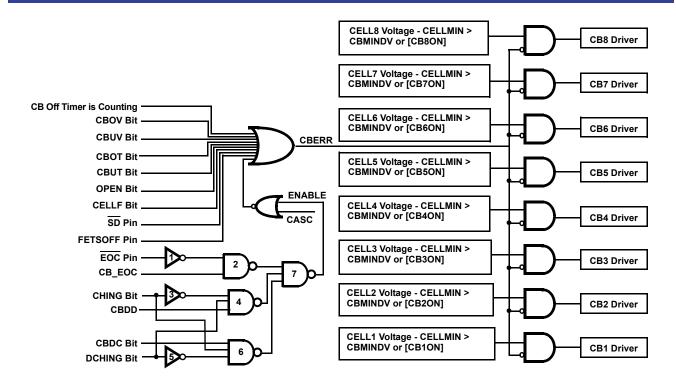

| 6.5.1        | Automatic CB.                   |     |

| 6.5.2        | MCU CB                          |     |

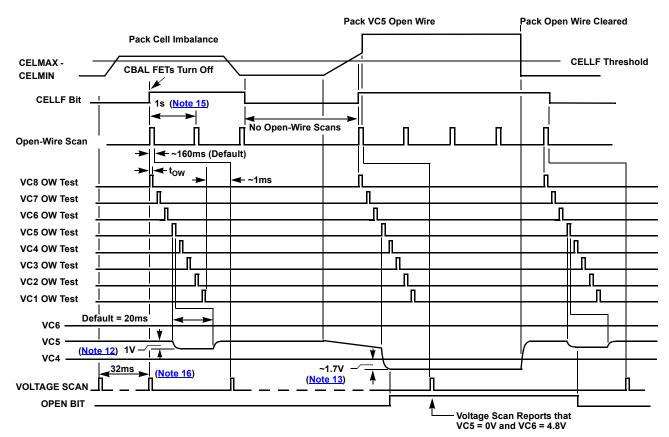

| 6.6          | Open Wire                       |     |

| 6.7          | Cell Fail                       |     |

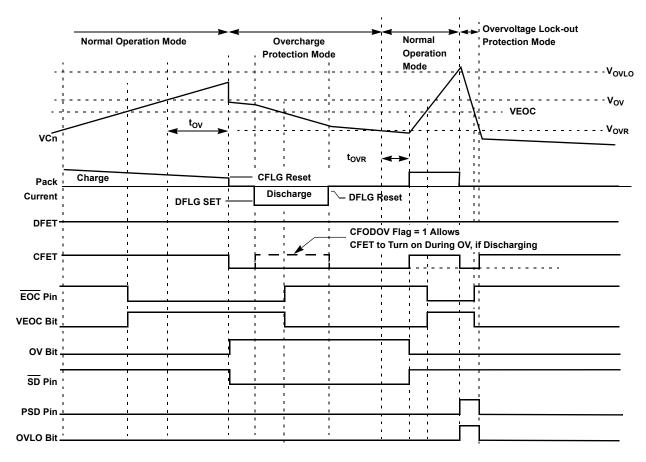

| 6.8          | OV Detection/Response           |     |

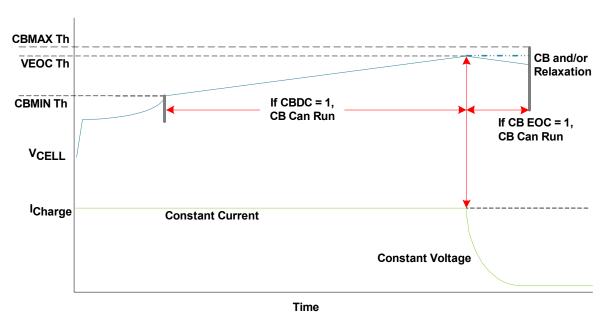

| 6.8.1        | VEOC                            |     |

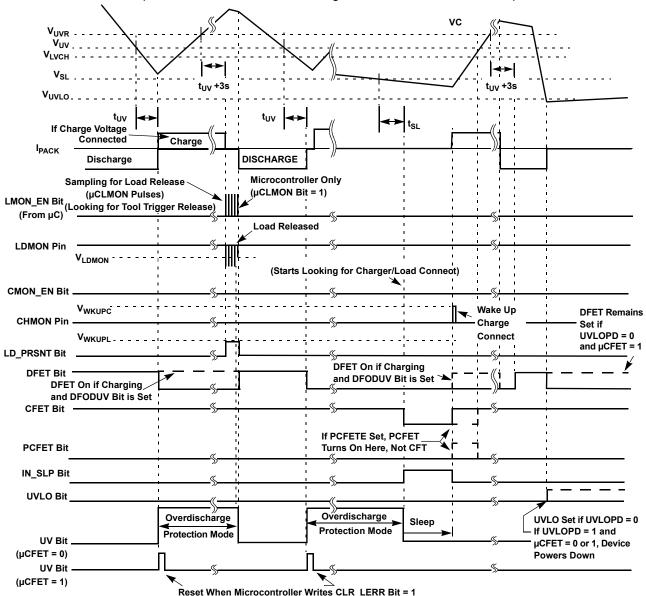

| 6.9          | UV Detection & Response         |     |

| 6.10         | Current Monitoring/Response     |     |

| 6.10.1       |                                 |     |

| 6.10         | 0.1.1 DOC and DSC Response      |     |

|              | 0.1.2 COC Response              |     |

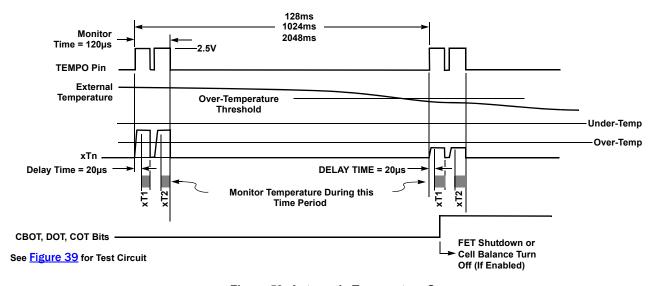

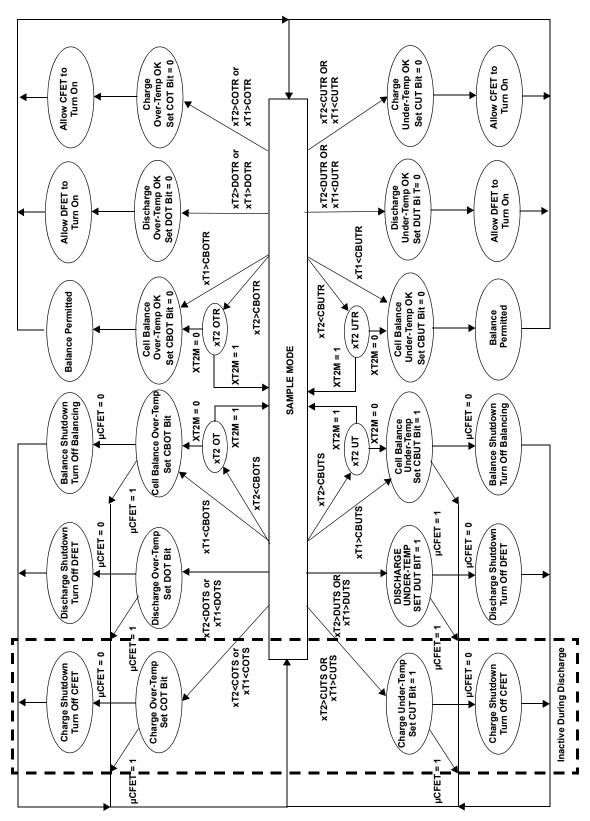

| 6.11         | Temperature Monitoring/Response | 135 |

| 6.11.1       |                                 |     |

| 6.11.2       |                                 |     |

| 6.11.3       | ·                               |     |

| 6.12         | Operational Options             |     |

| 6.12.1       | •                               |     |

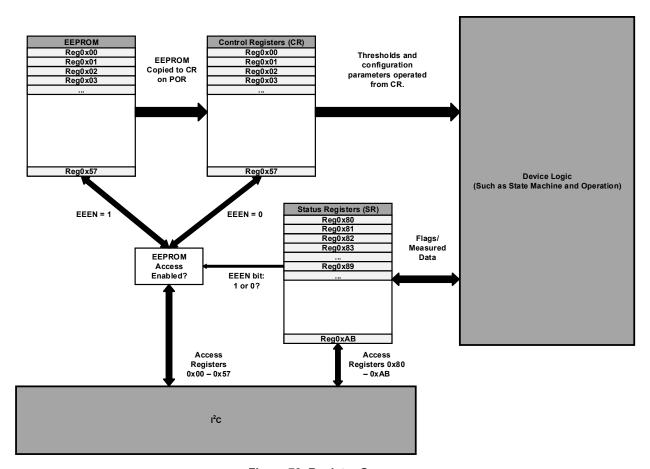

|              | 2.1.1 EEPROM                    |     |

| 6.12.2       |                                 |     |

| 6.12.3       |                                 |     |

| 6.12.4       | Mixed Control                   | 140 |

| 7. Co        | mmunication Interface           | 141 |

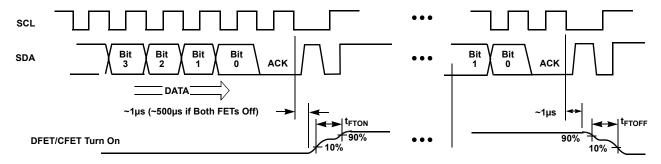

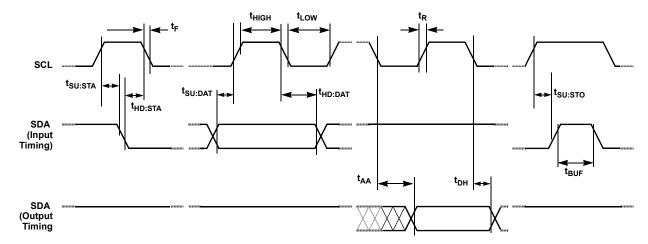

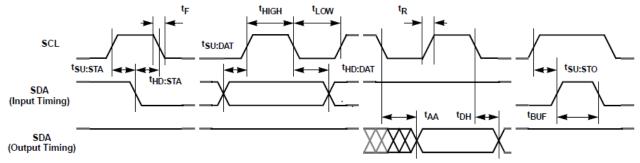

| 7.1          | I <sup>2</sup> C Interface      | 141 |

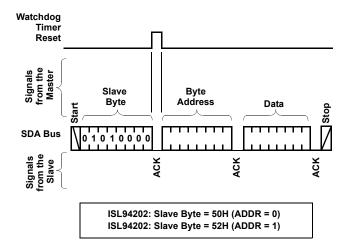

| 7.1.1        | I <sup>2</sup> C Address        |     |

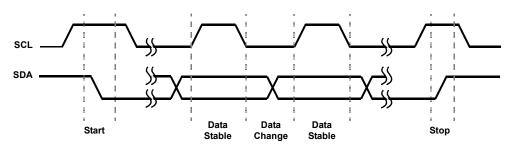

| 7.1.2        | Clock/Data Timing               |     |

| 7.1.3        | Start Condition                 |     |

| 7.1.4        | Stop Condition                  | 142 |

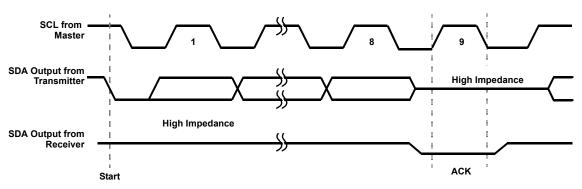

| 7.1.5        | Acknowledge                     | 143 |

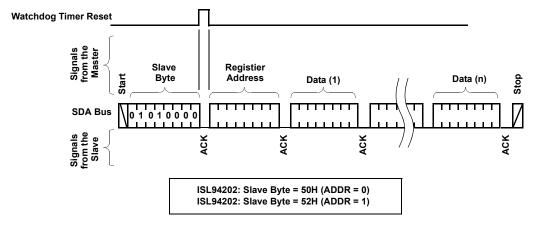

| 7.1.6        | Write Operation                 | 143 |

| 7.1.         | .6.1 Byte Write                 | 143 |

## ISL94202

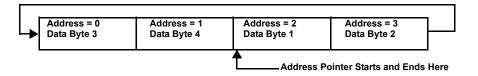

|     | 7.1.6.2 Page Write                              | 144 |

|-----|-------------------------------------------------|-----|

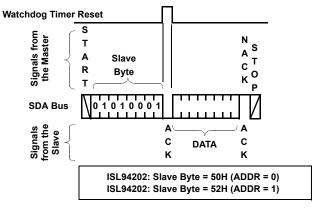

|     | 1.7 Read Operation                              | 146 |

|     | 7.1.7.1 Current Address Read                    | 146 |

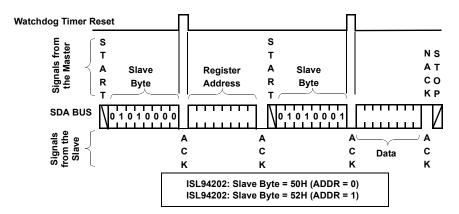

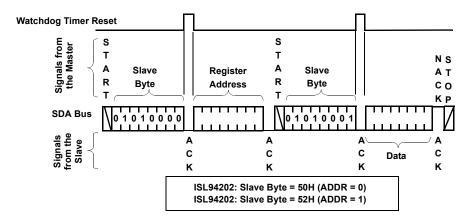

|     | 7.1.7.2 Random Read                             |     |

|     | 7.1.7.3 Sequential Read                         | 146 |

| 7.  | 1.8 EEPROM Access                               |     |

| 7.  | 1.9 EEPROM Read                                 | 148 |

| 7.  | 1.10 EEPROM Write                               | 148 |

|     | 7.1.10.1 Prepare the ISL94202                   | 148 |

|     | 7.1.10.2 Program EEPROM                         | 149 |

|     | 7.1.10.3 Verify EEPROM                          | 149 |

| 7.2 | Synchronizing MCU Operations with Internal Scan | 149 |

| 8.  | Reduced Cell Count                              | 150 |

| 9.  | Revision History                                | 151 |

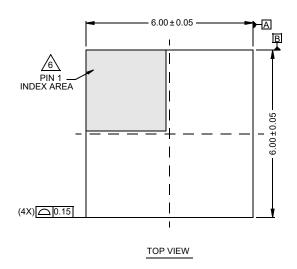

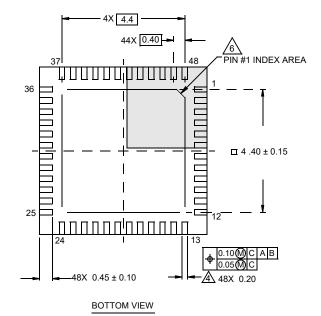

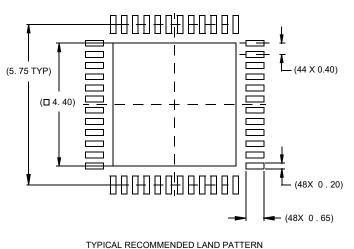

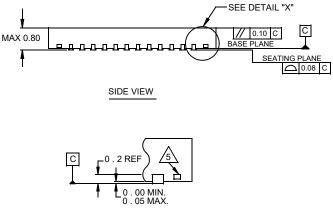

| 10. | Package Outline Drawing                         | 152 |

## 1. Overview

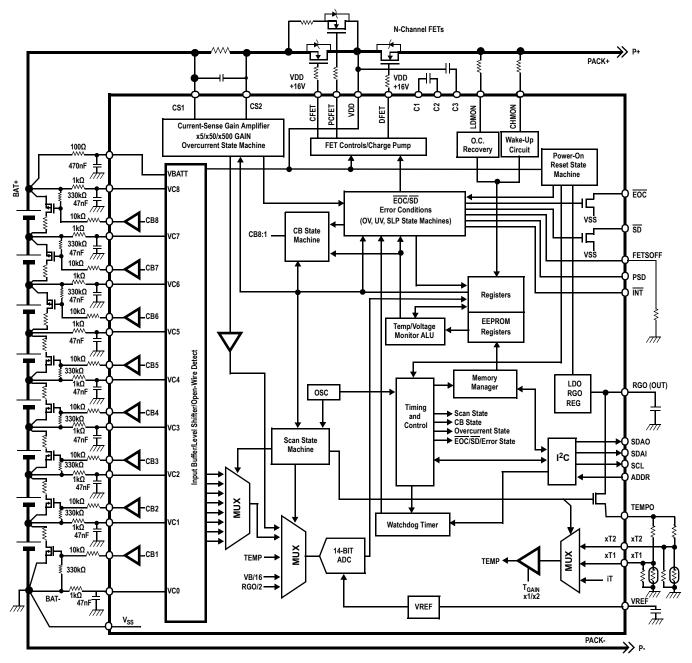

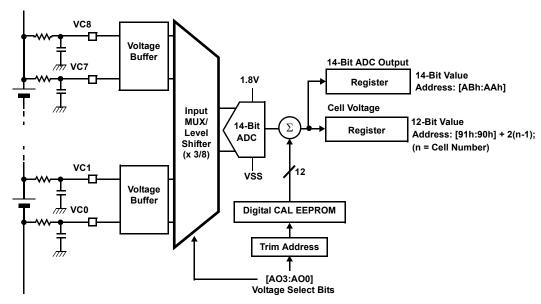

# 1.1 Block Diagram

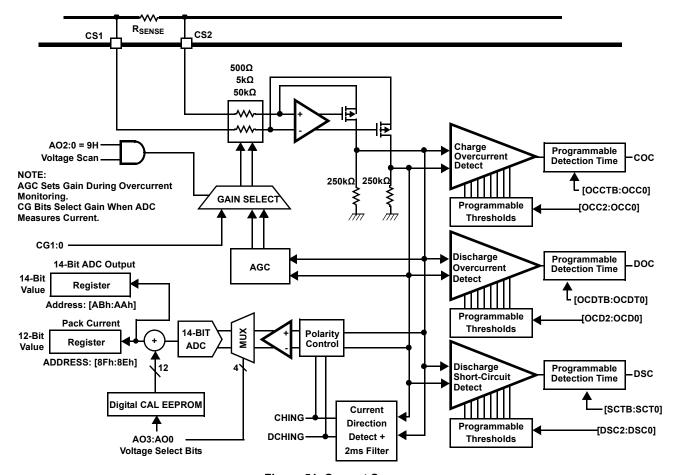

Figure 2. Block Diagram

## 1.2 Ordering Information

| Part Number<br>( <u>Notes 2, 3</u> ) | Part<br>Marking | Temp. Range<br>(°C) | Tape and Reel<br>(Units) (Note 1) | Package<br>(RoHS Compliant) | Pkg.<br>Dwg.# |

|--------------------------------------|-----------------|---------------------|-----------------------------------|-----------------------------|---------------|

| ISL94202IRTZ                         | 94202 IRTZ      | -40 to +85          | -                                 | 48 Ld TQFN                  | L48.6x6       |

| ISL94202IRTZ-T                       | 94202 IRTZ      | -40 to +85          | 4k                                | 48 Ld TQFN                  | L48.6x6       |

| ISL94202IRTZ-T7                      | 94202 IRTZ      | -40 to +85          | 1k                                | 48 Ld TQFN                  | L48.6x6       |

| ISL94202IRTZ-T7A                     | 94202 IRTZ      | -40 to +85          | 250                               | 48 Ld TQFN                  | L48.6x6       |

| ISL94202EVKIT1Z                      | Evaluation Kit  |                     |                                   |                             |               |

#### Notes

- 1. See <u>TB347</u> for details on reel specifications.

- These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations).

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC

J-STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the ISL94202 device page. For more information on MSL, see TB363.

Table 1. Key Differences Between Family of Parts

|                |     | ells<br>oorted | Vol        | ack<br>tage<br>Op) |                 |                |               | Charge/Discharge<br>FET |           |        |       |                  |                 |                |

|----------------|-----|----------------|------------|--------------------|-----------------|----------------|---------------|-------------------------|-----------|--------|-------|------------------|-----------------|----------------|

| Part<br>Number | Min | Max            | Min<br>(V) | Max<br>(V)         | Cell<br>Balance | IPack<br>Sense | Fuel<br>Gauge | Config.                 | Location  | Normal | Sleep | Standalone       | Internal<br>ADC | Daisy<br>Chain |

| ISL94202       | 3   | 8              | 4          | 36                 | External        | High<br>Side   | No            | Both                    | High Side | 348µA  | 13µA  | State<br>Machine | 14b             | No             |

| ISL94203       | 3   | 8              | 4          | 36                 | External        | High<br>Side   | No            | Parallel                | High Side | 348µA  | 13µA  | State<br>Machine | 14b             | No             |

| ISL94208       | 4   | 6              | 8          | 27                 | Internal        | Low<br>Side    | No            | Both                    | Low Side  | 850µA  | 2µA   | No               | N/A             | No             |

| ISL94212       | 6   | 12             | 6          | 60                 | External        | No             | No            | N/A                     | N/A       | 3.31mA | 12µA  | No               | 14b             | Yes            |

| RAJ240100      | 3   | 10             | 4          | 50                 | Both            | Low<br>Side    | Yes           | Both                    | High Side | 50μΑ   | 1µA   | Int MCU          | 18b             | No             |

| RAJ240090      | 3   | 8              | 4          | 50                 | Both            | Low<br>Side    | Yes           | Both                    | High Side | 50μΑ   | 1µA   | Int MCU          | 18b             | No             |

| RAJ240080      | 2   | 5              | 4          | 28                 | Both            | Low<br>Side    | Yes           | Both                    | High Side | 50μΑ   | 1µA   | Int MCU          | 18b             | No             |

# 1.3 Pin Configuration

# 1.4 Pin Descriptions

| Pin Number                          | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 3, 5, 7,<br>9, 11, 13,<br>15, 17 | VC[8:0] | <b>Battery Cell n voltage sense input.</b> These pins monitor the voltage of the battery pack cells. The voltage is level shifted to a ground reference and is monitored internally by an ADC converter. VCn connects to the positive terminal of a battery cell (CELLN) and VC(n-1) connects to the negative terminal of CELLN.                                                                                                                                                                             |  |  |  |

| 2, 4, 6, 8,<br>10, 12, 14, 16       | CB[8:1] | <b>Tell Balancing FET control output n.</b> An internal drive circuit controls an external FET that is used to diversortion of the current around a cell while the cell charges or adds to the current pulled from a cell during ischarge to perform a cell voltage balancing operation. This function is generally used to reduce the voltage in individual cell relative to other cells in the pack. The cell balancing FETs are turned on or off by an internal calance state machine or an external MCU. |  |  |  |

| 18, 28, 29                          | VSS     | <b>Ground</b> . This pin connects to the most negative terminal in the battery string. If separate analog and digita ground planes are used they should be connected together at the VSS pins.                                                                                                                                                                                                                                                                                                               |  |  |  |

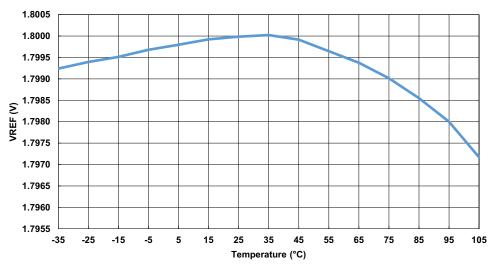

| 19                                  | VREF    | <b>Voltage Reference Output.</b> This output is the a 1.8V reference voltage used by the internal circuitry (ADC). I pin should not be loaded as this could cause significant ADC error. The VREF pin should be connected to G through a 1µF capacitor.                                                                                                                                                                                                                                                      |  |  |  |

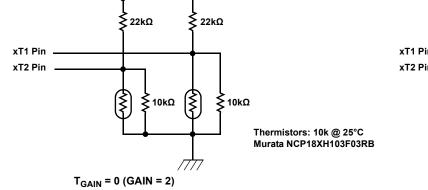

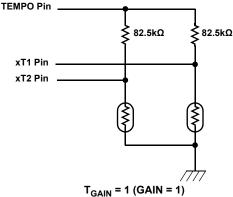

| 20                                  | XT1     | Temperature monitor inputs. These pins input the voltage across two external NTC thermistors used to                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 21                                  | XT2     | determine the temperature of the cells and or the power FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 22                                  | TEMPO   | <b>Temperature Monitor Output Reference.</b> This pin outputs a voltage to be used in a divider that consists fixed resistor and a thermistor. The thermistor is located in close proximity to the cells or a power FET. The TEMPO output is connected internally to the VRGO voltage through a PMOS switch only during a measur of the temperature, otherwise the TEMPO output is off.                                                                                                                      |  |  |  |

| 23, 30                              | DNC     | Do not connect, pin must be floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 24                                  | ADDR    | Serial Address. This is an address input for an I <sup>2</sup> C communication link to allow for two devices on one bus.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 25                                  | SCL     | Serial Clock. This is the clock input for an I <sup>2</sup> C communication link.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Pin Number | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 26         | SDAI    | <b>Serial Data.</b> These are the data lines for an I <sup>2</sup> C interface. When connected together, they form the standard                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 27         | SDAO    | bidirectional interface for the I <sup>2</sup> C bus (recommended).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 31         | ĪNT     | nterrupt. This pin goes active low when there is an external MCU connected to the ISL94202 and MCU communication fails to send a slave byte within a watchdog timer period. This is a CMOS type output.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 32         | PSD     | Pack Shutdown. This pin is set high when any cell voltage reaches the OVLO threshold (OVLO flag). Optionally, PSD is also set if there is a voltage differential between any two cells that is greater than a specified limit (CELLF flag) or if there is an open-wire condition. This pin can be used with external circuitry for blowing a fuse in the pack or as an interrupt to an external MCU.                                                                                                                                                                                 |  |  |  |  |  |

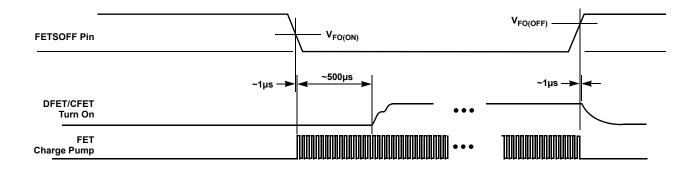

| 33         | FETSOFF | <b>FETSOFF.</b> This input allows an external MCU to turn off both Power FET and CB outputs. This pin should be pulled low when inactive or tied to ground if unused.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 34         | SD      | <b>Shutdown.</b> This output indicates that the ISL94202 detected a failure condition that would result in the DFET turning off. This could be undervoltage, over-temperature, under-temperature, etc. The SD pin also goes active if there is any charge overcurrent condition. This is an open-drain output.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 35         | EOC     | <b>End-of-Charge.</b> This output indicates that the ISL94202 detected a fully charged condition. This is defined by any cell voltage exceeding an EOC voltage (as defined by an EOC value in EEPROM).                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 36         | RGO     | Regulator Output. This is the 2.5V regulator output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

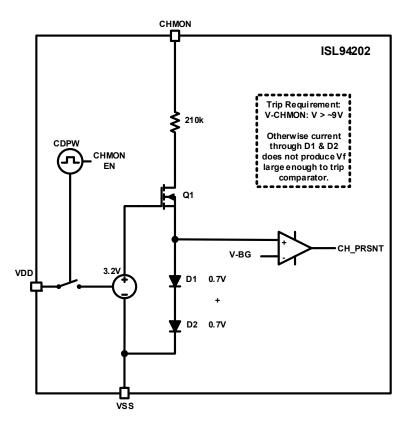

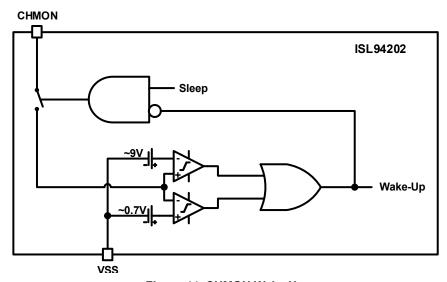

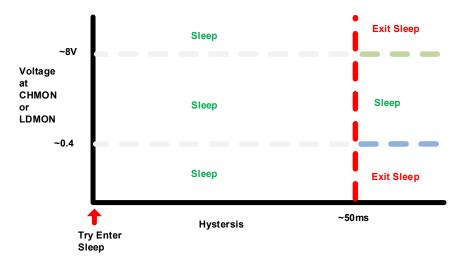

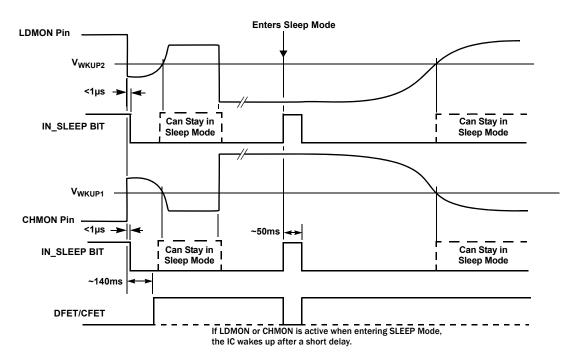

| 37         | CHMON   | <b>Charge Monitor.</b> This pin is used to detect a charger connection. When the IC is in the Powerdown State or SLEEP Mode, connecting this pin to the charger wakes up the device. When the IC recovers from a charge overcurrent condition, this pin is used to determine if the charger is removed prior to turning on the power FETs.                                                                                                                                                                                                                                           |  |  |  |  |  |

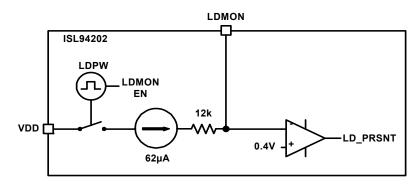

| 38         | LDMON   | <b>Load Monitor.</b> This pin is used to detect a load connection. When the IC is in the SLEEP Mode, connecting this pin to a load wakes up the device. When the IC recovers from a discharge overcurrent or short-circuit condition, this pin is used to determine if the load is removed prior to turning on the power FETs.                                                                                                                                                                                                                                                       |  |  |  |  |  |

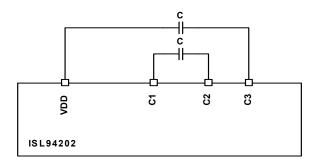

| 39, 40, 41 | C[3:1]  | Charge Pump Capacitors. These external capacitors are used by the charge pump to drive the power FETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

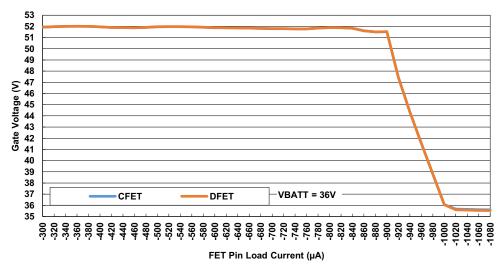

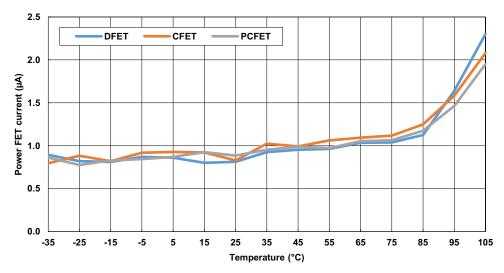

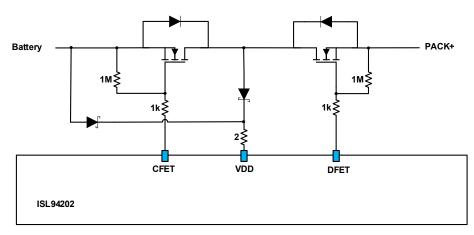

| 42         | DFET    | <b>Discharge FET Control.</b> The ISL94202 controls the gate of a Discharge N-channel FET through this pin. The FET is turned on by the ISL94202 if all conditions are acceptable. The ISL94202 turns off the FET if an out-of-bounds condition occurs. The FET can be turned off by an external MCU by writing to the DFET control bit. The DFET output is also turned off by the FETSOFF pin. The FET output cannot be turned on by an external MCU if there are any out-of-bounds conditions.                                                                                     |  |  |  |  |  |

| 43         | VDD     | Power Supply. This pin provides the operating voltage for the IC circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 44         | PCFET   | Precharge FET Control. The ISL94202 controls the gate of a Precharge N-channel FET through this pin. FET is turned on by the ISL94202 under precharge conditions, a trickle charge of the cells at the low end charge range. The ISL94202 turns off the FET if an out-of-bounds condition occurs. The FET can be turned by an external MCU by writing to the PCFET control bit. The PCFET output is also turned off by the FETS pin. The FET output cannot be turned on by an external MCU if there are any out-of-bounds conditions. E the PCFET or the CFET turn on, but not both. |  |  |  |  |  |

| 45         | CFET    | Charge FET Control. The ISL94202 controls the gate of a Charge N-channel FET through this pin. The turned on by the ISL94202 if all conditions are acceptable. The ISL94202 turns off the FET if an out-of-bo condition occurs. The FET can be turned off by an external MCU by writing to the CFET control bit. The Coutput is also turned off by the FETSOFF pin. The FET output cannot be turned on by an external MCU is are any out-of-bounds conditions. Either the PCFET or the CFET turn on, but not both.                                                                   |  |  |  |  |  |

| 46         | CSI2    | Current-Sense Inputs. These pins connect the ISL94202 current-sense circuit to the external sense resistor to                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 47         | CSI1    | measure the differential voltage. The sense resistor is typically in the range of $0.2m\Omega$ to $5m\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 48         | VBATT   | Input Level Shifter Supply and Battery Pack Voltage Input. This pin powers the input level shifters and is als used to monitor the voltage of the battery stack. The voltage is internally divided by 32 and connected to an AD converter through a MUX.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| PAD        | GND     | Thermal Pad. This pad should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

# 2. Specifications

# 2.1 Absolute Maximum Ratings

| Parameter                                                                 | Minimum   | Maximum (Note 4)     | Unit |  |

|---------------------------------------------------------------------------|-----------|----------------------|------|--|

| Power Supply Voltage, VDD                                                 | VSS - 0.5 | VSS+ 45.0            | V    |  |

| Cell Voltage (VC, VBATT)                                                  |           |                      | u .  |  |

| VCn                                                                       | -0.5      | VBATT + 0.5          | V    |  |

| VCn - VSS (n = 8)                                                         | -0.5      | 45.0                 | V    |  |

| VCn - VSS (n = 6, 7)                                                      | -0.5      | 36.0                 | V    |  |

| VCn - VSS (n = 4, 5)                                                      | -0.5      | 27.0                 | V    |  |

| VCn - VSS (n = 2, 3)                                                      | -0.5      | 17.0                 | V    |  |

| VCn - VSS (n = 1)                                                         | -0.5      | 7.0                  | V    |  |

| VCn - VSS (n = 0)                                                         | -0.5      | 3.0                  | V    |  |

| VCn - VC(n-1) (n = 2 to 12)                                               | -3.0      | 7.0                  | V    |  |

| VC1 - VC0                                                                 | -0.5      | 7.0                  | V    |  |

| Cell Balance Pin Voltages (VCB)                                           | <u> </u>  |                      | •    |  |

| VCBn - VC(n-1), n = 1 to 5                                                | -0.5      | 7.0                  | V    |  |

| VCn - VCBn, n = 6 to 8                                                    | -0.5      | 7.0                  | V    |  |

| Terminal Voltage                                                          | <u> </u>  |                      | •    |  |

| ADDR, xT1, xT2, FETSOFF, PSD, INT                                         | -0.5      | VRGO +0.5            | V    |  |

| SCL, SDAI, SDAO, $\overline{\overline{EOC}}$ , $\overline{\overline{SD}}$ | -0.5      | 5.5                  | V    |  |

| CFET, PCFET, C1, C2, C3                                                   | VDD - 0.5 | VDD + 15.5 (60V max) | V    |  |

| DFET, CHMON, LDMON                                                        | -0.5      | VDD + 15.0 (60V max) | V    |  |

| Terminal Current                                                          | <u> </u>  | -                    | !    |  |

| RGO                                                                       |           | 25                   | mA   |  |

| Current-Sense Voltage                                                     | <u> </u>  |                      | •    |  |

| VBATT, CS1, CS2                                                           | -0.5      | VDD +1.0             | V    |  |

| VBATT - CS1, VBATT - CS2                                                  | -0.5      | +0.5                 | V    |  |

| CS1 - CS2                                                                 | -0.5      | +0.5                 | V    |  |

| ESD Rating                                                                |           | Value                |      |  |

| Human Body Model (Tested per JS-001-2014)                                 |           | 1.5                  | kV   |  |

| Charged Device Model (Tested per JS-002-2014)                             |           | 1                    | kV   |  |

| Latch-Up (Tested per JESD78E; Class 2, Level A)                           |           | 100                  | mA   |  |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### Note

4. Devices are characterized, but not production tested, at Absolute Maximum Voltages.

## 2.2 Thermal Information

| Thermal Resistance (Typical)   | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------|------------------------|------------------------|

| 48 Ld QFN Package (Notes 5, 6) | 28                     | 0.75                   |

#### Notes:

5.  $\theta_{JA}$  is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

6. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                            | Minimum          | Maximum | Unit |  |  |  |  |  |

|--------------------------------------|------------------|---------|------|--|--|--|--|--|

| Continuous Package Power Dissipation |                  | 400     | mW   |  |  |  |  |  |

| Maximum Junction Temperature         |                  | +125    | °C   |  |  |  |  |  |

| Storage Temperature Range            | -55              | +125    | °C   |  |  |  |  |  |

| Pb-Free Reflow Profile               | see <u>TB493</u> |         |      |  |  |  |  |  |

# 2.3 Recommended Operating Conditions

| Parameter                            | Minimum | Maximum | Unit |

|--------------------------------------|---------|---------|------|

| Temperature Range                    | -40     | +85     | °C   |

| Operating Voltage                    |         |         |      |

| VDD                                  | 4V      | 36      | V    |

| VCn-VC(n-1) Specified Range          | 2.0     | 4.3     | V    |

| VCn-VC(n-1) Extended Range           | 1.0     | 4.4     | V    |

| VCn-VC(n-1) Maximum Range (any cell) | 0.5     | 4.8     | V    |

# 2.4 Electrical Specifications

$V_{DD}$  = 26.4V,  $T_A$  = -40°C to +85°C, unless otherwise specified. **Boldface specification limits apply across operating temperature range,** -40°C to +85°C.

| Parameter                                                                | Symbol                           | Test Conditions                                                                                | Min<br>( <u>Note 7</u> ) | Тур             | Max<br>( <u>Note 7</u> ) | Unit |

|--------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------|--------------------------|-----------------|--------------------------|------|

| Power-Up Condition – Threshold<br>Rising (Device becomes<br>operational) | (Device becomes operation begins |                                                                                                |                          | 6.0             |                          | V    |

|                                                                          | V <sub>PORR2</sub>               | CHMON minimum voltage at which device operation begins (CFET turns on; V <sub>DD</sub> > 6.0V) |                          | V <sub>DD</sub> |                          | V    |

| Powerdown Condition – Threshold Falling                                  | V <sub>PORF</sub>                | V <sub>DD</sub> minimum voltage device remains operational (RGO turns off)                     |                          | 3.0             |                          | V    |

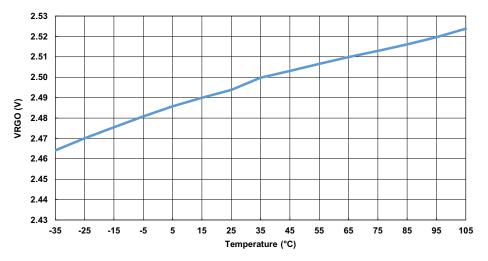

| 2.5V Regulated Voltage                                                   | $V_{RGO}$                        | I <sub>RGO</sub> = 3mA                                                                         | 2.4                      | 2.5             | 2.6                      | V    |

| 1.8V Reference Voltage                                                   | V <sub>REF</sub>                 |                                                                                                | 1.79                     | 1.8             | 1.81                     | V    |

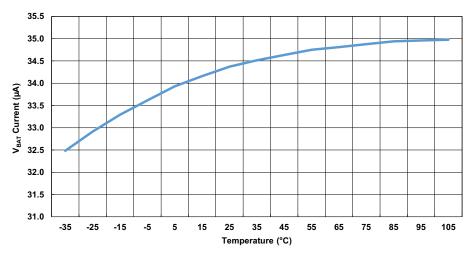

| VBATT Input Current - V <sub>BATT</sub>                                  | I <sub>VBATT</sub>               | Input current; NORMAL/IDLE/DOZE Modes V <sub>DD</sub> = 33.6V                                  |                          | 38              | 45                       | μΑ   |

|                                                                          |                                  | Input current; SLEEP/Powerdown Modes V <sub>DD</sub> = 33.6V                                   |                          |                 | 1                        | μА   |

$V_{DD}$  = 26.4V,  $T_A$  = -40°C to +85°C, unless otherwise specified. **Boldface specification limits apply across operating temperature range,** -40°C to +85°C. (Continued)

| Parameter                                                                                       | Symbol              | Test Conditions                                                                                                        | Min<br>( <u>Note 7</u> ) | Тур   | Max<br>( <u>Note 7</u> ) | Unit  |

|-------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|

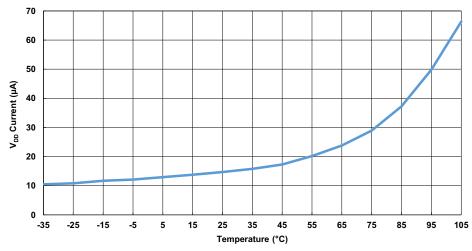

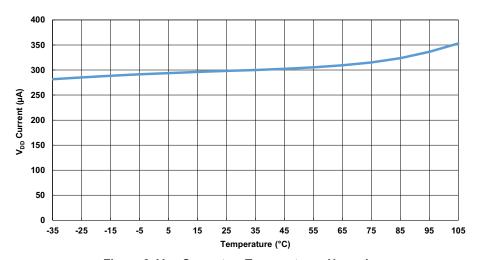

| V <sub>DD</sub> Supply Current                                                                  | I <sub>VDD1</sub>   | Device active (NORMAL Mode)<br>(No error conditions)<br>CFET, PCFET, DFET = OFF; V <sub>DD</sub> = 33.6V               |                          | 310   | 370                      | μА    |

|                                                                                                 | I <sub>VDD2</sub>   | Device active (IDLE Mode) (No error conditions) IDLE = 1 CFET, PCFET, DFET = OFF; V <sub>DD</sub> = 33.6V              |                          | 215   | 275                      | μА    |

|                                                                                                 | I <sub>VDD3</sub>   | Device active (DOZE Mode) (No error conditions) DOZE = 1 CFET, PCFET, DFET = OFF; V <sub>DD</sub> = 33.6V              |                          | 210   | 265                      | μА    |

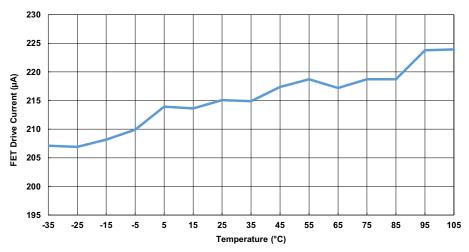

|                                                                                                 | I <sub>VDD4</sub>   | FET drive current<br>(I <sub>VDD</sub> increase when FETs are on -<br>NORMAL/IDLE/DOZE Modes); V <sub>DD</sub> = 33.6V |                          | 215   |                          | μА    |

|                                                                                                 | I <sub>VDD5</sub>   | Device active (SLEEP Mode);<br>SLEEP = 1; V <sub>DD</sub> = 33.6V                                                      |                          |       |                          |       |

|                                                                                                 |                     | 0°C to +60°C                                                                                                           |                          | 13    | 30                       | μA    |

|                                                                                                 |                     | -40°C to +85°C                                                                                                         |                          |       | 50                       | μA    |

|                                                                                                 | I <sub>VDD6</sub>   | Powerdown<br>PDWN = 1; V <sub>DD</sub> = 33.6V                                                                         |                          |       | 1                        | μΑ    |

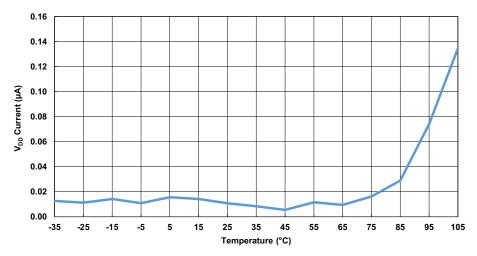

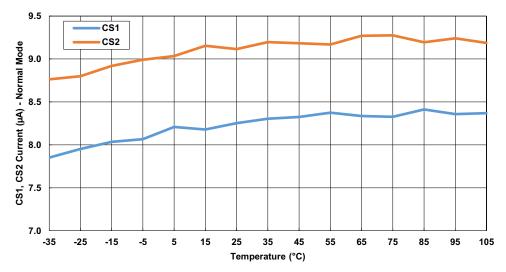

| Input Bias Current                                                                              | ICS1                | V <sub>DD</sub> = V <sub>BATT</sub> = VCS1 = VCS2 = 33.6V<br>(NORMAL, IDLE, DOZE)                                      |                          | 10    | 15                       | μА    |

|                                                                                                 |                     | V <sub>DD</sub> = V <sub>BATT</sub> = VCS1 = VCS2 = 33.6V<br>(SLEEP, Powerdown)                                        |                          |       |                          |       |

|                                                                                                 |                     | 0°C to +60°C                                                                                                           |                          |       | 1                        | μA    |

|                                                                                                 |                     | -40°C to +85°C                                                                                                         |                          |       | 3                        | μA    |

|                                                                                                 | ICS2                | V <sub>DD</sub> = V <sub>BATT</sub> = VCS1 = VCS2 = 33.6V<br>(NORMAL, IDLE, DOZE)                                      |                          | 10    | 15                       | μΑ    |

|                                                                                                 |                     | V <sub>DD</sub> = V <sub>BATT</sub> = VCS1 = VCS2 = 33.6V<br>(SLEEP, Powerdown)                                        |                          |       |                          |       |

|                                                                                                 |                     | 0°C to +60°C                                                                                                           |                          |       | 1                        | μA    |

|                                                                                                 |                     | -40°C to +85°C                                                                                                         |                          |       | 3                        | μA    |

| VCn Input Current                                                                               | I <sub>VCN</sub>    | Cell input leakage current AO2:AO0 = 0000H (NORMAL/IDLE/DOZE; not sampling cells)                                      | -1                       |       | 1                        | μА    |

| CBn Input Current                                                                               | I <sub>CBN</sub>    | Cell Balance pin leakage current (no balance active)                                                                   | -1                       |       | 1                        | μΑ    |

| Temperature Monitor Specification                                                               | ıs                  |                                                                                                                        |                          |       |                          | •     |

| External Temperature Accuracy                                                                   | V <sub>XT1</sub>    | External temperature monitoring error. ADC voltage error when monitoring xT1 input. TGain = 0; (xTn = 0.2V to 0.737V)  | -25                      |       | 15                       | mV    |

| Internal Temperature Monitor Output (See: <u>"Temperature</u> Monitoring/Response" on page 135) | T <sub>INT25</sub>  | [iTB:iT0] <sub>10</sub> *1.8/4095/GAIN<br>GAIN = 2 (TGain bit = 0)<br>Temperature = +25°C                              |                          | 0.276 |                          | V     |

|                                                                                                 | V <sub>INTMON</sub> | Change in<br>[iTB:iT0] <sub>10</sub> *1.8/4095/GAIN<br>GAIN = 2 (TGain bit = 0)<br>Temperature = -40°C to +85°C        |                          | 1.0   |                          | mV/°C |

$V_{DD}$  = 26.4V,  $T_A$  = -40°C to +85°C, unless otherwise specified. **Boldface specification limits apply across operating temperature range,** -40°C to +85°C. (Continued)

| Davamatav                                   | Symphol           | Toot Conditions                                                                                                                    | Min               | Turn  | Max               | Umit |

|---------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------|------|

| Parameter                                   | Symbol            | Test Conditions                                                                                                                    | ( <u>Note 7</u> ) | Тур   | ( <u>Note 7</u> ) | Unit |

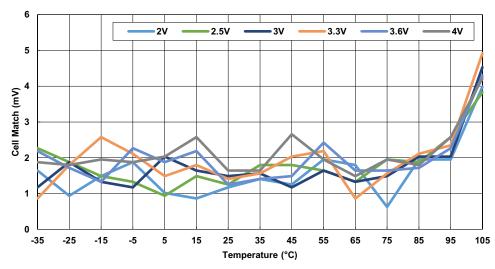

| Cell Voltage Monitor Specification          | _                 | T=                                                                                                                                 |                   | 1 1   |                   |      |

| Cell Monitor Voltage Accuracy (Relative)    | V <sub>ADCR</sub> | Relative cell measurement error (Maximum absolute cell measurement error                                                           |                   |       |                   |      |

|                                             |                   | Minimum absolute cell measurement error)                                                                                           |                   |       |                   |      |

|                                             |                   | VCn -VC(n-1) = 2.4V to 4.2V; 0°C to +60°C                                                                                          |                   | 3     | 10                | mV   |

|                                             |                   | VCn -VC(n-1) = 0.1V to 4.7V; 0°C to +60°C                                                                                          |                   |       | 15                | mV   |

|                                             |                   | VCn -VC(n-1) = 0.1V to 4.7V; -40°C to +85°C                                                                                        |                   |       | 30                | mV   |

| Cell Monitor Voltage Accuracy<br>(Absolute) | V <sub>ADC</sub>  | Absolute cell measurement error (Cell measurement error compared with voltage at the cell)                                         |                   |       |                   |      |

|                                             |                   | VCn - VC(n-1) = 2.4V to 4.2V; 0°C to +60°C                                                                                         | -15               |       | 15                | mV   |

|                                             |                   | VCn - VC(n-1) = 0.1V to 4.7V; 0°C to +60°C                                                                                         | -20               |       | 20                | mV   |

|                                             |                   | VCn - VC(n-1) = 0.1V to 4.7V; -40°C to +85°C                                                                                       | -30               |       | 30                | mV   |

| V <sub>BATT</sub> Voltage Accuracy          | $V_{BATT}$        | V <sub>BATT</sub> - [VBB:VB0] <sub>10</sub> *32*1.8/4095;                                                                          |                   |       |                   |      |

|                                             |                   | 0°C to +60°C                                                                                                                       | -200              |       | 200               | mV   |

|                                             |                   | -40°C to +85°C                                                                                                                     | -270              |       | 270               | mV   |

| Current-Sense Amplifier Specific            | ations            |                                                                                                                                    |                   | 1     |                   | 1    |

| Charge Current Threshold                    | VCCTH             | VCS1-VCS2, CHING set (charging)                                                                                                    |                   | -100  |                   | μV   |

| Discharge Current Threshold                 | VDCTH             | VCS1-VCS2, DCHING set (discharging)                                                                                                |                   | 100   |                   | μV   |

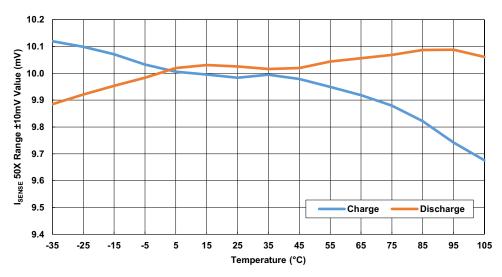

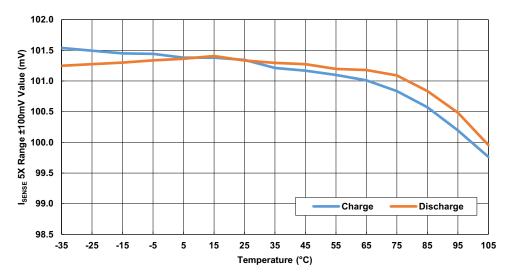

| Current-Sense Accuracy                      | VIA1              | V <sub>IA1</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/5;<br>CHING bit set; Gain = 5<br>VCS1 = 26.4V, VCS2 - VCS1 = + 100mV    | 97                | 102   | 107               | mV   |

|                                             | VIA2              | V <sub>IA2</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/5;<br>DCHING bit set; Gain = 5<br>VCS1 = 26.4V, VCS2 - VCS1 = - 100mV   | -107              | -102  | -97               | mV   |

|                                             | VIA3              | V <sub>IA3</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/50;<br>CHING bit set; Gain = 50<br>VCS1 = 26.4V, VCS2 - VCS1 = + 10mV   | 8.0               | 10.0  | 12.0              | mV   |

|                                             | VIA4              | V <sub>IA4</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/50;<br>DCHING bit set; Gain = 50<br>VCS1 = 26.4V, VCS2 - VCS1 = - 10mV  | -12.0             | -10.0 | -8.0              | mV   |

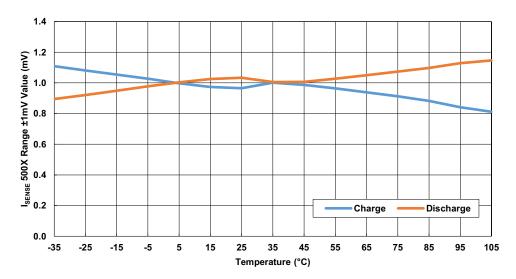

|                                             | VIA5              | V <sub>IA3</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/500;<br>CHING bit set; Gain = 500<br>VCS1 = 26.4V, VCS2 - VCS1 = + 1mV  |                   |       |                   |      |

|                                             |                   | 0°C to +60°C                                                                                                                       | 0.5               | 1.0   | 1.5               | mV   |

|                                             |                   | -40°C to +85°C                                                                                                                     | 0.4               |       | 1.6               | mV   |

|                                             | VIA6              | V <sub>IA4</sub> = ([ISNSB:ISNS0] <sub>10</sub> *1.8/4095)/500;<br>DCHING bit set; Gain = 500<br>VCS1 = 26.4V, VCS2 - VCS1 = - 1mV |                   |       |                   |      |

|                                             |                   | 0°C to +60°C                                                                                                                       | -1.5              | -1.0  | -0.5              | mV   |

|                                             |                   | -40°C to +85°C                                                                                                                     | -1.6              |       | -0.4              | mV   |

$V_{DD}$  = 26.4V,  $T_A$  = -40°C to +85°C, unless otherwise specified. **Boldface specification limits apply across operating temperature range,** -40°C to +85°C. (Continued)

| Parameter                                        | Symbol             | Test Conditions                                                                                        | Min<br>( <u>Note 7</u> ) | Тур  | Max<br>( <u>Note 7</u> ) | Unit |

|--------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|

| Overcurrent/Short-Circuit Protection             | on Specific        | cations                                                                                                |                          | J    |                          | ,L   |

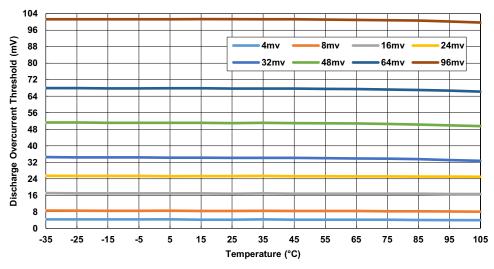

| Discharge Overcurrent Detection                  | V <sub>OCD</sub>   | V <sub>OCD</sub> = 4mV [OCD2:0] = 0,0,0                                                                | 2.6                      | 4.0  | 5.4                      | mV   |

| Threshold                                        |                    | V <sub>OCD</sub> = 8mV [OCD2:0] = 0,0,1                                                                | 6.4                      | 8.0  | 9.6                      | mV   |

|                                                  |                    | V <sub>OCD</sub> = 16mV [OCD2:0] = 0,1,0                                                               | 12.8                     | 16.0 | 19.2                     | mV   |

|                                                  |                    | V <sub>OCD</sub> = 24mV [OCD2:0] = 0,1,1                                                               | 20                       | 25   | 30                       | mV   |

|                                                  |                    | V <sub>OCD</sub> = 32mV [OCD2:0] = 1,0,0 (default)                                                     | 26.4                     | 33.0 | 39.6                     | mV   |

|                                                  |                    | V <sub>OCD</sub> = 48mV [OCD2:0] = 1,0,1                                                               | 42.5                     | 50.0 | 57.5                     | mV   |

|                                                  |                    | V <sub>OCD</sub> = 64mV [OCD2:0] = 1,1,0                                                               | 60.3                     | 67.0 | 73.7                     | mV   |

|                                                  |                    | V <sub>OCD</sub> = 96mV [OCD2:0] = 1,1,1                                                               | 90                       | 100  | 110                      | mV   |

| Discharge Overcurrent Detection<br>Time          | t <sub>OCDT</sub>  | [OCDTA:OCDT0] = 0A0H (160ms) (default)<br>Range:<br>0ms to 1023ms 1ms/step<br>0s to 1023s; 1s/step     |                          | 160  |                          | ms   |

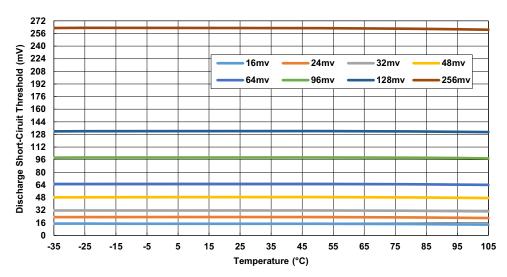

| Short-Circuit Detection Threshold                | V <sub>SCD</sub>   | V <sub>SCD</sub> = 16mV [SCD2:0] = 0,0,0                                                               | 10.4                     | 16.0 | 21.6                     | mV   |

|                                                  |                    | V <sub>SCD</sub> = 24mV [SCD2:0] = 0,0,1                                                               | 18                       | 24   | 30                       | mV   |

|                                                  |                    | V <sub>SCD</sub> = 32mV [SCD2:0] = 0,1,0                                                               | 26                       | 33   | 40                       | mV   |

|                                                  |                    | V <sub>SCD</sub> = 48mV [SCD2:0] = 0,1,1                                                               | 42                       | 49   | 56                       | mV   |

|                                                  |                    | V <sub>SCD</sub> = 64mV [SCD2:0] = 1,0,0                                                               | 60                       | 67   | 74                       | mV   |

|                                                  |                    | V <sub>SCD</sub> = 96mV [SCD2:0] = 1,0,1 (default)                                                     | 90                       | 100  | 110                      | mV   |

|                                                  |                    | V <sub>SCD</sub> = 128mV [SCD2:0] = 1,1,0                                                              | 127                      | 134  | 141                      | mV   |

|                                                  |                    | V <sub>SCD</sub> = 256mV [SCD2:0] = 1,1,1                                                              | 249                      | 262  | 275                      | mV   |

| Short-Circuit Current Detection Time             | t <sub>SCT</sub>   | [SCTA:SCT0] = 0C8H (200µs) (default)<br>Range:<br>0µs to 1023µs; 1µs/step<br>0ms to 1023ms 1ms/step    |                          | 200  |                          | μs   |

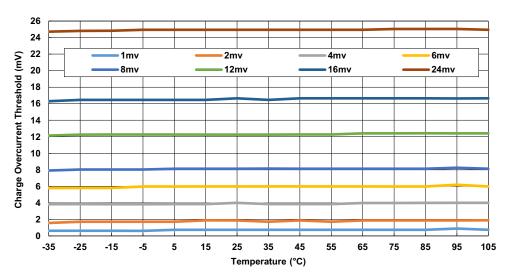

| Charge Overcurrent Detection                     | V <sub>occ</sub>   | V <sub>OCC</sub> = 1mV [OCC2:0] = 0,0,0                                                                | 0.2                      | 1.0  | 2.1                      | mV   |

| Threshold                                        |                    | V <sub>OCC</sub> = 2mV [OCC2:0] = 0,0,1                                                                | 0.7                      | 2.0  | 3.3                      | mV   |

|                                                  |                    | V <sub>OCC</sub> = 4mV [OCC2:0] = 0,1,0                                                                | 2.8                      | 4.0  | 5.2                      | mV   |

|                                                  |                    | V <sub>OCC</sub> = 6mV [OCC2:0] = 0,1,1                                                                | 4.5                      | 6.0  | 7.5                      | mV   |

|                                                  |                    | V <sub>OCC</sub> = 8mV [OCC2:0] = 1,0,0 (default)                                                      | 6.6                      | 8.0  | 9.8                      | mV   |

|                                                  |                    | V <sub>OCC</sub> = 12mV [OCC2:0] = 1,0,1                                                               | 9.6                      | 12.0 | 14.4                     | mV   |

|                                                  |                    | V <sub>OCC</sub> = 16mV [OCC2:0] = 1,1,0                                                               | 14.5                     | 17.0 | 19.6                     | mV   |

|                                                  |                    | V <sub>OCC</sub> = 24mV [OCC2:0] = 1,1,1                                                               | 22.5                     | 25.0 | 27.5                     | mV   |

| Overcurrent Charge Detection Time                | t <sub>OCCT</sub>  | [OCCTA:OCCT0] = 0A0H (160ms) (default)<br>Range:<br>0ms to 1023ms 1ms/step<br>0s to 1023s; 1s per step |                          | 160  |                          | ms   |

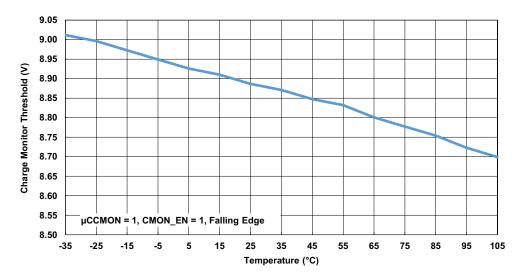

| Charge Monitor Input Threshold<br>(Falling Edge) | V <sub>CHMON</sub> | μCCMON bit = 1; CMON_EN bit = 1                                                                        | 8.2                      | 8.9  | 9.8                      | V    |

| Load Monitor Input Threshold<br>(Rising Edge)    | V <sub>LDMON</sub> | μCLMON bit = 1; LMON_EN bit = 1                                                                        | 0.45                     | 0.60 | 0.75                     | V    |

| Load Monitor Output Current                      | I <sub>LDMON</sub> | μCLMON bit = 1; LMON_EN bit = 1                                                                        |                          | 62   |                          | μΑ   |

$V_{DD}$  = 26.4V,  $T_A$  = -40°C to +85°C, unless otherwise specified. **Boldface specification limits apply across operating temperature range,** -40°C to +85°C. (Continued)

| Parameter                                                                    | Symbol                                               | Test Conditions                                                                                                     | Min<br>( <u>Note 7</u> ) | Тур              | Max<br>( <u>Note 7</u> ) | Unit |

|------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|--------------------------|------|

| Voltage Protection Specifications                                            |                                                      |                                                                                                                     |                          |                  |                          | •    |

| Overvoltage Lockout Threshold (Rising Edge - Any Cell) [VCn-VC(n-1)]         | V <sub>OVLO</sub>                                    | [OVLOB:OVLO0] = 0E80H (4.35V) (default)<br>Range: 12-bit value (0V to 4.8V)                                         |                          | 4.35             |                          | V    |

| Overvoltage Lockout Recovery<br>Threshold - All Cells                        | V <sub>OVLOR</sub>                                   | Falling edge                                                                                                        |                          | V <sub>OVR</sub> |                          | ٧    |

| Undervoltage Lockout Threshold<br>(Falling Edge - Any Cell)<br>[VCn-VC(n-1)] | V <sub>UVLO</sub>                                    | [UVLOB:UVLO0] = 0600H (1.8V) (default)<br>Range: 12-bit value (0V to 4.8V)                                          |                          | 1.8              |                          | ٧    |

| Undervoltage Lockout Recovery<br>Threshold - All Cells                       | V <sub>UVLOR</sub>                                   | Rising edge                                                                                                         |                          | V <sub>UVR</sub> |                          | ٧    |

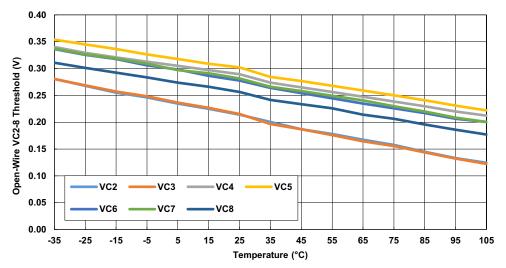

| Overvoltage Lockout Detection Time                                           | t <sub>OVLO</sub>                                    | NORMAL Mode 5 consecutive samples over the limit (minimum = 160ms, maximum = 192ms)                                 |                          | 176              |                          | ms   |