NOT RECOMMENDED FOR NEW DESIGNS

USE DROP IN REPLACEMENT ISL94202. EXISTING

CUSTOMERS WILL CONTINUE TO RECEIVE SUPPORT

https://www.renesas.com/support/contact.html

ISL94203EVKIT1Z

User's Manual: Evaluation Kit

**Battery and Optical**

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

# ISL94203EVKIT1Z

**Evaluation Kit**

## 1. Overview

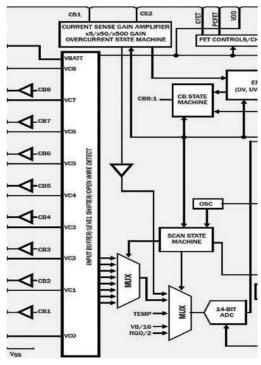

The ISL94203EVKIT1Z evaluation kit facilitates testing of the ISL94203 Li-ion battery pack monitor and control ICs. The <u>ISL94203</u> monitors cell voltage, current, and temperature. It converts the cell voltages, pack current, and temperatures to 12-bit digital values, provides cell balance control, and provides complete stand-alone battery pack operation.

The ISL94203 default stand-alone operation can be overridden by an external microcontroller. The PC graphical user interface (GUI) supports the hooks needed to monitor stand-alone operation and to demonstrate operation with an external microcontroller.

# 1.1 Key Features

- · Status LEDs monitor RGO, EOC, SD, and PSD conditions

- · Jumper configuration single or split path applications

- Wakeup push button for Exit Sleep control

- · FETs off push button for quick all FETs off condition

- · Cell balance LEDs for MCB process observation

- · PCB layout accommodates solder braid addition for high current evaluation

- Software enables real-time observation and data collection of 14 analog measurements and 27 digital status indicators

# 1.2 Specifications

- This board has been configured and optimized for the following operating conditions:

- · Configurable to 3 to 8 cells, default 3 cells

- Standard cell voltage range 2.699V to 4.250V

- · OV delay time of 1 second

- · UV delay time of 4 seconds

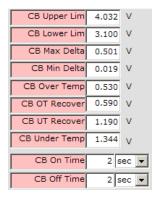

- · CB max delta voltage 0.501

- CB max/min voltage 4.032V and 3.100V

Note: Consult programming options for full listing of programmable parameters and ranges.

# 1.3 Ordering Information

| Part Number     | Description                     |

|-----------------|---------------------------------|

| ISL94203EVKIT1Z | Evaluation kit for the ISL94203 |

## 1.4 Related Literature

For a full list of related documents, visit our website:

• ISL94203 device page

## 1.5 What is Inside the Evaluation Kit

- · ISL94203 evaluation board

- MCB\_PS\_Z multicell power supply test board

- ISL94203INTFACEKIT1Z USB to I<sup>2</sup>C interface kit, includes a PCB and I<sup>2</sup>C cable

- USB cable, connects PC to USB-I<sup>2</sup>C interface board

ISL94203EVKIT1Z 1. Overview

## 1.6 What is Needed

The following instruments are required to perform testing:

- · 30V/1A adjustable power supply

- Wires to connect power supply to MCB\_PS\_Z board

- · Precision multimeter (optional)

- Oscilloscope (optional)

- · Cables and wires (optional)

#### 1.7 Software Installation

- 1. Connect the ISL94203INTFACEKIT1Z to the PC through the USB port. The board should automatically enumerate in the device control panel under Human Interface Devices. The vendor ID is 0x09AA and the product ID is 0x2036. Because it is a HID device, no special driver is needed.

- 2. Copy the isl94203evkit1z-software.exe program to the PC (any desired location). Double-click to run the installation file. **Note:** you might need to have "Run as Administrator" open when performing the installation.file.

# 1.8 Quick Hardware Setup Guide

- 1. Check the jumpers and switches on the board. The board should be configured as follows:

- a. ADDR jumper set to 0"

- b. xT2 Select jumper on either CELL or FET.

- c. FET jumpers set for either one path or two path. Start with one path.

- d. J<sub>4</sub> jumper is set to 1 Path.J<sub>9</sub> jumper is set to 1 Path.

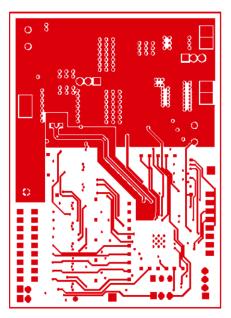

- 2. Connect the power supply to the MCB\_PS\_Z board. The positive terminal is  $J_5/J_{11}$  and the negative terminal is  $J_8/J_{12}$ . There should be a jumper on  $J_{13}$  as shown in Figure 2 on page 5.

- 3. Set the power supply voltage to 28V (3.5V per cell). (Optional: check that the voltages at terminal  $J_1$  or  $J_3$  are 3.5V per cell).

- 4. Turn off the power to the power supply.

- 5. Connect the ISL94203 board directly to the MCB\_PS\_Z board at connector J<sub>1</sub>. Make sure the board is connected on the ground side of J<sub>1</sub> (see <u>Figure 2</u>).

- 6. Turn on the power to the supply. If no LEDs light, press the **WakeUp** button. Notice that there is one green LED (RGO) indicating that the LDO regulator on the ISL94203 is operating.

The voltages at various points should be:

```

RGO = 2.5V \pm 3\%

```

$V_{REF} = 1.80V \pm 0.5\%$

- 7. Connect the USB port of the PC to the USB port of the ISL94203INTFACEKIT1Z interface board.

- 8. Connect the I<sup>2</sup>C cable from the ISL94203INTFACEKIT1Z board to the ISL94203EVKIT1Z board (J<sub>13</sub>).

- 9. Open the ISL94203 GUI software 1.7. Use the software to read the cell voltages.

- 10. Compare the voltages at the board input (use a meter to measure each input voltage, because the MCB\_PS\_Z board might not accurately divide the voltages into equal 3.5V steps) with the readings provided by the GUI. These voltages should closely match.

- 11. See other operations described later in this document.

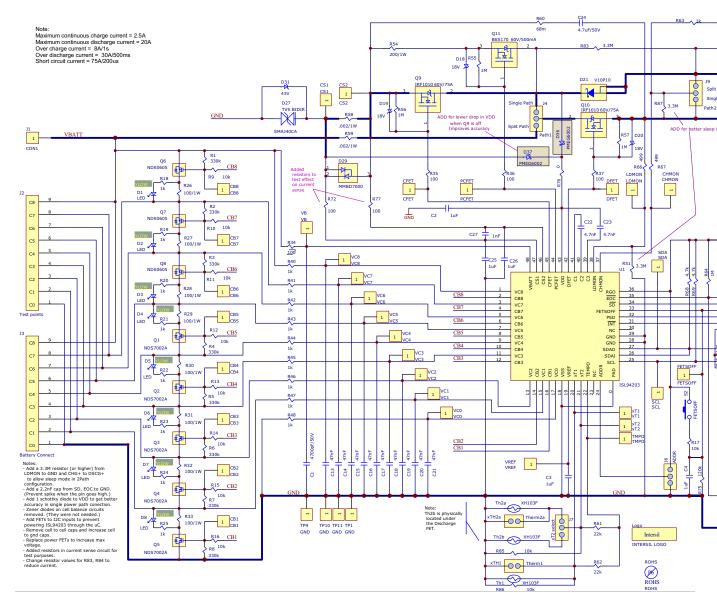

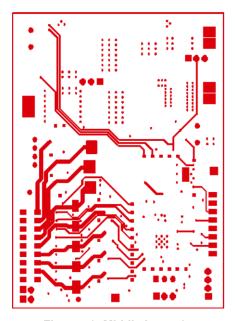

# 2. PCB Layout Guidelines

The AC performance of this circuit depends greatly on the care taken in designing the PC board. The following are recommendations to achieve optimum high performance from your PC board:

- The use of low inductance components, such as chip resistors and chip capacitors, is strongly recommended.

- Minimize signal trace lengths. This is especially true for the VDD, charge pump decoupling, C<sub>S1</sub>, C<sub>S2</sub>, and VC0-VC8 inputs. Trace inductance and capacitance can easily affect circuit performance. Vias in the signal lines add inductance at high frequency and should be avoided.

- Match channel-to-channel analog I/O trace lengths and layout symmetry. This is especially true for the  $C_{S1}$  and  $C_{S2}$  lines, because their inputs are normally very low voltage.

- Maximize use of AC decoupled PCB layers. All signal I/O lines should be routed over continuous ground planes (that is, no split planes or PCB gaps under these lines). Avoid vias in the signal I/O lines.

- When testing, use good quality connectors and cables, matching cable types and keep cable lengths to a minimum.

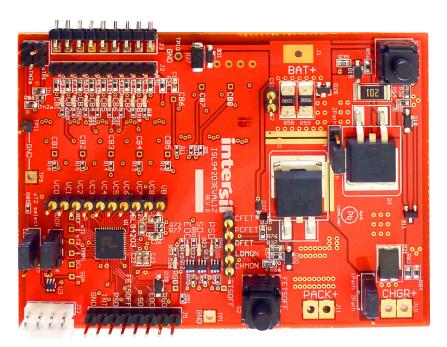

Figure 1. ISL94203EVKIT1Z Evaluation Board

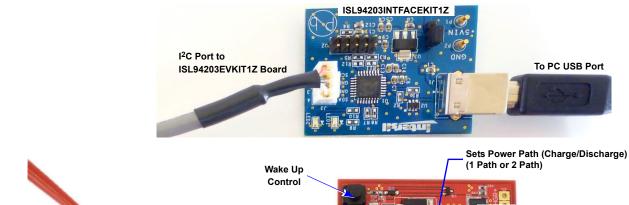

Figure 2. ISL94203EVKIT1Z Board Setup

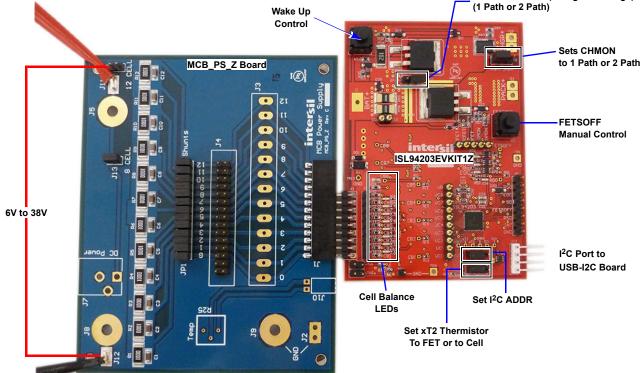

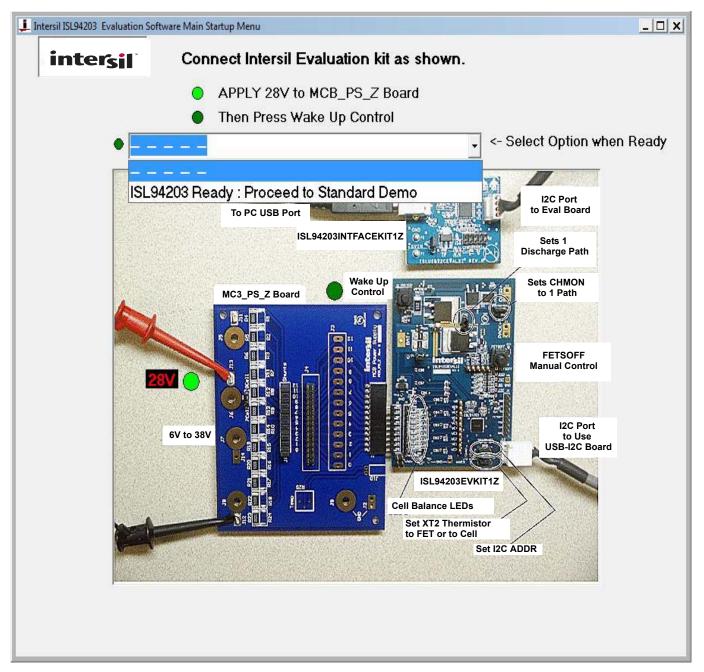

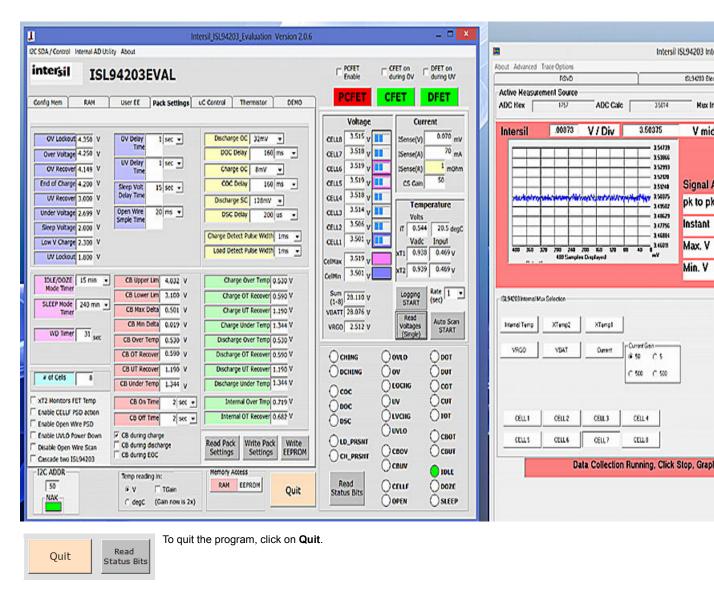

# 3. Quick GUI Setup Guide

1. When the board is powered up and connected to the PC through the USB cable, start the GUI program and click on the dropdown box.

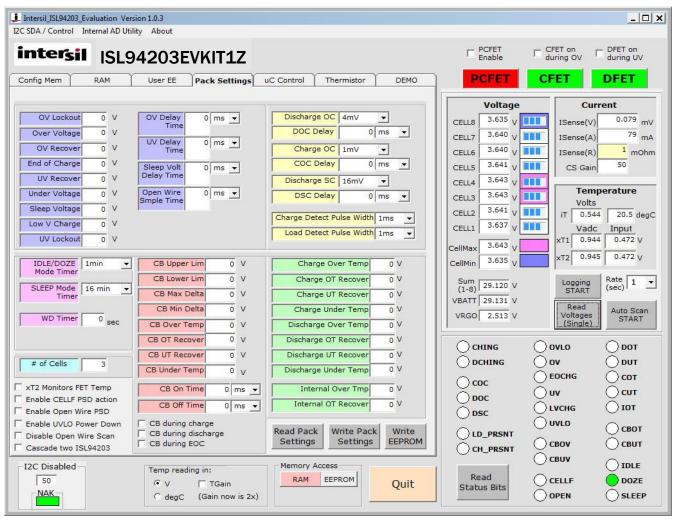

Figure 3. Main GUI Start-Up Window

- 2. Click on **Read Voltages (Single)**. This updates all the cell voltages, temperature and current readings, and updates the status indicators.

- 3. Click on Read Pack Settings. This returns the configuration parameters set in the device.

- 4. Review the operation of the GUI features in the following sections.

Figure 4. Main GUI Window Showing Pack Settings

# 4. Using the GUI

## 4.1 Common Screen

The right side of the GUI shows the status of the ISL94203. At the top are voltage, current, and temperature readings. The bottom shows the status bits.

At the bottom of the screen are several controls for temperature settings and memory access.

# 4.1.1 CELL Voltage Scans

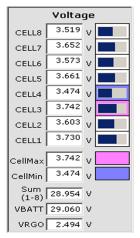

The voltage readouts (Figure 5) show the values for each cell, plus CELLMAX and CELLMIN values. The CELLMAX and CELLMIN values are returned from the ISL94203 registers. To properly implement this operation, the GUI stops the internal voltage scan of the ISL94203 (using the µCSCAN bit). It reads the cell voltages and CELLMAX and CELLMIN values and restarts the automatic scan of the device. The values are read asynchronously, so without stopping the scan there is not sufficient time to read all the values prior to the next internal scan. For this reason, the CELLMIN and CELLMAX values are often reported from a different scan than the rest of the cell voltages. Also, during the scan, the cell balance operation is stopped. The operation stops so that the cell balance currents do not cause false readings of the cell voltages, due to external voltage drops.

Figure 5. Voltage Readouts

To the right of the cell voltages, there is a graphic indication of the capacity of the cell. This is based on the voltage of the cell. In this graphic depiction, the scale shows no bar when the voltage is less than or equal to the undervoltage threshold. It shows 100%, or maximum, when the cell voltage is equal to or greater than the overvoltage threshold. See the overvoltage and undervoltage thresholds in the Pack settings tab on the left of the screen.

The GUI highlights the specific cells that equal the CELLMAX and CELLMIN voltages. This helps to identify which cells are high or low on quick inspection.

When any cell voltage is lower than the undervoltage level, or higher than the overvoltage level, the background color of that voltage readout changes to red. When the voltage rises above the UV recovery voltage or drops below the OV recovery voltage the background color returns to white. These color changes are GUI representations of the cell voltage conditions, the actual indication from the device is shown by the UV and OV status indicators (bottom right of the screen). These indicators come directly from the device status bits.

Below the CellMIN and CellMAX readings are three boxes that show additional voltage values. The top box contains the sum of the individual cell readings. The middle box shows the voltage reading of the total battery pack as derived from an internal divide by 16 voltage divider and converted by the ADC. Comparing these two values allows a gross determination if there is a cell voltage failure.

The bottom box shows the voltage of the 2.5V regulator. The regulator voltage is internally divided by 2, converted by the ADC, and multiplied by 2 prior to display.

Pressing the **Read Voltages (Single)** button completes one read of the values in the device, (see <u>Figure 6</u>). This includes all of the voltages and the status bits. Between presses of this button, the device continues to scan the voltage, current and temperature values at the rate of 32ms (or 256ms if in IDLE mode, or 512ms if in DOZE mode).

Figure 6.

Pressing the **Auto Scan START** button starts a repetitive update of the values. The rate of update is set by the **Rate (sec)** dropdown box. As shown, the GUI updates the voltages and status every 1 second. Autoscan is stopped by pressing the autoscan **STOP** button. While the autoscan is operating, all other memory accesses are prohibited. To read the pack settings or change a register value, first stop the automatic scan.

To log the data, press **Logging START** prior to clicking on the **Auto Scan START** button. The data is stored as a text document in a file location specified by the user. When all data has been captured, stop the auto scan and stop logging.

## 4.1.2 Temperature Readings

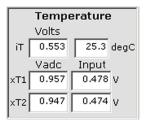

To the right of the pack voltage values are the temperature readings, (see <u>Figure 7</u>). In the default state, these boxes report the voltage on the temperature inputs. There are two boxes for each temperature.

Figure 7. Temperature Readings

The internal temperature reading (at the top) has two boxes. The left box shows the voltage reading from the internal temperature sensor. This voltage is dependent on the setting of the temperature gain bit (TGAIN). The temperature gain can be changed using the GUI by clicking the **TGAIN** button in the temperature box in the bottom left of the screen (below the tabs). The box on the right shows the conversion of the internal temperature to °C. This conversion uses <u>Equations 1</u> and <u>2</u>:

(EQ. 1) TGAIN = 0

$$\frac{intTemp(mV)}{1.8527} - 273.15 = ICTemp(^{\circ}C)$$

(EQ. 2) TGAIN = 1

$$\frac{intTemp(mV)}{0.92635} - 273.15 = ICTemp(^{\circ}C)$$

For the external temperatures, the left box shows the digital reading from the ADC. The right box shows the applied input voltage. The value on the left is dependent on the setting of the TGAIN bit. If TGAIN = 0, then the temperature input voltage is multiplied by 2 prior to being read by the ADC. If TGAIN = 1, the temperature input voltage is multiplied by 1. The left box of the external temperature readings simply translates the voltage readout by the ADC. The right box calculates the input voltage, based on the setting of the TGAIN bit.

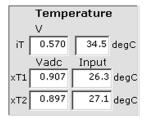

The temperature readings can also be displayed in °C, (see <u>Figure 8</u>). The conversion to °C depends on several items. First is the gain setting, so the actual input voltage is known. Second is the external resistor divider components. Third is the conversion of the thermistor value to °C.

Figure 8. Temperature Readings Displayed in °C

The gain setting is important only for determining the voltage applied at the input xTn pin.

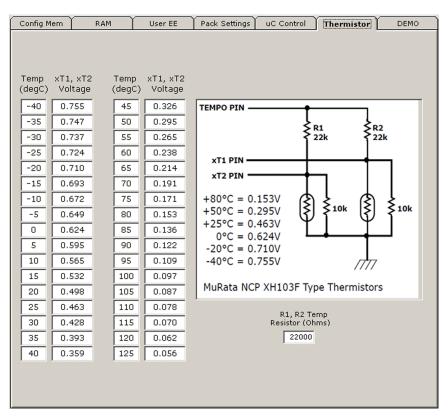

Next, the conversion depends on the external resistor divider, and assumes that the external circuit is implemented as shown in the Thermistor tab drawing, <u>Figure 9 on page 10</u>.

There is a 10k resistor parallel to the thermistor. There are two reasons for this. First, it makes the conversion curve more linear. Second, the thermistor voltage range better matches the default 2x gain on the temperature input amplifier. The thermistors are from Murata (XH103F). If an external thermistor replaces the thermistors on the board, the conversion can be changed by changing the values in the Thermistor tab of the GUI. The values in the table are the voltages applied to the xTn input pins. The voltage depends on the resistance of the Thermistor at each temperature and the voltage on the TEMPCO pin. The TEMPCO voltage is 2.5V.

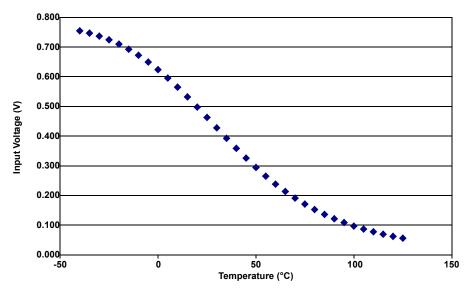

Based on calculations, the voltage/temperature curve for this circuit is shown in <u>Figure 10 on page 11</u>. The GUI uses the Thermistor table for this conversion and performs a linear interpolation between points.

For calculations of the external temperature, the Thermistor tab contains a value for the external divider resistor. This can be changed by the user, but not saved.

Figure 9. ISL94203 GUI Thermistor Tab

Figure 10. Voltage to Temperature Conversion

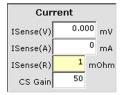

# 4.1.3 Current Readings

The current readout consists of four boxes, (see Figure 11). The top box shows the voltage across the sense resistor, as reported by the device and converted to volts. The next box shows the current reading in milliamps. This value depends on the value of the current resistor. This can be entered into the third current box. The default value is  $1\Omega$ , because that is the value on the ISL94203EVKIT1Z board. If the resistor value changes, this value can be changed in the GUI (but the default cannot be changed in this revision of the GUI). The bottom box simply relates the current amplifier gain setting in the device. In automatic scans, there is an automatic gain control. The gain setting is most useful when forcing a current read by the GUI.

Figure 11. Current Readout

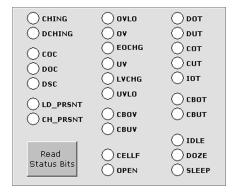

## 4.1.4 Status Bits

The status indicators on the lower right of the GUI screen (see <u>Figure 12</u>), reflect the status of the bits in the device. If an indicator is red, it shows a fault or out-of-bounds condition. If an indicator is green, it is showing an operating condition, such as current direction or power mode.

The status indicators are automatically updated when doing a voltage read operation. However, refreshing only the status bits is much quicker. So, clicking the **Read Status bits** updates only the status.

Figure 12. Status Indicators

#### 4.1.5 FET Indicators

Above the voltage readings are the FET indicators, (see <u>Figure 13</u>). These show the status of the PCFET, CFET and DFET control bits. If the bit is 1 indicating that the FET should be on, the indicator is green. If the bit is 0 indicating that the FET should be off, the indicator is red.

Figure 13. FET Indicators

The FET indicators are more than just readouts. Clicking on the indicators can also set or clear the bits to turn on or turn off the FETs. However, the GUI does not have control over the FETs when the device is operating in standalone mode. To control the FETs through the GUI requires that the  $\mu$ CFET bit is set first. This bit is set or reset using the  $\mu$ C Controls FET button in the  $\mu$ C Control Tab.

Above the FET control bits are some controls to change the operation of the device. These controls are **PCFET enable**, **CFET on during OV**, and **DFET on during UV**.

Setting the **PCFET enable** to active causes the PCFET to turn on, instead of the CFET, when the voltage is below the Low V Charge threshold voltage (see the Pack settings).

Setting the **CFET on during OV** to active means that the charge FET turns on when there is an overvoltage condition, if the device detects a discharge current. This reduces heat generated in the CFET during discharge. This is more important when there is a single charge/discharge path configuration.

Similarly, setting the DFET on during UV to active means that the discharge FET turns on when there is an undervoltage condition, if the device detects a charge current. This reduces heat generated in the DFET during charge. This is more important when there is a single charge/discharge path configuration.

#### 4.1.6 Other Main Screen Controls

Communication to the device requires an I<sup>2</sup>C bus. The I<sup>2</sup>C bus uses a Slave byte to determine the specific device on the bus that is being addressed. In the GUI this is set by the I2C Addr box (see <u>Figure 14</u>). This is located in the lower left of the screen. By default, the Slave Byte is 50H (0101 000x). This addresses the device having the ADDR pin pulled low. Applications where the ADDR pin is tied high are not supported.

Figure 14. I<sup>2</sup>C Address Box

Temperature measurement options are selected in this box (<u>Figure 15</u>) below the tabs. The pack settings and temperature outputs can be shown as either volts or °C. Changing the setting initiates a voltage scan and an update of the Pack Settings. The calculations are made in the GUI as described previously. The device simply maintains the voltage value associated with the temperature.

**Figure 15. Temperature Measurement Options**

This box also has the selection for the TGAIN bit. Clicking on the TGAIN box changes the TGAIN bit in the device, updates all of the RAM settings for temperature limits and initiates an update of the Pack Settings tab. It does not do a voltage scan. The caption shows the current status of the temperature gain. Figure 15 indicates that the temperature gain is set to 2x.

Access to the EEPROM requires an access control bit to be set prior to a read or write operation. In all of the screens where a button initiates multiple read or write operations, the memory access is automatically set to the correct access code and automatically reverts to RAM access. However, for individual memory read or write, it may be necessary to change the access code. These buttons allow this access code change. Simply click on the desired memory area button, prior to the actual read or write operation.

Figure 16. Memory Access

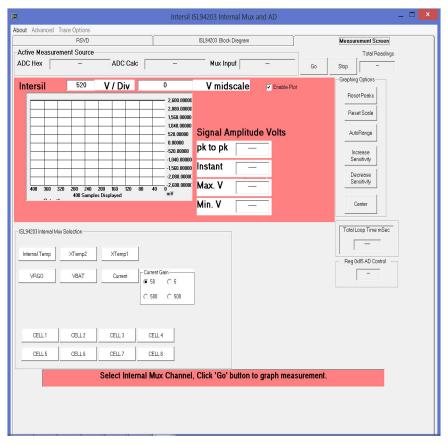

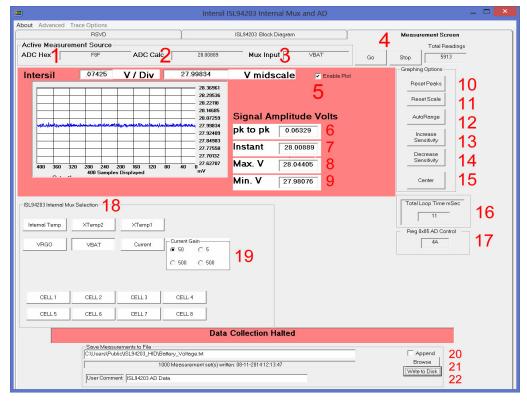

The ISL94203 Internal AD Utility screen enables you to view and record AD readings in real time. By using the I<sup>2</sup>C interface, the GUI enables you to select any of the internal Mux channels and view/capture the results in real time.

To bring up the AD form, click on the Internal AD Utility selection on the menu bar of the main form.

Figure 17. Menu Bar

When first loaded, the new form appears as shown in Figure 18.

Figure 18.

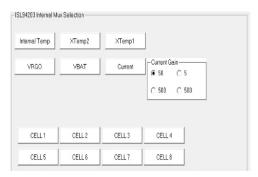

An important first step is to select an internal Mux Channel that is going to be measured. By making a selection (clicking on a Mux selection button, see <u>Figure 19</u>), data collection/graphing automatically starts and after a few seconds **Auto Range** takes place.

Figure 19.

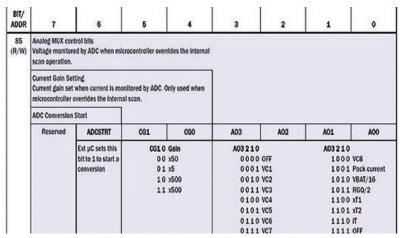

Essentially, clicking in the frame selection selects the value written to register 0x85. You can consult the ISL94203 datasheet for specifics related to each Mux Input connection. A real-time display of the register contents is displayed in Figure 21.

Figure 20.

Figure 21.

Therefore, this selection programs the MUX blocks connected to the input of the internal AD.

Figure 22.

# 4.1.7 Main AD Form Tools

Figure 23.

- 1. Actual Dual Byte Hex value of AD reading

- 2. Calculated value based on channel selected

- 3. Active channel being measured

- 4. GO Starts and STOP ends data collection. Click Stop to save collected readings to file.

- 5. Enable Plot, speeds up data collection by disabling real-time graphing

- 6. Highest reading lowest reading

- 7. Display of most recent reading

- 8. Peak/Maximum value recorded

- 9. Minimum value recorded

- 10. Clears items 6, 8, 9

- 11. Resets graphing scale to max default

- 12. Recalculate Maximum and Minimum values of graphing area

- 13. Decreases volts per division (visual only does not affect collected readings)

- 14. Increase voltages per division (visual only does not affect collected readings)

- 15. Recenters midrange scale and moves graphing range

- 16. Actual time in milliseconds to capture and graph a measurement

- 17. Hex value of Mux control register

- 18. Internal Mux selection

- 19. PGA gain selected when making a current measurement

- 20. Checking appends the latest collection of readings to a file

- 21. Browse to directory location where captured readings are saved

- 22. Perform actual write operation

Page 16 of 43

The Internal AD Utility form is a separated form that can be closed or minimized independent of the main screen (see F

Figure 24.

## 5. Tab Controls

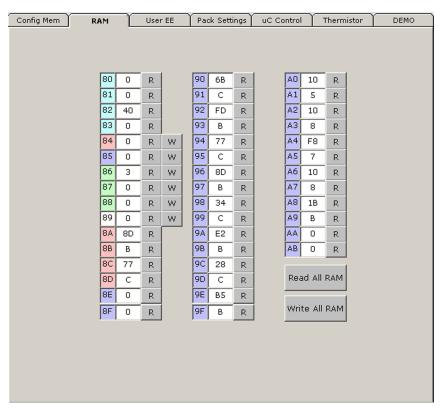

# 5.1 ISL94203 Memory Access

# 5.1.1 RAM

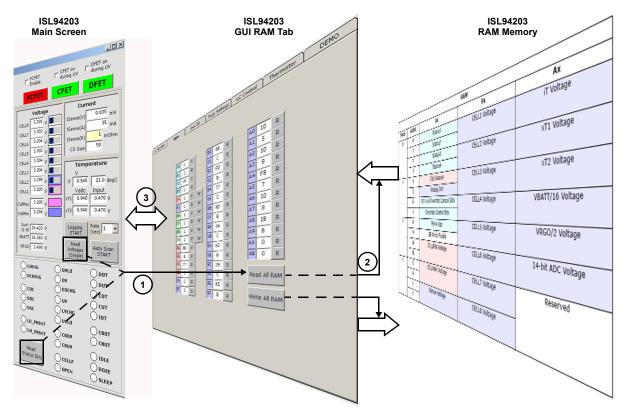

The ISL94203 has two main memory areas, RAM and Configuration Memory. The RAM area contains the transient values, such as cell voltages, status bits, and microcontroller override conditions. The RAM registers relate to the part of the GUI already described and the GUI reads and writes these registers as needed. You also have direct access to the RAM memory through the RAM tab, see Figure 25.

To update the values in the GUI with the values in the ISL94203, press the **Read All RAM** button. The display now shows the hex values of the RAM registers. Alternatively, each individual location can be updated by clicking on the **R** to the right of the register location.

There are only six registers that can be changed by the user. These are addresses 84H to 89H. These locations have a **W** next to the register. To change the register contents, write a new hex value in the desired location and press the **W** button (or the **Write All RAM** button). Until a write occurs, the contents of the ISL94203 RAM is not changed.

As shown in <u>Figure 25</u>, hovering the mouse pointer over the address of a register returns a description of the register. Also, the registers are color coded to match the datasheet and to group like registers. For example, in <u>Figure 25</u>, registers 80H to 84H are cyan color. These are the status registers. Also, registers 8EH through ABH are blue. These registers hold the voltage readings for the cells, current and temperature.

When pressing the **Read All RAM** or **Write All RAM** buttons, the color of the button changes and the caption changes to **Busy**. During this time the GUI is performing the specified operation and other operations are prohibited until the read or write completes and the color and caption return to normal. This sequence occurs on all controls described in the following.

The main screen shows the real world contents of the ISL94203 registers, converting hex values to volts, current, or temperature and indicating individual status bits. The GUI performs this update when the **Read Voltages** (**Single**) or automatic scan executes. The update operation begins with a Read All RAM operation. This brings in values from the ISL94203 (see <u>Figure 26 on page 18</u>). The GUI converts the hex values in RAM to the proper voltage, current, or temperature value.

The GUI controls for the writable RAM registers are located in the  $\mu$ C Control tab. These tab operations are discussed in more detail in the following.

Figure 25. ISL94203 GUI RAM Access Tab

Note: Read Voltages (Single) or Read Status Bits Operation execution steps are numbered. Write All RAM writes to the ISL94203 RAM memory, and updates the Main Screen.

Figure 26. ISL94203 GUI RAM Update Operation (Read Operation Numbered)

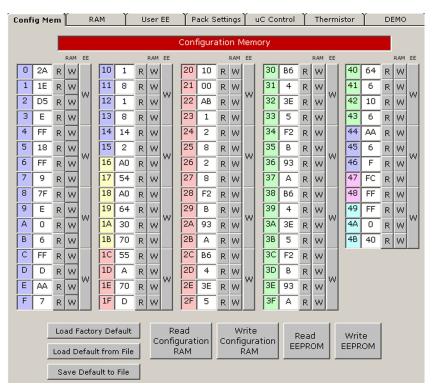

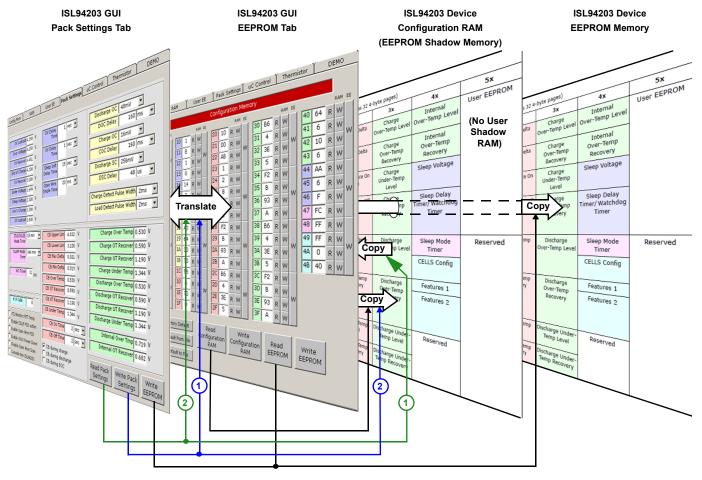

# 5.1.2 Configuration Memory

The Configuration Memory consists of two parts, the EEPROM cells and Configuration RAM. On power-up, the contents of the EEPROM is copied to the Configuration RAM. The device operates out of Configuration RAM.

Reading and writing the EEPROM does not automatically go through the Configuration RAM. Writes made to the EEPROM locations go into effect when the device power cycles or when the EEPROM contents are read from the EEPROM and rewritten to the Configuration RAM.

In the normal course of developing an application, a change is made to the Configuration RAM. This changes the operation of the device. For example, changing the overvoltage setting in the Configuration RAM changes the voltage at which the device detects a fault condition. However, the value has not yet changed in the EEPROM, so a power cycle returns the old OV threshold. To make the value permanent requires that the value also be written to the EEPROM.

The EEPROM tab (see Figure 27) of the GUI shows only one set of registers. This could be the values read from the Configuration RAM or from the EEPROM. Which values it displays is dependent on the access code. The access code is set in Register 89H, but the GUI automatically sets this bit when the **Read EEPROM** or **Write EEPROM** buttons are pressed. The Access code is also settable by clicking the Memory Access button as described previously.

To write to individual bytes of the RAM part of the Configuration Memory, set the **RAM Access** in the Memory access box. Each byte in RAM can be written separately.

Writing to individual bytes to the EEPROM part of the Configuration Memory is limited. Each EEPROM write needs to write all four bytes on a page. For this reason, the GUI has a different (larger) button for writing to EEPROM. As previously mentioned, to write to a page of EEPROM, it is necessary to set the **EEPROM Access** in the Memory access box prior to the write.

As with the RAM tab, hovering over an address box brings up a dialog showing a simple description of the register contents. Also, the various registers are color coded as shown in the datasheet and are grouped by function.

The EEPROM tab has three other buttons. The first is a **Load Factory Default** button. This fills the GUI EEPROM locations with the factory default values (as defined at the time of the GUI release). This lets you recover to a known good operating point. Again, use of this button fills the GUI registers. To change the operation of the device or the contents of the EEPROM requires a separate write for each memory location.

The other two buttons are **Save User Default to File** and **Load User Default from File**. These commands allow the user Configuration Memory to be saved and recalled. The values saved are locations 0H through 4BH.

Figure 27. ISL94203 GUI - EEPROM Access Tab

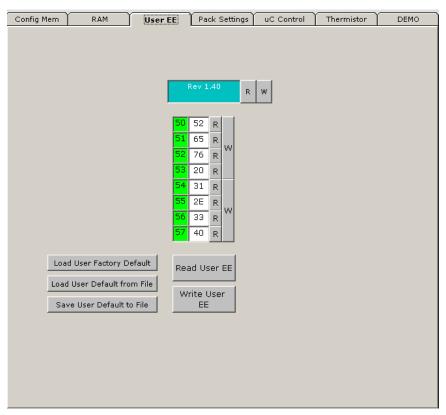

# 5.1.3 User Memory

The user memory area is different from the Configuration memory. The User memory does not have a RAM component, so all reads and writes are to the EEPROM only. Also, the device ships with the user memory cleared. So, an initial read from user memory reads 0.

Using the **Load User Factory Default** tells the GUI to put the software revision number in the GUI locations for the user memory. You can keep these values or load other data in the GUI boxes. To write the data to the ISL94203 User EEPROM requires individual writes (click the **EEPROM Memory Access** first) or a write all, using the **Write User EE** button (this automatically sets the EEPROM Access bit).

The User EE tab also includes a **Load Default from File** and a **Save User Default to File**. These buttons load and save User EE data at addresses 50H to 57H only.

Figure 28. ISL94203 GUI - USER EEPROM TAB

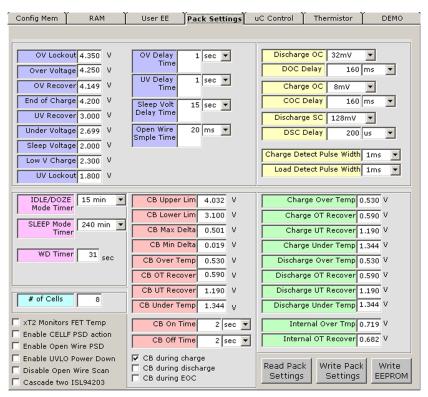

## 5.1.4 Pack Settings Tab

The Pack Settings tab (see <u>Figure 29</u>) provides access to the contents of the Configuration RAM, but with real-world values. This provides an easier way to program the operation of the pack and to monitor the present settings. Values in the Pack Settings tab are saved in the GUI. When a **Read Pack Settings** button is pressed, the value is read from the device and loaded into the Configuration RAM tab of the GUI. The GUI then takes the contents of the Configuration RAM, calculates the real world value and writes it to the pack settings tab.

When a value is changed in the Pack Settings tab, nothing happens until a **Write Pack Settings** button is pressed. The GUI takes the value in the Pack Settings tab, converts the value to hex and writes the new value to the Configuration RAM tab in the GUI. These values are written from the GUI to the RAM part of the device Configuration memory. If a value is changed in the GUI, but no write button is pressed, the device is not updated with the new value.

As soon as the Write Pack operation completes, the ISL94203 begins operating with the new parameters.

The Pack Settings tab also includes a **Write EEPROM** button. This is a convenience, because it does the same function as the button in the EEPROM Tab. However, in the Pack Settings tab, it is necessary to do a **Write Pack Settings** operation prior to doing the **Write EEPROM**. Otherwise, the EEPROM would not get the latest values from the Configuration Memory RAM to write to EEPROM. This is because the **Write EEPROM** writes values from the GUI Config Mem tab to the device and the values in the GUI Config Mem tab are not updated until execution of the **Write Pack Settings** operation.

<u>Figure 30 on page 22</u> shows a graphical representation of the operation of the Pack Settings tab operation, the GUI EEPROM tab and the ISL94203 internal registers.

The memory operations of the Pack Settings tab was described above. The next section covers some additional details about the calculations and use of the values shown in the Pack Settings tab.

Figure 29. ISL94203 GUI - Pack Settings Tab

Figure 30. ISL94203 GUI Pack Settings Tab Memory Operations

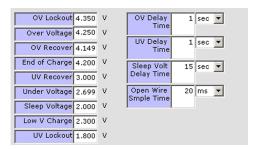

## 5.1.5 Voltage Limits

The upper left section of the Pack Settings tab contains the voltage thresholds and delay times, (see <u>Figure 31</u>). The voltages can be set from 0V to 4.8V. A negative number loads 0 and a value greater than 4.8V loads 4.8V. The timer values for OV Delay, UV Delay, and Open Wire Sample Time can be between 0 and 1023. The timer value for Sleep Voltage Delay time can be between 0 and 512.

Figure 31. Voltage Thresholds and Delay Times

Normally, the OV Lockout threshold is greater than the Overvoltage threshold and the UV Lockout threshold is lower than the Undervoltage threshold. The reason for this is based on the definition of the values. Reaching the overvoltage and undervoltage thresholds causes the respective power FETs to turn off, but the pack continues to operate normally. However, if the voltage of any cell reaches the UVLO or OVLO thresholds, something is very wrong with the pack or the charger. Reaching the OVLO threshold causes the device to set a pack shutdown (PSD) bit. This can be used to blow a fuse to disable the pack. Reaching the UVLO threshold indicates that one or more cells are much below their lower limit, so the device powers down to remove as much load as possible from the cells.

The End of Charge threshold is usually lower than the overvoltage threshold. When a cell reaches the overvoltage threshold, the end of charge output (EOC pin) can turn off the charger. If the voltage continues to rise, there is something wrong with the charger, so the overvoltage indication turns off the charger current from within the pack.

Alternatively, the EOC limit can be used for cell balancing to specify a level where balancing is to begin. In this case, when any cell reaches the End of Charge threshold, all cells that are higher than CELLMIN + CB MIN Delta start to balance. Balancing continues until all cells are below the EOC Threshold -117mV.

The Sleep voltage, along with the sleep voltage timer determine if the cells drop below a sleep threshold. If so, the power FETs turn off and the device enters a sleep mode. The device wakes from a sleep mode by the connection of a load or a charger to the pack.

The **Low V Charge** threshold is used when the precharge FET is enabled. The low voltage charge threshold is the level where the charge FET turns on instead of the precharge FET. When the cell voltages are below the Low V charge level, the precharge FET is on. When the cell voltages are greater than the Low V charge level, the charge FET is on.

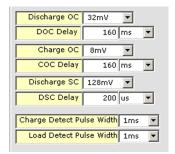

## 5.1.6 Current Limits

To the right of the voltage settings are the current limits for discharge overcurrent, charge overcurrent, and discharge short-circuit events, (see Figure 32 on page 24). The delay time values can be 0 to 1023 microseconds, milliseconds, seconds or minutes. Care should be taken when setting the range of these timers. The threshold levels are set by drop down boxes and set the overcurrent level by setting the voltage expected across the sense resistor.

Figure 32. Current Limits

Also in this selection is the setting for the duration of the charge and load pulse widths. When the power FETs turn off in response to an overcurrent event, the ISL94203 starts looking for the release of the load or charger. It does this by periodically sourcing or sinking a current to the load or from the charger. The duration of the pulse width might need to be changed, depending on the load or charger capacitance, because the detection circuit is attempting to pull the voltage at the terminals to some intermediate state. If the load or charger is off, but there is a large capacitance still connected to the terminals, a short pulse width takes longer to detect the removal. The ISL94203 allows detection pulse widths from 1ms to 16ms.

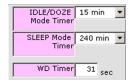

#### **5.1.7 Timers**

Below the voltage settings are some timer controls. The upper box specifies the amount of time the device spends in normal mode (with no measured current) before entering into IDLE and the time the device spends in IDLE before entering the DOZE mode. The Sleep Mode Timer specifies how long the device remains in DOZE mode (with no measured current) before going to sleep. Detection of any current returns the part to the normal operating mode.

Figure 33. Timer Controls

The WD Timer setting is used with  $\mu$ C override operations. When the  $\mu$ C sets any condition that overrides internal operation, the WD timer starts. The WDT is reset by any valid reception of an I<sup>2</sup>C slave byte. If there are no valid communications before the WDT times out, the ISL94203 turns off all FETs and waits for a valid command.

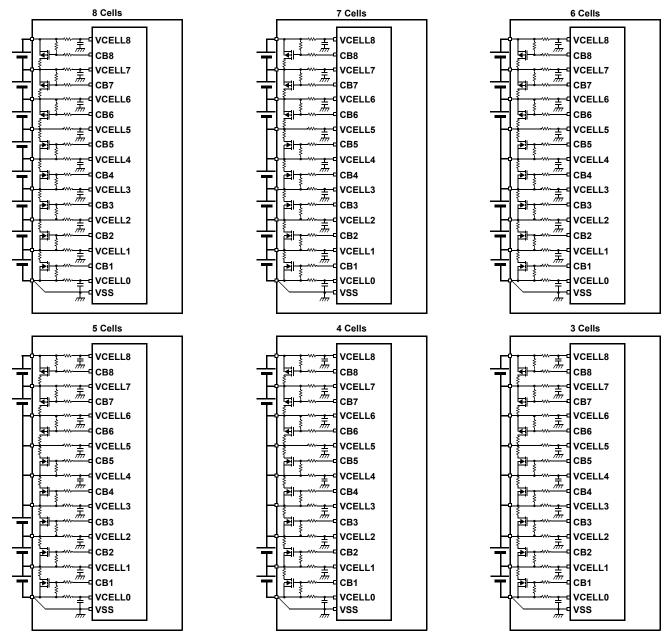

## 5.1.8 Number of Cells

The **# of Cells** box specifies the number of cells connected to the pack. The number in the box can be lower than the number of cells connected to the pack. This value is a direct representation of the number of cells, it is not the value stored in memory. The GUI translates the number of cells value to the proper code for the device, as specified in <u>Table 1</u>.

When the board first powers up, the **# of Cells** is set to 3. This causes some of the cells to show 0V in a Voltage Scan. This is because the cells are skipped in the scan. If there are more cells connected, change the setting, write the values to the pack, and write the values to EEPROM.

The reason for the default value of 3 in the # of Cells box is that if the number in the box is greater than the number of cells connected to the pack, when the ISL94203 first powers up it reads a cell input as 0V. The ISL94203 thinks that this is a cell failure, so does not complete its power up sequence. This is part of the protection mechanisms of the part. If the value written to the EEPROM is higher than the number of cells connected and the device powers down, it does not power up properly. It is necessary to connect the programmed number of cells (or more) so the device powers up. Then the EEPROM value can be reset.

For the proper connections of fewer than 8 cells, see <u>Table 1</u>. When using the evaluation board with fewer than 8 cells, connect the unused cell inputs at the board connection. It is not necessary to remove any components on the board (see <u>Figure 52 on page 38</u>).

Table 1. ISL94203 Cell Configuration

| Cells Value | Number of Cells                               |

|-------------|-----------------------------------------------|

| 1000011     | 3 Cells connected, C1, C2, C8                 |

| 11000011    | 4 Cells connected, C1, C2, C7, C8             |

| 11000111    | 5 Cells connected,<br>C1, C2, C3, C7, C8      |

| 11100111    | 6 Cells connected, C1, C2, C3, C6, C7, C8     |

| 11101111    | 7 Cells connected, C1, C2, C3, C4, C6, C7, C8 |

| 11111111    | 8 Cells connected, All cells connected        |

Note: Only these combinations are acceptable. Any other combination prevents any FET from turning on.

#### 5.1.9 Cell Balance Limits

The next box to the right (<u>Figure 34</u>) contains the settings for cell balancing. The voltage limits that can be set in the GUI are fixed at 0 and 4.8V. There are no limits to the temperature settings. The temperature values are limited by the GUI from 0 to 1.8V (voltage setting) or -40°C to +125°C (temperature setting).

Figure 34. Number of Cells Box

The CB lower limit and CB upper limit define the boundaries of the cell voltage operation (except in EOC balancing). If ALL cell voltages exceed the limits, then balancing stops. Balancing starts again when ALL cell voltages drop back within the specified limits plus a hysteresis. For example, if the CB upper limit is set to 4.0V, balancing stops when all cell voltages exceed 4.0V. Balancing resumes when all cell voltages drop below 3.883V.

**CB Max Delta** specifies the maximum difference between the CELLMAX and CELLMIN values. When this happens, it implies that there is something wrong with the cells or connections. When cell voltages exceed the CB Max Delta limits, the CELLF flag is set. This can cause the PSD pin to active (optional) which can shut down the pack. The CELLF indication also starts the open wire detection operation.

The CB over- and under-temperature settings specify the temperature range over which the cell balance operates. If the external temperature sensors show that the temperature is out of bounds, cell balance stops.

The CBON and CBOFF times specify how long the cell balance is on and off. These timers are mainly used for thermal control to manage the heat dissipated by the cell balance resistors.

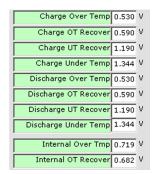

## 5.1.10 Temperature Limits

On the lower right of the Pack Settings tab are the pack temperature limit settings. There are temperature limits for charge and discharge as well as temperature recovery levels for each. These limits refer to the ADC converted value of the temperature sensor inputs, so they are affected by the TGAIN bit. The GUI limits values in these locations from 0 to 1.8V (voltage setting) or -40°C to +125°C (temperature setting).

Figure 35. Pack Temperature Limit Settings

When the TGAIN bit changes from 0 to 1 or 1 to 0, the GUI rewrites the values of the temperature limits in the EEPROM tab (based on the temperature input amplifier gain) and sends these new values to the ISL94203. The GUI also updates the Pack Settings Information. The Pack Settings tab temperature limits do not change if they are shown in °C, but the value in the device does change. This is because the calculations for the temperature settings in °C includes the setting of the TGAIN bit.

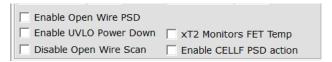

# 5.1.11 Pack Options

In the lower left of the Pack Setting tab are various option controls (see Figure 36).

Figure 36. Option Controls

Setting the **xT2 Monitors FET Temp** to 1 tells the device to treat the xT2 input as a FET temperature, not a cell temperature. With this bit set, an over-temperature on the xT2 input does not stop cell balancing, it only turns off the power FET.

The **Enable CELLF PSD action**, when set to 1, causes the PSD bit to be set when the device detects a condition that sets the CELLF bit.

The **Enable Open Wire PSD** bit, when set to 1, causes the PSD bit to be set when the device detects an open wire condition

The **Enable UVLO Power Down**, when set to 1, causes the device to power down when it detects an undervoltage lockout condition.

The **Disable Open Wire Scan** bit, when set to 1, turns off the open wire scan operation.

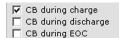

#### 5.1.12 Cell Balance Enable

As part of the Cell balance settings are the Cell Balance controls for charge, discharge or end-of-charge balancing.

If **CB during charge** is checked, the device activates cell balancing if charge current is detected and all other conditions are within limits. If there is no current or there is discharge current, the device does not balance.

If **CB during discharge** is checked, then the device activates cell balancing if discharge current is detected and all other conditions are within limits. If there is no current or there is a charge current, the device does not balance.

If the **CB during EOC** is checked, the device ignores the current detection and balances only based on the end-of-charge condition (as long as all other conditions are with limits). With this option selected, cell balancing is enabled when any cell reaches the end-of-charge threshold. Balancing continues as long as any cell is greater than the EOC threshold minus 117mV.

While cell balancing is enabled, in any mode, balancing is turned on for any cell whose voltage is more than CELLMIN + CB Min Delta volts.

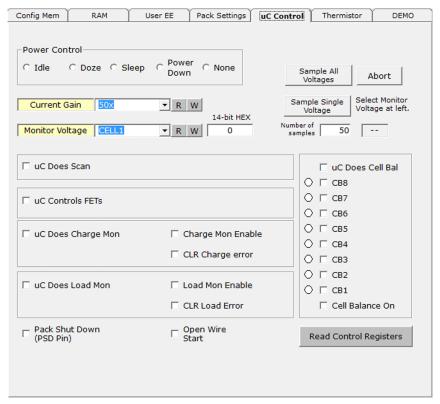

## 5.2 µC Control Tab

The  $\mu$ C Control tab provides a mechanism for the GUI to override the internal operation of the device. An external microcontroller would use similar techniques to provide different functionality to the pack than is offered by the built-in automatic operations. The options available on the  $\mu$ C Control tab are shown in Figure 37 on page 28.

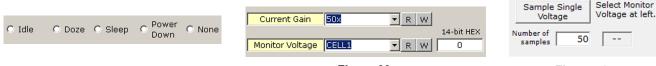

#### 5.2.1 Power Control

The mode of operation of the device is controlled by these check boxes (see Figure 38 on page 28). Clicking any box puts the device into that mode of operation. Clicking on **None** removes any forcing condition. The  $\mu$ C Control features does not allow the device to be placed back into normal operation. For example, when the device enters IDLE mode, it can be placed in DOZE mode, returned to IDLE mode, put to sleep, or set to power down, but it can only return to a normal scan operation if it detects current flow in the pack. The GUI also offers a demo mode that forces a current indication, which can be used to return to normal mode.

It is not necessary to override any internal operation to change the operating mode.

# 5.2.2 Individual Voltage Monitoring

The GUI or an external  $\mu$ C can force a read of any voltage available from the internal MUX. This includes cell voltages, pack current and voltage, and temperatures. It is not necessary to override any internal function to use this measurement.

To use this feature, select the voltage to be measured and click the **W** button. The **R** button reads the status of the AO3:AO0 bits, but a write operation sets the bits for the desired voltage and sets the ADCSTRT bit, which is needed to start the internal conversion operation. The resulting voltage shows in the box at the right, (see <a href="Figure 39 on page 28">Figure 39 on page 28</a>). This is a 14-bit hex value. This value needs to be converted to voltage, current, or temperature.

When measuring the current, the gain of the amplifier can be manually set prior to the ADC read by using the drop down box and **W** button on the top line.

The GUI allows the repetitive capture of any single voltage or all voltages. For a single voltage capture, the desired voltage is selected by the Monitor Voltage box (see <u>Figure 40 on page 28</u>). The number of samples is specified and the **Sample Voltages** button is pressed. This brings up a dialog box asking for the file name for the data to be stored. The GUI captures the specified number of samples and stores the data to the file. This is a tab delimited file that can be imported into Excel.

Between the **Sample All Voltages** and **Sample Single Voltage** buttons is a progress indicator showing the ongoing data capture.

Figure 37. ISL94203 GUI - μC Control Tab

Figure 38. Figure 39. Figure 40.

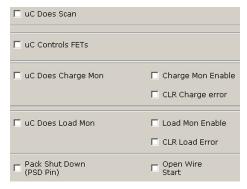

## 5.2.3 Microcontroller Does...

The next set of controls (Figure 41) allows the GUI (or microcontroller) to take over several functions of the device. The most general is the  $\mu$ C Does Scan box. When checked, the device stops scanning the cells, which effectively stops automatic operation. When this box is checked, cell voltages are scanned by the external  $\mu$ C, OV and UV voltages must be manually compared with limits and cell balance must be controlled externally. The only function maintained internally during a  $\mu$ CSCAN operation is the overcurrent/short circuit monitoring. These continue to be automatically monitored.

Figure 41.

Sample All

Voltages

Abort

The  $\mu$ C Controls FETs operation gives the GUI or external  $\mu$ C control over the FETs. With this box unchecked, the ISL94203 has exclusive control over the FETs. It is not possible to change the FETs from the outside. When the box is checked, the FETs are only controlled by the GUI or an external  $\mu$ C.

The  $\mu$ C Does Charge Mon bit overrides the internal charger monitor function. When overridden, the GUI or an external  $\mu$ C can turn on the charger monitor current and detection hardware by setting the **Charge Mon Enable**. The GUI or external  $\mu$ C needs to monitor the CH\_PRSNT bit to detect if there is a charger present. If the charger is removed following an overcurrent condition, the GUI/ $\mu$ C needs to reset the charge error bit by clicking on **CLR Charge Error**.

The  $\mu$ C Does Load Mon bit overrides the internal load monitor function. When overridden, the GUI or an external  $\mu$ C can turn on the load monitor current and detection hardware by setting the Load Mon Enable. The GUI or external  $\mu$ C needs to monitor the LD\_PRSNT bit to detect if there is a load present. If the load is removed following an overcurrent condition, the GUI/ $\mu$ C needs to reset the load error bit by clicking on CLR Load Error.

All of these operations start the Watchdog timer. If communications with the device stop for more than the Watchdog time-out period, the device resets the override bits and waits for a valid communication. When a valid communication is received, the device resumes normal, default operation.

The **Pack Shut Down** control is a direct control of the PSD pin. The **Open Wire Start** is a manual open wire start operation. This open wire scan does not need to first wait for a CELLF condition.

# 5.2.4 µC Cell Balance

The GUI/ $\mu$ C can manually control the cell balance operation, overriding the internal automatic balancing. Set the  $\mu$ C Does Cell Bal bit and the Cell Balance On bit. Check any, or all, of the individual cell balance bits to activate the cell balance outputs (see Figure 42)

Figure 42. Cell Balance

However, before the balancing outputs turn on, all other conditions for balancing must be met. There can be no error conditions and if balancing is selected during charge, there must be a charge current before the cell balance outputs turn on. During a  $\mu$ C controlled cell balance operation the CBON and CBOFF timers are not used.

When the  $\mu$ C Does Cell Bal is set, the Watchdog timer starts and communications must happen within the watchdog time out period. If there is an interruption in the communications, the  $\mu$ CCBAL bit is reset and the device waits for a valid communication. When a valid communication is received, the device resumes normal, default operation.

The indicators to the left of the control boxes indicates which cells are to be balanced. If proper balancing conditions are not met, the indicators are off. If the cells should be balancing, the indicators are on. If the LEDs on the board are not on at the same time as the indicators in the GUI, there could be a hardware problem.

Read Control Registers

When clicking the Read Control Registers button, the status of all of the override bits are updated.

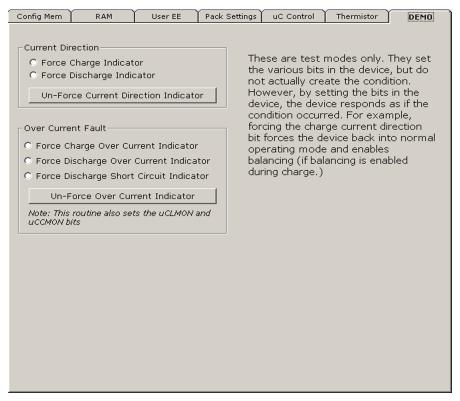

## 5.3 DEMO Tab

The last tab in the GUI offers some demonstration controls, see <u>Figure 43</u>. This allows you to test some items without connecting a real charger or load to the system. This is useful in simulating current flow and overcurrent errors

The controls available in this tab are test modes only. They set the various bits in the device, but do not actually create the condition. However, by setting the bits in the device, the device responds as if the condition occurred. For example, forcing the charge current direction bit forces the device back into normal operating mode and enables balancing (if balancing is enabled during charge).

Figure 43. ISL94203 GUI - DEMO Tab

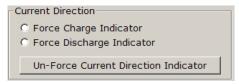

## 5.3.1 Current Direction Demo

The **Force Charge Indicator** or **Force Discharge Indicator** controls force the device to indicate a charge or discharge condition (see <u>Figure 44</u>). This is not a real condition, for example, the current readout shows no current flow. However, the device responds as if there is a current.

Figure 44.

While in either of these demo modes, the device does not respond to real overcurrent or short circuit conditions.

To clear the conditions, click on the **Un-force Current Direction Indicator** button.

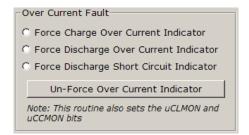

#### 5.3.2 Overcurrent Demo

To simulate any of the overcurrent or short circuit conditions, use the Over Current Fault demo options (see Figure 45). The **Force Charge Over Current Condition** sets the COC bit and the device responds as if that condition exists. To better view the operation, the GUI sets the  $\mu$ CLMON and  $\mu$ CCMON bits so the recovery conditions are controlled manually. Without the  $\mu$ CCMON and  $\mu$ CLMON bits set, the device does the following:

- The test bit indicates to the device that there is an overcurrent condition.

- The device sees that there is no current, so starts the LDMON or CHMON operation.

- The device sees that there is no load and no charger, so it clears the fault condition.

- The device immediately sees the test mode fault condition, so it again responds as if there is fault.

- The device continues to oscillate between these modes, because the demo condition is not real.

Figure 45. Overcurrent Fault Demo Options

To get a better understanding of the operation, connect a potentiometer to the load output. Make sure that the minimum resistance on the potentiometer is about  $1k\Omega$ . This is not so low that it is damaged when the FETs are on, but is low enough to detect a load. Now, force a discharge overcurrent condition. (Look at the SD LED on the PCB, it should be on continuously). Use the  $\mu$ C Control tab to clear the  $\mu$ C Load Monitor bit. Now, the device detects the overcurrent (from the test bit). It sees that there is no current, so it starts the load monitor. Because of the potentiometer, it sees that there is a load, so the fault condition remains in effect and the SD LED remains on. By gradually increasing the resistance on the potentiometer, the device reaches the point where the device detects that the load is removed. At this point, the SD LED resumes the oscillations as it detects the load clearing and sees the demo fault.

# 6. ISL94203EVKIT1Z Hardware Design

Figure 46. ISL94203EVKIT1Z Hardware Design

# 6.1 Bill of Materials

| Qty | Reference<br>Designator        | Description                                                   | Manufacturer         | Manufacturer Part       |

|-----|--------------------------------|---------------------------------------------------------------|----------------------|-------------------------|

| 9   | C13-C21                        | CAP, SMD, 0603, 47nF, 100V, 10%, X7R, ROHS                    | Venkel               | C0603X7R101-473KNE      |

| 3   | C2, C25, C26                   | CAP, SMD, 0603, 1µF, 50V, 10%, X5R, ROHS                      | TDK                  | C1608X5R1H105K          |

| 3   | C1, C22, C23                   | CAP, SMD, 0603, 4700pF, 100V, 10%, X7R, ROHS                  | Venkel               | C0603X7R101-472KNE      |

| 1   | C27                            | CAP, SMD, 0603, 1000pF, 16V, 10%, X7R, ROHS                   | Venkel               | C0603X7R160102KNE       |

| 1   | C28                            | CAP, SMD, 0603, 2.2µF, 10V, 10%, X7R, ROHS                    | Murata               | GRM188R71A225KE15D      |

| 2   | C3, C4                         | CAP, SMD, 0603, 1.0µF, 10V, 10%, X7R, ROHS                    | AVX                  | 0603ZC105KAT2A          |

| 2   | C31, C32                       | CAP, SMD, 0603, 2.2nF, 100V, 10%, X7R, ROHS                   | Venkel               | C0603X7R101-222KNE      |

| 3   | D18-D20                        | DIODE-ZENER, SMD, 2P, SOD-123, 18V, 500mW, ROHS               | Diodes Inc.          | MMSZ5248B-7-F-T         |

| 8   | D1-D8                          | LED-SMART, SMD, 0603, YELLOW, 1.8V, 2mA, 587nm, 7.9mcd, ROHS  | Osram                | LY L29K-J1K2-26-Z       |

| 1   | D21                            | DIODE-RECTIFIER, SMD, SMPC, 100V, 10A, ROHS                   | Vishay               | V10P10-M3/86A           |

| 3   | D22-D23, D25                   | LED-SMART, SMD, 0603, 2P, RED, 1.8V, 2mA, 630nm, 4.5mcd, ROHS | Osram                | LSL29K-G1J2-1-0-2-R18-Z |

| 1   | D26                            | LED-SMART, SMD, 0603, GREEN, 1.7V, 2mA, 570nm, 3.9mcd, ROHS   | Osram                | LGL29K-G2J1-24-Z        |

| 3   | D27, D28, D34                  | DIODE-TVS, BIDIRECTIONAL, SMD, 2P, SMA, 40V, 400W, ROHS       | Diodes, Inc.         | SMAJ40CA-13-F           |

| 1   | D29                            | DIODE-DUAL, SWT, SMD, SOT23, 100V, 2A, 350mW, ROHS            | Diodes Inc.          | MMBD7000HS-7-F          |

| 1   | D30                            | DIODE-ZENER, SMD, 2P, SOD-123, 3.3V, 500mW, ROHS              | Diodes, Inc.         | BZT52C3V3-7-F           |

| 3   | D31, D33, D32                  | DIODE-ZENER, SMD, SOD-123, 43V, 410mW, ROHS                   | Diodes, Inc.         | BZT52C43-7-F            |

| 1   | D35                            | DIODE SCHOTTKY, SOD323                                        |                      |                         |

| 2   | D36, D37                       | DIODE, SCHOTTKY, SOD523                                       |                      |                         |

| 1   | Q11                            | TRANSIST-MOS, N-CHANNEL, SMD, DPAK, 40V, 9A, ROHS             | Fairchild            | FDD8451                 |

| 4   | Q12, Q13,<br>Q15, Q16          | TRANSISTOR-DUAL NPN, SMD, 6P, SOT363, 40V, 200mA, ROHS        | Diodes, Inc.         | MMDT3904-7-F            |

| 5   | Q1-Q5                          | TRANSISTOR-MOS, N-CHANNEL, SMD, SOT23, 60V, 280mA, ROHS       | Fairchild            | NDS7002A                |

| 3   | Q6-Q8                          | TRANSISTOR, P-CHANNEL, SMD, SOT23, -60V, -180mA, ROHS         | Fairchild            | NDS0605                 |

| 2   | Q9, Q10                        | TRANSISTOR-MOS, N-CHANNEL, SMD, D2PAK, 40V, 75A, ROHS         | NXP<br>Semiconductor | PHB101NQ04T             |

| 12  | R18-R25, R49,<br>R50, R52, R53 | RES, SMD, 0402, 1k, 1/16W, 1%, TF, ROHS                       | Venkel               | CR0402-16W-102JT        |

| 8   | R1-R8                          | RES, SMD, 0603, 330k, 1/10W, 1%, TF, ROHS                     | Yageo                | RC0603FR-07330KL        |

| 8   | R26 - R33                      | RES, SMD, 2512, 100Ω, 1W, 1%, TF, ROHS                        | Vishay/dale          | CRCW2512100RFKEG        |

| 10  | R40-R48, R63                   | RES, SMD, 0603, 1k, 1/10W, 1%, TF, ROHS                       | Panasonic            | ERJ-3EKF1001V           |

| 7   | R34-R39                        | RES, SMD, 0603, 100Ω, 1/10W, 1%, TF, ROHS                     | Venkel               | CR0603-10W-1000FT       |

| 1   | R54                            | RES, SMD, 2512, 200, 1W, 5%, TF, ROHS                         | Venkel               | CR2512-1W-201JT         |

| 5   | R55-R57, R64,<br>R65           | RES, SMD, 0603, 1M, 1/10W, 1%, TF, ROHS                       | Panasonic            | ERJ-3EKF1004V           |

| 2   | R58, R59                       | RES, SMD, 2512, 002Ω, 1W, 1%, TF, ROHS                        | Panasonic            | ERJ-M1WTF2M0U           |

| 2   | R61, R62                       | RES, SMD, 0402, 22k, 1/16W, 1%, TF, ROHS                      | Venkel               | CR0402-16W-223JT        |

| 2   | R66, R67                       | RES, SMD, 0603, 499Ω, 1/10W, 1%, TF, ROHS                     | Venkel               | CR0603-10W-4990FT       |

| 2   | R68, R69                       | RES, SMD, 0402, 4.7k, 1/16W,1%,TF,ROHS                        | Venkel               | CR0402-16W-4701FT       |

| 5   | R70-R74                        | RES, SMD, 0402, 49.9k, 1/16W, 1%, TF, ROHS                    | Panasonic            | ERJ-2RKF4992            |

| 1   | R75                            | RES, SMD, 0603, 120k, 1/10W, 1%, TF, ROHS                     | Vishay/dale          | CRCW0603120KFKEA        |

| Qty  | Reference<br>Designator                  | Description                                              | Manufacturer           | Manufacturer Part    |

|------|------------------------------------------|----------------------------------------------------------|------------------------|----------------------|

| 1    | R76                                      | RES, SMD, 0603, 0Ω, 1/10W, TF, ROHS                      | Venkel                 | CR0603-10W-000T      |

| 1    | R77                                      | RES, SMD, 0402, 0Ω, 1/16W, 5%, TF, ROHS                  | Venkel                 | CR0402-16W-00T       |

| 4    | R78, R79,                                | RES, SMD, 0402, 2.49k, 1/16W, 1%, TF, ROHS               | Panasonic              | ERJ-2RKF2491V        |

| 7    | R81, R82                                 | TKLO, OWID, 0402, 2.49K, 1/10W, 170, 11, KOHO            | anasomo                | LIW-21441 2491 V     |

| 2    | R83, R87                                 | RES, SMD, 0603, 3.3M, 1/10W, 1%, TF, ROHS                | Panasonic              | ERJ-3EKF3304V        |

| 1    | R84                                      | RES, SMD, 0603, 550k, 1/10W, 1%, TF, ROHS                | Venkel                 | CR0603-10W-5503FT    |

| 11   | R9-R17, R85,<br>R86                      | RES, SMD, 0402, 10k, 1/16W, 1%, TF, ROHS                 | Panasonic              | ERJ-2RKF1002X        |

| 2    | S1, S2                                   | SWITCH-TACTILE, PUSH, TH, 8X8mm, SPST, 12V, 50mA, ROHS   | Omron                  | B3WN-6002            |

| 3    | Th1, TH2a,<br>TH2b                       |                                                          |                        | ERT-J1VG103JA        |

| 1    | U1                                       | IC-MULTI-CELL, LI-ION MONITOR, 48P, QFN, 6X6, ROHS       | Renesas                | ISL94203IRTZ         |

| 1    | U2                                       | IC-TVS, ESD PROTECTOR, SMD, 6P, SOT-23-6L, 3pF, 6V, ROHS | ST<br>Microelectronics | USBLC6-2SC6          |

| 1    |                                          | PWB-PCB, ISL94203EVKIT1Z, REVD, ROHS                     |                        |                      |

| Con  | nectors/Headers                          | s                                                        |                        |                      |

| 1    | J13                                      | CONN-HEADER, 4PIN, 2.54mm, RIGHT-ANGLE, ROHS             | Molex                  | 22-05-2041           |

| 1    | J3                                       | CONN-HEADER, 1X9, FLAT BRK-AWAY, 2.54mm, R/A, ROHS       | Molex                  | 22-28-8091           |

| 1    | TP11                                     | CONN-HEADER, 1x1, BREAKAWAY 1X36, 2.54mm, ROHS           | Berg/FCI               | 68000-236HLF         |

| 4    | 1Path, 2Path,<br>xTH1, xTH2a             | CONN-HEADER, 1x2, BRKAWY 1X36, 2.54mm, ROHS              | Berg/FCI               | 68000-236HLF         |

| 3    | ADDR, J7, J9                             | CONN-HEADER, 1x3, BREAKAWY 1X36, 2.54mm, ROHS            | Berg/FCI               | 68000-236HLF         |

| 1    | J5                                       | CONN-HEADER, 1X8, BRKAWY 1X36, 2.54mm, ROHS              | Berg/FCI               | 68000-236HLF         |

| 1    | J2                                       | CONN-HDR, 1x9, BRKAWY 1X36, 2.54mm, ST, ROHS             | Berg/FCI               | 68000-236            |

| 1    | CS1, CS2                                 | CONN-HEADER, 1X2, BRKAWY 1X64, 2.54mm, 0.195x0.118, ROHS | Mill-max               | 800-10-064-10-001000 |

| 1    | CHMON,<br>LDMON,<br>PCFET, CFET,<br>DFET | CONN-HEADER, 1X5, BRKAWY 1X64, 2.54mm, 0.195x0.118, ROHS | Mill-max               | 800-10-064-10-001000 |

| 1    | VB, VC0-VC8                              | CONN-HDR, 1X10, BRKAWY 1X64, 2.54mm, 0.195x0.118. ROHS   | Mill-max               | 800-10-064-10-001000 |

| Do N | lot Populate                             |                                                          |                        |                      |

| 0    | C24                                      | CAP, SMD, 1206, ROHS                                     |                        |                      |

| 0    | R60                                      | RES, SMD, 0805, 68mΩ, ROHS                               |                        |                      |

| 0    | J1, J10, J11                             | DO NOT POPULATE                                          |                        |                      |

| 0    | TP1, TP9,<br>TP10                        | DO NOT POPULATE                                          |                        |                      |

| 0    | CB1-CB8                                  | CONN-HEADER, 1X1, BRKAWY 1X64,2.54mm, 0.195x0.118, ROHS  | Mill-max               | 800-10-064-10-001000 |

| 0    | SCL, SDA,<br>TMPO, VREF,<br>xT1, xT2     | CONN-HEADER, 1X3, BRKAWY 1X64, 2.54mm, 0.195x0.118, ROHS | Mill-max               | 800-10-064-10-001000 |

| 0    | FETSOFF,<br>PSD, INT, SD,<br>EOC, RGO    | CONN-HEADER, 1X6, BRKAWY 1X64, 2.54mm, 0.195x0.118, ROHS | Mill-Max               | 800-10-064-10-001000 |

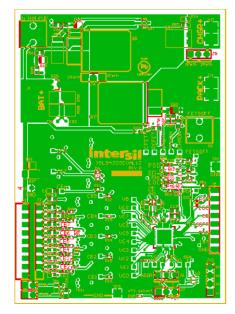

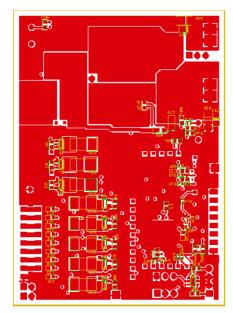

# 6.2 Layout

Figure 47. Top Layer

Figure 49. Middle Layer 2

Figure 48. Middle Layer 1

Figure 50. Bottom Layer

ISL94203EVKIT1Z 7. Hardware Overview

## 7. Hardware Overview

The hardware design follows recommendations in the datasheet. However, this section provides some additional guidelines and explanations.

# 7.1 Jumpers

There are three user selectable options on the ISL94203EVKIT1Z board.

## 7.1.1 ADDR

This jumper selects the I<sup>2</sup>C address. Normally this jumper connects to the 0 position. With the jumper set to the 1 position, the GUI I<sup>2</sup>C address value must be changed to 52.

## 7.1.2 xT2 Select

There are three external thermistors on the board. There are two near the battery connectors. These can be used to monitor the battery cells (connect external thermistors to connectors xTh1 or xTH2a and remove the on-board thermistors Th1 and Th2a). There is a third resistor located under the discharge power FET.

The xT2Select jumper allows the ISL94203 to monitor either the Th2a thermistor near the battery terminals (CELL position) or the Th2b thermistor under the power FET (FET position). When monitoring the FET thermistor, you might want to check the **xT2 Monitors FET** box in the GUI (see <u>"Pack Options" on page 26</u>).

# 7.1.3 Power FET Configuration

The board allows for both a single charge/discharge path and a separate charge/discharge path. Configuring the options requires two jumpers. For a single path, connect a shunt on the 1Path side of  $J_4$ . Also connect a shunt on the 1Path side of jumper  $J_9$ . In this configuration both charge and discharge connections of the pack connect to the DSCG+ pin.

For the separate charge and discharge path, connect a shunt on  $J_4$  and  $J_9$  on the 2Path side of each. In this configuration, discharge is on the DSCG+ pin and charge is on the CHRG+ pin.

If the plan is to test the board with significant amounts of current, replace the shunt with some soldered braided wire to complete the circuit. In this way the board should be able to handle a discharge current of 20A and charge current of 2.5A.

Figure 51. Solder Jumpers for Higher Current

## 7.2 AFE

The Analog Front End (AFE) of the ISL94203 adds external cell balancing components. The cell balance output from each cell balance pin is a constant current of about 25µA. This generates about 8.25V across the 330k resistor between the gate and source of the balancing transistor. If a balance FET with lower gate voltage requirements is desired, reduce the value of the gate resistor.

The evaluation board uses  $100\Omega$  cell balance resistors, so it balances about 40mA of current. The board also includes LEDs on each cell balance circuit to indicate when the cell balance is active.

The cell input filters consist of a 1k resistor, a 4.7nF capacitor to ground, and a 10nF capacitor cell-to-cell. These can be changed to suit the application, but the following guidelines should be considered.

ISL94203EVKIT1Z 7. Hardware Overview

• The 1k resistor can be reduced, but this makes the part more susceptible to input currents during hot plug of the battery cells. A smaller input resistor would also require higher value capacitors to ground to maintain the same filter. Higher value resistors on the upper cells would be higher cost.

- The 1k resistor can be increased. The limit relates to the accuracy of measurement. In the worst case conditions, there is a difference of about 2µA of bias current on the inputs. The ISL94203 is factory calibrated assuming an input 1k resistor. An extra 1k input resistor can generate up to 2mV of error. Larger input resistors increase this error.

- The capacitors from each input to ground provide a better filter than the capacitors across each input. However, differences in capacitors on adjacent inputs could result in some voltage errors on the input. Both capacitors to ground and capacitors across inputs are provided on the board, but the application may not need both.

- Larger input capacitors can affect the open wire detection circuit. If larger capacitors are used and the open wire circuit does not seem to detect the open condition, increase the Open Wire Sample Time timer value in the GUI.

## 7.3 Protection Circuits

The board contains several protection components that should be on any application.

- There should be diodes on VBATT, DSCG+ and CHRG+ to GND to prevent negative voltages on the pins of the ISL94203. The schematics show the use of 43V zener diodes, so the inputs are also protected against high voltage transients.

- The board provides transient voltage suppressors on the pack pins to help minimize problems with ESD on the board

- There is a protection device (USBLC6) on the  $I^2C$  inputs to minimize damage due to ESD on the  $I^2C$  connector. While this component helps protect against ESD, it is also a problem for the board. Because this component has internal diodes between the  $I^2C$  pins and the RGO power pin, connecting the  $I^2C$  interface to an externally powered  $\mu C$  before the  $I^2C$  powers up prevents proper power-up of the  $I^2C$  interface to an externally powered  $\mu C$  before the  $\mu C$  and the evaluation board,  $U^2$  can be removed from the board and replaced with jumpers across pins 1 to 6 and 3 to 4. This allows the  $\mu C$  to power up before the  $I^2C$  powers up.

- Back to back diodes are connected across the current sense inputs to prevent excessive differential voltage across these pins.

## 7.4 Push Buttons

The board provides two push buttons for ease of use and evaluation purposes. These are not required in an application.

- The wake up push button simulates the connection of a pack to a charger. It does this by connecting the CHRG+ pin to VDD using a 1k series resistor. The device sees this as a charger connection. The ISL94203 can also be wakened by momentarily connecting a resistor from the DSCG+ pin to GND. Use a 2k resistor to minimize current when the power FETs turn on. During manufacture of the battery pack, the finished pack can be connected to a charger, or this wake up switch can be included on an external jig to power up the board prior to final programming.

- The FETSOFF pin connects directly to the FETSOFF input of the ISL94203. When pressed, the power FETs and cell balance FETs turn off. Normally in a system, this input would connect to a µC or an external control source. If FETSOFF connects off board, add a 3V zener diode to GND to prevent glitches on this input from going too high or negative.

## 7.5 LED Indicators

There are 4 LED indicators on the board. The LEDs are not required in a real application, they are used here to provide quick monitoring of the system. The LEDs are RGO (Green), EOC (Red), SD (Red), and PSD (Red).

The LED indicator circuits use current mirrors to drive the LEDs. There are several reasons for this.

ISL94203EVKIT1Z 7. Hardware Overview

• The ISL94203 RGO regulator output voltage is 2.5V (2.25V to 2.75V). Because of this voltage and range, it is difficult to directly drive LEDs that have a forward voltage drop of 1.8V to 2.3V while controlling current to acceptable levels.

- When directly driving the LEDs from the RGO output using a current limiting resistor, small variations in the supply voltage result in large changes in LED brightness.

- If the LEDs connect direct to the RGO output, the 4 LEDs would pull at least 5mA from the RGO output. While

this is within the capability of the RGO, it could lead to some internal heating of the die. Because this board is for

evaluation, and an actual application would not normally have the LEDs, an indirect approach to powering the

LEDs was adopted.

The current mirrors use a resistor on one side to provide a current gain. The LEDs are each driven with ~1mA of current from VBATT, but the drain from the RGO output is only ~40µA.

Figure 52. Battery Connection Options Using the ISL94203EVKIT1Z Board

ISL94203EVKIT1Z 8. Errata/Q&A

# 8. Errata/Q&A

Q: When I power the board, the device does not power up correctly. It looks like it is in sleep mode.

**A:** Before applying power to the evaluation board, disconnect the I<sup>2</sup>C cable. When the board is powered, connect the I<sup>2</sup>C interface. The reason for this is that U2 on the board has internal protection diodes from the I<sup>2</sup>C traces to RGO. When SCL and SDA pull up externally to 3.3V the ISL94203 is partially powered, so it does not complete its power-up cycle.

Q: Cell measurement accuracy does not match the specifications in the datasheet.

A: There are some other potential reasons for inaccurate readings:

- The source of measurement should have a low output impedance. A string of resistors that sets the input voltages, like the MCB\_PS\_Z board can have small changes in the input voltage as the ISL94203 samples each cell. Later models of the MCB\_PS\_Z board have 10μF capacitors across each input. These capacitors should minimize sampling errors.

- The ADC reading should be compared with the voltage on the PCB before the input resistors (at J<sub>2</sub>). If the voltages are compared with DVM readings at the battery pack where there is a long cable, there should be separate wires for GND and VC0; and for VC8 and VBAT. The reason for this is that the VBAT and GND leads might carry a lot of current, so there can be voltage drops across the wires. The VC0 and VC8 terminals are Kelvin connections that do not carry much current. Cell voltage measurements are based on VC0 and VC8, not GND and VBAT.

- Soldering the board to the PCB can change the stresses on the package from what they were during device calibration. This can change the value of the voltage reference, which changes the ADC converted value.

This does not affect the relative voltage readings. If there is an external μC, an offset can be added to the μC to correct for solder induced stresses.

**Q:** I changed the **Pack Settings** tab such that the **CB during EOC** button is checked. But after power cycling the part, the **CB during EOC** is no longer checked and the part is not balancing during End of Charge.

**A:** After clicking on any of the option bits in the **Pack Settings** tab or on the main screen (above the FET control indicators) it is necessary to do a **Write EEPROM** either on the **Pack Settings** tab or the **Config Mem** tab. Without this write operation the change only resides in the ISL94203 Configuration RAM space.

Q: When I repeatedly read the EEPROM memory in the configuration tab, the communications lock up.

**A:** There was a problem with the old GUI code. The best solution is to get the new Win7/8 code. This new code does not have this problem. Until you have the new code, the best way to clear this, without removing the battery from the board, is to remove the I<sup>2</sup>C cable and use a jumper to momentarily connect and release the SCL line to VSS (it is pulled up by a resistor). This creates a clock whine. Do this up to 9 times to clear the ISL94203 port. Then reconnect the I<sup>2</sup>C cable.

# 9. FET Gate Drive Rise/Fall Characteristics

Verify basic digital logic, analog interface, level shifters, and charge pump operation.

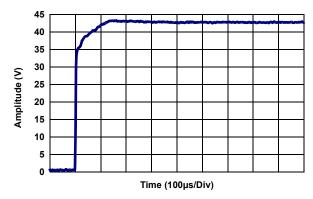

Figure 53. DFET Rise

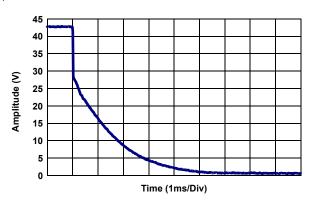

Figure 54. DFET Fall

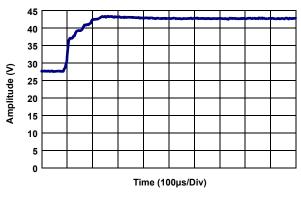

Figure 55. CFET Rise

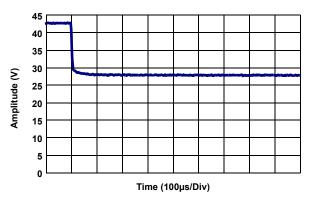

Figure 56. CFET Fall

ISL94203EVKIT1Z 10. Revision History

# 10. Revision History

| Rev. | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.00 | May.9.19 | Updated to new template Software Installation on page 3, step 1changed from: "Connect the ISLUSBI2C USB to the PC." to: "Connect the ISL94202INTFACEKIT1Z to the PC through the USB port. Quick Hardware Setup on page 3: step 2 changed from: JP2/8Cell to: J13. Updated Figure 2. Removed mention of the Cascade feature Pack Options section page 26, last paragraph deleted and Figure 36 replaced. Added Revision History Stamped Not Recommended for New Designs Updated disclaimer |

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.