# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## M66592FP/WG

ASSP (USB2.0 Peripheral Controller)

REJ03F0111-0100Z Rev1.00 2004.10.01

## 1 Overview

## 1.1 Overview

The M66592 is a USB 2.0 peripheral controller that is compliant with USB (Universal Serial Bus) specification Rev. 2.0 for both Hi-Speed and Full-Speed transfers. This controller has a built-in USB transceiver and supports all of the transfer types defined by the USB specification. The compact package and low power consumption make it ideal for use in mobile devices.

The M66592 has a 5 kB built-in buffer memory for data transfers and enables use of up to eight pipes. For pipes 1 to 7, any end point numbers can be assigned, based on the user's system. The M66592 can be connected to the CPU using either a separate bus or a multiplex bus. Moreover, a split bus interface (dedicated DMA interface) is provided independent of the CPU bus interface, making this an ideal choice for systems that require transfer of large volumes of data at high speed.

#### 1.2 Features

## 1.2.1 USB Rev. 2.0 Hi-Speed supported

- ♦ Compliant with USB specification Rev. 2.0

- ◆ Both Hi-Speed transfer(480 Mbps)and Full-Speed transfer (12 Mbps) are supported

- ♦ Built-in Hi-Speed / Full-Speed USB transceiver

- ◆ Can be operated as a Hi-Speed / Full-Speed peripheral controller

## 1.2.2 Reduced power consumption

- ◆ 1.5 V core power supply

- ♦ Low power consumption makes this ideal for mobile devices

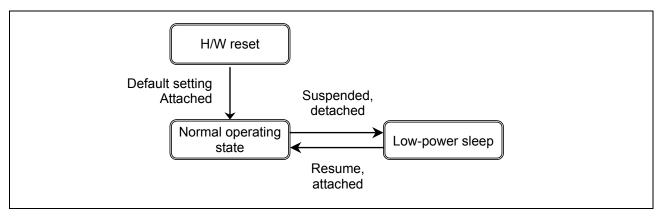

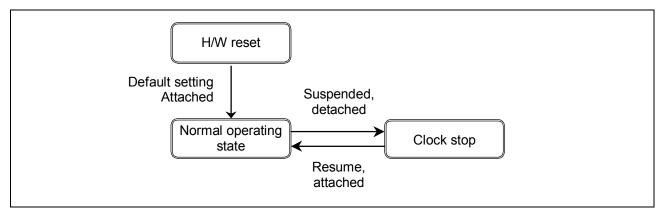

- ♦ Low-power mode (power-saving sleep state) supported to reduce power consumption during suspended operation

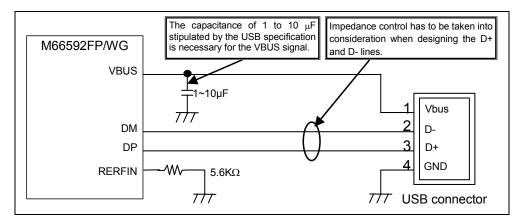

## 1.2.3 Space-saving installation supported

- Few external elements are used, so less space is required for mounting

- VBUS signal can be connected directly to the controller pin

- Built-in D+ pull-up resistor

- Built-in D+ and D- terminating resistors (for Hi-Speed operation)

- Built-in D+ and D- output resistors (for Full-Speed operation)

- ♦ Compact 64-pin package used

#### 1.2.4 Isochronous transfer supported

- ♦ All types of USB transfers supported

- Control transfers

- Bulk transfers

- Interrupt transfers (High-Bandwidth transfers are not supported)

- Isochronous transfers (High-Bandwidth transfers are not supported)

#### 1.2.5 Bus interfaces

- ♦ The user can select either a 1.8 V or 3.3 V bus interface power supply

- ♦ 16-bit CPU bus interface

- 16-bit separate bus and 16-bit multiplex bus supported

- 8-bit and 16-bit DMA interface (slave function) supported

- ♦ 8-bit split bus (dedicated external DMA interface) supported

- ♦ DMA interface has two channels built into it.

- ♦ DMA transfer enables high-speed access of 40 MB/sec.

## 1.2.6 Pipe configuration

- ♦ Internal 5 KB buffer memory for USB communication built in

- ♦ Up to 8 pipes(endpoints) can be selected (including the default control pipe for endpoint 0)

- ♦ Programmable pipe configuration

- End point numbers can be assigned flexibly to PIPE1to PIPE7.

- ♦ Transfer conditions that can be set for theeach pipe

- Pipe 0: Control transfer, continuous transfer mode, 256-byte fixed single buffer

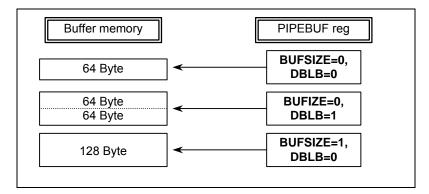

- PIPE1 and PIPE2: Bulk transfer / isochronous transfer, continuous transfer mode, programmable buffer size (up to 2 KB; double buffer can be specified)

- PIPE 3 to PIPE5: Bulk transfer, continuous transfer mode, programmable buffer size (up to 2 KB; double buffer can be specified)

- PIPE6 and PIPE7: Interrupt transfer, 64-byte fixed single buffer

#### 1.2.7 Other functions

- ♦ Automatic recognition of Hi-Speed operation or Full-Speed operation based on automatic response to the reset handshake

- Byte endian swap function when using 16-bit data transfers

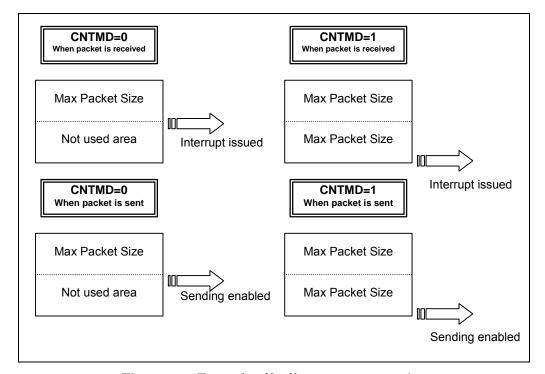

- ♦ Transaction count function when using DMA transfers

- ♦ DMA transfer termination function using external trigger (DEND pin)

- ♦ Control transfer stage control function

- ♦ Device state control function

- ♦ Auto response function for SET\_ADDRESS request

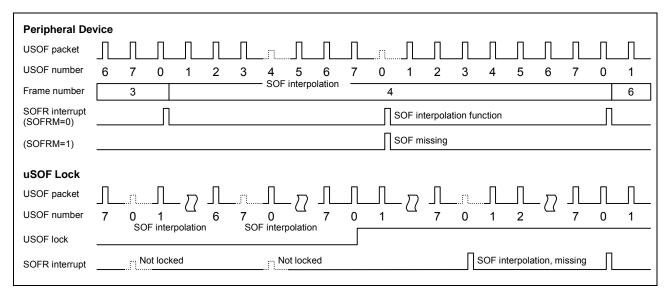

- ♦ SOF interpolation function

- ♦ SOF pulse output function

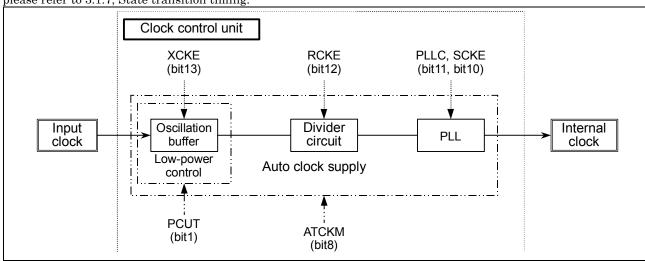

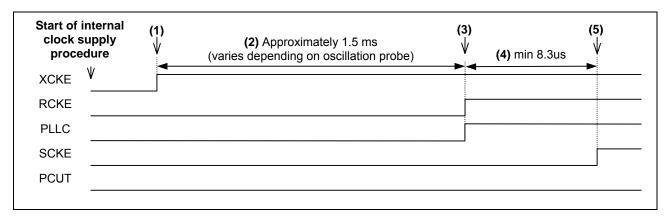

- ♦ Three types of input clocks can built into the PLL and are available for selection

- Input clocks of 48 MHz / 24 MHz / 12 MHz can be selected

- ◆ Zero-Length packet addition function (**DEZPM**) when ending DMA transfers using the DEND pin

- ◆ BRDY interrupt event notification timing change function (**BFRE**)

- ◆ Function that automatically clears the buffer memory after the data for the pipe specified at the DxFIFO port has been read (DCLRM)

- ◆ Function to automatically supply a clock from the low-power sleep state (ATCKM)

- ◆ NAK setting function for response PID generated by end of transfer (SHTNAK)

- ♦ NAK response assignment function (NRDY)

### 1.2.8 Applications

Digital video cameras, digital still cameras, printers, external storage devices, portable information terminals, USB audio devices

Also: GeneralOrdinary PC peripheral devices equipped with Hi-Speed USB

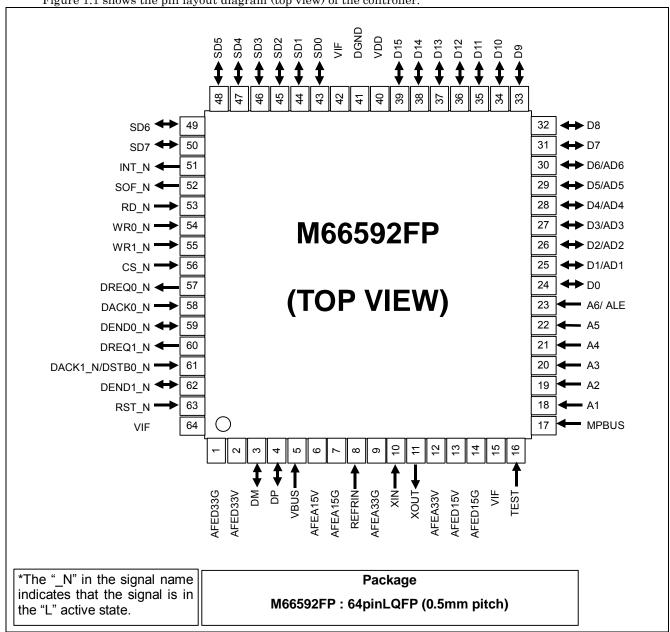

## 1.3 Pin layout diagram

Figure 1.1 shows the pin layout diagram (top view) of the controller.

Figure 1.1 Pin layout diagram of M66592FP

#### M66592WG(TOP VIEW) DGND VDD 8 SD6 SD4 SD2 D13 D10 D9 7 SD7 SD5 SD3 VIF D15 D12 D8 D7 6 RD\_N SOF\_N INT\_N SD0 D14 D11 D6/AD6 D5/AD5 CS\_N WR0\_N D2/AD2 D1/AD1 D4/AD4 5 WR1\_N SD1 D3/AD3 DENDO\_N DREQ1\_N DREQ0\_N DACKO\_N A6/ALE A5 A2 D0 4 DACK1\_N /DSTB0\_N VIF DEND1\_N AFEA15V AFEA33G AFEA33V А3 3 A4 2 RST\_N AFED33V **VBUS** AFEA15G **XOUT** AFED15G **TEST** Α1 AFED33G DM DP REFRIN XIN AFED15V VIF **MPBUS** 1 В С D F Α Ε G Н \*The "\_N" in the signal name indicates that the signal is in **Package** M66592WG: 64pin FBGA (0.8mm pitch) the "L" active state.

Figure 1.2 Pin layout diagram of M66592WG

# 1.4 Description of pins

Table 1.1 describes the controller pins.

Table 1.1 Pin descriptions

| Category                    | Pin name                            | Name                         | I/O | Function                                                                                                                                                                                                                                                                              | Pin                 | Sta             | ate of pin        | *7)                      |

|-----------------------------|-------------------------------------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-------------------|--------------------------|

|                             |                                     |                              |     |                                                                                                                                                                                                                                                                                       | count<br>(Pin nos.) | RST_N="<br>L"   | RST_N<br>goes "H" | PCUT=1                   |

| CPU bus interface           | D15-0                               | Data Bus                     | I/O | This is a 16-bit data bus.                                                                                                                                                                                                                                                            | 16<br>(24-39)       | *4)             | *4)               | Input<br>(Hi-z)          |

|                             | AD6-1                               | Multiplex<br>Address Bus     | I/O | When a multiplex bus is specified, this group of pins is used on a time-shared basis for some of the data buses (D6-D1), or for 6 bits of the address bus (A6-A1).                                                                                                                    | ,                   |                 |                   | ,                        |

|                             | A6-1                                | Address Bus                  | IN  | Because the data bus consists of 16 bits, there is no A0.                                                                                                                                                                                                                             | 6<br>(18-23)        | *5)             | *5)               | Input<br>(Hi-z)<br>Input |

|                             | ALE                                 | Enable                       |     | When a multiplex bus is specified, the A6 pin is used as the ALE signal.                                                                                                                                                                                                              |                     | Input           | Input             |                          |

|                             | CS_N                                | Chip Select                  | IN  |                                                                                                                                                                                                                                                                                       | 1<br>(56)           | Input<br>*6)    | Input<br>*6)      | Input                    |

|                             | RD_N                                | Read Strobe                  | IN  | Setting this to the "L" level reads data                                                                                                                                                                                                                                              | 1<br>(53)           |                 |                   | Input                    |

|                             | WR0_N                               | D7-0 Byte Write<br>Strobe    | IN  | At the rising edge, D7-D0 are written to                                                                                                                                                                                                                                              | 1<br>(54)           | Input<br>*6)    | Input<br>*6)      | Input                    |

|                             | WR1_N                               | D15-8 Byte Write<br>Strobe   |     | At the rising edge, D15-D8 are written to                                                                                                                                                                                                                                             | 1<br>(55)           |                 |                   | Input                    |

|                             | MPBUS*3                             |                              | IN  | Setting this to the "L" level selects a                                                                                                                                                                                                                                               | 1<br>(17)           |                 |                   | Input<br>*3)             |

| Split bus interface         | SD7-0                               | Split Data Bus               | I/O | If a split bus is selected, this functions as the data bus for the split bus.                                                                                                                                                                                                         | 8<br>(43-50)        | Input<br>(Hi-z) | Input<br>(Hi-z)   | Input<br>(Hi-z)          |

|                             | DREQ0_N*1<br>DREQ1 N*1              | DMA Request                  | OUT | This notifies the system of a D0FIFO port or D1FIFO port DMA transfer request.                                                                                                                                                                                                        | 2<br>(57, 60)       | H               | H                 | H/L<br>*8)               |

|                             | DACK0_N*1<br>DACK1_N*1<br>DSTB0_N*2 | Acknowledge<br>Data Strobe 0 |     | Input the DMA Acknowledge signal for the D0FIFO or D1FIFO port.  This functions as the data strobe signal for the D0FIFO port.  Because it is also used for the DMA Acknowledge signal of the D1FIFO port, the DSTB0_N function cannot be used if the DACK1_N function is being used. |                     | ,               | Input             | Input                    |

|                             | DEND1_N*1                           | End                          |     | direction> This receives the Transfer End signal from another peripheral chip or the CPU as an input signal. <in access="" direction="" fifo="" port="" reading="" the=""> This indicates the transfer end data as an output signal.</in>                                             | 2 (59, 62)          |                 | 71 is \           | Input<br>(Hi-z)          |

| Interrupt/<br>SOF<br>output | INT_N                               | Interrupt                    |     | In the "L" active state, this notifies the system of various types of interrupts relating to USB communication.                                                                                                                                                                       | 1<br>(51)           | Н               | H                 | H                        |

|                             | SOF_N                               | SOF pulse output             |     | When an SOF is detected in the "L" active state, an SOF pulse is output.                                                                                                                                                                                                              | 1<br>(52)           | Н               | Н                 | Н                        |

| Clock                       | XIN                                 | Oscillation input            |     | A crystal oscillator should be connected                                                                                                                                                                                                                                              | 1<br>(10)           |                 |                   |                          |

|                             | XOUT                                | Oscillation output           | OUT | external clock input, the external clock                                                                                                                                                                                                                                              | 1<br>(11)           |                 |                   |                          |

| Category                 | Pin name | Name                                        | I/O | Function                                                                                                                  | Pin                  | Sta             | ate of pin        | *7)             |

|--------------------------|----------|---------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|-------------------|-----------------|

|                          |          |                                             |     |                                                                                                                           | count<br>(Pin nos.)  | RST_N="<br>L"   | RST_N<br>goes "H" | PCUT=1          |

| System control           | RST_N    | Reset signal                                | IN  | At "L" level, the controller is initialized.                                                                              | 1<br>(63)            | Input<br>(L)    | Input<br>(H)      | Input<br>(H)    |

|                          | TEST     | Test signal                                 | IN  | This should be fixed at "L" or open.                                                                                      | 1<br>(16)            |                 |                   |                 |

| USB bus interface        |          | USB D+ data                                 | I/O | This should be connected to the D+ pin of the USB bus.                                                                    | (4)                  | Input<br>(Hi-z) | Input<br>(Hi-z)   | Input<br>(Hi-z) |

|                          | DM       | USB D- data                                 | I/O | This should be connected to the D- pin of the USB bus.                                                                    | 1<br>(3)             |                 | Input<br>(Hi-z)   | Input<br>(Hi-z) |

| VBUS<br>monitor<br>input | VBUS     | VBUS input                                  | IN  | disconnected state of the Vbus can be detected. If This pin is not connectted with Vbus of a USB bus, connect it with 5V. | 1<br>(5)             | Input<br>(Hi-z) | Input<br>(Hi-z)   | Input<br>(Hi-z) |

| Reference resistance     |          | Reference input                             | IN  | through a 5.6 kΩ±1% resistance.                                                                                           | 1<br>(8)             |                 |                   |                 |

| Power<br>supply /<br>GND | AFEA33V  | Transceiver unit analog power supply        | -   | This should be connected to 3.3 V.                                                                                        | 1<br>(12)            |                 |                   |                 |

|                          | AFEA33G  | Transceiver unit analog GND                 | -   |                                                                                                                           | 1<br>(9)             |                 |                   |                 |

|                          | AFED33V  | Transceiver unit digital power supply       | -   | This should be connected to 3.3 V.                                                                                        | 1 (2)                |                 |                   |                 |

|                          | AFED33G  | Transceiver unit digital GND                | -   |                                                                                                                           | 1<br>(1)             |                 |                   |                 |

|                          | AFEA15V  | Transceiver unit analog 1.5 V power supply  |     | This should be connected to 1.5 V.                                                                                        | 1<br>(6)             |                 |                   |                 |

|                          | AFEA15G  | Transceiver unit analog GND                 | -   |                                                                                                                           | 1<br>(7)             |                 |                   |                 |

|                          | AFED15V  | Transceiver unit digital 1.5 V power supply | -   | This should be connected to 1.5 V.                                                                                        | 1<br>(13)            |                 |                   |                 |

|                          | AFED15G  | Transceiver unit digital GND                | -   |                                                                                                                           | 1<br>(14)            |                 |                   |                 |

|                          | VDD      | Core power supply                           | -   | This should be connected to 1.5 V.                                                                                        | 1<br>(40)            |                 |                   |                 |

| 1                        | VIF      | IO power supply                             | -   | This should be connected to 3.3 V or 1.8 V.                                                                               | 3<br>(15, 42,<br>64) |                 |                   |                 |

|                          | DGND     | Digital GND                                 | -   |                                                                                                                           | 1<br>(41)            |                 |                   |                 |

- \*1) The "L" active and "H" active states of these pins can be specified using the control program for the user system.

"\_N" indicates that the "L" active state is the default state.

- \*2) DSTBO\_N and DACK1\_N are assigned to the same pin, so the functions of one or the other are valid.

- \*3) The input level of the MPBUS pin needs to be established just before the end of H/W reset. Also, this should not be switched during operation.

- \*4) When CS\_N and RD\_N are "L", these pins output "H" or "L".

- $\star 5$ ) If MPBUS is "H", these pins can be made to open.

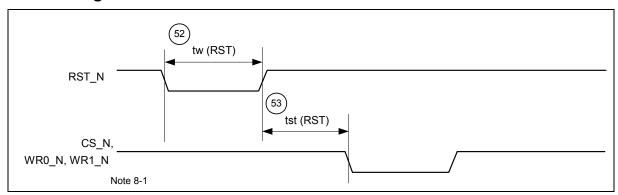

- \*6) CS\_N, WR0\_N, and WR1\_N should be kept as (a) or (b) during RST\_N="L" (from RST\_N goes "L" to right after RST\_N goes "H").

- (a) CS\_N="H"

- (b) WR0\_N="H" and WR1\_N="H"

- \*7) Discription of "State of pin"

- (a) Input: Pins are Hi-z state. Please do not make it "open" on a board.

- (b) Input(Hi-z): Pins are Hi-z state. Pins can be "open" on a board.

- (c) H, L, H/L: Output states is shown.

- \*8) These pins are in an inactive state.

Table 1.2 The example of not used pins

| Category            | Pin name        | Description          |

|---------------------|-----------------|----------------------|

| SPLIT bus interface | SD7-0           | "Open"               |

| DMA bus interface   | DREQ0_N         | "Open"               |

|                     | DREQ1_N         | "Open"               |

|                     | DACK0_N         | Fix to "H" *1)       |

|                     | DACK1_N/DSTB0_N | Fix to "H" *1)       |

|                     | DEND0_N         | "Open" *2)           |

|                     | DEND1_N         | "Open" *2)           |

| SOF output          | SOF_N           | "Open"               |

| System control      | TEST            | Fix to "L" or "Open" |

| VBUS monitor input  | VBUS            | Fix to 5V *3)        |

$<sup>\</sup>star 9$ ) When DACKn\_N pin is not used, please set DACKA bit of DMAnCFG register as "0" (n=0,1).

$<sup>\</sup>star 10$ ) When DENDx\_N pin is not used, please set DENDA bit of DMAnCFG register as "0" (n=0,1).

<sup>\*11)</sup> If this pin is not connected with Vbus of a USB bus, fix to 5V.

## 1.5 Pin function configuration

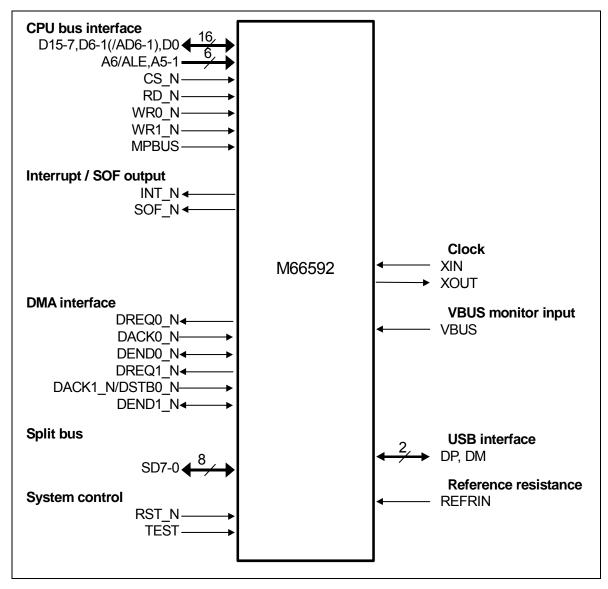

Figure 1.3 shows a diagram of the pin function configuration of the controller.

Figure 1.3 Pin function configuration diagram

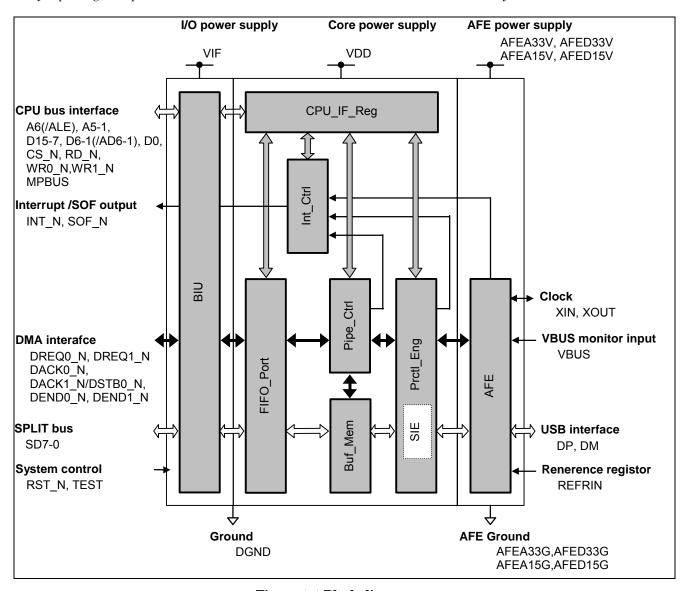

## 1.6 Block diagram

The controller is configured with an analog front end unit (AFE), a protocol engine unit (Prtcl\_Eng) that includes an SIE, a pipe control unit (Pipe\_Ctrl), a FIFO port unit (FIFO\_Port), a buffer memory unit (Buf\_Mem), an interrupt control unit (Int\_Ctrl), a bus interface unit (BIU), and a CPU interface register unit (CPU\_IF\_Reg). Figure 1.4 shows a block diagram of the controller.

When data is being sent and received between the controller and a host controller connected on the USB bus, a buffer memory assigned to each of the pipes is used. Two-way communication is possible by the controller changing data stored in the buffer memory into USB data packets and outputting them to the USB bus using serial output, and by inputting data packets on the USB bus which are then stored in the buffer memory.

Figure 1.4 Block diagram

### 1.7 An overview of functions

#### 1.7.1 Bus interfaces

The controller supports the bus interfaces noted below.

#### 1.7.1.1 External bus interface

The controller uses a CPU bus interface to access control registers.

The bus interface with the CPU supports the two access methods noted below. The Chip Select pin (CS\_N) and the three strobe pins (RD\_N, WR0\_N and WR1\_N) should be used for access.

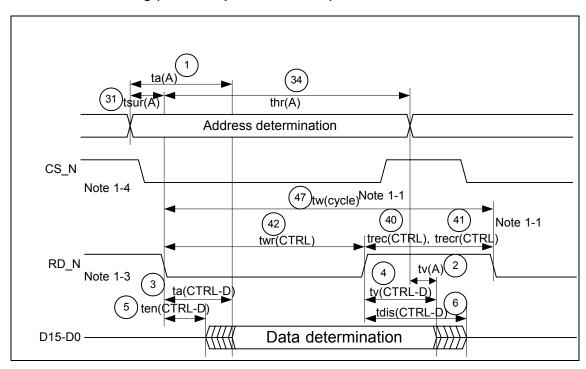

(1) (16-bit separate bus

The six address buses (A6-1) and the 16 data buses (D15-0) are used.

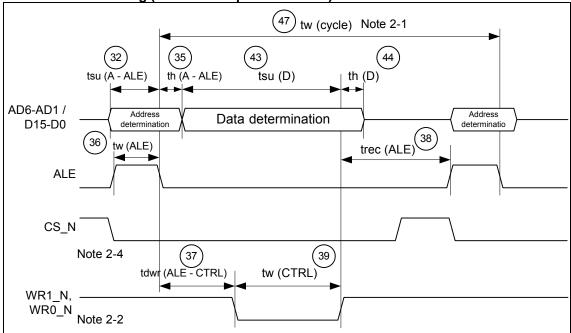

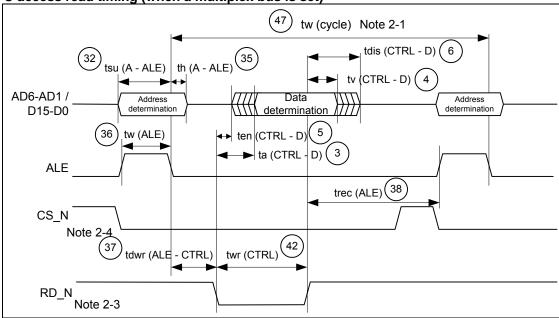

(2) 16-bit multiplex bus

The ALE pin (ALE) and the 16 data buses (D15-0) are used. The data buses are used for addresses and data on a time-shared basis.

The separate bus and multiplex bus are selected based on the MPBUS pin signal level when the H/W reset is canceled.

#### 1.7.1.2 Accessing the buffer memory

The controller supports the two methods described below to access the USB data transfer buffer memory.

(1) CPU access

Addresses and control signals should be used to write data to the buffer memory or read it from the buffer memory.

(2) DMA access

Data should be written to the buffer memory of the controller, or read from the buffer memory, from the DMAC in the CPU or a dedicated DMAC.

USB data communication is done using Little Endian. There is a byte Endian swap function for FIFO port access, and when using 16-bit access, the Endian can be switched using the register settings.

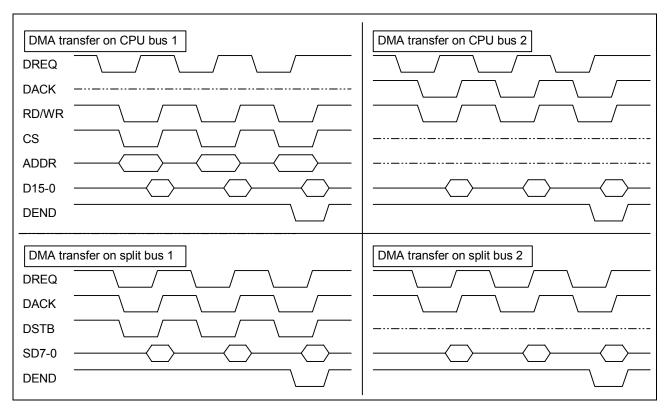

## 1.7.1.3 DMA access methods

When using DMA access to access the buffer memory, the two access methods noted below can be selected.

- (1) Method using a bus shared with the CPU

- (2) Method using a dedicated bus (split bus)

### 1.7.2 USB events

The controller notifies the user's system of USB operation events by means of interrupts. Moreover, with a pipe for which the DMA interface has been selected, the system is notified that the buffer memory of the controller can be accessed by asserting the DREQ signal.

There are eight types of interrupts and 35 causes for interrupts being generated. The user can select whether or not interrupt notification is permitted for each type and each cause, using settings in the control program for the user system.

#### 1.7.3 USB data transfers

The controller is capable of all types of transfers: USB communication control transfers, bulk transfers, and interrupt transfers, as well as isochronous data transfers. The pipes noted below can be used with data transfers for various types of communication.

- (1) Dedicated control transfer pipe

- (2) Two dedicated interrupt transfer pipes

- (3) Three dedicated bulk transfer pipes

- (4) Two pipes for which bulk transfers or isochronous transfers can be selected

The settings necessary for USB transfers, such as the transfer type, end point number, and maximum packet size, should be set for each pipe, in conjunction with the user system.

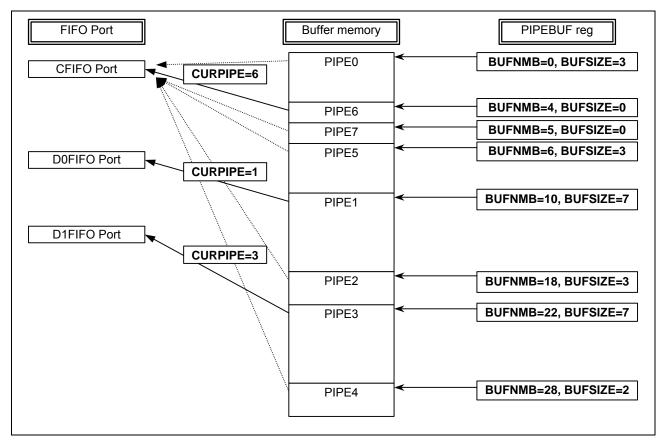

Also, the controller has a built-in 5 kB buffer memory. For a dedicated bulk transfer pipe and the pipes for which bulk transfers or isochronous transfers can be selected, settings such as the buffer memory assignment and buffer operation mode which are based on the user system should be entered. The buffer operation mode setting can be set to enable high-speed data transfers with few interrupts, using the double-buffer configuration and data packet continuous transfer function.

Access to the buffer memory from the control CPU of the user's system and the DMA controller is done through the three FIFO port registers.

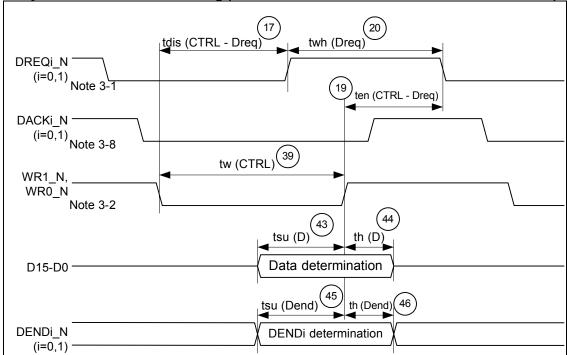

#### 1.7.4 DMA interface

The DMA (Direct Memory Access) interface consists of data transfers between the user system and the controller using the DxFIFO port, and is a type of data transfer in which the CPU is not involved. The controller is equipped with a 2-channel DMA interface and has the following functions.

- (1) A transfer end notification function using the Transfer End signal (DEND signal)

- (2) An auto-clear function activated when a Zero-Length packet is received

- (3) A "send addition" function used to send a Zero-Length packet based on input of the Transfer End signal (DEND signal)

- (4) A transfer end function using a transaction counter function

The controller supports the two types of DMA interfaces noted below.

- (1) Cycle steal transfer

- With this type of transfer, the DREQ pin is repeatedly asserted and negated each time a data transfer (1 byte / 1 word) is carried out.

- (2) Burst transfer

- With this type of transfer, the DREQ pin remains asserted for the pipe buffer area assigned to the pertinent FIFO port, or until the transfer is ended by the DEND signal, without ever being negated.

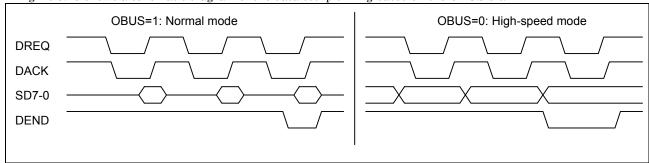

Also, the following can be selected as the DMA interface handshake signal (pin): CS\_N, RD\_N, or WR\_N, or DACK\_N. With DMA transfers using a split bus, high-speed DMA transfers are possible by changing the data setup timing, by operating the **OBUS** bit of the **DMAxCFG** register.

#### 1.7.5 SOF pulse output function

An SOF pulse output function is provided that notifies the system of the timing at which SOF packets are received. This function outputs pulses at fairly regular intervals, using an SOF interpolation timer, even if an SOF packet is damaged.

### 1.7.6 External elements integration

The controller has the following external elements built into it. Also, because the VBUS pin can withstand 5 V, the user system can input the VBUS signal directly to the controller.

- (1) Resistors necessary for D+ and D- line control

This makes it possible to configure the system without adding an external resistor.

- (2) 48 MHz and 480 MHz PLL One of three external clocks (12 MHz / 24 MHz / 48 MHz) can be selected and Hi-Speed and Full-Speed operation carried out.

Providing this many external elements in the controller and using a 64-pin compact package mean that less space is required for mounting in the user system.

## 1.7.7 Low-power sleep state function

The controller is equipped with a low-power sleep state that reduces current consumption. The low-power sleep state functions effectively under the following circumstances.

- (1) When there is no host controller connected

- (2) When the device state is shifted to the suspended state, and USB data transfer is not necessary

The system is returned from the low-power sleep state to the normal operating state using a designated interrupt, or by dummy writing to the controller.

# 2 Registers

## Reading the table of registers

① Bit no. Each register is connected to a 16-bit internal bus.

Odd-numbered addresses will use b15 to b8, and even-numbered addresses b7 to b0.

② Status after reset

This indicates the default state of the register immediately after a reset operation, and after recovering from the low-power sleep state.

H/W Reset is the default state when an external reset signal has been input from the RST\_N

S/W Reset is the default state when the user system has carried out a bit operation using the USBE bit.

USB Reset is the default state when the controller has detected a USB bus reset.

Low-power Sleep is the default state when the controller has recovered from the low-power sleep state.

Items that require particular attention during a reset operation are noted under "Notes". "-" indicates a state in which there is no operation by the controller, and the user setting is retained

"?" indicates that a value is undecided.

S/W Access Condition

This is the condition in effect if the user system control program is accessing a register.

⑤ H/W Access Condition

This is the condition in effect if the controller is accessing a register during any operation other than a reset.

R ..... Read Only

W ..... Write Only

R/W ..... Read / Write

R(0) ..... "0"Read Only

W(1) ..... "1"Write Only

© Note

This is the number of detailed explanations and the number of notes.

Bit Name

This indicates the bit symbol and bit name.

This describes active items and notes.

#### <Example of table notation>

Nothing is placed in shaded sections. These should be fixed at "0".

| ⊕ Bit number → → → → → → → → → → → → → → → → → → → | <u> 18</u> | 14 | 13    | 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------------------|------------|----|-------|-------|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit symbol -                                       | · <b>/</b> |    | B bit | C bit |    |    |   |   |   |   |   |   |   |   |   |   |

| ②H/W reset →                                       | ?          | 0  | 0     | 0     |    |    |   |   |   |   |   |   |   |   |   |   |

| S/W reset →                                        | ?          | 0  | 0     | -     |    |    |   |   |   |   |   |   |   |   |   |   |

| USB reset →                                        | ?          | 0  | -     | -     |    |    |   |   |   |   |   |   |   |   |   |   |

| Low-power sleep state→                             | ?          | 0  | 0     | 0     |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit | Name                   | Function                     | S/W   | H/W | Note  |

|-----|------------------------|------------------------------|-------|-----|-------|

| 15  | Nothing is placed here | . It should be fixed at "0". |       |     |       |

| 14  | A bit                  | 0: Operation disabled        | R/W   | R   | 2.3.1 |

|     | AAA enabled            | 1 : Operation enabled        |       |     | *1    |

| 13  | B bit                  | 0: "L"output                 | R     | W   | 2.3.2 |

|     | BBB operation          | 1: "H"output                 |       |     | *1    |

| 12  | C bit                  | 0:                           | R(0)/ | R   | 2.3.2 |

|     | CCC control            | 1:                           | W(1)  |     |       |

|     |                        |                              |       |     |       |

|     | <b>⑦</b>               | 8                            | 4     | (5) | 6     |

#### «Note»

\*1) If the A bit and B bit are being accessed in succession for writing, an access cycle of 300 ns is necessary.

# 2.1 Table of registers

Table 2.1 shows the controller registers.

Table 2.1 Registers

| Address | Symbol    | Name                                             | Index |

|---------|-----------|--------------------------------------------------|-------|

| 00      | SYSCFG    | System configuration control register            | 2.3   |

| 02      | SYSSTS    | System configuration status register             | 2.3   |

| 04      | DVSTCTR   | Device state control register                    | 2.4   |

| 06      | TESTMODE  | Test mode register                               | 2.4   |

| 08      |           |                                                  |       |

| 0A      | PINCFG    | Data pin configuration register                  | 2.5   |

| 0C      | DMA0CFG   | DMA0 pin configuration register                  | 2.5   |

| 0E      | DMA1CFG   | DMA1 pin configuration register                  | 2.5   |

| 10      | CFIFO     | CFIFO port register                              | 2.6   |

| 12      |           |                                                  |       |

| 14      | D0FIFO    | D0FIFO port register                             | 2.6   |

| 16      |           |                                                  |       |

| 18      | D1FIFO    | D1FIFO port register                             | 2.6   |

| 1A      |           |                                                  |       |

| 1C      |           |                                                  |       |

| 1E      | CFIFOSEL  | CFIFO port selection register                    | 2.6   |

| 20      | CFIFOCTR  | CFIFO port control register                      | 2.6   |

| 22      | CFIFOSIE  | CFIFO port SIE register                          | 2.6   |

| 24      | D0FIFOSEL | D0FIFO port selection register                   | 2.6   |

| 26      | D0FIFOCTR | D0FIFO port control register                     | 2.6   |

| 28      | D0FIFOTRN | D0 transaction counter register                  | 2.6   |

| 2A      | D1FIFOSEL | D1FIFO port selection register                   | 2.6   |

| 2C      | D1FIFOCTR | D1FIFO port control register                     | 2.6   |

| 2E      | D1FIFOTRN | D1 transaction counter register                  | 2.6   |

| 30      | INTENB0   | Interrupt enable register 0                      | 2.7   |

| 32      | INTENB1   | Interrupt enable register 1                      | 2.7   |

| 34      |           |                                                  |       |

| 36      | BRDYENB   | BRDY interrupt enable register                   | 2.7   |

| 38      | NRDYENB   | NRDY interrupt enable register                   | 2.7   |

| 3A      | BEMPENB   | BEMP interrupt enable register                   | 2.7   |

| 3C      | SOFCFG    | SOF pin configuration register                   | 2.8   |

| 3E      |           |                                                  |       |

| 40      | INTSTS0   | Interrupt status register 0                      | 2.9   |

| 42      |           |                                                  |       |

| 44      |           |                                                  |       |

| 46      | BRDYSTS   | BRDY interrupt status register                   | 2.9   |

| 48      | NRDYSTS   | NRDY interrupt status register                   | 2.9   |

| 4A      | BEMPSTS   | BEMP interrupt status register                   | 2.9   |

| 4C      | FRMNUM    | Frame number register                            | 2.10  |

| 4E      | UFRMNUM   | Micro frame number register                      | 2.10  |

| 50      | RECOVER   | USB address / low-power status recovery register | 2.11  |

| 52      |           |                                                  |       |

| 54      | USBREQ    | USB request type register                        | 2.12  |

| 56      | USBVAL    | USB request value register                       | 2.12  |

| 58      | USBINDX   | USB request index register                       | 2.12  |

| 5A      | USBLENG   | USB request length register                      | 2.12  |

| 5C      | DCPCFG    | DCP configuration register                       | 2.13  |

| 5E      | DCPMAXP   | DCP maximum packet size register                 | 2.13  |

| Address | Symbol   | Name                              | Index |

|---------|----------|-----------------------------------|-------|

| 60      | DCPCTR   | DCP control register              | 2.13  |

| 62      |          |                                   |       |

| 64      | PIPESEL  | Pipe window selection register    | 2.14  |

| 66      | PIPECFG  | Pipe configuration register       | 2.14  |

| 6E      | PIPEBUF  | Pipe buffer setting register      | 2.14  |

| 6A      | PIPEMAXP | Pipe maximum packet size register | 2.14  |

| 6C      | PIPEPERI | Pipe period control register      | 2.14  |

| 6E      |          |                                   |       |

| 70      | PIPE1CTR | Pipe 1 control register           | 2.14  |

| 72      | PIPE2CTR | Pipe 2 control register           | 2.14  |

| 74      | PIPE3CTR | Pipe 3 control register           | 2.14  |

| 76      | PIPE4CTR | Pipe 4 control register           | 2.14  |

| 78      | PIPE5CTR | Pipe 5 control register           | 2.14  |

| 7A      | PIPE6CTR | Pipe 6 control register           | 2.14  |

| 7C      | PIPE7CTR | Pipe 7 control register           | 2.14  |

| 7E      |          |                                   |       |

Nothing is placed in addresses that are shaded. These addresses should not be accessed.

# 2.2 Table of bit symbols

Table 2.2shows the controller bit symbols.

Table 2.2 Bit symbols

| 0.11 | Register               |       |        | Odd   | d-number | ed addre | sses   |        |              |         |       | Eve  | n-numbe | red addre | sses     |          |      |

|------|------------------------|-------|--------|-------|----------|----------|--------|--------|--------------|---------|-------|------|---------|-----------|----------|----------|------|

| Addr | name                   | 15    | 14     | 13    | 12       | 11       | 10     | 9      | 8            | 7       | 6     | 5    | 4       | 3         | 2        | 1        | 0    |

| 00   | SYSCFG                 | XT    | AL     | XCKE  | RCKE     | PLLC     | SCKE   |        | ATCKM        | HSE     |       |      | DPRPU   |           |          | PCUT     | USBE |

|      | SYSSTS                 |       |        |       |          |          |        |        |              |         |       |      |         |           |          | LN:      | ST   |

|      | DVSTCTR                |       |        |       |          |          |        |        | WKUP         |         |       |      |         |           |          | RH       | ST   |

| 06   | TESTMODE               |       |        |       |          |          |        |        |              |         |       |      |         |           |          | UTST     |      |

| 80   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | PINCFG                 | LDRV  |        |       |          |          |        |        | BIGEND       |         |       |      |         |           |          |          |      |

|      | DMA0CFG                |       | DREQA  | BURST |          |          | DACKA  |        | DFORM        |         | DENDA | PKTM | DENDE   |           | OBUS     |          |      |

|      | DMA1CFG                |       | DREQA  | BURST |          |          | DACKA  |        | DFORM        |         | DENDA | PKTM | DENDE   |           | OBUS     |          |      |

| 10   | CFIFO                  |       |        |       |          |          |        |        | CFP          | ORT     |       |      |         |           |          |          |      |

| 12   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | D0FIFO                 |       |        |       |          |          |        |        | D0FF         | PORT    |       |      |         |           |          |          |      |

| 16   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | D1FIFO                 |       |        |       |          |          |        |        | D1FII        | PORT    |       |      |         |           |          |          |      |

| 1A   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

| 1C   | 05:5005:               |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | CFIFOSEL               | RCNT  | REW    |       |          |          | MBW    |        |              |         |       | ISEL |         |           |          | CURPIPE  |      |

|      | CFIFOCTR               | BVAL  | BCLR   | FRDY  |          |          |        |        |              |         | DT    | LN   |         |           |          |          |      |

|      | CFIFOSIE               | TGL   | SCLR   | SBUSY | DD====   |          | 14500  | TD=::- | TDO: -       | DESE    |       |      |         |           |          | OLIBB:=  |      |

|      | D0FIFOSEL              | RCNT  | REW    | DCLRM | DREQE    |          | MBW    | TRENB  | TRCLR        | DEZPM   | D.T.  |      |         |           |          | CURPIPE  |      |

|      | D0FIFOCTR              | BVAL  | BCLR   | FRDY  |          |          |        |        |              | A. I.T. | DT    | LN   |         |           |          |          |      |

| _    | D0FIFOTRN<br>D1FIFOSEL | DONT  | DEW    | DOLDM | DDEOE    |          | MDW    | TDEND  |              | CNT     |       |      |         |           | Ι .      | OLIDDIDE |      |

| -    | D1FIFOSEL<br>D1FIFOCTR | RCNT  | REW    | DCLRM | DREQE    |          | MBW    | IKENB  | TRCLR        | DEZPM   | DT    | ı Nı |         |           | <u> </u> | CURPIPE  |      |

|      | D1FIFOTRN              | BVAL  | BCLR   | FRDY  |          |          |        |        | TDN          | CNT     | DT    | LN   |         |           |          |          |      |

|      | INTENB0                | VBSE  | RSME   | SOFE  | DVSE     | CTRE     | DEMDE  | NDDVE  | TRN<br>BRDYE | URST    | SADR  | SCFG | SUSP    | WDST      | RDST     | CMPL     | SERR |

|      | INTENB1                | VDSE  | ROIVIE | SUFE  | DVSE     | CIRE     | BEIMPE | NRDTE  | BRUTE        | URST    | SADR  | SUFG | 303P    | WDST      | BRDYM    | INTL     | PCSE |

| 34   | INTENDI                |       |        |       |          |          |        |        |              |         |       |      |         |           | BKDTW    | INIL     | FUSE |

|      | BRDYENB                |       |        |       |          |          |        |        |              |         |       |      | PIPEB   | RDVE      |          |          |      |

|      | NRDYENB                |       |        |       |          |          |        |        |              |         |       |      | PIPEN   |           |          |          |      |

| -    | BEMPENB                |       |        |       |          |          |        |        |              |         |       |      | PIPEB   |           |          |          |      |

|      | SOFCFG                 |       |        |       |          |          |        |        |              |         |       |      | 1 2.2   |           | FM       |          |      |

| 3E   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | INTSTS0                | VBINT | RESM   | SOFR  | DVST     | CTRT     | BEMP   | NRDY   | BRDY         | VBSTS   |       | DVSQ |         | VALID     |          | CTSQ     |      |

| 42   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

| 44   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | BRDYSTS                |       |        |       |          |          |        |        |              |         |       |      | PIPE    | BRDY      |          |          |      |

|      | NRDYSTS                |       |        |       |          |          |        |        |              |         |       |      | PIPE    |           |          |          |      |

|      | BEMPSTS                |       |        |       |          |          |        |        |              |         |       |      | PIPE    | BEMP      |          |          |      |

|      | FRMNUM                 | OVRN  | CRCE   |       |          | SOFRM    |        |        |              |         |       | FRNM |         |           |          | -        |      |

|      | UFRMNUM                |       |        |       |          |          |        |        |              |         |       |      |         |           |          | UFRNM    |      |

| 50   | RECOVER                |       |        |       |          |          | S      | TSRECO | V            |         |       |      |         | JSBADDF   | ?        |          |      |

| 52   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

|      | USBREQ                 |       |        |       | bRed     | quest    |        |        |              |         |       |      | bmRequ  | estType   |          |          |      |

|      | USBVAL                 |       |        |       |          |          |        |        | wVa          | alue    |       |      |         |           |          |          |      |

|      | USBINDX                |       |        |       |          |          |        |        | wln          |         |       |      |         |           |          |          |      |

|      | USBLENG                |       |        |       |          |          |        |        | wLe          | ngth    |       |      |         |           |          |          |      |

|      | DCPCFG                 |       |        |       |          |          |        |        | CNTMD        |         |       |      |         |           |          |          |      |

|      | DCPMAXP                |       |        |       |          |          |        |        |              |         |       |      |         | MXPS      |          |          |      |

|      | DCPCTR                 | BSTS  |        |       |          |          |        |        | SQCLR        | SQSET   | SQMON |      |         |           | CCPL     | PI       | D    |

| 62   |                        |       |        |       |          |          |        |        |              |         |       |      |         |           |          |          |      |

| Addr | Register |      |        | Odd | d-number | ed addre | sses |       |       |        |       | Ever | 1-numbe | red addre | sses |         |   |

|------|----------|------|--------|-----|----------|----------|------|-------|-------|--------|-------|------|---------|-----------|------|---------|---|

| Auui | name     | 15   | 14     | 13  | 12       | 11       | 10   | 9     | 8     | 7      | 6     | 5    | 4       | 3         | 2    | 1       | 0 |

| 64   | PIPESEL  |      |        |     |          |          |      |       |       |        |       |      |         |           |      | PIPESEL |   |

| 66   | PIPECFG  | TY   | PE     |     |          |          | BFRE | DBLB  | CNTMD | SHTNAK |       |      | DIR     |           | EPN  | IUM     |   |

| 68   | PIPEBUF  |      |        |     | BUFSIZE  |          |      |       |       |        |       |      | BUF     | NMB       |      |         |   |

| 6A   | PIPEMAXP |      |        |     |          |          |      |       |       |        |       | MXPS |         |           |      |         |   |

| 6C   | PIPEPERI |      |        |     | IFIS     |          |      |       |       |        |       |      |         |           |      | IITV    |   |

| 6E   |          |      |        |     |          |          |      |       |       |        |       |      |         |           |      |         |   |

| 70   | PIPE1CTR | BSTS | INBUFM |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 72   | PIPE2CTR | BSTS | INBUFM |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 74   | PIPE3CTR | BSTS | INBUFM |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 76   | PIPE4CTR | BSTS | INBUFM |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 78   | PIPE5CTR | BSTS | INBUFM |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 7A   | PIPE6CTR | BSTS |        |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 7C   | PIPE7CTR | BSTS |        |     |          |          |      | ACLRM | SQCLR | SQSET  | SQMON |      |         |           |      | PII     | D |

| 7E   |          |      |        |     |          |          |      |       |       |        |       |      |         |           |      |         |   |

## 2.3 System control

◆ System configuration control register [SYSCFG]

| <address 00h="" :=""></address> |

|---------------------------------|

|---------------------------------|

|   | 15 | 14 | 13   | 12   | 11   | 10   | 9 | 8     | 7 | 6 | 5 | 4     | 3 | 2 | 1    | 0    |

|---|----|----|------|------|------|------|---|-------|---|---|---|-------|---|---|------|------|

|   | XT | AL | XCKE | RCKE | PLLC | SCKE |   | ATCKM |   |   |   | DPRPU |   |   | PCUT | USBE |

| Г | 0  | 0  | 0    | 0    | 0    | 0    | ? | 0     | 0 | ? | ? | 0     | ? | ? | 0    | 0    |

|   | -  | -  | -    | -    | -    | -    | ? | -     | - | ? | ? | -     | ? | ? | -    | -    |

|   | -  | -  | -    | -    | -    | -    | ? | -     | - | ? | ? | -     | ? | ? | -    | -    |

|   | -  | -  | 1    | 0    | 0    | 0    | ? | -     | - | ? | ? | -     | ? | ? | 0    | -    |

| Bit   | Name                                          | Function                                              | S/W    | H/W    | Note    |

|-------|-----------------------------------------------|-------------------------------------------------------|--------|--------|---------|

| 15-14 |                                               | 00: 12 MHz input                                      | R/W    | R      | 3.1.5   |

|       | Clock selection                               | 01: 24 MHz input                                      |        |        |         |

|       |                                               | 10: 48 MHz input                                      |        |        |         |

|       |                                               | 11: Reserved                                          |        |        |         |

| 13    | XCKE                                          | 0: Oscillation buffer operation disabled              | R/W    | R/W(1) | 3.1.5   |

|       | Oscillation buffer enabled                    | Oscillation buffer operation enabled                  |        |        | *2)     |

|       | RCKE                                          | 0: Reference clock supply stopped                     | R/W    | R      | 3.1.5   |

|       | Reference clock enabled                       | Reference clock supply enabled                        |        |        |         |

| 11    | PLLC                                          | 0: PLL operation disabled                             | R/W    | R      | 3.1.5   |

|       | PLL operation enabled                         | 1: PLL operation enabled                              |        |        |         |

| 10    | SCKE                                          | 0: Internal clock supply stopped                      | R/W    | R      | 3.1.5   |

|       | Internal clock enabled                        | 1: Internal clock supply enabled                      |        |        |         |

| 9     | Nothing is placed here. It should be fixed    | at "0".                                               | •      |        |         |

| 8     | ATCKM                                         | The clock is supplied from the low-power sleep        | R/W    | R      | 3.1.6.6 |

|       | Auto clock supply function enabled            | state or clock stop state.                            |        |        |         |

|       |                                               | 0: Auto clock supply function disabled                |        |        |         |

|       |                                               | 1: Auto clock supply function enabled                 |        |        |         |

| _     | HSE                                           | This enables Hi-Speed operation.                      | R/W    | R      | 3.1.3   |

|       | Hi-Speed operation enabled                    | 0: Hi-Speed operation disabled (Full-Speed)           |        |        | *1)     |

|       |                                               | 1: Hi-Speed operation enabled (detected by            |        |        |         |

| C F   | Nothing is placed here. These should be       | controller)                                           |        |        |         |

|       | Nothing is placed here. These should be DPRPU |                                                       | DAA    | _      | 0.1.4   |

|       | DPRPU<br>D+ line pull-up control              | Issues notification of connection to host controller. | R/W    | R      | 3.1.4   |

|       | D+ lifte pull-up control                      | 0: Pull-up disabled                                   |        |        |         |

|       |                                               | 1: Pull-up enabled                                    |        |        |         |

| 3-2   | Nothing is placed here. These should be       |                                                       |        |        |         |

|       | PCUT                                          | 0: Normal operation state                             | R/W(1) | R/W(0) | 3.1.6   |

|       | Low-power sleep state enabled                 | 1: Low-power sleep state                              |        | (3)    | 5.1.0   |

| 0     | USBE                                          | 0: USB block operation disabled (S/W Reset)           | R/W    | R      | 2.3.1   |

|       | USB block operation enabled                   | 1: USB block operation enabled                        |        |        | 3.1.1   |

#### «Notes»

- \*1) The Hi-Speed operation enabled((HSE) bit should be set beforethe DPRPU bit is set to "1".

- **\*2)** When the system returns from the low-power sleep state to the normal operation state, the controller sets "XCKE = 1".

| •  | ◆ System configuration status register [SYSSTS] |    |    |    |    |   |   |   | <address: 02h=""></address:> |   |   |   |   |    |    |

|----|-------------------------------------------------|----|----|----|----|---|---|---|------------------------------|---|---|---|---|----|----|

| 15 | 14                                              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6                            | 5 | 4 | 3 | 2 | 1  | 0  |

|    |                                                 |    |    |    |    |   |   |   |                              |   |   |   |   | LN | ST |

| ?  | ?                                               | ?  | ?  | ?  | ?  | ? | ? | ? | ?                            | ? | ? | ? | ? | ?  | ?  |

| ?  | ?                                               | ?  | ?  | ?  | ?  | ? | ? | ? | ?                            | ? | ? | ? | ? | ?  | ?  |

| ?  | ?                                               | ?  | ?  | ?  | ?  | ? | ? | ? | ?                            | ? | ? | ? | ? | ?  | ?  |

| ?  | ?                                               | ?  | ?  | ?  | ?  | ? | ? | ? | ?                            | ? | ? | ? | ? | ?  | ?  |

| Bit  | Name                                                  | Function | S/W | H/W | Note |  |  |  |  |  |

|------|-------------------------------------------------------|----------|-----|-----|------|--|--|--|--|--|

| 15-2 | Nothing is placed here. These should be fixed at "0". |          |     |     |      |  |  |  |  |  |

| _    |                                                       | 5        |     |     |      |  |  |  |  |  |

#### «Notes»

None in particular

#### 2.3.1 USB block operation enabled

The USBE bit of the SYSCFG register should be used to enable USB block operation.

The same bit can be used to carry out an S/W reset of the controller. When software is set to "USBE=0", the controller resets the register targeted for S/W reset initialization to the default setting value. As long as "USBE=0" is set, no data can be written by software to the bit targeted for S/W reset initialization. "USBE=1" should be set following an S/W reset to enable controller operation.

#### 2.3.2 Line status monitor

Table 2.3 shows the USB data bus line statuses of the controller. The controller monitors the line status (D+ line and D- line) of the USB data bus using the **LNST** bit of the **SYSSTS** register. The **LNST** bit is configured of two bits. For the meaning of each of the bits, please refer to the table below. The timing at which the **LNST** bit becomes valid differs depending on the selected controller function. In the normal operating state, the line status can be monitored on an ongoing basis, but in the low-power sleep state, the line status cannot be monitored.

Table 2.3 USB data bus line statuses

| LNST [1] | LNST [0] | During Full-Speed operation | During Hi-Speed operation | During chirp operation |

|----------|----------|-----------------------------|---------------------------|------------------------|

| 0        | 0        | SE0                         | Squelch                   | Squelch                |

| 0        | 1        | J State                     | not Squelch               | Chirp J                |

| 1        | 0        | K State                     | Invalid                   | Chirp K                |

| 1        | 1        | SE1                         | Invalid                   | Invalid                |

Chirp: The reset handshake protocol is being executed in the Hi-Speed operation enabled state (HSE = "1").

Squelch: SE0 or Idle state

not Squelch: Hi-Speed J state or Hi-Speed K state

Chirp J: Chirp J state Chirp K: Chirp K state

## 2.4 USB signal control

◆ Device state control register [**DVSTCTR**]

| - 1 | ddr | •    | 04  | тτ、 |

|-----|-----|------|-----|-----|

| < A | aar | DSS. | 114 | н.  |

|     |     |      |     |     |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0   |

|----|----|----|----|----|----|---|------|---|---|---|---|---|---|----|-----|

|    |    |    |    |    |    |   | WKUP |   |   |   |   |   |   | R⊦ | IST |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | 0    | ? | ? | ? | ? | ? | ? | 0  | 0   |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | 0    | ? | ? | ? | ? | ? | ? | 0  | 0   |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | 0    | ? | ? | ? | ? | ? | ? | -  | -   |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | 0    | ? | ? | ? | ? | ? | ? | 0  | 0   |

| Bit  | Name                                                  | Function                                                                                                                                                 | S/W    | H/W | Note                      |  |  |  |  |  |

|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---------------------------|--|--|--|--|--|

| 15-9 | Nothing is placed here. These should be               | fixed at "0".                                                                                                                                            |        |     |                           |  |  |  |  |  |

| _    | WKUP<br>Wakeup output                                 | 0: Non-output<br>1: Remote wakeup signal output                                                                                                          | R/W(1) | . , | 2.4.1<br>*1) <u>.</u> *2) |  |  |  |  |  |

| 7-2  | Nothing is placed here. These should be fixed at "0". |                                                                                                                                                          |        |     |                           |  |  |  |  |  |

| _    | Reset handshake                                       | 00: Communication speed not decided<br>01: Reset handshake being processed<br>10: Full-Speed operation established<br>11: Hi-Speed operation established | R      | W   | 2.4.2                     |  |  |  |  |  |

#### «Notes»

- \*1) "1" should never be written to the **WKUP** bit unless "Suspended" is set for the device state ("DVSQ = 1x") and a remote wakeup from the USB host is enabled.

- \*2) When the **WKUP** bit is set to "1", software should not disable oscillation buffer operation.

◆ Test mode register [TESTMODE]

| <address: (<="" th=""><th>06H</th><th>[&gt;</th></address:> | 06H | [> |

|-------------------------------------------------------------|-----|----|

|-------------------------------------------------------------|-----|----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|------|---|

|    |    |    |    |    |    |   |   |   |   |   |   |   |   | UTST |   |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | ? | ? | ? | ? | ? | ? | 0 | 0    | 0 |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | ? | ? | ? | ? | ? | ? | 0 | 0    | 0 |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | ? | ? | ? | ? | ? | ? | - | -    | - |

| ?  | ?  | ?  | ?  | ?  | ?  | ? | ? | ? | ? | ? | ? | ? | 0 | 0    | 0 |

| Bit  | Name                                    | Function                                                  | S/W | H/W | Note         |

|------|-----------------------------------------|-----------------------------------------------------------|-----|-----|--------------|

| 15-4 | Nothing is placed here. These should be |                                                           |     |     |              |

|      | UTST<br>Test mode                       | Please see the detailed explanation concerning this item. | R/W | R   | 2.4.3<br>*3) |

## «Note»

\*3) The UTST bit is valid only during Hi-Speed operation. Check to make sure the "RHST=11" before using it.

#### 2.4.1 USB data bus control

Each bit of the **DVSTCTR** register can be used to control and confirm the state of the USB data bus based on the user system.

The **WKUP** bit handles control of remote wakeup signal output to the USB bus. The controller controls the output time for remote wakeup signals. 2ms after a software has set "1" for the **WKUP** bit, the controller outputs a 10 ms "K-State" then it transfers the bus state to idle. When the bus state is transferred to the idle state, the controller sets "WKUP=0".

According to the USB specification, USB idle state must be kept longer than 5ms. Thus if the software set "WKUP=1" right after detection of Suspend state, the controller will assert "K-State" after 2ms.

## 2.4.2 Communication speed discrimination

Software is able to confirm the USB speed at which communication is being carried out with the host controller (the communication bit rate), using the **RHST** bit.

If Hi-Speed operation has been set to the disabled state ("HSE=0") by software, the controller immediately establishes Full-Speed operation ("RHST=10") after a USB bus reset has been detected, without executing the reset handshake protocol. If Hi-Speed operation has been set to the enabled state ("HSE=1"), the controller executes the reset handshake protocol ("RHST=01" during execution of the protocol), and feeds back the execution results to the **RHST** bit ("RHST=11": Hi-Speed operation, or "RHST=10": Full-Speed operation).

#### 2.4.3 Test mode

Table 2.4 shows the test mode operation of the controller. The **UTST** bit of the **TESTMODE** register controls the USB test signal output during Hi-Speed operation.

Test mode

UTST bit setting

Normal operation

000

Test\_J

001

Test\_K

010

Test\_SE0\_NAK

011

Test\_Packet

100

Reserved

101-111

Table 2.4 Test mode operation

## 2.5 External input/output control

◆ Data pin configuration register [PINCFG] <Address: 0AH>

| 15   | 14 | 13 | 12 | 11 | 10 | 9 | 8      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----|----|----|----|----|---|--------|---|---|---|---|---|---|---|---|

| LDRV |    |    |    |    |    |   | BIGEND |   |   |   |   |   |   |   |   |

| 0    | ?  | ?  | ?  | ?  | ?  | ? | 0      | ? | ? | ? | ? | ? | ? | ? | ? |

| -    | ?  | ?  | ?  | ?  | ?  | ? | -      | ? | ? | ? | ? | ? | ? | ? | ? |

| -    | ?  | ?  | ?  | ?  | ?  | ? | -      | ? | ? | ? | ? | ? | ? | ? | ? |

| -    | ?  | ?  | ?  | ?  | ?  | ? | 0      | ? | ? | ? | ? | ? | ? | ? | ? |

| Bit  | Name                                                  | Function              | S/W | H/W | Note  |  |  |  |  |  |  |

|------|-------------------------------------------------------|-----------------------|-----|-----|-------|--|--|--|--|--|--|

| 15   |                                                       | 0: When VIF=1.6-2.0 V | R/W | R   | 2.5.1 |  |  |  |  |  |  |

|      | Output pins drive current control                     | 1: When VIF=2.7-3.6 V |     |     |       |  |  |  |  |  |  |

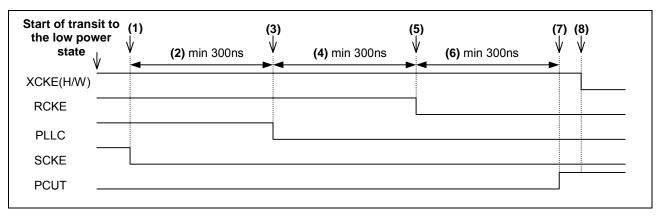

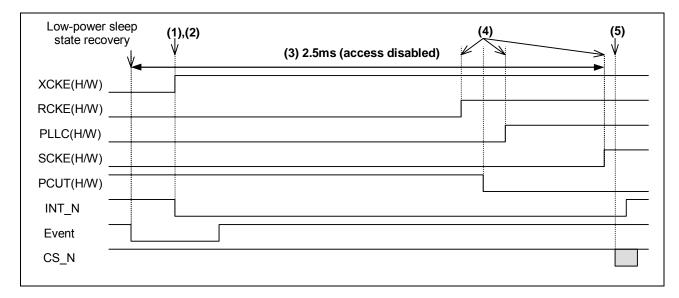

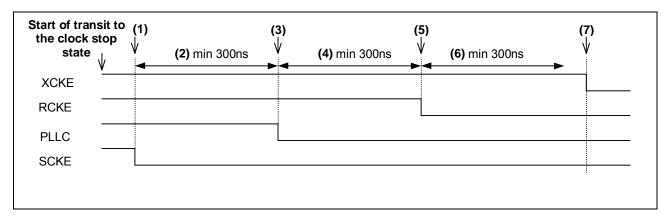

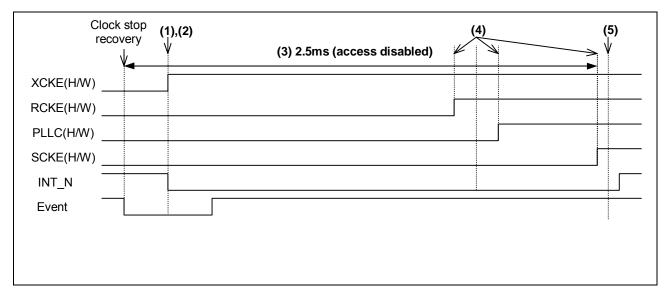

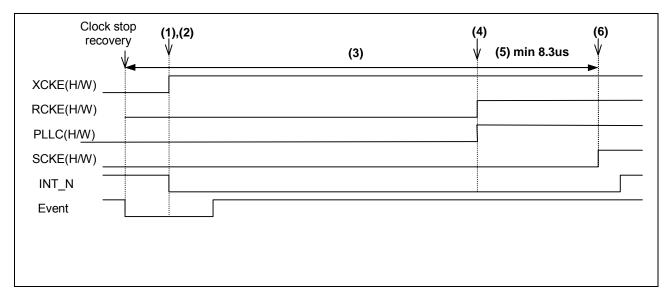

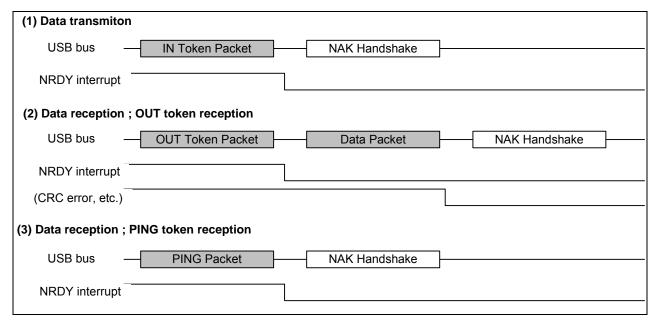

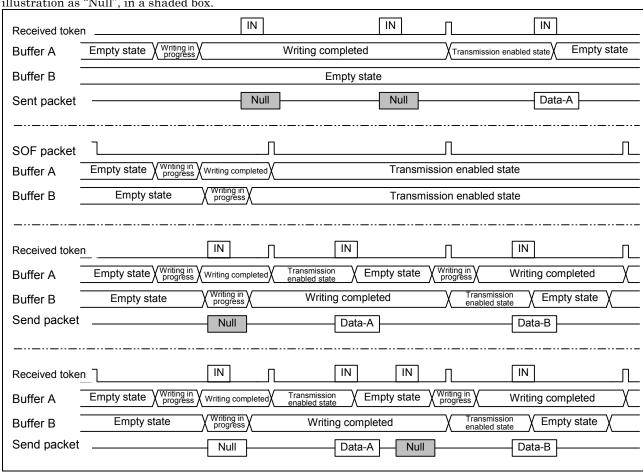

| 14-9 | Nothing is placed here. These should be fixed at "0". |                       |     |     |       |  |  |  |  |  |  |