### **Description**

The OB1203 Sensor Module integrates a multi-channel light sensor (LS/CS), a proximity sensor (PS), and a photoplethysmography sensor (PPG).

The light sensor can be configured as ambient light sensor (LS) to measure ambient light similar to the human eye experience or as an RGB color sensor (CS). The module has a fully integrated biosensor for reflective photoplethysmography. With the appropriate algorithm, it can determine human heart rate (HR), oxygen saturation (SpO2), respiration rate, and heart rate variability (a measure of stress). The OB1203 integrates light sources and drivers in a single optically optimized package.

A major LS application of the device is in smart phones or other mobile devices to enable brightness control of display panels. The OB1203 can also determine proximity of nearby objects in order to support the activation of touch screen displays or system functions. The sensor combines optical sensing features (CS, LS, and PS) and bio-sensing functionality (PPG) without needing a visible optical opening. The unique implementation of the OB1203 enables  $SpO_2$  measurements behind ink that is IR transmissive, but visibly dark, allowing implementation in aesthetic industrial designs.

### **Biosensor Features**

- SpO<sub>2</sub> measurement behind visibly dark, IR transmissive ink

- Industry's smallest optical biosensor module

- Fully integrated and trimmed module, including two LEDs, 250mA maximum drive current, and photodetectors

- Output resolution PPG: 16 to 18 bits

- Data stored in 18-bit wide, 32-sample FIFO memory

- Integrated averaging function for higher signal-to-noise ratio (SNR) and data rate reduction

- Programmable measurement rate: up to 3200 samples per second

- High SNR

## **Ambient Light Sensor Features**

- High lux accuracy over different light sources

- Absolute sensitivity: 0.06 lux to > 150000 lux

- Output resolution LS/CS: 13 to 20 bits

- Three LS/CS gain modes: x1 to x6

- Highly linear output, 50Hz/60Hz light and fluorescent light flicker immunity

#### **Color Sensor Features**

- Four parallel channels (red, green, blue, clear)

- Accurate Correlated Color Temperature (CCT)

- Accurate CIE 1931 XYZ (RGB) color measurement

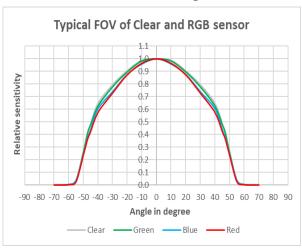

- Very stable spectral response over angle of light incidence

- Output resolution CS: 13 to 20 bits

### **Proximity Sensor Features**

- Integrated and trimmed LED source, driver, and photodetector

- Programmable pulsed LED up to 250mA output current

- High resolution (12 to 16 bits)

- Object movement detection (in/out)

- Ambient light suppression > 100klx sun light

- Crosstalk cancelation (analog and digital)

### **Physical Characteristics**

- Highly reliable and industry-proven OSIP package with integrated cover glass for hypoallergenic products

- Wide operation temperature: 40°C to +85°C

- Wide supply voltage: 1.7V to 3.6V

- Typical active current at minimum duty cycle:

- LS/CS:110µA

- PS: 90µA + LED current (typical ~300µA average)

- Low standby current: 2µA typical

- I2C interface capable of Standard Mode (100kHz) or Fast Mode (400kHz) communication; 1.8V to 3.3V logic compatible

- Programmable level-based interrupt functions with upper and lower thresholds for extending battery life

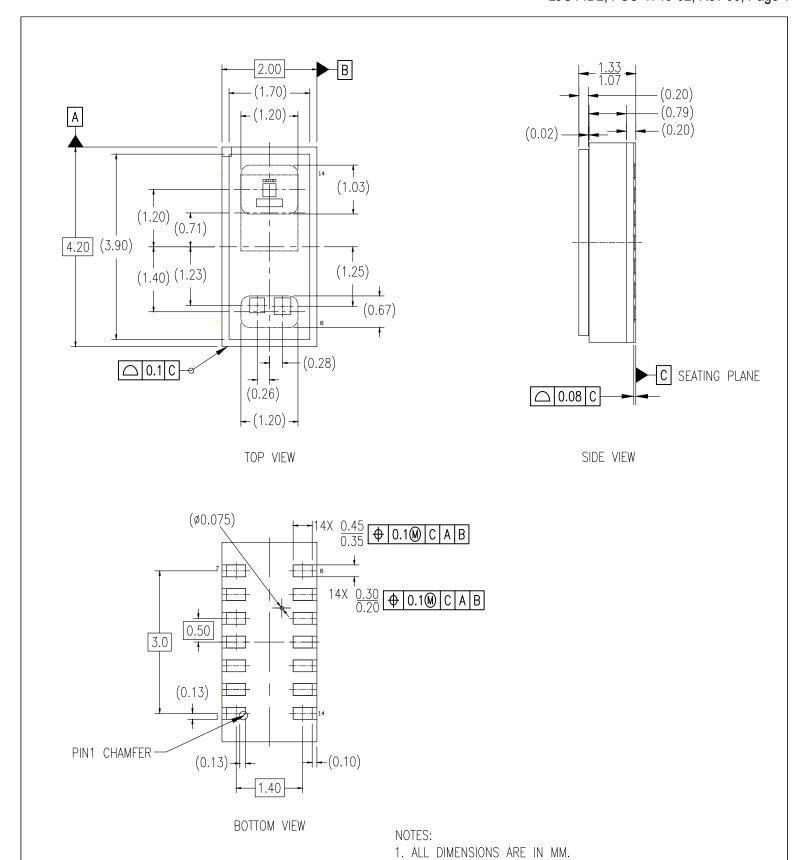

- Industry's smallest package: 4.2 × 2 × 1.2 mm<sup>3</sup> 14-OSIP module

Figure 1. 3D Package Rendering

## Biosensor, LS and PS Applications

- Mobile devices such as smartphones, smart accessories, touch screen disable, display brightness and color adjust, smartwatches, secondary sensor for blood pressure

- Head phones

- Hearables

- Fitness and wellness

- Occupancy

- Gesture detection

- Industrial applications such as proximity and light detection in less than 1ms, fast light barriers, lighting control, robotics, agriculture and hydroponic light sensing, daylighting

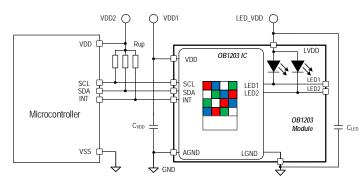

## **Application Circuit**

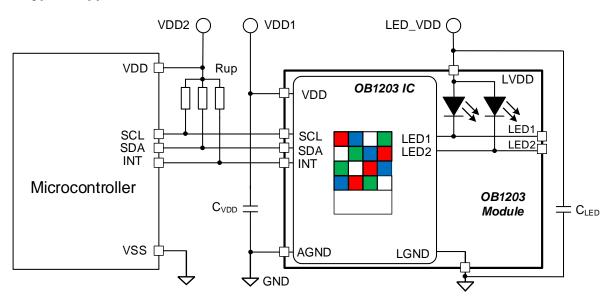

Figure 2. Typical Circuit - Only 6 Connections

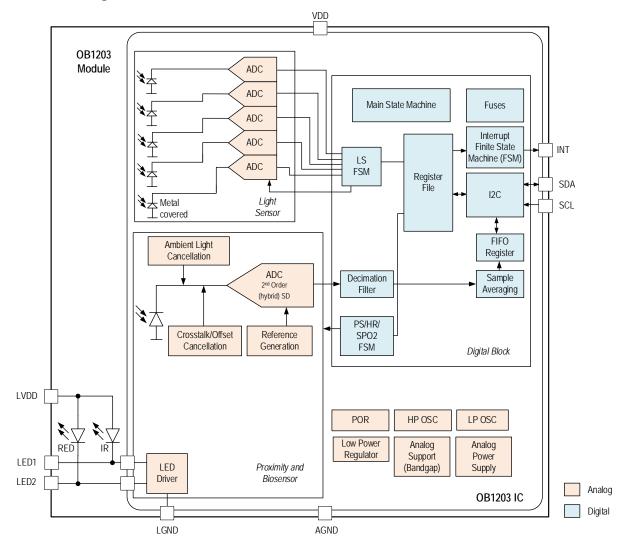

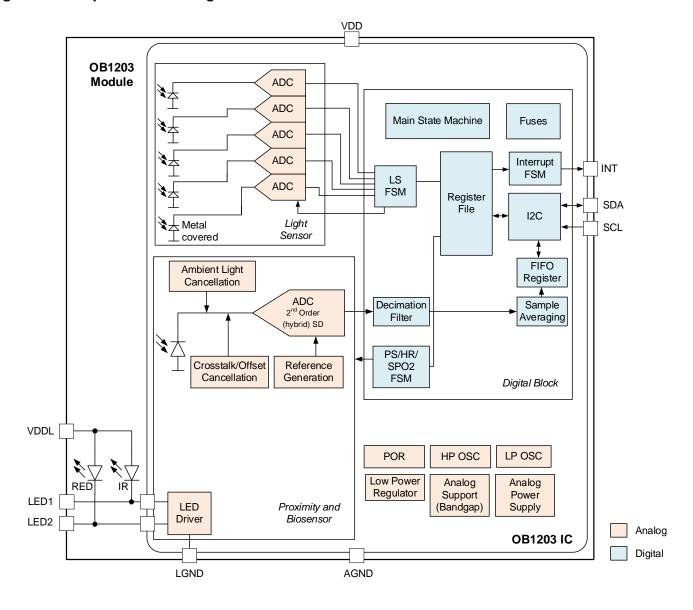

Figure 3. Block Diagram

## **Contents**

| 1. | Pin <i>i</i> | Assignme   | ents                                     | 7  |

|----|--------------|------------|------------------------------------------|----|

| 2. | Pin I        | Descriptio | ons                                      | 7  |

| 3. | Abso         | olute Max  | kimum Ratings                            | 8  |

| 4. | Reco         | ommende    | ed Operating Conditions                  | 8  |

| 5. | Elec         | trical and | l Optical Characteristics                | 9  |

| 6. | Турі         | cal Perfor | rmance Characteristics                   | 12 |

| 7. | Deta         | ailed Desc | cription                                 | 15 |

|    | 7.1          | Applicat   | tion Circuit                             | 16 |

|    | 7.2          | Modes      | of Operation                             | 16 |

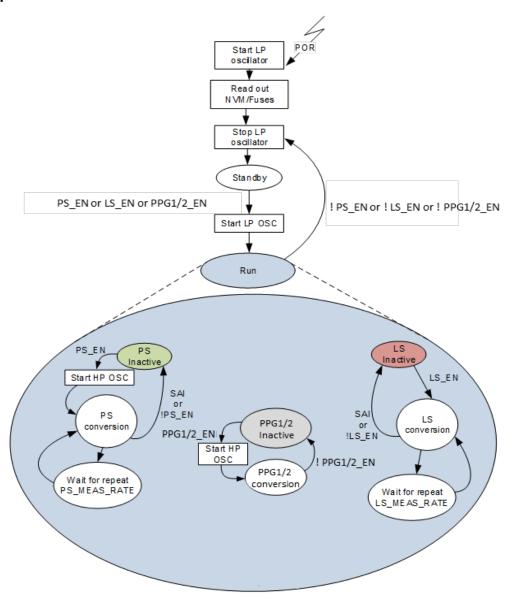

|    | 7.3          | Main St    | ate Machine                              | 16 |

|    | 7.4          | Light Se   | ensor Description                        | 18 |

|    | 7.5          | Proximit   | ty and PPG Sensor Description            | 19 |

|    |              | 7.5.1      | LEDs and Integrated LED Driver           | 19 |

|    |              | 7.5.2      | Principles of Proximity Sensor Operation | 19 |

|    |              | 7.5.3      | Principles of PPG Sensor Operation       | 20 |

|    | 7.6          | Interrup   | t Features                               | 22 |

|    |              | 7.6.1      | LS Interrupt                             | 22 |

|    |              | 7.6.2      | PS Interrupt                             | 22 |

|    |              | 7.6.3      | PPG Interrupt                            | 24 |

|    | 7.7          | I2C Inte   | erface                                   | 24 |

|    |              | 7.7.1      | I2C Address Decoding                     | 24 |

|    |              | 7.7.2      | I2C Register Read                        | 24 |

|    |              | 7.7.3      | I2C Register Write                       | 25 |

|    |              | 7.7.4      | I2C Interface Bus Timing                 | 26 |

|    | 7.8          | Summa      | ry of Internal Registers                 | 26 |

|    | 7.9          | Detailed   | d Description of Registers               | 29 |

|    |              | 7.9.1      | STATUS_0                                 | 29 |

|    |              | 7.9.2      | STATUS_1                                 | 30 |

|    |              | 7.9.3      | PS_DATA                                  | 31 |

|    |              | 7.9.4      | LS_CLEAR_DATA                            | 32 |

|    |              | 7.9.5      | LS_GREEN_DATA                            | 33 |

|    |              | 7.9.6      | LS_BLUE_DATA                             | 34 |

|    |              | 7.9.7      | LS_RED_DATA                              | 35 |

|    |              | 7.9.8      | COMP_DATA                                | 36 |

|    |              | 7.9.9      | MAIN_CTRL_0                              | 37 |

|    |              | 7.9.10     | MAIN_CTRL_1                              | 38 |

|    |              | 7.9.11     | PS_LED_CURR                              | 39 |

|    |              | 7.9.12     | PS_CAN_PULSES                            | 40 |

|    |              |            |                                          |    |

|     | 7.9.13           | PS_PWIDTH_PERIOD         | 41 |

|-----|------------------|--------------------------|----|

|     | 7.9.14           | PS_CAN_DIG               | 42 |

|     | 7.9.15           | PS_MOV_AVG_HYS           | 43 |

|     | 7.9.16           | PS_THRES_UP              | 44 |

|     | 7.9.17           | PS_THRES_LOW             | 44 |

|     | 7.9.18           | LS_RES_PERIOD            | 45 |

|     | 7.9.19           | LS_GAIN                  | 46 |

|     | 7.9.20           | LS_THRES_UP              | 47 |

|     | 7.9.21           | LS_THRES_LOW             | 48 |

|     | 7.9.22           | LS_THRES_VAR             | 49 |

|     | 7.9.23           | INT_CFG_0                | 50 |

|     | 7.9.24           | INT_CFG_1                | 51 |

|     | 7.9.25           | INT_PST                  | 52 |

|     | 7.9.26           | PPG_PS_GAIN              | 52 |

|     | 7.9.27           | PPG_PS_CFG               | 53 |

|     | 7.9.28           | PPG_IRLED_CURR           | 54 |

|     | 7.9.29           | PPG_RLED_CURR            | 55 |

|     | 7.9.30           | PPG_CAN_ANA              | 56 |

|     | 7.9.31           | PPG_AVG                  | 57 |

|     | 7.9.32           | PPG_PWIDTH_PERIOD        | 58 |

|     | 7.9.33           | FIFO_CFG                 | 61 |

|     | 7.9.34           | FIFO_WR_PTR              | 62 |

|     | 7.9.35           | FIFO_RD_PTR              | 63 |

|     | 7.9.36           | FIFO_OVF_CNT             | 63 |

|     | 7.9.37           | FIFO_DATA                | 64 |

|     | 7.9.38           | PART_ID                  | 64 |

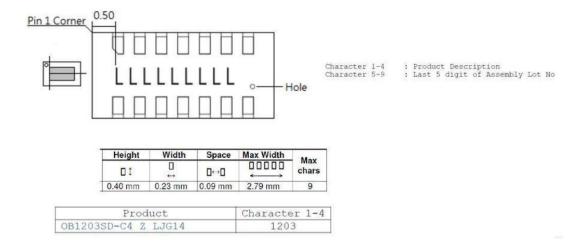

| 8.  | Package Outl     | ine Drawings             | 65 |

| 9.  | Reflow Profile   | )                        | 65 |

| 10. | 0 0              | ram: Bottom of Part Only |    |

| 11. | Ordering Info    | rmation                  | 66 |

| 12. | Glossary         |                          | 66 |

| 13. | Revision History | ory                      | 67 |

# **List of Figures**

| Figure 1.  | 3D Package Rendering                                                             | 1  |

|------------|----------------------------------------------------------------------------------|----|

| Figure 2.  | Typical Circuit – Only 6 Connections                                             | 2  |

| Figure 3.  | Block Diagram                                                                    | 2  |

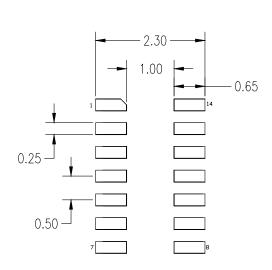

| Figure 4.  | Pin Assignments for 2 × 4.2 × 1.2 mm 14-OSIP Package – Top View                  | 7  |

| Figure 5.  | Package Rotation Axes for Field of View                                          | 12 |

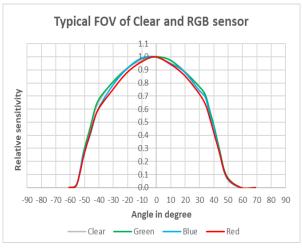

| Figure 6.  | Typical FOV of R, G, B and Clear Photodiode along Width of Package               | 12 |

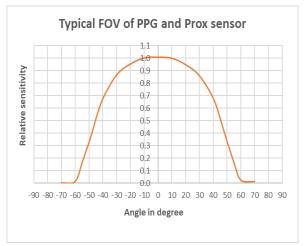

| Figure 7.  | Typical FOV of PPG and Proximity Photodiode along Width of Package               | 12 |

| Figure 8.  | Typical FOV of R, G, B and Clear Photodiode along Length of Package              | 12 |

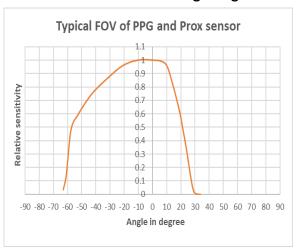

| Figure 9.  | Typical FOV of PPG and Proximity Photodiode along Length of Package              | 12 |

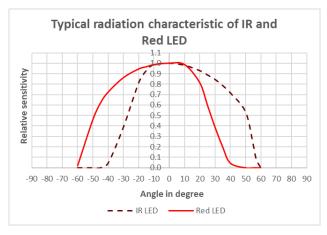

| Figure 10. | Typical Radiation Characteristic of the LEDs along Width of Package              | 13 |

| Figure 11. | Typical Radiation Characteristic of the LEDs along Length of Package             | 13 |

| Figure 12. | Typical Normalized Spectral Response of R, G, B and Clear Sensors                | 13 |

| Figure 13. | Typical Linearity of R, G, B and Clear Sensors                                   | 13 |

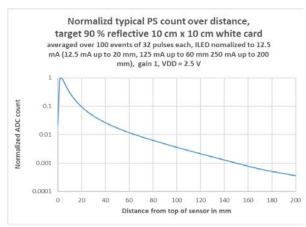

| Figure 14. | Typical PS Count over Distance                                                   | 13 |

| Figure 15. | Log of Typical PS Count                                                          | 13 |

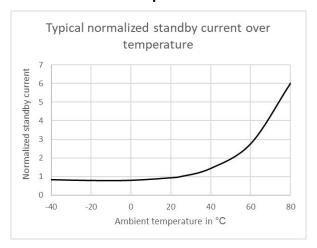

| Figure 16. | Typical Normalized Standby Current over Temperature                              | 14 |

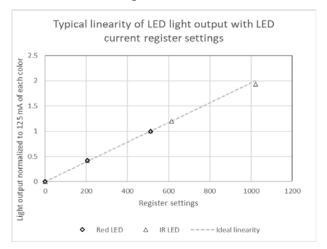

| Figure 17. | Typical Normalized LED Light Output Linearity with LED Current Register Settings | 14 |

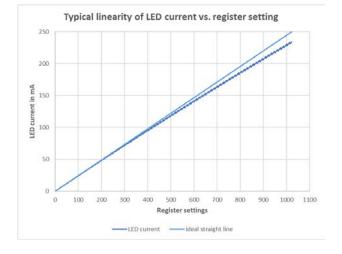

| Figure 18. | Typical LED Driver Current vs. Current Register Setting                          | 14 |

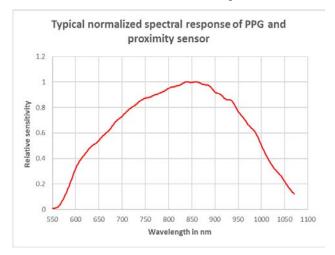

| Figure 19. | Typical Normalized Spectral Response of PPG and Proximity Sensor                 | 14 |

| Figure 20. | Simplified Block Diagram                                                         | 15 |

| Figure 21. | Typical Application Circuit                                                      | 16 |

| Figure 22. | Simplified Main State Machine                                                    | 17 |

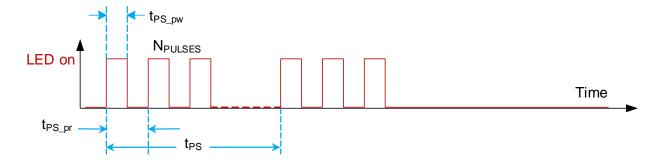

| Figure 23. | PS Timing Characteristic                                                         | 20 |

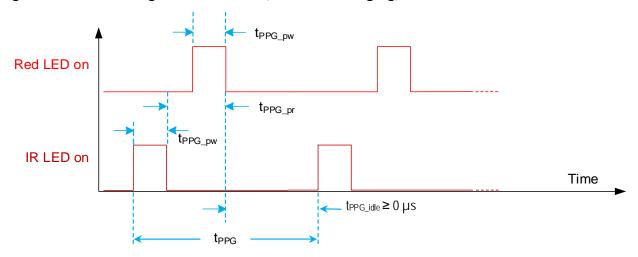

| Figure 24. | PPG Timing Characteristic (without Averaging)                                    | 21 |

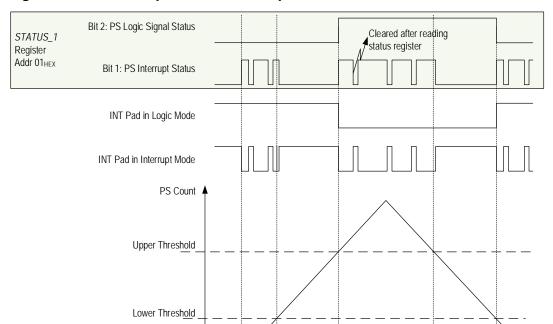

| Figure 25. | PS Interrupt Behavior Examples                                                   | 23 |

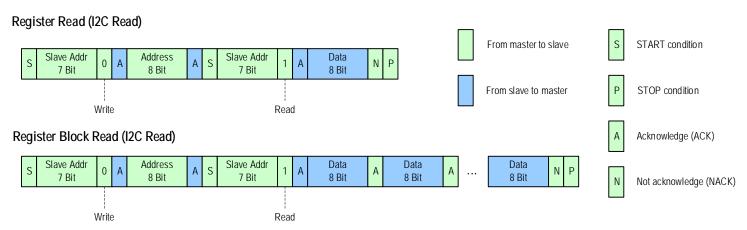

| Figure 26. | I2C Register Read                                                                | 25 |

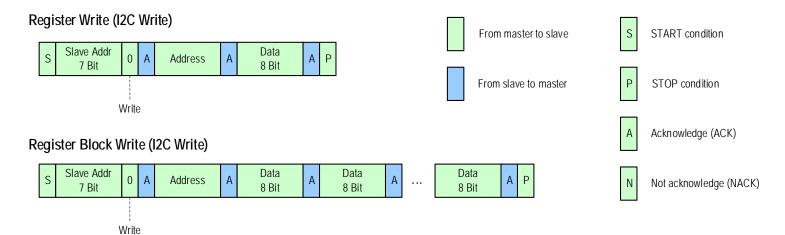

| Figure 27. | I2C Register Write                                                               | 25 |

| Figure 28. | Bus Timing                                                                       | 26 |

## **List of Tables**

| Table 1.  | Pin Descriptions                                        | 7  |

|-----------|---------------------------------------------------------|----|

| Table 2.  | Absolute Maximum Ratings                                | 8  |

| Table 3.  | Recommended Operating Conditions                        | 8  |

| Table 4.  | Electrical and Optical Characteristics                  | 9  |

| Table 5.  | Channel Activation during Operation Modes               |    |

| Table 6.  | LS Channel Activation in LS and CS Mode                 | 18 |

| Table 7.  | LS Detection Ranges and Sensitivity Calculation Example | 19 |

| Table 8.  | PS Parameter                                            | 20 |

| Table 9.  | PPG Parameters                                          | 21 |

| Table 10. | Supported I2C clock Frequencies                         | 24 |

| Table 11. | Bus Timing Characteristic                               | 26 |

| Table 12. | Bus Timing Characteristic                               | 26 |

| Table 13. | PS Measurement Output Resolution                        | 41 |

|           | PPG Measurement Output Resolution                       |    |

| Table 15. | PPG1 Mode Parameter                                     | 59 |

| Table 16. | PPG2 Mode Parameter                                     | 60 |

|           | Recommended Reflow Profile                              |    |

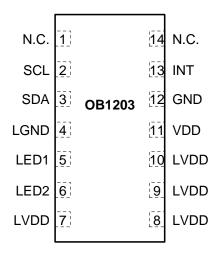

## 1. Pin Assignments

Figure 4. Pin Assignments for  $2 \times 4.2 \times 1.2$  mm 14-OSIP Package – Top View

## 2. Pin Descriptions

Table 1. Pin Descriptions

| Pin Number  | Name | I/O Type | Description                                            |

|-------------|------|----------|--------------------------------------------------------|

| 1           | N.C. |          | Not connected internally. Can be connected to ground.  |

| 2           | SCL  | IN       | I2C serial clock line.                                 |

| 3           | SDA  | IN/OUT   | I2C serial data line.                                  |

| 4           | LGND | GROUND   | LED/digital ground (required).                         |

| 5           | LED1 | _        | IR LED driver test pin (LED cathode / driver output).  |

| 6           | LED2 | _        | Red LED driver test pin (LED cathode / driver output). |

| 7, 8, 9, 10 | LVDD | SUPPLY   | LED power supply.                                      |

| 11          | VDD  | SUPPLY   | Digital/analog power supply.                           |

| 12          | GND  | GROUND   | Analog ground.                                         |

| 13          | INT  | OUT      | Interrupt pin.                                         |

| 14 N.C. –   |      | _        | Not connected internally. Can be connected to ground.  |

## 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. The device might not function or be operable above the recommended operating conditions given in this section. Stresses exceeding the absolute maximum ratings might damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. Renesas does not recommend designing to the "Absolute Maximum Ratings."

Global measurement conditions V<sub>DD</sub> = 2.8V, T<sub>AMB</sub> = 25°C unless otherwise noted.

**Table 2. Absolute Maximum Ratings**

| Symbol               | Parameter                                                              | Conditions                      | Minimum | Maximum            | Units |

|----------------------|------------------------------------------------------------------------|---------------------------------|---------|--------------------|-------|

| $V_{\text{DD-GND}}$  | Maximum input supply voltage (VDD pin)                                 |                                 |         | 3.6                | V     |

| V <sub>I2C</sub>     | Maximum voltage on SCL, SDA and INT pins                               |                                 | -0.5    | 3.6                | V     |

| $V_{LED}$            | Maximum voltage on LVDD pins                                           | VDD supplied in operation range | -0.5    | 5.0 <sup>[a]</sup> | V     |

| T <sub>AMB_MAX</sub> | Maximum operating temperature range                                    |                                 | -40     | 85                 | °C    |

| T <sub>STOR</sub>    | Storage temperature                                                    |                                 | -45     | 90                 | °C    |

| I <sub>IN</sub>      | Maximum input current into any pin except supply / LED pins (latch-up) |                                 | -100    | 100                | mA    |

| $V_{HBM}$            | Electrostatic discharge protection [b]                                 | Human Body Model, JESD22-A114   | 2000    |                    | V     |

| $V_{CDM}$            | Charge Device Model                                                    |                                 | 1000    |                    | V     |

<sup>[</sup>a] If  $V_{DD} = 0V$ , then maximum  $V_{LED} = 3.6V$ .

## 4. Recommended Operating Conditions

Global measurement conditions V<sub>DD</sub> = 2.8V, T<sub>AMB</sub> = 25°C unless otherwise noted.

**Table 3. Recommended Operating Conditions**

| Symbol           | Parameter                                          | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------------------------|---------|---------|---------|-------|

| $V_{DD}$         | Voltage supply on VDD pin                          | 1.7     |         | 3.6     | V     |

| Тамв             | Ambient operating temperature range                | -40     |         | 85      | °C    |

| V <sub>LED</sub> | LED power supply (VDD supplied in operating range) | 3.3     |         | 4.5 [a] | V     |

<sup>[</sup>a] If  $V_{DD} = 0V$ , then maximum  $V_{LED} = 3.6V$ .

<sup>[</sup>b] HBM: C = 100pF charged to  $V_{HBM}$  with resistor R = 1.5k $\Omega$  in series; valid for all pins.

## 5. Electrical and Optical Characteristics

Global measurement conditions  $V_{DD} = 2.8V$ ,  $T_{AMB} = 25$ °C unless otherwise noted.

### **Table 4. Electrical and Optical Characteristics**

Note: See important table notes at the end of the table.

| Symbol                | Parameter                                              | Conditions                                                                                  | Minimum | Typical | Maximum | Units |

|-----------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| Power On              | Reset                                                  |                                                                                             |         |         |         |       |

| POR <sub>LH</sub>     | DC power-on reset level                                | Slow variation of VDD (< 1ms),                                                              |         | 1.2     |         | V     |

| POR <sub>HL</sub>     | DC power-off reset level                               | T <sub>A</sub> = 25°C                                                                       |         | 1.2     |         | V     |

| Current Co            | onsumption                                             |                                                                                             |         |         |         |       |

| I <sub>LS</sub>       | LS/CS (clear and color sensor) active mode current [a] | Default setting; 100% duty cycle;<br>VDD = 2.8V; Gain Mode 3                                |         | 110     |         | μΑ    |

| I <sub>PS_pk</sub>    | PS (proximity sensor) active mode peak current [b]     | Default setting; 100ms period; VDD = 2.8V                                                   |         | 750     |         | μΑ    |

| I <sub>PS_avg</sub>   | PS (proximity sensor) active mode average current [b]  | Default setting; 100ms period; VDD = 2.8V                                                   |         | 80      |         | μΑ    |

| IPPG1_VDD             | PPG1 active mode VDD average current                   | Default measurement period and pulse width                                                  |         | 730     |         | μΑ    |

| I <sub>PPG2_VDD</sub> | PPG2 active mode VDD average current                   | Minimum PPG pulse width and period setting (maximum rate)                                   |         | 780     |         | μΑ    |

|                       | PPG1 active mode LED average current                   | 125mA LED current setting,<br>default PPG pulse width and<br>period settings                |         | 30      |         | mA    |

| IPPG1_LED             |                                                        | 125mA LED current setting,<br>minimum PPG pulse width and<br>period settings (maximum rate) |         | 50      |         | mA    |

|                       | PPG2 active mode LED average current                   | 125mA LED current setting,<br>default PPG pulse width and<br>period settings                |         | 48      |         | mA    |

| IPPG2_LED             |                                                        | 125mA LED current setting,<br>minimum PPG pulse width and<br>period settings (maximum rate) |         | 43      |         | mA    |

| I <sub>SBY</sub>      | Standby VDD current [c]                                | The OB1203 is in Standby Mode; no active I2C communication                                  |         | < 2     | 5       | μΑ    |

| I2C Interfac          | ce                                                     |                                                                                             |         |         |         |       |

| V <sub>I2Chigh</sub>  | I2C signal input high                                  |                                                                                             | 1.26    |         | VDD     | V     |

| V <sub>I2Clow</sub>   | I2C signal input low                                   |                                                                                             | 0       |         | 0.54    | V     |

| Symbol                | Parameter                         | Conditions                                                                                                                   | Minimum | Typical                                     | Maximum | Units         |

|-----------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------|---------|---------------|

| LS Light S            | ensor Characteristics             | ,                                                                                                                            |         |                                             |         |               |

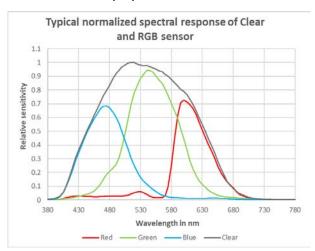

|                       | Spectral response                 |                                                                                                                              |         | See Figur                                   | e 12.   |               |

| RES <sub>LS</sub>     | LS output resolution              | Programmable to 13, 16, 17, 18, 19, 20 bit                                                                                   | 13      | 18                                          | 20      | bit           |

|                       | Dark level count                  | 0 lx, 18-bit range                                                                                                           |         | 0                                           |         | count         |

| t <sub>LS</sub>       | Measurement repetition period [d] | Programmable in 8 steps                                                                                                      | 25      |                                             | 2000    | ms            |

| t <sub>INT</sub>      | Measurement integration time [d]  | Programmable in 6 steps                                                                                                      | 50      |                                             | 400     | ms            |

| G <sub>1</sub>        | Sensitivity at gain 1             | Example for 3050 K, 5 klx LED light, 18-bit sensor resolution. Specification changes with the resolution setting as shown in |         | C: 9160<br>R: 3160<br>G: 4280<br>B: 1470    |         | counts        |

| G <sub>3</sub>        | Sensitivity at gain 3             | Table 7.  Typical spectrum of used LED light source                                                                          |         | C: 27480<br>R: 9480<br>G: 12840<br>B: 4410  |         | counts        |

| G <sub>6</sub>        | Sensitivity at gain 6             | 0.5<br>0.04<br>0.2<br>0.1<br>0.0<br>0.2<br>0.1<br>0.0<br>0.0<br>0.0<br>0.0<br>0.0<br>0.0<br>0.0                              |         | C: 54960<br>R: 18960<br>G: 25680<br>B: 8820 |         | counts        |

| PS Proxim             | ity Sensor Characteristics        | -                                                                                                                            |         |                                             |         | <u> </u>      |

| RES <sub>PS_bit</sub> | Measurement resolution            | Depends on pulse width and number of LED pulses; see sections 7.9.12 and 7.9.13                                              | 10      | 15                                          | 16      | bit           |

| RES <sub>PS_irr</sub> | Signal strength IR                | 125mA LED current; 8 pulse                                                                                                   | 2830    | 3300                                        | 4030    | counts        |

| RES <sub>PS_red</sub> | Signal strength Red               | average; gain mode 1;<br>4.6cm round white reflective target<br>el in 4.6cm distance                                         | 2300    | 2660                                        | 3200    | counts        |

| ALC <sub>max</sub>    | Ambient light cancellation        |                                                                                                                              |         | >100000                                     |         | lx            |

| N <sub>PULSE</sub>    | Number of LED pulses              |                                                                                                                              | 1       | 8                                           | 32      |               |

| t <sub>PS</sub>       | Measurement period                | Programmable in 8 steps                                                                                                      |         | 3.125 to 400                                |         | ms            |

|                       |                                   | Three possible settings; configur-                                                                                           |         | 26                                          |         | μs            |

| t <sub>PS_pw</sub>    | Pulse width                       | able via register setting; see                                                                                               |         | 42                                          |         | μs            |

|                       |                                   | section 7.9.13                                                                                                               |         | 71                                          |         | μs            |

|                       | Analog crosstalk cancellation     | Programmable 0 or 50% FS                                                                                                     |         | 50%                                         |         | Full<br>scale |

|                       | Digital crosstalk cancellation    | Programmable: 0 to full signal level. For 16-bit resolution.                                                                 | 0       |                                             | 65535   | count         |

| Symbol Parameter           |                                           | Conditions                                                                               | Minimum | Typical      | Maximum | Units         |

|----------------------------|-------------------------------------------|------------------------------------------------------------------------------------------|---------|--------------|---------|---------------|

| PPG Chara                  | cteristics                                |                                                                                          |         |              |         |               |

| RESppg                     | Measurement resolution                    |                                                                                          | 16      | 18           | 18      | bit           |

| Appg                       | Digital averaging factor                  |                                                                                          | 1       |              | 32      |               |

| tppg                       | Measurement period                        | Programmable in 8 steps                                                                  |         | 0.3125 to 20 |         | ms            |

| t <sub>PPG_pw</sub>        | Pulse width                               | Configurable via register setting;                                                       |         | 130          |         | μs            |

|                            |                                           | see section 7.9.32                                                                       |         | 247          |         |               |

|                            |                                           |                                                                                          |         | 481          |         |               |

|                            |                                           |                                                                                          |         | 949          |         |               |

|                            | IR counts                                 | 18% grey card reflector (6mm from top of package); sample under clear cover glass; 125mA |         | 28000        |         | count         |

|                            | Red counts                                | LED current; 130µs LED on time; average over 100 samples per second.                     |         | 28000        |         | count         |

|                            | Analog crosstalk cancellation             | Programmable 0 or 50% FS                                                                 |         | 50%          |         | Full<br>scale |

|                            | Sample rate accuracy vs. nominal          |                                                                                          | -2      |              | 2       | %             |

| Measureme                  | ent Timing                                |                                                                                          | •       |              |         |               |

| twake-stb                  | Wake-up time from Standby<br>Mode         | From Standby to Active Mode (measurement can start)                                      |         | 1.5          |         | ms            |

| tstart                     | Start time from VDD apply to Standby Mode |                                                                                          |         | 10           |         | ms            |

| IR LED (LE                 | D1 Pin) Characteristics                   |                                                                                          | •       |              |         |               |

| $\lambda_{Peak}$           | Peak wavelength                           | I <sub>LED</sub> = 100mA, T <sub>A</sub> = 25°C                                          |         | 940          |         | nm            |

| I <sub>IR_LED</sub> (Max)  | IR LED current                            | Programmable in 1024 steps                                                               |         | 250          |         | mA            |

| Red LED (L                 | ED2 Pin) Characteristics                  |                                                                                          |         |              |         |               |

| $\lambda_{Peak}$           | Peak wavelength                           | I <sub>LED</sub> = 20mA, T <sub>A</sub> = 25°C                                           |         | 700          |         | nm            |

| I <sub>RED_LED</sub> (Max) | Red LED current                           | Programmable in 512 steps                                                                |         | 125          |         | mA            |

<sup>[</sup>a] For the LS, the maximum duty cycle is selected with 100ms measurement time (default) and 100ms period at an illumination of 1000 lux.

<sup>[</sup>b] For the PS, 100ms measurement period, 42µs pulse width, 8 pulses, 15-bit resolution, and Gain Mode 1 are selected.

<sup>[</sup>c] Refer to Figure 16 for typical temperature dependence.

<sup>[</sup>d] Typical timing accuracy applied.

<sup>[</sup>e] 90 % reflective Kodak R-27.

### 6. Typical Performance Characteristics

Global measurement conditions V<sub>DD</sub> = 2.8V, T<sub>AMB</sub> = 25°C, and default power-up settings, unless otherwise noted.

Figure 5. Package Rotation Axes for Field of View

Note: For Figure 6 through Figure 11, positive angle values apply to rotations where the respective right side of the package as shown in Figure 5 rotates upwards.

Figure 6. Typical FOV of R, G, B and Clear Photodiode along Width of Package

Figure 8. Typical FOV of R, G, B and Clear Photodiode along Length of Package

Figure 7. Typical FOV of PPG and Proximity

Photodiode along Width of Package

Figure 9. Typical FOV of PPG and Proximity

Photodiode along Length of Package

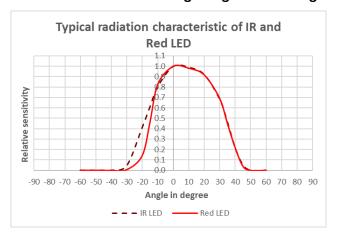

Figure 10. Typical Radiation Characteristic of the LEDs along Width of Package

Figure 12. Typical Normalized Spectral Response of R, G, B and Clear Sensors

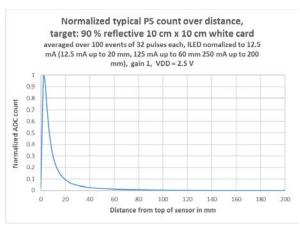

Figure 14. Typical PS Count over Distance

Figure 11. Typical Radiation Characteristic of the LEDs along Length of Package

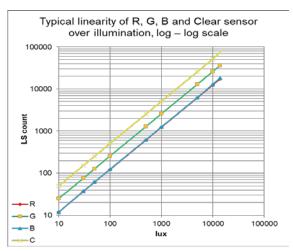

Figure 13. Typical Linearity of R, G, B and Clear Sensors

Figure 15. Log of Typical PS Count

Figure 16. Typical Normalized Standby Current over Temperature

Figure 18. Typical LED Driver Current vs. Current Register Setting

Figure 17. Typical Normalized LED Light Output Linearity with LED Current Register Settings

Figure 19. Typical Normalized Spectral Response of PPG and Proximity Sensor

### 7. Detailed Description

The OB1203 incorporates a sensor IC and two LEDs for excitation in the optical red and infrared range. The IC contains different photodiodes for light (R, G, B, and Clear channels) and proximity measurements as well as photoplethysmography. It also has photodiodes for temperature compensation of the light sensor. The sensor diodes are arranged in a matrix array while the single diode for PS/PPG measurement is located below the matrix. The photodiode current is converted to digital values by an analog-to-digital converter (ADC). The OB1203 also includes a current driver for the LEDs as well as some peripheral circuits, such as two internal oscillators, a current source, and voltage reference. It is trimmed and calibrated at final test using settings in nonvolatile memory (NVM).

Figure 20. Simplified Block Diagram

### 7.1 Application Circuit

Figure 21. Typical Application Circuit

### 7.2 Modes of Operation

Table 5. Channel Activation during Operation Modes

| Mode Name <sup>[a]</sup> | LS      |        | PS      |        | IR PPG  |        | Red PPG |        |

|--------------------------|---------|--------|---------|--------|---------|--------|---------|--------|

| wode warner              | Standby | Active | Standby | Active | Standby | Active | Standby | Active |

| Standby                  | ✓       |        | ✓       |        | ✓       |        | ✓       |        |

| LS only                  |         | ✓      | ✓       |        | ✓       |        | ✓       |        |

| PS only                  | ✓       |        |         | ✓      | ✓       |        | ✓       |        |

| LS+PS                    |         | ✓      |         | ✓      | ✓       |        | ✓       |        |

| PPG1                     | ✓       |        | ✓       |        |         | ✓      | ✓       |        |

| PPG2                     | ✓       |        | ✓       |        |         | ✓      |         | ✓      |

<sup>[</sup>a] All other mode combinations are prohibited and should not be used. Otherwise proper operation is not guaranteed.

#### 7.3 Main State Machine

The main state machine is set to "Start State" during a power-on or software reset. As soon as the reset is released, the internal low power (LP) oscillator is started and the programmed I2C address and the trim values are read from the internal NVM trimming data block. The OB1203 enters Standby Mode as soon as the Idle State is reached (see Figure 22).

NOTE: If the I2C address has yet not been read, the device will respond with NACK to any I2C command and ignore any request in order to avoid responding to an incorrect I2C address.

The sensor mode is selected with the respective bits in the *MAIN\_CTRL\_0* (see section 7.9.9) or *MAIN\_CTRL\_1* register (see section 7.9.10; e.g., the LS\_EN bit is set to 1. If any of the sensor operation modes are activated through an I2C command, the internal support blocks are immediately powered on. Once the voltages and currents are settled (typically after 1.5ms), the state machine checks for trigger events from a measurement scheduler to start conversions according to the selected measurement periods (see sections 7.9.13, 7.9.18, and 7.9.32).

When the user resets the LS\_EN bit (or the PPG\_PS\_EN bit) to '0,' a running conversion will be completed and the relevant ADCs will move to Standby Mode thereafter. The support blocks will only move to Standby Mode if all sensors are inactive.

If any of the sensors are programmed to "Sleep After Interrupt" (SAI) with the SAI bits in the MAIN\_CTRL\_0 or MAIN\_CTRL\_1 register, the relevant ADCs will move to Standby Mode after the interrupt condition occurs. Also the sensor enable bits LS\_EN or PPG\_PS\_EN will be set following a read out of the corresponding status register STATUS\_0 or STATUS\_1.

The deactivation of either LS or PPG/PS in the *MAIN\_CTRL\_0* or *MAIN\_CTRL\_1* registers will not clear the related status bits in the *STATUS\_0* or *STATUS\_1* register. They will always be reset upon activation of the respective sensor.

If no measurements are enabled, as on power-up, the OB1203 is automatically in Low-Power Standby Mode.

Figure 22. Simplified Main State Machine

### 7.4 Light Sensor Description

The light sensor (LS) can be operated independently and in parallel to the proximity sensor (PS). It can be configured to run in LS Mode (Green, Clear and Comp) or in CS mode (Red, Green, Blue, Clear, and Comp) (see Table 6). If the full CS functionality is not needed, LS Mode can be selected in the MAIN\_CTRL\_0 (15<sub>HEX</sub>) register (see section 7.9.9).

The Comp channel receives data from a metal-covered photodiode used to measure dark current and compensate the readings of the light sensors for temperature changes.

Table 6. LS Channel Activation in LS and CS Mode

| LS Mode          | Red | Green | Blue | Clear | Comp |

|------------------|-----|-------|------|-------|------|

| LS (LS_Mode = 0) |     | ✓     |      | ✓     | ✓    |

| CS (LS_Mode = 1) | ✓   | ✓     | ✓    | ✓     | ✓    |

The OB1203 light sensor range and sensitivity are configured by the LS\_RES\_PERIOD register (22<sub>HEX</sub>; see section 7.9.18) and LS\_GAIN register (23<sub>HEX</sub>; see section 7.9.19). The same gain and resolution (measurement time) settings are applied to the LS/CS channels. If different gain or resolution settings are required for different channels, conversions must be performed consecutively with modified settings.

Gain (i.e., 1x, 3x, 6x) sets the maximum light level that will saturate the sensor. Higher gain means a smaller maximum and minimum detectable signal.

Resolution sets the dynamic range, namely the number of counts that corresponds to the highest signal. Higher resolutions have a higher maximum number of counts and a correspondingly smaller least significant bit (higher sensitivity). Higher resolution is obtained by a longer integration (measurement) time.

For automatic gain control methods, if a channel is saturated or close to saturation, e.g. above 80% of max counts, the user application can decrease the gain. If the light level is less than about 20% for all sensors' readings, the user's application can increase the gain.

In order to make measurements at different resolutions and gains equivalent, appropriate scaling should be performed. An example calculation of lux given in Equation 1, Equation 2, and Equation 3 scales all measurements to the highest gain and highest resolution.

$$Lux = Gain_{scale} Res_{scale} (C_1R + C_2G + C_3B)$$

Equation 1

$$Gain_{scale} = \frac{6}{gain}$$

Equation 2

$$Res_{scale} = 2^{(20 - res)}$$

Equation 3

Where *gain* is 1, 3, or 6, res is 13, 16, 17, 18, 19, or 20 and  $C_1$ ,  $C_2$ , and  $C_3$  are application-specific color correction coefficients.

| Table 7. | LS Detection Ranges and Sensitivity Calculation Example |

|----------|---------------------------------------------------------|

|----------|---------------------------------------------------------|

|                      |                          |                   |             | Gain <sup>[a]</sup> 1              | Gain        | 3     | Gain        | 6     |

|----------------------|--------------------------|-------------------|-------------|------------------------------------|-------------|-------|-------------|-------|

| Resolution<br>[bits] | Measurement<br>Time [ms] | Maximum<br>Counts | Sensitivity | Range (Detectable<br>Light Levels) | Sensitivity | Range | Sensitivity | Range |

| 13                   | 3.125                    | 8191              | 1x          | 6x                                 | 3x          | 3x    | 6х          | 1x    |

| 16                   | 25                       | 65535             | 8x          | 6x                                 | 24x         | 3x    | 48x         | 1x    |

| 17                   | 50                       | 131071            | 16x         | 6x                                 | 48x         | 3x    | 96x         | 1x    |

| 18 (default)         | 100                      | 262143            | 32x         | 6x                                 | 96x         | 3x    | 192x        | 1x    |

| 19                   | 200                      | 524,288           | 64x         | 6x                                 | 192x        | 3x    | 384x        | 1x    |

| 20                   | 400                      | 1,048,575         | 128x        | 6x                                 | 384x        | 3x    | 768x        | 1x    |

### 7.5 Proximity and PPG Sensor Description

The proximity and PPG sensor measures the amount of reflected energy in the red and infrared range from a target object using the LED cathode/driver outputs on the LED2 and LED1 pins, respectively. The transmitter is realized with an infrared LED (peak wavelength of approximately 940nm) and a red LED (peak wavelength of approximately 700nm) that are integrated in the OB1203 module.

The photodiode is integrated on-chip. Its analog output signal is converted to a digital value by an integrated ADC. The conversion result is stored in an output register that can be read via the I2C bus. There are four gain modes to adjust the PS/PPG sensitivity of the OB1203 to the needs of the application.

Ambient light influence is suppressed by default (ambient light cancellation). To reduce the influence of crosstalk of reflected LED light behind a cover glass or from the skin surface, the OB1203 has an analog crosstalk cancellation built in. This function can subtract a DC offset signal before the analog-to-digital conversion and therefore avoids reduction in the sensor's dynamic range by optical crosstalk or unwanted optical back scatter. For further details, see the *OB1203 Application Note – PS/PPG Crosstalk Cancelation*. The value of the DC offset signal is accessible via a register each for the PPG and PS measurements. The external application must determine the appropriate cancelation values prior to the start of the measurement. After AD conversion but before the interrupt threshold comparison, the PS Mode allows an additional digital crosstalk reduction (see 7.5.2).

#### 7.5.1 LEDs and Integrated LED Driver

The built-in LEDs are controlled via the integrated LED driver of the OB1203. The LED intensity can be adjusted by the LED current (refer to Table 4). The LED currents are adjustable in register *PS\_LED\_CURR* for PS and *PPG\_IRLED\_CURR/PPG\_RLED\_CURR* for PPG independently (sections 7.9.11, 7.9.28, and 7.9.29).

#### 7.5.2 Principles of Proximity Sensor Operation

The proximity sensor can be operated independently and in parallel with the light sensor. By default, the IR LED (LED1 pin) is used as the transmitter. The PS gain is adjustable in four steps with the *PPG PS GAIN* register (see section 7.9.26).

The timing is programmable by defining the number of LED pulses  $N_{PULSES}$ , the pulse width  $t_{PS\_pW}$ , and the measurement period  $t_{PS}$  (refer to Figure 23 and Table 8) in the  $PS\_PWIDTH\_PERIOD$  register; see section 7.9.13. The pulse repetition period  $t_{PS\_pV}$  depends on the pulse width  $t_{PS\_pW}$ .

An analog cancellation that allows a rough adjustment without loss of dynamic range for the PS is accessible with the *PS\_CAN\_PULSES* register; see section 7.9.30. A digital crosstalk cancellation can be used for fine adjustments (see sections 7.5 and 7.9.12). The digital cancellation value is automatically subtracted from the PS conversion result.

To improve PS data noise, the moving average and hysteresis features can be activated in the *PS\_MOV\_AVG\_HYS* register; refer to section 7.9.15.

Figure 23. PS Timing Characteristic

Table 8. PS Parameter

| Setting                  | Symbol             | Range of settings    |

|--------------------------|--------------------|----------------------|

| Number of LED pulses [a] | Npulses            | 1 to 32              |

| Measurement period       | tps                | 3.125ms to 400ms     |

| Pulse width              | t <sub>PS_pw</sub> | 26µs   42µs   71µs   |

| Pulse repetition period  | t <sub>PS_pr</sub> | 89µs   118µs   176µs |

<sup>[</sup>a] For measurement periods of 3.125ms and pulse widths above 26µs, the number of LED pulses is limited to 16.

#### 7.5.3 Principles of PPG Sensor Operation

The PPG sensor can operate with two modes: PPG1 and PPG2. For PPG1 Mode, only LED1 (the IR LED) is used by default. This mode allows determination of parameters related to heart rate with an appropriate algorithm. The PPG2 Mode also uses LED2 (the Red LED) as a transmitter. This mode supports further analysis, such as  $SpO_2$  and respiration rate determination. By (temporarily) enabling the LED\_FLIP bit during the measurement, it is possible to use the red LED for PPG1 Mode; see section 7.9.27. Hence, an optical feedback on the correct positioning of the person's finger can be provided. Furthermore HR determination with the red LED instead of the IR LED is supported.

The timing is programmable by defining the pulse width tppg\_pw and the measurement period Tppg (see Figure 24 and Table 9) via changing register *PPG\_PWIDTH\_PERIOD*; see section 7.9.32. The pulse repetition period tppg\_pr depends on the pulse width tppg\_pw.

The influence of reflected light from the skin surface may be reduced by using the analog crosstalk cancellation. This modification is available via a setting in the register *PPG\_CAN\_ANA*, see section 7.9.30.

An averaging function can be applied to improve the signal to noise ratio and to reduce the data rate of the PPG data obtained. The number of samples averaged is programmable via the *PPG AVG* register (see section 7.9.31).

Figure 24. PPG Timing Characteristic (without Averaging)

Table 9. PPG Parameters

Note: Not all combinations of settings are valid. For details, see section 7.9.32.

| Setting                 | Symbol              | Range of Settings |

|-------------------------|---------------------|-------------------|

| Measurement period      | t <sub>PPG</sub>    | 0.3125ms to 20ms  |

| Pulse width             | t <sub>PPG_pw</sub> | 130µs to 949µs    |

| Pulse repetition period | t <sub>PPG_pr</sub> | 294µs to 1934µs   |

The PPG data is stored in a FIFO register. The FIFO consists of 32 words of 3 bytes each, so the FIFO can hold up to 32 samples of PPG1 measurement data or 16 sample pairs of PPG2 measurement data. In PPG2 Mode, the IR LED (LED1) data is written to the FIFO first followed by the result of the red LED (LED2) by default. The FIFO register read out via the I2C register *FIFO\_DATA* has special features to enable reliable, time-resolved PPG measurements; see section 7.7.2.

The FIFO Write Pointer, FIFO Read Pointer, and FIFO Overflow Counter help to control the readout without losing samples. The FIFO Write Pointer contains the FIFO index where the next sample of PPG data will be written in the FIFO (see section 7.9.34). The FIFO Read Pointer contains the FIFO index of the FIFO register (of the first data which has not been read) (section 7.9.35). The FIFO Overflow Counter (see section 7.9.36) counts the number of lost or overwritten samples if the FIFO Rollover Enable is set (see section 7.9.33).

The FIFO\_DATA ( $3B_{HEX}$ ; see section 7.9.37) data register is special, providing access to an internal RAM that stores the biosensor data. Successive reads of the FIFO\_DATA register are indexed through the RAM, not the register map. To access registers beyond  $3B_{HEX}$ , a write operation to a register beyond  $3B_{HEX}$  must be performed.

It is necessary for the FIFO\_DATA register to be read in a single burst (a.k.a. "block") read. To read one data word (of 18 bits), a 3-byte block read at the address 3B<sub>HEX</sub> must be performed. For the read of *n* words a 3*n* byte block read can be performed.

Several readout scenarios depending on the demands of the application are supported by using the "FIFO almost full interrupt" and "PPG data interrupt" settings; see section 7.6.3.

By default, in the event of a full FIFO, no further samples of PPG data are written into the FIFO. If the FIFO Rollover Enable bit (refer to section 7.9.33) is set to 1, when the FIFO is full, new PPG data will overwrite old data in the FIFO.

### 7.6 Interrupt Features

The OB1203 can generate independent LS, PS, and PPG interrupt signals. LS and PS interrupts will be triggered if the upper or lower threshold values are crossed. The PPG interrupts notify on the availability of new PPG data and on an adjustable number of free FIFO registers remaining during a PPG measurement.

Another feature is the option to deactivate a sensor after an interrupt event occurs by setting the *Sleep After Interrupt* bit in the respective *MAIN\_CTRL\_0* or *MAIN\_CTRL\_1* register (*SAI\_LS* and *SAI\_PS* for light and proximity sensors respectively). This feature is independently available for both the PS and LS/CS sensors.

The LS and PS persistence settings determine the number of consecutive samples that must be measured before the interrupt is asserted.

For LS, an interrupt can also be triggered if the output count variation of consecutive conversions has exceeded a defined limit.

The PS Logic Output Mode allows the interrupt pin to show whether objects are near or far. If the PS Logic Output Mode is set, then no other interrupts will be asserted.

All interrupt signals as well as *ps\_logic\_mode* are active low at the INT pin.

Clearing the interrupt status flag by reading the status register will also clear the interrupt signal on the INT pin except in the PS Logic Output Mode.

#### 7.6.1 LS Interrupt

The LS interrupt functionality is configured by the bits in the *INT\_CFG\_0* register (see section 7.9.23). It can function as either threshold triggered (LS\_VAR\_MODE = 0) or variance trigged (LS\_VAR\_MODE = 1).

The LS\_INT\_SEL bits in the *INT\_CFG\_0* register configure which of the LS/CS channels (Clear, Green, Red or Blue) will be compared with the interrupt thresholds.

The threshold interrupt is enabled with LS\_INT\_EN = 1 and LS\_VAR\_MODE = 0. The interrupt is set when the respective \*\_DATA register of the selected interrupt source channel is above the upper or below the lower threshold configured in the LS\_THRES\_UP and LS\_THRES\_LOW registers (see sections 7.9.20 and 7.9.21 respectively) for a specified number of consecutive measurements as configured in the INT\_PST register (1 + LS\_PERSIST) (see section 7.9.25).

The variance interrupt is enabled with LS\_INT\_EN = 1 and LS\_VAR\_MODE = 1. It is set when the absolute value difference between the preceding and the current output data of the selected interrupt source channel is above the variance threshold.

In Variance Mode if LS\_PERSIST > 0 (see section 7.9.25), each measurement must differ from the previous by the specified variance (any combination of up and down changes). LS\_PERSTIST > 0 is not recommended in Variance Mode.

#### 7.6.2 PS Interrupt

The interrupt is configured by the bits in the  $INT\_CFG\_1$  register (see section 7.9.24) and enabled with  $PS\_INT\_EN = 1$ .

The bit *PS\_LOGIC\_MODE* in the *INT\_CFG\_1* register further defines the behavior of the interrupt.

**PS\_LOGIC\_MODE** = 0: The interrupt is set (interrupt pin to ground and the status bits to 1) after each measurement when the *PS\_DATA* is above the upper threshold configured in the *PS\_THRES\_UP* register (see section 7.9.16).

The interrupt is also set (interrupt pin to ground and the status bits to 1) after each measurement when the *PS\_DATA* is below the lower threshold configured in the *PS\_THRES\_LOW* (see section 7.9.17).

The interrupt is cleared (interrupt pin to high; status bit to zero) when the STATUS or PS DATA registers are read or the data measurement is between the two thresholds.

For  $PS\_PERSIST > 0$ , the interrupts occur only after a specified number of consecutive measurements above or below the respective thresholds, as configured in the  $INT\_PST$  register (1 + PS\\_PERSIST) (see section 7.9.25).

To obtain interrupts whenever new data is available, set the upper threshold below the lower threshold and PS\_PERSIST = 0.

Interrupt pin and PS\_interrupt\_status bit: Reset by STATUS\_1 register read (see section 7.9.2)

PS\_data\_status bit: Reset by data register read

PS\_logic\_signal\_status bit: Reset by interrupt condition (signal below lower threshold)

**PS\_LOGIC\_MODE** = 1: The interrupt and the status bits in the *STATUS\_1* register are set (interrupt pin to ground) when the *PS\_DATA* content is above the upper threshold configured in the *PS\_THRES\_UP* register and held until the *PS\_DATA* drops below the lower threshold configured in the *PS\_THRES\_LOW* register. For the PS logic status bit, a set interrupt is equal to the Near Mode (strong reflective signal, object close), while a weak signal (no interrupt) is the Far Mode (object far away).

For PS\_PERSIST > 0, the interrupt changes only after a specified number of consecutive measurements above or below the respective thresholds, as configured in the *INT\_PST* register (1 + PS\_PERSIST) (see section 7.9.25).

PS\_interrupt\_status bit: Reset by STATUS\_1 register read

PS data status bit: Reset by data register read

Interrupt pin and *PS logic status* bit: Reset by interrupt condition (signal below lower threshold)

The PS interrupt generator is shown in the upper part of Figure 25. An example of the interrupt behavior is shown in Figure 25.

Figure 25. PS Interrupt Behavior Examples

Note: The *STATUS\_0* and *STATUS\_1* registers should be read out immediately after an interrupt transition has occurred on the INT pin. As the interrupts are not reset automatically, an interrupt event caused by crossing the opposite threshold could be missed.

#### 7.6.3 PPG Interrupt

The FIFO\_almost\_full interrupt is enabled by setting the A\_FULL\_INT\_EN bit in register INT\_CFG\_1 to '1' (see section 7.9.24). It is triggered when a certain number of free FIFO registers are remaining. This number can be configured in register FIFO\_CFG (see section 7.9.33). The status bit of the FIFO almost full interrupt in the STATUS\_1 register is set even if the interrupt pin is disabled. The status bit FIFO almost full interrupt is cleared by reading the STATUS\_1 register or reading the FIFO\_DATA register.

The PPG data interrupt is enabled by setting the *PPG\_INT\_EN* bit in register *INT\_CFG\_1* to '1' (see section 7.9.24). It is triggered when a new sample of PPG measurement data is available in the FIFO. The *PPG data status* bit is set even if the interrupt pin is disabled. The *PPG data status* bit is cleared by reading the *STATUS\_1* register or reading the *FIFO\_DATA* register.

#### 7.7 I2C Interface

The OB1203 is equipped with an I2C interface for control and data communication. The chip always operates as a slave. A read/write bit must be appended to the slave address by the master device to properly communicate with the device.

The interface is compatible with Standard Mode (100kHz) and Fast Mode (400kHz) I2C communication.

Table 10. Supported I2C clock Frequencies

| Mode     | Frequency | Transient Noise Filter |

|----------|-----------|------------------------|

| Standard | 100kHz    | 50ns                   |

| Fast     | 400kHz    | 50ns                   |

The I2C circuitry is always active (Standby or Active Mode of the OB1203). If the I2C address is not yet read from the memory block, the device will respond with "NACK" to any request and ignore the possible commands. An attempt to read or write to non-existing addresses will be answered with "NACK."

#### 7.7.1 I2C Address Decoding

The 7 bit I2C address of the device is 53<sub>HEX</sub>. Appending the write / read bit yields A6<sub>HEX</sub> for write and A7<sub>HEX</sub> for read in the I2C address command.

#### 7.7.2 I2C Register Read

The OB1203 registers can be read individually or in Block Read Mode. If the last valid address (51<sub>HEX</sub>) has been reached, but the master continues with the block read, the address counter in the OB1203 will not roll over and the OB1203 returns 00<sub>HEX</sub> for every subsequent byte read.

The block read operation is the only way to ensure correct data read out of multi-byte data registers and to avoid splitting of results with HIGH and LOW bytes originating from different conversions. If an I2C read operation is active, all registers are locked until the I2C read operation is completed. This guarantees that the data in the LS/PS data and status registers come from the same measurement even if an additional measurement cycle ends during the read operation. New measurement data is stored into temporary registers and the I2C \*\_DATA registers are updated as soon as there is no on-going I2C read operation.

The FIFO\_DATA register (see section 7.9.37) behaves differently from all other readable registers. Reading the FIFO\_DATA register does not increment the register address. A block read from this register reads this address again and again. However the FIFO\_RD\_PTR register is incremented after reading a sample consisting of 3 bytes and so the FIFO can be read byte-by-byte. To continue I2C register reads after FIFO\_DATA, a new command with the address of this register must be sent before the data from this and the following registers can be read. See section 7.9.37 for more details.

If a read access is started on an address outside the valid address range, the OB1203 will return NACK until the I2C operation is ended.

Read operations must follow the timing diagram in Figure 26.

#### Figure 26. I2C Register Read

#### 7.7.3 I2C Register Write

The OB1203 registers can be written to individually or in Block Write Mode. If a register includes read (R) and read/write (RW) bits, data written to read-only bits are ignored.

If the last valid address (51<sub>HEX</sub>) of the OB1203 address range is reached but the master attempts to continue the block write operation, the address counter of the OB1203 will not roll over. The OB1203 will return NACK for every following byte sent by the master until the I2C operation is ended.

If a write access is started on an address outside the valid address range, the OB1203 will return NACK until the I2C operation is ended.

Some register bits are R/W and must be set to a specific value 0 or 1 as indicated in the register map.

Write operations must follow the timing diagram in Figure 27.

Figure 27. I2C Register Write

## 7.7.4 I2C Interface Bus Timing

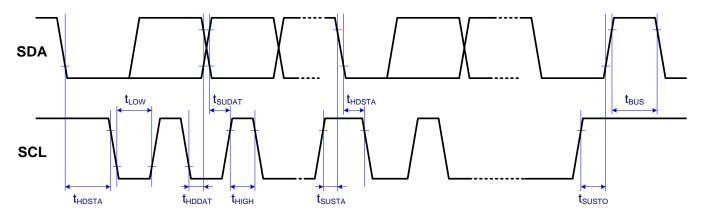

Figure 28. Bus Timing

Table 11. Bus Timing Characteristic

| Parameter                                                        | Symbol             | Standard Mode | Fast Mode | Units |

|------------------------------------------------------------------|--------------------|---------------|-----------|-------|

| Maximum SCL clock frequency                                      | f <sub>SCL</sub>   | 100           | 400       | kHz   |

| Minimum START condition hold time relative to SCL edge           | thdsta             | 4             |           | μs    |

| Minimum SCL clock low width                                      | t <sub>LOW</sub>   | 4.7           |           | μs    |

| Minimum SCL clock high width                                     | thigh              | 4             |           | μs    |

| Minimum START condition setup time relative to SCL edge          | tsusta             | 4.7           |           | μs    |

| Minimum data hold time on SDA relative to SCL edge               | t <sub>HDDAT</sub> | 0             |           | μs    |

| Minimum data setup time on SDA relative to SCL edge              | tsudat             | 0.1           | 0.1       | μs    |

| Minimum STOP condition setup time on SCL                         | tsusто             | 4             |           | μs    |

| Minimum bus free time between stop condition and start condition | t <sub>BUS</sub>   | 4.7           |           | μs    |

## 7.8 Summary of Internal Registers

Table 12. Register Map

| Address           | Туре | Name            | Default Value     | Description                                       |

|-------------------|------|-----------------|-------------------|---------------------------------------------------|

| 00 <sub>HEX</sub> | R    | STATUS_0        | 80 <sub>HEX</sub> | Power-on status, LS interrupt, and LS data status |

| 01 <sub>HEX</sub> | R    | STATUS_1        | 00 <sub>HEX</sub> | PPG/PS data status, PS/PPG interrupt status       |

| 02нех             | R    | PS_DATA_0       | 00нех             | PS measurement data, LSB                          |

| 03нех             | R    | PS_DATA_1       | 00нех             | PS measurement data, MSB                          |

| 04нех             | R    | LS_CLEAR_DATA_0 | 00нех             | LS Clear measurement data, LSB                    |

| 05нех             | R    | LS_CLEAR_DATA_1 | 00нех             | LS Clear measurement data intervening bits        |

| 06нех             | R    | LS_CLEAR_DATA_2 | 00нех             | LS Clear measurement data, MSB                    |

| Address           | Туре | Name             | Default Value     | Description                                    |

|-------------------|------|------------------|-------------------|------------------------------------------------|

| 07нех             | R    | LS_GREEN_DATA_0  | 00нех             | LS Green/LS measurement data, LSB              |

| 08нех             | R    | LS_GREEN_DATA_1  | 00нех             | LS Green/LS measurement data intervening bits  |

| 09нех             | R    | LS_GREEN_DATA_2  | 00нех             | LS Green/LS measurement data, MSB              |

| ОАнех             | R    | LS_BLUE_DATA_0   | 00нех             | LS Blue measurement data, LSB                  |

| 0Внех             | R    | LS_BLUE_DATA_1   | 00 <sub>HEX</sub> | LS Blue measurement data intervening bits      |

| 0Снех             | R    | LS_BLUE_DATA_2   | 00 <sub>HEX</sub> | LS Blue measurement data, MSB                  |

| 0D <sub>HEX</sub> | R    | LS_RED_DATA_0    | 00 <sub>HEX</sub> | LS Red measurement data, LSB                   |

| 0E <sub>HEX</sub> | R    | LS_RED_DATA_1    | 00 <sub>HEX</sub> | LS Red measurement data intervening bits       |

| 0F <sub>HEX</sub> | R    | LS_RED_DATA_2    | 00 <sub>HEX</sub> | LS Red measurement data, MSB                   |

| 10 <sub>HEX</sub> | R    | COMP_DATA_0      | 00 <sub>HEX</sub> | LS Comp measurement data, LSB                  |

| 11 <sub>HEX</sub> | R    | COMP_DATA_1      | 00 <sub>HEX</sub> | LS Comp measurement data intervening bits      |

| 12 <sub>HEX</sub> | R    | COMP_DATA_2      | 00 <sub>HEX</sub> | LS Comp measurement data, MSB                  |

| 15нех             | R/W  | MAIN_CTRL_0      | 00нех             | LS operation mode control, software (SW) reset |

| 16нех             | R/W  | MAIN_CTRL_1      | 00нех             | PPG/PS operation mode control                  |

| 17нех             | R/W  | PS_LED_CURR_0    | FFHEX             | PS LED current, LSB                            |

| 18нех             | R/W  | PS_LED_CURR_1    | 01нех             | PS LED current, MSB                            |

| 19 <sub>HEX</sub> | R/W  | PS_CAN_PULSES    | 1A <sub>HEX</sub> | PS analog cancellation level and pulse setting |

| 1A <sub>HEX</sub> | R/W  | PS_PWIDTH_PERIOD | 15нех             | PS pulse width and measurement period          |

| 1Внех             | R/W  | PS_CAN_DIG_0     | 00нех             | PS digital cancellation level setting, LSB     |

| 1Снех             | R/W  | PS_CAN_DIG_1     | 00нех             | PS digital cancellation level setting, MSB     |

| 1D <sub>HEX</sub> | R/W  | PS_MOV_AVG_HYS   | 00 <sub>HEX</sub> | PS moving average and hysteresis configuration |

| 1E <sub>HEX</sub> | R/W  | PS_THRES_UP_0    | FF <sub>HEX</sub> | PS interrupt upper threshold, LSB              |

| 1F <sub>HEX</sub> | R/W  | PS_THRES_UP_1    | FF <sub>HEX</sub> | PS interrupt upper threshold, MSB              |

| 20 <sub>HEX</sub> | R/W  | PS_THRES_LOW_0   | 00 <sub>HEX</sub> | PS interrupt lower threshold, LSB              |

| 21 <sub>HEX</sub> | R/W  | PS_THRES_LOW_1   | 00 <sub>HEX</sub> | PS interrupt lower threshold, MSB              |

| 22 <sub>HEX</sub> | R/W  | LS_RES_PERIOD    | 22 <sub>HEX</sub> | LS resolution and measurement period setting   |

| 23 <sub>нех</sub> | R/W  | LS_GAIN          | 01 <sub>HEX</sub> | LS analog gain range setting                   |

| 24 <sub>HEX</sub> | R/W  | LS_THRES_UP_0    | FF <sub>HEX</sub> | LS interrupt upper threshold, LSB              |

| 25нех             | R/W  | LS_THRES_UP_1    | FFHEX             | LS interrupt upper threshold, intervening bits |

| 26нех             | R/W  | LS_THRES_UP_2    | 0F <sub>HEX</sub> | LS interrupt upper threshold, MSB              |

| 27нех             | R/W  | LS_THRES_LOW_0   | 00нех             | LS interrupt lower threshold, LSB              |

| 28нех             | R/W  | LS_THRES_LOW_1   | 00нех             | LS interrupt lower threshold, intervening bits |

| 29нех             | R/W  | LS_THRES_LOW_2   | 00нех             | LS interrupt lower threshold, MSB              |

| 2A <sub>HEX</sub> | R/W  | LS_THRES_VAR     | 00нех             | LS interrupt variance threshold                |

| Address           | Туре  | Name              | Default Value     | Description                                 |

|-------------------|-------|-------------------|-------------------|---------------------------------------------|

| 2Внех             | R/W   | INT_CFG_0         | 10нех             | LS interrupt configuration                  |

| 2Снех             | R/W   | INT_CFG_1         | 00нех             | PS/PPG interrupt configuration              |

| 2D <sub>HEX</sub> | R/W   | INT_PST           | 00нех             | LS/PS interrupt persist setting             |

| 2E <sub>HEX</sub> | R/W   | PPG_PS_GAIN       | 09нех             | PPG/PS gain setting                         |

| 2F <sub>HEX</sub> | R/W   | PPG_PS_CFG        | 40 <sub>HEX</sub> | PPG power save and LED flip setting         |

| 30 <sub>HEX</sub> | R/W   | PPG_IRLED_CURR_0  | 00 <sub>HEX</sub> | PPG IR LED (LED1) current, LSB              |

| 31 <sub>HEX</sub> | R/W   | PPG_IRLED_CURR_1  | 00 <sub>HEX</sub> | PPG IR LED current, MSB                     |

| 32 <sub>HEX</sub> | R/W   | PPG_RLED_CURR_0   | 00 <sub>HEX</sub> | PPG Red LED (LED2) current, LSB             |

| 33 <sub>HEX</sub> | R/W   | PPG_RLED_CURR_1   | 00 <sub>HEX</sub> | PPG Red LED current, MSB                    |

| 34 <sub>HEX</sub> | R/W   | PPG_CAN_ANA       | 00 <sub>HEX</sub> | PPG analog cancellation value               |

| 35 <sub>HEX</sub> | R/W   | PPG_AVG           | 0A <sub>HEX</sub> | Number of averaged PPG samples              |

| 36нех             | R/W   | PPG_PWIDTH_PERIOD | 42 <sub>HEX</sub> | PPG pulse width and measurement period      |

| 37 <sub>HEX</sub> | R/W   | FIFO_CFG          | 00нех             | FIFO rollover and almost full configuration |

| 38нех             | R/(W) | FIFO_WR_PTR       | 00нех             | FIFO write pointer                          |

| 39нех             | R/(W) | FIFO_RD_PTR       | 00нех             | FIFO read pointer                           |

| ЗАнех             | R/(W) | FIFO_OVF_CNT      | 00нех             | FIFO overflow counter                       |

| 3Внех             | R     | FIFO_DATA         | 00нех             | FIFO mirrored PPG data                      |

| 3D <sub>HEX</sub> | R     | PART_ID           | TBD               | Part number ID                              |

### 7.9 Detailed Description of Registers

#### 7.9.1 STATUS\_0

Address 00<sub>HEX</sub>

Default value 80<sub>HEX</sub>

Register access R

| Bit   |

|-------|

| 00нех |

| 7                   | 6 | 5 | 4 | 3 | 2 | 1                       | 0                  |

|---------------------|---|---|---|---|---|-------------------------|--------------------|

| Power-On_<br>status | 0 | 0 | 0 | 0 | 0 | LS_interrupt_<br>status | LS_data_<br>status |

Bit[7] Power-On\_ status:

If set to 1, the part has had a power-up event, either because the part was turned on or because there was a power-supply voltage disturbance

A value of 1 is the default for the first register read after power-on reset.

**Note:** All interrupt threshold settings in the registers have been reset to power-on default states and should be examined if the *Power-On status* flag is set.

The flag is cleared after the register is read.

Bit[1] LS\_ interrupt\_status: (updated even if the interrupt pin is disabled)

0 Interrupt condition has not occurred (default)

1 Interrupt condition has occurred (cleared after read)

Bit[0] LS\_data\_status:

Old data, already read (default)

1 New data, not yet read (cleared after read)

#### 7.9.2 STATUS\_1

$\begin{array}{lll} \text{Address} & \text{O1}_{\text{HEX}} \\ \text{Default value} & \text{O0}_{\text{HEX}} \\ \text{Register access} & \text{R} \\ \end{array}$

| BII   |  |

|-------|--|

| 01нех |  |

| 7              | 6 | 5                              | 4                   | 3 | 2                       | 1                       | 0              |

|----------------|---|--------------------------------|---------------------|---|-------------------------|-------------------------|----------------|

| TS_data_status | Х | FIFO_almost_<br>full_interrupt | PPG_data_<br>status | 0 | PS_logic_signal _status | PS_interrupt_<br>status | PS_data_status |

Bit[7] *TS\_data\_status:*

Old data, already read (default)

1 New data, not yet read (cleared after read)

Bit[6] reserved

Bit[5] FIFO\_almost\_full\_interrupt (updated even when the interrupt pin is disabled)

0 Interrupt condition has not occurred (default)

1 Interrupt condition has occurred (cleared after read, also cleared by reading FIFO\_DATA)

Bit[4] *PPG\_data\_status*:

Old data, already read (default)

1 New data, not yet read (cleared after read, also cleared by reading FIFO\_DATA)

Bit[2] *PS\_logic\_signal\_status*:

Object is far (default)

1 Object is close

Bit[1] PS\_interrupt\_status: (updated even when the interrupt pin is disabled)

0 Interrupt condition has not occurred (default)

1 Interrupt condition has occurred (cleared after read)

Bit[0] *PS\_data\_status:*

Old data, already read (default)

1 New data, not yet read (cleared after read)

#### 7.9.3 PS\_DATA

Address 02<sub>HEX</sub> and 03<sub>HEX</sub>

Default value 00<sub>HEX</sub> and 00<sub>HEX</sub>

Register access R

| Bit           | 7         | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------------|-----------|-----------|---|---|---|---|---|---|--|--|

| <b>02</b> HEX |           | PS_DATA_0 |   |   |   |   |   |   |  |  |

| 03нех         | PS_DATA_1 |           |   |   |   |   |   |   |  |  |

The PS conversion result is automatically corrected by the value of the PS cancellation register (*PS\_CAN\_DIG*, see section 7.9.14):

PS\_ DATA = PS\_meas - PS\_CAN\_DIG

*PS\_meas* is the internal raw value obtained from the PS ADC. If the operations PS moving average and/or PS hysteresis are enabled, they will affect the PS data before they are written in the *PS\_DATA* register.

The PS conversion result is written MSB-aligned into the PS\_DATA registers. The result must always be treated as a 16-bit value regardless of the measurement resolution resulting from the pulse width setting selected in the *PS\_PWIDTH\_PERIOD* register (see section 7.9.13). For example, in 10-bit resolution, bits 0 to 5 in *PS\_DATA\_0* are always zero. The smallest value above zero is therefore 64 counts.

Reg 02<sub>HEX</sub> Bit[7:0] PS measurement least significant data byte, bit 0 is always the LSB of the data word

Reg 03<sub>HEX</sub> Bit[7:0] PS measurement most significant data byte, bit 7 is always the MSB of the data word

#### 7.9.4 LS\_CLEAR\_DATA

Address 04HEX, 05HEX, and 06HEX

Default value 00HEX, 00HEX, and 00HEX

Register access R

| Bit           | 7               | 6 | 5 | 4 | 3               | 2 | 1 | 0 |  |

|---------------|-----------------|---|---|---|-----------------|---|---|---|--|

| <b>04</b> HEX | LS_CLEAR_DATA_0 |   |   |   |                 |   |   |   |  |

| 05нех         | LS_CLEAR_DATA_1 |   |   |   |                 |   |   |   |  |

| 06нех         | 0               | 0 | 0 | 0 | LS_CLEAR_DATA_2 |   |   |   |  |

Light sensor Clear channel digital output data:

The LS conversion results are automatically compensated by the value of COMP\_DATA:

$LS\_CLEAR\_DATA = (LS\_CLEAR_{int} - COMP\_DATA)$

LS\_CLEAR<sub>int</sub> is the internal raw value obtained from the Clear LS ADC. If LS\_CLEAR<sub>int</sub> is already full-scale, then the value of LS\_CLEAR\_DATA is set to its maximum value without subtracting COMP\_DATA.