# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

4M High Speed SRAM (256-kword × 16-bit)

REJ03C0107-0200 Rev. 2.00 Dec.12.2008

### Description

The R1RW0416D is a 4-Mbit high speed static RAM organized 256-kword  $\times$  16-bit. It has realized high speed access time by employing CMOS process (6-transistor memory cell) and high speed circuit designing technology. It is most appropriate for the application which requires high speed, high density memory and wide bit width configuration, such as cache and buffer memory in system. Especially, L-Version and S-Version are low power consumption and it is the best for the battery backup system. The package prepares 400-mil 44-pin SOJ and 400-mil 44-pin plastic TSOPII for high density surface mounting.

#### Features

- Single 3.3 V supply:  $3.3 \text{ V} \pm 0.3 \text{ V}$

- Access time: 10 ns / 12 ns (max)

- Completely static memory

No clock or timing strobe required

- Equal access and cycle times

- Directly TTL compatible

- All inputs and outputs

- Operating current: 145 / 130mA (max)

- TTL standby current: 40 mA (max)

- CMOS standby current: 5 mA (max)

- : 0.8 mA (max) (L-version)

- : 0.5 mA (max) (S-version)

- Data retention current : 0.4 mA (max) (L-version)

- :0.2 mA (max) (S-version)

- Data retention voltage: 2.0 V (min) (L-version, S-version)

- Center V<sub>CC</sub> and V<sub>SS</sub> type pin out

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 1 of 15

# **Ordering Information**

| Access time | Package                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 ns       |                                                                                                                                                                                                                                                     |

| 12 ns       | 400-mil 44-pin plastic SOJ (44P0K)                                                                                                                                                                                                                  |

| 12 ns       |                                                                                                                                                                                                                                                     |

| 12 ns       |                                                                                                                                                                                                                                                     |

| 10 ns       |                                                                                                                                                                                                                                                     |

| 12 ns       | 400-mil 44-pin plastic TSOPII (44P3W-H)                                                                                                                                                                                                             |

| 12 ns       |                                                                                                                                                                                                                                                     |

| 12 ns       |                                                                                                                                                                                                                                                     |

|             | 10 ns         12 ns |

## **Pin Arrangement**

| 44-pin S                                                                                                                                                                                                     | OJ                                                                                                                                                                                                                                           | 44-pir                                                                                                                                                                                                                                                                                                   | TSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 1 A1 A2<br>A2 3<br>A3 4<br>A4 5<br>CS# 6<br>I/O1 7<br>I/O2 8<br>I/O3 9<br>I/O4 10<br>Vcc 11<br>V55 13<br>I/O6 14<br>I/O7 15<br>I/O8 16<br>WE# 17<br>A5 18<br>A6 19<br>A7 20<br>A8 21<br>A9 22<br>(Top Vie | 44 A17<br>43 A16<br>42 A15<br>41 OE#<br>40 UB#<br>39 LB#<br>38 I/O16<br>37 I/O15<br>36 I/O14<br>35 I/O13<br>34 Vss<br>33 Vcc<br>32 I/O12<br>31 I/O11<br>30 I/O10<br>29 I/O9<br>28 NC<br>27 A14<br>26 A13<br>25 A12<br>24 A11<br>23 A10<br>W) | A0 $\begin{bmatrix} 1 \\ A1 \\ 2 \\ A2 \\ 3 \\ A3 \\ 4 \\ A4 \\ 5 \\ CS# \\ 6 \\ I/O1 \\ 7 \\ I/O2 \\ 8 \\ I/O3 \\ 9 \\ I/O4 \\ 10 \\ V_{CC} \\ 11 \\ V_{SS} \\ 105 \\ 13 \\ I/O6 \\ 14 \\ I/O7 \\ 15 \\ I/O8 \\ 16 \\ WE# \\ 17 \\ A5 \\ 18 \\ A6 \\ 19 \\ A7 \\ 20 \\ A8 \\ 21 \\ A9 \\ 22 \\ (Top V)$ | 44       A17         43       A16         42       A15         41       OE#         40       UB#         39       LB#         38       I/O16         37       I/O15         36       I/O14         35       I/O13         34       Vss         33       Vcc         32       I/O12         31       I/O11         30       I/O10         29       I/O9         28       NC         27       A14         26       A13         25       A12         24       A11         23       A10 |

Dec.12.2008, page 2 of 15

## **Pin Description**

| Pin name        | Function          |  |

|-----------------|-------------------|--|

| A0 to A17       | Address input     |  |

| I/O1 to I/O16   | Data input/output |  |

| CS#             | Chip select       |  |

| OE#             | Output enable     |  |

| WE#             | Write enable      |  |

| UB#             | Upper byte select |  |

| LB#             | Lower byte select |  |

| V <sub>cc</sub> | Power supply      |  |

| V <sub>SS</sub> | Ground            |  |

| NC              | No connection     |  |

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 3 of 15

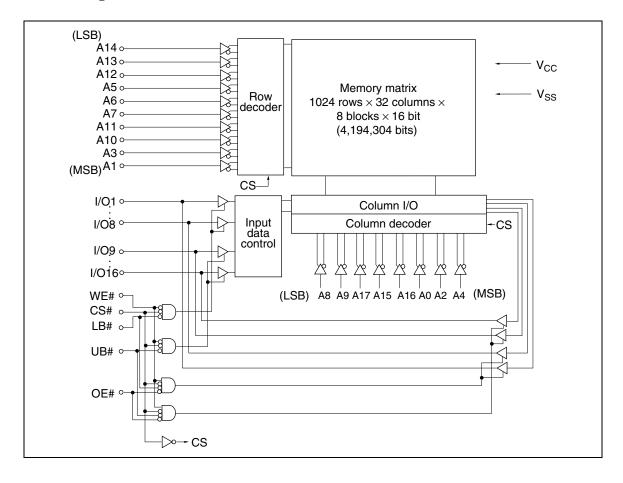

## **Block Diagram**

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 4 of 15

## **Operation Table**

| CS# | OE# | WE# | LB#  | UB# | Mode             | V <sub>cc</sub> current            | I/O1–I/O8 | I/O9–I/O16 | Ref. cycle  |

|-----|-----|-----|------|-----|------------------|------------------------------------|-----------|------------|-------------|

| Н   | ×   | ×   | ×    | ×   | Standby          | I <sub>SB</sub> , I <sub>SB1</sub> | High-Z    | High-Z     | _           |

| L   | Н   | Н   | ×    | ×   | Output disable   | I <sub>CC</sub>                    | High-Z    | High-Z     | _           |

| L   | L   | Н   | L    | L   | Read             | I <sub>CC</sub>                    | Output    | Output     | Read cycle  |

| L   | L   | Н   | L    | Н   | Lower byte read  | I <sub>CC</sub>                    | Output    | High-Z     | Read cycle  |

| L   | L   | Н   | Н    | L   | Upper byte read  | I <sub>CC</sub>                    | High-Z    | Output     | Read cycle  |

| L   | L   | Н   | Н    | Н   | _                | I <sub>CC</sub>                    | High-Z    | High-Z     | _           |

| L   | ×   | L   | L    | L   | Write            | I <sub>CC</sub>                    | Input     | Input      | Write cycle |

| L   | ×   | L   | L    | Н   | Lower byte write | I <sub>CC</sub>                    | Input     | High-Z     | Write cycle |

| L   | ×   | L   | Н    | L   | Upper byte write | I <sub>CC</sub>                    | High-Z    | Input      | Write cycle |

| L   | ×   | L   | Н    | Н   | _                | I <sub>CC</sub>                    | High-Z    | High-Z     | _           |

|     |     |     | - N/ |     | 1                |                                    |           |            |             |

Note: H: V<sub>IH</sub>, L: V<sub>IL</sub>,  $\times$ : V<sub>IH</sub> or V<sub>IL</sub>

## **Absolute Maximum Ratings**

| Parameter                                      | Symbol          | Value                                        | Unit |

|------------------------------------------------|-----------------|----------------------------------------------|------|

| Supply voltage relative to $V_{SS}$            | V <sub>CC</sub> | –0.5 to +4.6                                 | V    |

| Voltage on any pin relative to $V_{\text{SS}}$ | V <sub>T</sub>  | $-0.5^{*1}$ to V <sub>CC</sub> + 0.5 $^{*2}$ | V    |

| Power dissipation                              | P <sub>T</sub>  | 1.0                                          | W    |

| Operating temperature                          | Topr            | 0 to +70                                     | °C   |

| Storage temperature                            | Tstg            | –55 to +125                                  | °C   |

| Storage temperature under bias                 | Tbias           | -10 to +85                                   | °C   |

Notes: 1.  $V_T$  (min) = -2.0 V for pulse width (under shoot)  $\leq$  6 ns.

2.  $V_T$  (max) =  $V_{CC}$  + 2.0 V for pulse width (over shoot)  $\leq$  6 ns.

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 5 of 15

#### **Recommended DC Operating Conditions**

$(Ta = 0 \text{ to } +70^{\circ}C)$

| Parameter      | Symbol                         | Min         | Тур | Max                   | Unit  |  |

|----------------|--------------------------------|-------------|-----|-----------------------|-------|--|

| Supply voltage | V <sub>CC</sub> * <sup>3</sup> | 3.0         | 3.3 | 3.6                   | V     |  |

|                | V <sub>SS</sub> *4             | 0           | 0   | 0                     | V     |  |

| Input voltage  | V <sub>IH</sub>                | 2.0         | _   | V <sub>CC</sub> + 0.5 | i∗² V |  |

|                | V <sub>IL</sub>                | $-0.5^{*1}$ |     | 0.8                   | V     |  |

Notes: 1.  $V_{IL}$  (min) = -2.0 V for pulse width (under shoot)  $\leq$  6 ns.

2.  $V_{IH}$  (max) =  $V_{CC}$  + 2.0 V for pulse width (over shoot)  $\leq$  6 ns.

3. The supply voltage with all  $V_{\text{CC}}$  pins must be on the same level.

4. The supply voltage with all  $V_{\text{SS}}$  pins must be on the same level.

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 6 of 15

### **DC Characteristics**

(Ta = 0 to +70°C,  $V_{CC}$  = 3.3 V ± 0.3 V,  $V_{SS}$  = 0 V)

| Parameter                                  | Symbol                       | Min              | Max            | Unit              | Test conditions |                                                               |

|--------------------------------------------|------------------------------|------------------|----------------|-------------------|-----------------|---------------------------------------------------------------|

| Input leakage current                      |                              | I <sub>LI</sub>  |                | 2                 | μΑ              | $V_{IN} = V_{SS}$ to $V_{CC}$                                 |

| Output leakage current                     |                              | I <sub>LO</sub>  |                | 2                 | μΑ              | $V_{IN} = V_{SS}$ to $V_{CC}$                                 |

| Operating power supply 10 ns cycle current |                              | I <sub>CC</sub>  |                | 145               | mA              |                                                               |

|                                            | 12 ns cycle                  | I <sub>CC</sub>  |                | 130               | mA              |                                                               |

| Standby power supply curre                 | Standby power supply current |                  | _              | 40                | mA              | Min cycle, CS# = $V_{IH}$ ,<br>Other inputs = $V_{IH}/V_{IL}$ |

|                                            |                              | I <sub>SB1</sub> | _              | 5                 | mA              |                                                               |

|                                            |                              |                  | * <sup>1</sup> | 0.8* <sup>1</sup> | mA              |                                                               |

|                                            |                              |                  | *2             | 0.5* <sup>2</sup> | mA              |                                                               |

| Output voltage                             |                              | V <sub>OL</sub>  |                | 0.4               | V               | I <sub>OL</sub> = 8 mA                                        |

|                                            |                              | V <sub>OH</sub>  | 2.4            |                   | V               | $I_{OH} = -4 \text{ mA}$                                      |

Note: 1. This characteristics is guaranteed only for L-version.

2. This characteristics is guaranteed only for S-version.

### Capacitance

$(Ta = +25^{\circ}C, f = 1.0 \text{ MHz})$

| Parameter                  | Symbol          | Min | Max | Unit | Test conditions |

|----------------------------|-----------------|-----|-----|------|-----------------|

| Input capacitance*1        | C <sub>IN</sub> | —   | 6   | pF   | $V_{IN} = 0 V$  |

| Input/output capacitance*1 | CI/O            |     | 8   | pF   | $V_{I/O} = 0 V$ |

Note: 1. This parameter is sampled and not 100% tested.

Dec.12.2008, page 7 of 15

### **AC Characteristics**

(Ta = 0 to +70°C,  $V_{CC}$  = 3.3 V ± 0.3 V, unless otherwise noted.)

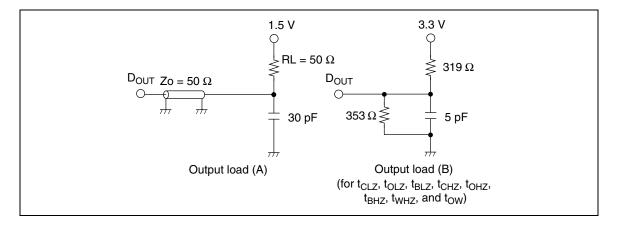

#### **Test Conditions**

- Input pulse levels: 3.0 V/0.0 V

- Input rise and fall time: 3 ns

- Input and output timing reference levels: 1.5 V

- Output load: See figures (Including scope and jig)

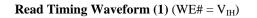

#### **Read Cycle**

|                                                    |                  | R1RV         | V0416D |              |     |      |       |

|----------------------------------------------------|------------------|--------------|--------|--------------|-----|------|-------|

|                                                    |                  | 10ns Version |        | 12ns Version |     | _    |       |

| Parameter                                          | Symbol           | Min          | Max    | Min          | Max | Unit | Notes |

| Read cycle time                                    | t <sub>RC</sub>  | 10           |        | 12           |     | ns   |       |

| Address access time                                | t <sub>AA</sub>  | _            | 10     | _            | 12  | ns   |       |

| Chip select access time                            | t <sub>ACS</sub> | _            | 10     | _            | 12  | ns   |       |

| Output enable to output valid                      | t <sub>OE</sub>  |              | 5      | _            | 6   | ns   |       |

| Byte select to output valid                        | t <sub>BA</sub>  | _            | 5      | _            | 6   | ns   |       |

| Output hold from address change                    | t <sub>OH</sub>  | 3            | _      | 3            | _   | ns   |       |

| Chip select to output in low-Z                     | t <sub>CLZ</sub> | 3            | _      | 3            | _   | ns   | 1     |

| Output enable to output in low-Z                   | t <sub>OLZ</sub> | 0            | _      | 0            | _   | ns   | 1     |

| Byte select to output in low-Z                     | t <sub>BLZ</sub> | 0            | _      | 0            |     | ns   | 1     |

| Chip deselect to output in high-Z t <sub>CHZ</sub> |                  | —            | 5      | —            | 6   | ns   | 1     |

| Output disable to output in high-Z                 | t <sub>OHZ</sub> |              | 5      | _            | 6   | ns   | 1     |

| Byte deselect to output in high-Z                  | t <sub>BHZ</sub> | —            | 5      | —            | 6   | ns   | 1     |

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 8 of 15

#### Write Cycle

|                                    |                  | R1RW | /0416D       |     |         |      |       |

|------------------------------------|------------------|------|--------------|-----|---------|------|-------|

|                                    |                  | 10ns | 10ns Version |     | Version | _    |       |

| Parameter                          | Symbol           | Min  | Max          | Min | Max     | Unit | Notes |

| Write cycle time                   | t <sub>WC</sub>  | 10   |              | 12  | _       | ns   |       |

| Address valid to end of write      | t <sub>AW</sub>  | 7    | _            | 8   | _       | ns   |       |

| Chip select to end of write        | t <sub>CW</sub>  | 7    | _            | 8   | _       | ns   | 8     |

| Write pulse width                  | t <sub>WP</sub>  | 7    |              | 8   | _       | ns   | 7     |

| Byte select to end of write        | t <sub>BW</sub>  | 7    |              | 8   | _       | ns   |       |

| Address setup time                 | t <sub>AS</sub>  | 0    | _            | 0   | _       | ns   | 5     |

| Write recovery time                | t <sub>WR</sub>  | 0    | _            | 0   | _       | ns   | 6     |

| Data to write time overlap         | t <sub>DW</sub>  | 5    | _            | 6   | _       | ns   |       |

| Data hold from write time          | t <sub>DH</sub>  | 0    | _            | 0   | _       | ns   |       |

| Write disable to output in low-Z   | t <sub>OW</sub>  | 3    | _            | 3   | _       | ns   | 1     |

| Output disable to output in high-Z | t <sub>OHZ</sub> |      | 5            |     | 6       | ns   | 1     |

| Write enable to output in high-Z   | t <sub>WHZ</sub> |      | 5            | —   | 6       | ns   | 1     |

Notes: 1. Transition is measured ±200 mV from steady voltage with output load (B). This parameter is sampled and not 100% tested.

2. If the CS# or LB# or UB# low transition occurs simultaneously with the WE# low transition or after the WE# transition, output remains a high impedance state.

- 3. WE# and/or CS# must be high during address transition time.

- 4. If CS#, OE#, LB# and UB# are low during this period, I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.

- 5.  $t_{AS}$  is measured from the latest address transition to the latest of CS#, WE#, LB# or UB# going low.

- 6.  $t_{WR}$  is measured from the earliest of CS#, WE#, LB# or UB# going high to the first address transition.

- 7. A write occurs during the overlap of a low CS#, a low WE# and a low LB# or a low UB# (t<sub>WP</sub>). A write begins at the latest transition among CS# going low, WE# going low and LB# going low or UB# going low. A write ends at the earliest transition among CS# going high, WE# going high and LB# going high or UB# going high.

- 8.  $t_{CW}$  is measured from the later of CS# going low to the end of write.

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 9 of 15

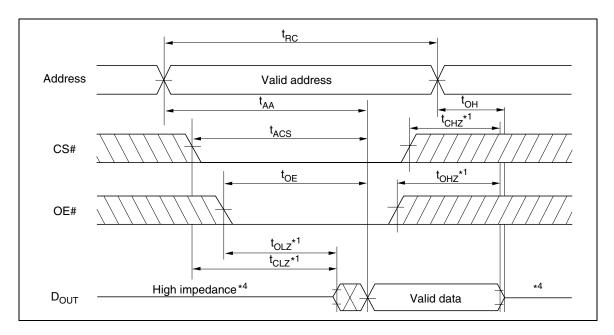

## **Timing Waveforms**

Dec.12.2008, page 10 of 15

Read Timing Waveform (2) (WE# =  $V_{IH}$ , LB# =  $V_{IL}$ , UB# =  $V_{IL}$ )

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 11 of 15

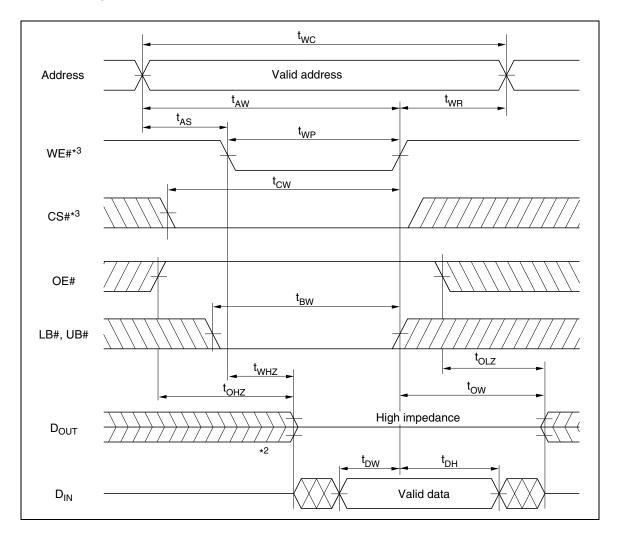

Write Timing Waveform (1) (WE# Controlled)

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 12 of 15

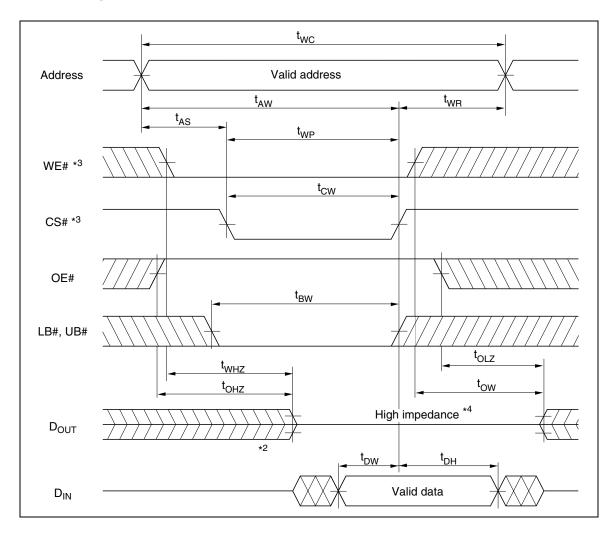

Write Timing Waveform (2) (CS# Controlled)

REJ03C0107-0200 Rev.2.00,

Dec.12.2008, page 13 of 15

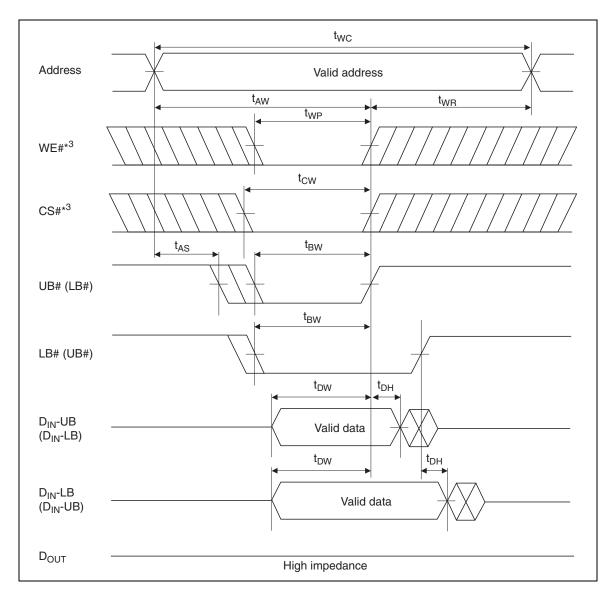

Write Timing Waveform (3) (LB#, UB# Controlled,  $OE# = V_{IH}$ )

Dec.12.2008, page 14 of 15

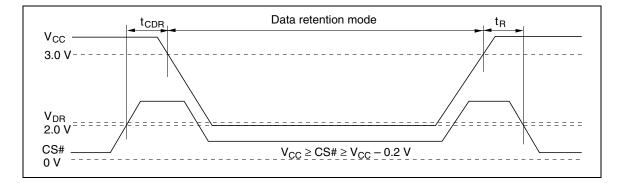

## Low $V_{CC}$ Data Retention Characteristics

#### $(Ta = 0 \text{ to } +70^{\circ}C)$

This characteristics is guaranteed only for L-version and S-version.

| Parameter                            | Symbol            | Min | Max | Unit | Test conditions                                                                                                                                                                                                                                          |

|--------------------------------------|-------------------|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{CC}$ for data retention          | $V_{DR}$          | 2.0 | —   | V    | $ \begin{array}{l} {\sf V}_{CC} \geq CS\# \geq {\sf V}_{CC} - 0.2 \; {\sf V}, \\ (1)  0 \; {\sf V} \leq {\sf V}_{{\sf IN}} \leq 0.2 \; {\sf V} \; {\sf or} \\ (2)  {\sf V}_{CC} \geq {\sf V}_{{\sf IN}} \geq {\sf V}_{CC} - 0.2 \; {\sf V} \end{array} $ |

| Data retention current L-Version     | I <sub>CCDR</sub> | _   | 400 | μΑ   | $V_{CC} = 3 V$                                                                                                                                                                                                                                           |

|                                      |                   |     |     |      | $V_{CC} \ge CS\# \ge V_{CC} - 0.2 \text{ V},$<br>(1) $0 \text{ V} \le V_{IN} \le 0.2 \text{ V or}$                                                                                                                                                       |

| S-Version                            |                   |     | 200 |      | (1) $V \leq V_{IN} \leq 0.2 \ V \ Oldson (2) \ V_{CC} \geq V_{IN} \geq V_{CC} - 0.2 \ V$                                                                                                                                                                 |

| Chip deselect to data retention time | t <sub>CDR</sub>  | 0   | _   | ns   | See retention waveform                                                                                                                                                                                                                                   |

| Operation recovery time              | t <sub>R</sub>    | 5   |     | ms   |                                                                                                                                                                                                                                                          |

### Low $V_{CC}$ Data Retention Timing Waveform

Dec.12.2008, page 15 of 15

# **Revision History**

## **R1RW0416D Series Data Sheet**

| Rev. | Date          | Conte | nts of Modification                                                           |

|------|---------------|-------|-------------------------------------------------------------------------------|

|      |               | Page  | Description                                                                   |

| 0.01 | Sep. 30, 2003 | _     | Initial issue                                                                 |

| 1.00 | Mar.12.2004   | _     | Deletion of Preliminary                                                       |

| 2.00 | Dec.12.2008   | —     | Addition of access grade 10ns version and S-version.                          |

|      |               | P2    | The product lineup :R1RW0416DSB-0PR/DGE-0PR is added.                         |

|      |               | P2    | The product lineup :R1RW0416DSB-2SR/DGE-2SR is added.                         |

|      |               | P7    | Operating power supply current of 10ns cycle version is described to the      |

|      |               |       | DC characteristic.                                                            |

|      |               |       | ISB1 of S-Version is described to the DC characteristic.                      |

|      |               | P8/P9 | The timing standard of 10ns version is described at the read cycle            |

|      |               |       | The timing standard of 10ns version is described at the write cycle           |

|      |               | P15   | ICCDR of S-version is described to the low Vcc data retention characteristic. |

## RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Nice

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for the true. Renesas neither makes document.

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for the true of any information in this document.

This document is provided due to the purpose of any other military use. When exporting the products or the technology described herein, you should follow the applicable export control laws and regulations.

Al information included in this document, such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document, with a the groups of any other military use. When exporting the products or the technology described herein, you should follow the applicable export control laws and regulations.

Particular and the subscenter and the date ware and the product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document.

Renesas has used reasonable care in compiling the information in this document. Dut Renesas assumes no liability whatsoever for any damages incurred as a subscente and the subscenter on y damages incurred as a subscente and the date different information in the date the information on this document.

When using or otherwise relying on the information in the document.

When using or otherwise relying on the information infits document.

When usi

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### **Renesas Technology America, Inc**

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

5962-8855206XA CY6116A-35DMB CY7C128A-45DMB CY7C1461KV33-133AXI CY7C199-45LMB GS8161Z36DD-200I GS88237CB-200I R1QDA7236ABB-20IB0 RMLV0408EGSB-4S2#AA0 IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI 47L16-E/SN IS66WVE4M16EALL-70BLI IS62WV6416DBLL-45BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1381KV33-100BZXI CY7C1373KV33-100AXC CY7C1381KVE33-133AXI CY7C4042KV13-933FCXC 8602501XA 5962-3829425MUA 5962-8855206YA 5962-8866201XA 5962-8866201YA 5962-8866204TA 5962-8866206MA 5962-8866207NA 5962-8866208UA 5962-8872502XA 5962-8959836MZA 5962-8959841MZA 5962-9062007MXA 5962-9161705MXA N08L63W2AB7I 7130LA100PDG GS81284Z36B-250I M38510/28902BVA IS62WV12816ALL-70BLI 5962-8971203XA 5962-8971202ZA