The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

H8S/20103R, H8S/20203R, H8S/20223R, H8S/20323R, H8S/20115R, H8S/20215R, H8S/20235R, H8S/20335R Groups

User's Manual: Hardware

# Renesas 16-Bit Single-Chip Microcomputer H8S Family / H8S/Tiny Series

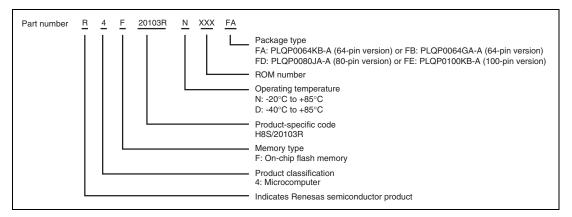

| H8S/20103R | R4F20103R |

|------------|-----------|

| H8S/20203R | R4F20203R |

| H8S/20223R | R4F20223R |

| H8S/20323R | R4F20323R |

| H8S/20115R | R4F20115R |

| H8S/20215R | R4F20215R |

| H8S/20235R | R4F20235R |

| H8S/20335R | R4F20335R |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of

third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No

license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of

Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

### 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for the H8S/20103R, H8S/20203R, H8S/20223R, H8S/20323R, H8S/20115R, H8S/20215R, H8S/20235R, and H8S/20335R Groups. Before using any of the documents, please visit our web site to verify that you have the most up-to-date available version of the document.

| Document Type                 | Contents                                                                                                                                                                   | Document Title                                                                                                                               | Document No.          |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Data Sheet                    | Overview of hardware and electrical characteristics                                                                                                                        | _                                                                                                                                            | _                     |

| User's manual for<br>Hardware | Hardware specifications (pin<br>assignments, memory maps,<br>peripheral specifications, electrical<br>characteristics, and timing charts) and<br>descriptions of operation | H8S/20103R, H8S/20203R,<br>H8S/20223R, H8S/20323R,<br>H8S/20115R, H8S/20215R,<br>H8S/20235R, H8S/20335R<br>Groups User's Manual:<br>Hardware | This User's<br>manual |

| User's manual for<br>Software | Detailed descriptions of the CPU and instruction set                                                                                                                       | H8S/2600 Series,<br>H8S/2000 Series<br>Software Manual                                                                                       | REJ09B0139            |

| Application Note              | Examples of applications and sample programs                                                                                                                               | The latest versions are available web site.                                                                                                  | able from our         |

| Renesas Technical<br>Update   | Preliminary report on the specifications of a product, document, etc.                                                                                                      |                                                                                                                                              |                       |

# 2. Description of Numbers and Symbols

Aspects of the notations for register names, bit names, numbers, and symbolic names in this manual are explained below.

#### (1) Overall notation

In descriptions involving the names of bits and bit fields within this manual, the modules and registers to which the bits belong may be clarified by giving the names in the forms "module name". "register name". "bit name" or "register name". "bit name".

#### (2) Register notation

The style "register name"\_"instance number" is used in cases where there is more than one instance of the same function or similar functions.

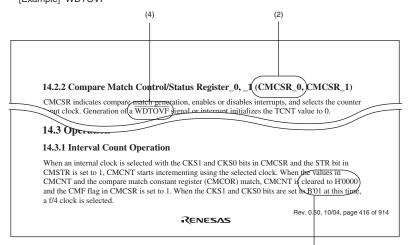

[Example] CMCSR\_0: Indicates the CMCSR register for the compare-match timer of channel 0.

#### (3) Number notation

Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary), hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn. [Examples] Binary:

B'11 or 11

Hexadecimal: H'EFA0 or 0xEFA0

Decimal: 1234

#### (4) Notation for active-low

An overbar on the name indicates that a signal or pin is active-low. [Example]  $\overline{\text{WDTOVF}}$

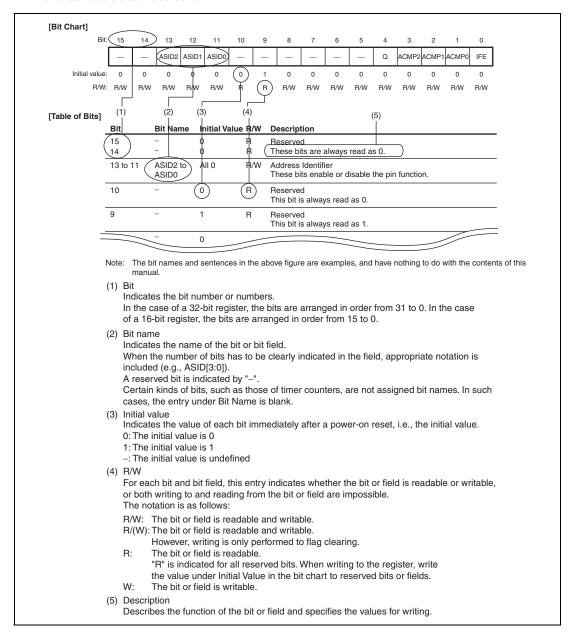

Note: The bit names and sentences in the above figure are examples and have nothing to do with the contents of this manual.

(3)

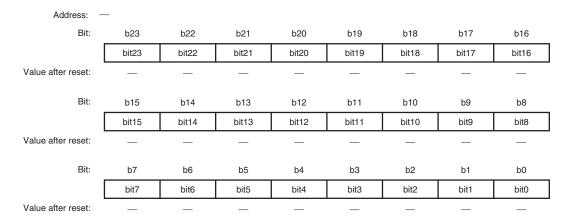

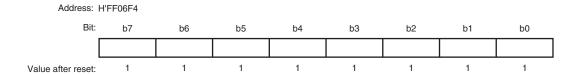

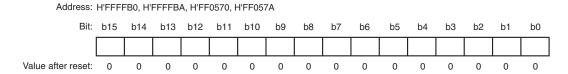

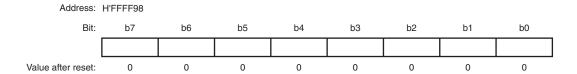

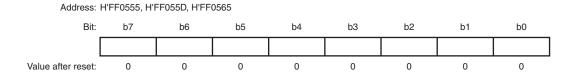

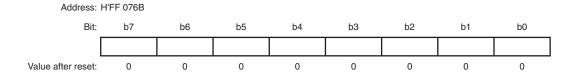

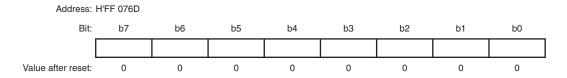

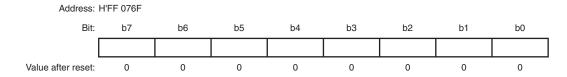

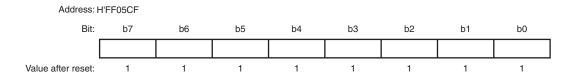

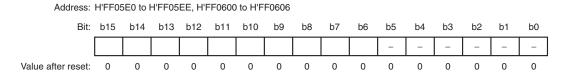

## 3. Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

# 4. Description of Abbreviations

The abbreviations used in this manual are listed below.

• Abbreviations specific to this product

| Abbreviation | Description                           |

|--------------|---------------------------------------|

| BSC          | Bus controller                        |

| CPG          | Clock pulse generator                 |

| INT          | Interrupt controller                  |

| SCI3         | Serial communications interface 3     |

| PMC          | Peripheral I/O mapping controller     |

| WDT          | Watchdog timer                        |

| DTC          | Data transfer controller              |

| ELC          | Event link controller                 |

| IIC2         | Inter IC bus interface 2              |

| SSU          | Synchronous serial communication unit |

| LVD          | Low-voltage detection circuits        |

# • Abbreviations other than those listed above

| Abbreviation | Description                                 |

|--------------|---------------------------------------------|

| Bps          | Bits per second                             |

| CRC          | Cyclic redundancy check                     |

| DMA          | Direct memory access                        |

| Hi-Z         | High impedance                              |

| I/O          | Input/output                                |

| IrDA         | Infrared Data Association                   |

| LSB          | Least significant bit                       |

| MSB          | Most significant bit                        |

| NC           | No connection                               |

| PLL          | Phase-locked loop                           |

| PWM          | Pulse width modulation                      |

| SFR          | Special function register                   |

| UART         | Universal asynchronous receiver/transmitter |

| VCO          | Voltage-controlled oscillator               |

All trademarks and registered trademarks are the property of their respective owners.

Page viii of xxviii

# Contents

| Sect | tion 1  | Overview                                                              | 1  |

|------|---------|-----------------------------------------------------------------------|----|

| 1.1  | Featur  | es                                                                    | 1  |

|      | 1.1.1   | Applications                                                          | 1  |

|      | 1.1.2   | Overview of Functions                                                 | 2  |

| 1.2  | List of | f Products                                                            | 7  |

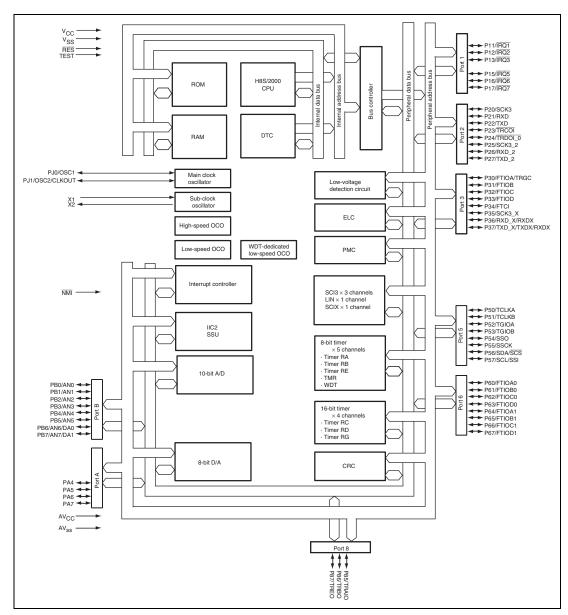

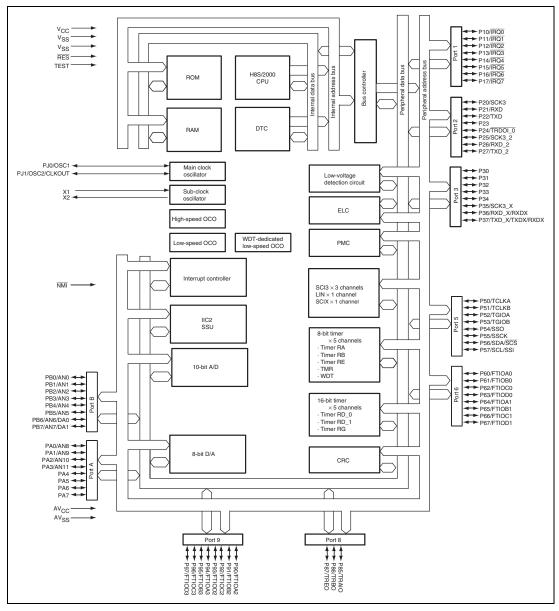

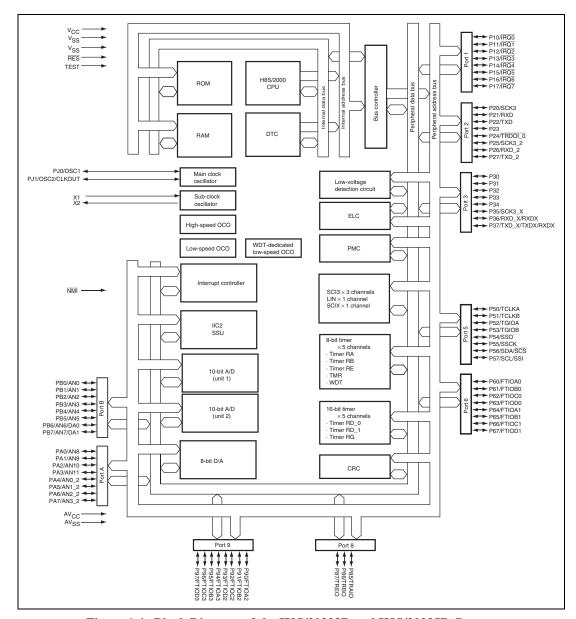

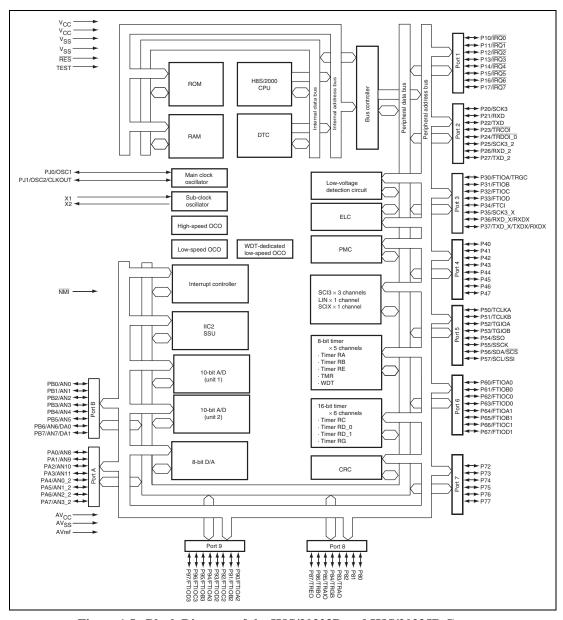

| 1.3  | Block   | Diagram                                                               | 11 |

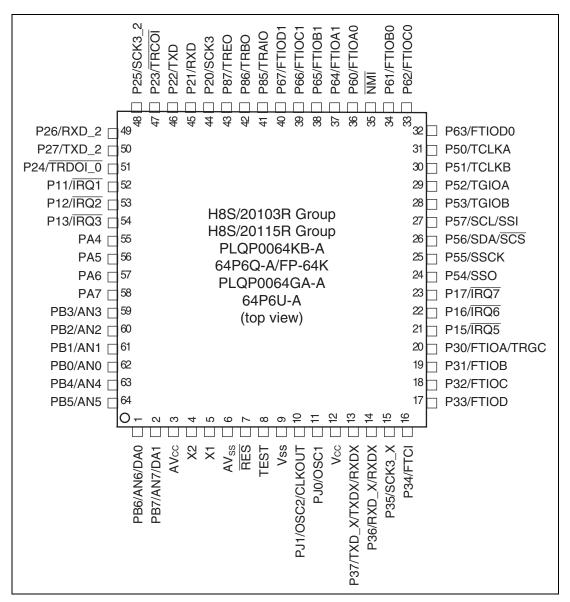

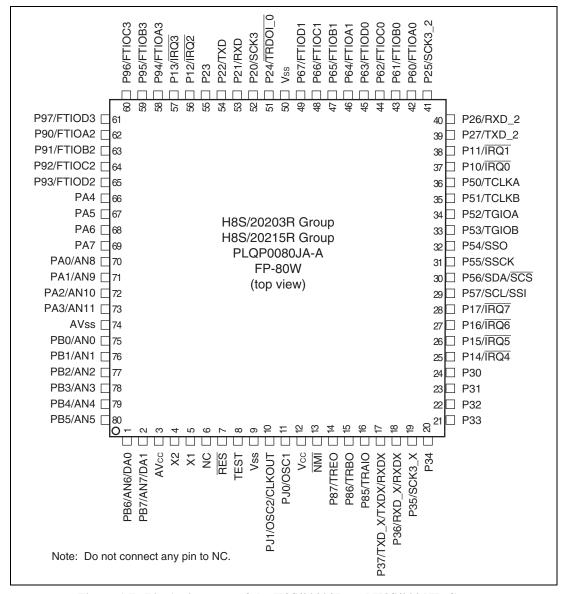

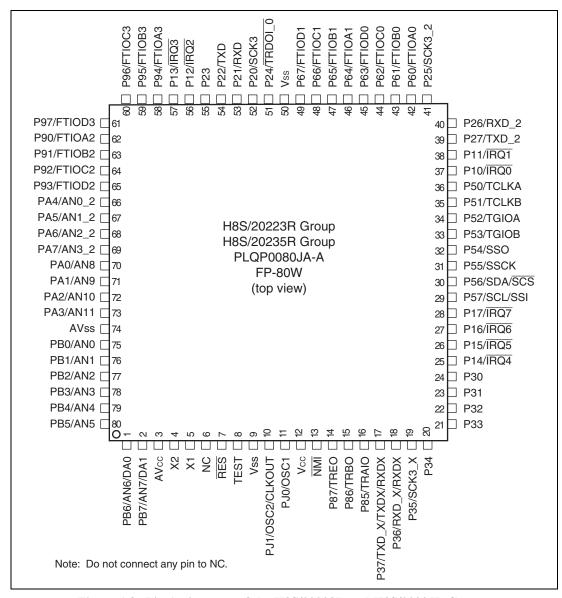

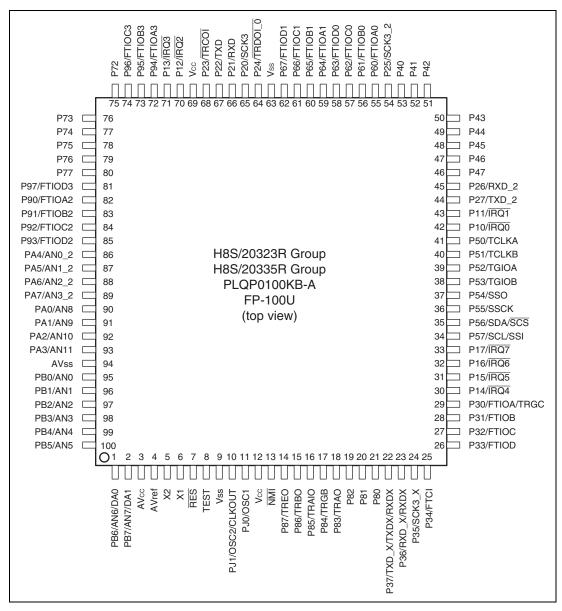

| 1.4  | Pin As  | ssignments                                                            | 15 |

|      | 1.4.1   | Pin Functions                                                         | 19 |

| Sec  | tion 2  | CPU                                                                   | 29 |

| 2.1  | Featur  | es                                                                    | 29 |

|      | 2.1.1   | Differences between H8S/2600 CPU and H8S/2000 CPU                     | 30 |

|      | 2.1.2   | Differences from H8/300 CPU                                           | 31 |

|      | 2.1.3   | Differences from H8/300H CPU                                          | 31 |

| 2.2  | CPU (   | Operating Modes                                                       | 32 |

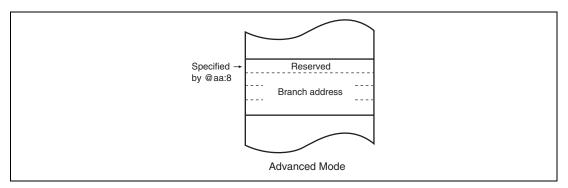

|      | 2.2.1   | Advanced Mode                                                         | 32 |

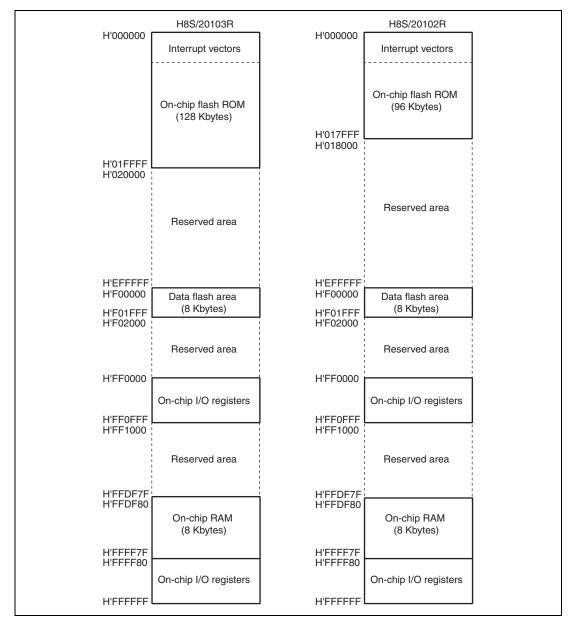

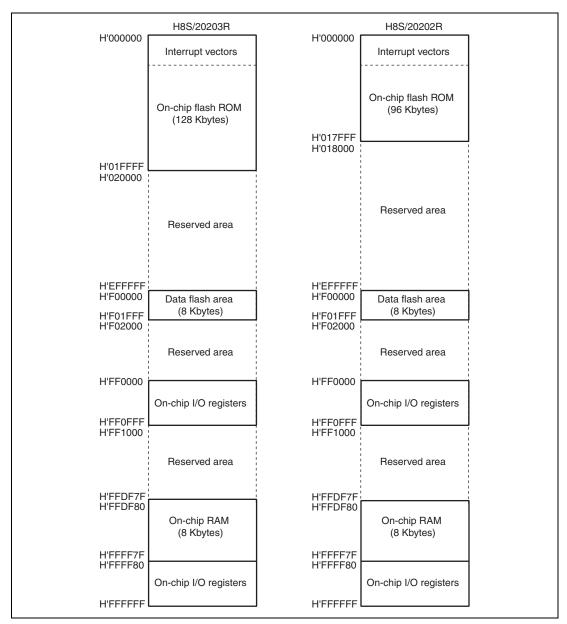

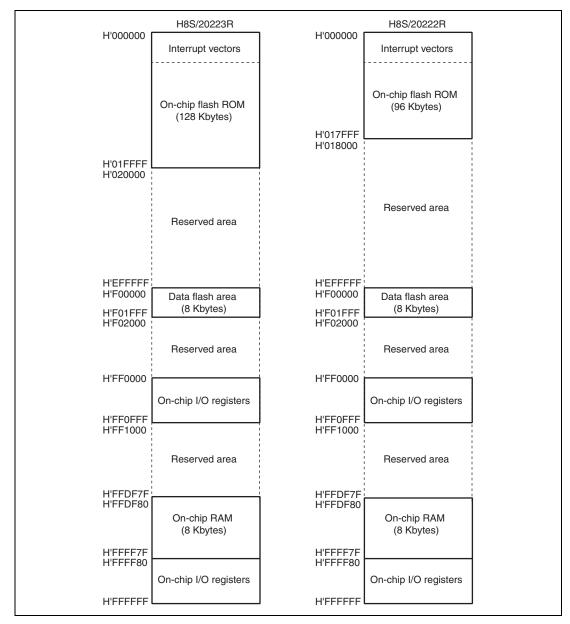

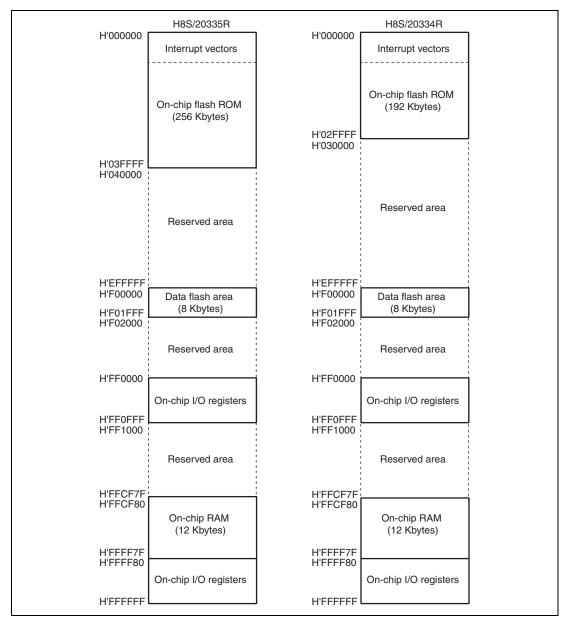

| 2.3  | Addre   | ss Space                                                              | 34 |

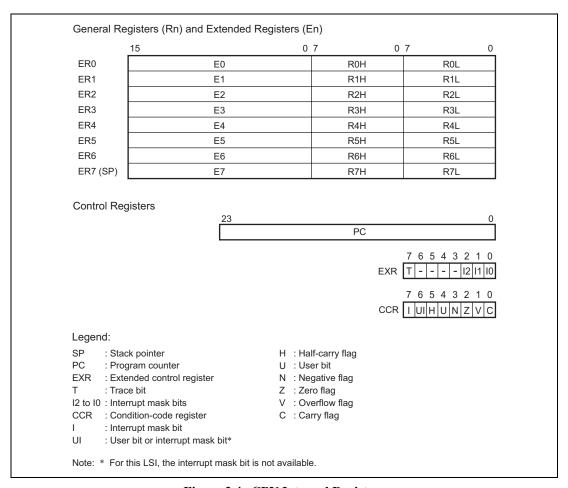

| 2.4  | Regist  | er Configuration                                                      | 43 |

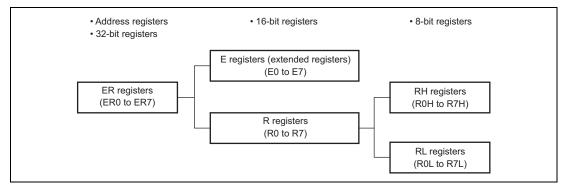

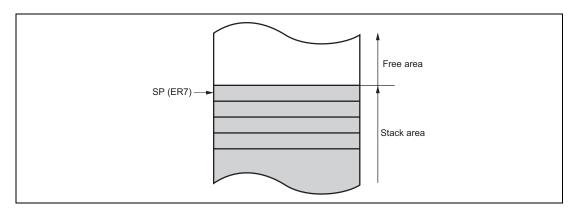

|      | 2.4.1   | General Registers                                                     | 44 |

|      | 2.4.2   | Program Counter (PC)                                                  | 45 |

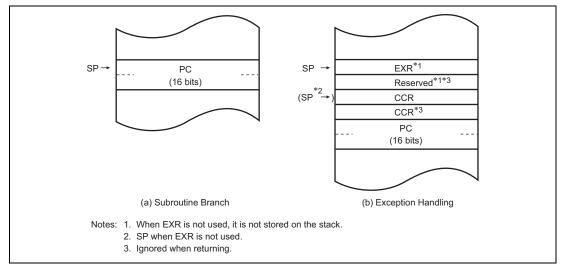

|      | 2.4.3   | Extended Control Register (EXR)                                       | 45 |

|      | 2.4.4   | Condition-Code Register (CCR)                                         | 46 |

|      | 2.4.5   | Initial Register Values                                               | 48 |

| 2.5  | Data I  | Formats                                                               | 49 |

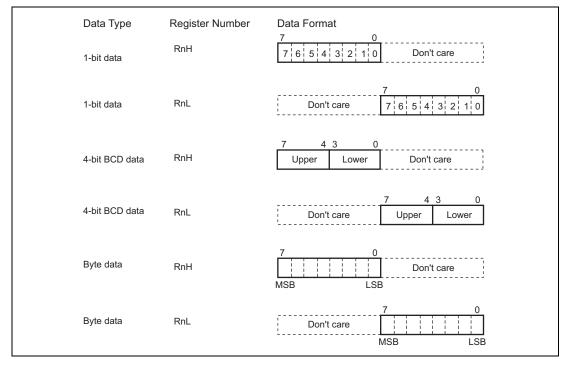

|      | 2.5.1   | General Register Data Formats                                         | 49 |

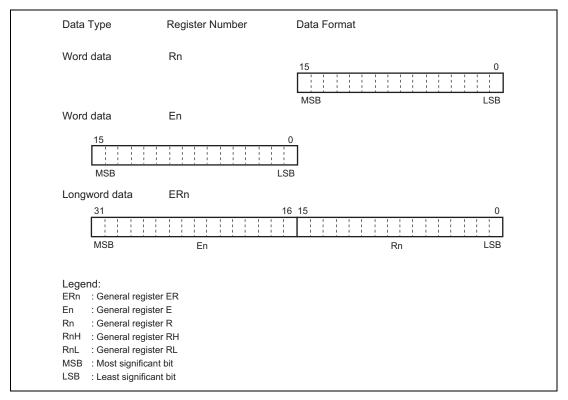

|      | 2.5.2   | Memory Data Formats                                                   | 51 |

| 2.6  | Instru  | ction Set                                                             | 52 |

|      | 2.6.1   | Table of Instructions Classified by Function                          | 53 |

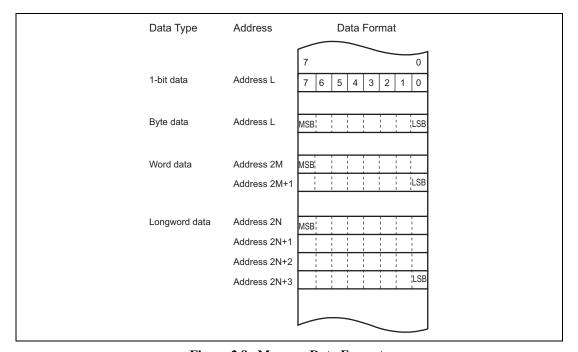

|      | 2.6.2   | Basic Instruction Formats                                             | 63 |

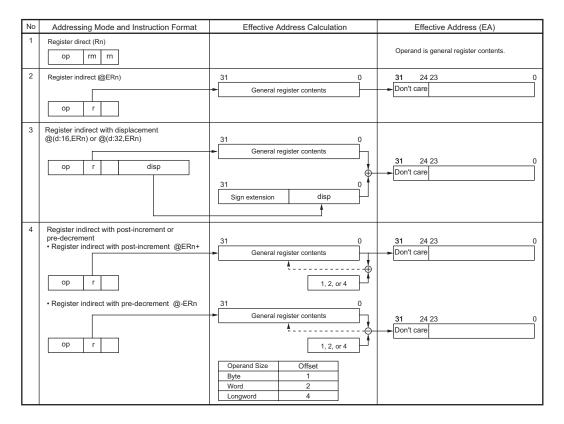

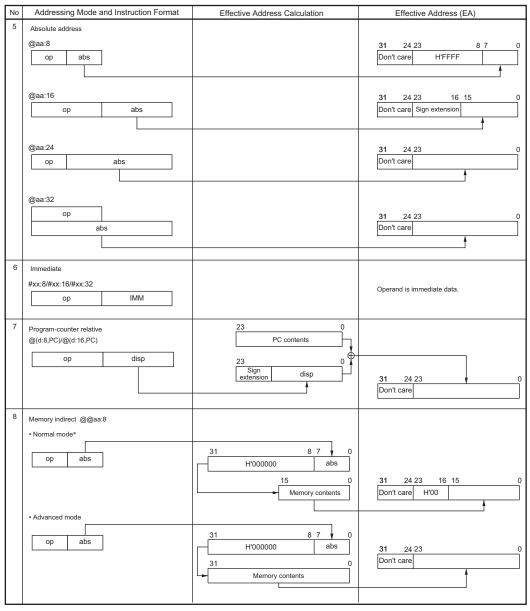

| 2.7  | Addre   | ssing Modes and Effective Address Calculation                         | 65 |

|      | 2.7.1   | Register Direct—Rn                                                    | 65 |

|      | 2.7.2   | Register Indirect—@ERn                                                | 65 |

|      | 2.7.3   | Register Indirect with Displacement—@(d:16, ERn) or @(d:32, ERn)      | 66 |

|      | 2.7.4   | Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn | 66 |

|      | 2.7.5   | Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32                     | 66 |

|      | 276     | Immediate_#yy:8 #yy:16 or #yy:32                                      | 67 |

|     | 2.7.7 Program-Counter Relat     | ive—@(d:8, PC) or @(d:16, PC)   | 67  |

|-----|---------------------------------|---------------------------------|-----|

|     | 2.7.8 Memory Indirect—@@        | aa:8                            | 68  |

|     | 2.7.9 Effective Address Calcu   | ulation                         | 69  |

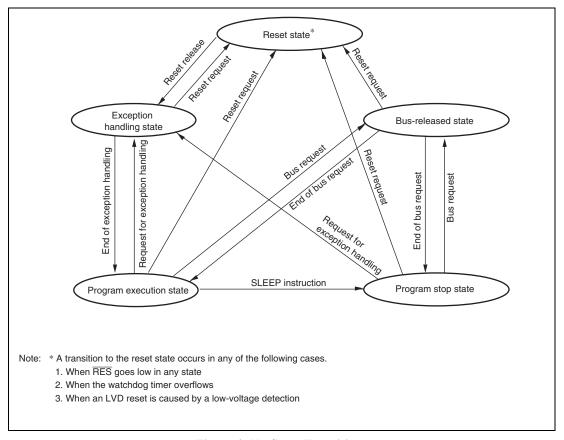

| 2.8 | Processing States               |                                 | 71  |

| 2.9 | Usage Notes                     |                                 | 73  |

|     | 2.9.1 TAS Instruction           |                                 | 73  |

|     | 2.9.2 STM and LDM Instruct      | tions                           | 73  |

|     | 2.9.3 Note on Bit Manipulation  | on Instructions                 | 73  |

|     | 2.9.4 EEPMOV Instruction        |                                 | 74  |

| Sec |                                 |                                 |     |

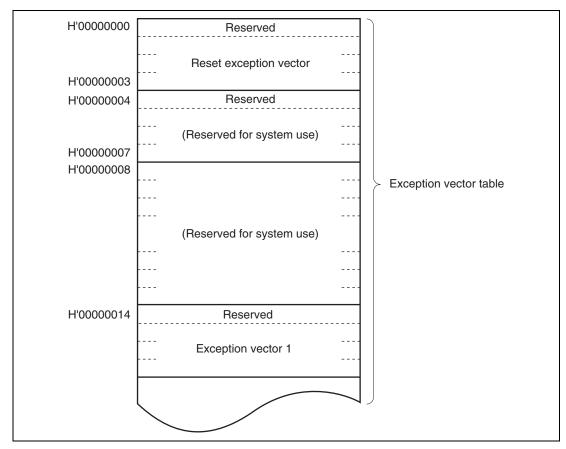

| 3.1 | Exception Handling Types and    | Priority                        | 75  |

| 3.2 | Exception Handling Sources and  | d Vector Table                  | 75  |

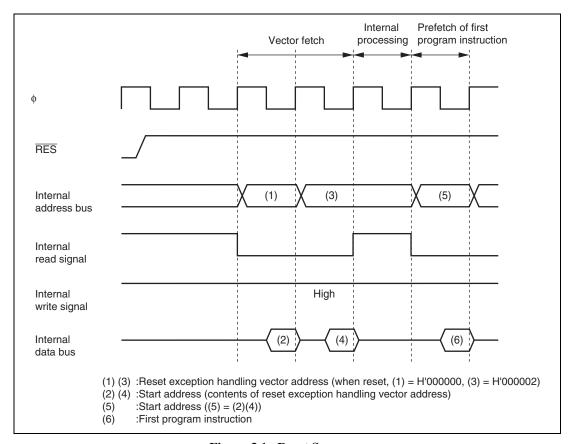

| 3.3 | Reset                           |                                 | 76  |

|     | 3.3.1 Reset Sources             |                                 | 76  |

|     | 3.3.2 Reset Exception Handli    | ng                              | 79  |

|     | 3.3.3 Interrupts immediately    | after Reset                     | 80  |

|     | 3.3.4 On-Chip Peripheral Fur    | nctions after Reset Release     | 80  |

| 3.4 | Trace Exception Handling        |                                 | 81  |

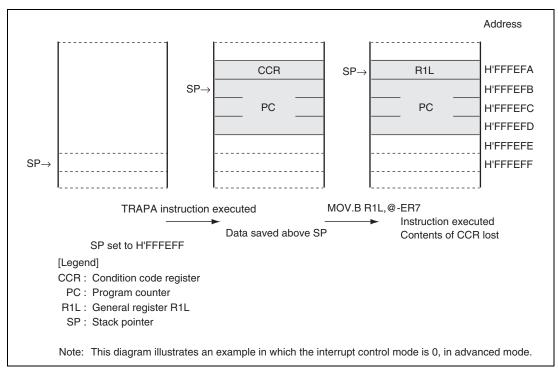

| 3.5 | Interrupt Exception Handling    |                                 | 82  |

| 3.6 | Trap Instruction Exception Han  | dling                           | 82  |

| 3.7 | •                               | ndling                          |     |

| 3.8 | Usage Note                      |                                 | 84  |

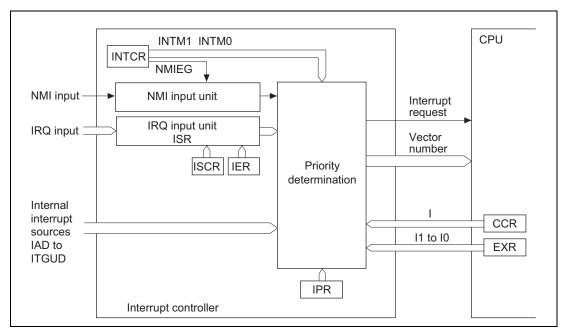

| Sec | tion 4 Interrupt Controller     |                                 | 85  |

| 4.1 | Features                        |                                 | 85  |

| 4.2 |                                 |                                 |     |

|     |                                 | ter (INTCR)                     |     |

|     | , ,                             | ters A to J (IPRA to IPRJ)      |     |

|     |                                 | ER)                             |     |

|     |                                 | ister H and L (ISCRH and ISCRL) |     |

|     |                                 | R)                              |     |

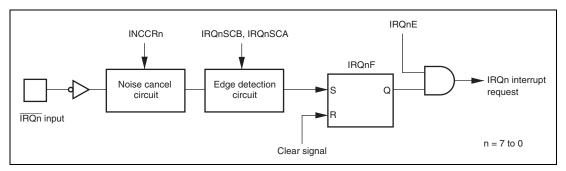

|     | -                               | ontrol Register (INCCR)         |     |

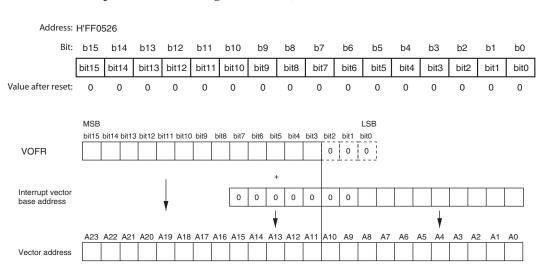

|     |                                 | Register (VOFR)                 |     |

|     | 1                               | ontrol Status Register (ELCSR)  |     |

| 4.3 |                                 |                                 |     |

|     | <u>*</u>                        | es                              |     |

|     | -                               |                                 |     |

| 4.4 | Interrupt Exception Handling V  | ector Table                     | 102 |

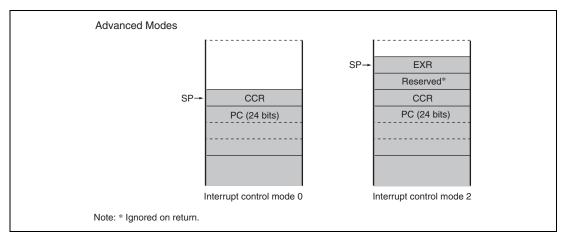

| 45  | Interrupt Control Modes and Int | terrunt Operation               | 110 |

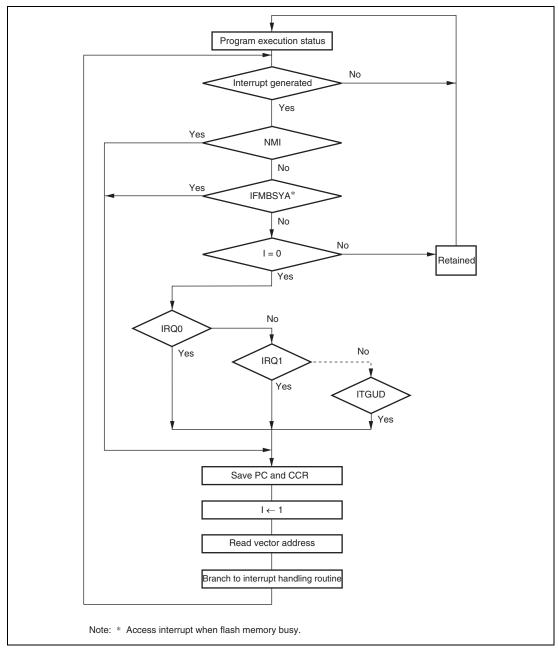

|     | 4.5.1            | Interrupt Control Mode 0                                                       | 111 |

|-----|------------------|--------------------------------------------------------------------------------|-----|

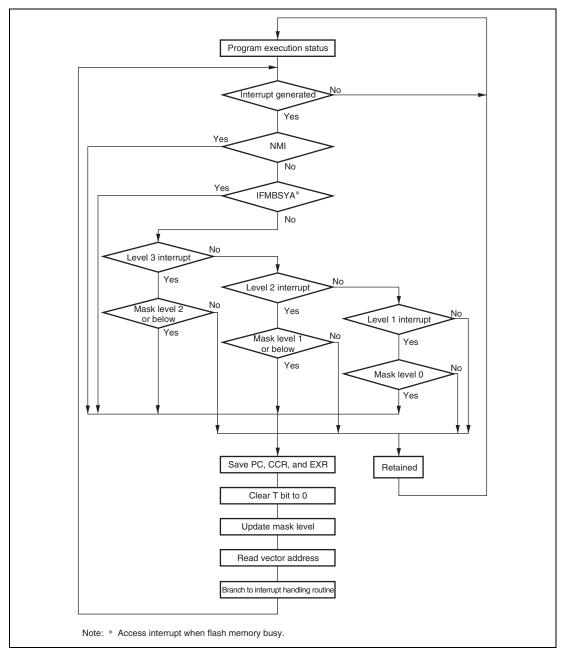

|     | 4.5.2            | Interrupt Control Mode 2                                                       | 113 |

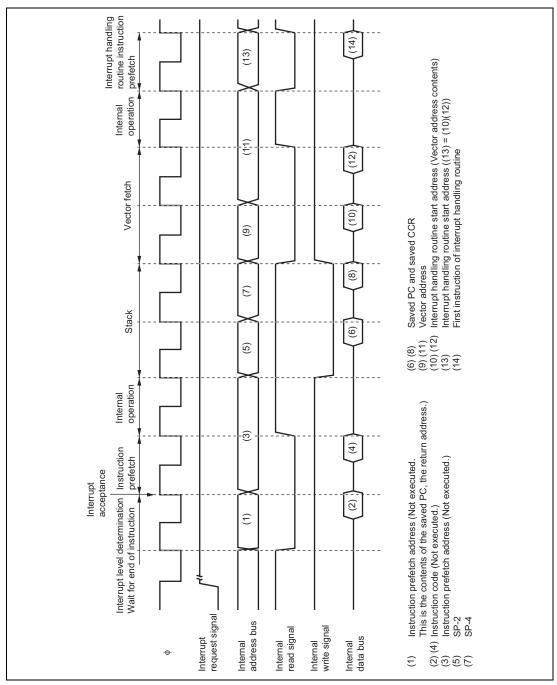

|     | 4.5.3            | Interrupt Exception Handling Sequence                                          | 115 |

|     | 4.5.4            | Interrupt Response Time                                                        | 117 |

|     | 4.5.5            | DTC Activation by Interrupt                                                    | 117 |

| 4.6 | Usage            | Notes                                                                          | 118 |

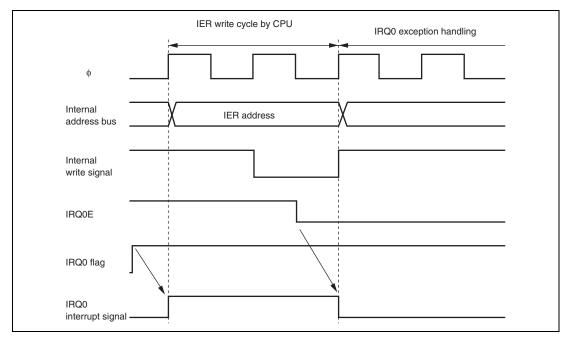

|     | 4.6.1            | Conflict between Interrupt Generation and Disabling                            | 118 |

|     | 4.6.2            | Instructions that Disable Interrupts                                           | 119 |

|     | 4.6.3            | Time when Interrupts are Disabled                                              | 119 |

|     | 4.6.4            | Interrupts during Execution of EEPMOV Instruction                              | 119 |

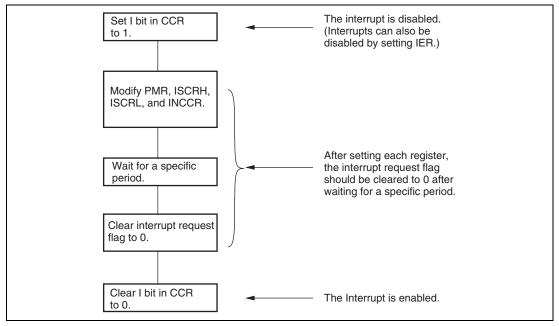

|     | 4.6.5            | Changing PMR, ISCRH, ISCRL and INCCR                                           | 120 |

|     | 4.6.6            | IRQ Status Register (ISR)                                                      | 120 |

|     | 4.6.7            | NMI Pin                                                                        | 121 |

| C4  | : /              | Clark Dalas Cananatan                                                          | 100 |

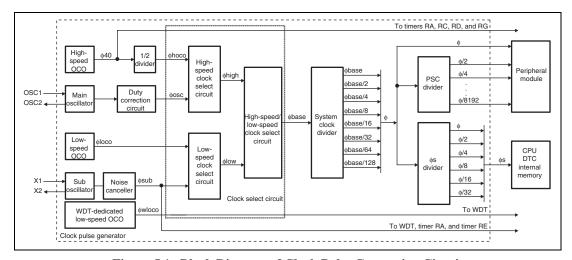

|     |                  | Clock Pulse Generator                                                          |     |

| 5.1 |                  | ew                                                                             |     |

| 5.2 | _                | er Descriptions                                                                |     |

|     | 5.2.1            | Backup Control Register (BAKCR)                                                |     |

|     | 5.2.2            | System Clock Control Register (SYSCCR)                                         |     |

|     | 5.2.3<br>5.2.4   | Power-Down Control Register 1 (LPCR1)                                          |     |

|     |                  | Power-Down Control Register 2 (LPCR2)                                          |     |

|     | 5.2.5            | Power-Down Control Register 3 (LPCR3)                                          |     |

|     | 5.2.6            | OSC Oscillation Settling Control Status Register (OSCCSR)                      |     |

|     | 5.2.7            | High-Speed OCO Control Register (HOCR)                                         |     |

|     | 5.2.8            | High-Speed OCO Trimming Data Protect Register (HOTRMDPR)                       |     |

|     | 5.2.9            | High-Speed OCO Trimming Data Register 1 (HOTRMDR1)                             |     |

|     | 5.2.10           | High-Speed OCO Trimming Data Register 2 (HOTRMDR2)                             |     |

|     | 5.2.11<br>5.2.12 | High-Speed OCO Trimming Data Register 4 (HOTRMDR4)                             |     |

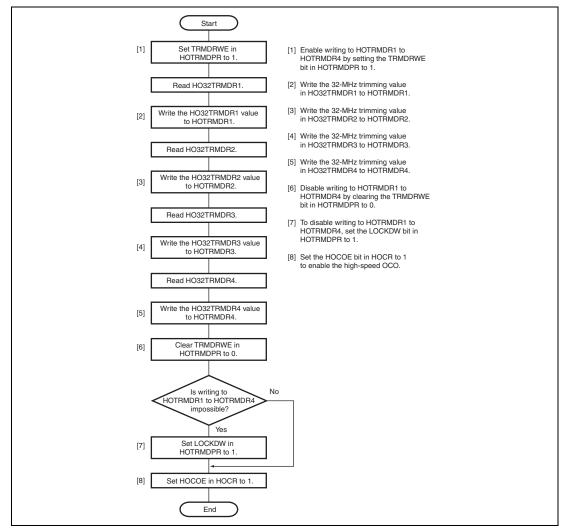

|     |                  | 32-MHz High-Speed OCO Trimming Data Register 1 (HO32TRMDR1)                    |     |

|     | 5.2.13<br>5.2.14 | 32-MHz High-Speed OCO Trimming Data Register 1 (HO32TRMDR1)                    |     |

|     | 5.2.14           | 32-MHz High-Speed OCO Trimming Data Register 2 (HO32TRMDR2)                    |     |

|     | 5.2.16           |                                                                                |     |

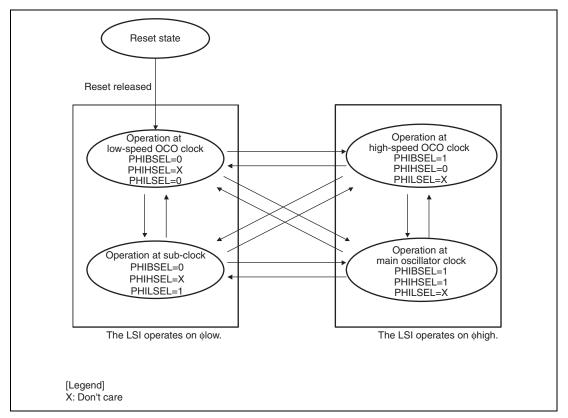

| 5 3 |                  | ion of Selection of System Reference Clock                                     |     |

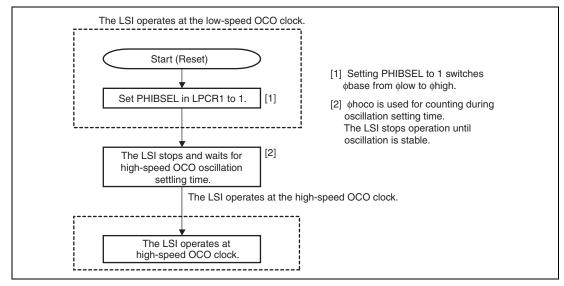

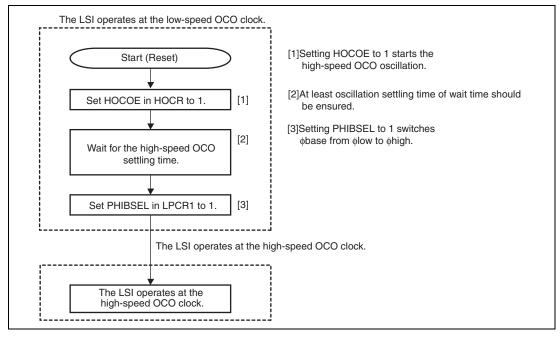

| 5.3 | 5.3.1            | Switching System Reference Clock to $\phi$ hoco                                |     |

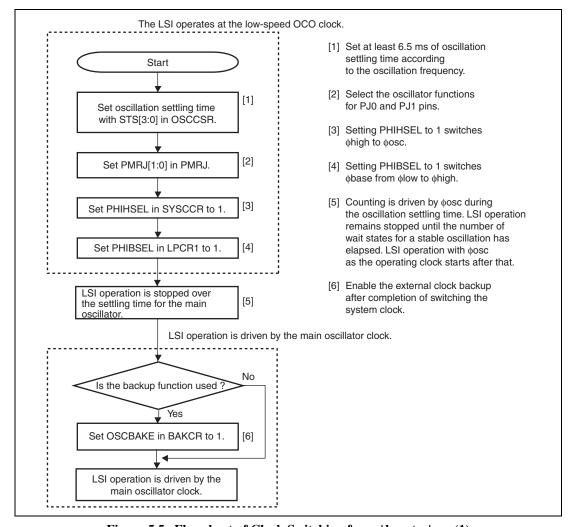

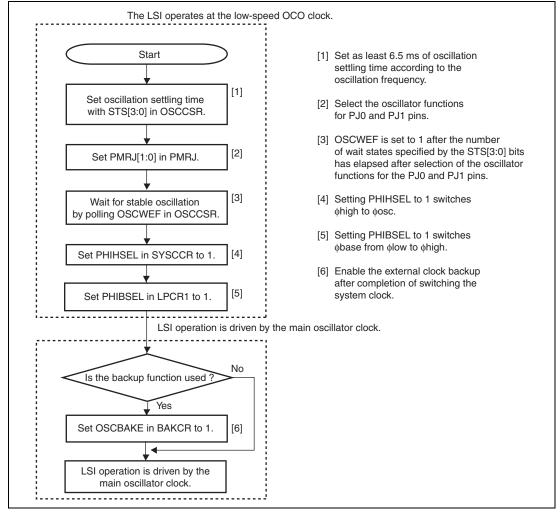

|     |                  | · · · · · · · · · · · · · · · · · · ·                                          |     |

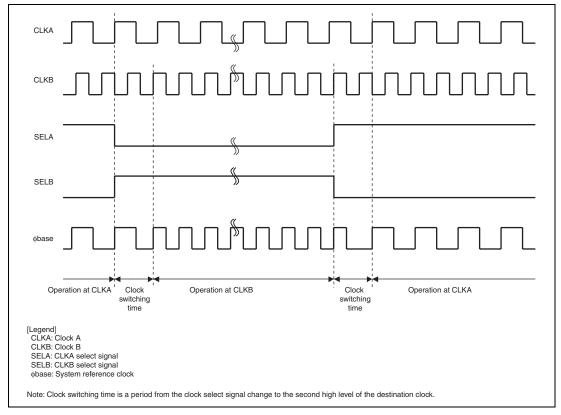

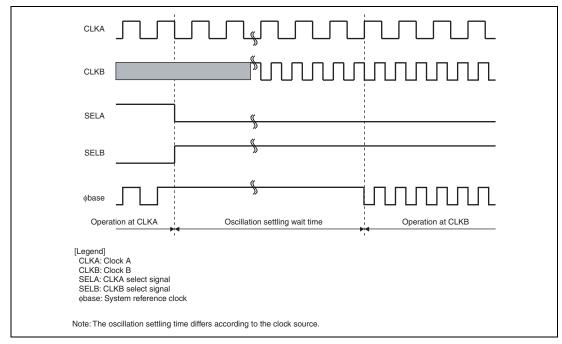

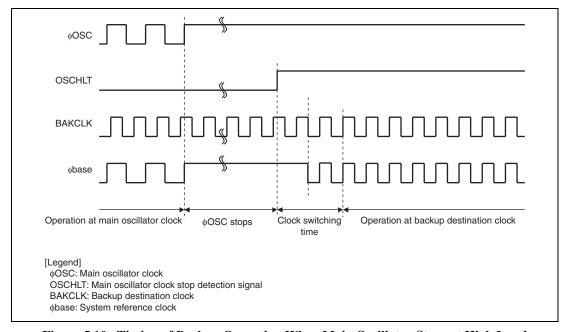

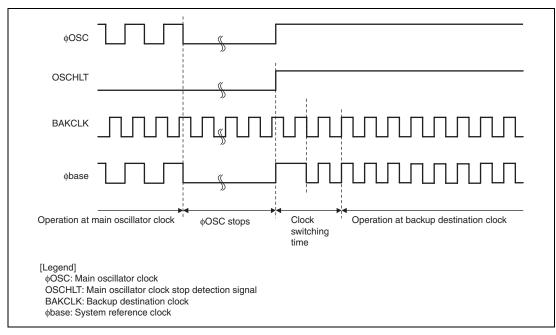

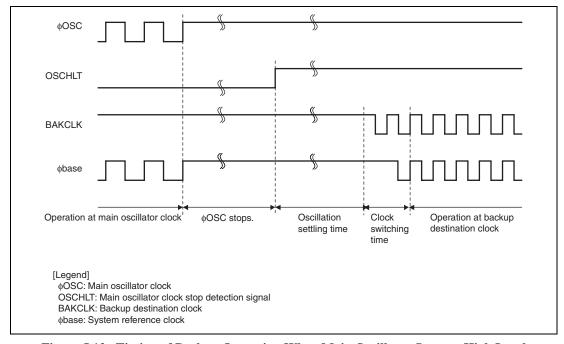

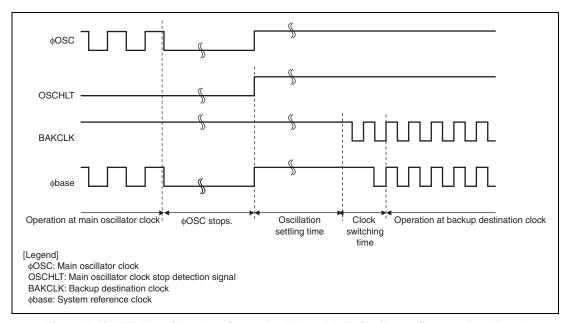

|     | 5.3.2<br>5.3.3   | Switching System Reference Clock to \( \phi \text{osc} \)  Clock Change Timing |     |

|     |                  | e e                                                                            |     |

| 5 1 | 5.3.4            | Backup Operation                                                               |     |

| 5.4 | _                | peed On-Chip Oscillator                                                        |     |

|     | ) 4 I            | FIOCEOMES TOF SWITCHING TO SZIVITIZ                                            | 104 |

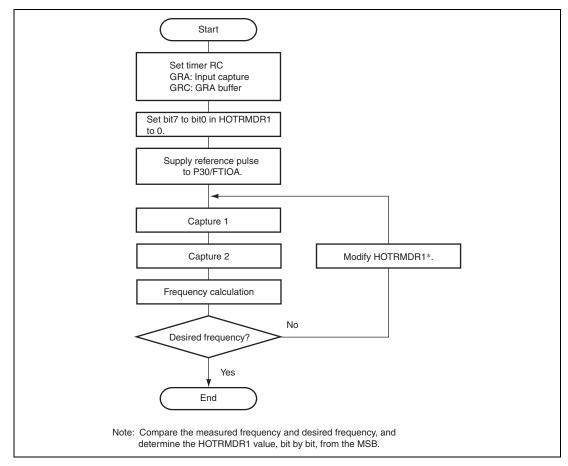

|      | 5.4.2 Trimming of High-Speed OCO                                     | 165 |

|------|----------------------------------------------------------------------|-----|

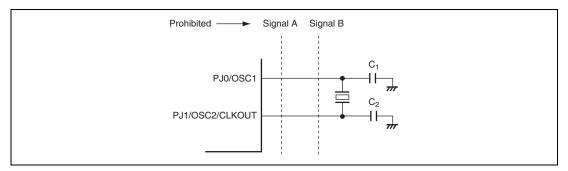

| 5.5  | Main Oscillator                                                      | 167 |

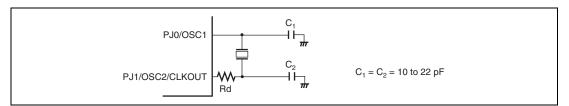

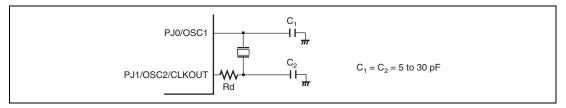

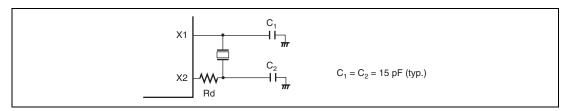

|      | 5.5.1 Connecting Crystal Resonator                                   | 167 |

|      | 5.5.2 Connecting Ceramic Resonator                                   | 168 |

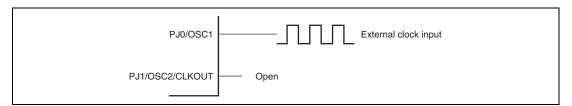

|      | 5.5.3 External Clock Input Method                                    | 168 |

| 5.6  | Sub Oscillator                                                       | 169 |

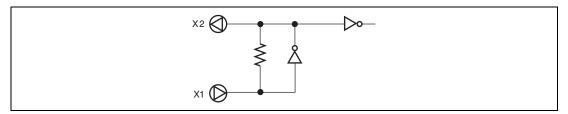

|      | 5.6.1 Connecting 32.768-kHz Crystal Resonator                        | 169 |

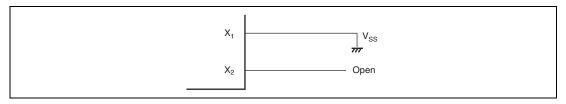

|      | 5.6.2 Pin Connection when not Using Subclock                         | 169 |

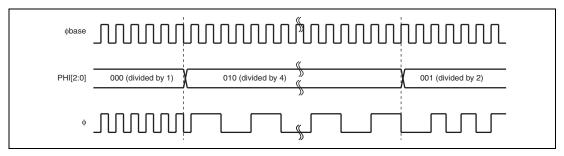

| 5.7  | Prescaler                                                            | 170 |

| 5.8  | Usage Notes                                                          | 171 |

|      | 5.8.1 Note on Resonators                                             | 171 |

|      | 5.8.2 Notes on Board Design                                          | 171 |

| Sect | tion 6 Power-Down Modes                                              | 173 |

| 6.1  | Register Descriptions                                                |     |

|      | 6.1.1 Power-Down Control Registers 1, 2, and 3 (LPCR1, LPCR2, LPCR3) |     |

|      | 6.1.2 Module Standby Control Register 1 (MSTCR1)                     |     |

|      | 6.1.3 Module Standby Control Register 2 (MSTCR2)                     |     |

|      | 6.1.4 Module Standby Control Register 3 (MSTCR3)                     |     |

|      | 6.1.5 Module Standby Control Register 4 (MSTCR4)                     |     |

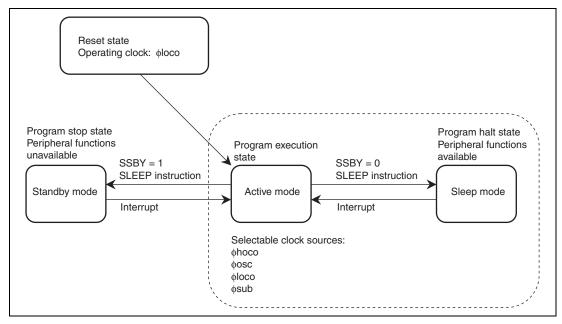

| 6.2  | Mode Transitions and States of LSI                                   |     |

|      | 6.2.1 Active Mode                                                    | 182 |

|      | 6.2.2 Sleep Mode                                                     | 182 |

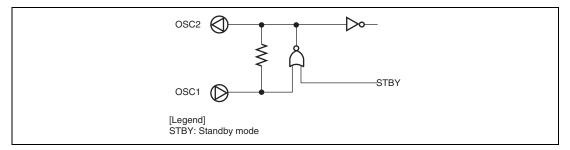

|      | 6.2.3 Standby Mode                                                   |     |

| 6.3  | Bus Master Clock Division Function                                   | 184 |

|      | 6.3.1 Reset States                                                   | 184 |

| 6.4  | Module Standby Function                                              |     |

| 6.5  | PSC Divider Stop Function                                            |     |

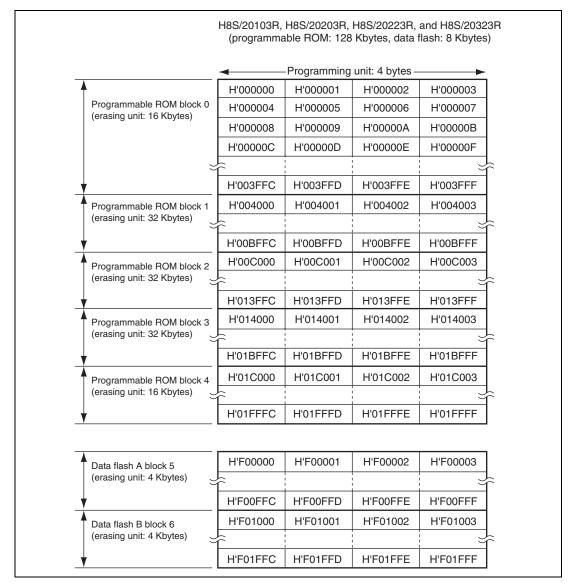

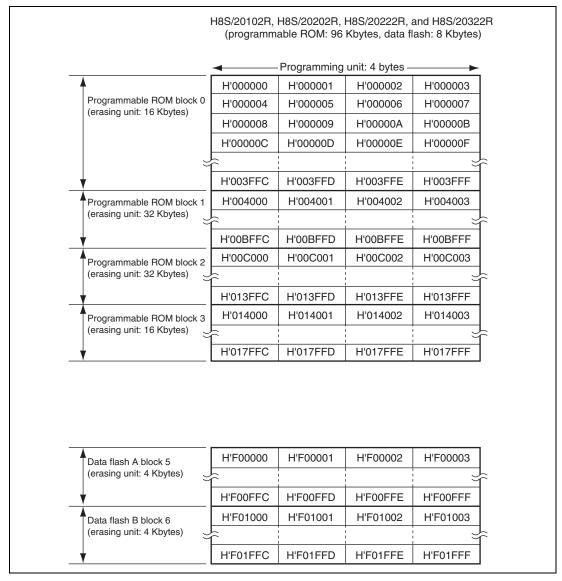

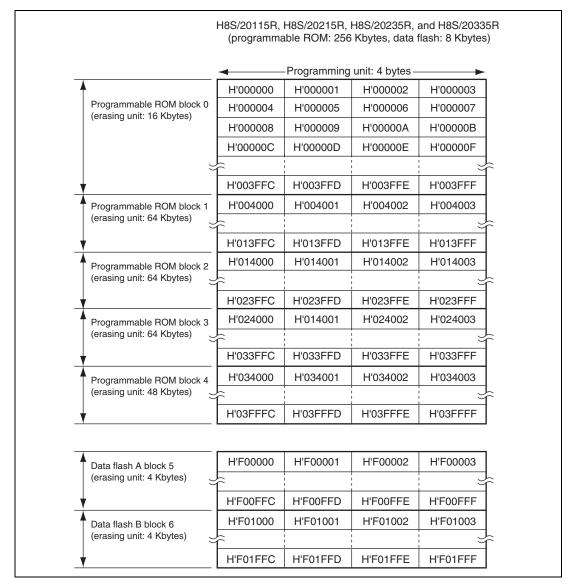

| Sect | tion 7 ROM                                                           | 185 |

| 7.1  | Overview                                                             |     |

| 7.2  | Block Configuration                                                  | 186 |

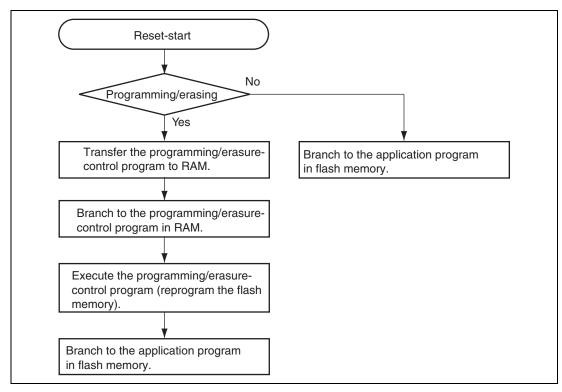

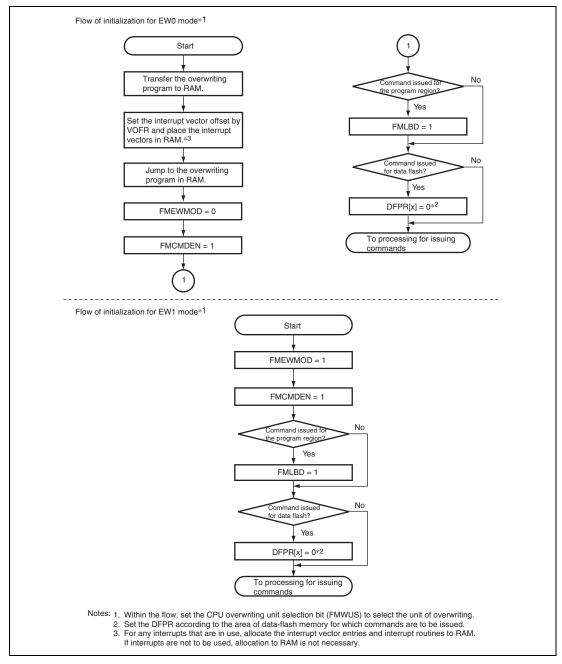

| 7.3  | CPU Reprogramming Mode                                               |     |

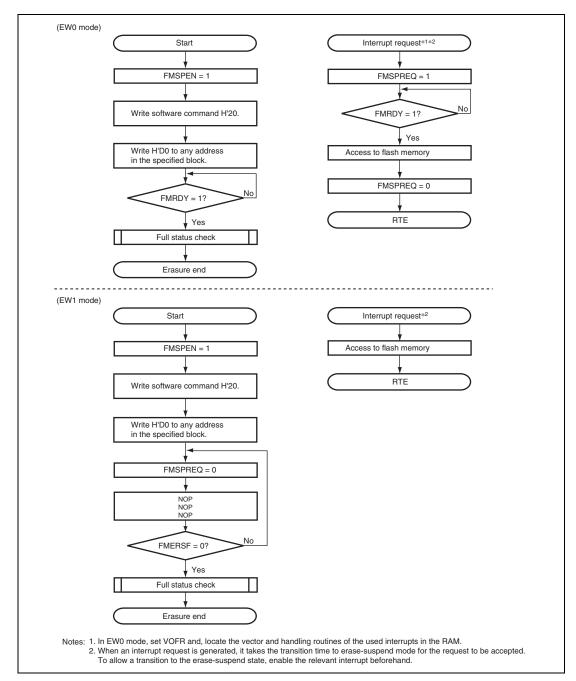

|      | 7.3.1 EW0 Mode                                                       |     |

|      | 7.3.2 EW1 Mode                                                       | 193 |

| 7.4  | Register Descriptions                                                |     |

|      | 7.4.1 Flash Memory Control Register 1 (FLMCR1)                       |     |

|      | 7.4.2 Flash Memory Control Register 2 (FLMCR2)                       |     |

|      | 7.4.3 Flash Memory Data Flash Protect Register (DFPR)                |     |

|      | 7.4.4 Flash Memory Status Register (FI MSTR)                         |     |

| 7.5  | On-Bo  | oard Programming                                                       | 202 |

|------|--------|------------------------------------------------------------------------|-----|

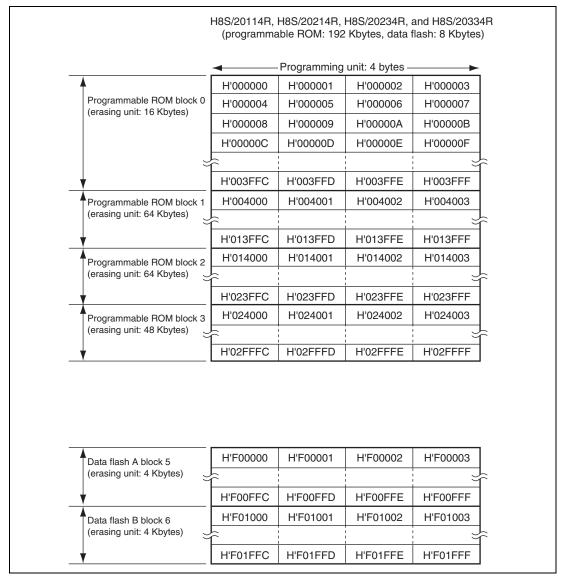

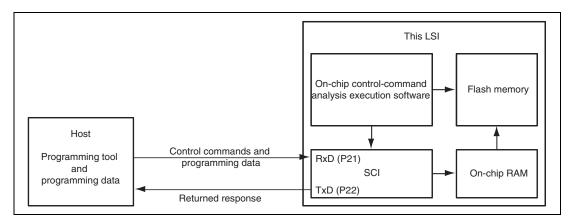

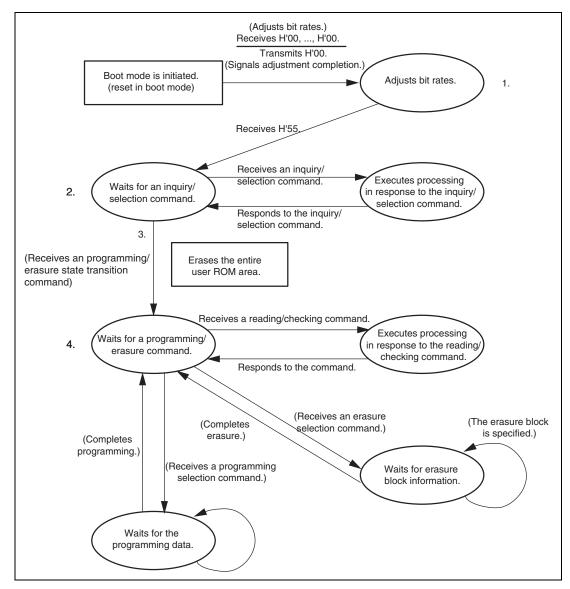

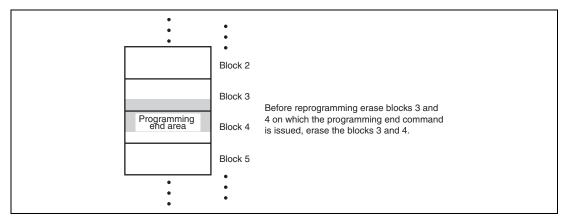

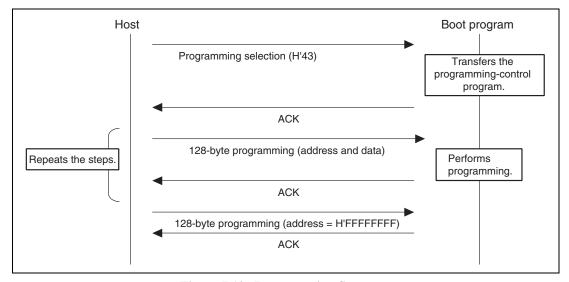

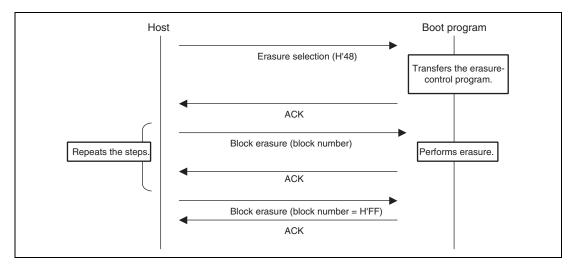

|      | 7.5.1  | Boot Mode                                                              | 202 |

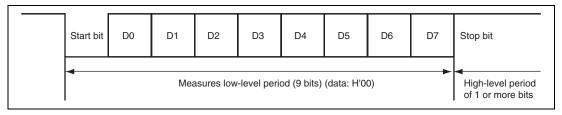

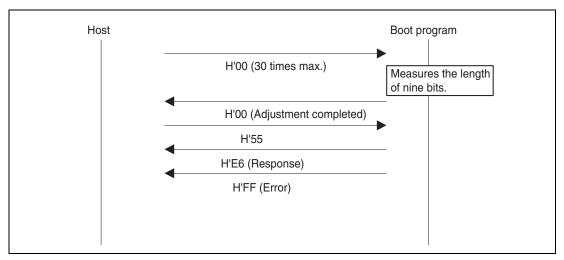

|      | 7.5.2  | Specifications of Standard Serial Communication Interface in Boot Mode | 207 |

|      | 7.5.3  | Programming/Erasing in User Mode                                       | 242 |

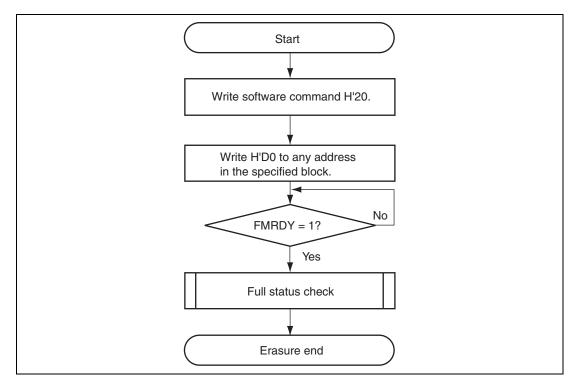

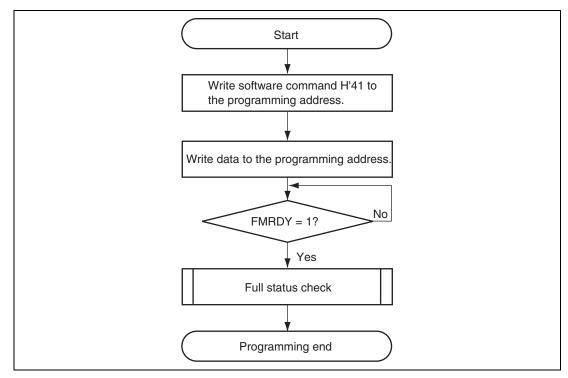

| 7.6  | Progra | amming/Erasing                                                         | 244 |

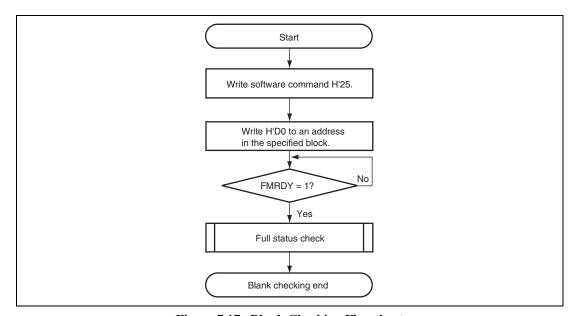

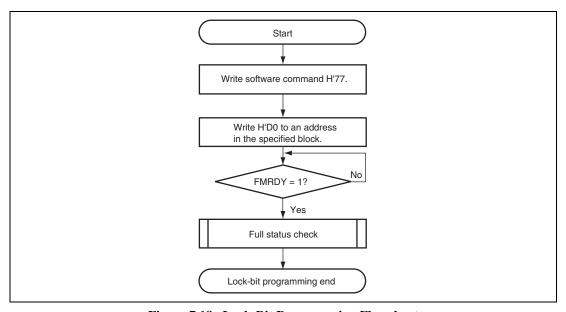

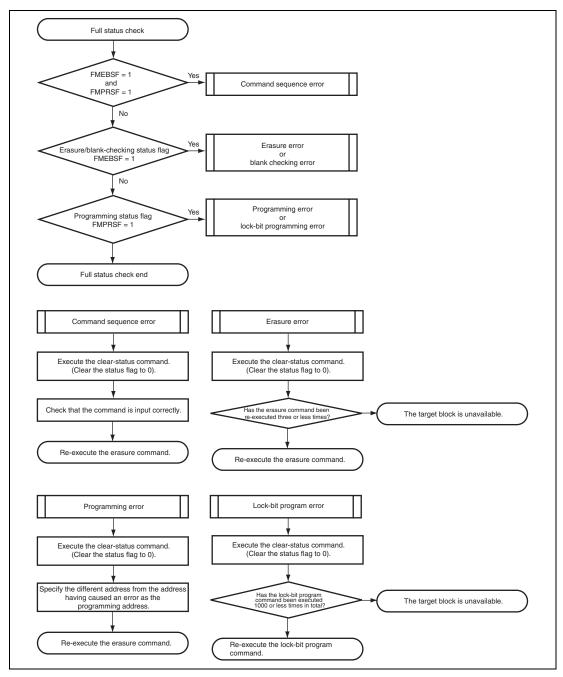

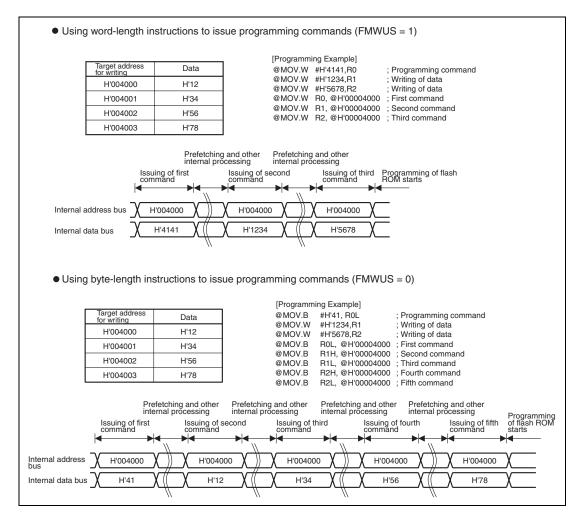

|      | 7.6.1  | Software Commands                                                      | 244 |

| 7.7  | Protec | tion                                                                   | 260 |

|      | 7.7.1  | Software Protection                                                    | 260 |

|      | 7.7.2  | Lock-Bit Protection                                                    | 260 |

|      | 7.7.3  | PROM Programmer Protection/Boot Mode Protection                        | 261 |

| 7.8  | Progra | ammer Mode                                                             | 263 |

| 7.9  | Usage  | Notes                                                                  | 264 |

| Sect | ion 8  | RAM                                                                    | 269 |

| Sect | ion 9  | Peripheral I/O Mapping Controller                                      | 271 |

| 9.1  | Regist | ter Descriptions                                                       | 273 |

|      | 9.1.1  | Peripheral Function Mapping Register Write-Protect Register (PMCWPR)   | 275 |

|      | 9.1.2  | Port Group 1 Peripheral Function Mapping Registers 1 to 4              |     |

|      |        | (PMCRn1 to PMCRn4 (n = 1, 2, 3, 5, and 6))                             | 276 |

|      | 9.1.3  | Port Group 2 Peripheral Function Mapping Registers 1 to 4              |     |

|      |        | (PMCRn1 to PMCRn4 (n = 4, 7, 8, 9, and A))                             | 297 |

| 9.2  | Usage  | Notes                                                                  | 314 |

|      | 9.2.1  | Procedures for Setting Multiplexed Port Functions                      | 314 |

|      | 9.2.2  | Notes on Setting PMC Registers                                         | 314 |

| Sect | ion 10 | I/O Ports                                                              | 315 |

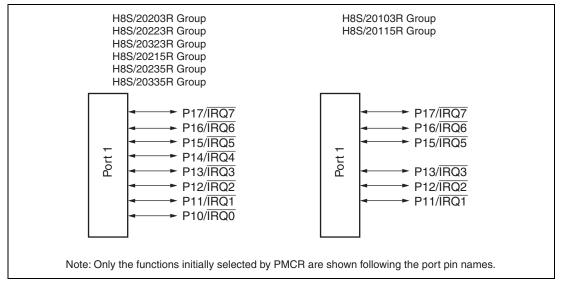

| 10.1 | Port 1 |                                                                        | 315 |

|      | 10.1.1 | Port Mode Register 1 (PMR1)                                            | 316 |

|      |        | Port Control Register 1 (PCR1)                                         |     |

|      | 10.1.3 | Port Data Register 1 (PDR1)                                            | 318 |

|      | 10.1.4 | Port Pull-Up Control Register 1 (PUCR1)                                | 319 |

|      | 10.1.5 | Port Drive Control Register 1 (PDVR1)                                  | 320 |

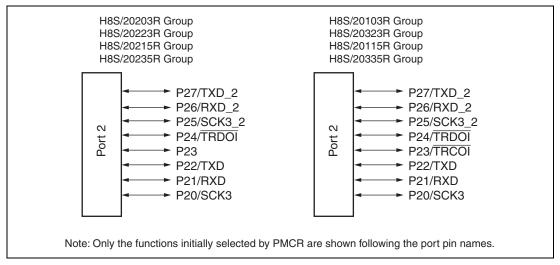

| 10.2 | Port 2 |                                                                        | 321 |

|      | 10.2.1 | Port Mode Register 2 (PMR2)                                            | 322 |

|      | 10.2.2 | Port Control Register 2 (PCR2)                                         | 323 |

|      |        | Port Data Register 2 (PDR2)                                            |     |

|      | 10.2.4 | Port Pull-Up Control Register 2 (PUCR2)                                | 325 |

|      |        | Port Drive Control Register 2 (PDVR2)                                  |     |

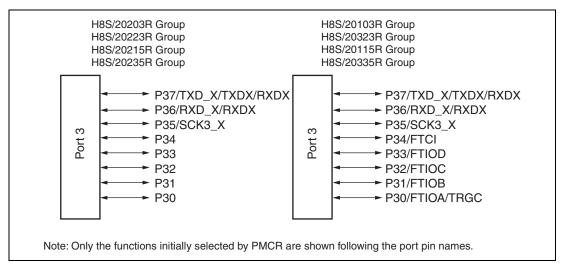

| 10.3 |        |                                                                        | 327 |

|      | 10.3.1  | Port Mode Register 3 (PMR3)             | 328 |

|------|---------|-----------------------------------------|-----|

|      | 10.3.2  | Port Control Register 3 (PCR3)          | 329 |

|      | 10.3.3  | Port Data Register 3 (PDR3)             | 330 |

|      |         | Port Pull-Up Control Register 3 (PUCR3) |     |

|      |         | Port Drive Control Register 3 (PDVR3)   |     |

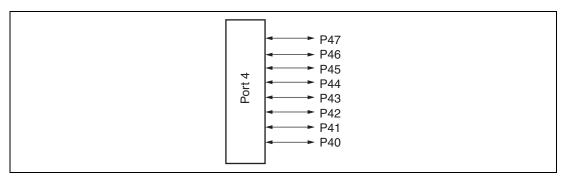

| 10.4 | Port 4. |                                         | 333 |

|      | 10.4.1  | Port Mode Register 4 (PMR4)             | 334 |

|      | 10.4.2  | Port Control Register 4 (PCR4)          | 335 |

|      | 10.4.3  | Port Data Register 4 (PDR4)             | 336 |

|      | 10.4.4  | Port Pull-Up Control Register 4 (PUCR4) | 337 |

|      | 10.4.5  | Port Drive Control Register 4 (PDVR4)   | 338 |

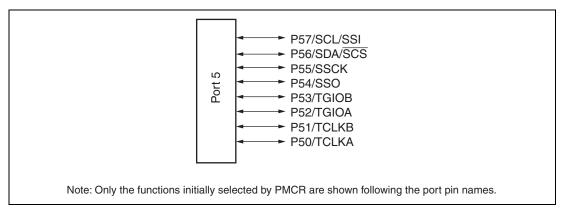

| 10.5 | Port 5. | -                                       | 339 |

|      | 10.5.1  | Port Mode Register 5 (PMR5)             | 340 |

|      | 10.5.2  | Port Control Register 5 (PCR5)          | 341 |

|      | 10.5.3  | Port Data Register 5 (PDR5)             | 342 |

|      | 10.5.4  | Port Pull-Up Control Register 5 (PUCR5) | 343 |

|      | 10.5.5  | Port Drive Control Register 5 (PDVR5)   | 344 |

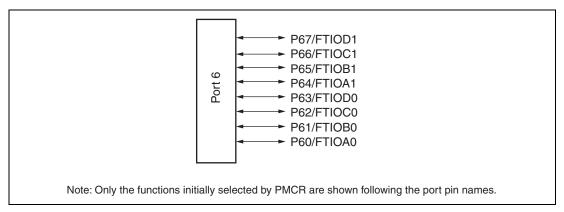

| 10.6 | Port 6. |                                         | 345 |

|      | 10.6.1  | Port Mode Register 6 (PMR6)             | 346 |

|      | 10.6.2  | Port Control Register 6 (PCR6)          | 347 |

|      | 10.6.3  | Port Data Register 6 (PDR6)             | 348 |

|      | 10.6.4  | Port Pull-Up Control Register 6 (PUCR6) | 349 |

|      | 10.6.5  | Port Drive Control Register 6 (PDVR6)   | 350 |

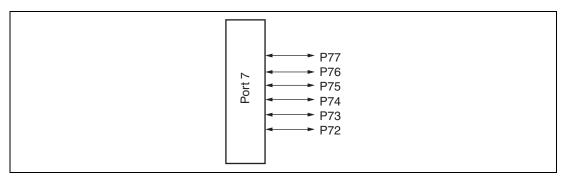

| 10.7 | Port 7. |                                         | 351 |

|      | 10.7.1  | Port Mode Register 7 (PMR7)             | 352 |

|      | 10.7.2  | Port Control Register 7 (PCR7)          | 353 |

|      | 10.7.3  | Port Data Register 7 (PDR7)             | 354 |

|      | 10.7.4  | Port Pull-Up Control Register 7 (PUCR7) | 355 |

|      | 10.7.5  | Port Drive Control Register 7 (PDVR7)   | 356 |

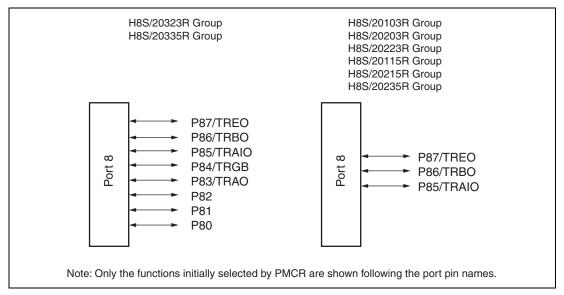

| 10.8 | Port 8. |                                         | 357 |

|      | 10.8.1  | Port Mode Register 8 (PMR8)             | 358 |

|      | 10.8.2  | Port Control Register 8 (PCR8)          | 359 |

|      |         | Port Data Register 8 (PDR8)             |     |

|      | 10.8.4  | Port Pull-Up Control Register 8 (PUCR8) | 361 |

|      | 10.8.5  | Port Drive Control Register 8 (PDVR8)   | 362 |

|      | 10.8.6  | Notes on Using Port 8                   | 362 |

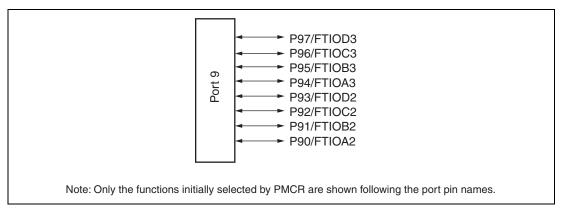

| 10.9 |         |                                         |     |

|      | 10.9.1  | Port Mode Register 9 (PMR9)             | 364 |

|      | 10.9.2  | Port Control Register 9 (PCR9)          | 365 |

|      | 1093    | Port Data Register 9 (PDR9)             | 366 |

|       | 10.9.4  | Port Pull-Up Control Register 9 (PUCR9)         | 367 |

|-------|---------|-------------------------------------------------|-----|

|       | 10.9.5  | Port Drive Control Register 9 (PDVR9)           | 368 |

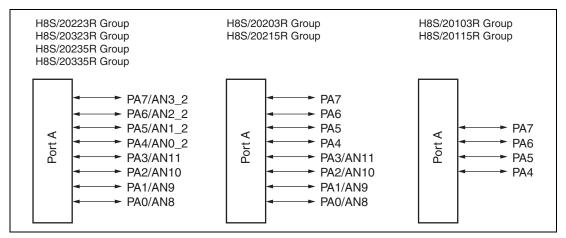

| 10.10 | Port A  | -                                               | 369 |

|       | 10.10.1 | Port Mode Register A (PMRA)                     | 370 |

|       | 10.10.2 | Port Control Register A (PCRA)                  | 371 |

|       |         | Port Data Register A (PDRA)                     |     |

|       | 10.10.4 | Port Pull-Up Control Register A (PUCRA)         | 373 |

|       | 10.10.5 | Port Mode Register A (PMRA)                     | 374 |

|       | 10.10.6 | Port Control Register A (PCRA)                  | 375 |

|       | 10.10.7 | Port Data Register A (PDRA)                     | 376 |

|       | 10.10.8 | Port Pull-Up Control Register A (PUCRA)         | 377 |

|       | 10.10.9 | Port Mode Register A (PMRA)                     | 378 |

|       | 10.10.1 | 0 Port Control Register A (PCRA)                | 379 |

|       | 10.10.1 | 1 Port Data Register A (PDRA)                   | 380 |

|       | 10.10.1 | 2 Port Pull-Up Control Register A (PUCRA)       | 381 |

|       | 10.10.1 | 3 Notes on Using Port A                         | 381 |

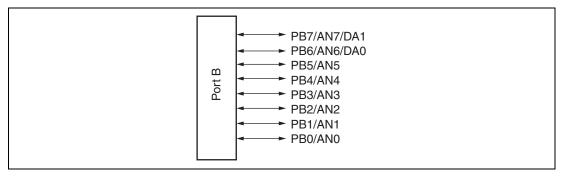

| 10.11 | Port B  |                                                 | 382 |

|       | 10.11.1 | Port Control Register B (PCRB)                  | 383 |

|       |         | Port Data Register B (PDRB)                     |     |

|       | 10.11.3 | Port Pull-Up Control Register B (PUCRB)         | 385 |

|       | 10.11.4 | Notes on Using Port B                           | 385 |

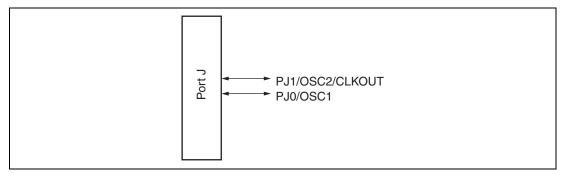

| 10.12 | Port J. |                                                 | 386 |

|       |         | Port Mode Register J (PMRJ)                     |     |

|       | 10.12.2 | Port Control Register J (PCRJ)                  | 388 |

|       | 10.12.3 | Port Data Register J (PDRJ)                     | 389 |

|       | 10.12.4 | Port Pull-Up Control Register J (PUCRJ)         | 390 |

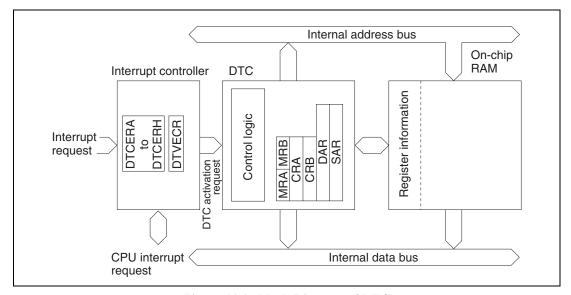

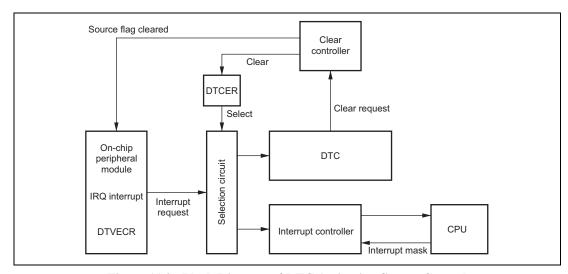

| Secti | on 11   | Data Transfer Controller (DTC)                  | 391 |

| 11.1  | Feature | PS                                              | 391 |

| 11.2  | Registe | er Descriptions                                 | 393 |

|       | 11.2.1  | DTC Mode Register A (MRA)                       | 394 |

|       | 11.2.2  | DTC Mode Register B (MRB)                       | 396 |

|       | 11.2.3  | DTC Source Address Register (SAR)               | 397 |

|       | 11.2.4  | DTC Destination Address Register (DAR)          | 397 |

|       | 11.2.5  | DTC Transfer Count Register A (CRA)             | 398 |

|       | 11.2.6  | DTC Transfer Count Register B (CRB)             | 398 |

|       | 11.2.7  | DTC Enable Registers A to H (DTCERA to DTCERH)  | 399 |

|       | 11.2.8  | DTC Vector Register (DTVECR)                    | 401 |

| 11.3  | Activat | ion Sources                                     | 402 |

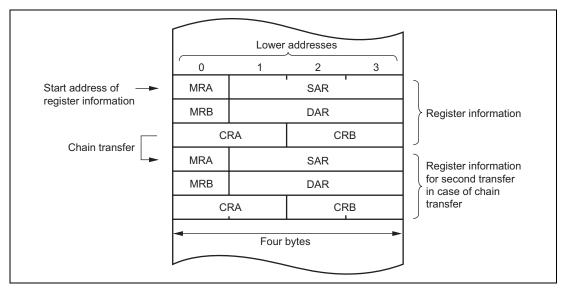

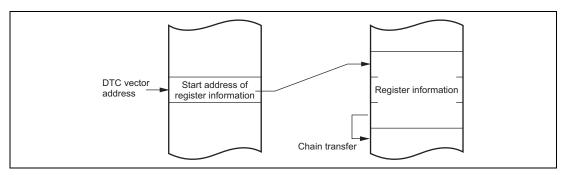

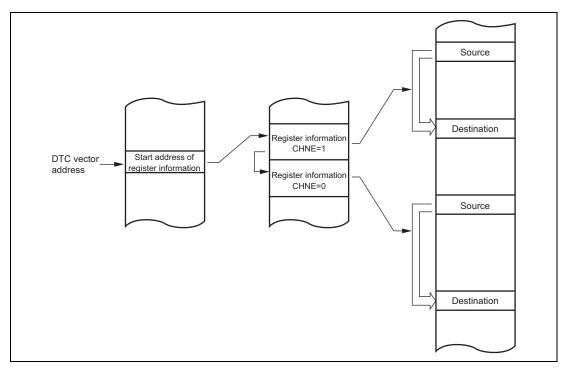

| 11.4  | Locatio | on of Register Information and DTC Vector Table | 404 |

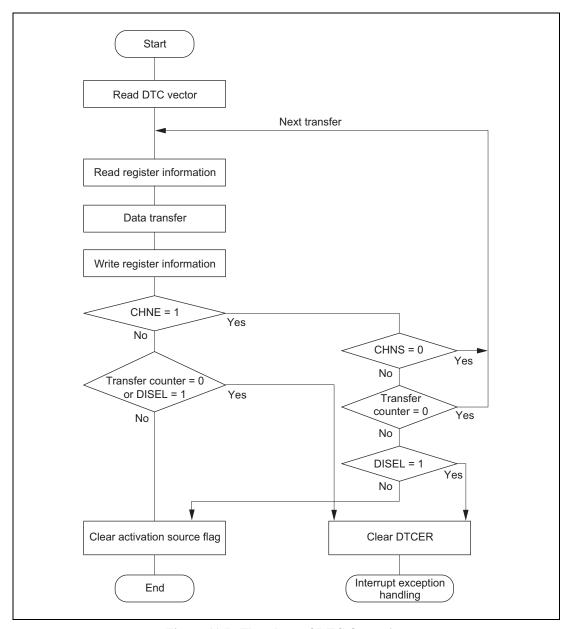

| 11.5 | Operati | on                                                                   | 410 |

|------|---------|----------------------------------------------------------------------|-----|

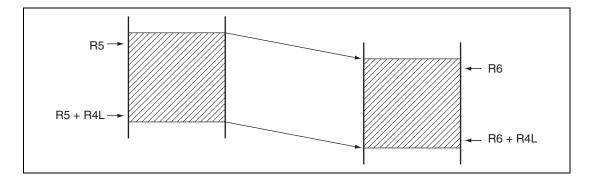

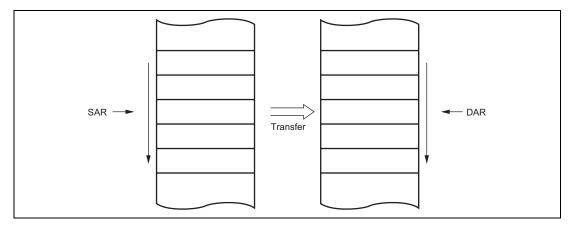

|      | 11.5.1  | Normal Mode                                                          | 412 |

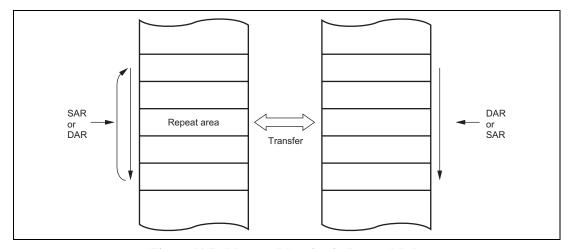

|      | 11.5.2  | Repeat Mode                                                          | 413 |

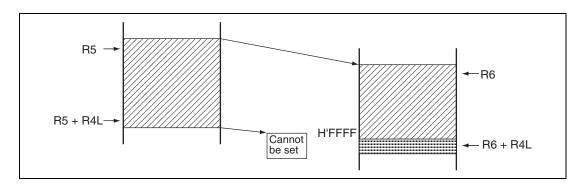

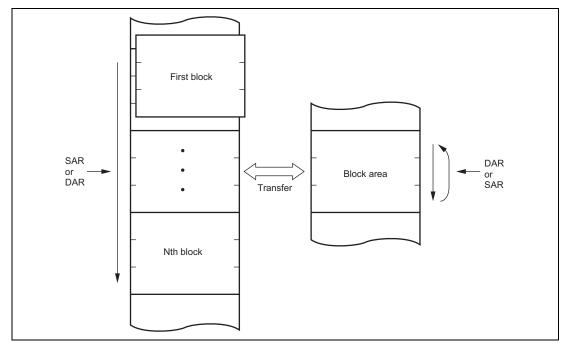

|      | 11.5.3  | Block Transfer Mode                                                  | 414 |

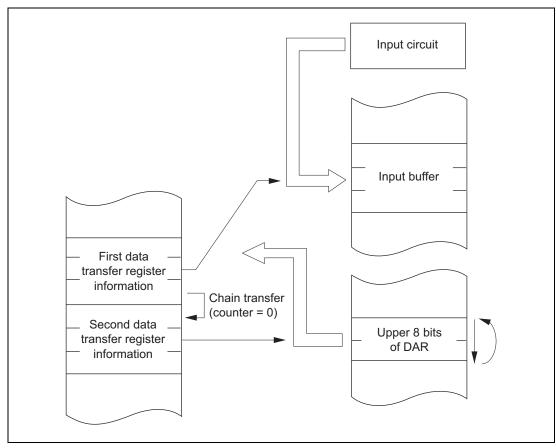

|      | 11.5.4  | Chain Transfer                                                       | 415 |

|      | 11.5.5  | Interrupt Sources                                                    | 416 |

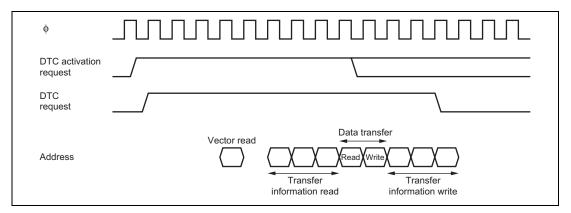

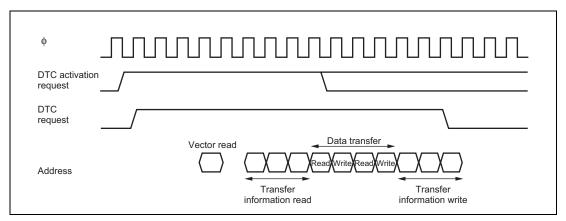

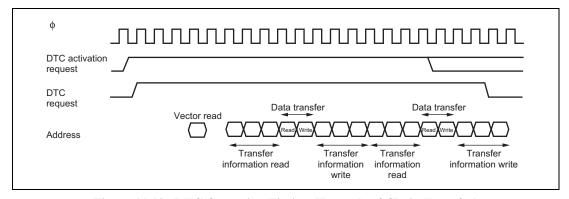

|      | 11.5.6  | Operation Timing                                                     | 417 |

|      |         | Number of DTC Execution States                                       |     |

| 11.6 |         | ures for Using DTC                                                   |     |

|      | 11.6.1  | Activation by Interrupt                                              | 420 |

|      | 11.6.2  | Activation by Software                                               | 420 |

| 11.7 |         | les of Use of the DTC                                                |     |

|      | 11.7.1  | Normal Mode                                                          | 421 |

|      | 11.7.2  | Chain Transfer when Transfer Counter = 0                             | 422 |

|      | 11.7.3  | Software Activation                                                  | 424 |

| 11.8 | Usage 1 | Notes                                                                | 425 |

|      | _       | Module Standby Mode Setting                                          |     |

|      |         | DTCE Bit Setting                                                     |     |

|      | 11.8.3  | DTC Activation by SCI3, IIC2/SSU and A/D Converter Interrupt Sources | 425 |

| Sect | ion 12  | Event Link Controller                                                | 427 |

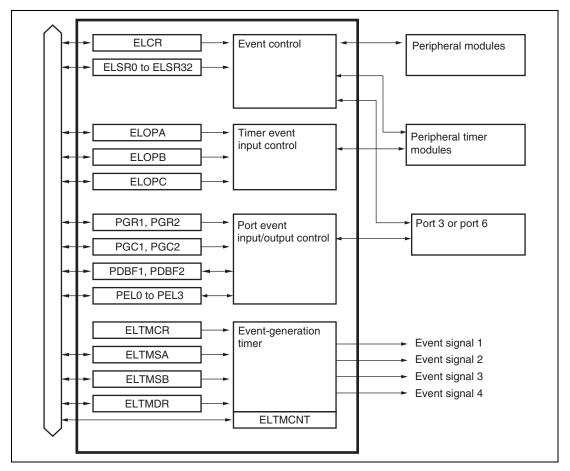

| 12.1 | Overvi  | ew                                                                   | 427 |

| 12.2 | Registe | r Descriptions                                                       | 429 |

|      |         | Event Link Control Register (ELCR)                                   |     |

|      | 12.2.2  | Event Link Setting Registers 0 to 32 (ELSR0 to ELSR32)               | 430 |

|      |         | Event Link Option Setting Register A (ELOPA)                         |     |

|      | 12.2.4  | Event Link Option Setting Register B (ELOPB)                         | 435 |

|      | 12.2.5  | Event Link Option Setting Register C (ELOPC)                         | 435 |

|      | 12.2.6  | Port-Group Setting Registers 1 and 2 (PGR1 and PGR2)                 | 436 |

|      | 12.2.7  | Port-Group Control Registers 1 and 2 (PGC1 and PGC2)                 | 437 |

|      |         | Port Buffer Registers 1 and 2 (PDBF1 and PDBF2)                      |     |

|      | 12.2.9  | Event Link Port Setting Registers 0 to 3 (PEL0 to PEL3)              | 439 |

|      | 12.2.10 | Event-Generation Timer Control Register (ELTMCR)                     | 440 |

|      | 12.2.11 | Event-Generation Timer Interval Setting Register A (ELTMSA)          | 441 |

|      |         | Event-Generation Timer Interval Setting Register B (ELTMSB)          |     |

|      |         | Event-Generation Timer Delay Selection Register (ELTMDR)             |     |

|      |         | ELC Timer Counter (ELTMCNT)                                          |     |

| 12.3 |         | ion                                                                  |     |

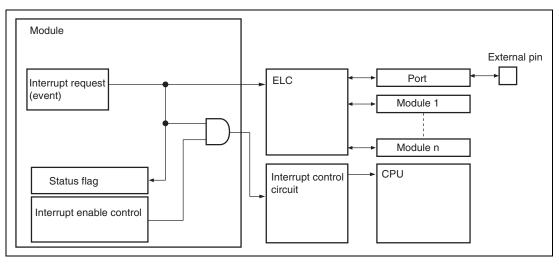

|      |         | Relation between Interrupt Processing and Event Linking              |     |

|      |         | Event Linkage                                                        |     |

|      | 12.3.3  | Operation of Peripheral Timer Modules When Event is Input | 449 |

|------|---------|-----------------------------------------------------------|-----|

|      | 12.3.4  | Operation of A/D and D/A Converters When Event is Input   | 449 |

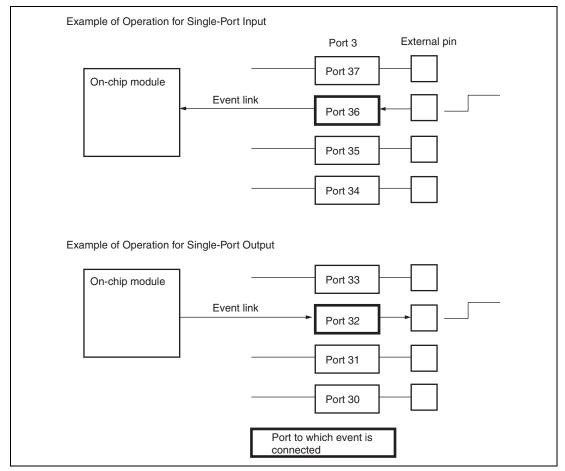

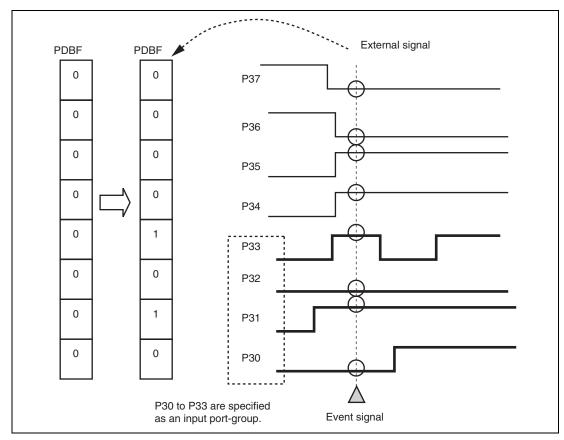

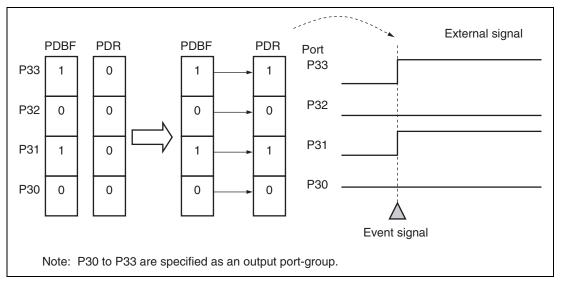

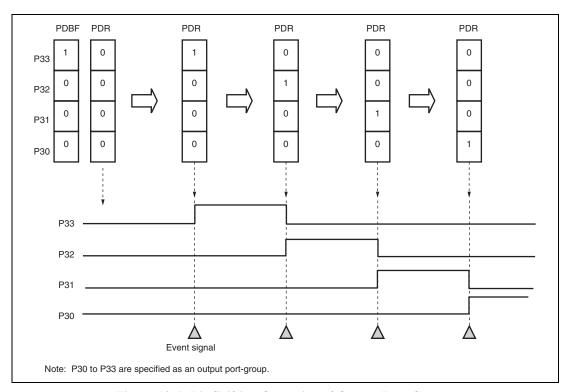

|      | 12.3.5  | Port Operation upon Event Input and Event Generation      | 450 |

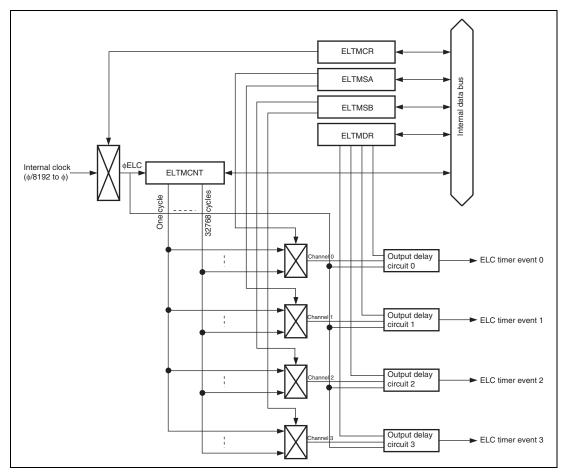

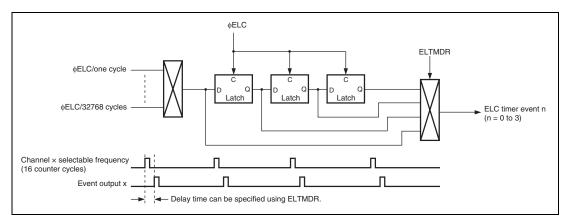

|      | 12.3.6  | Event-Generation Timer                                    | 456 |

|      | 12.3.7  | Procedure for Linking Events                              | 458 |

| Sect | ion 13  | Timer RA                                                  | 459 |

| 13.1 | Overvi  | ew                                                        | 459 |

| 13.2 | Registe | er Descriptions                                           | 460 |

|      | 13.2.1  | Timer RA Control Register (TRACR)                         | 461 |

|      | 13.2.2  | Timer RA I/O Control Register (TRAIOC)                    | 463 |

|      | 13.2.3  | Timer RA Mode Register (TRAMR)                            | 465 |

|      | 13.2.4  | Timer RA Interrupt Enable Status Register (TRAIR)         | 466 |

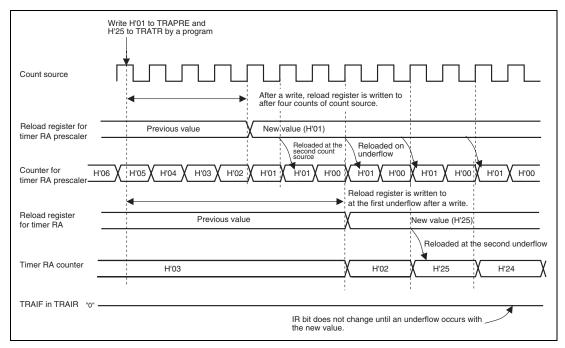

|      | 13.2.5  | Timer RA Prescaler Register (TRAPRE)                      | 467 |

|      | 13.2.6  | Timer RA Timer Register (TRATR)                           | 468 |

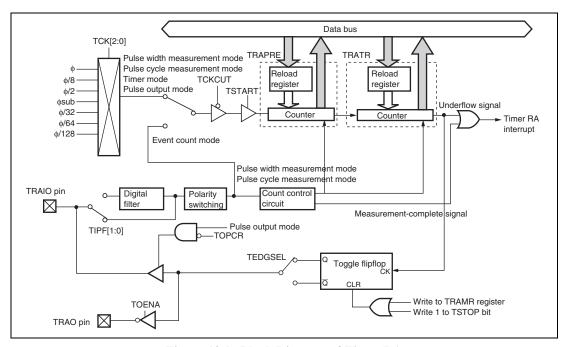

| 13.3 | Operat  | ion                                                       | 469 |

|      | 13.3.1  | Operations Common to Various Modes                        | 469 |

|      | 13.3.2  | Timer Mode                                                | 470 |

|      | 13.3.3  | Pulse Output Mode                                         | 470 |

|      | 13.3.4  | Event Counter Mode                                        | 471 |

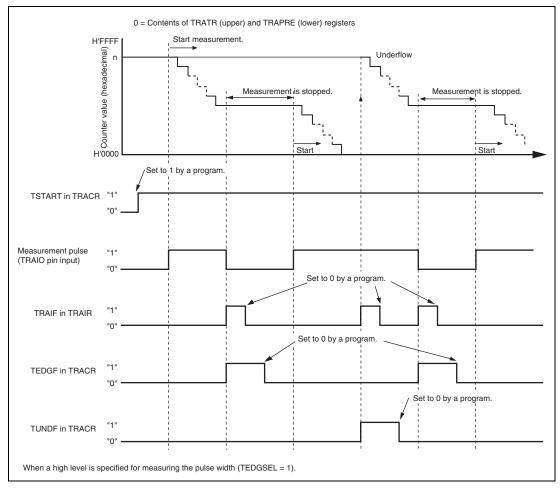

|      | 13.3.5  | Pulse Width Measurement Mode                              | 471 |

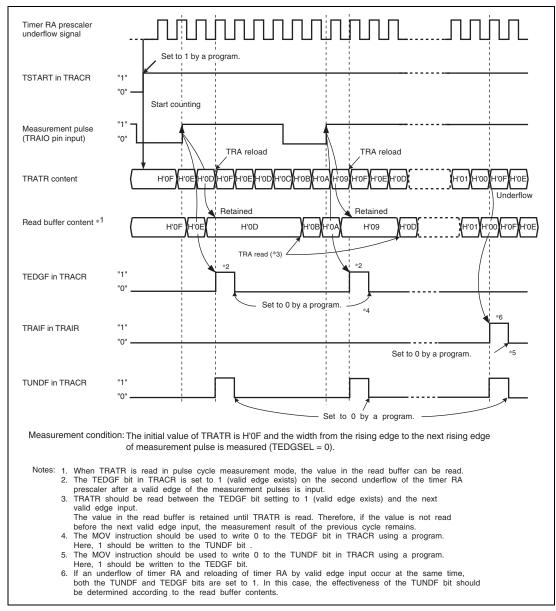

|      | 13.3.6  | Pulse Cycle Measurement Mode                              | 473 |

|      | 13.3.7  | Operation through an Event Link                           | 474 |

| 13.4 | Usage   | Notes                                                     | 476 |

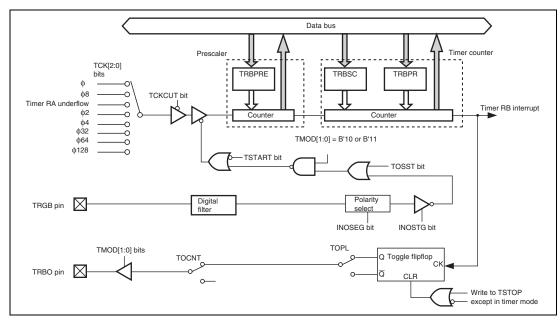

| Sect | ion 14  | Timer RB                                                  | 477 |

| 14.1 | Overvi  | ew                                                        | 477 |

| 14.2 | Registe | er Descriptions                                           | 478 |

|      | 14.2.1  | Timer RB Control Register (TRBCR)                         | 479 |

|      | 14.2.2  | Timer RB One-Shot Control Register (TRBOCR)               | 480 |

|      | 14.2.3  | Timer RB I/O Control Register (TRBIOC)                    | 481 |

|      | 14.2.4  | Timer RB Mode Register (TRBMR)                            | 483 |

|      | 14.2.5  | Timer RB Interrupt Enable Status Register (TRBIR)         | 484 |

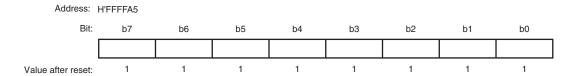

|      | 14.2.6  | Timer RB Prescaler Register (TRBPRE)                      | 485 |

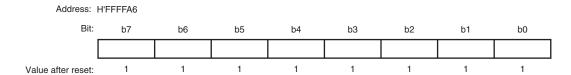

|      | 14.2.7  | Timer RB Secondary Register (TRBSC)                       | 485 |

|      | 14.2.8  | Timer RB Primary Register (TRBPR)                         | 486 |

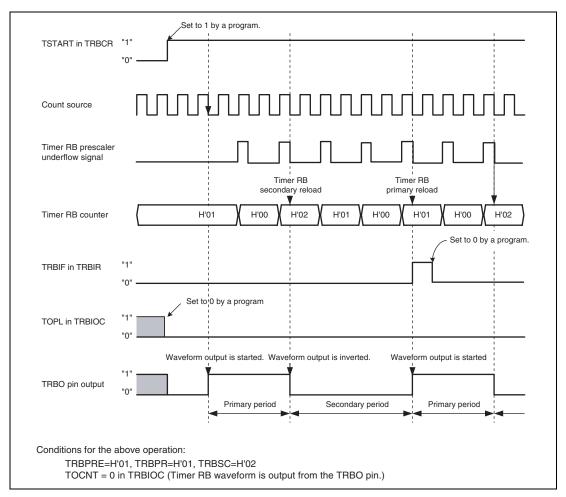

| 14.3 | Operat  | ion                                                       | 487 |

|      | 14.3.1  | Timer Mode                                                | 487 |

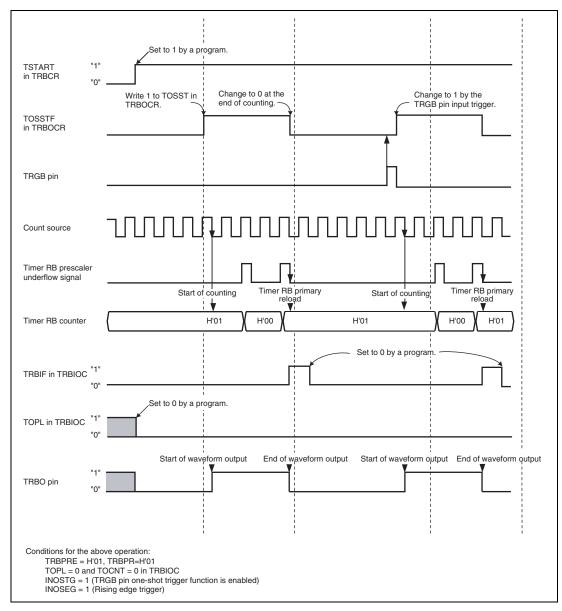

|      | 14.3.2  | Programmable Waveform Generation Mode                     | 488 |

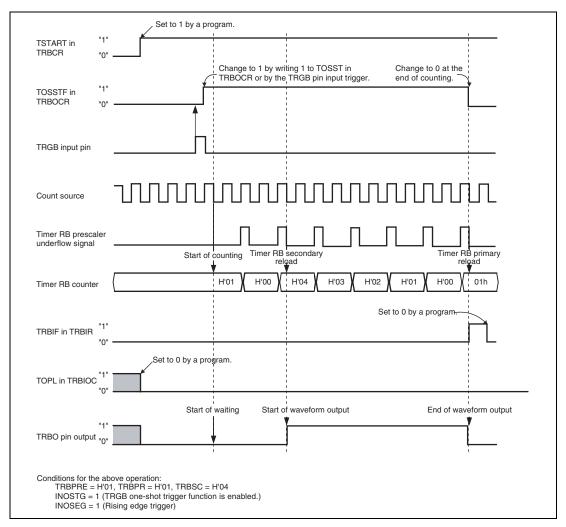

|      | 14 3 3  | Programmable One-Shot Generation Mode                     | 490 |

|      | 14.3.4   | Programmable Wait One-Shot Generation Mode                              | 492 |

|------|----------|-------------------------------------------------------------------------|-----|

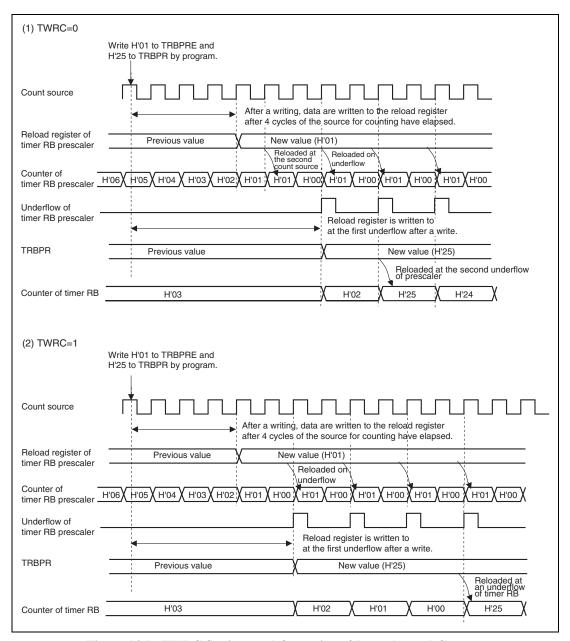

|      |          | Timing at Which Values Take Effect in Prescaler or Counter Depending on |     |

|      |          | TWRC Bit                                                                | 494 |

|      | 14.3.6   | TOCNT Settings and Pin State Update Conditions                          | 496 |

|      | 14.3.7   | Operation through an Event Link                                         | 497 |

| 14.4 | Interruj | pt Request                                                              | 498 |

| 14.5 | Usage    | Notes                                                                   | 499 |

| Sect | ion 15   | Timer RC                                                                | 501 |

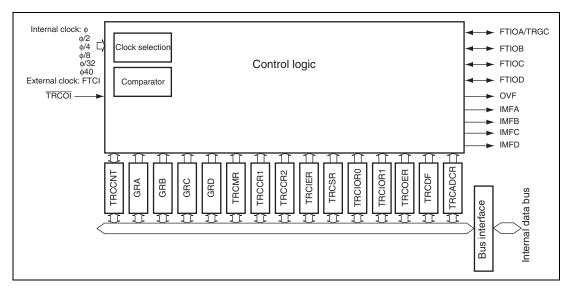

| 15.1 | Feature  | PS                                                                      | 501 |

| 15.2 | Registe  | er Descriptions                                                         | 504 |

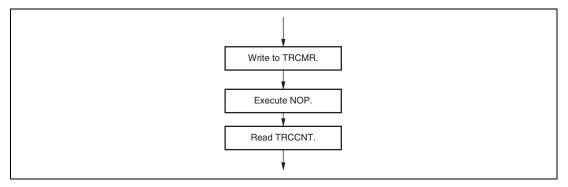

|      | 15.2.1   | Timer RC Mode Register (TRCMR)                                          | 505 |

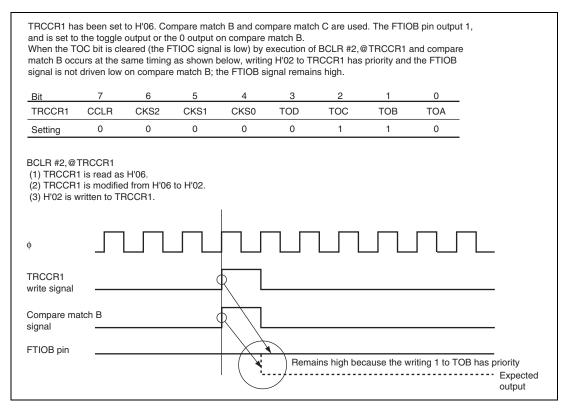

|      | 15.2.2   | Timer RC Control Register 1 (TRCCR1)                                    | 506 |

|      | 15.2.3   | Timer RC Control Register 2 (TRCCR2)                                    | 508 |

|      | 15.2.4   | Timer RC Interrupt Enable Register (TRCIER)                             | 509 |

|      | 15.2.5   | Timer RC Status Register (TRCSR)                                        | 510 |

|      | 15.2.6   | Timer RC I/O Control Register 0 (TRCIOR0)                               | 513 |

|      | 15.2.7   | Timer RC I/O Control Register 1 (TRCIOR1)                               | 515 |

|      |          | Timer RC Output Enable Register (TRCOER)                                |     |

|      | 15.2.9   | Timer RC Digital Filtering Function Select Register (TRCDF)             | 518 |

|      | 15.2.10  | Timer RC A/D Conversion Start Trigger Control Register (TRCADCR)        | 519 |

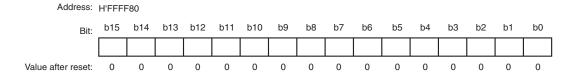

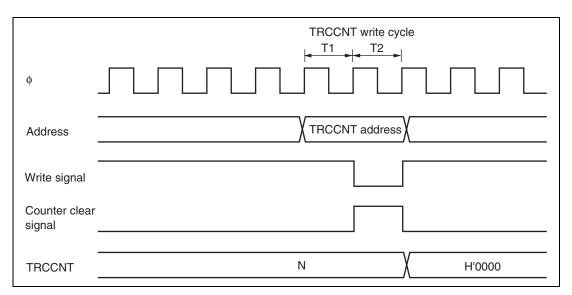

|      | 15.2.11  | Timer RC Counter (TRCCNT)                                               | 520 |

|      | 15.2.12  | 2 General Registers A, B, C, and D (GRA, GRB, GRC, and GRD)             | 521 |

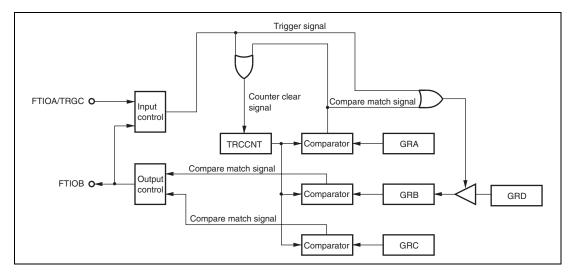

| 15.3 | Operati  | ion                                                                     | 523 |

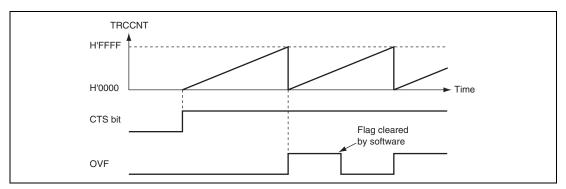

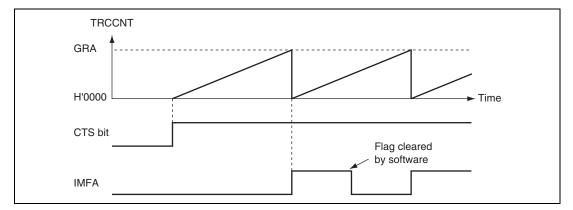

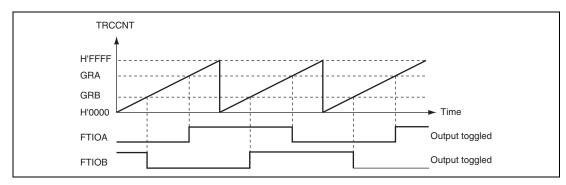

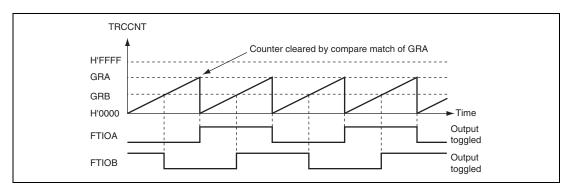

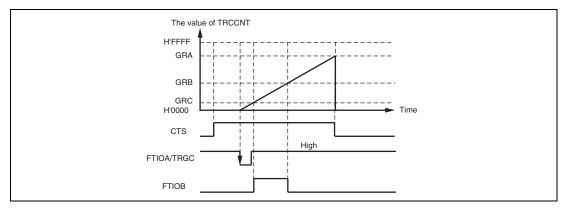

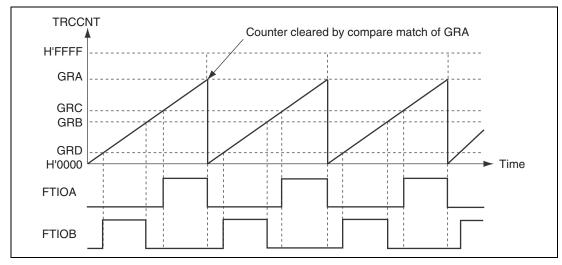

|      | 15.3.1   | Timer Mode Operation                                                    | 525 |

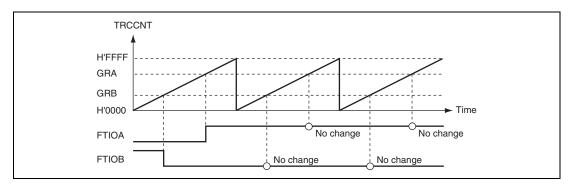

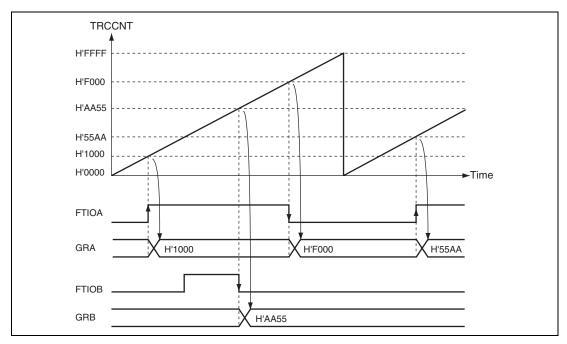

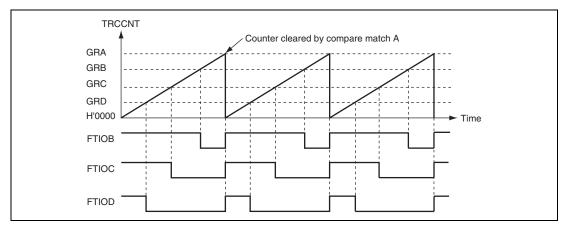

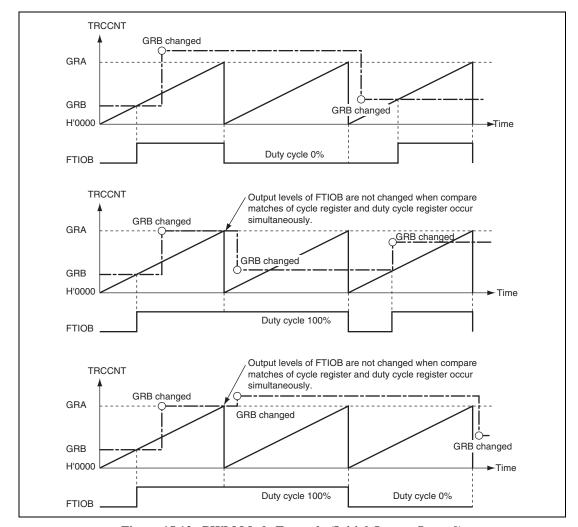

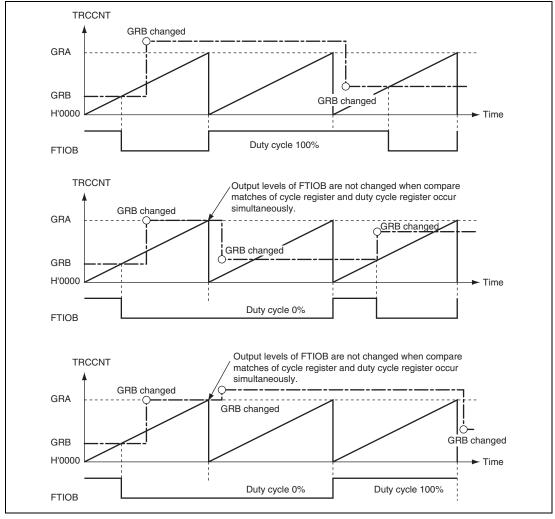

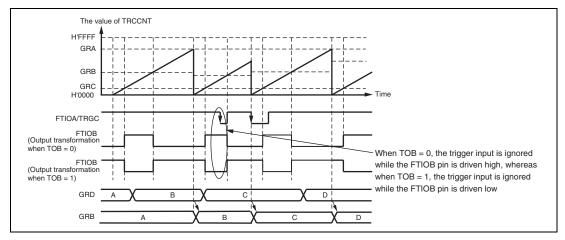

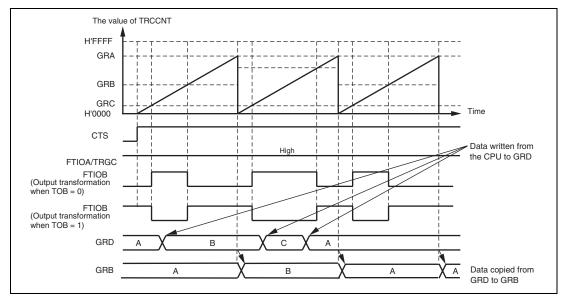

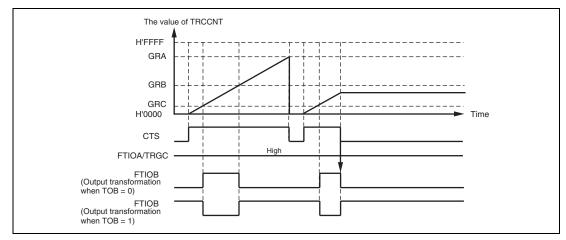

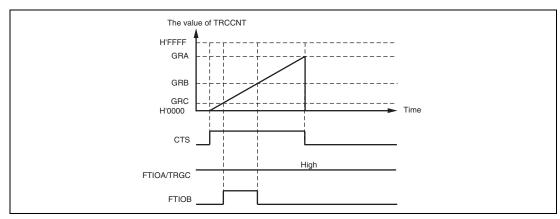

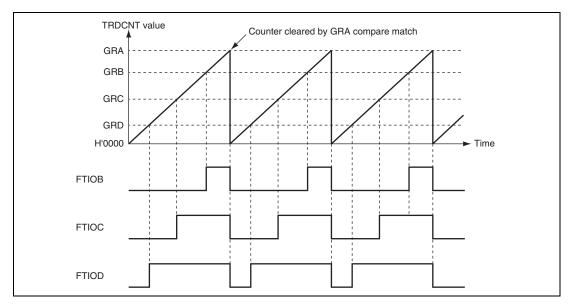

|      | 15.3.2   | PWM Mode Operation                                                      | 530 |

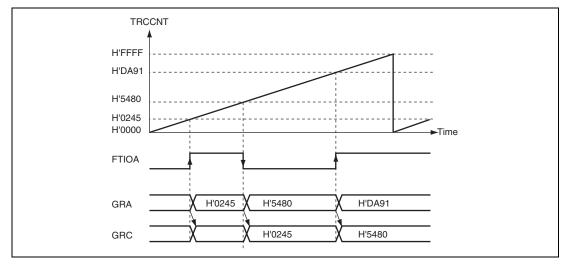

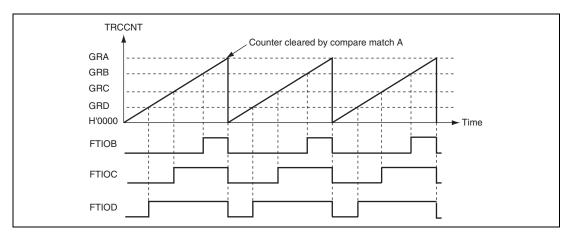

|      | 15.3.3   | PWM2 Mode Operation                                                     | 535 |

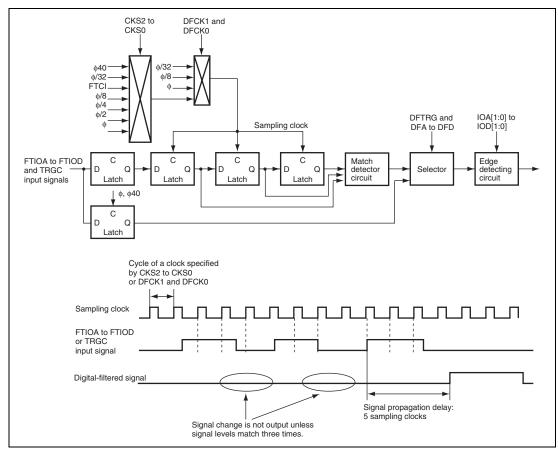

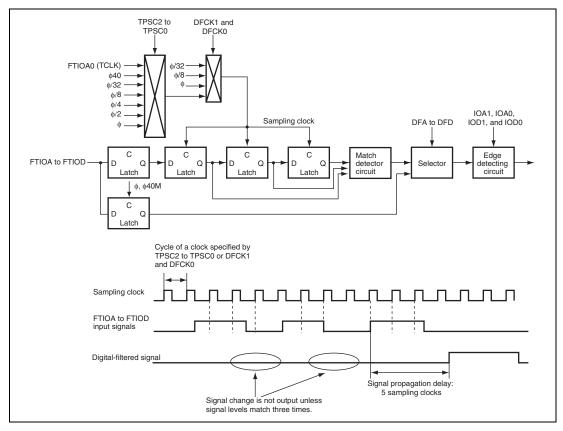

|      | 15.3.4   | Digital Filtering Function for Input Capture Inputs                     | 541 |

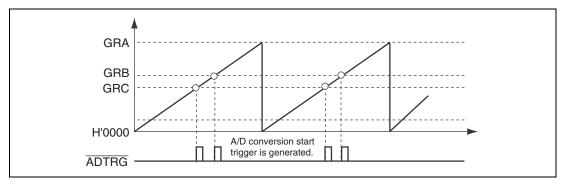

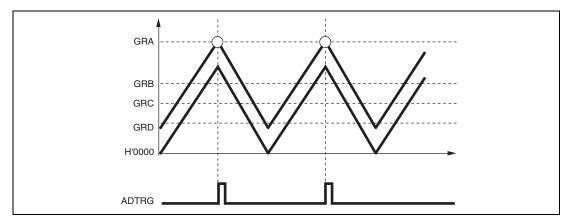

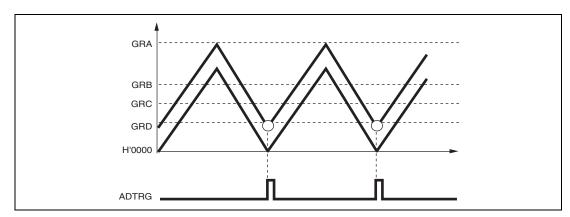

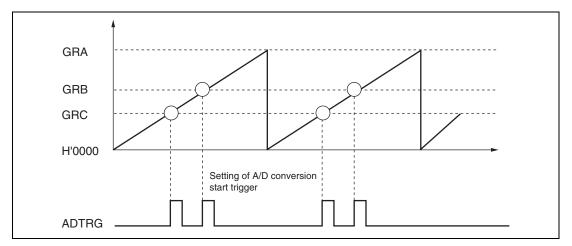

|      | 15.3.5   | A/D Conversion Start Trigger Setting Function                           | 542 |

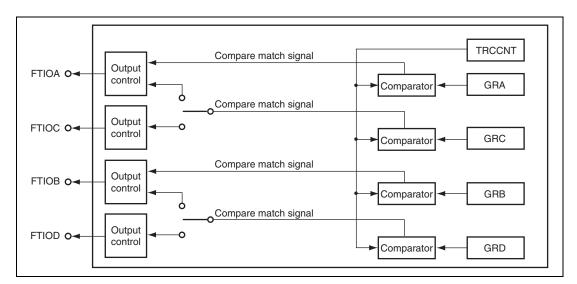

|      | 15.3.6   | Function of Changing Output Pins for GR                                 | 544 |

|      | 15.3.7   | Operation through an Event Link                                         | 546 |

| 15.4 | Operati  | ion Timing                                                              | 547 |

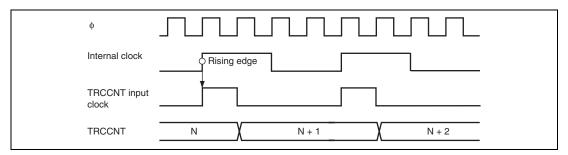

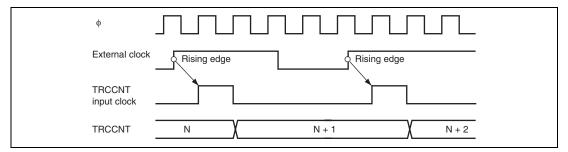

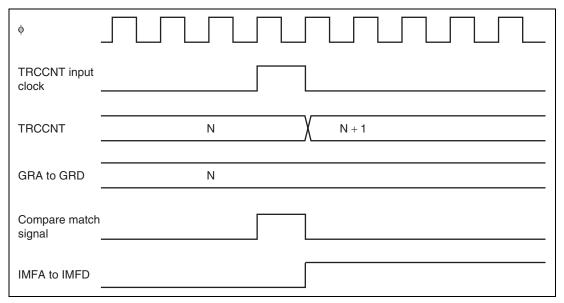

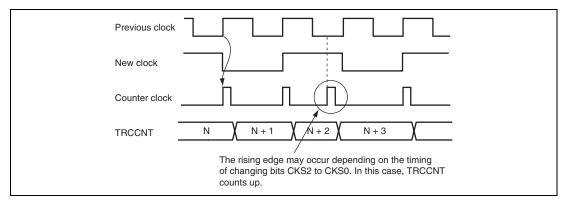

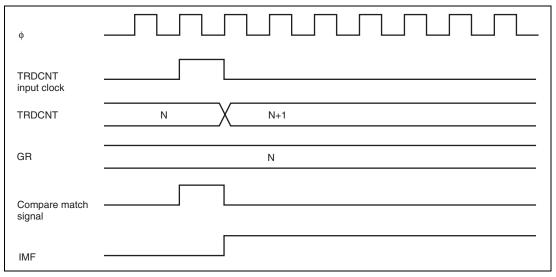

|      | 15.4.1   | TRCCNT Counting Timing                                                  | 547 |

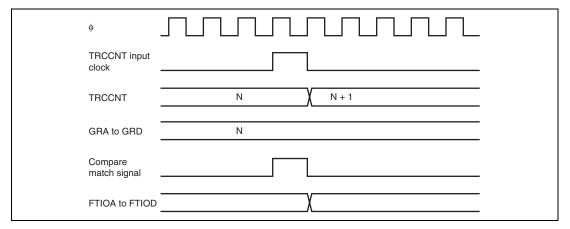

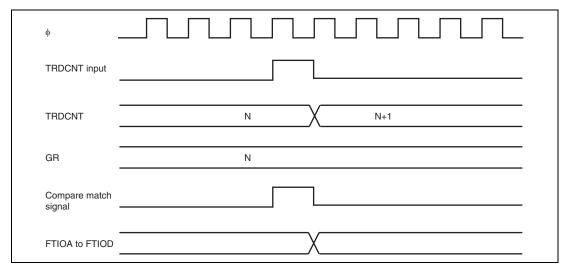

|      | 15.4.2   | Output Compare Output Timing                                            | 548 |

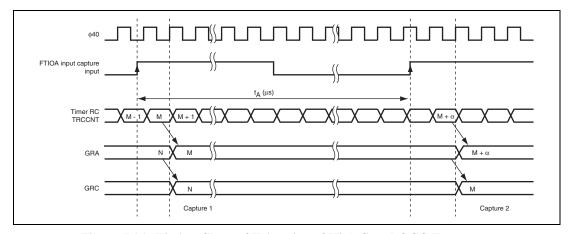

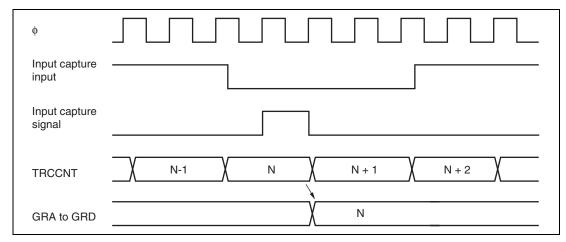

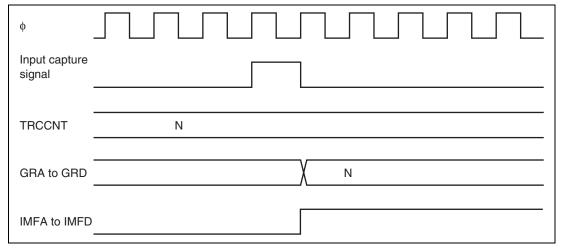

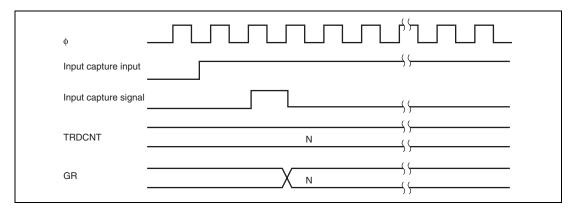

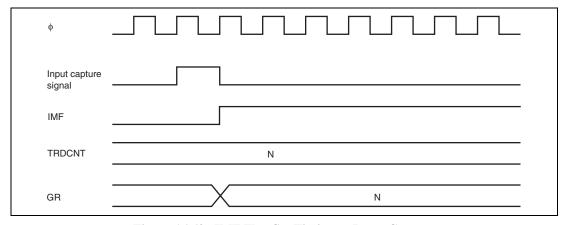

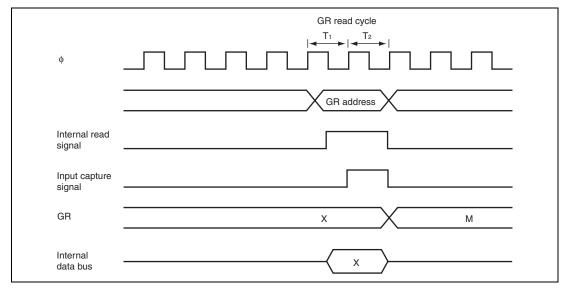

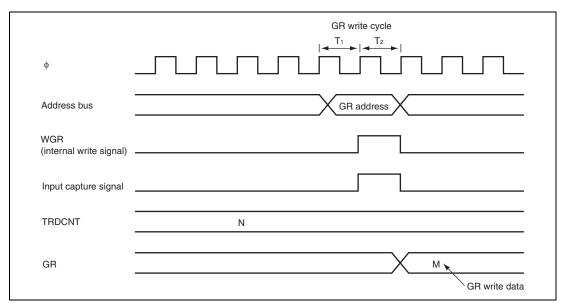

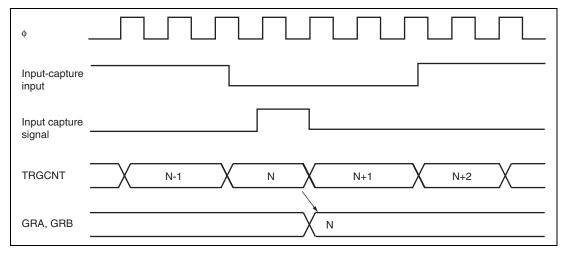

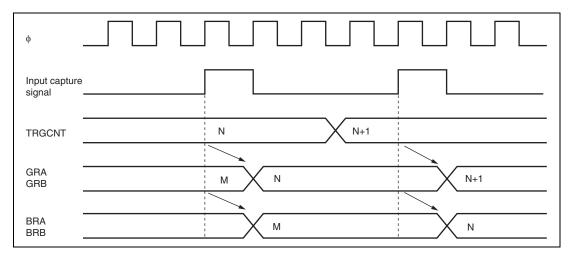

|      | 15.4.3   | Input Capture Timing                                                    | 549 |

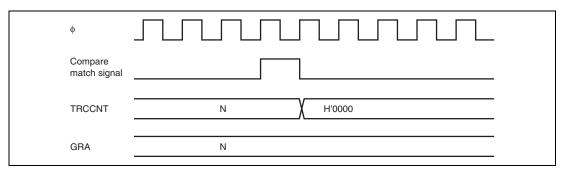

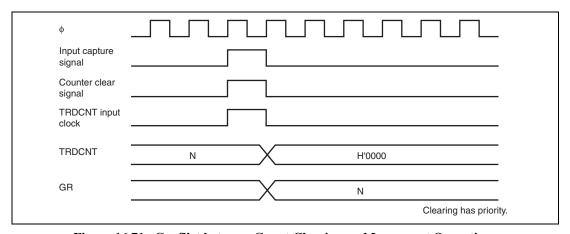

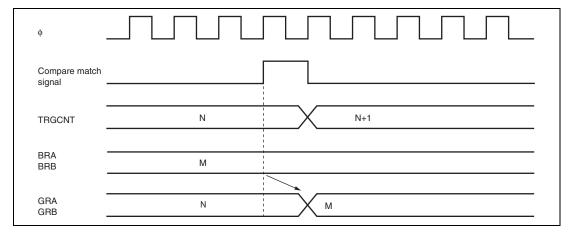

|      | 15.4.4   | Timing of Counter Clearing by Compare Match                             | 549 |

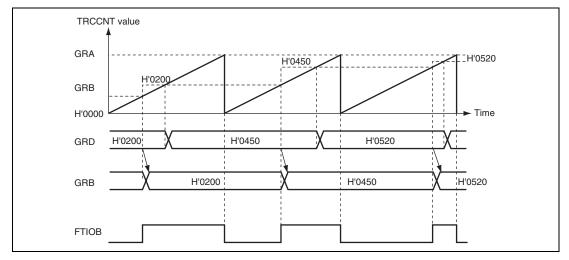

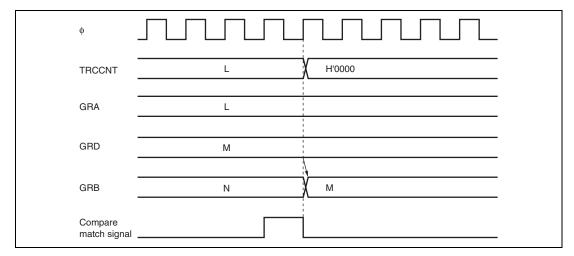

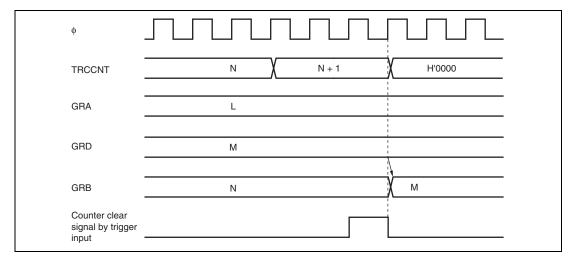

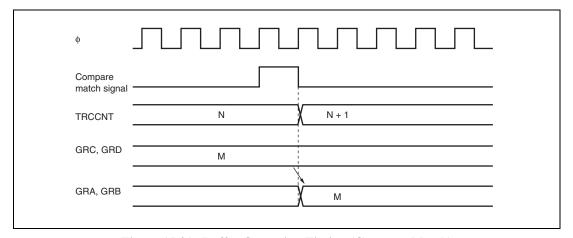

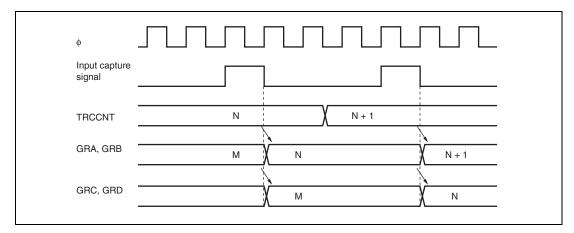

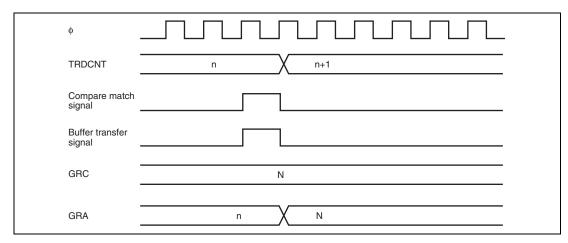

|      | 15.4.5   | Buffer Operation Timing                                                 | 550 |

|      | 15.4.6   | Timing of IMFA to IMFD Flag Setting at Compare Match                    | 551 |

|      | 15.4.7   | Timing of IMFA to IMFD Setting at Input Capture                         | 552 |

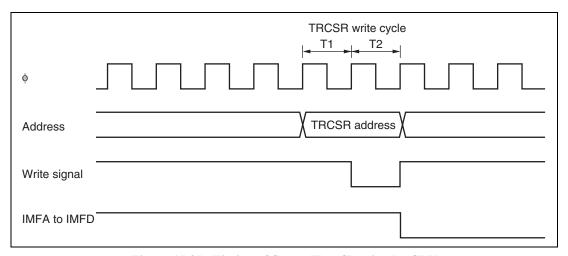

|      | 1548     | Timing of Status Flag Clearing                                          | 553 |

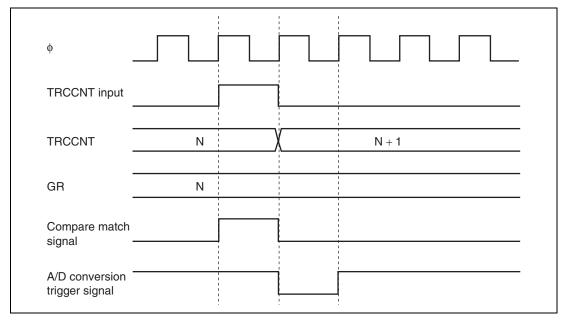

|      | 15.4.9  | Timing of A/D Conversion Start Trigger Generation on Compare Match | 554 |

|------|---------|--------------------------------------------------------------------|-----|

| 15.5 | Usage 1 | Notes                                                              | 555 |

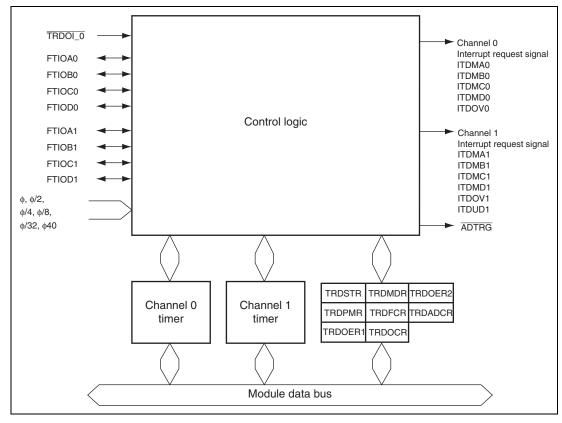

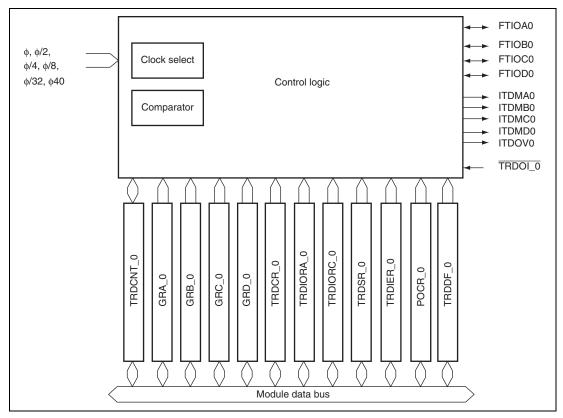

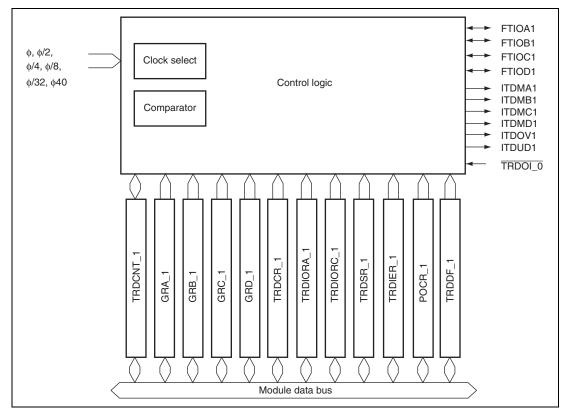

| Cont | ion 16  | Timer RD                                                           | 550 |

| 16.1 |         | Timer KD                                                           |     |

| 16.1 |         | er Descriptions                                                    |     |

| 10.2 | _       | Timer RD Start Register (TRDSTR)                                   |     |

|      |         | Timer RD Mode Register (TRDMDR)                                    |     |

|      |         | Timer RD PWM Mode Register (TRDPMR)                                |     |

|      | 16.2.4  |                                                                    |     |

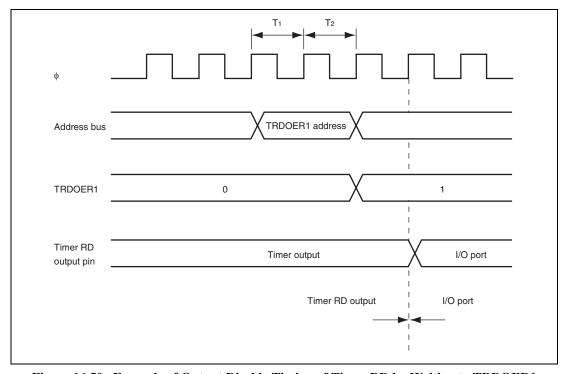

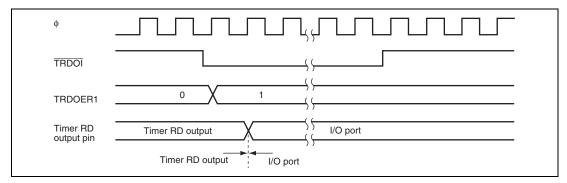

|      | 16.2.4  | Timer RD Output Master Enable Register 1 (TRDOER1)                 |     |

|      | 16.2.5  | Timer RD Output Master Enable Register 2 (TRDOER1)                 |     |

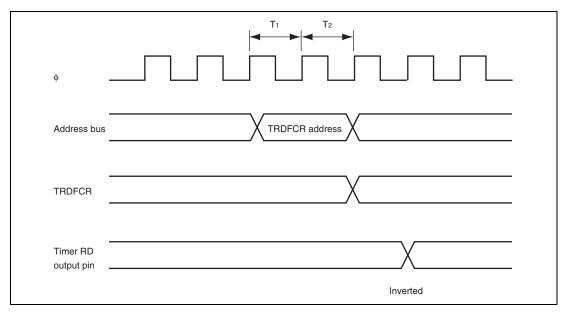

|      |         | Timer RD Output (Master Eliable Register 2 (TRDOER2)               |     |

|      |         | Timer RD A/D Conversion Start Trigger Control Register (TRDADCR)   |     |

|      |         | Timer RD Counter (TRDCNT)                                          |     |

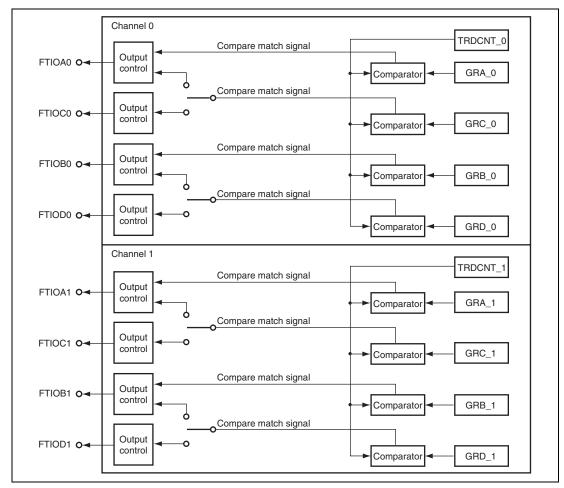

|      |         | General Registers A, B, C, and D (GRA, GRB, GRC, and GRD)          |     |

|      |         | Timer RD Control Register (TRDCR)                                  |     |

|      |         | 2 Timer RD I/O Control Registers (TRDIORA and TRDIORC)             |     |

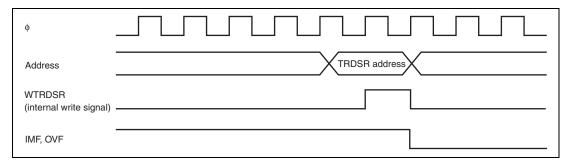

|      |         | 3 Timer RD Status Register (TRDSR)                                 |     |

|      |         | Timer RD Interrupt Enable Register (TRDIER)                        |     |

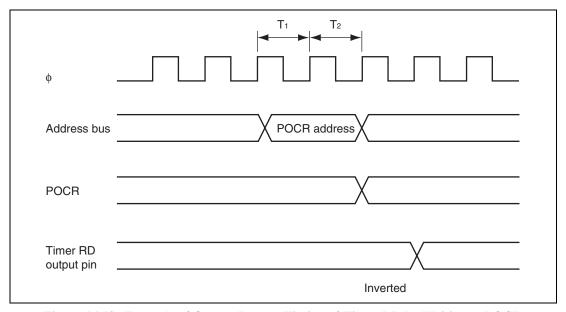

|      |         | 5 PWM Mode Output Level Control Register (POCR)                    |     |

|      |         | Timer RD Digital Filtering Function Select Register (TRDDF)        |     |

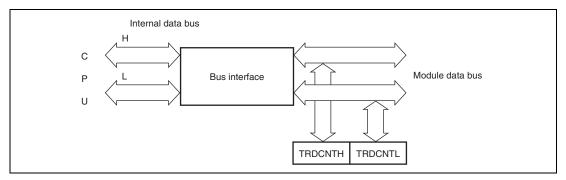

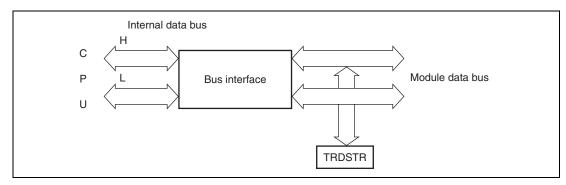

|      |         | Interface with CPU                                                 |     |

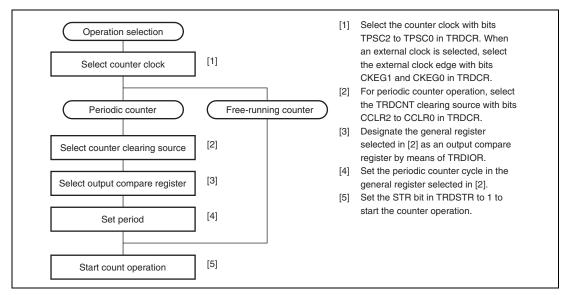

| 16.3 |         | ion                                                                |     |

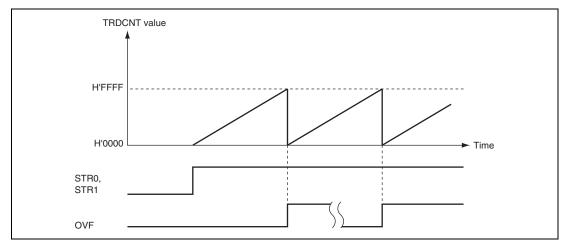

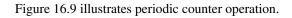

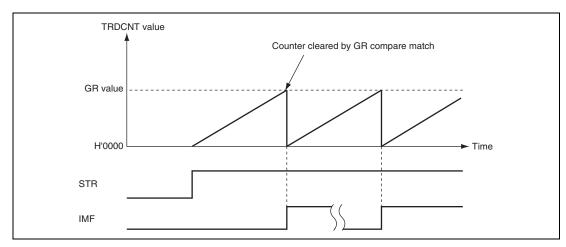

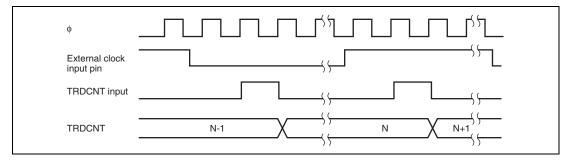

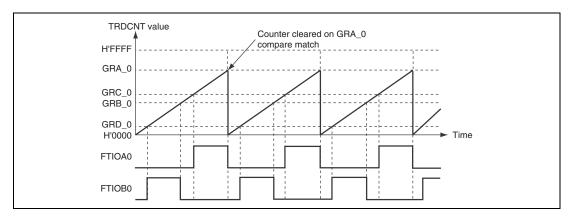

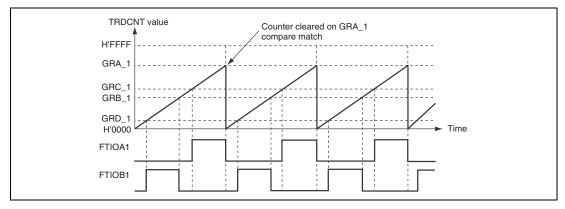

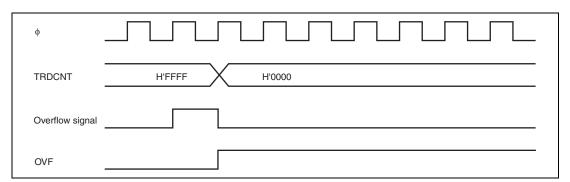

|      | -       | Counter Operation                                                  |     |

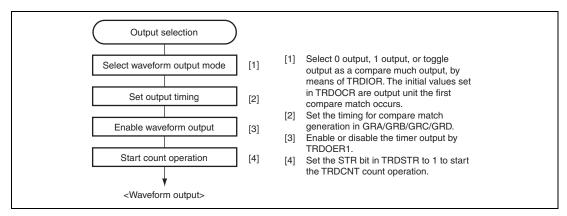

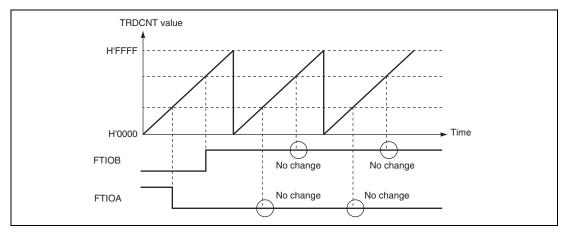

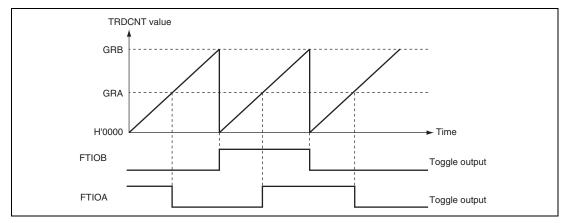

|      |         | Waveform Output by Compare Match                                   |     |

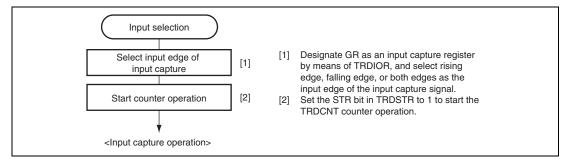

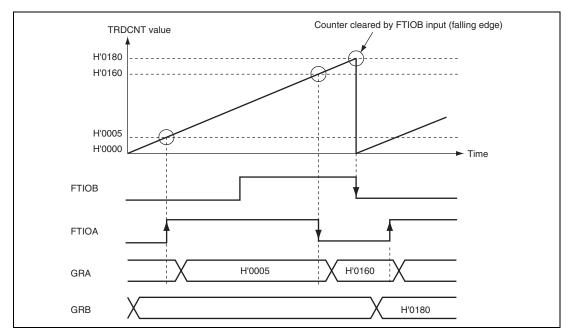

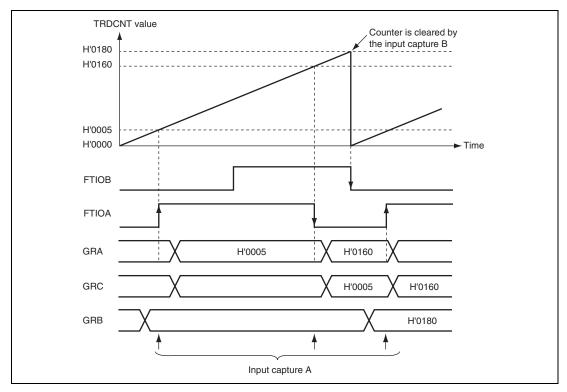

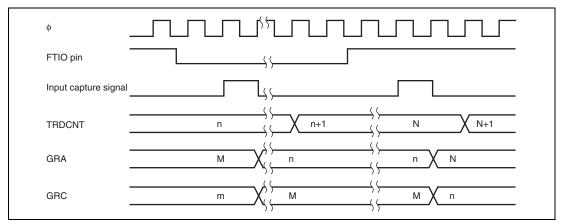

|      |         | Input Capture Function                                             |     |

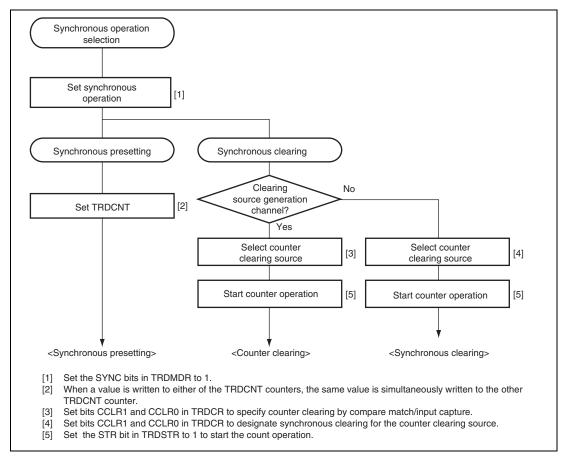

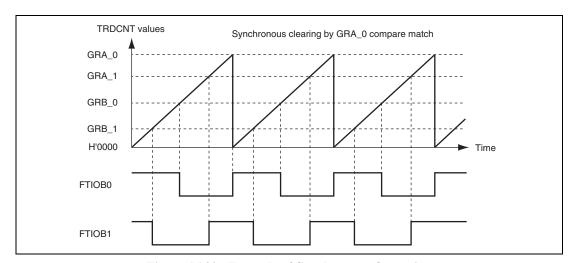

|      |         | Synchronous Operation                                              |     |

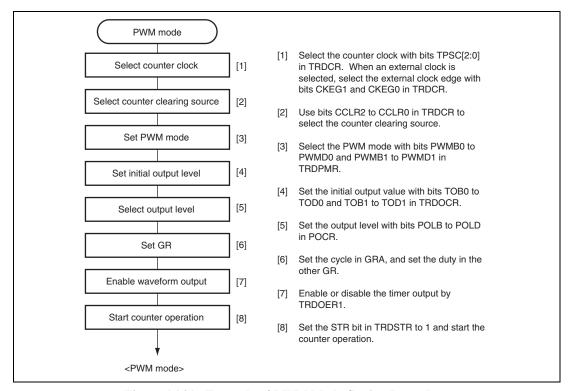

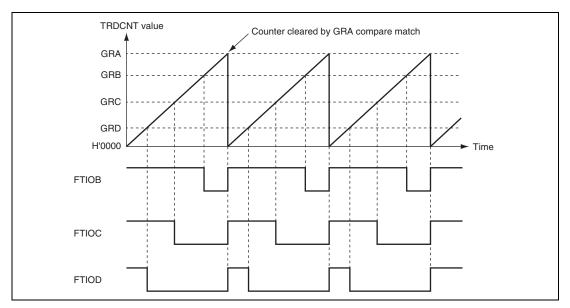

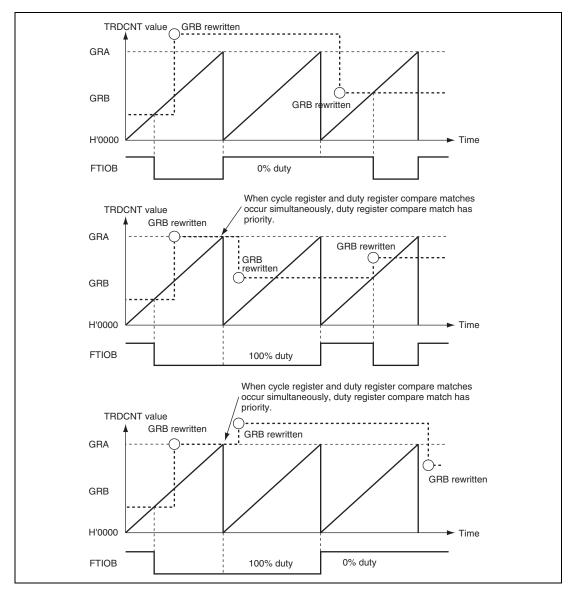

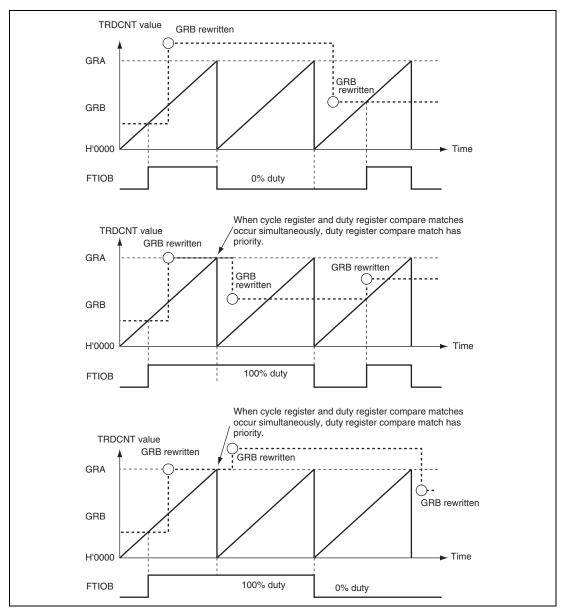

|      | 16.3.5  | PWM Mode                                                           | 615 |

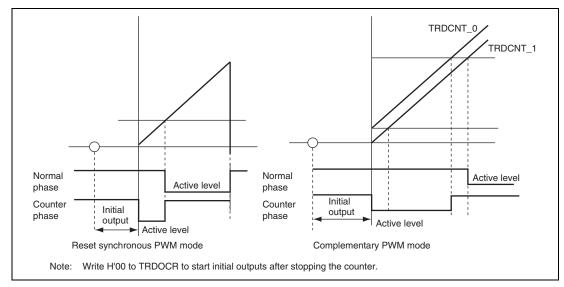

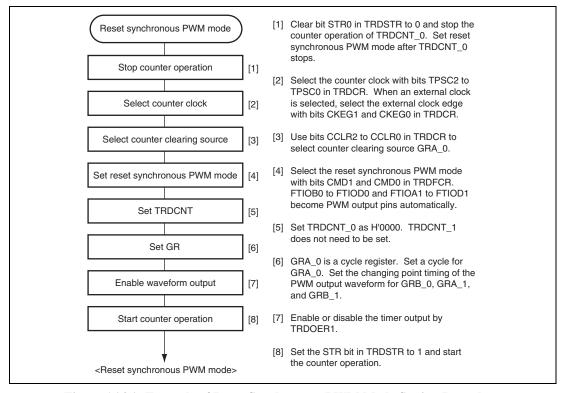

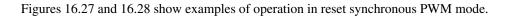

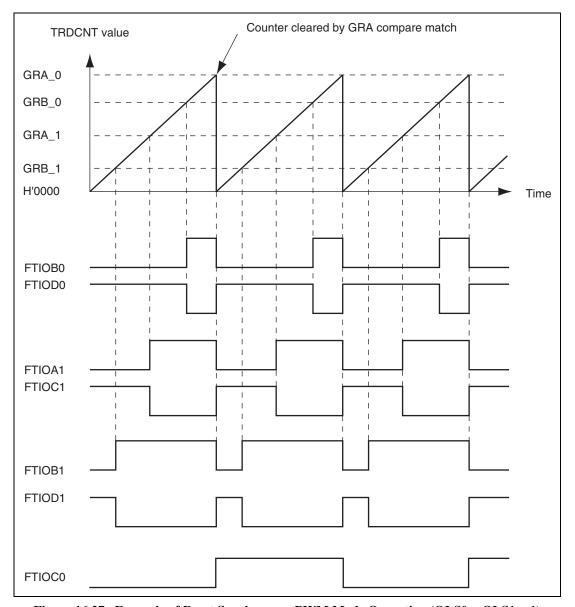

|      |         | Reset Synchronous PWM Mode                                         |     |

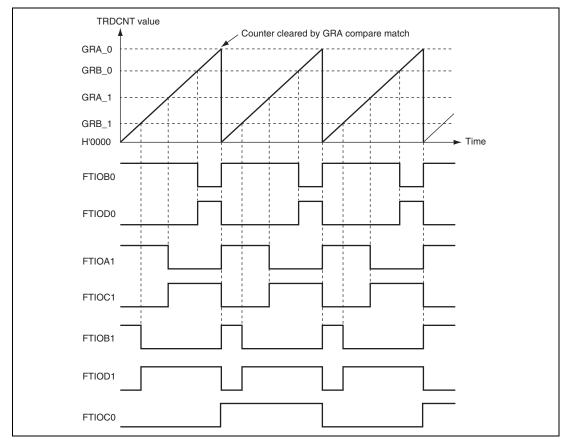

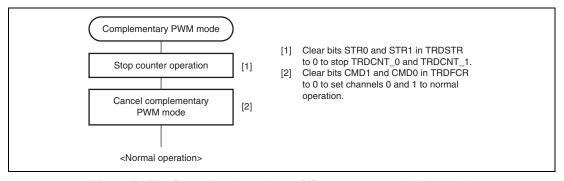

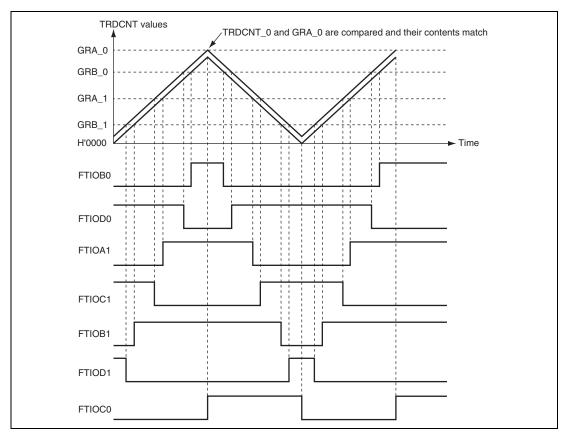

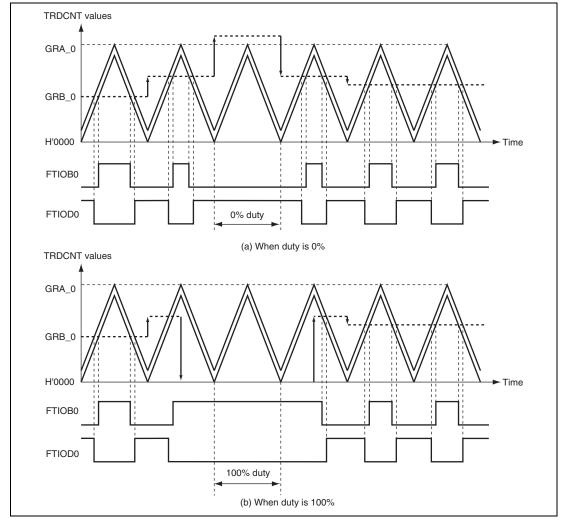

|      | 16.3.7  | Complementary PWM Mode                                             | 625 |

|      | 16.3.8  | PWM3 Mode Operation                                                | 631 |

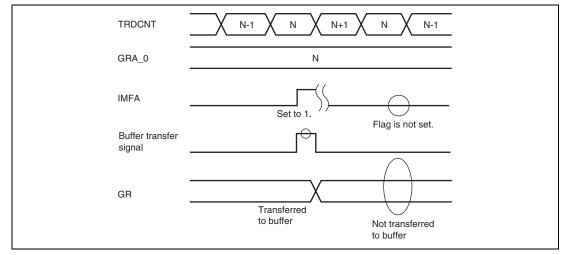

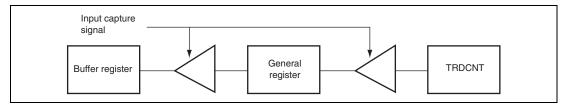

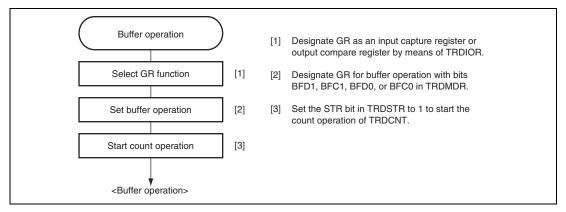

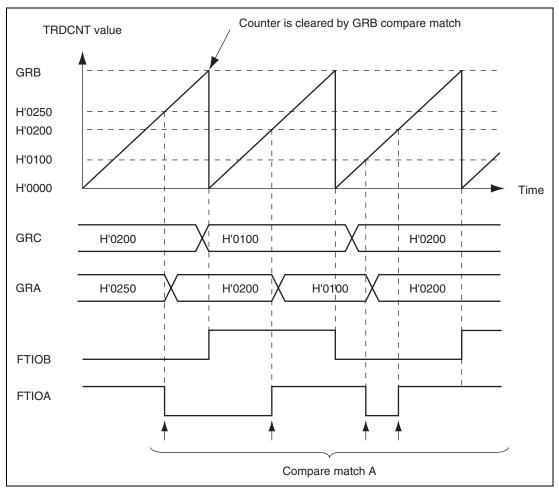

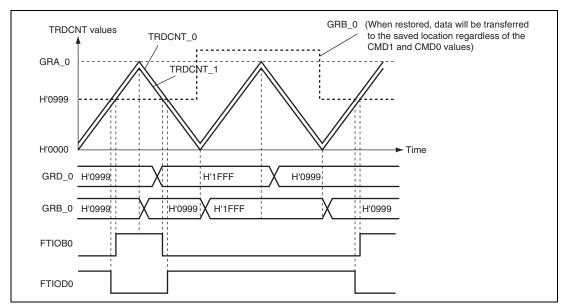

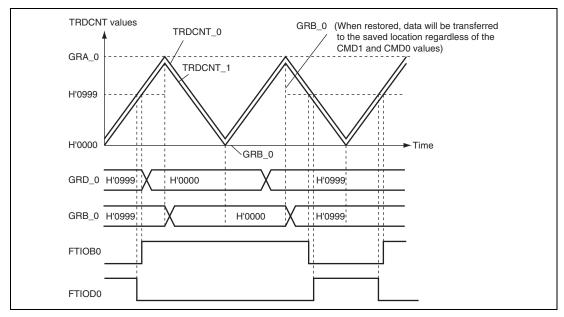

|      |         | Buffer Operation                                                   |     |

|      | 16.3.10 | Timer RD Output Timing                                             | 645 |

|      | 16.3.11 | Digital Filtering Function for Input Capture Inputs                | 648 |

|      | 16.3.12 | Prunction of Changing Output Pins for GR                           | 649 |

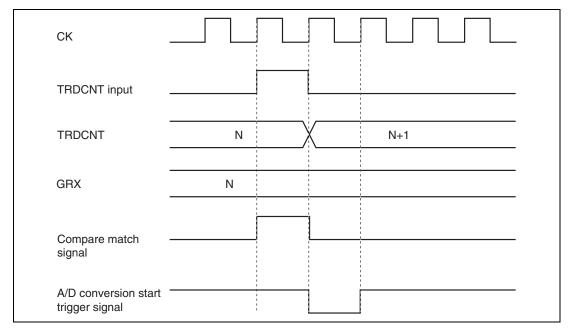

|      | 16.3.13 | A/D Conversion Start Trigger Setting Function                      | 651 |

|      | 16.3.14 | Operation through an Event Link                                    | 653 |

| 16.4 |         | pt Sources                                                         |     |

|      | 16.4.1  | Status Flag Set Timing                                             | 654 |

|      | 16.4.2  | Status Flag Clearing Timing                                        | 656 |

|------|---------|--------------------------------------------------------------------|-----|

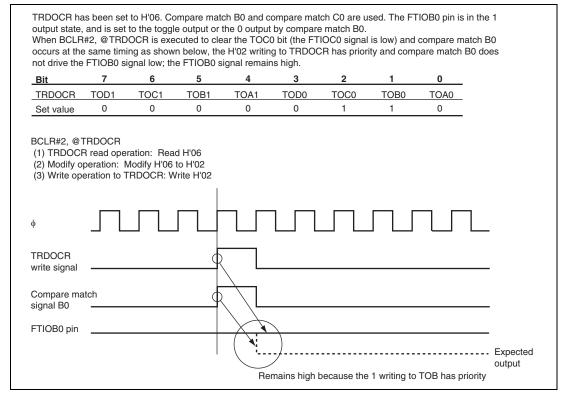

| 16.5 | Usage   | Notes                                                              | 656 |

|      |         |                                                                    |     |

| Sect | ion 17  | Timer RE                                                           | 667 |

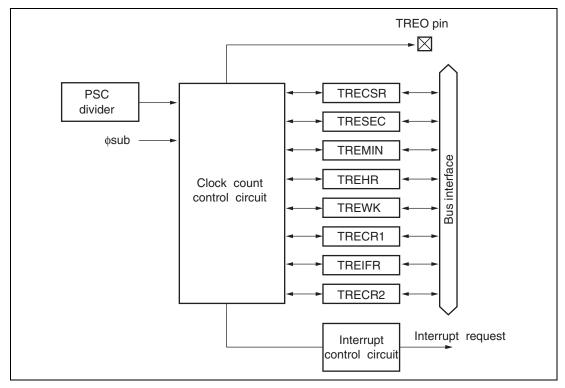

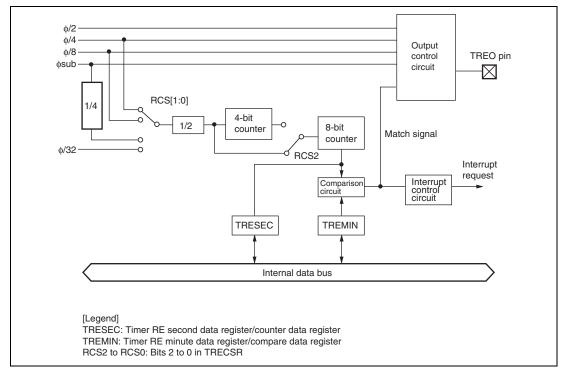

| 17.1 | Feature | es                                                                 | 667 |

| 17.2 | Registe | er Descriptions                                                    | 669 |

|      | 17.2.1  | Timer RE Second Data Register/Counter Data Register (TRESEC)       | 670 |

|      | 17.2.2  | Timer RE Minute Data Register/Compare Data Register (TREMIN)       | 671 |

|      | 17.2.3  | Timer RE Hour Data Register (TREHR)                                | 672 |

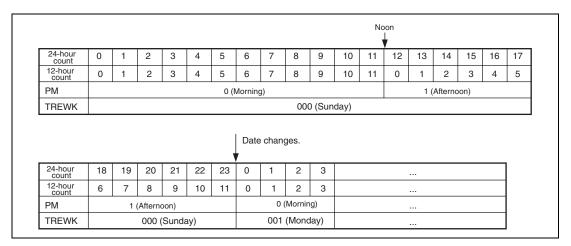

|      | 17.2.4  | Timer RE Day-of-Week Data Register (TREWK)                         | 673 |

|      | 17.2.5  | Timer RE Control Register 1 (TRECR1)                               | 674 |

|      | 17.2.6  | Timer RE Control Register 2 (TRECR2)                               | 677 |

|      | 17.2.7  | Timer RE Interrupt Flag Register (TREIFR)                          | 678 |

|      | 17.2.8  | Timer RE Clock Source Select Register (TRECSR)                     | 680 |

| 17.3 | Operat  | ion of Realtime Clock Mode                                         |     |

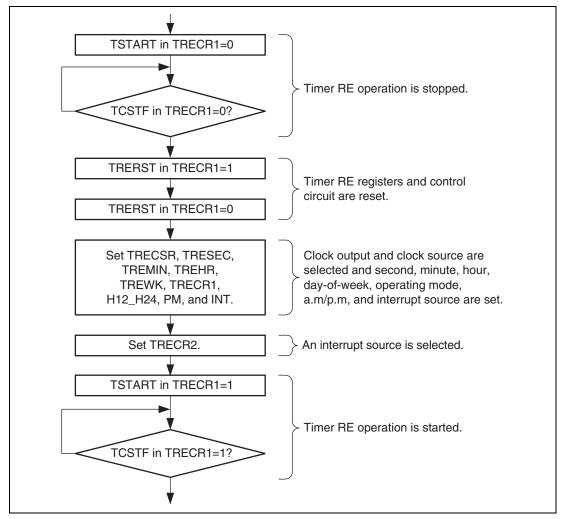

|      | 17.3.1  | Initial Settings of Registers after Power-On                       | 681 |

|      | 17.3.2  | Initial Setting Procedure                                          | 681 |

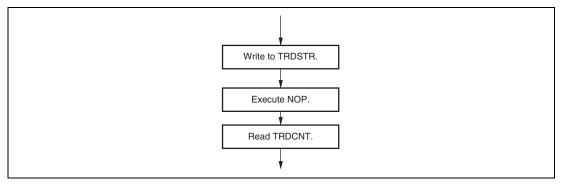

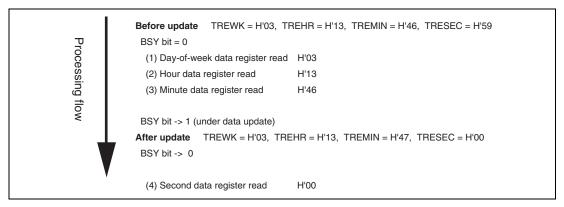

|      | 17.3.3  | Data Reading Procedure in Realtime Clock Mode                      | 683 |

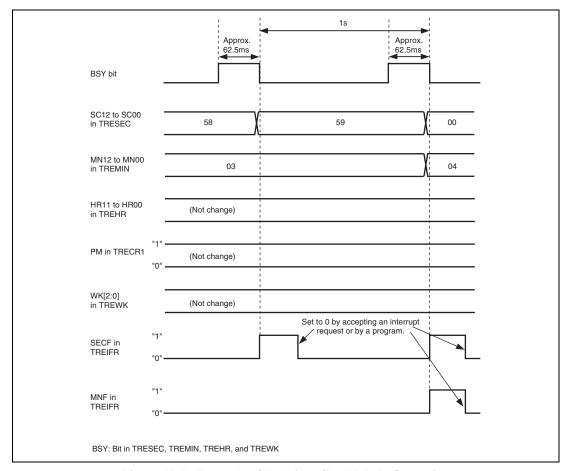

|      | 17.3.4  | Operation in Realtime Clock Mode                                   | 684 |

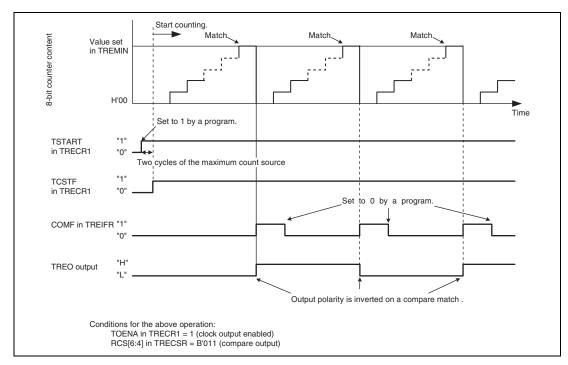

| 17.4 | Operat  | ion of Output Compare Mode                                         | 685 |

| 17.5 | Interru | pt Sources                                                         | 688 |

| 17.6 | Usage   | Notes                                                              | 689 |

|      |         |                                                                    |     |

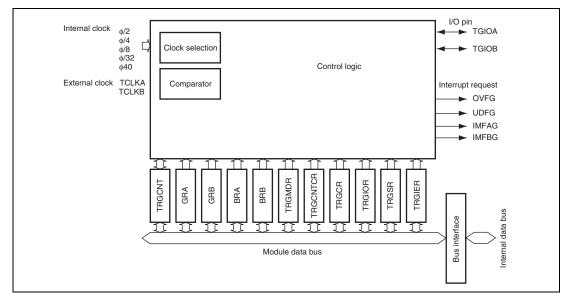

| Sect |         | Timer RG                                                           |     |

| 18.1 |         | es                                                                 |     |

| 18.2 | Registe | er Descriptions                                                    |     |

|      | 18.2.1  | Timer RG Mode Register (TRGMDR)                                    |     |

|      | 18.2.2  |                                                                    |     |

|      | 18.2.3  |                                                                    |     |

|      | 18.2.4  |                                                                    |     |

|      | 18.2.5  | Timer RG Status Register (TRGSR)                                   |     |

|      | 18.2.6  | Timer RG Interrupt Enable Register (TRGIER)                        | 701 |

|      | 18.2.7  | Timer RG Counter (TRGCNT)                                          | 702 |

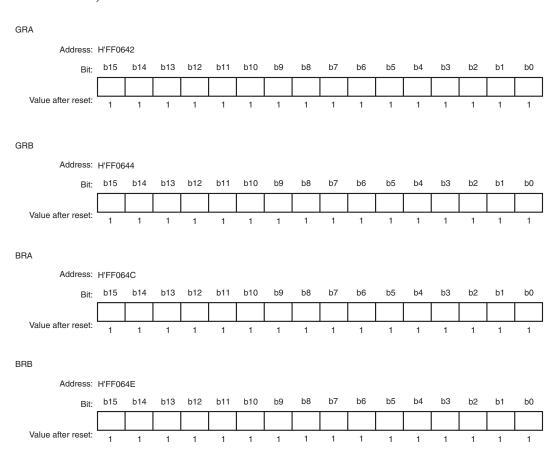

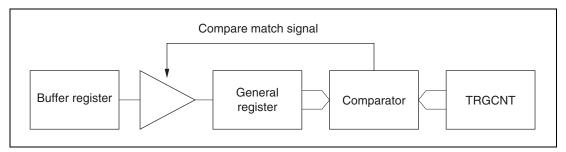

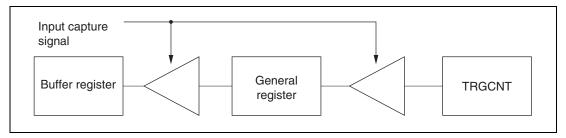

|      | 18.2.8  | General Registers A and B (GRA, GRB), GRA and GRB Buffer Registers |     |

|      |         | (BRA, BRB)                                                         |     |

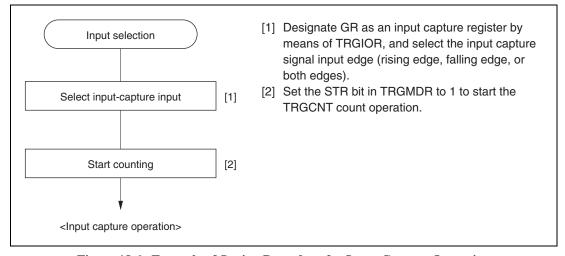

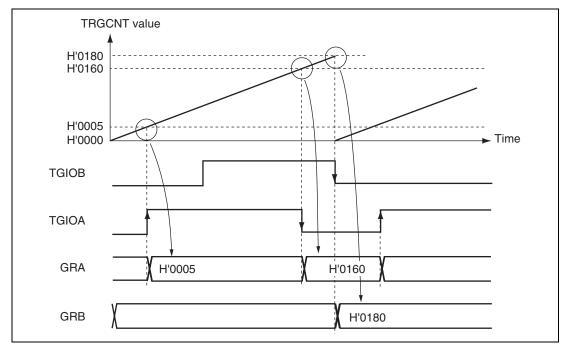

| 18.3 | Operat  | ion                                                                |     |

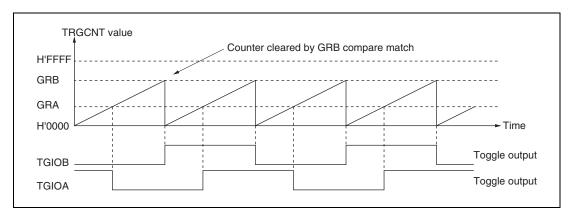

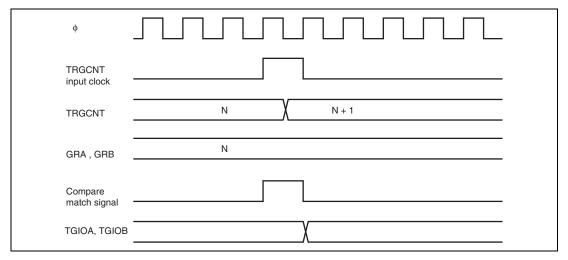

|      | 18.3.1  | Timer Mode                                                         |     |

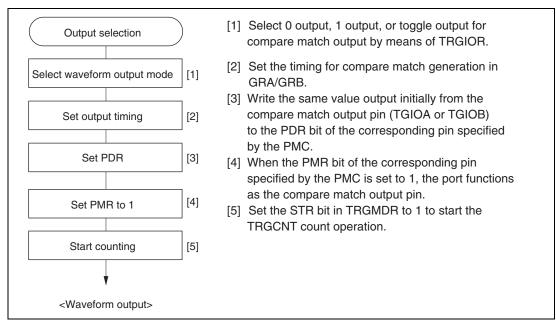

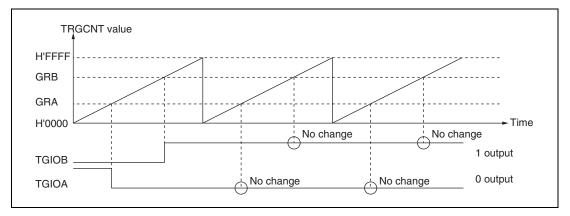

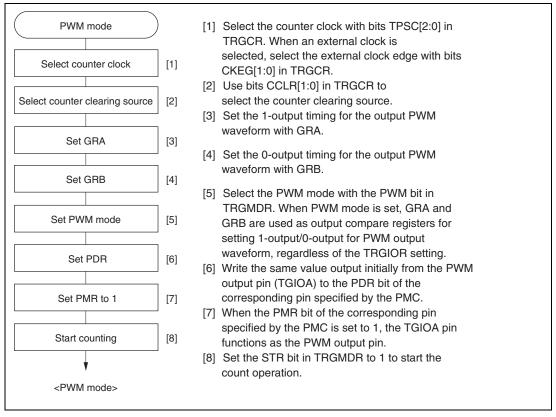

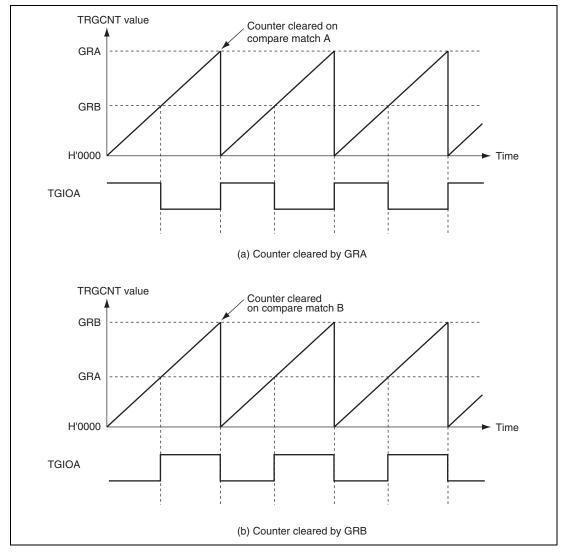

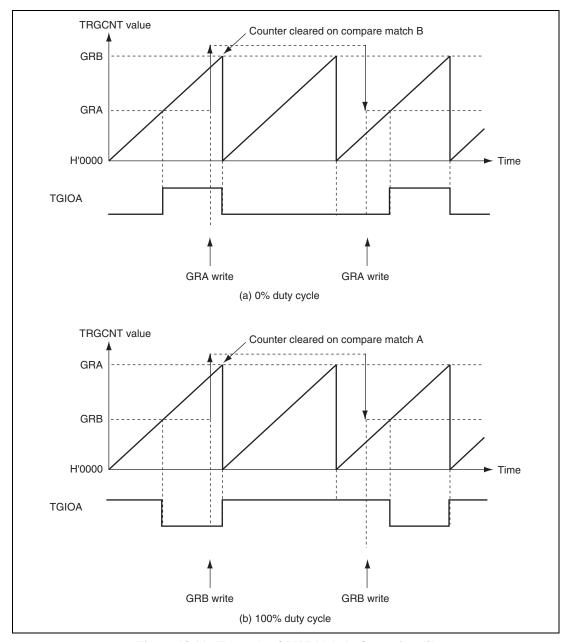

|      |         | PWM Mode                                                           |     |

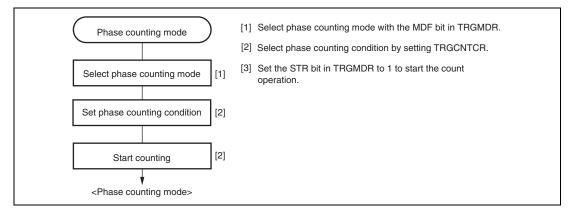

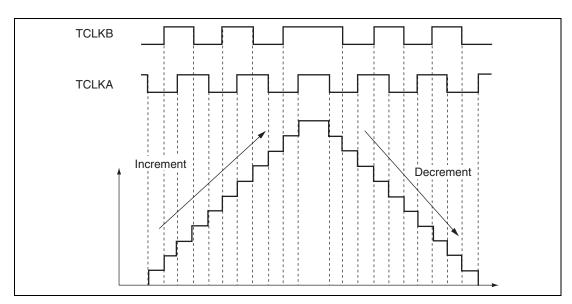

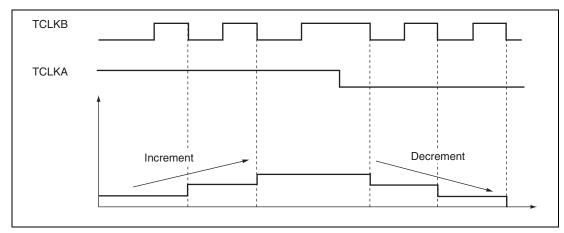

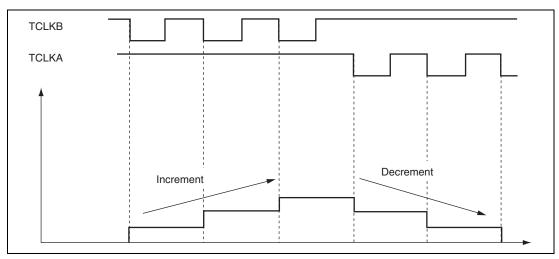

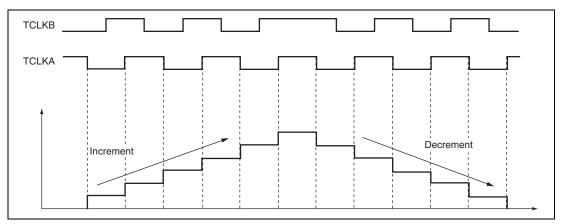

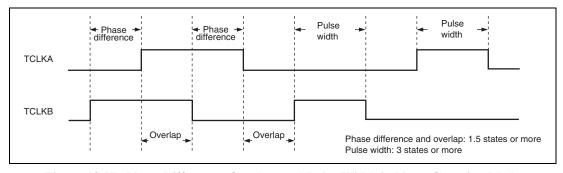

|      | 18.3.3  | Phase Counting Mode                                                | 717 |

|      | 18.3.4  | Buffer Operation                                                   | 722 |

|       | 18.3.5  | Operation through an Event Link                                            | 725 |

|-------|---------|----------------------------------------------------------------------------|-----|

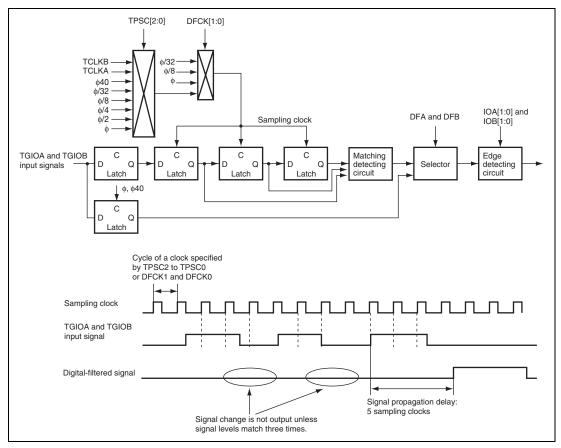

|       | 18.3.6  | Digital Filtering Function for Input Capture Inputs                        | 726 |

| 18.4  | Usage   | Note                                                                       | 727 |

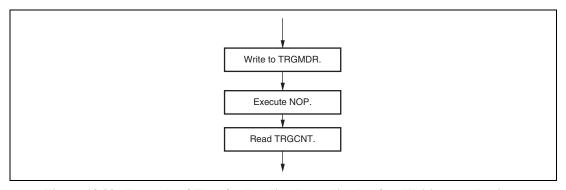

|       | 18.4.1  | Restrictions on Access to Registers when Internal φ40 Clock is Selected as |     |

|       |         | Counter Clock                                                              | 727 |

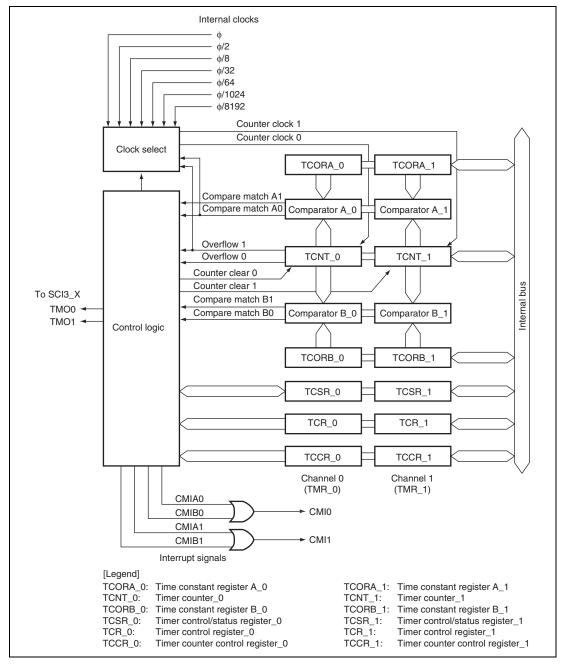

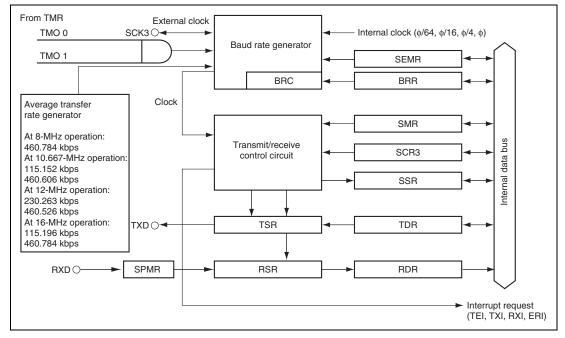

| Secti | ion 19  | 8-Bit Timers (TMR)                                                         | 729 |

| 19.1  |         | 28                                                                         |     |

| 19.2  | Registe | er Descriptions                                                            | 731 |

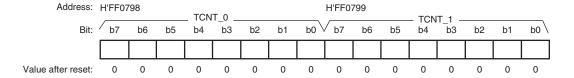

|       | 19.2.1  | Timer Counter (TCNT)                                                       | 732 |

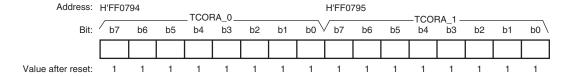

|       | 19.2.2  | Time Constant Register A (TCORA)                                           | 732 |

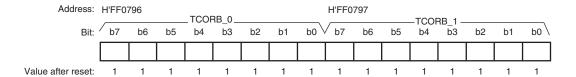

|       | 19.2.3  | Time Constant Register B (TCORB)                                           | 733 |

|       | 19.2.4  | Timer Control Register (TCR)                                               | 734 |

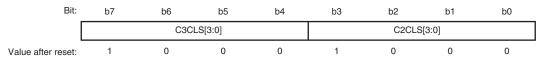

|       | 19.2.5  | Timer Counter Control Register (TCCR)                                      | 735 |

|       | 19.2.6  | Timer Control/Status Register (TCSR)                                       | 737 |

| 19.3  | Operat  | ion Timing                                                                 | 740 |

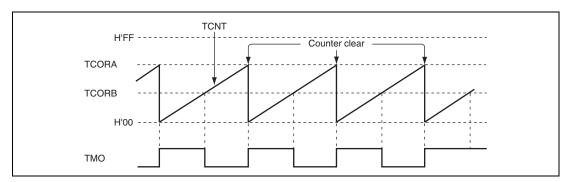

|       | 19.3.1  | Pulse Output                                                               | 740 |

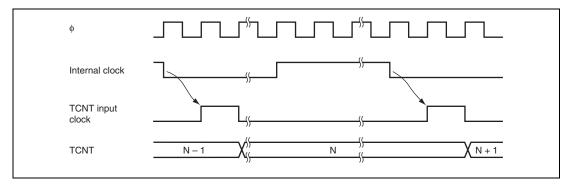

|       | 19.3.2  | TCNT Count Timing                                                          | 741 |

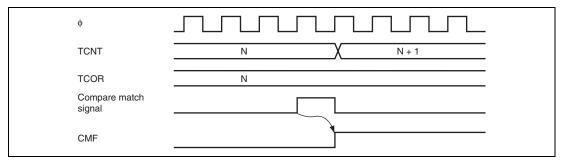

|       | 19.3.3  | Timing of CMFA and CMFB Setting at Compare Match                           | 742 |

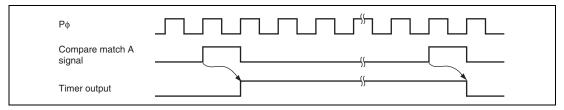

|       | 19.3.4  | Timing of Timer Output at Compare Match                                    | 743 |

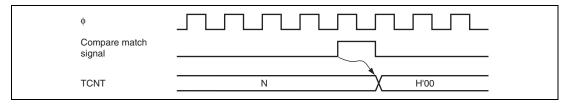

|       | 19.3.5  | Timing of Counter Clear by Compare Match                                   | 744 |

| 19.4  | Operat  | ion with Cascaded Connection                                               | 745 |

|       | 19.4.1  | 16-Bit Count Mode                                                          | 745 |

|       | 19.4.2  | Compare Match Count Mode                                                   | 745 |

| 19.5  | Interru | pt Sources                                                                 | 746 |

|       | 19.5.1  | Interrupt Sources and DTC Activation                                       | 746 |

| 19.6  | Usage   | Notes                                                                      | 747 |

|       | 19.6.1  | Notes on Setting Cycle                                                     | 747 |

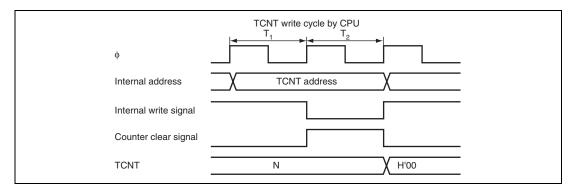

|       | 19.6.2  | Conflict between TCNT Write and Counter Clear                              | 747 |

|       | 19.6.3  | Conflict between TCNT Write and Increment                                  | 748 |

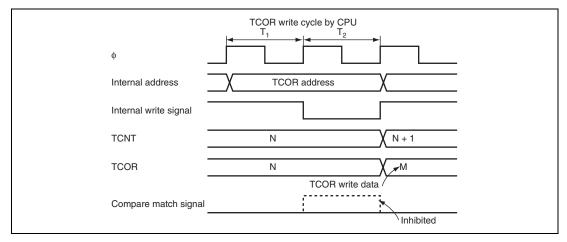

|       | 19.6.4  | Conflict between TCOR Write and Compare Match                              | 748 |

|       | 19.6.5  | Conflict between Compare Matches A and B                                   | 749 |

|       | 19.6.6  | Switching of Internal Clocks and TCNT Operation                            | 749 |

|       | 19.6.7  | Mode Setting with Cascaded Connection                                      | 751 |

|       | 19.6.8  | Module Standby Function Setting                                            | 751 |

|       | 19.6.9  | Interrupts in Module Standby State                                         | 751 |

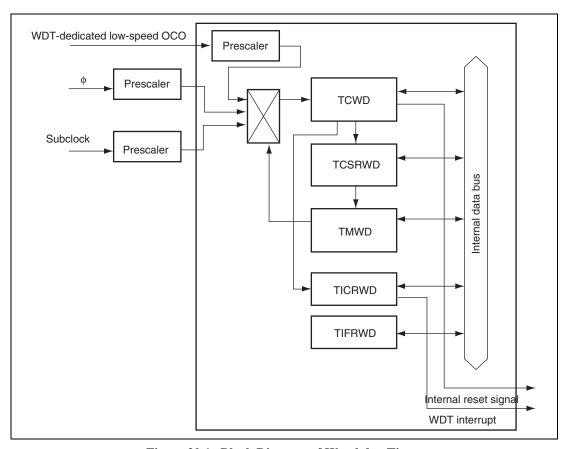

| Secti | ion 20  | Watchdog Timer (WDT)                                                       | 753 |

| 20.1  | Feature | es                                                                         | 754 |

| 20.2  | Registe | er Descriptions                                                            | 755 |

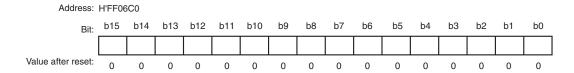

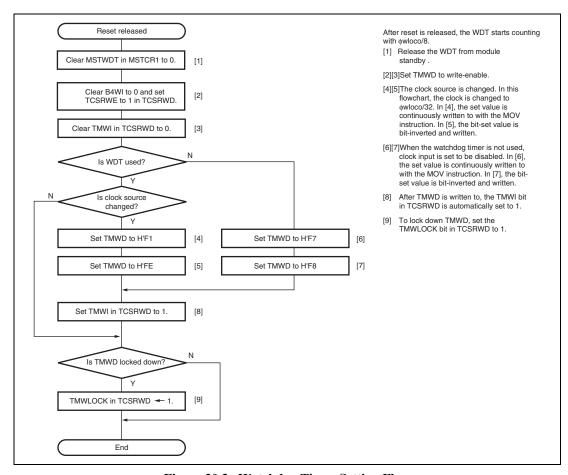

|      | 20.2.1  | Timer Control/Status Register WD (TCSRWD)                          | 755 |

|------|---------|--------------------------------------------------------------------|-----|

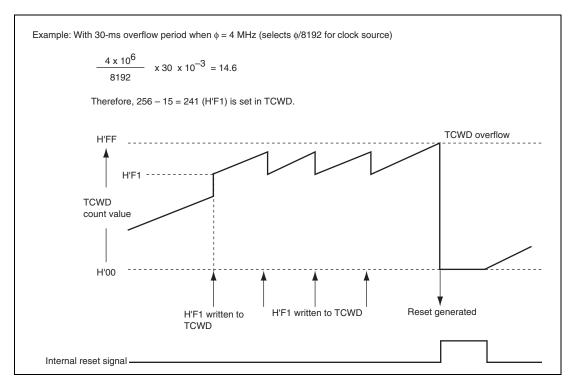

|      | 20.2.2  | Timer Counter WD (TCWD)                                            | 756 |

|      | 20.2.3  | Timer Mode Register WD (TMWD)                                      | 757 |

|      | 20.2.4  | Timer Interrupt Control Register WD (TICRWD)                       | 758 |

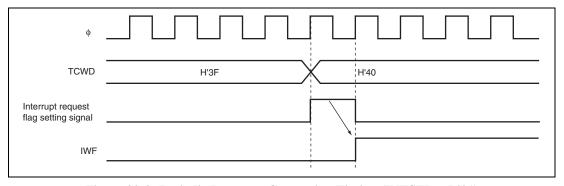

|      | 20.2.5  | Timer Interrupt Flag Register WD (TIFRWD)                          | 759 |

| 20.3 | Operat  | ion                                                                |     |

|      | 20.3.1  | Watchdog Timer Overflow Reset                                      | 760 |

|      | 20.3.2  | Watchdog Timer Setting Flow                                        | 761 |

|      | 20.3.3  | Watchdog Timer Periodic Interrupt                                  | 762 |

| 20.4 | Usage   | Notes                                                              | 763 |

|      | 20.4.1  | Notes on System Design                                             | 763 |

|      | 20.4.2  | Notes on Stopping the Watchdog Timer or Switching the Clock Source | 763 |

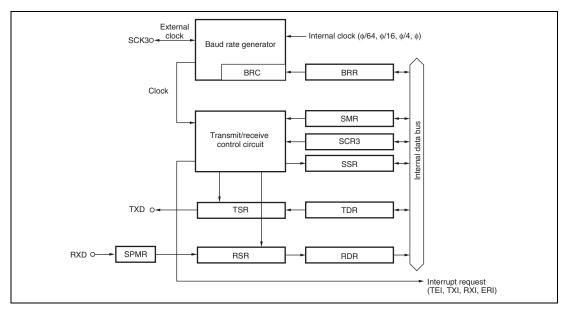

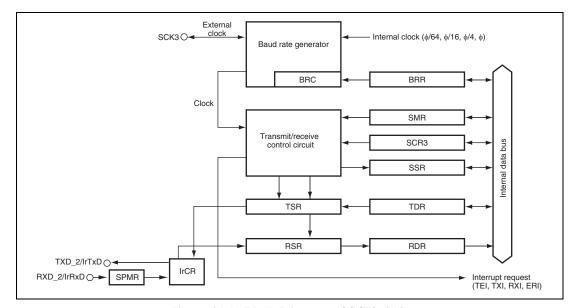

| Sect | ion 21  | Serial Communication Interface 3 (SCI3, IrDA)                      | 765 |

| 21.1 | Feature | es                                                                 | 765 |

| 21.2 | Registe | er Descriptions                                                    | 770 |

|      | 21.2.1  | Receive Shift Register (RSR)                                       | 771 |

|      | 21.2.2  | Receive Data Register (RDR)                                        | 771 |

|      | 21.2.3  | Transmit Shift Register (TSR)                                      | 771 |

|      | 21.2.4  | Transmit Data Register (TDR)                                       | 772 |

|      | 21.2.5  | Serial Mode Register (SMR)                                         | 772 |

|      | 21.2.6  | Serial Control Register 3 (SCR3)                                   | 774 |

|      | 21.2.7  | Serial Status Register (SSR)                                       | 776 |

|      | 21.2.8  | Bit Rate Register (BRR)                                            | 778 |

|      | 21.2.9  | Sampling Mode Register (SPMR)                                      | 783 |

|      | 21.2.10 | ) IrDA Control Register (IrCR)                                     | 783 |

|      | 21.2.11 | Serial Extended Mode Register (SEMR)                               | 785 |

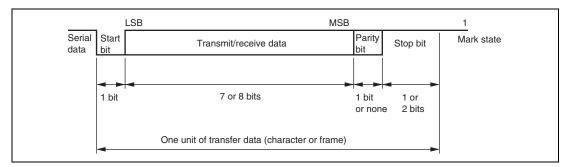

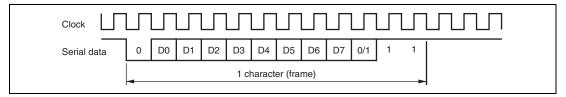

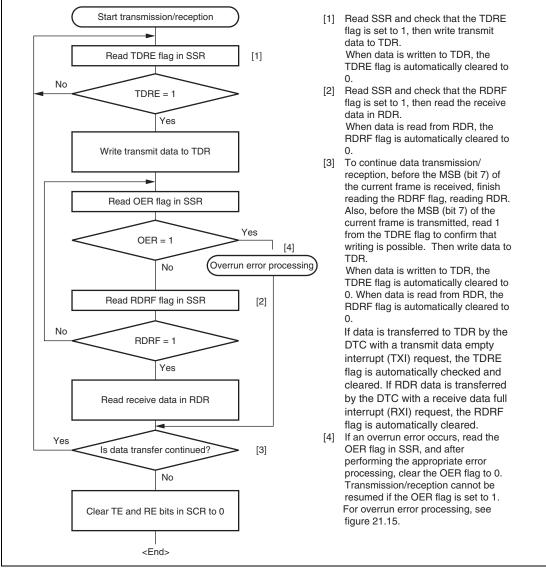

| 21.3 | Operat  | ion in Asynchronous Mode                                           | 791 |

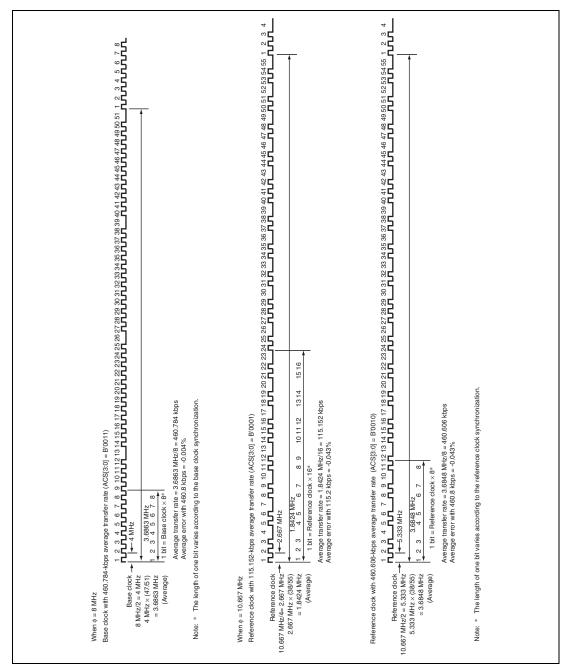

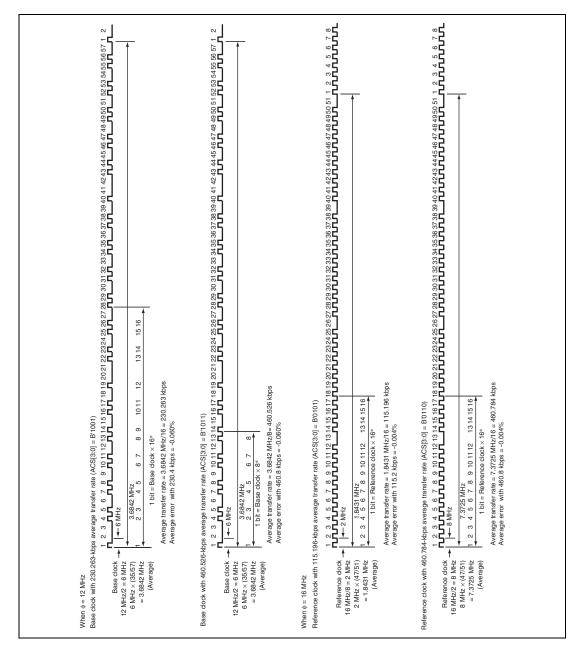

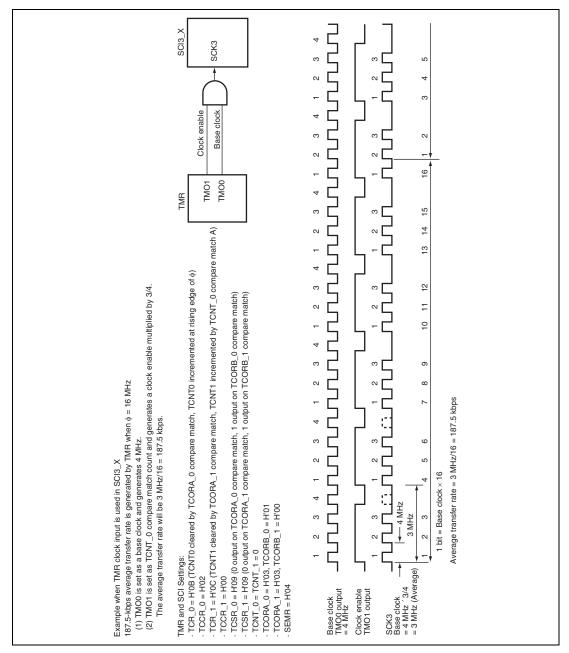

|      | 21.3.1  | Clock                                                              | 791 |

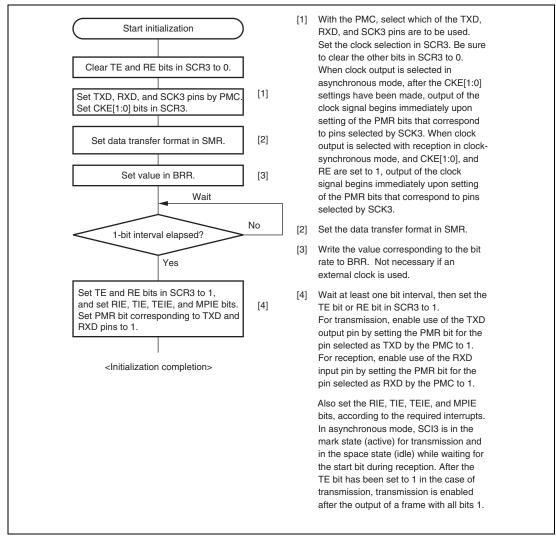

|      | 21.3.2  | SCI3 Initialization                                                | 793 |

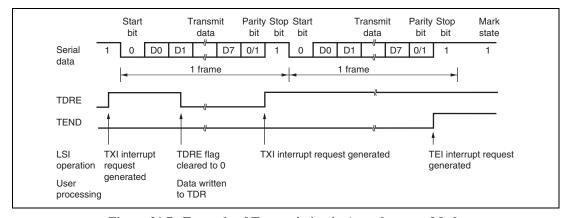

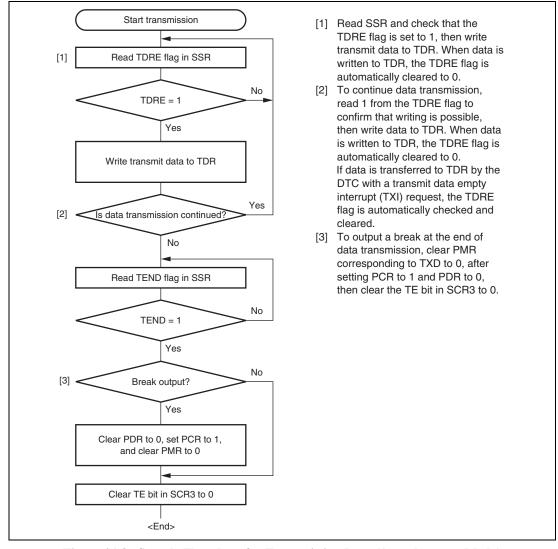

|      | 21.3.3  | Data Transmission                                                  | 794 |

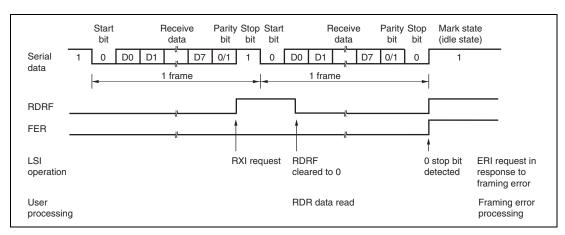

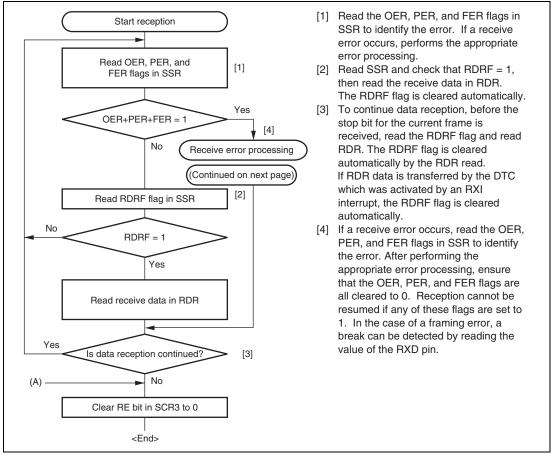

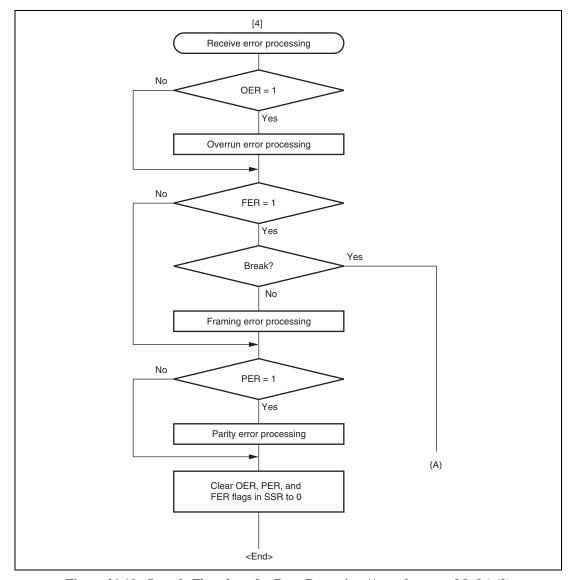

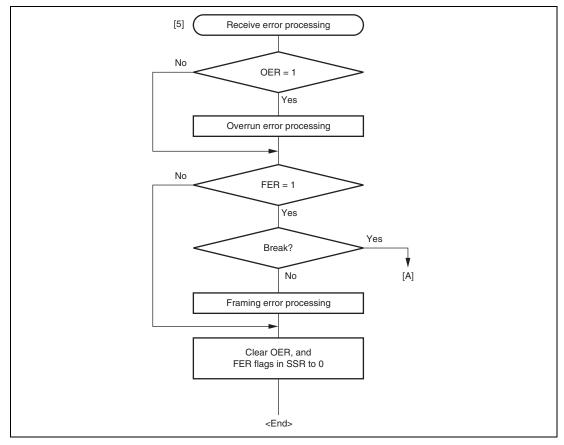

|      | 21.3.4  | Data Reception                                                     | 796 |

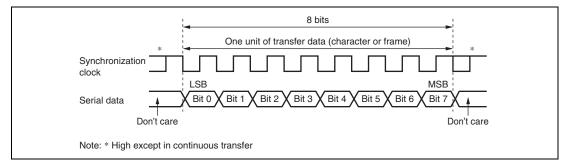

| 21.4 |         | ion in Clocked Synchronous Mode                                    |     |

|      | 21.4.1  | Clock                                                              | 800 |

|      | 21.4.2  | SCI3 Initialization                                                | 800 |

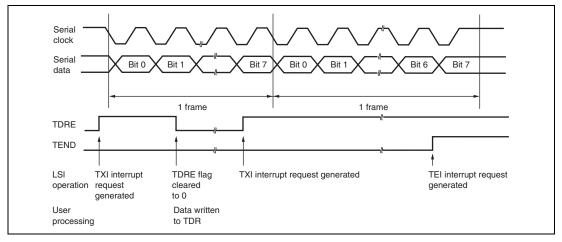

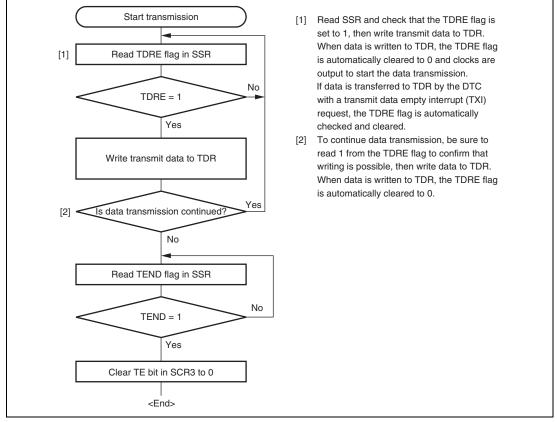

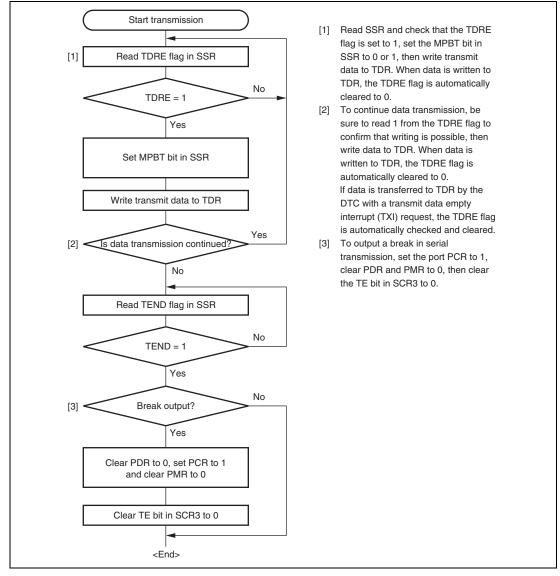

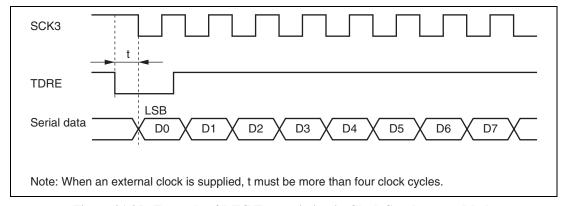

|      | 21.4.3  | Data Transmission                                                  | 801 |

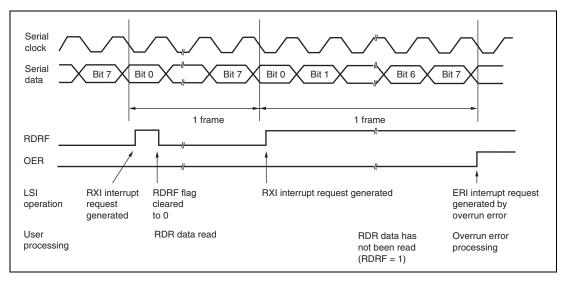

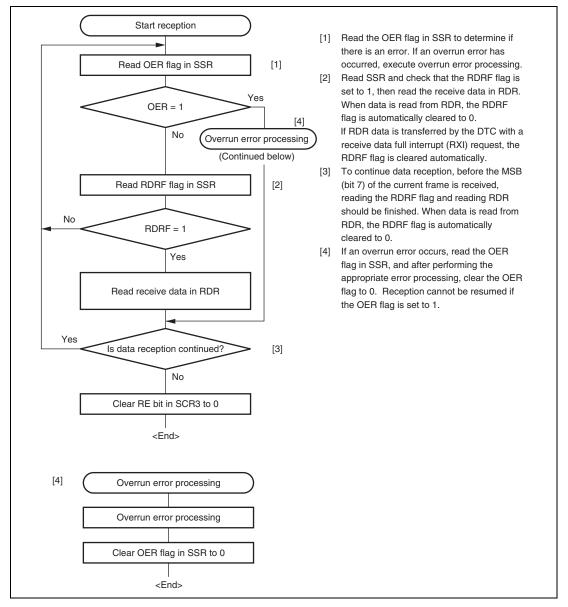

|      | 21.4.4  | Data Reception (Clocked Synchronous Mode)                          | 803 |

|      | 21.4.5  | Simultaneous Data Transmission and Reception                       | 805 |

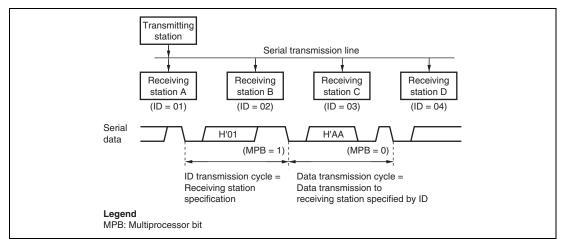

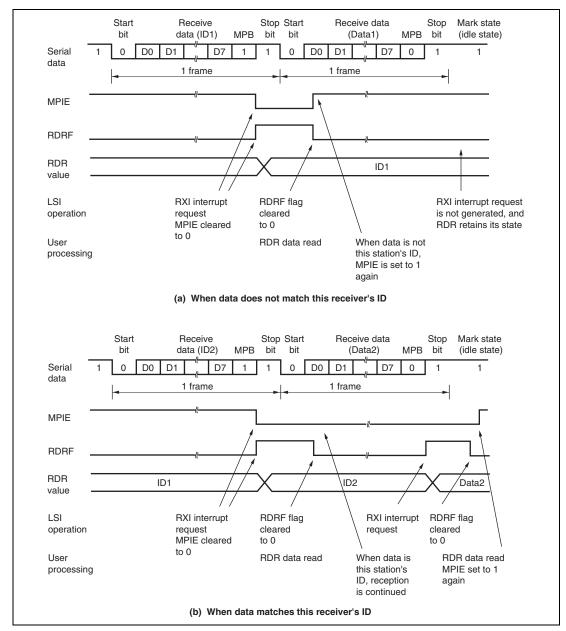

| 21.5 | Multip  | rocessor Communication Function                                    | 807 |

|      | 21.5.1  | Multiprocessor Data Transmission                                   | 808 |

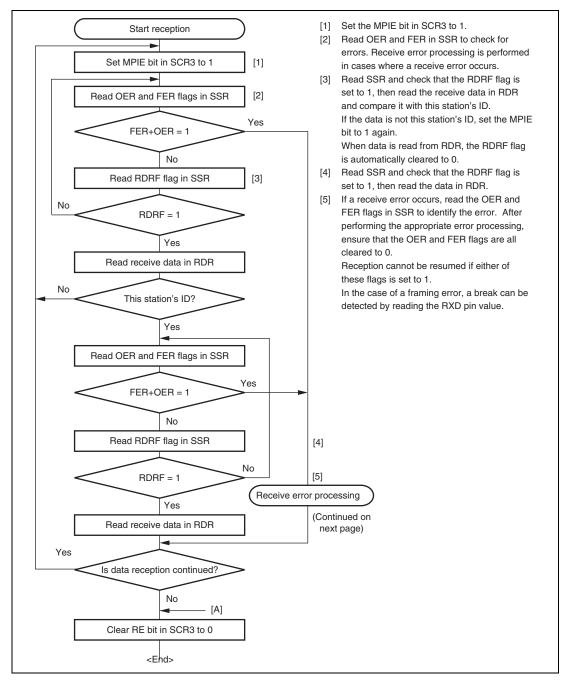

|       | 21.5.2                | Multiprocessor Data Reception.                                         | 810 |

|-------|-----------------------|------------------------------------------------------------------------|-----|

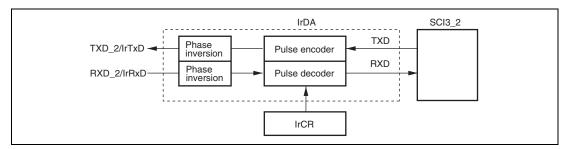

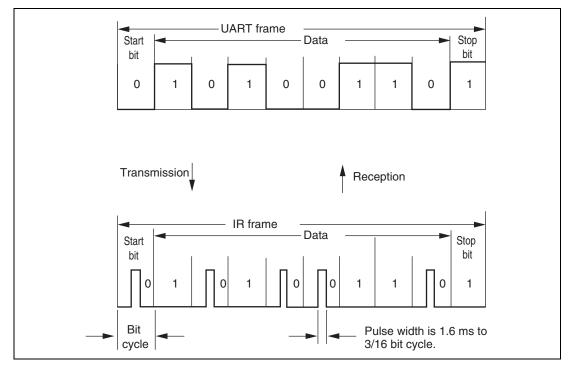

| 21.6  | IrDA O                | peration                                                               | 814 |

|       | 21.6.1                | Transmission                                                           | 815 |

|       | 21.6.2                | Reception                                                              | 815 |

|       | 21.6.3                | High-Level Pulse Width Selection                                       | 816 |

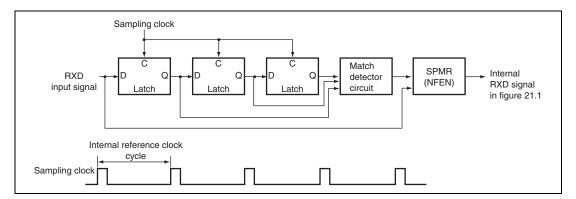

| 21.7  | Noise C               | Canceler                                                               | 817 |

| 21.8  | Interrup              | t Requests                                                             | 818 |

| 21.9  | Usage N               | Notes                                                                  | 819 |

|       | 21.9.1                | Break Detection and Processing                                         | 819 |

|       | 21.9.2                | Mark State and Break Sending                                           | 819 |

|       | 21.9.3                | Receive Error Flags and Transmit Operations                            |     |

|       |                       | (Clocked Synchronous Mode Only)                                        | 819 |

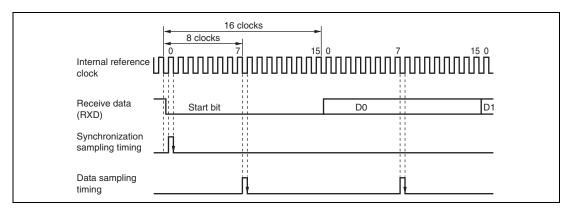

|       | 21.9.4                | Receive Data Sampling Timing and Reception Margin in Asynchronous Mode | 820 |

|       | 21.9.5                | Relation between Writes to TDR and TDRE Flag                           |     |

|       |                       | Restrictions on Using DTC                                              |     |

|       | 21.7.0                | Restrictions on Using DTC                                              | 021 |

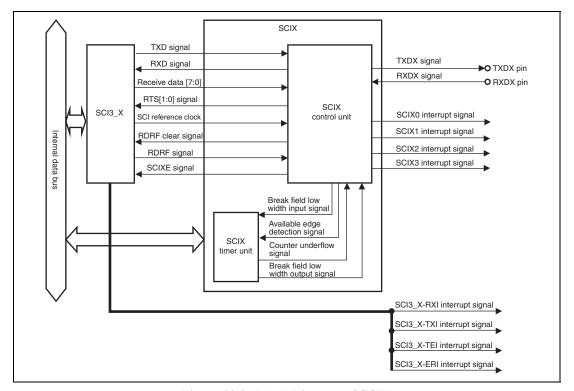

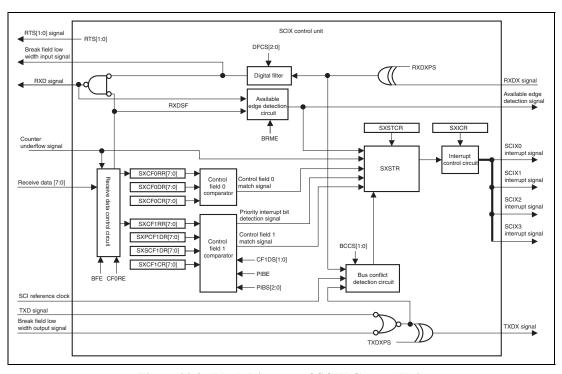

| Secti | ion 22                | Serial Communication Interface X                                       | 823 |

| 22.1  | Overvie               | ·w                                                                     | 823 |

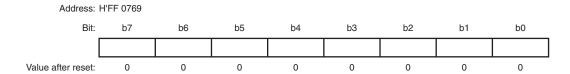

| 22.2  | Register Descriptions |                                                                        |     |

|       | 22.2.1                | SCIX Module Enable Register (SXMER)                                    | 828 |

|       | 22.2.2                | SCIX Control Register 0 (SXCR0)                                        | 829 |

|       | 22.2.3                | SCIX Control Register 1 (SXCR1)                                        | 830 |

|       | 22.2.4                | SCIX Control Register 2 (SXCR2)                                        | 832 |

|       | 22.2.5                | SCIX Control Register 3 (SXCR3)                                        | 833 |

|       | 22.2.6                | SCIX Port Control Register (SXPCR)                                     | 833 |

|       | 22.2.7                | SCIX Interrupt Control Register (SXICR)                                | 835 |

|       | 22.2.8                | SCIX Status Register (SXSTR)                                           | 836 |

|       | 22.2.9                | SCIX Status Clear Register (SXSTCR)                                    | 838 |

|       | 22.2.10               | SCIX Control Field 0 Data Register (SXCF0DR)                           | 839 |

|       | 22.2.11               | SCIX Control Field 0 Compare Enable Register (SXCF0CR)                 | 839 |

|       | 22.2.12               | SCIX Control Field 0 Receive Data Register (SXCF0RR)                   | 840 |

|       | 22.2.13               | SCIX Primary Control Field 1 Data Register (SXPCF1DR)                  | 840 |

|       | 22.2.14               | SCIX Secondary Control Field 1 Data Register (SXSCF1DR)                | 840 |

|       | 22.2.15               | SCIX Control Field 1 Compare Enable Register (SXCF1CR)                 | 841 |

|       | 22.2.16               | SCIX Control Field 1 Receive Data Register (SXCF1RR)                   | 842 |

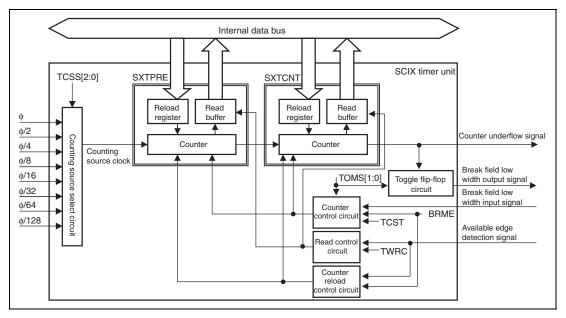

|       | 22.2.17               | SCIX Timer Control Register (SXTCR)                                    | 842 |

|       | 22.2.18               | SCIX Timer Mode Register (SXTMR)                                       | 843 |

|       | 22.2.19               | SCIX Timer Prescaler Register (SXTPRE)                                 | 844 |

|       | 22.2.20               | SCIX Timer Count Register (SXTCNT)                                     | 844 |

|       |                       |                                                                        |     |

| 22.3  | Operat  | ion                                                                      | 845 |

|-------|---------|--------------------------------------------------------------------------|-----|

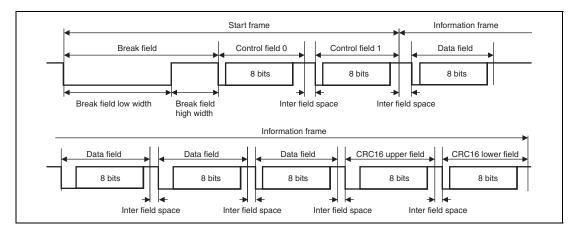

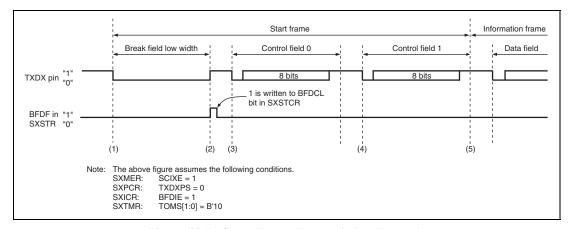

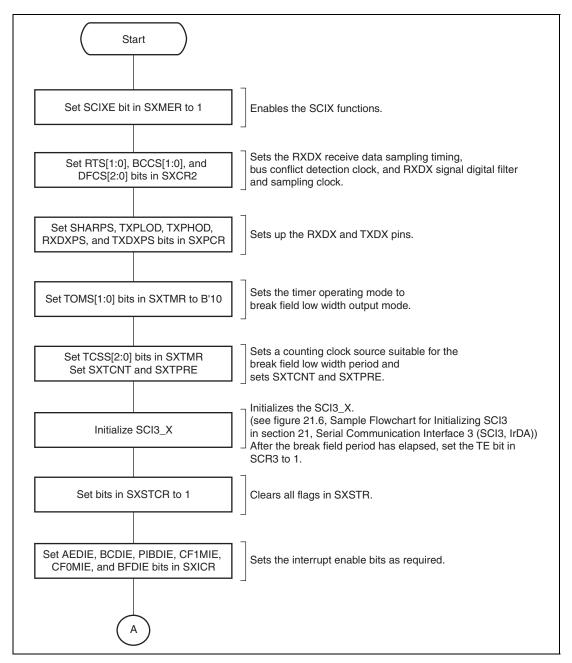

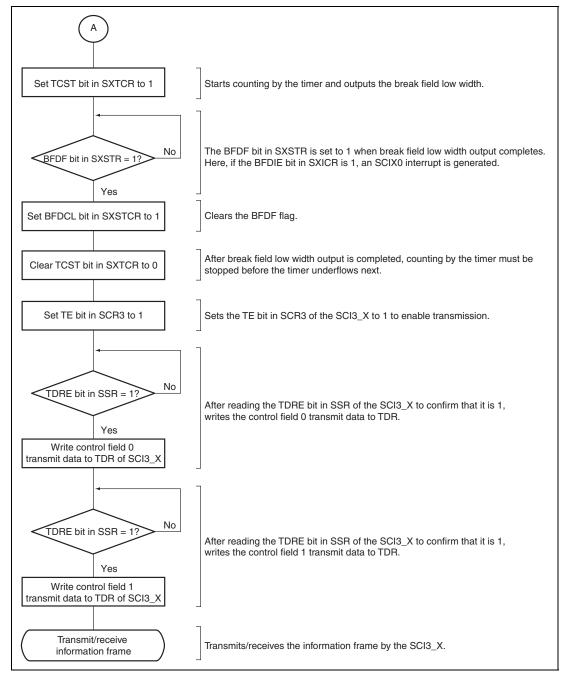

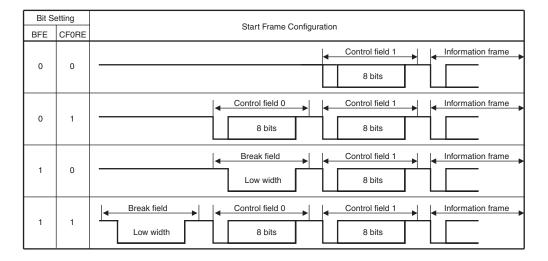

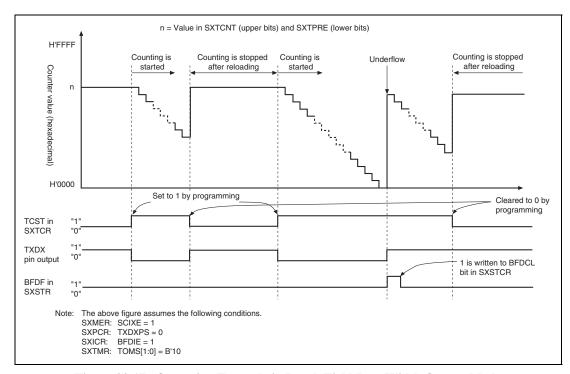

|       | 22.3.1  | Start Frame Transmission                                                 | 845 |

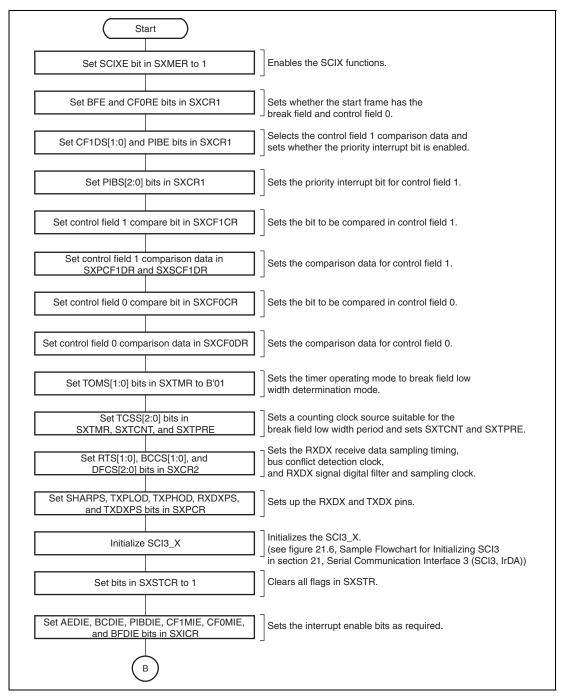

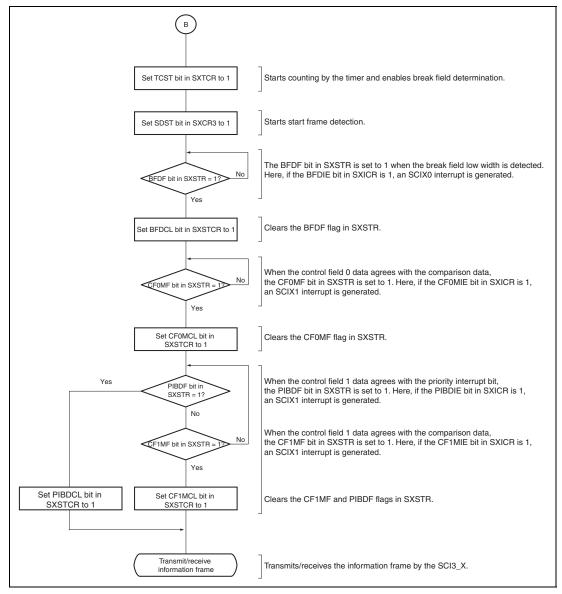

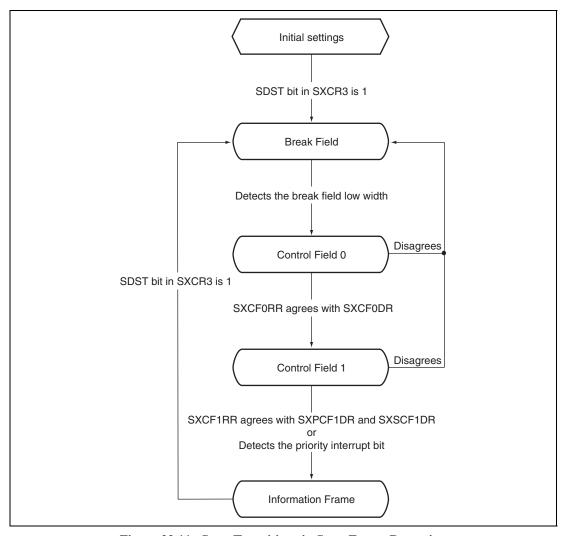

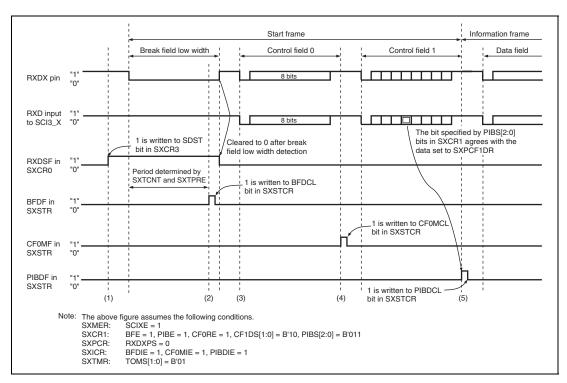

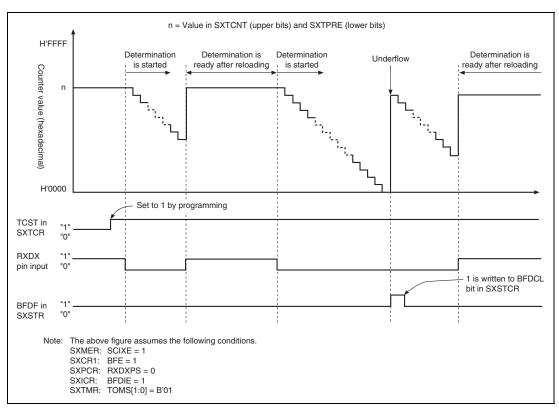

|       | 22.3.2  | Start Frame Reception                                                    | 849 |

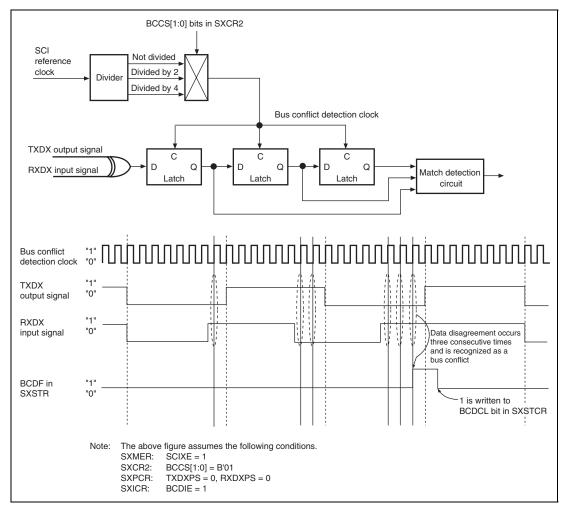

|       | 22.3.3  | Bus Conflict Detection                                                   | 855 |

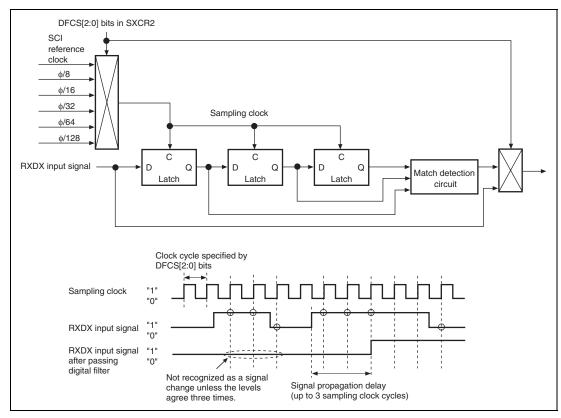

|       | 22.3.4  | RXDX Pin Input Digital Filter                                            | 856 |

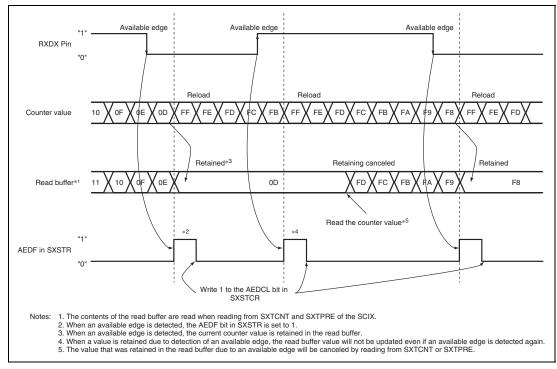

|       | 22.3.5  | Bit Rate Measurement                                                     | 857 |

|       | 22.3.6  | Interrupt Requests                                                       | 859 |

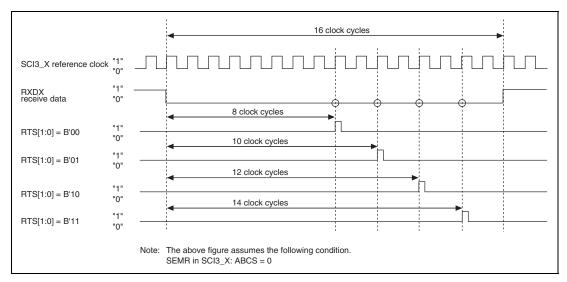

|       | 22.3.7  | RXDX Receive Data Sampling Timing Selection                              | 860 |

|       | 22.3.8  | SCIX Timer                                                               | 861 |

| 22.4  | Usage   | Note                                                                     | 863 |

|       | 22.4.1  | Output for Pins on which the TXDX and RXDX Functions are Multiplexed     | 863 |

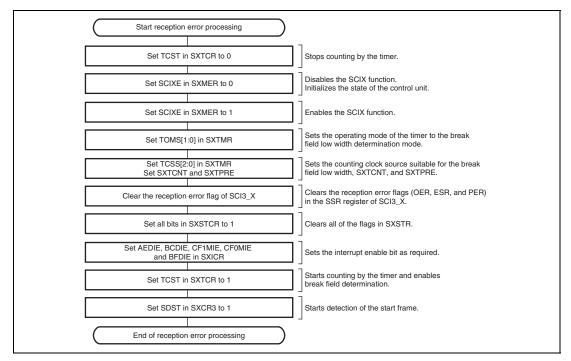

|       | 22.4.2  | Processing in Response to a SCI3_X Reception Error During Reception of a |     |

|       |         | Start Frame                                                              | 863 |

|       |         |                                                                          |     |

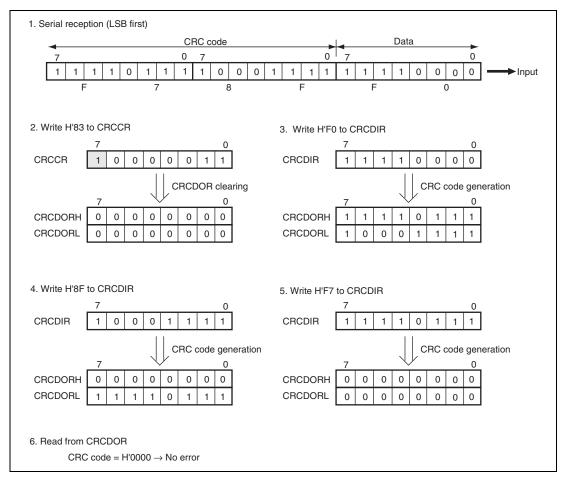

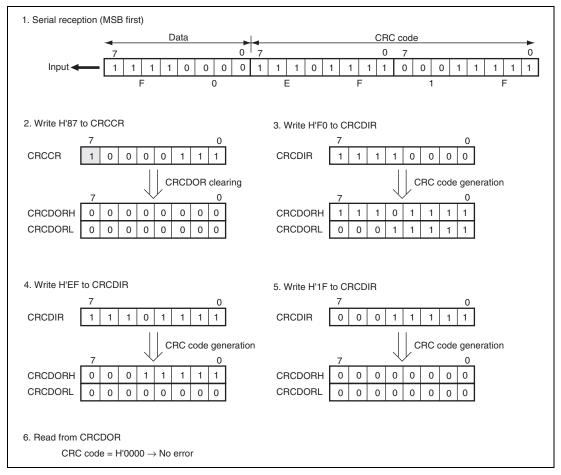

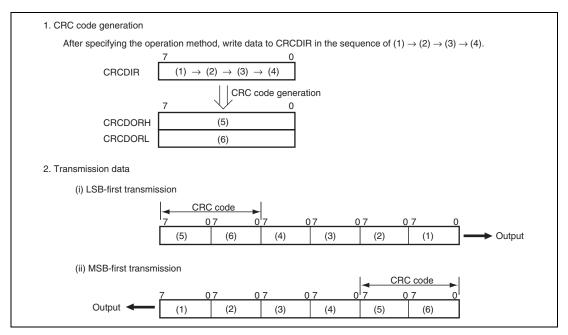

| Secti | ion 23  | CRC Operation Circuit                                                    | 865 |

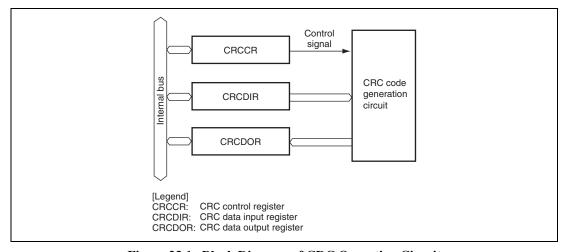

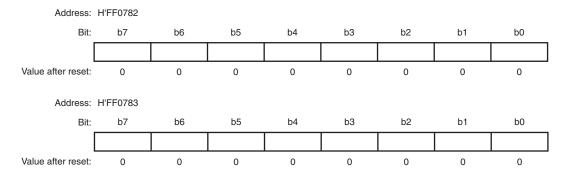

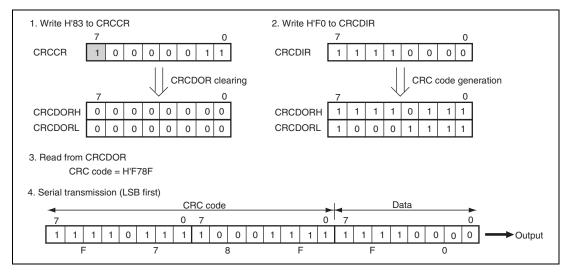

| 23.1  | Feature | es                                                                       | 865 |

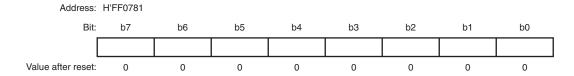

| 23.2  | Registe | er Descriptions                                                          | 866 |

|       | 23.2.1  | CRC Control Register (CRCCR)                                             | 866 |

|       | 23.2.2  | CRC Data Input Register (CRCDIR)                                         | 867 |

|       | 23.2.3  | CRC Data Output Register (CRCDOR)                                        | 867 |

| 23.3  | CRC C   | Pperation Circuit Operation                                              | 868 |

| 23.4  | Note or | n CRC Operation Circuit                                                  | 871 |

| 23.5  | Setting | of Module Standby Function                                               | 871 |

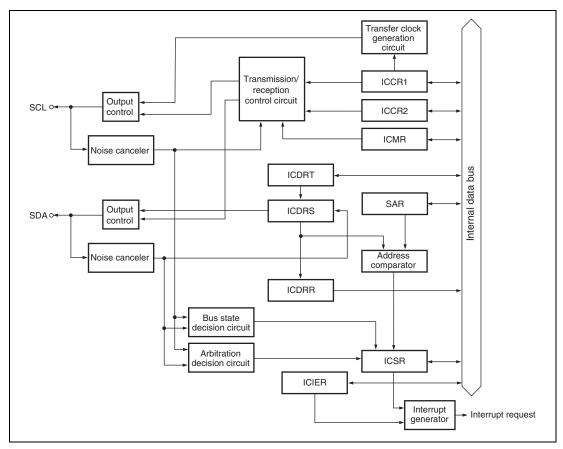

| Secti | ion 24  | I <sup>2</sup> C Bus Interface 2 (IIC2)                                  | 873 |