# RENESAS

# RL78/G1P

# RENESAS MCU

# Datasheet

R01DS0371EJ0100 Rev.1.00 Nov 29, 2019

True low-power platform (66 µA/MHz, and 0.31 µA for LVD) for the general-purpose and sensor control applications, with 2.7-V to 3.6-V operation, low pin counts (24 or 32 pins), small ROM capacity (16 Kbytes), and highly-functional analog circuits (12-bit A/D and 10-bit D/A converters)

# 1. OUTLINE

# 1.1 Features

- O Minimum instruction execution time can be changed from high speed (0.03125 μs: @ 32 MHz operation with high-speed on-chip oscillator) to low-speed (1 μs: @ 1 MHz operation with highspeed on-chip oscillator)

- O General-purpose registers: 8 bits × 32 registers (8 bits × 8 registers × 4 banks)

- O ROM: 16 KB, RAM: 1.5 KB, Data flash: 2 KB

- O High-speed on-chip oscillator

- Select from 32 MHz (TYP.), 24 MHz (TYP.), 16 MHz (TYP.), 12 MHz (TYP.), 8 MHz (TYP.), 6 MHz (TYP.), 4 MHz (TYP.), 3 MHz (TYP.), 2 MHz (TYP.), and 1 MHz (TYP.)

- On-chip single-power supply flash memory (with prohibition of block erase/writing function)

- O Self-programming

- O On-chip debug function

- On-chip power-on-reset (POR) circuit and voltage detector (LVD)

- On-chip watchdog timer (operable with the dedicated low-speed on-chip oscillator)

- O On-chip clock output/buzzer output controller

- O On-chip BCD adjustment

- O I/O ports: 26 or 28 (N-ch open drain: 2)

- O Timer

- 16-bit timer TAU: 4 channels

- Watchdog timer: 1 channel

- O Serial interface

- CSI: 1 channel

- UART: 1 channel

- I<sup>2</sup>C 1 channel (2 slave addresses)

- 8/12-bit resolution A/D converter (VDD = 2.7 to 3.6

V): 6 or 8 channels

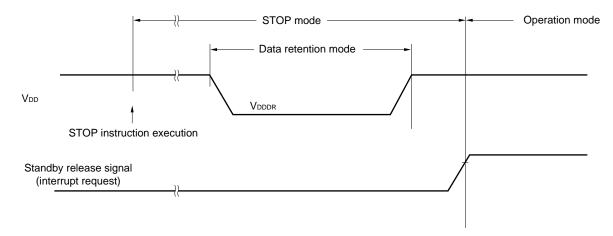

- O Standby function: HALT, STOP, SNOOZE mode

- O On-chip 10-bit D/A converter

- O DMA controller: 2 channels

- O On-chip event link controller (ELC)

- O Power supply voltage: VDD = 2.7 to 3.6 V

- Operating ambient temperature: T<sub>A</sub> = -40 to +85°C (A: Consumer applications, D: Industrial applications)

- Remark The functions mounted depend on the product. See 1.6 Outline of Functions.

#### O ROM, RAM capacities

| Flash ROM | Data Flash | RAM <sup>Note</sup> | 24-pin                   | 32-pin                   |  |

|-----------|------------|---------------------|--------------------------|--------------------------|--|

| 16 KB     | 2 KB       | 1.5 KB              | R5F11Z7AANA, R5F11Z7ADNA | R5F11ZBAAFP, R5F11ZBADFP |  |

**Note** The flash libraries use the on-chip RAM area from FFE20H to FFEFFH and the parts of the RAM area referred to as self RAM (RAM for use in self-programming), which are listed in the table below, for self-programming or rewriting of the data flash memory.

See below for the RAM areas used by the flash library.

|             | RAM    | FSL Type01                | FDL Type04       | EEL Pack01, EEL Pack02 |

|-------------|--------|---------------------------|------------------|------------------------|

|             |        | Self RAM size             | Self RAM size    |                        |

|             |        | 896 bytes <sup>Note</sup> | 136 bytes        |                        |

| R5F11Z7AANA | 1.5 KB | FF900H to FFC7FH          | FF900H to FF987H | Not available          |

| R5F11Z7ADNA |        |                           |                  |                        |

| R5F11ZBAAFP |        |                           |                  |                        |

| R5F11ZBADFP |        |                           |                  |                        |

**Note** Functions supported in FSL Type01 are only basic functions. Other functions are not supported. Basic functions: FSL\_Init, FSL\_Open, FSL\_Close, FSL\_PrepareFunctions, FSL\_BlankCheck, FSL\_Erase, FSL\_IVerify, FSL\_Write, and FSL\_StatusCheck

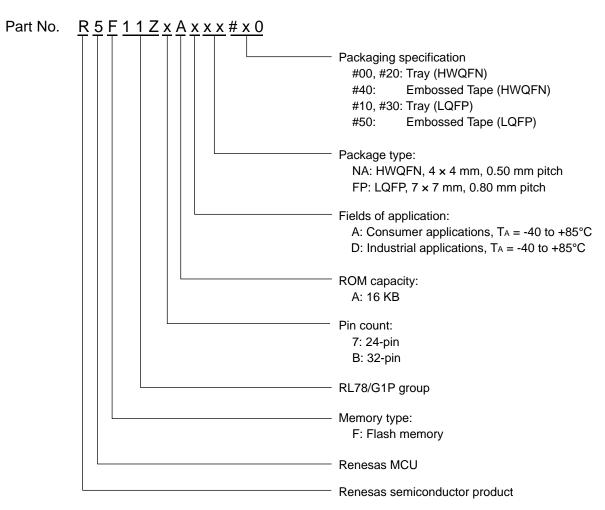

# 1.2 List of Part Numbers

| Figure 1-1. | Part Number. | Memory Size | , and Package |

|-------------|--------------|-------------|---------------|

|             |              |             | ,             |

| Pin Count | Package                                          | Data Flash | Fields of<br>Application | Packaging<br>Specification | Part Number                       |

|-----------|--------------------------------------------------|------------|--------------------------|----------------------------|-----------------------------------|

| 24 pins   | 24-pin plastic HWQFN<br>(4 × 4 mm, 0.5 mm pitch) | 2 KB       | А                        | Tray                       | R5F11Z7AANA#00,<br>R5F11Z7AANA#20 |

|           |                                                  |            |                          | Embossed Tape              | R5F11Z7AANA#40                    |

|           |                                                  |            | D                        | Tray                       | R5F11Z7ADNA#00,<br>R5F11Z7ADNA#20 |

|           |                                                  |            |                          | Embossed Tape              | R5F11Z7ADNA#40                    |

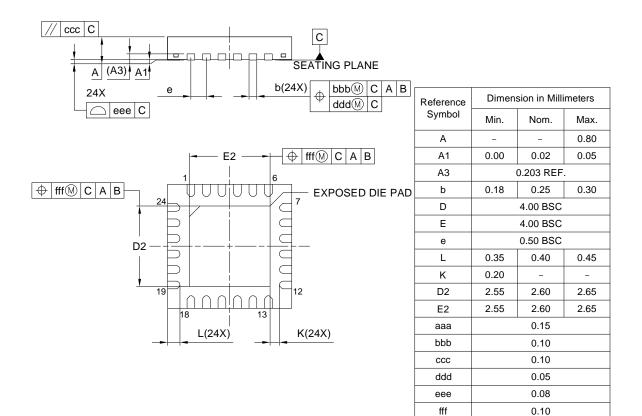

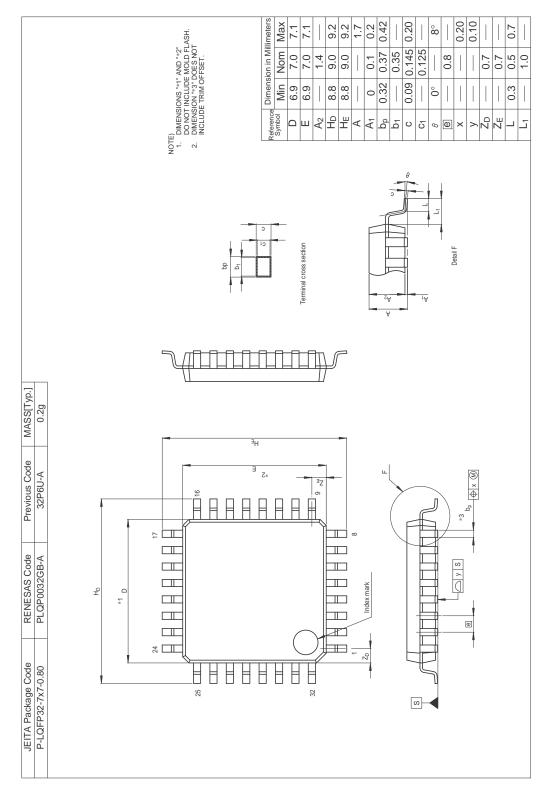

| 32 pins   | 32-pin plastic LQFP<br>(7 × 7 mm, 0.8 mm pitch)  |            | А                        | Tray                       | R5F11ZBAAFP#10,<br>R5F11ZBAAFP#30 |

|           |                                                  |            |                          | Embossed Tape              | R5F11ZBAAFP#50                    |

|           |                                                  |            | D                        | Tray                       | R5F11ZBADFP#10,<br>R5F11ZBADFP#30 |

|           |                                                  |            |                          | Embossed Tape              | R5F11ZBADFP#50                    |

# 1.3 Pin Configuration (Top View)

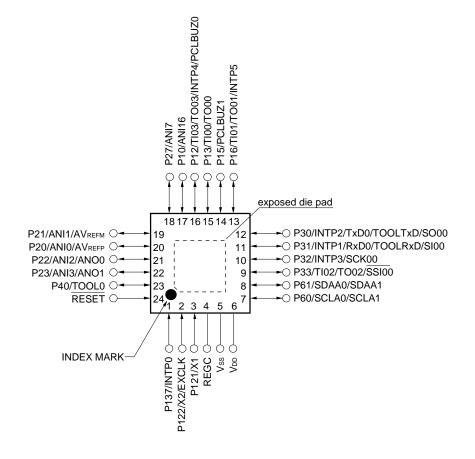

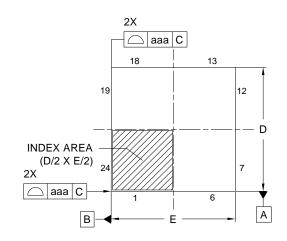

#### 1.3.1 24-pin products

• 24-pin plastic HWQFN (4 × 4 mm, 0.5 mm pitch)

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

2. It is recommended to connect an exposed die pad to  $V_{SS}$ .

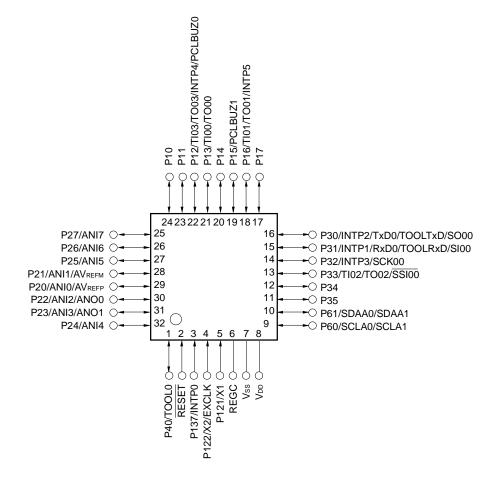

#### 1.3.2 32-pin products

• 32-pin plastic LQFP (7 × 7 mm, 0.8 mm pitch)

- Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- Remark For pin identification, see 1.4 Pin Identification.

# 1.4 Pin Identification

| ANI0 to ANI7, ANI16: | Analog input             | RxD0:             | Receive data                           |

|----------------------|--------------------------|-------------------|----------------------------------------|

| ANO0, ANO1:          | Analog output            | SCK00:            | Serial clock input/output              |

| AVREFM:              | Analog reference voltage | SCLA0, SCLA1:     | Serial clock input/output              |

|                      | minus                    | SDAA0, SDAA1:     | Serial data input/output               |

| AVREFP:              | Analog reference voltage | SI00:             | Serial data input                      |

|                      | plus                     | SO00:             | Serial data output                     |

| EXCLK:               | External clock input     | SSI00:            | Serial interface chip select input     |

|                      | (main system clock)      | TI00 to TI03:     | Timer input                            |

| INTP0 to INTP5:      | External Interrupt Input | TO00 to TO03:     | Timer output                           |

| P10 to P17:          | Port 1                   | TOOL0:            | Data input/output for tool             |

| P20 to P27:          | Port 2                   | TOOLRxD, TOOLTxD: | Data input/output for external device  |

| P30 to P35:          | Port 3                   | TxD0:             | Transmit data                          |

| P40:                 | Port 4                   | Vdd:              | Power supply                           |

| P60, P61:            | Port 6                   | Vss:              | Ground                                 |

| P121, P122:          | Port 12                  | X1, X2:           | Crystal oscillator (main system clock) |

| P137:                | Port 13                  |                   |                                        |

| PCLBUZ0, PCLBUZ1     | : Programmable clock     |                   |                                        |

|                      | output/buzzer output     |                   |                                        |

| REGC:                | Regulator capacitance    |                   |                                        |

| RESET:               | Reset                    |                   |                                        |

|                      |                          |                   |                                        |

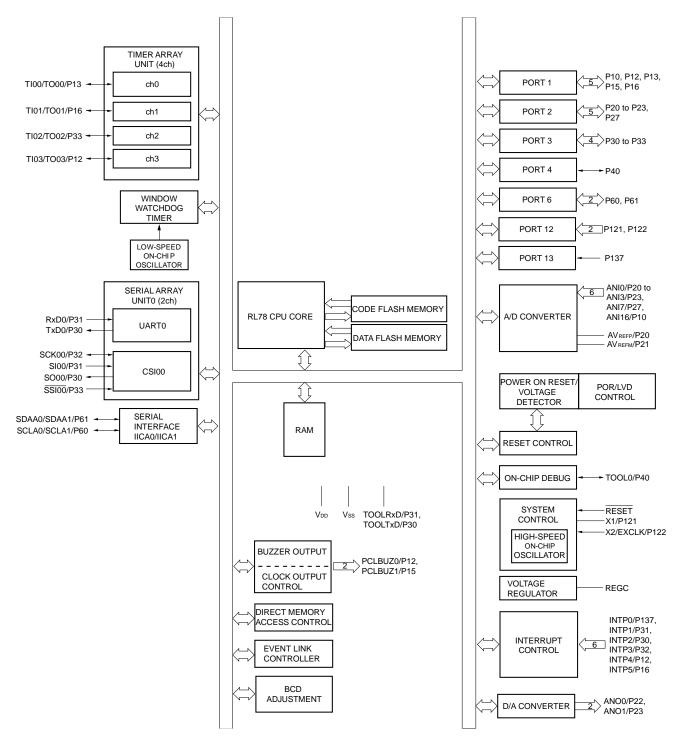

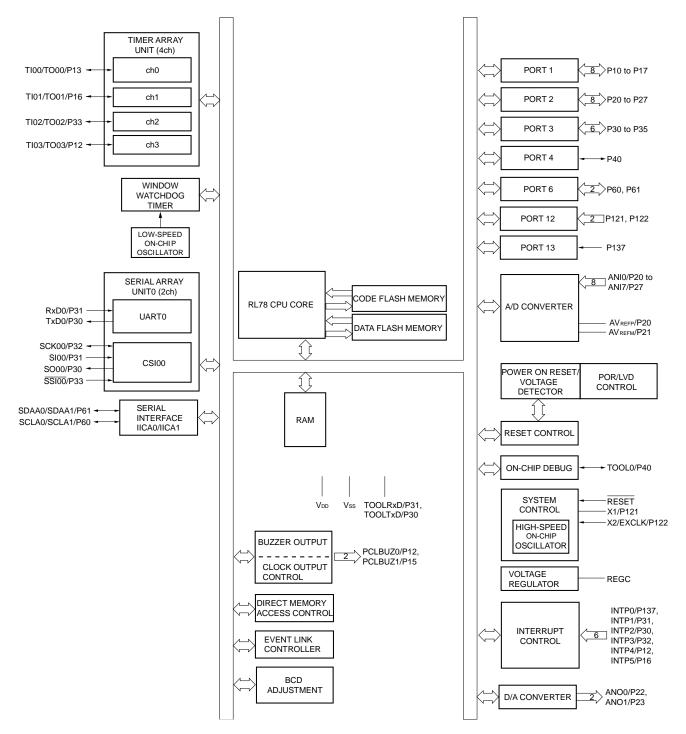

# 1.5 Block Diagram

#### 1.5.1 24-pin products

#### 1.5.2 32-pin products

# 1.6 Outline of Functions

| Item<br>Code flash memory<br>Data flash memory<br>RAM<br>Memory space |                                                 | 24-pin<br>R5F11Z7AANA, R5F11Z7ADNA<br>16 KB<br>2 KB                                                                                                                                                                                                     | 32-pin<br>R5F11ZBAAFP, R5F11ZBADFP |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| Data flash memory<br>RAM<br>Memory space                              |                                                 | 16 KB                                                                                                                                                                                                                                                   | R5F11ZBAAFP, R5F11ZBADFP           |  |  |  |  |

| Data flash memory<br>RAM<br>Memory space                              |                                                 |                                                                                                                                                                                                                                                         |                                    |  |  |  |  |

| RAM<br>Memory space                                                   |                                                 | 2 KB                                                                                                                                                                                                                                                    | 16 KB                              |  |  |  |  |

| Memory space                                                          |                                                 | 2 NB                                                                                                                                                                                                                                                    |                                    |  |  |  |  |

|                                                                       |                                                 | 1.5 KB <sup>Note</sup>                                                                                                                                                                                                                                  |                                    |  |  |  |  |

|                                                                       |                                                 | 1 MB                                                                                                                                                                                                                                                    |                                    |  |  |  |  |

| -                                                                     | High-speed<br>system clock                      | X1 (crystal/ceramic) oscillation, external main system clock input (EXCLK)<br>1 to 20 MHz: $V_{DD}$ = 2.7 to 3.6 V                                                                                                                                      |                                    |  |  |  |  |

| с                                                                     | High-speed on-<br>chip oscillator<br>clock (f⊮) | High-speed operation: 32 MHz ( $V_{DD}$ = 2.7 to 3.6 V)                                                                                                                                                                                                 |                                    |  |  |  |  |

| Low-speed on-chip o                                                   | oscillator clock                                | 15 kHz (TYP.): VDD = 2.7 to 3.6 V                                                                                                                                                                                                                       |                                    |  |  |  |  |

| General-purpose reg                                                   | jisters                                         | 8 bits $\times$ 32 registers (8 bits $\times$ 8 registers $\times$ 4 ban                                                                                                                                                                                | ks)                                |  |  |  |  |

| Minimum instruction                                                   | execution time                                  | 0.03125 $\mu$ s (High-speed on-chip oscillator: fiH =                                                                                                                                                                                                   | 32 MHz operation)                  |  |  |  |  |

|                                                                       |                                                 | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)                                                                                                                                                                              |                                    |  |  |  |  |

| Instruction set                                                       |                                                 | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits)</li> <li>Multiplication (8 bits × 8 bits)</li> <li>Rotate, barrel shift, and bit manipulation (set, reset, test, and boolean operation), etc.</li> </ul> |                                    |  |  |  |  |

| I/O port T                                                            | Total                                           | 20                                                                                                                                                                                                                                                      | 28                                 |  |  |  |  |

| (                                                                     | CMOS I/O                                        | 15                                                                                                                                                                                                                                                      | 23                                 |  |  |  |  |

| (                                                                     | CMOS input                                      | 3                                                                                                                                                                                                                                                       | 3                                  |  |  |  |  |

|                                                                       | N-ch O.D I/O<br>(6 V tolerance)                 | 2                                                                                                                                                                                                                                                       | 2                                  |  |  |  |  |

| Timer 1                                                               | 16-bit timer                                    | 4 channels (TAU)                                                                                                                                                                                                                                        |                                    |  |  |  |  |

| ١                                                                     | Watchdog timer                                  | 1 channel                                                                                                                                                                                                                                               |                                    |  |  |  |  |

| T                                                                     | Timer output                                    | 4<br>PWM outputs: 3                                                                                                                                                                                                                                     |                                    |  |  |  |  |

| Clock output/buzzer                                                   | output                                          | 2                                                                                                                                                                                                                                                       |                                    |  |  |  |  |

|                                                                       |                                                 | <ul> <li>2.44 kHz, 4.88 kHz, 9.77 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz<br/>(Main system clock: fmain = 20 MHz operation)</li> </ul>                                                                                                                    |                                    |  |  |  |  |

| 8/12-bit resolution A/                                                | D converter                                     | 6 channels                                                                                                                                                                                                                                              | 8 channels                         |  |  |  |  |

| 10-bit D/A converter                                                  |                                                 | 2 channels                                                                                                                                                                                                                                              |                                    |  |  |  |  |

| Serial interface                                                      |                                                 | CSI: 1 channel/UART: 1 channel                                                                                                                                                                                                                          |                                    |  |  |  |  |

| ľ                                                                     | <sup>2</sup> C bus                              | 1 channel (2 slave addresses)                                                                                                                                                                                                                           |                                    |  |  |  |  |

| DMA controller                                                        |                                                 | 2 channels                                                                                                                                                                                                                                              |                                    |  |  |  |  |

| Event link controller (                                               | (ELC)                                           | Event input: 10, Event trigger output: 3                                                                                                                                                                                                                |                                    |  |  |  |  |

| Vectored I                                                            | Internal                                        | 12                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

| interrupt sources E                                                   | External                                        | 6                                                                                                                                                                                                                                                       |                                    |  |  |  |  |

**Note** This is about 0.5 KB when the self-programming function and data flash function are used. For details, see **CHAPTER 3** in the RL78/G1P User's Manual.

(2/2)

| Item                          | 24-pin                                                                                                                                                                                                                                                                                                                                      | 32-pin                   |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                               | R5F11Z7AANA, R5F11Z7ADNA                                                                                                                                                                                                                                                                                                                    | R5F11ZBAAFP, R5F11ZBADFP |

| Reset                         | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-reset</li> <li>Internal reset by voltage detector</li> <li>Internal reset by illegal instruction execution<sup>Note</sup></li> <li>Internal reset by RAM parity error</li> <li>Internal reset by illegal-memory access</li> </ul> |                          |

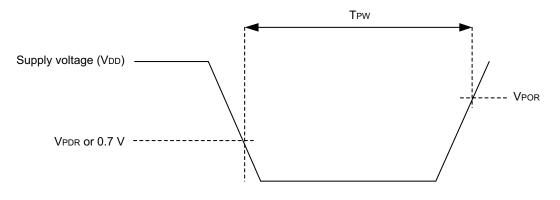

| Power-on-reset circuit        | <ul> <li>Power-on-reset: 1.51 ±0.03 V</li> <li>Power-down-reset: 1.50 ±0.03 V</li> </ul>                                                                                                                                                                                                                                                    |                          |

| Voltage detector              | 2.75 V to 3.13 V (4 stages)                                                                                                                                                                                                                                                                                                                 |                          |

| On-chip debug function        | Provided                                                                                                                                                                                                                                                                                                                                    |                          |

| Power supply voltage          | V <sub>DD</sub> = 2.7 to 3.6 V                                                                                                                                                                                                                                                                                                              |                          |

| Operating ambient temperature | $T_A = -40$ to +85°C                                                                                                                                                                                                                                                                                                                        |                          |

**Note** The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip debug emulator.

# 2. ELECTRICAL SPECIFICATIONS

- Cautions 1. The RL78 microcontrollers have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 2. The pins mounted depend on the product. See 2.1 Pin Function List to 2.2.1 With functions for each product in the RL78/G1P User's Manual.

# 2.1 Absolute Maximum Ratings

| Parameter              | Symbols | Conditions                                                             | Ratings                                                                | Unit |

|------------------------|---------|------------------------------------------------------------------------|------------------------------------------------------------------------|------|

| Supply voltage         | Vdd     |                                                                        | –0.5 to +4.6                                                           | V    |

|                        | Vss     |                                                                        | –0.5 to +0.3                                                           | V    |

| REGC pin input voltage | Viregc  | REGC                                                                   | –0.3 to +2.8<br>and –0.3 to V <sub>DD</sub> +0.3 <sup>Note 1</sup>     | V    |

| Input voltage          | VI1     | P10 to P17, P20 to P27, P30 to P35, P40, P121,<br>P122, P137           | –0.3 to V <sub>DD</sub> +0.3 <sup>Note 2</sup>                         | V    |

|                        | VI2     | P60, P61 (N-ch open-drain)                                             | -0.3 to +6.5                                                           | V    |

| Output voltage         | Vo1     | P10 to P17, P20 to P27, P30 to P35, P40, P60,<br>P61, P121, P122, P137 | -0.3 to V <sub>DD</sub> +0.3 <sup>Note 2</sup>                         | V    |

| Analog input voltage   | Val1    | ANI0 to ANI7, ANI16                                                    | $-0.3$ to V_DD +0.3 and $-0.3$ to AV_{REF(+)} +0.3^{\text{Notes 2, 3}} | V    |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (1/2)

**Notes 1.** Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F). This value regulates the absolute maximum rating of the REGC pin. Do not use this pin with voltage applied to it.

- **2.** Must be 4.6 V or lower.

- 3. Do not exceed  $AV_{REF(+)}$  + 0.3 V in case of A/D conversion target pin.

- Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- **Remarks 1.** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

- **2.** AV<sub>REF(+)</sub>: + side reference voltage of the A/D converter.

- 3. Vss: Reference voltage

| Parameter            | Symbols                   |                          | Conditions                       | Ratings     | Unit |

|----------------------|---------------------------|--------------------------|----------------------------------|-------------|------|

| Output current, high | Dutput current, high Іонт |                          | P10 to P17, P30 to P35, P40      | -40         | mA   |

|                      |                           |                          | -40                              | mA          |      |

|                      |                           |                          | -100                             | mA          |      |

|                      | Іон2                      | Per pin                  | P20 to P27                       | -0.5        | mA   |

|                      |                           |                          | -2                               | mA          |      |

| Output current, low  | Iol1                      | Per pin                  |                                  | 40          | mA   |

|                      |                           | Total of all pins        | P40                              | 40          | mA   |

|                      |                           | 140 mA                   | P10 to P17, P30 to P35, P60, P61 | 100         | mA   |

|                      | IOL2                      | Per pin                  | P20 to P27                       | 1           | mA   |

|                      |                           | Total of all pins        |                                  | 5           | mA   |

| Operating ambient    | TA                        | In normal operation mode |                                  | -40 to +85  | °C   |

| temperature          |                           | In flash memory p        | programming mode                 | 0 to +40    |      |

| Storage temperature  | Tstg                      |                          |                                  | -65 to +150 | °C   |

### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

# 2.2 Oscillator Characteristics

#### 2.2.1 X1 oscillator characteristics

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter | Resonator                               | Conditions                            | MIN. | TYP. | MAX. | Unit |

|-----------|-----------------------------------------|---------------------------------------|------|------|------|------|

|           | Ceramic resonator/<br>crystal resonator | $2.7~V \leq V_{\text{DD}} \leq 3.6~V$ | 1.0  |      | 20.0 | MHz  |

Note Indicates only oscillator characteristics. See 2.4 AC Characteristics for instruction execution time. Request evaluation by the manufacturer of the oscillator circuit mounted on a board to check the oscillator characteristics.

- Caution Since the CPU is started by the high-speed on-chip oscillator clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and the oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

- Remark When using the X1 oscillator, refer to 5.4 System Clock Oscillator in the RL78/G1P User's Manual.

#### 2.2.2 On-chip oscillator characteristics

| Oscillators                                                    | Parameters |                 | Conditions                                                   |      | TYP. | MAX. | Unit |

|----------------------------------------------------------------|------------|-----------------|--------------------------------------------------------------|------|------|------|------|

| High-speed on-chip oscillator                                  | fін        | 32 MHz selected |                                                              | 1    |      | 32   | MHz  |

| clock frequency <sup>Notes 1, 2</sup>                          |            | 24 MHz selected |                                                              | 1    |      | 24   | MHz  |

| High-speed on-chip oscillator                                  |            | -20 to +85°C    | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ | -1.0 |      | +1.0 | %    |

| clock frequency accuracy                                       |            | -40 to -20°C    | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ | -1.5 |      | +1.5 | %    |

| Low-speed on-chip oscillator clock frequency <sup>Note 2</sup> | fı∟        |                 |                                                              |      | 15   |      | kHz  |

| Low-speed on-chip oscillator<br>clock frequency accuracy       |            |                 |                                                              | -15  |      | +15  | %    |

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

- **Notes 1.** High-speed on-chip oscillator frequency is selected by bits 0 to 3 of option byte (000C2H) and bits 0 to 2 of HOCODIV register.

- 2. This indicates the oscillator characteristics only. See 2.4 AC Characteristics for instruction execution time.

# 2.3 DC Characteristics

#### 2.3.1 Pin characteristics

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$ (1/3)

| Items                      | Symbol | Conditions MIN. TYP. M                                                  |                                | MAX. | Unit                   |    |

|----------------------------|--------|-------------------------------------------------------------------------|--------------------------------|------|------------------------|----|

| Output current, highNote 1 | Іон1   | Per pin for P10 to P17, P30 to P35, P40                                 |                                |      | -2.0 <sup>Note 2</sup> | mA |

|                            |        | Total of P10 to P17, P30 to P35<br>(When duty ≤ 70% <sup>Note 3</sup> ) | duty ≤ 70% <sup>Note 3</sup> ) |      | -19.0                  | mA |

|                            |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )               | all pins -21.                  |      | -21.0                  | mA |

|                            | Іон2   | Per pin for P20 to P27                                                  |                                |      | -0.1                   | mA |

|                            |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )               |                                |      | -0.8                   | mA |

**Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from the V<sub>DD</sub> pin to an output pin.

- 2. Do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OH} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoH = -19.0 mA

Total output current of pins = (-19.0 × 0.7)/(80 × 0.01) = -16.625 mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

| Items                                 | Symbol | Conditions                                                                        | MIN.          | TYP. | MAX.                  | Unit |  |  |

|---------------------------------------|--------|-----------------------------------------------------------------------------------|---------------|------|-----------------------|------|--|--|

| Output current, low <sup>Note 1</sup> | IOL1   | Per pin for P10 to P17, P30 to P35, P40                                           |               |      | 3.0 <sup>Note 2</sup> | mA   |  |  |

|                                       |        | Per pin for P60, P61                                                              |               |      | 3.0 <sup>Note 2</sup> | mA   |  |  |

|                                       |        | Total of P10 to P17, P30 to P35, P60, P61<br>(When duty ≤ 70% <sup>Note 3</sup> ) |               |      | 35.0                  | mA   |  |  |

|                                       |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                         | l of all pins |      |                       |      |  |  |

|                                       | IOL2   | Per pin for P20 to P27                                                            |               |      | 0.4                   | mA   |  |  |

|                                       |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                         |               |      | 3.2                   | mA   |  |  |

### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{V}_{\text{SS}} = 0 \text{ V})$ (2/3)

- Notes 1. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 2. However, do not exceed the total current value.

- Specification under conditions where the duty factor ≤ 70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the

- following expression (when changing the duty factor from 70% to n%).

- Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80% and IoL = 35.0 mA

Total output current of pins =  $(35.0 \times 0.7)/(80 \times 0.01) = 30.625$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

| Items                          | Symbol |                                                            | Conditions                    | ;                                     | MIN.      | TYP. | MAX.   | Unit |

|--------------------------------|--------|------------------------------------------------------------|-------------------------------|---------------------------------------|-----------|------|--------|------|

| Input voltage, high            | VIH1   | P10 to P17, P30 to F<br>EXCLK, RESET                       | P35, P40, P1                  | 21, P122, P137,                       | 0.8Vdd    |      | Vdd    | V    |

|                                | VIH2   | P20 to P27                                                 |                               |                                       | 0.7Vdd    |      | Vdd    | V    |

|                                | Vінз   | P60, P61                                                   |                               |                                       | 0.7Vdd    |      | 6.0    | V    |

| Input voltage, low             | VIL1   | P10 to P17, P30 to F<br>EXCLK, RESET                       | P35, P40, P1                  | 21, P122, P137,                       | 0         |      | 0.2Vdd | V    |

|                                | VIL2   | P20 to P27, P60, P6                                        | 1                             |                                       | 0         |      | 0.3Vdd | V    |

| Output voltage, high           | Vон1   | P10 to P17, P30 to<br>P35, P40                             | Іон1 = −2.0                   | mA                                    | Vdd - 0.6 |      |        | V    |

|                                | Vон2   | P20 to P27                                                 | Іон1 <b>=</b> -100 <i>µ</i> А |                                       | Vdd - 0.5 |      |        | V    |

| Output voltage, low            | Vol1   | P10 to P17, P30 to                                         | lol1 = 3.0 mA                 |                                       |           |      | 0.6    | V    |

|                                |        | P35, P40                                                   | lol1 = 1.5 n                  | nA                                    |           |      | 0.4    | V    |

|                                | Vol2   | P20 to P27                                                 | IOL2 = 400                    | иA                                    |           |      | 0.4    | V    |

|                                | Vol3   | P60, P61                                                   | lоьз = 3.0 n                  | nA                                    |           |      | 0.4    | V    |

| Input leakage current,<br>high | ILIH1  | P10 to P17, P20 to<br>P27, P30 to P35,<br>P40, P137, RESET | Vi = Vdd                      |                                       |           |      | 1      | μA   |

|                                | Ілн2   | P121, P122<br>(X1, X2, EXCLK)                              | Vi = Vdd                      | In input port or external clock input |           |      | 1      | μA   |

|                                |        |                                                            |                               | In resonator connection               |           |      | 10     | μA   |

| Input leakage current,<br>low  | ILIL1  | P10 to P17, P20 to<br>P27, P30 to P35,<br>P40, P137, RESET | VI = Vss                      |                                       |           |      | -1     | μA   |

|                                | ILIL2  | P121, P122<br>(X1, X2, EXCLK)                              | VI = Vss                      | In input port or external clock input |           |      | -1     | μA   |

|                                |        |                                                            |                               | In resonator connection               |           |      | -10    | μA   |

| On-chip pull-up<br>resistance  | Ru     | P10 to P17, P30 to<br>P35, P40                             | Vi = Vss, In input port       |                                       | 10        | 20   | 100    | kΩ   |

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{V}_{\text{SS}} = 0 \text{ V})$ (3/3)

# 2.3.2 Supply current characteristics

| Parameter      | Symbol                                           |                                            |                                             | Conditions                                   |                         |                      | MIN. | TYP. | MAX. | Unit |

|----------------|--------------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------------------|-------------------------|----------------------|------|------|------|------|

| Supply current | DD1 <sup>Note 1</sup>                            | Operating mode                             | HS (high-<br>speed main)                    | f <sub>IH</sub> = 32 MHz <sup>Note 3</sup>   | Basic operation         | Vdd = 3.0 V          |      | 2.1  |      | mA   |

|                |                                                  | mode <sup>Note 4</sup>                     |                                             | Normal operation                             | Vdd = 3.0 V             |                      | 4.8  | 7.0  | mA   |      |

|                |                                                  | f <sub>IH</sub> = 24 MHz <sup>Note 3</sup> | Normal operation                            | $V_{DD} = 3.0 V$                             |                         | 3.8                  | 5.5  | mA   |      |      |

|                |                                                  | $f_{H} = 16 \text{ MHz}^{Note 3}$          | Normal operation                            | $V_{DD} = 3.0 V$                             |                         | 2.8                  | 4.0  | mA   |      |      |

|                | LS (low-<br>speed main<br>mode <sup>Note 4</sup> | speed main)                                | f <sub>IH</sub> = 8 MHz <sup>Note 3</sup>   | Normal operation                             | V <sub>DD</sub> = 3.0 V |                      | 1.3  | 2.0  | mA   |      |

|                |                                                  |                                            | HS (high-                                   | f <sub>MX</sub> = 20 MHz <sup>Note 2</sup> , | Normal                  | Square wave input    |      | 3.3  | 4.6  | mA   |

|                |                                                  |                                            | speed main)<br>mode <sup>Note 4</sup>       | V <sub>DD</sub> = 3.0 V                      | operation               | Resonator connection |      | 3.5  | 4.8  |      |

|                |                                                  |                                            |                                             | $f_{MX} = 10 \text{ MHz}^{Note 2},$          | Normal                  | Square wave input    |      | 2.0  | 2.7  | mA   |

|                |                                                  | Vdd = 3.0 V                                | operation                                   | Resonator connection                         |                         | 2.1                  | 2.7  |      |      |      |

|                | LS                                               | LS (low-                                   | f <sub>MX</sub> = 8 MHz <sup>Note 2</sup> , | Normal                                       | Square wave input       |                      | 1.2  | 2.0  | mA   |      |

|                |                                                  | speed main)<br>mode <sup>Note 4</sup>      | . ,                                         |                                              | Resonator connection    |                      | 1.2  | 2.0  |      |      |

# (TA = -40 to +85°C, 2.7 V $\leq$ V\_DD $\leq$ 3.6 V, Vss = 0 V) (1/3)

**Notes 1.** Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. When high-speed on-chip oscillator is stopped.

- **3.** When high-speed system clock is stopped.

- 4. Relationship between operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode: @1 MHz to 32 MHz

- LS (low-speed main) mode: @1 MHz to 8 MHz

- Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fil: High-speed on-chip oscillator clock frequency

- 3. Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

| Parameter                 | Symbol                                     |                              |                                            | Conditions                                   |                         | MIN. | TYP. | MAX. | Unit |

|---------------------------|--------------------------------------------|------------------------------|--------------------------------------------|----------------------------------------------|-------------------------|------|------|------|------|

| Supply                    | IDD2 <sup>Note 2</sup>                     | HALT                         | HS (high-speed                             | fin = 32 MHz <sup>Note 4</sup>               | V <sub>DD</sub> = 3.0 V |      | 0.60 | 1.63 | mA   |

| current <sup>Note 1</sup> |                                            | mode                         | main) mode <sup>Note 6</sup>               | fін = 24 MHz <sup>Note 4</sup>               | V <sub>DD</sub> = 3.0 V |      | 0.49 | 1.28 | mA   |

|                           |                                            |                              |                                            | fін = 16 MHz <sup>Note 4</sup>               | V <sub>DD</sub> = 3.0 V |      | 0.45 | 1.00 | mA   |

|                           | LS (low-speed main) mode <sup>Note 6</sup> | f⊪ = 8 MHz <sup>Note 4</sup> | Vdd = 3.0 V                                |                                              | 320                     | 530  | μA   |      |      |

|                           |                                            |                              | main) modeNote 6                           | f <sub>MX</sub> = 20 MHz <sup>Note 3</sup> , | Square wave input       |      | 0.28 | 1.00 | mA   |

|                           |                                            | -                            | VDD = 3.0 V                                | Resonator connection                         |                         | 0.49 | 1.17 | mA   |      |

|                           |                                            |                              | $f_{MX} = 10 \text{ MHz}^{\text{Note 3}},$ | Square wave input                            |                         | 0.19 | 0.60 | mA   |      |

|                           |                                            |                              |                                            | $V_{DD} = 3.0 V$                             | Resonator connection    |      | 0.30 | 0.67 | mA   |

|                           |                                            |                              | LS (low-speed                              | f <sub>MX</sub> = 8 MHz <sup>Note 3</sup> ,  | Square wave input       |      | 95   | 330  | μA   |

|                           |                                            |                              | main) mode <sup>Note 6</sup>               | $V_{DD} = 3.0 V$                             | Resonator connection    |      | 145  | 380  |      |

|                           | IDD3 <sup>Note 5</sup>                     | STOP                         | $T_A = -40^{\circ}C$                       |                                              |                         |      | 0.18 |      | μA   |

|                           |                                            | mode                         | T <sub>A</sub> = +25°C                     |                                              |                         |      | 0.23 | 0.50 |      |

|                           | Ta =                                       | T <sub>A</sub> = +50°C       | T <sub>A</sub> = +50°C                     |                                              |                         | 0.26 | 1.10 |      |      |

|                           |                                            | $T_A = +70^{\circ}C$         |                                            |                                              |                         | 0.29 | 1.90 |      |      |

|                           |                                            | T <sub>A</sub> = +85°C       | $T_A = +85^{\circ}C$                       |                                              |                         |      | 3.30 |      |      |

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{V}_{\text{SS}} = 0 \text{ V})$ (2/3)

- **Notes 1.** Total current flowing into V<sub>DD</sub>, including the input leakage current flowing when the level of the input pin is fixed to V<sub>DD</sub> or V<sub>SS</sub>. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, D/A converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. During HALT instruction execution by flash memory.

- 3. When high-speed on-chip oscillator is stopped.

- 4. When high-speed system clock is stopped.

- **5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When watchdog timer is stopped. The values below the MAX. column include the leakage current.

- 6. Relationship between operation frequency of CPU and operation mode is as below.

- HS (high-speed main) mode: @1 MHz to 32 MHz

- LS (low-speed main) mode: @1 MHz to 8 MHz

- Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fil: High-speed on-chip oscillator clock frequency

- 3. Except STOP mode, temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

| Parameter                                     | Symbol                       | Conditions                                    | MIN. | TYP. | MAX.  | Unit |

|-----------------------------------------------|------------------------------|-----------------------------------------------|------|------|-------|------|

| Watchdog timer<br>operating current           | WDT <sup>Notes 1, 2, 3</sup> | fı∟ = 15 kHz                                  |      | 0.22 |       | μA   |

| A/D converter<br>operating current            | ADC <sup>Notes 1, 4</sup>    | VDD = 3.0 V, When conversion at maximum speed |      | 0.58 | 0.82  | mA   |

| A/D converter<br>reference voltage<br>current | ADREF <sup>Note 1</sup>      |                                               |      | 75.0 |       | μA   |

| Temperature sensor<br>operating current       | TMPS <sup>Note 1</sup>       |                                               |      | 75.0 |       | μA   |

| D/A converter<br>operating current            | DAC <sup>Notes 1, 5</sup>    |                                               |      |      | 2     | mA   |

| LVD operating<br>current                      | <sub>LVI</sub> Notes 1, 6    |                                               |      | 0.08 |       | μΑ   |

| Self-programming operating current            | <sub>FSP</sub> Notes 1, 8    |                                               |      | 2.50 | 12.20 | mA   |

| BGO operating<br>current                      | BGO <sup>Notes 1, 7</sup>    |                                               |      | 2.50 | 12.20 | mA   |

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$  (3/3)

Notes 1. Current flowing to VDD.

- 2. When high speed on-chip oscillator and high-speed system clock are stopped.

- 3. Current flowing only to the watchdog timer (including the operating current of the 15 kHz low-speed on-chip oscillator). The supply current of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and IWDT when the watchdog timer is in operation.

- **4.** Current flowing only to the A/D converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IADC when the A/D converter operates in an operation mode or the HALT mode.

- 5. Current flowing only to the D/A converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IDAC when the D/A converter operates in an operation mode or the HALT mode.

- **6.** Current flowing only to the LVD circuit. The supply current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ILVD when the LVD circuit is in operation.

- 7. Current flowing during programming of the data flash.

- 8. Current flowing during self-programming.

Remarks 1. fil: Low-speed on-chip oscillator clock frequency

- 2. fclk: CPU/peripheral hardware clock frequency

- **3.** Temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

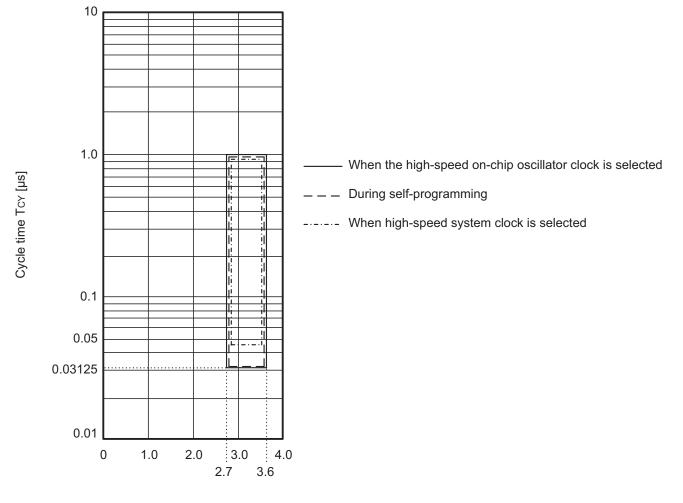

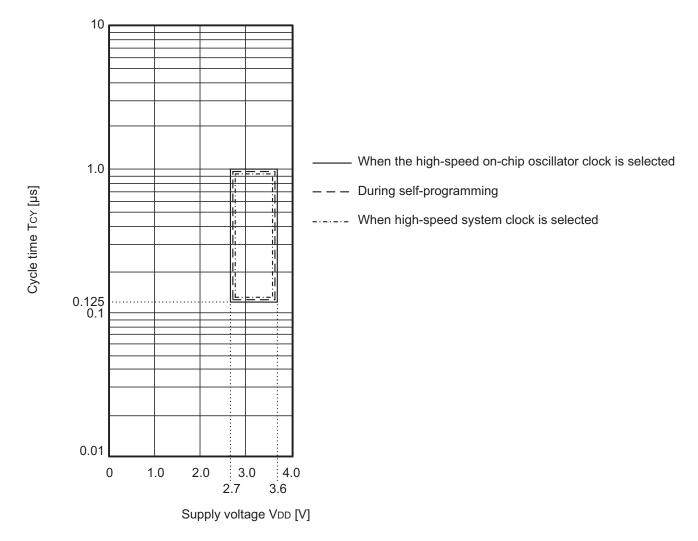

# 2.4 AC Characteristics

$(T_A = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le V_{DD} \le 3.6 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Items                                                          | Symbol          | (                   | Conditions                | MIN.      | TYP. | MAX. | Unit |

|----------------------------------------------------------------|-----------------|---------------------|---------------------------|-----------|------|------|------|

| Instruction cycle (minimum                                     | Тсү             | Main system clock   | HS (high-speed main) mode | 0.03125   |      | 1    | μS   |

| instruction execution time)                                    |                 | (fmain) operation   | LS (low-speed main) mode  | 0.125     |      | 1    | μS   |

|                                                                |                 | In the self-        | HS (high-speed main) mode | 0.03125   |      | 1    | μS   |

|                                                                |                 | programming mode    | LS (low-speed main) mode  | 0.125     |      | 1    | μS   |

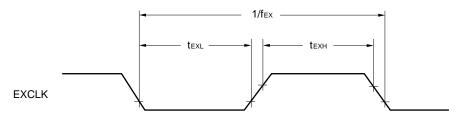

| External system clock<br>frequency                             | fex             |                     |                           | 1.0       |      | 20.0 | MHz  |

| External system clock input high-level width, low-level width, | tехн,<br>texl   |                     |                           | 24        |      |      | ns   |

| TI00 to TI03 input high-level width, low-level width           | t⊤ıн,<br>t⊤ı∟   |                     |                           | 1/fмск+10 |      |      | ns   |

| TO00 to TO03 output frequency                                  | fто             | HS (high-speed main | ) mode                    |           |      | 8    | MHz  |

|                                                                |                 | LS (low-speed main) | mode                      |           |      | 4    | MHz  |

| PCLBUZ0, PCLBUZ1 output                                        | <b>f</b> PCL    | HS (high-speed main | ) mode                    |           |      | 8    | MHz  |

| frequency                                                      |                 | LS (low-speed main) | mode                      |           |      | 4    | MHz  |

| Interrupt input high-level width,<br>low-level width           | tinth,<br>tintl | INTP0 to INTP5      | 1                         |           |      | μS   |      |

| RESET low-level width                                          | trsl            |                     |                           | 10        |      |      | μS   |

Remark fmck: Timer array unit operation clock frequency

(Operation clock to be set by the CKSmn0 and CKSmn1 bits of timer mode register mn (TMRmn). m: Unit number (m = 0), n: Channel number (n = 0 to 3))

Minimum Instruction Execution Time during Main System Clock Operation

TCY vs V<sub>DD</sub> (HS (high-speed main) mode)

Supply voltage VDD [V]

TCY vs VDD (LS (low-speed main) mode)

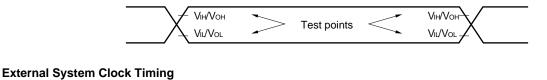

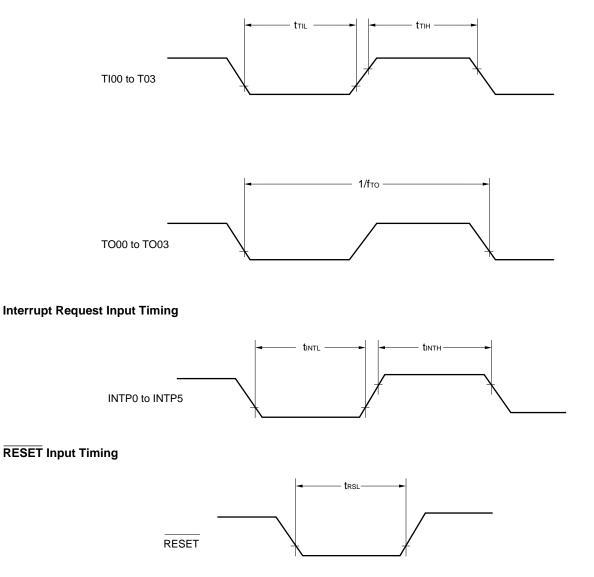

#### **AC Timing Test Points**

#### **TI/TO Timing**

# 2.5 Peripheral Functions Characteristics

#### AC Timing Test Points

#### 2.5.1 Serial array unit

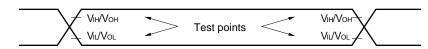

# (1) During communication at same potential (UART mode)

## $(T_A = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le V_{DD} \le 3.6 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Parameter                       | Symbol | Conditions                                                                                            |      | HS (high-speed<br>main) Mode |      | LS (low-speed main)<br>Mode |      |  |

|---------------------------------|--------|-------------------------------------------------------------------------------------------------------|------|------------------------------|------|-----------------------------|------|--|

|                                 |        |                                                                                                       | MIN. | TYP.                         | MIN. | MAX.                        |      |  |

| Transfer rate <sup>Note 1</sup> |        | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$                                          |      | fмск/6                       |      | fмск/6                      | bps  |  |

|                                 |        | Theoretical value of the maximum transfer rate $f_{\text{MCK}}$ = $f_{\text{CLK}}$ $^{\text{Note 2}}$ |      | 5.3                          |      | 1.3                         | Mbps |  |

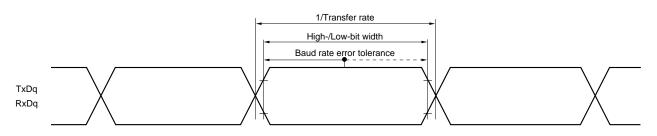

#### UART mode connection diagram (during communication at same potential)

#### UART mode bit width (during communication at same potential) (reference)

**Notes 1.** Transfer rate in the SNOOZE mode is 4800 bps only.

The maximum operating frequencies of the CPU/peripheral hardware clock (f<sub>CLK</sub>) are: HS (high-speed main) mode: 32 MHz (2.7 V ≤ V<sub>DD</sub> ≤ 3.6 V) LS (low-speed main) mode: 8 MHz (2.7 V ≤ V<sub>DD</sub> ≤ 3.6 V).

**Remarks 1.** q: UART number (q = 0)

fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00, 01))

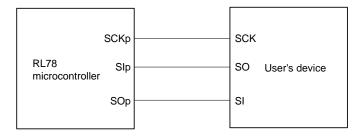

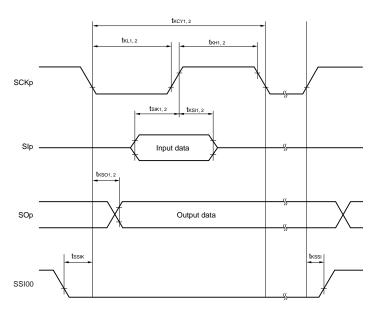

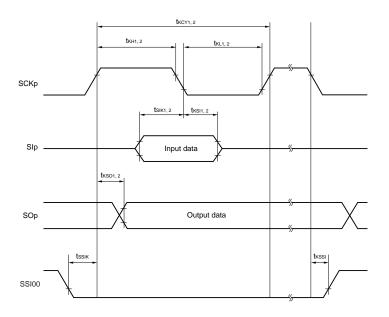

# (2) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter                                                          | Symbol     | Conditions       | HS (high-speed ma | ain) Mode | LS (low-speed m     | Unit |    |

|--------------------------------------------------------------------|------------|------------------|-------------------|-----------|---------------------|------|----|

|                                                                    |            |                  | MIN.              | MAX.      | MIN.                | MAX. |    |

| SCKp cycle time                                                    | tKCY1      |                  | 83.3              |           | 250                 |      | ns |

| SCKp high-/low-level width                                         | tĸнı, tĸ∟ı |                  | tксү1/2 - 10      |           | tксү1/2 <b>-</b> 50 |      | ns |

| SIp setup time (to SCKp↑) Note 1                                   | tsik1      |                  | 33                |           | 110                 |      | ns |

| SIp hold time (from SCKp↑) <sup>Note 1</sup>                       | tksi1      |                  | 10                |           | 10                  |      | ns |

| Delay time from SCKp $\downarrow$ to SOp output $^{\text{Note 2}}$ | tkso1      | C = 20 pF Note 3 |                   | 10        |                     | 10   | ns |

Notes 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" and the SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

**3.** C is the load capacitance of the SCKp and SOp output lines.

**Remarks 1.** p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0)

fMCK: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

# (3) During communication at same potential (CSI mode) (slave mode, SCKp... external clock input)

| Parameter                                                         | Symbol        | Conditions                  | HS (high-sp<br>Moo | ,         | LS (low-sp<br>Mo  | Unit       |    |

|-------------------------------------------------------------------|---------------|-----------------------------|--------------------|-----------|-------------------|------------|----|

|                                                                   |               |                             | MIN.               | MAX.      | MIN.              | MAX.       |    |

| SCKp cycle time <sup>Note 4</sup>                                 | tkCY2         | 16 MHz < fмск               | 8/fмск             |           | -                 |            | ns |

|                                                                   |               | $f_{MCK} \le 16 \ MHz$      | 6/fмск             |           | 6/fмск            |            | ns |

| SCKp high-/low-level width                                        | tкн2,<br>tкL2 |                             | tксү2/2-8          |           | tксү2/ <b>2-8</b> |            | ns |

| SIp setup time (to SCKp↑) <sup>Note 1</sup>                       | tsik2         |                             | 1/fмск+20          |           | 1/fмск+30         |            | ns |

| SIp hold time (from SCKp↑) <sup>Note 1</sup>                      | <b>t</b> KSI2 |                             | 1/fмск+31          |           | 1/fмск+31         |            | ns |

| Delay time from SCKp $\downarrow$ to SOp output <sup>Note 2</sup> | tkso2         | C = 30 pF <sup>Note 3</sup> |                    | 2/fмск+44 |                   | 2/fмск+110 | ns |

| SSI00 setup time                                                  | tssik         | DAPmn = 0                   | 120                |           | 120               |            | ns |

|                                                                   |               | DAPmn = 1                   | 1/fмск+120         |           | 1/fмск+120        |            | ns |

| SSI00 hold time                                                   | tĸssi         | DAPmn = 0                   | 1/fмск+120         |           | 1/fмск+120        |            | ns |

|                                                                   |               | DAPmn = 1                   | 120                |           | 120               |            | ns |

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

- Notes 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" and the SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 3. C is the load capacitance of the SOp output lines.

- 4. Transfer rate in the SNOOZE mode: MAX. 1 Mbps

**Remarks 1.** p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0)

fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

#### CSI mode connection diagram (during communication at same potential)

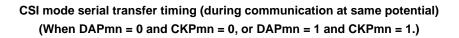

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

Remarks 1. p: CSI number (p = 00)2. m: Unit number, n: Channel number (mn = 00)

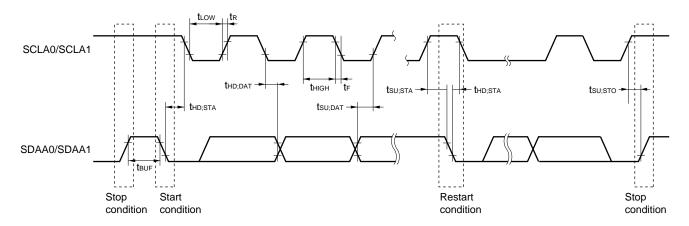

#### 2.5.2 Serial interface IICA

| Parameter                           | Symbol       | Conditions                                   | Standard<br>Mode |      | Fast Mode |      | Fast Mode<br>Plus |      | Unit |

|-------------------------------------|--------------|----------------------------------------------|------------------|------|-----------|------|-------------------|------|------|

|                                     |              |                                              | MIN.             | MAX. | MIN.      | MAX. | MIN.              | MAX. |      |

| SCLAn clock frequency               | fsc∟         | Fast mode plus: $f_{CLK} \ge 10 \text{ MHz}$ |                  |      |           |      | 0                 | 1000 | kHz  |

|                                     |              | Fast mode:<br>fc∟k ≥ 3.5 MHz                 |                  |      | 0         | 400  |                   |      | kHz  |

|                                     |              | Normal mode:<br>fc∟ĸ ≥ 1 MHz                 | 0                | 100  |           |      |                   |      | kHz  |

| Setup time of restart condition     | tsu:sta      |                                              | 4.7              |      | 0.6       |      | 0.26              |      | μs   |

| Hold time <sup>Note 1</sup>         | thd:sta      |                                              | 4.0              |      | 0.6       |      | 0.26              |      | μs   |

| Hold time when SCLAn = "L"          | tLOW         |                                              | 4.7              |      | 1.3       |      | 0.5               |      | μs   |

| Hold time when SCLAn = "H"          | tніgн        |                                              | 4.0              |      | 0.6       |      | 0.26              |      | μs   |

| Data setup time (reception)         | tsu:dat      |                                              | 250              |      | 100       |      | 50                |      | ns   |

| Data hold time (transmission)Note 2 | thd:dat      |                                              | 0                | 3.45 | 0         | 0.9  | 0                 | 0.45 | μs   |

| Setup time of stop condition        | tsu:sto      |                                              | 4.0              |      | 0.6       |      | 0.26              |      | μS   |

| Bus-free time                       | <b>t</b> BUF |                                              | 4.7              |      | 1.3       |      | 0.5               |      | μS   |

Notes 1. The first clock pulse is generated after this period when the start/restart condition is detected.

2. The maximum value (MAX.) of the:DAT is during normal transfer and a wait state is inserted in the ACK (acknowledge) timing.

#### IICA serial transfer timing

**Remarks 1.** The maximum value of C<sub>b</sub> (communication line capacitance) and the value of R<sub>b</sub> (communication line pull-up resistor) at that time in each mode are as follows.

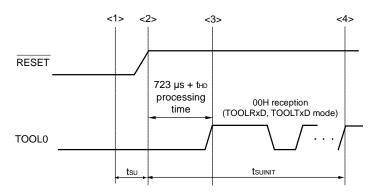

#### 2.5.3 Dedicated Flash Memory Programmer Communication (UART)

| Parameter     | Symbol | Conditions | MIN.    | TYP. | MAX. | Unit |

|---------------|--------|------------|---------|------|------|------|

| Transfer rate |        |            | 115.2 k |      | 1 M  | bps  |

#### 2.6 Analog Characteristics

#### 2.6.1 A/D converter characteristics

#### Classification of A/D converter characteristics

| Reference Voltage                 | Reference voltage (+) = AVREFP | Reference voltage (+) = VDD | Reference voltage (+) = VBGR    |

|-----------------------------------|--------------------------------|-----------------------------|---------------------------------|

| Input channel                     | Reference voltage (-) = AVREFM | Reference voltage (-) = Vss | Reference voltage (-) = AVREFM. |

| ANI0 to ANI7                      | Refer to 2.6.1 (1)             | Refer to 2.6.1 (2)          | Refer to 2.6.1 (5)              |

| ANI16                             | Refer to 2.6.1 (3)             | Refer to 2.6.1 (4)          |                                 |

| Internal reference voltage        | Refer to 2.6.1 (3)             | Refer to 2.6.1 (4)          | -                               |

| Temperature sensor output voltage |                                |                             |                                 |

# (1) When AVREF (+) = AVREFP/ANIO (ADREFP1 = 0, ADREFP0 = 1), AVREF (-) = AVREFM/ANI1 (ADREFM = 1), target ANI pin: ANIO to ANI7

| Parameter                                      | Symbol | Conditions                                                                                           | MIN.  | TYP. | MAX.   | Unit |

|------------------------------------------------|--------|------------------------------------------------------------------------------------------------------|-------|------|--------|------|

| Resolution                                     | RES    |                                                                                                      | 8     |      | 12     | bit  |

| Overall error <sup>Note 1</sup>                | AINL   | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            |       |      | ±6.0   | LSB  |

| Conversion time                                | tconv  | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            | 3.375 |      | 108    | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>         | Ezs    | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            |       |      | ±0.10  | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>         | Efs    | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            |       |      | ±0.10  | %FSR |

| Integral linearity error <sup>Note 1</sup>     | ILE    | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            |       |      | ±2.5   | LSB  |

| Differential linearity error <sup>Note 1</sup> | DLE    | 12-bit resolution<br>AV <sub>REFP</sub> = V <sub>DD</sub>                                            |       |      | ±1.5   | LSB  |

| Reference voltage (+)                          | AVREFP |                                                                                                      | 2.7   |      | Vdd    | V    |

| Reference voltage (-)                          | AVREFM |                                                                                                      | -0.5  |      | 0.3    | V    |

| Analog input voltage                           | VAIN   |                                                                                                      | 0     |      | AVREFP | V    |

|                                                | Vbgr   | Select internal reference voltage output 2.7 V $\leq$ V_{DD} $\leq$ 3.6 V, HS (high-speed main) mode | 1.38  | 1.45 | 1.5    | V    |

#### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V}, \text{Reference voltage (+)} = \text{AV}_{REFP}, \text{Reference voltage (-)} = \text{AV}_{REFM} = 0 \text{ V})$

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

**2.** This value is indicated as a ratio (%FSR) to the full-scale value.

#### (2) When AVREF (+) = VDD (ADREFP1 = 0, ADREFP0 = 0), AVREF (-) = Vss (ADREFM = 0), target ANI pin: ANI0 to ANI7

| Parameter                                  | Symbol        | Conditions                                                                                                                                                                                      | MIN.  | TYP. | MAX.   | Unit |

|--------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------|------|