# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# R8C/14 Group, R8C/15 Group SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0102-0200 Rev.2.00 Jan 30, 2006

### 1. Overview

This MCU is built using the high-performance silicon gate CMOS process using a R8C/Tiny Series CPU core and is packaged in a 20-pin plastic molded LSSOP. This MCU operates using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, it is capable of executing instructions at high speed.

Furthermore, the data flash ROM (1KB × 2blocks) is embedded in the R8C/15 group.

The difference between R8C/14 and R8C/15 groups is only the existence of the data flash ROM. Their peripheral functions are the same.

### 1.1 Applications

Electric household appliance, office equipment, housing equipment (sensor, security), general industrial equipment, audio, etc.

### 1.2 Performance Overview

Table 1.1 lists the Performance Outline of the R8C/14 Group and Table 1.2 lists the Performance Outline of the R8C/15 Group.

Table 1.1 Performance Outline of the R8C/14 Group

|                 | Item                         | Performance                                                    |

|-----------------|------------------------------|----------------------------------------------------------------|

| CPU             | Number of Basic Instructions |                                                                |

|                 | Minimum Instruction          | 50ns(f(XIN)=20MHz, VCC=3.0 to 5.5V)                            |

|                 | Execution Time               | 100ns(f(XIN)=10MHz, VCC=2.7 to 5.5V)                           |

|                 | Operating Mode               | Single-chip                                                    |

|                 | Memory Space                 | 1 Mbyte                                                        |

|                 | Memory Capacity              | See Table 1.3 R8C/14 Group Product Information                 |

| Peripheral      | Port                         | I/O port : 13 pins (including LED drive port),                 |

| Function        |                              | Input: 2 pins                                                  |

|                 | LED Drive Port               | I/O port: 4 pins                                               |

|                 | Timer                        | Timer X: 8 bits x 1 channel, Timer Z: 8 bits x 1 channel       |

|                 |                              | (Each timer equipped with 8-bit prescaler)                     |

|                 |                              | Timer C: 16 bits x 1 channel                                   |

|                 |                              | (Circuits of input capture and output compare)                 |

|                 | Serial Interface             | 1 channel                                                      |

|                 |                              | Clock synchronous serial I/O, UART                             |

|                 | Chip-Select Clock            | 1 channel                                                      |

|                 | Synchronous Serial I/O       |                                                                |

|                 | (SSU)                        |                                                                |

|                 | A/D Converter                | 10-bit A/D converter: 1 circuit, 4 channels                    |

|                 | Watchdog Timer               | 15 bits ×1 channel (with prescaler)                            |

| Ĭ               |                              | Reset start selectable, Count source protection mode           |

|                 | Interrupt                    | Internal: 9 factors, External: 4 factors, Software: 4 factors, |

|                 | •                            | Priority level: 7 levels                                       |

|                 | Clock Generation Circuit     | 2 circuits                                                     |

|                 |                              | Main clock oscillation circuit (Equipped with a built-in       |

|                 |                              | feedback resistor)                                             |

|                 |                              | On-chip oscillator (high speed, low speed)                     |

|                 |                              | Equipped with frequency adjustment function on high-           |

|                 |                              | speed on-chip oscillator                                       |

|                 | Oscillation Stop Detection   | Main clock oscillation stop detection function                 |

|                 | Function                     |                                                                |

|                 | Voltage Detection Circuit    | Included                                                       |

|                 | Power-On Reset Circuit       | Included                                                       |

| Electric        | Supply Voltage               | VCC=3.0 to 5.5V (f(XIN)=20MHz)                                 |

| Characteristics |                              | VCC=2.7 to 5.5V (f(XIN)=10MHz)                                 |

|                 | Power Consumption            | Typ. 9mA (VCC=5.0V, f(XIN)=20MHz)                              |

|                 | ·                            | Typ. 5mA (VCC=3.0V, f(XIN)=10MHz)                              |

|                 |                              | Typ. 35μA (VCC=3.0V, wait mode, peripheral clock off)          |

|                 |                              | Typ. 0.7μA (VCC=3.0V, stop mode)                               |

| Flash Memory    | Program/Erase Supply         | VCC=2.7 to 5.5V                                                |

|                 | Voltage                      |                                                                |

|                 | Program/Erase Endurance      | 100 times                                                      |

| Operating Ambi  | ent Temperature              | -20 to 85°C                                                    |

| ,               | - p                          | -40 to 85°C (D Version)                                        |

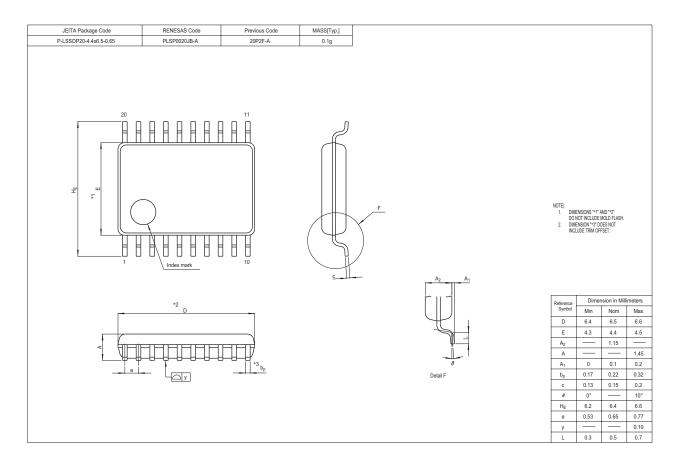

| Package         |                              | 20-pin plastic mold LSSOP                                      |

|                 |                              | 1 - c L L. 2000                                                |

Table 1.2 Performance Outline of the R8C/15 Group

| Table 1.2 P     | Item                         | Performance                                                   |

|-----------------|------------------------------|---------------------------------------------------------------|

| CPU             | Number of Basic Instructions | 89 instructions                                               |

| CPU             | Minimum Instruction          | 50ns (f(XIN)=20MHz, VCC=3.0 to 5.5V)                          |

|                 |                              |                                                               |

|                 | Execution Time               | 100ns (f(XIN)=10MHz, VCC=2.7 to 5.5V)                         |

|                 | Operating Mode               | Single-chip                                                   |

|                 | Memory Space                 | 1 Mbyte                                                       |

|                 | Memory Capacity              | See Table 1.4 R8C/15 Group Product Information                |

| Peripheral      | Port                         | I/O : 13 pins (including LED drive port),                     |

| Function        |                              | Input: 2 pins                                                 |

|                 | LED drive port               | I/O port: 4 pins                                              |

|                 | Timer                        | Timer X: 8 bits x 1 channel, Timer Z: 8 bits x 1 channel      |

|                 |                              | (Each timer equipped with 8-bit prescaler)                    |

|                 |                              | Timer C: 16 bits x 1 channel                                  |

|                 |                              | (Circuits of input capture and output compare)                |

|                 | Serial Interface             | 1 channel                                                     |

|                 |                              | Clock synchronous serial I/O, UART                            |

|                 | Chip-select clock            | 1 channel                                                     |

|                 | synchronous serial I/O (SSU) |                                                               |

|                 | A/D Converter                | 10-bit A/D converter: 1 circuit, 4 channels                   |

|                 | Watchdog Timer               | 15 bits × 1 channel (with prescaler)                          |

|                 | Trateriaeg Timer             | Reset start selectable, Count source protection mode          |

|                 | Interrupt                    | Internal: 9 factors, External: 4 factors, Software: 4 factors |

|                 | Interrupt                    | Priority level: 7 levels                                      |

|                 | Clock Generation Circuit     | 2 circuits                                                    |

|                 | Clock Generation Circuit     |                                                               |

|                 |                              | Main clock generation circuit (Equipped with a built-in       |

|                 |                              | feedback resistor)                                            |

|                 |                              | On-chip oscillator (high speed, low speed)                    |

|                 |                              | Equipped with frequency adjustment function on high-          |

|                 |                              | speed on-chip oscillator                                      |

|                 | Oscillation Stop Detection   | Main clock oscillation stop detection function                |

|                 | Function                     |                                                               |

|                 | Voltage Detection Circuit    | Included                                                      |

|                 | Power on Reset Circuit       | Included                                                      |

| Electric        | Supply Voltage               | VCC=3.0 to 5.5V (f(XIN)=20MHz)                                |

| Characteristics |                              | VCC=2.7 to 5.5V (f(XIN)=10MHz)                                |

|                 | Power Consumption            | Typ. 9mA (VCC=5.0V, f(XIN)=20MHz)                             |

|                 |                              | Typ. 5mA (VCC=3.0V, f(XIN)=10MHz)                             |

|                 |                              | Typ. 35μA (VCC=3.0V, wait mode, peripheral clock off)         |

|                 |                              | Typ. $0.7\mu A$ (VCC=3.0V, stop mode)                         |

| Flash Memory    | Program/Erase Supply         | VCC=2.7 to 5.5V                                               |

| ac.i Momory     | Voltage                      |                                                               |

|                 | Program/Erase Endurance      | 10,000 times (Data flash)                                     |

|                 | Togram Erass Eradianos       | 1,000 times (Pata hash)                                       |

| Operating Ambi  | l<br>ient Temperature        | -20 to 85°C                                                   |

|                 | one remperature              | -40 to 85°C (D Version)                                       |

| Package         |                              | 20-pin plastic mold LSSOP                                     |

| Package         |                              | Zu-pin piastic molu LSSOF                                     |

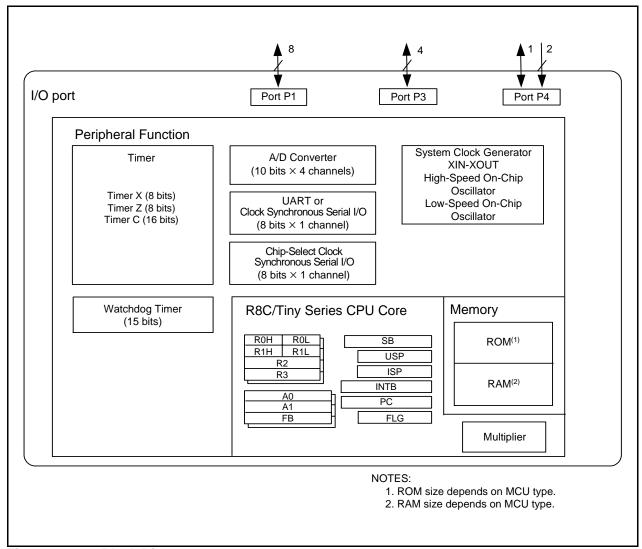

### 1.3 Block Diagram

Figure 1.1 shows a Block Diagram.

Figure 1.1 Block Diagram

### 1.4 Product Information

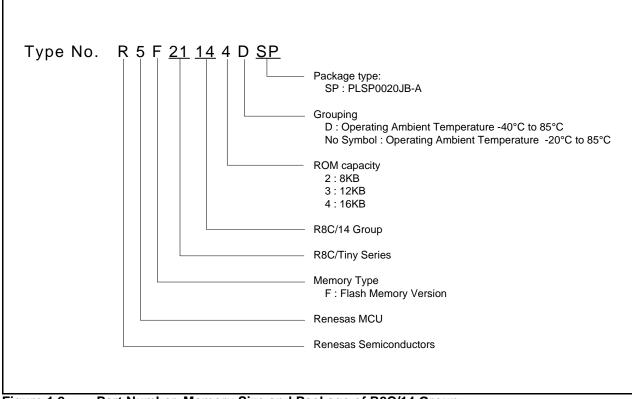

Table 1.3 lists the Product Information of R8C/14 Group and Table 1.4 lists the Product Information of R8C/15 Group.

Table 1.3 Product Information of R8C/14 Group

As of Jan 2006

| Type No.    | ROM capacity | RAM capacity | Package type | Remarks              |

|-------------|--------------|--------------|--------------|----------------------|

| R5F21142SP  | 8 Kbytes     | 512 bytes    | PLSP0020JB-A | Flash memory version |

| R5F21143SP  | 12 Kbytes    | 768 bytes    | PLSP0020JB-A |                      |

| R5F21144SP  | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |                      |

| R5F21142DSP | 8 Kbytes     | 512 bytes    | PLSP0020JB-A | D version            |

| R5F21143DSP | 12 Kbytes    | 768 bytes    | PLSP0020JB-A |                      |

| R5F21144DSP | 16 Kbytes    | 1 Kbyte      | PLSP0020JB-A |                      |

Figure 1.2 Part Number, Memory Size and Package of R8C/14 Group

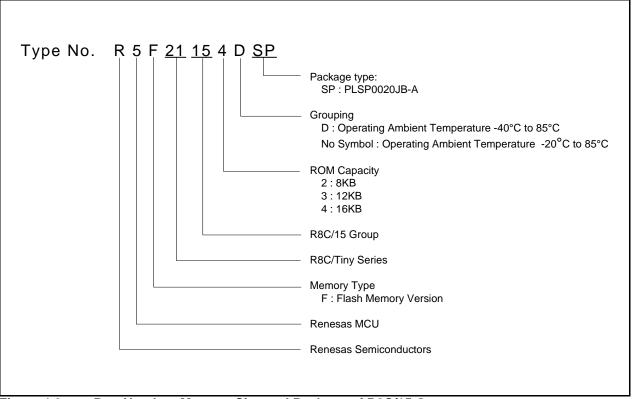

Table 1.4 Product Information of R8C/15 Group

### As of Jan 2006

| Type No.    | ROM capacity |             | RAM       | Package type | Remarks              |

|-------------|--------------|-------------|-----------|--------------|----------------------|

| Type No.    | Program ROM  | Data flash  | capacity  | Fackage type | Remarks              |

| R5F21152SP  | 8 Kbytes     | 1 Kbyte x 2 | 512 bytes | PLSP0020JB-A | Flash memory version |

| R5F21153SP  | 12 Kbytes    | 1 Kbyte × 2 | 768 bytes | PLSP0020JB-A |                      |

| R5F21154SP  | 16 Kbytes    | 1 Kbyte × 2 | 1 Kbyte   | PLSP0020JB-A |                      |

| R5F21152DSP | 8 Kbytes     | 1 Kbyte x 2 | 512 bytes | PLSP0020JB-A | D version            |

| R5F21153DSP | 12 Kbytes    | 1 Kbyte × 2 | 768 bytes | PLSP0020JB-A |                      |

| R5F21154DSP | 16 Kbytes    | 1 Kbyte × 2 | 1 Kbyte   | PLSP0020JB-A |                      |

Figure 1.3 Part Number, Memory Size and Package of R8C/15 Group

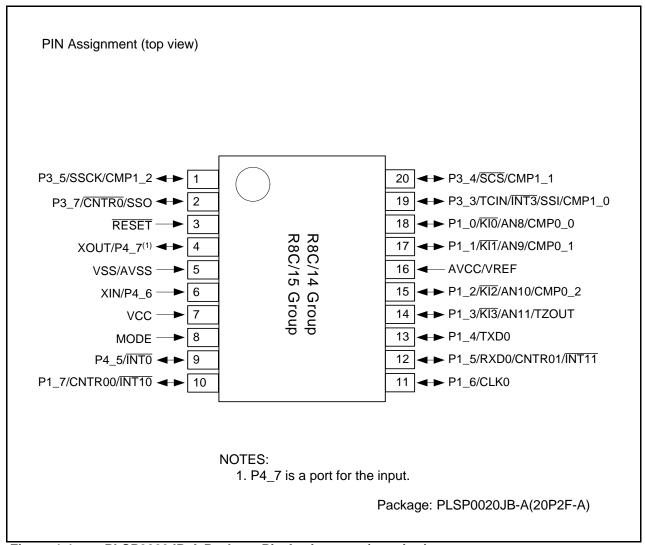

### 1.5 Pin Assignments

Figure 1.4 shows the PLSP0020JB-A Package Pin Assignment (top view).

Figure 1.4 PLSP0020JB-A Package Pin Assignment (top view)

# 1.6 Pin Description

Table 1.5 lists the Pin Description and Table 1.6 lists the Pin Name Information by Pin Number.

Table 1.5 Pin Description

| Function                     | Pin name                                  | I/O type | Description                                                                                                                                                                                                                                                                                           |

|------------------------------|-------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply Input           | VCC<br>VSS                                | I        | Apply 2.7V to 5.5V to the VCC pin. Apply 0V to the VSS pin                                                                                                                                                                                                                                            |

| Analog Power Supply<br>Input | AVCC<br>AVSS                              | I        | Power supply input pins to A/D converter. Connect AVCC to VCC. Apply 0V to AVSS. Connect a capacitor between AVCC and AVSS.                                                                                                                                                                           |

| Reset Input                  | RESET                                     | I        | Input "L" on this pin resets the MCU                                                                                                                                                                                                                                                                  |

| MODE                         | MODE                                      | I        | Connect this pin to VCC via a resistor                                                                                                                                                                                                                                                                |

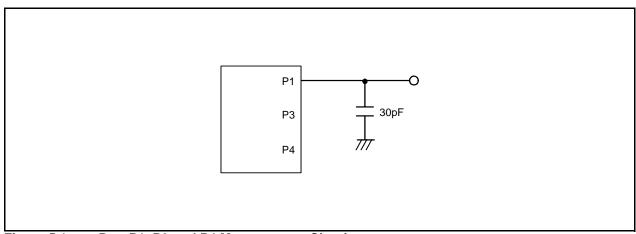

| Main Clock Input             | XIN                                       | I        | These pins are provided for the main clock                                                                                                                                                                                                                                                            |

| Main Clock Output            | XOUT                                      | 0        | generation circuit I/O. Connect a ceramic resonator or a crystal oscillator between the XIN and XOUT pins. To use an externally derived clock, input it to the XIN pin and leave the XOUT pin open.                                                                                                   |

| INT Interrupt                | ĪNTO, ĪNT1, ĪNT3                          | I        | INT interrupt input pins                                                                                                                                                                                                                                                                              |

| Key Input Interrupt          | KI0 to KI3                                | I        | Key input interrupt input pins                                                                                                                                                                                                                                                                        |

| Timer X                      | CNTR0                                     | I/O      | Timer X I/O pin                                                                                                                                                                                                                                                                                       |

|                              | CNTR0                                     | 0        | Timer X output pin.                                                                                                                                                                                                                                                                                   |

| Timer Z                      | TZOUT                                     | 0        | Timer Z output pin                                                                                                                                                                                                                                                                                    |

| Timer C                      | TCIN                                      | I        | Timer C input pin                                                                                                                                                                                                                                                                                     |

|                              | CMP0_0 to CMP0_2,<br>CMP1_0 to CMP1_2     | 0        | Timer C output pins.                                                                                                                                                                                                                                                                                  |

| Serial Interface             | CLK0                                      | I/O      | Transfer clock I/O pin.                                                                                                                                                                                                                                                                               |

|                              | RXD0                                      | I        | Serial data input pin.                                                                                                                                                                                                                                                                                |

|                              | TXD0                                      | 0        | Serial data output pin.                                                                                                                                                                                                                                                                               |

| SSU                          | SSI                                       | I/O      | Data I/O pin.                                                                                                                                                                                                                                                                                         |

|                              | SCS                                       | I/O      | Chip-select signal I/O pin.                                                                                                                                                                                                                                                                           |

|                              | SSCK                                      | I/O      | Clock I/O pin.                                                                                                                                                                                                                                                                                        |

|                              | SSO                                       | I/O      | Data I/O pin.                                                                                                                                                                                                                                                                                         |

| Reference Voltage<br>Input   | VREF                                      | I        | Reference voltage input pin to A/D converter Connect VREF to VCC                                                                                                                                                                                                                                      |

| A/D Converter                | AN8 to AN11                               | I        | Analog input pins to A/D converter                                                                                                                                                                                                                                                                    |

| I/O Port                     | P1_0 to P1_7, P3_3<br>to P3_5, P3_7, P4_5 | I/O      | These are CMOS I/O ports. Each port contains an I/O select direction register, allowing each pin in that port to be directed for input or output individually.  Any port set to input can select whether to use a pull-up resistor or not by program.  P1_0 to P1_3 also function as LED drive ports. |

| Input Port                   | P4_6, P4_7                                | I        | Port for input-only                                                                                                                                                                                                                                                                                   |

I: Input

O: Output

I/O: Input and output

Table 1.6 Pin Name Information by Pin Number

|               |                |      | I/O Pin of Peripheral Function |             |                     |                                         |                  |  |

|---------------|----------------|------|--------------------------------|-------------|---------------------|-----------------------------------------|------------------|--|

| Pin<br>Number | Control<br>Pin | Port | Interrupt                      | Timer       | Serial<br>Interface | Clock<br>Synchronous<br>Serial I/O with | A/D<br>Converter |  |

| 1             |                | P3_5 |                                | CMP1_2      |                     | Chip Select<br>SSCK                     |                  |  |

| 2             |                | P3_7 |                                | CNTR0       |                     | SSO                                     |                  |  |

| 3             | RESET          |      |                                | 011110      |                     |                                         |                  |  |

| 4             | XOUT           | P4_7 |                                |             |                     |                                         |                  |  |

| 5             | VSS/AVSS       |      |                                |             |                     |                                         |                  |  |

| 6             | XIN            | P4_6 |                                |             |                     |                                         |                  |  |

| 7             | VCC            |      |                                |             |                     |                                         |                  |  |

| 8             | MODE           |      |                                |             |                     |                                         |                  |  |

| 9             |                | P4_5 | ĪNT0                           |             |                     |                                         |                  |  |

| 10            |                | P1_7 | ĪNT10                          | CNTR00      |                     |                                         |                  |  |

| 11            |                | P1_6 |                                |             | CLK0                |                                         |                  |  |

| 12            |                | P1_5 | ĪNT11                          | CNTR01      | RXD0                |                                         |                  |  |

| 13            |                | P1_4 |                                |             | TXD0                |                                         |                  |  |

| 14            |                | P1_3 | KI3                            | TZOUT       |                     |                                         | AN11             |  |

| 15            |                | P1_2 | KI2                            | CMP0_2      |                     |                                         | AN10             |  |

| 16            | AVCC/VREF      |      |                                |             |                     |                                         |                  |  |

| 17            |                | P1_1 | KI1                            | CMP0_1      |                     |                                         | AN9              |  |

| 18            |                | P1_0 | KI0                            | CMP0_0      |                     |                                         | AN8              |  |

| 19            |                | P3_3 | ĪNT3                           | TCIN/CMP1_0 |                     | SSI                                     |                  |  |

| 20            |                | P3_4 |                                | CMP1_1      |                     | SCS                                     |                  |  |

# 2. Central Processing Unit (CPU)

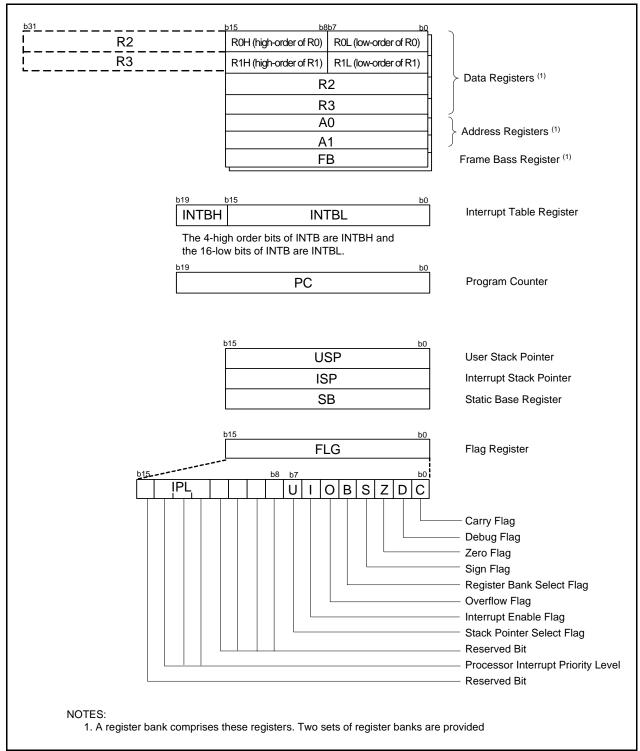

Figure 2.1 shows the CPU Register. The CPU contains 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. Two sets of register banks are provided.

Figure 2.1 CPU Register

### 2.1 Data Registers (R0, R1, R2 and R3)

R0 is a 16-bit register for transfer, arithmetic and logic operations. The same applies to R1 to R3. The R0 can be split into high-order bit (R0H) and low-order bit (R0L) to be used separately as 8-bit data registers. The same applies to R1H and R1L as R0H and R0L. R2 can be combined with R0 to be used as a 32-bit data register (R2R0). The same applies to R3R1 as R2R0.

### 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. They also are used for transfer, arithmetic and logic operations. The same applies to A1 as A0. A0 can be combined with A0 to be used as a 32-bit address register (A1A0).

### 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

### 2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register indicates the start address of an interrupt vector table.

### 2.5 Program Counter (PC)

PC, 20 bits wide, indicates the address of an instruction to be executed.

### 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointer (SP), USP and ISP, are 16 bits wide each. The U flag of FLG is used to switch between USP and ISP.

### 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

### 2.8 Flag Register (FLG)

FLG is a 11-bit register indicating the CPU state.

### 2.8.1 **Carry Flag (C)**

The C flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic logic unit.

### 2.8.2 Debug Flag (D)

The D flag is for debug only. Set to "0".

### 2.8.3 **Zero Flag (Z)**

The Z flag is set to "1" when an arithmetic operation resulted in 0; otherwise, "0".

### 2.8.4 Sign Flag (S)

The S flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, "0".

### 2.8.5 Register Bank Select Flag (B)

The register bank 0 is selected when the B flag is "0". The register bank 1 is selected when this flag is set to "1".

### 2.8.6 Overflow Flag (O)

The O flag is set to "1" when the operation resulted in an overflow; otherwise, "0".

### 2.8.7 Interrupt Enable Flag (I Flag)

The I flag enables a maskable interrupt.

An interrupt is disabled when the I flag is set to "0", and are enabled when the I flag is set to "1". The I flag is set to "0" when an interrupt request is acknowledged.

### 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is set to "0", USP is selected when the U flag is set to "1". The U flag is set to "0" when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.

### 2.8.9 Processor Interrupt Priority Level (IPL)

IPL, 3 bits wide, assigns processor interrupt priority levels from level 0 to level 7. If a requested interrupt has greater priority than IPL, the interrupt is enabled.

### 2.8.10 Reserved Bit

When write to this bit, set to "0". When read, its content is indeterminate.

#### 3. **Memory**

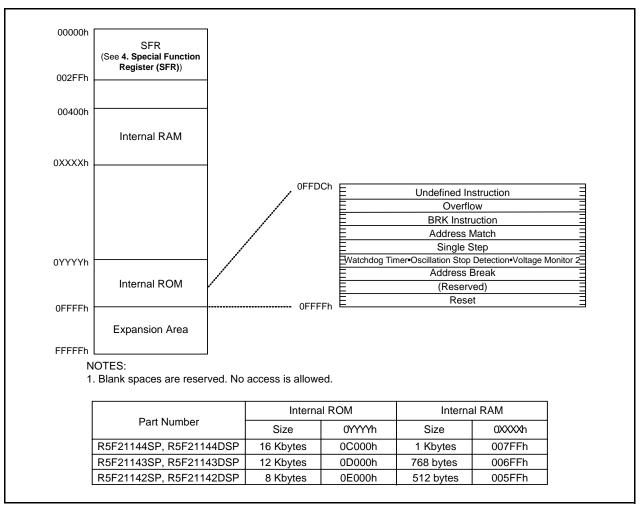

#### 3.1 R8C/14 Group

Figure 3.1 is a Memory Map of R8C/14 Group. The R8C/14 group provides 1-Mbyte address space from addresses 00000h to FFFFFh.

The internal ROM is allocated lower addresses beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM is allocated addresses 0C000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal RAM is allocated higher addresses beginning with address 00400h. For example, a 1-Kbyte internal RAM is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but for calling subroutines and stacks when interrupt request is acknowledged.

Special function registers (SFR) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated them. All addresses, which have nothing allocated within the SFR, are reserved area and cannot be accessed by users.

Figure 3.1 Memory Map of R8C/14 Group

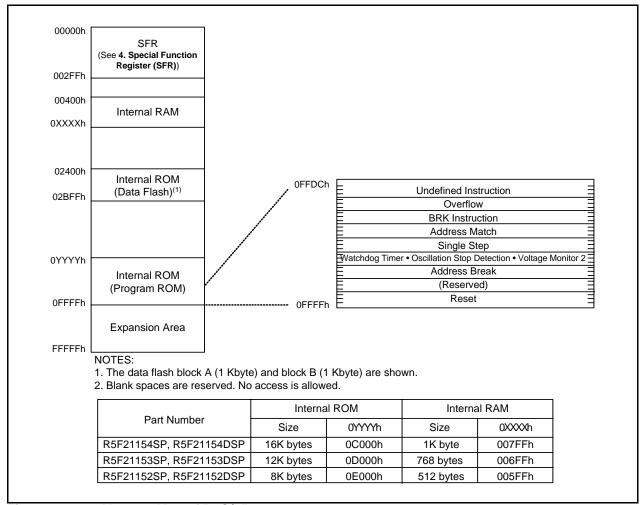

#### 3.2 R8C/15 Group

Figure 3.2 is a Memory Map of R8C/15 Group. The R8C/15 group provides 1-Mbyte address space from addresses 00000h to FFFFFh.

The internal ROM (program ROM) is allocated lower addresses beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM is allocated addresses 0C000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.

The internal RAM is allocated higher addresses beginning with address 00400h. For example, a 1-Kbyte internal RAM is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but for calling subroutines and stacks when interrupt request is acknowledged.

Special function registers (SFR) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated them. All addresses, which have nothing allocated within the SFR, are reserved area and cannot be accessed by users.

Figure 3.2 Memory Map of R8C/15 Group

# 4. Special Function Register (SFR)

SFR (Special Function Register) is the control register of peripheral functions. Tables 4.1 to 4.4 list the SFR information.

Table 4.1 SFR Information(1)<sup>(1)</sup>

|         |                                                  |        | A.C.                                    |

|---------|--------------------------------------------------|--------|-----------------------------------------|

| Address | Register                                         | Symbol | After reset                             |

| 0000h   |                                                  |        |                                         |

| 0001h   |                                                  |        |                                         |

| 0002h   |                                                  |        |                                         |

| 0003h   |                                                  |        |                                         |

| 0004h   | Processor Mode Register 0                        | PM0    | 00h                                     |

| 0005h   | Processor Mode Register 1                        | PM1    | 00h                                     |

| 0006h   | System Clock Control Register 0                  | CM0    | 01101000b                               |

| 0007h   | System Clock Control Register 1                  | CM1    | 00100000b                               |

| 0008h   |                                                  |        |                                         |

| 0009h   | Address Match Interrupt Enable Register          | AIER   | 00h                                     |

| 000Ah   | Protect Register                                 | PRCR   | 00h                                     |

| 000Bh   |                                                  |        |                                         |

| 000Ch   | Oscillation Stop Detection Register              | OCD    | 00000100b                               |

| 000Dh   | Watchdog Timer Reset Register                    | WDTR   | XXh                                     |

| 000Eh   | Watchdog Timer Start Register                    | WDTS   | XXh                                     |

| 000Fh   | Watchdog Timer Control Register                  | WDC    | 00011111b                               |

| 0010h   | Address Match Interrupt Register 0               | RMAD0  | 00h                                     |

| 0011h   |                                                  |        | 00h                                     |

| 0012h   |                                                  |        | X0h                                     |

| 0013h   |                                                  |        |                                         |

| 0014h   | Address Match Interrupt Register 1               | RMAD1  | 00h                                     |

| 0015h   | 1                                                |        | 00h                                     |

| 0016h   | †                                                |        | X0h                                     |

| 0017h   |                                                  |        |                                         |

| 0018h   |                                                  |        |                                         |

| 0019h   |                                                  |        |                                         |

| 001Ah   |                                                  |        |                                         |

| 001Bh   |                                                  |        |                                         |

| 001Ch   | Count Source Protection Mode Register            | CSPR   | 00h                                     |

| 001Dh   | Count Source Frotection wode Register            | COFIC  | 0011                                    |

| 001Eh   |                                                  | INTOF  | 00h                                     |

|         | INT0 Input Filter Select Register                | INTOF  | 0011                                    |

| 001Fh   |                                                  |        |                                         |

| 0020h   | High-Speed On-Chip Oscillator Control Register 0 | HRA0   | 00h                                     |

| 0021h   | High-Speed On-Chip Oscillator Control Register 1 | HRA1   | When shipping                           |

| 0022h   | High-Speed On-Chip Oscillator Control Register 2 | HRA2   | 00h                                     |

| 0023h   |                                                  |        |                                         |

|         |                                                  |        |                                         |

| 002Ah   |                                                  |        |                                         |

| 002Bh   |                                                  |        |                                         |

| 002Ch   |                                                  |        |                                         |

| 002Dh   |                                                  |        |                                         |

| 002Eh   |                                                  |        |                                         |

| 002Fh   |                                                  |        |                                         |

| 0030h   |                                                  |        |                                         |

| 0031h   | Voltage Detection Register 1 <sup>(2)</sup>      | VCA1   | 00001000b                               |

| 0032h   | Voltage Detection Register 2 <sup>(2)</sup>      | VCA2   | 00h <sup>(3)</sup>                      |

|         | Total 2 of other in the global 200               |        | 01000000b <sup>(4)</sup>                |

| 0033h   |                                                  |        | 010000000000000000000000000000000000000 |

| 0033h   |                                                  |        |                                         |

| 0034h   |                                                  |        |                                         |

| 0035h   |                                                  | VW1C   | 000000000000000000000000000000000000000 |

| 110000  | Voltage Monitor 1 Circuit Control Register (2)   | VVVIC  | 0000X000b <sup>(3)</sup>                |

|         |                                                  |        | 0100X001b <sup>(4)</sup>                |

| 0037h   | Voltage Monitor 2 Circuit Control Register (5)   | VW2C   | 00h                                     |

| 0038h   |                                                  |        |                                         |

| 0039h   |                                                  |        |                                         |

| 003Ah   |                                                  |        |                                         |

| 003Bh   |                                                  |        |                                         |

| 003Ch   |                                                  |        |                                         |

| 003Dh   |                                                  |        |                                         |

|         |                                                  |        |                                         |

| 003Eh   |                                                  |        |                                         |

### X: Undefined

- 1. Blank spaces are reserved. No access is allowed.

- 2. Software reset, the watchdog timer reset or the voltage monitor 2 reset does not affect this register.

- 3. Owing to Hardware reset.

- 4. Owing to Power-on reset or the voltage monitor 1 reset.

- 5. Software reset, the watchdog timer reset or the voltage monitor 2 reset does not affect the b2 and b3.

SFR Information(2)<sup>(1)</sup> Table 4.2

| Address                 | Register                                  | Symbol | After reset |

|-------------------------|-------------------------------------------|--------|-------------|

| 0040h                   | 1.1.5.1.1.                                | 5,     |             |

| 0041h                   |                                           |        |             |

| 0042h                   |                                           |        |             |

| 0043h                   |                                           |        |             |

| 0044h                   |                                           |        |             |

| 0045h                   |                                           |        |             |

| 0046h                   |                                           |        |             |

| 0047h                   |                                           |        |             |

| 0048h                   |                                           |        |             |

| 0049h                   |                                           |        |             |

| 004Ah                   |                                           |        |             |

| 004Bh                   |                                           |        |             |

| 004Ch                   |                                           |        |             |

| 004Dh                   | Key Input Interrupt Control Register      | KUPIC  | XXXXX000b   |

| 004Eh                   | A/D Conversion Interrupt Control Register | ADIC   | XXXXX000b   |

| 004Fh                   | SSU Interrupt Control Register            | SSUAIC | XXXXX000b   |

| 0050h                   | Compare 1 Interrupt Control Register      | CMP1IC | XXXXX000b   |

| 0050H                   | UART0 Transmit Interrupt Control Register | SOTIC  | XXXXX000b   |

| 0051h                   | UARTO Receive Interrupt Control Register  | SORIC  | XXXXX000b   |

| 0052H                   | Ontro receive interrupt control register  | SURIC  | 77777000D   |

| 0053h                   |                                           |        |             |

| 0054H                   |                                           |        |             |

| 0056h                   | Timer X Interrupt Control Register        | TXIC   | XXXXX000b   |

| 0056h                   | Times A interrupt Control Register        | IAIC   | ^^^^0       |

| 0057h<br>0058h          | Timor 7 Interrupt Control Projector       | TZIC   | XXXXX000b   |

| 0059h                   | Timer Z Interrupt Control Register        | INT1IC | XXXXX000b   |

|                         | INT1 Interrupt Control Register           |        |             |

| 005Ah                   | INT3 Interrupt Control Register           | INT3IC | XXXXX000b   |

| 005Bh                   | Timer C Interrupt Control Register        | TCIC   | XXXXX000b   |

| 005Ch                   | Compare 0 Interrupt Control Register      | CMP0IC | XXXXX000b   |

| 005Dh                   | INTO Interrupt Control Register           | INT0IC | XX00X000b   |

| 005Eh                   | intro interrupt control register          |        |             |

| 005Fh                   |                                           |        |             |

| 0060h                   |                                           |        |             |

| 0061h                   |                                           |        |             |

| 0062h                   |                                           |        |             |

| 0063h                   |                                           |        |             |

| 0064h                   |                                           |        |             |

| 0065h                   |                                           |        |             |

| 0066h                   |                                           |        |             |

| 0067h                   |                                           |        |             |

| 0067H                   |                                           |        |             |

| 0069h                   |                                           |        |             |

| 0069H                   |                                           |        |             |

| 006An                   |                                           |        |             |

|                         |                                           |        |             |

| 006Ch                   |                                           |        |             |

| 006Dh                   |                                           |        |             |

| 006Eh                   |                                           |        |             |

| 006Fh                   |                                           |        |             |

| 0070h                   |                                           |        |             |

| 0071h                   |                                           |        |             |

| 0072h                   |                                           |        |             |

| 0073h                   |                                           |        |             |

| 0074h                   |                                           |        |             |

| 0075h                   |                                           |        |             |

| 0076h                   |                                           |        |             |

| 0077h                   |                                           |        |             |

| 0078h                   |                                           |        |             |

| 0079h                   |                                           |        |             |

| 007Ah                   |                                           |        |             |

| 007Bh                   |                                           |        |             |

| 007Ch                   |                                           |        |             |

|                         | 1                                         |        |             |

| 007Dh                   |                                           |        |             |

| 007Dh<br>007Eh<br>007Fh |                                           |        |             |

X: Undefined

NOTES:

1. Blank spaces are reserved. No access is allowed.

SFR Information(3)(1) Table 4.3

| Address                                                                                         | Register                                                                                                                              | Symbol                                | After reset                     |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------|

| 0080h                                                                                           | Timer Z Mode Register                                                                                                                 | TZMR                                  | 00h                             |

| 0081h                                                                                           | Time: 2 mad Nagista                                                                                                                   | . =                                   | 55                              |

| 0082h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0083h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0084h                                                                                           | Timer Z Waveform Output Control Register                                                                                              | PUM                                   | 00h                             |

| 0085h                                                                                           | Prescaler Z Register                                                                                                                  | PREZ                                  | FFh                             |

| 0086h                                                                                           | Timer Z Secondary Register                                                                                                            | TZSC                                  | FFh                             |

| 0087h                                                                                           | Timer Z Primary Register                                                                                                              | TZPR                                  | FFh                             |

|                                                                                                 | Timer Z Primary Register                                                                                                              | IZPR                                  | FFII                            |

| 0088h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0089h                                                                                           |                                                                                                                                       |                                       |                                 |

| 008Ah                                                                                           | Timer Z Output Control Register                                                                                                       | TZOC                                  | 00h                             |

| 008Bh                                                                                           | Timer X Mode Register                                                                                                                 | TXMR                                  | 00h                             |

| 008Ch                                                                                           | Prescaler X Register                                                                                                                  | PREX                                  | FFh                             |

| 008Dh                                                                                           | Timer X Register                                                                                                                      | TX                                    | FFh                             |

| 008Eh                                                                                           | Timer Count Source Setting Register                                                                                                   | TCSS                                  | 00h                             |

| 008Fh                                                                                           |                                                                                                                                       |                                       |                                 |

| 0090h                                                                                           | Timer C Register                                                                                                                      | TC                                    | 00h                             |

| 0091h                                                                                           | <del>-</del>                                                                                                                          |                                       | 00h                             |

| 0092h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0093h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0094h                                                                                           |                                                                                                                                       |                                       |                                 |

| 0094H                                                                                           |                                                                                                                                       |                                       |                                 |

| 0095h                                                                                           | External Input Enable Register                                                                                                        | INTEN                                 | 00h                             |

| 0096h                                                                                           | External Iliput Eliable Negistel                                                                                                      | IINTEIN                               | OOII                            |

|                                                                                                 | Was land Frankla Baristan                                                                                                             | KIENI                                 | 001-                            |

| 0098h                                                                                           | Key Input Enable Register                                                                                                             | KIEN                                  | 00h                             |

| 0099h                                                                                           |                                                                                                                                       |                                       |                                 |

| 009Ah                                                                                           | Timer C Control Register 0                                                                                                            | TCC0                                  | 00h                             |

| 009Bh                                                                                           | Timer C Control Register 1                                                                                                            | TCC1                                  | 00h                             |

| 009Ch                                                                                           | Capture, Compare 0 Register                                                                                                           | TM0                                   | 00h                             |

| 009Dh                                                                                           |                                                                                                                                       |                                       | 00h <sup>(2)</sup>              |

| 009Eh                                                                                           | Compare 1 Register                                                                                                                    | TM1                                   | FFh                             |

| 009Fh                                                                                           | <u> </u>                                                                                                                              |                                       | FFh                             |

| 00A0h                                                                                           | UART0 Transmit/Receive Mode Register                                                                                                  | U0MR                                  | 00h                             |

| 00A1h                                                                                           | UART0 Bit Rate Register                                                                                                               | U0BRG                                 | XXh                             |

| 00A2h                                                                                           | UARTO Transmit Buffer Register                                                                                                        | U0TB                                  | XXh                             |

| 00A3h                                                                                           |                                                                                                                                       | 33.2                                  | XXh                             |

| 00A4h                                                                                           | UART0 Transmit/Receive Control Register 0                                                                                             | U0C0                                  | 00001000b                       |

| 00A5h                                                                                           | UARTO Transmit/Receive Control Register 1                                                                                             | U0C1                                  | 00001000b                       |

| 00A5h                                                                                           | UARTO Receive Buffer Register                                                                                                         | UORB                                  | XXh                             |

| 00Adh                                                                                           | OAKTO Receive Bullet Register                                                                                                         | OOKB                                  | XXh                             |

|                                                                                                 |                                                                                                                                       |                                       | AAII                            |

| 00A8h                                                                                           |                                                                                                                                       |                                       |                                 |

| 00A9h                                                                                           |                                                                                                                                       |                                       |                                 |

| 00AAh                                                                                           |                                                                                                                                       |                                       |                                 |

| 00ABh                                                                                           |                                                                                                                                       |                                       |                                 |

| 00ACh                                                                                           |                                                                                                                                       |                                       |                                 |

| 00ADh                                                                                           |                                                                                                                                       |                                       |                                 |

|                                                                                                 |                                                                                                                                       |                                       |                                 |

| 00AEh                                                                                           |                                                                                                                                       |                                       |                                 |

| 00AEh<br>00AFh                                                                                  |                                                                                                                                       |                                       |                                 |

|                                                                                                 | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh                                                                                           | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h                                                                                  | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h                                                                | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | OOh                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h                                                       | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h                                              | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h                                     | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h<br>00B6h                            | UART Transmit/Receive Control Register 2                                                                                              | UCON                                  | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h<br>00B6h                            |                                                                                                                                       |                                       |                                 |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h<br>00B6h<br>00B7h                   | SS Control Register H                                                                                                                 | SSCRH                                 | 00h                             |

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h<br>00B6h<br>00B7h<br>00B8h          | SS Control Register H SS Control Register L                                                                                           | SSCRH<br>SSCRL                        | 00h<br>7Dh                      |

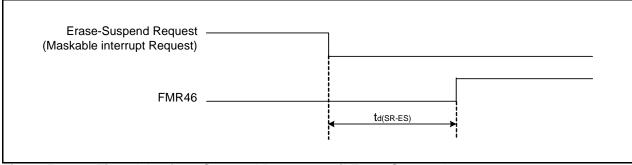

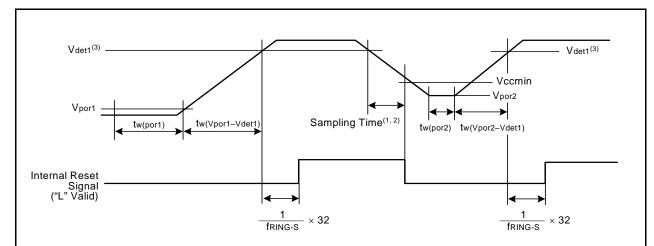

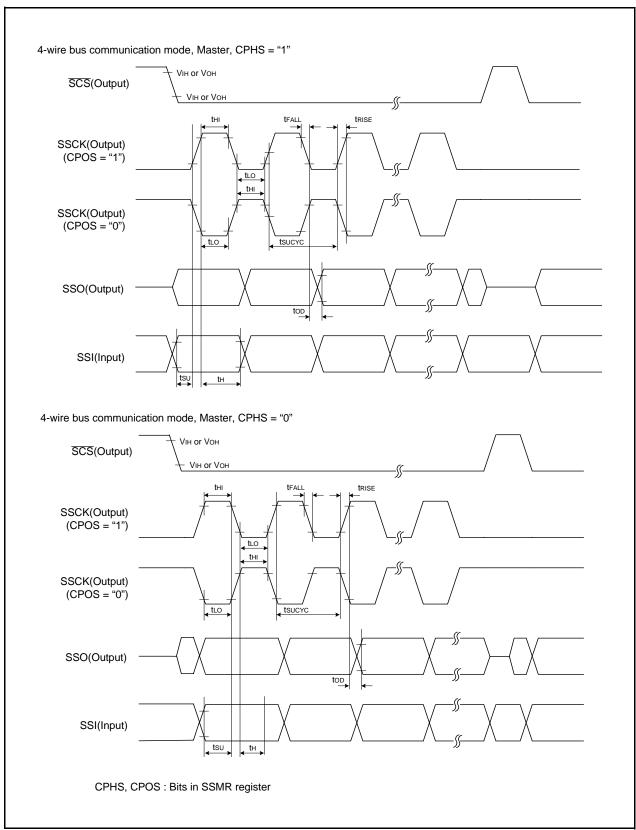

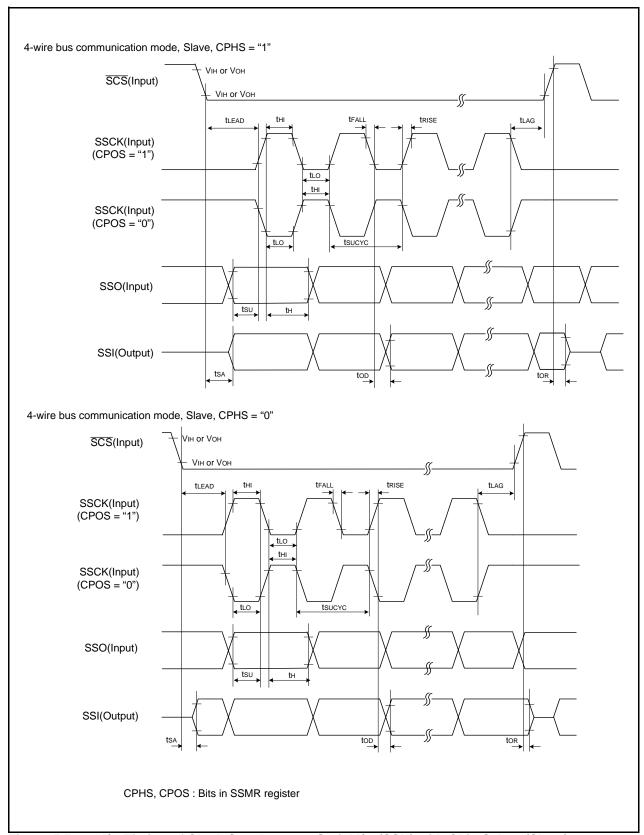

| 00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h<br>00B4h<br>00B5h<br>00B6h<br>00B7h<br>00B8h<br>00B9h | SS Control Register H SS Control Register L SS Mode Register                                                                          | SSCRH<br>SSCRL<br>SSMR                | 00h<br>7Dh<br>18h               |