# R32C/117 Group

# User's Manual: Hardware

RENESAS MCU M16C Family / R32C/100 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest informaton published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.1.10 Sep 2010

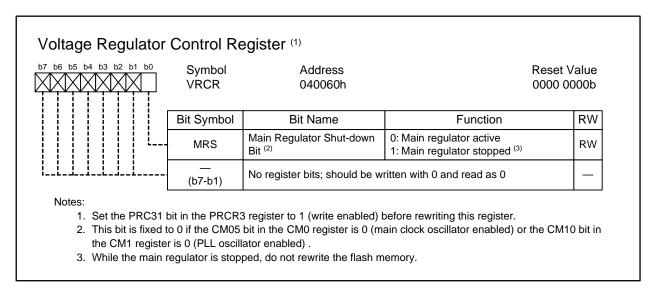

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

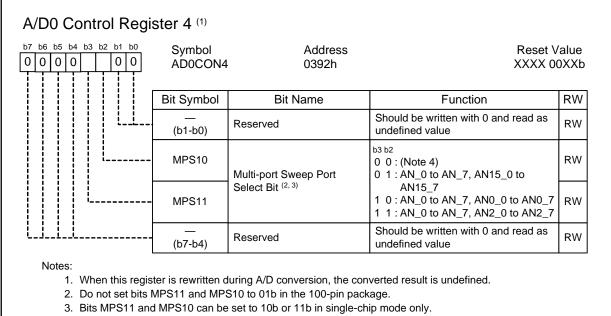

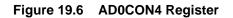

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

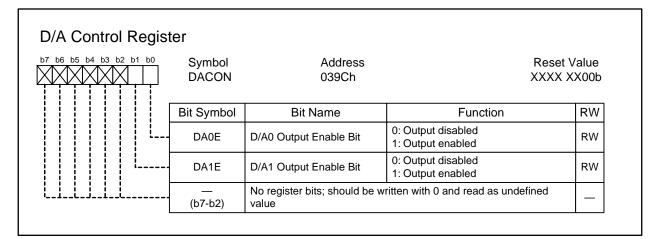

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

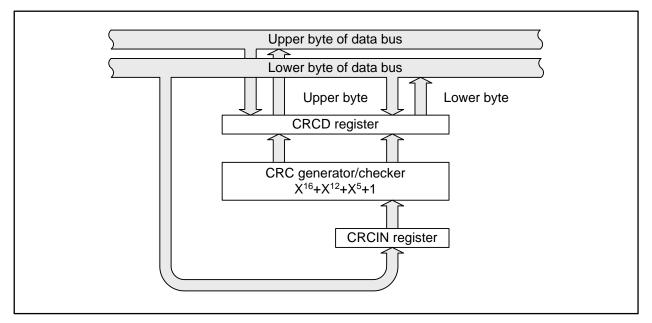

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

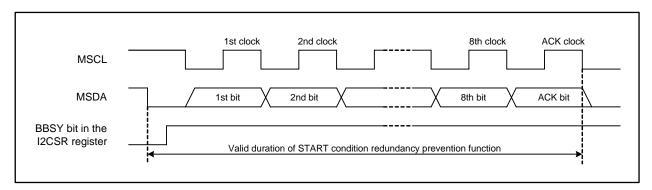

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# About This Manual

## 1. Purpose and Target User

This manual is designed to be read primarily by application developers who have an understanding of this microcomputer (MCU) including its hardware functions and electrical characteristics. The user should have a basic understanding of electric circuits, logic circuits and, MCUs.

This manual consists of 29 chapters covering six main categories: Overview, CPU, System Control, Peripherals, Electrical Characteristics, and Usage Notes.

Carefully read all notes in this document prior to use. Notes are found throughout each chapter, at the end of each chapter, and in the dedicated Usage Notes chapter.

The Revision History at the end of this manual summarizes primary modifications and additions to the previous versions. For details, please refer to the relative chapters or sections of this manual.

The R32C/117 Group includes the documents listed below. Verify this manual is the latest version by visiting the Renesas Electronics website.

| Type of Document                              | Contents                                                                                                                                                                                                            | Document Name                                | Document Number  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|

| Datasheet                                     | Overview of Hardware and Electrical Characteristics                                                                                                                                                                 | R32C/117 Group<br>Datasheet                  | REJ03B0254-0110  |

| User's Manual:<br>Hardware                    | Specifications and detailed<br>descriptions of:<br>-pin layout<br>-memory map<br>-peripherals<br>-electrical characteristics<br>-timing characteristics<br>Refer to the Application Manual for<br>peripheral usage. | R32C/117 Group<br>User's Manual:<br>Hardware | This publication |

| User's Manual:<br>Software/Software<br>Manual | Descriptions of instruction set                                                                                                                                                                                     | R32C/100 Series<br>Software Manual           | REJ09B0267-0100  |

| Application Note                              | -Usages<br>-Applications<br>-Sample programs<br>-Programing technics using<br>Assembly language or C<br>programming language                                                                                        | Available on the Rene<br>website.            | esas Electronics |

| Renesas Technical<br>Update                   | Bulletins on product specifications, documents, etc.                                                                                                                                                                |                                              |                  |

## 2. Numbers and Symbols

The following explains the denotations used in this manual for registers, bits, pins and various numbers.

(1) Registers, bits, and pins Registers, bits, and pins are indicated by symbols. Each symbol has a register/bit/pin identifier after the symbol. Example: PM03 bit in the PM0 register P3\_5 pin, VCC pin

(2) Numbers A binary number has the suffix "b" except for a 1-bit value. A hexadecimal number has the suffix "h". A decimal number has no suffix. Example: Binary notation: 11b Hexadecimal notation: EFA0h Decimal notation: 1234

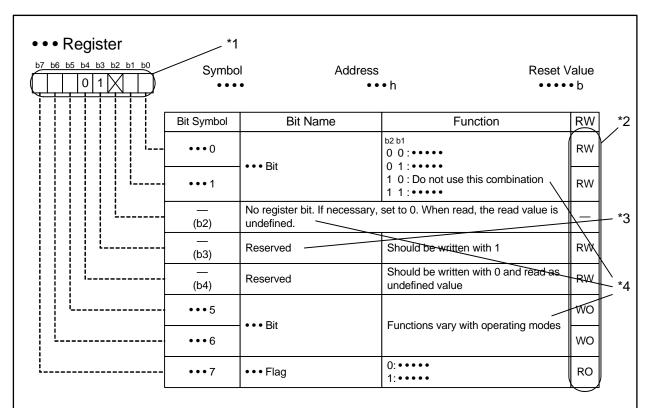

## 3. Registers

The following illustration describes registers used throughout this manual.

\*1

- Blank box: Set this bit to 0 or 1 according to the function.

- 0: Set this bit to 0.

- 1: Set this bit to 1.

- X: Nothing is assigned to this bit.

\*2

- RW: Read and write

- RO: Read only

- WO: Write only (the read value is undefined)

- -: Not applicable

\*3

• Reserved bit: This bit field is reserved. Set this bit to a specified value. For RW bits, the written value is read unless otherwise noted.

\*4

- No register bit(s): No register bit(s) is/are assigned to this field. If necessary, set to 0 for possible future implementation.

- Do not use this combination: Proper operation is not guaranteed when this value is set.

- Functions vary with operating modes: Functions vary with peripheral operating modes. Refer to register illustrations of the respective mode.

# 4. Abbreviations and Acronyms

The following acronyms and terms are used throughout this manual.

| Abbreviation/Acronym | Meaning                                      |

|----------------------|----------------------------------------------|

| ACIA                 | Asynchronous Communication Interface Adapter |

| bps                  | bits per second                              |

| CRC                  | Cyclic Redundancy Check                      |

| DMA                  | Direct Memory Access                         |

| DMAC                 | Direct Memory Access Controller              |

| GSM                  | Global System for Mobile Communications      |

| Hi-Z                 | High Impedance                               |

| IEBus                | Inter Equipment Bus                          |

| I/O                  | Input/Output                                 |

| IrDA                 | Infrared Data Association                    |

| LSB                  | Least Significant Bit                        |

| MSB                  | Most Significant Bit                         |

| NC                   | Non-Connection                               |

| PLL                  | Phase Locked Loop                            |

| PWM                  | Pulse Width Modulation                       |

| SIM                  | Subscriber Identity Module                   |

| UART                 | Universal Asynchronous Receiver/Transmitter  |

| VCO                  | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| 1.  | Ov  | erview                                                                | 1  |

|-----|-----|-----------------------------------------------------------------------|----|

| 1.1 |     | Features                                                              | 1  |

| 1.  | 1.1 | Applications                                                          | 1  |

| 1.  | 1.2 | Performance Overview                                                  | 2  |

| 1.2 |     | Product Information                                                   | 6  |

| 1.3 |     | Block Diagram                                                         | 9  |

| 1.4 |     | Pin Assignments                                                       | 10 |

| 1.5 |     | Pin Definitions and Functions                                         | 19 |

| 2.  | Ce  | ntral Processing Unit (CPU)                                           | 24 |

| 2.1 |     | General Purpose Registers                                             | 25 |

| 2.  | 1.1 | Data Registers (R2R0, R3R1, R6R4, and R7R5)                           |    |

| 2.  | 1.2 | Address Registers (A0, A1, A2, and A3)                                | 25 |

| 2.  | 1.3 | Static Base Register (SB)                                             | 25 |

| 2.  | 1.4 | Frame Base Register (FB)                                              | 25 |

| 2.  | 1.5 | Program Counter (PC)                                                  | 25 |

| 2.  | 1.6 | Interrupt Vector Table Base Register (INTB)                           | 25 |

| 2.  | 1.7 | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)            |    |

| 2.  | 1.8 | Flag Register (FLG)                                                   | 25 |

| 2.2 |     | Fast Interrupt Registers                                              | 27 |

| 2.  | 2.1 | Save Flag Register (SVF)                                              | 27 |

| 2.  | 2.2 | Save PC Register (SVP)                                                | 27 |

| 2.  | 2.3 | Vector Register (VCT)                                                 | 27 |

| 2.3 |     | DMAC-associated Registers                                             | 27 |

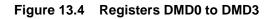

| 2.  | 3.1 | DMA Mode Registers (DMD0, DMD1, DMD2, and DMD3)                       | 27 |

| 2.  | 3.2 | DMA Terminal Count Registers (DCT0, DCT1, DCT2, and DCT3)             | 27 |

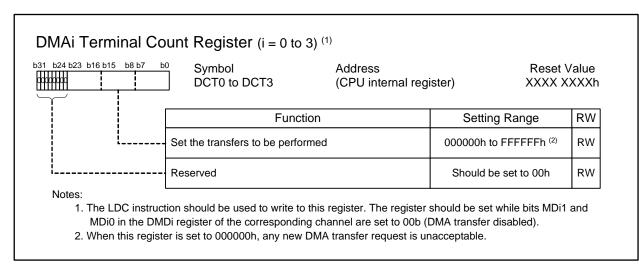

| 2.  | 3.3 | DMA Terminal Count Reload Registers (DCR0, DCR1, DCR2, and DCR3)      | 27 |

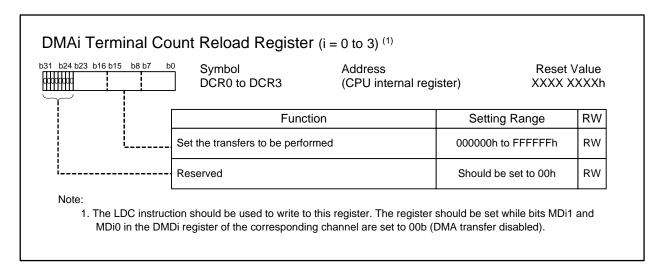

| 2.  | 3.4 | DMA Source Address Registers (DSA0, DSA1, DSA2, and DSA3)             | 27 |

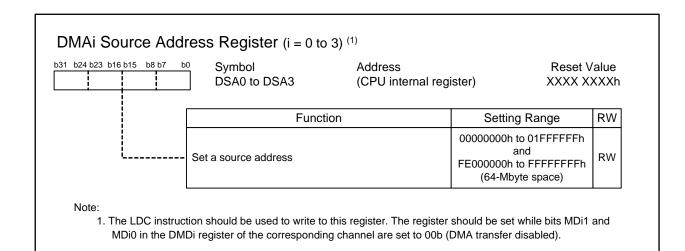

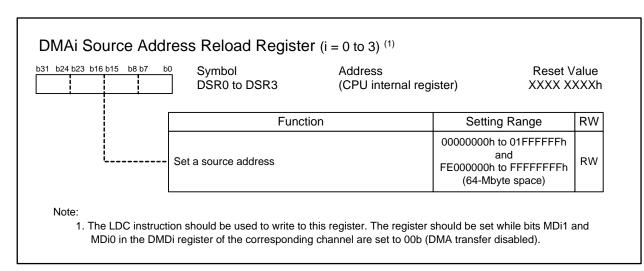

| 2.  | 3.5 | DMA Source Address Reload Registers (DSR0, DSR1, DSR2, and DSR3)      | 27 |

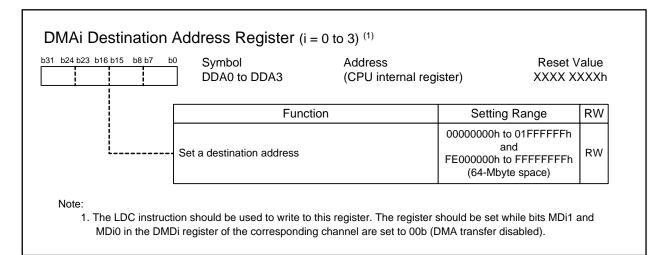

| 2.  | 3.6 | DMA Destination Address Registers (DDA0, DDA1, DDA2, and DDA3)        |    |

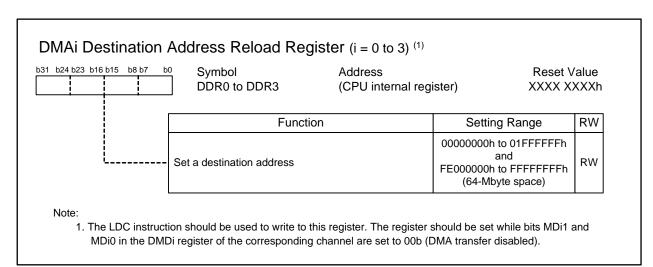

| 2.  | 3.7 | DMA Destination Address Reload Registers (DDR0, DDR1, DDR2, and DDR3) | 27 |

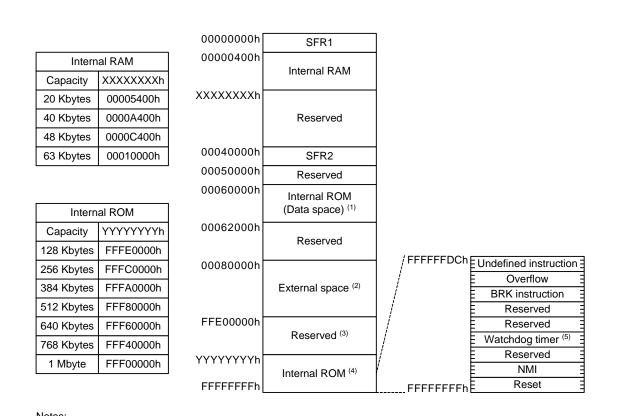

| 3.  | Me  | mory                                                                  | 28 |

| 4.  | Sp  | ecial Function Registers (SFRs)                                       | 29 |

| 5.  | Re  | sets                                                                  | 68 |

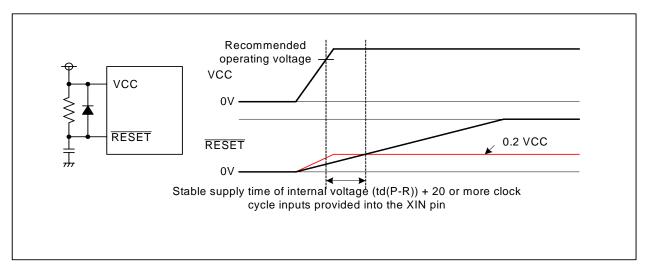

| 5.1 |     | Hardware Reset                                                        | 68 |

| 5.2 |     | Software Reset                                                        | 71 |

| 5.3 |     | Watchdog Timer Reset                                                  | 71 |

| 5.4 |     | Reset Vector                                                          | 71 |

| 6.  | Powe  | er Management                             | 72  |

|-----|-------|-------------------------------------------|-----|

| 6.1 | V     | /oltage Regulators for Internal Logic     | 72  |

| 6.1 | 1.1   | Decoupling Capacitor                      | 73  |

| 6.2 | L     | ow Voltage Detector                       | 74  |

| 6.2 | 2.1   | Operational State of Low Voltage Detector | 77  |

| 6.2 | 2.2   | Low Voltage Detection Interrupt           | 77  |

| 6.2 | 2.3   | An Application of Low Voltage Detector    | 78  |

| 7.  | Proc  | essor Mode                                | 79  |

| 7.1 | T     | ypes of Processor Modes                   | 79  |

| 7.2 | Р     | Processor Mode Setting                    | 79  |

| 8.  | Clocl | k Generator                               | 82  |

| 8.1 | С     | Clock Generator Types                     | 82  |

| 8.1 | 1.1   | Main Clock                                | 91  |

| 8.1 | 1.2   | Sub Clock (fC)                            | 92  |

| 8.1 | 1.3   | PLL Clock                                 | 93  |

| 8.1 | 1.4   | On-chip Oscillator Clock                  | 96  |

| 8.2 | С     | Dscillator Stop Detection                 | 97  |

| 8.2 | 2.1   | How to Use Oscillator Stop Detection      | 97  |

| 8.3 | В     | Base Clock                                | 97  |

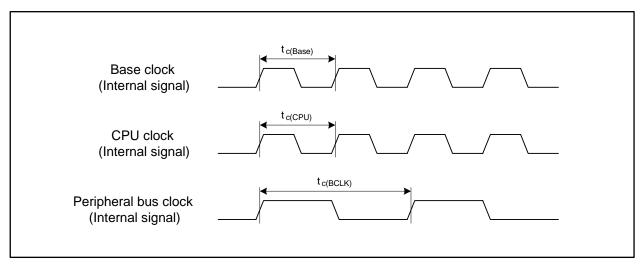

| 8.4 | С     | CPU Clock and Peripheral Bus Clock        | 98  |

| 8.5 | Р     | Peripheral Clock                          | 98  |

| 8.6 | С     | Clock Output Function                     | 99  |

| 8.7 | Р     | Power Control 1                           | 100 |

| 8.7 | 7.1   | Normal Operating Mode1                    | 101 |

| 8.7 | 7.2   | Wait Mode1                                | 106 |

| 8.7 | 7.3   | Stop Mode1                                | 109 |

| 8.8 | S     | System Clock Protection                   | 111 |

| 8.9 | N     | lotes on Clock Generator                  | 112 |

| 8.9 | 9.1   | Sub Clock                                 | 112 |

| 8.9 | 9.2   | Power Control                             | 112 |

| 9.  | Bus   | 1                                         | 13  |

| 9.1 | В     | Bus Setting                               | 113 |

| 9.2 | Ρ     | Peripheral Bus Timing Setting             | 114 |

| 9.3 | E     | xternal Bus Setting                       | 115 |

| 9.3 | 3.1   | External Address Space Setting            | 115 |

| 9.3 | 3.2   | External Data Bus Width Setting 1         | 121 |

| 9.3 | 3.3   | Separate Bus/Multiplexed Bus Selection1   | 123 |

| 9.3 | 3.4   | Read and Write Signals 1                  | 126 |

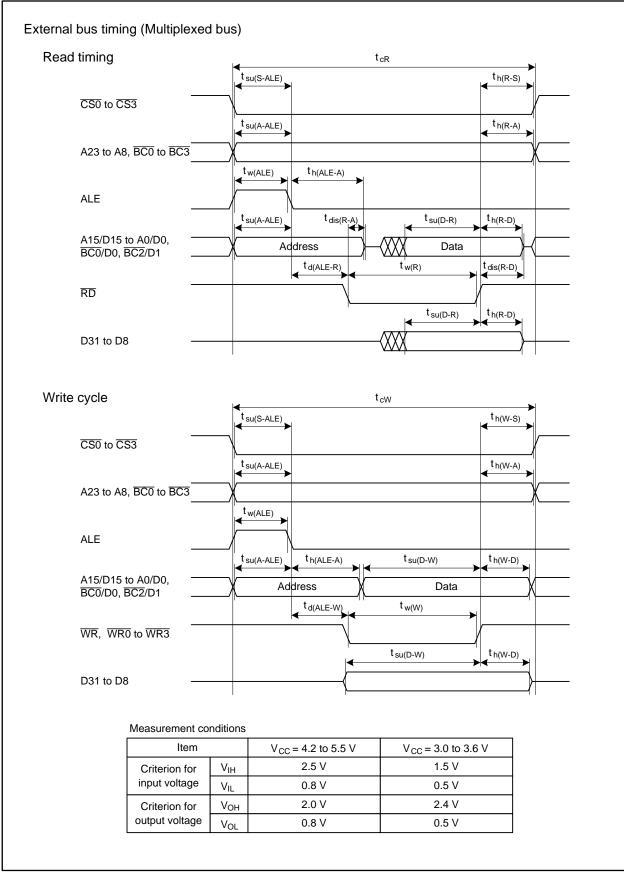

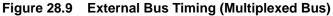

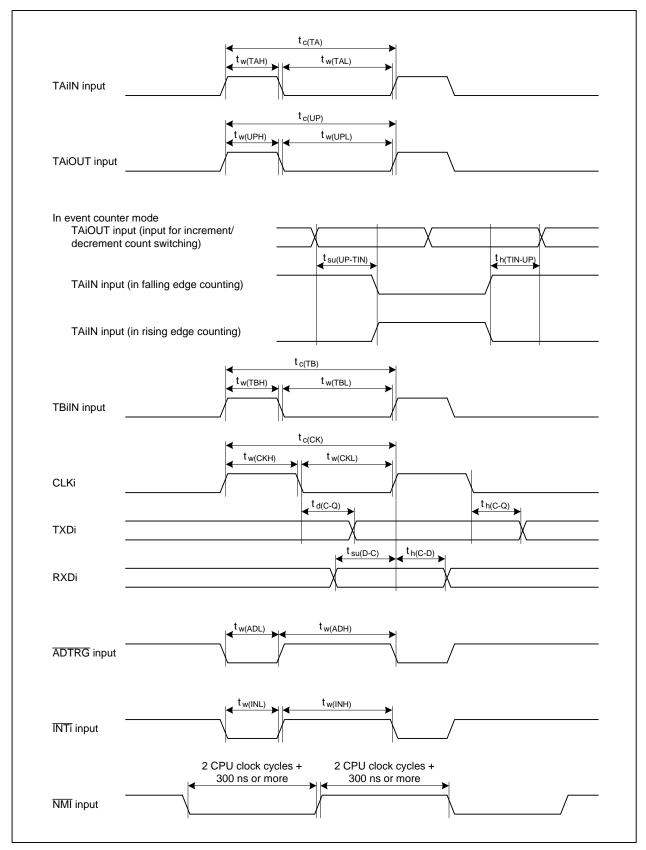

| 9.3 | 3.5   | External Bus Timing1                      | 128 |

| 9.3.6    | ALE Signal                                        | 132 |

|----------|---------------------------------------------------|-----|

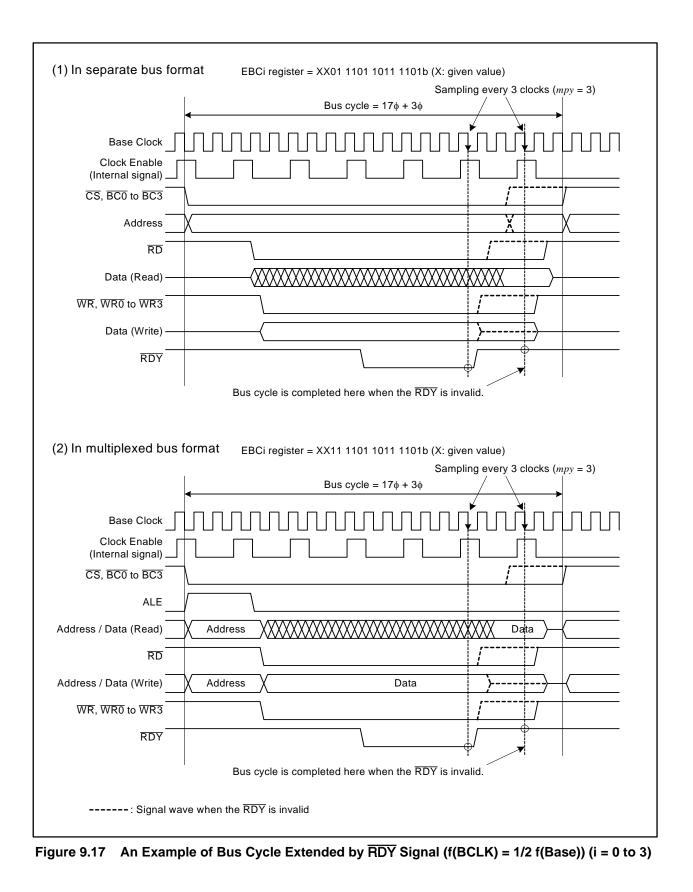

| 9.3.7    | RDY Signal                                        | 133 |

| 9.3.8    | HOLD Signal                                       | 136 |

| 9.3.9    | BCLK Output                                       | 136 |

| 9.4      | External Bus Status when Accessing Internal Space |     |

| 9.5      | Notes on Bus                                      | 137 |

| 9.5.1    | Notes on System Designing                         |     |

| 9.5.2    | Notes on Register Settings                        | 137 |

| 10. Pro  | tection                                           | 138 |

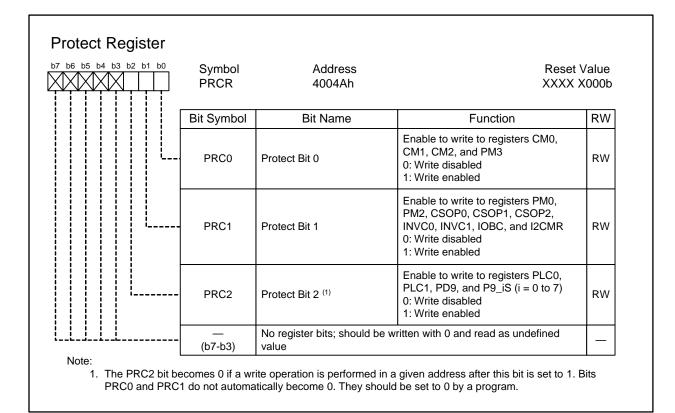

| 10.1     | Protect Register (PRCR Register)                  | 138 |

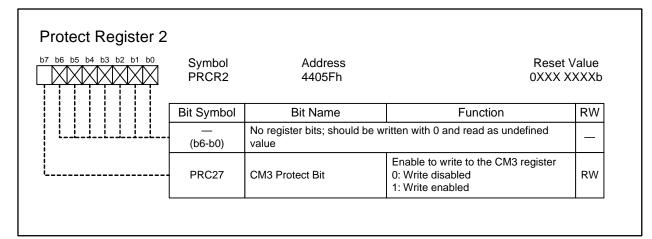

| 10.2     | Protect Register 2 (PRCR2 Register)               |     |

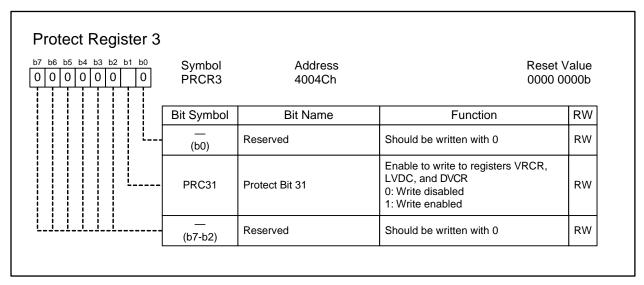

| 10.3     | Protect Register 3 (PRCR3 Register)               |     |

| 10.4     | Protect Release Register (PRR Register)           |     |

| 11. Inte | errupts                                           | 141 |

| 11.1     | Interrupt Types                                   | 141 |

| 11.2     | Software Interrupt                                |     |

| 11.3     | Hardware Interrupt                                | 143 |

| 11.3.1   | Special Interrupt                                 | 143 |

| 11.3.2   | Peripheral Interrupt                              | 143 |

| 11.4     | Fast Interrupt                                    |     |

| 11.5     | Interrupt Vectors                                 |     |

| 11.5.1   | Fixed Vector Table                                |     |

| 11.5.2   | Relocatable Vector Table                          |     |

| 11.6     | Interrupt Request Acceptance                      | 150 |

| 11.6.1   | I Flag and IPL                                    | 150 |

| 11.6.2   | Interrupt Control Register                        | 151 |

| 11.6.3   | Wake-up IPL Setting Register                      |     |

| 11.6.4   | Interrupt Sequence                                | 155 |

| 11.6.5   | Interrupt Response Time                           |     |

| 11.6.6   | IPL After Interrupt Request Acceptance            | 157 |

| 11.6.7   | Register Saving                                   | 157 |

| 11.7     | Register Restoring from Interrupt Handler         | 158 |

| 11.8     | Interrupt Priority                                | 158 |

| 11.9     | Priority Resolver                                 | 158 |

| 11.10    | External Interrupt                                | 160 |

| 11.11    | NMI                                               | 161 |

| 11.12    | Key Input Interrupt                               | 162 |

| 11.13    | Intelligent I/O Interrupt                         | 163 |

| 11.14    | Notes on Interrupts                               | 166 |

| 11.14.   | 1 ISP Setting                                     |     |

|     | 11.14.  | 2 NMI                                                 | 166 |

|-----|---------|-------------------------------------------------------|-----|

|     | 11.14.3 | B External Interrupt                                  | 166 |

| 12. | Wa      | ichdog Timer                                          | 167 |

| 13. | DM      | AC                                                    | 169 |

| 1:  | 3.1     | Transfer Cycle                                        |     |

|     | 13.1.1  | Effect of Transfer Address and Data Bus Width         | 178 |

|     | 13.1.2  | Effect of Bus Timing                                  | 179 |

|     | 13.1.3  | Effect of RDY Signal                                  | 179 |

| 1:  | 3.2     | DMA Transfer Cycle                                    | 181 |

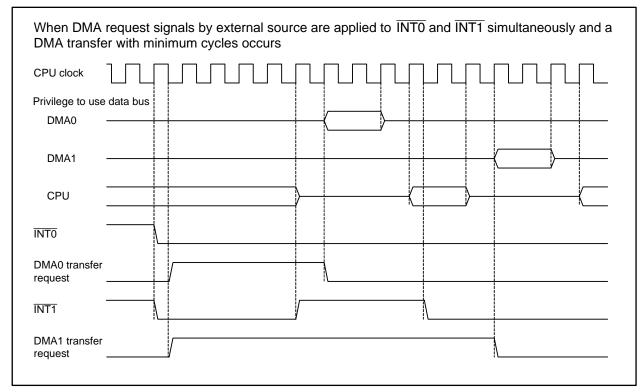

| 1:  | 3.3     | Channel Priority and DMA Transfer Timing              |     |

| 1:  | 3.4     | Notes on DMAC                                         | 183 |

|     | 13.4.1  | DMAC-associated Register Settings                     | 183 |

|     | 13.4.2  | Read from DMAC-associated Registers                   | 183 |

| 14. | DM      | AC II                                                 | 184 |

| 14  | 4.1     | DMAC II Settings                                      |     |

|     | 14.1.1  | Registers RIPL1 and RIPL2                             |     |

|     | 14.1.2  | DMAC II Index                                         |     |

|     | 14.1.3  | Interrupt Control Register of the Peripheral Function |     |

|     | 14.1.4  | Relocatable Vector Table of the Peripheral Function   |     |

|     | 14.1.5  | IRLT Bit in the IIOiIE Register (i = 0 to 11)         |     |

| 14  | 4.2     | DMAC II Performance                                   | 189 |

| 14  | 4.3     | Transfer Types                                        | 189 |

|     | 14.3.1  | Memory-to-memory Transfer                             |     |

|     | 14.3.2  | Immediate Data Transfer                               | 190 |

|     | 14.3.3  | Calculation Transfer                                  | 190 |

| 14  | 4.4     | Transfer Modes                                        | 190 |

|     | 14.4.1  | Single Transfer                                       | 190 |

|     | 14.4.2  | Burst Transfer                                        | 190 |

|     | 14.4.3  | Multiple Transfer                                     | 190 |

| 14  | 4.5     | Chained Transfer                                      | 191 |

| 14  | 4.6     | DMA II Transfer Complete Interrupt                    | 191 |

| 14  | 4.7     | Execution Time                                        | 192 |

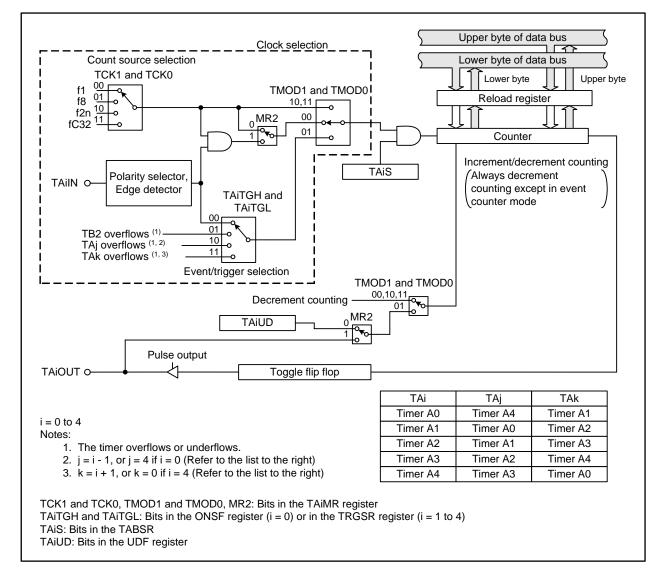

| 15. | Pro     | grammable I/O Ports                                   | 193 |

| 1   | 5.1     | Port Pi Register (Pi register, i = 0 to 15)           | 195 |

| 16. | Tim     | ers                                                   | 196 |

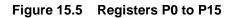

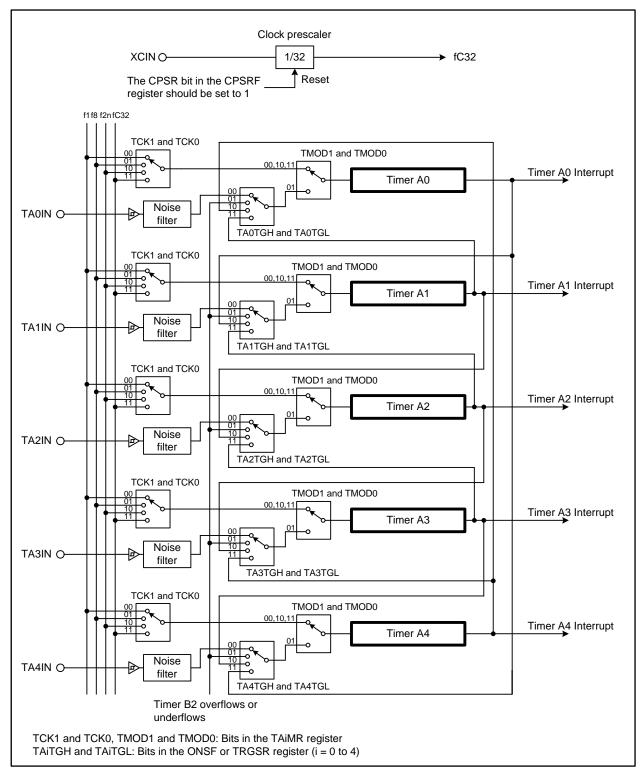

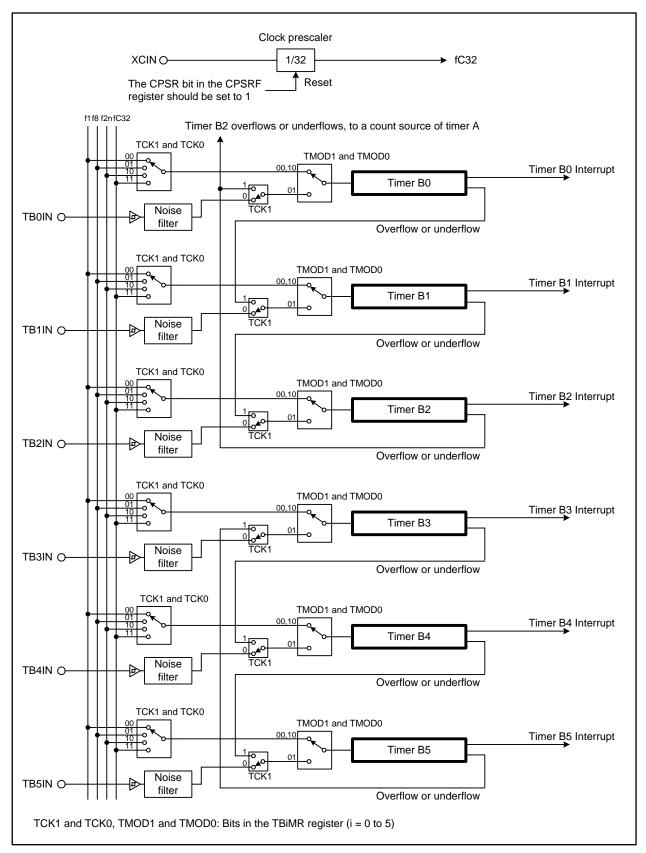

| 16  | 6.1     | Timer A                                               | 198 |

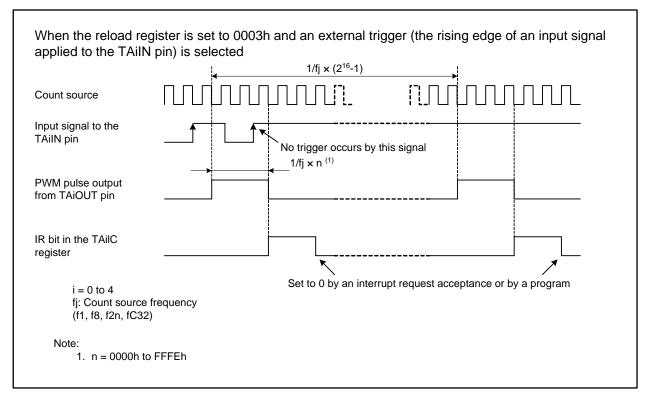

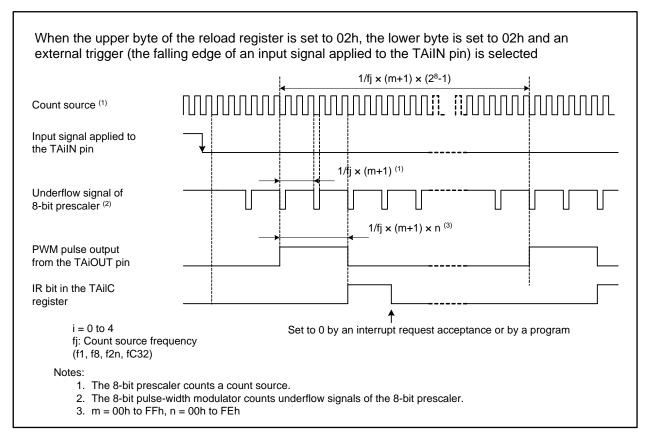

|     | 16.1.1  | Timer Mode                                            |     |

|     | 16.1.2  | Event Counter Mode                                    |     |

| 16.1.3  | One-shot Timer Mode                                    | 211 |

|---------|--------------------------------------------------------|-----|

| 16.1.4  | Pulse-width Modulation Mode                            | 213 |

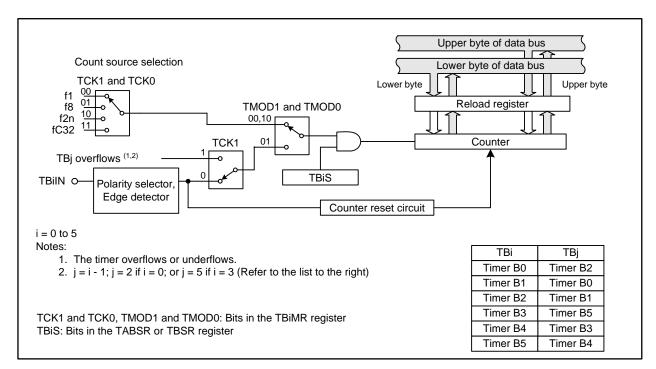

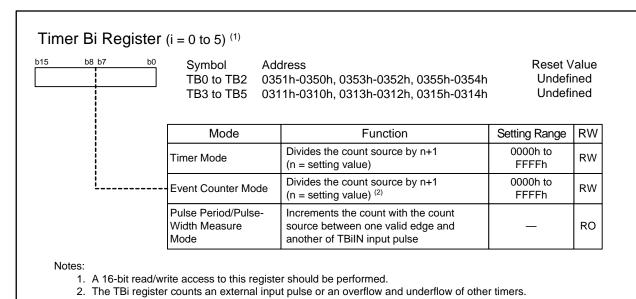

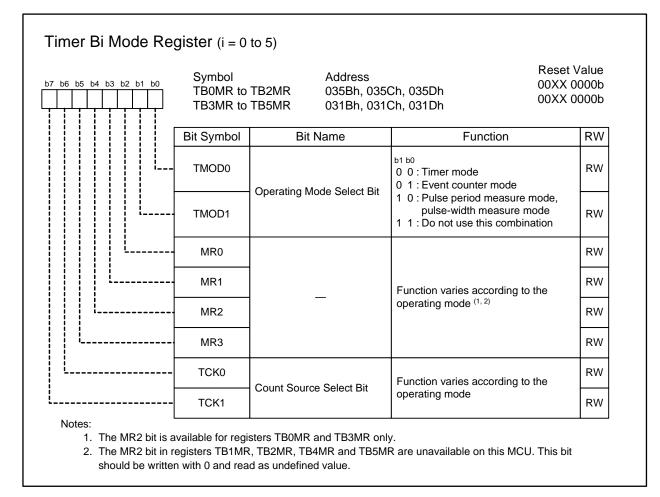

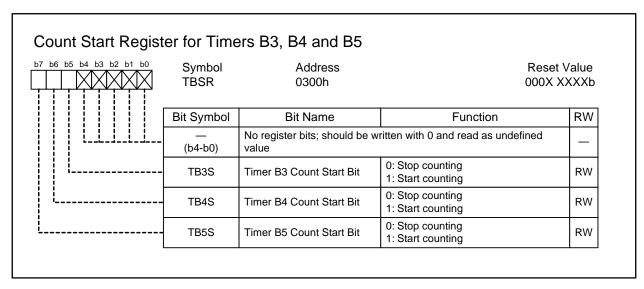

| 16.2    | Timer B                                                | 216 |

| 16.2.1  | Timer Mode                                             | 219 |

| 16.2.2  | Event Counter Mode                                     | 221 |

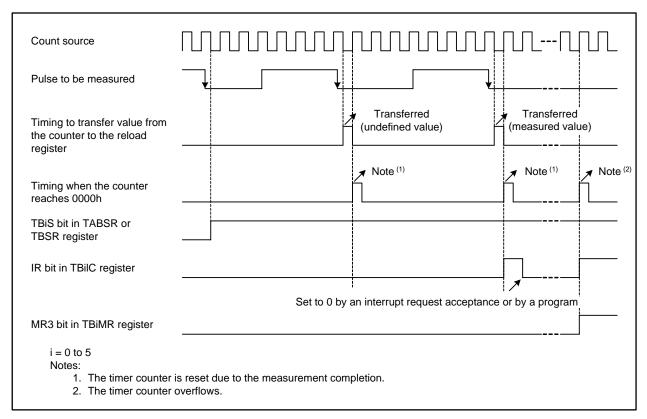

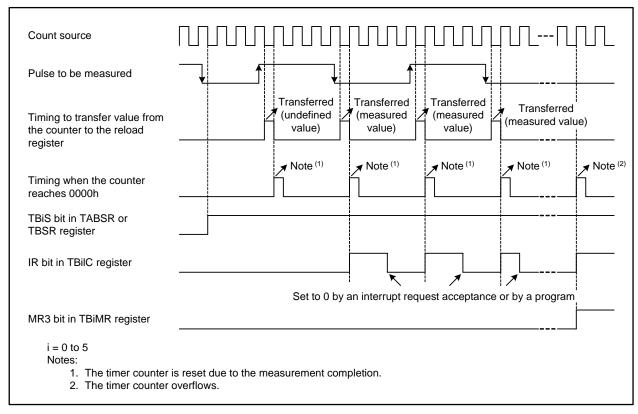

| 16.2.3  | Pulse Period/Pulse-width Measure Mode                  | 223 |

| 16.3    | Notes on Timers                                        | 226 |

| 16.3.1  | Timer A and Timer B                                    | 226 |

| 16.3.2  | Timer A                                                | 226 |

| 16.3.3  | Timer B                                                | 228 |

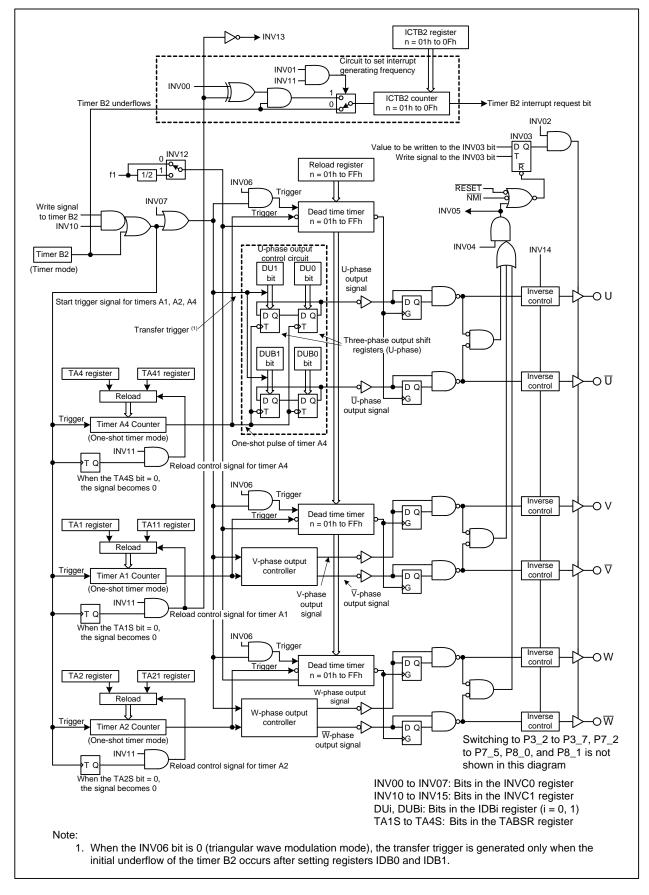

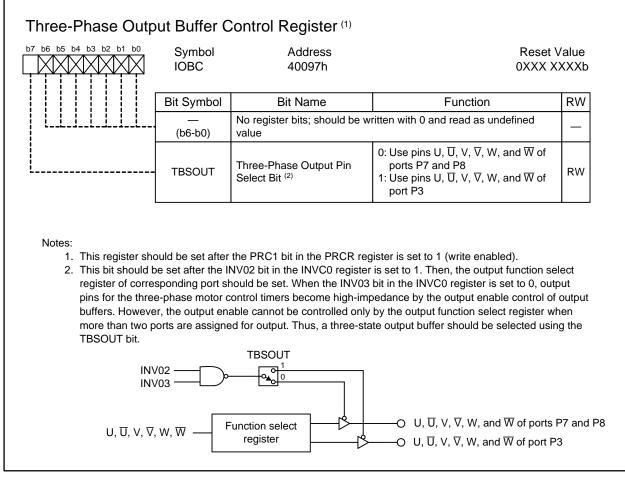

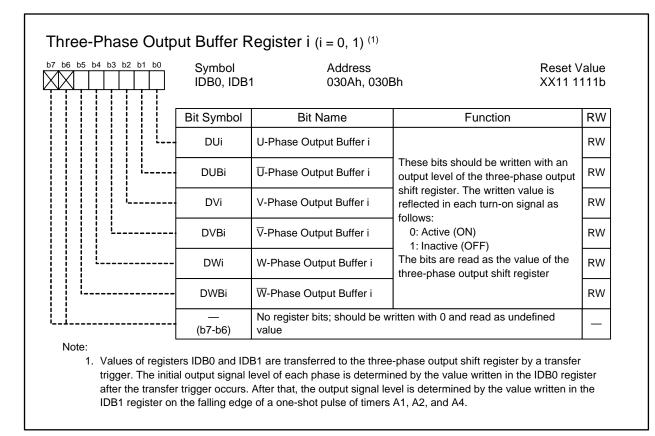

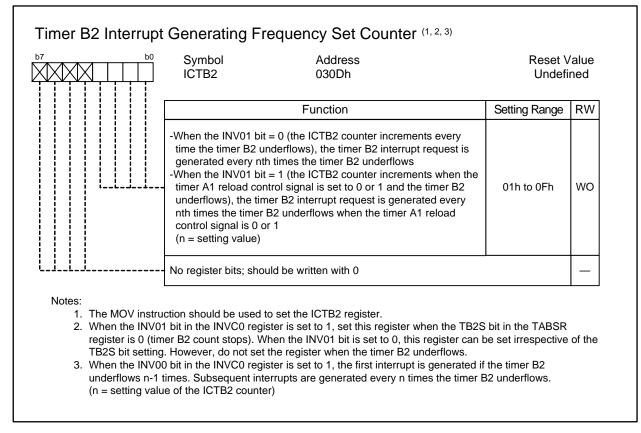

| 17. Thr | ee-phase Motor Control Timers                          | 229 |

| 17.1    | Modulation Modes of Three-phase Motor Control Timers   | 236 |

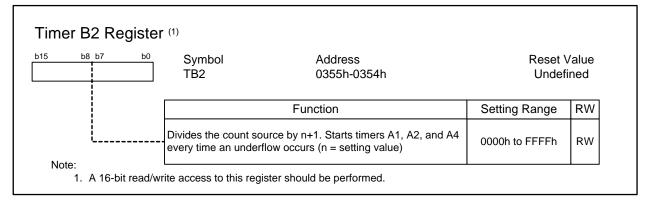

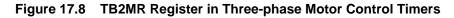

| 17.2    | Timer B2                                               | 237 |

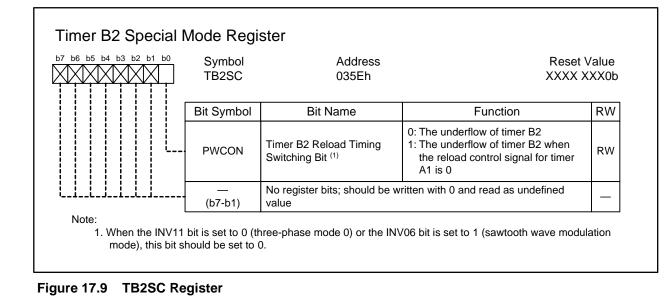

| 17.3    | Timers A4, A1, and A2                                  | 239 |

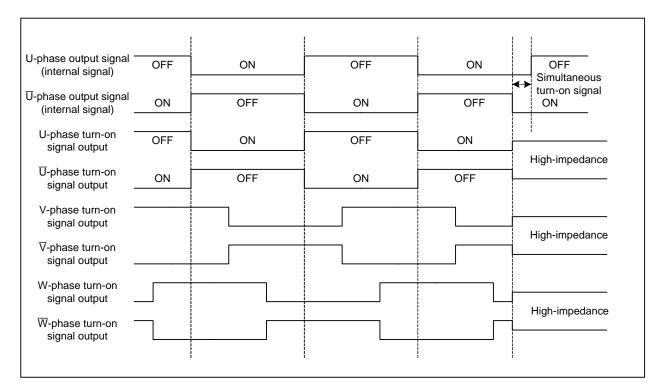

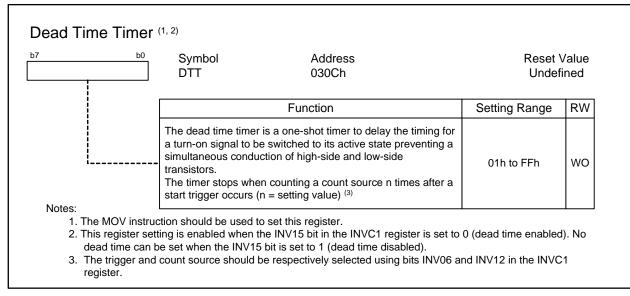

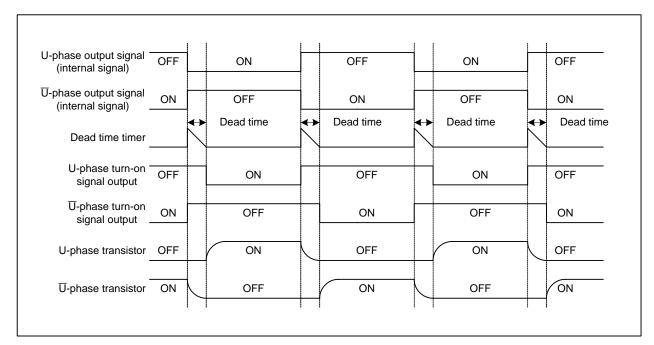

| 17.4    | Simultaneous Conduction Prevention and Dead Time Timer | 242 |

| 17.5    | Three-phase Motor Control Timer Operation              | 243 |

| 17.6    | Notes on Three-phase Motor Control Timers              | 246 |

| 17.6.1  | Shutdown                                               | 246 |

| 17.6.2  | Register setting                                       | 246 |

| 18. Ser | ial Interface                                          | 247 |

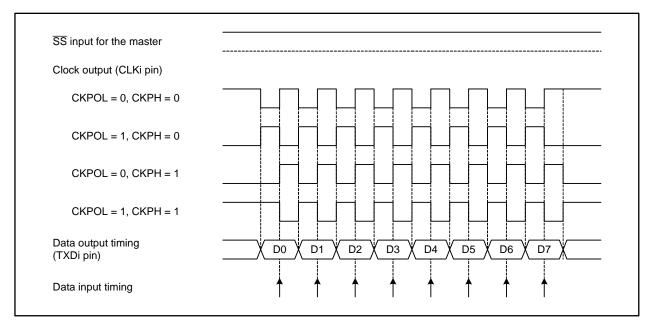

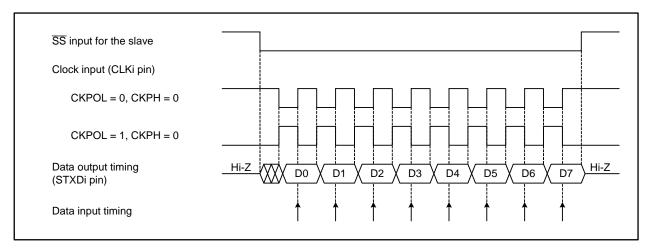

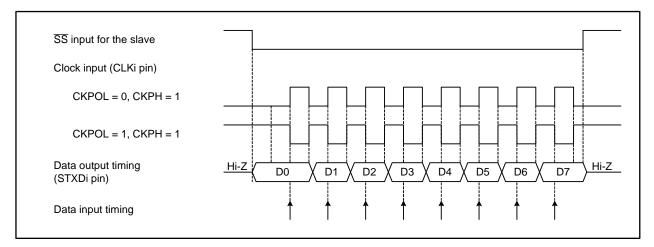

| 18.1    | Synchronous Serial Interface Mode                      | 264 |

| 18.1.1  | Reset Procedure on Transmit/Receive Error              | 269 |

| 18.1.2  | CLK Polarity                                           | 269 |

| 18.1.3  | LSB First and MSB First Selection                      | 270 |

| 18.1.4  | Continuous Receive Mode                                | 270 |

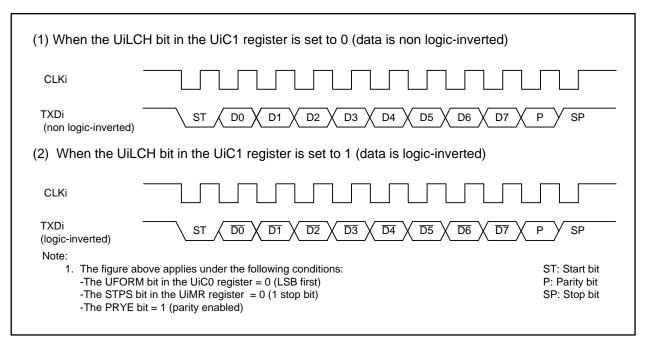

| 18.1.5  | Serial Data Logical Inversion                          | 271 |

| 18.1.6  | CTS/RTS Function                                       | 271 |

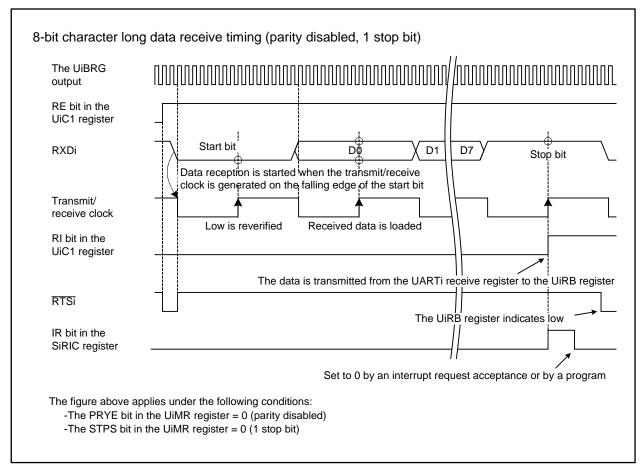

| 18.2    | Asynchronous Serial Interface Mode (UART Mode)         | 272 |

| 18.2.1  | Bit Rate                                               | 277 |

| 18.2.2  | Reset Procedure on Transmit/Receive Error              | 278 |

| 18.2.3  | LSB First and MSB First Selection                      | 278 |

| 18.2.4  | Serial Data Logical Inversion                          | 279 |

| 18.2.5  | TXD and RXD I/O Polarity Inversion                     | 280 |

| 18.2.6  | CTS/RTS Function                                       | 280 |

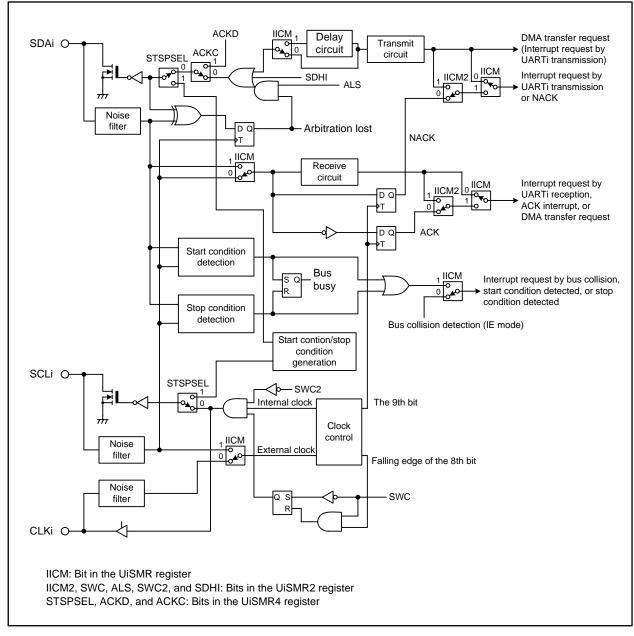

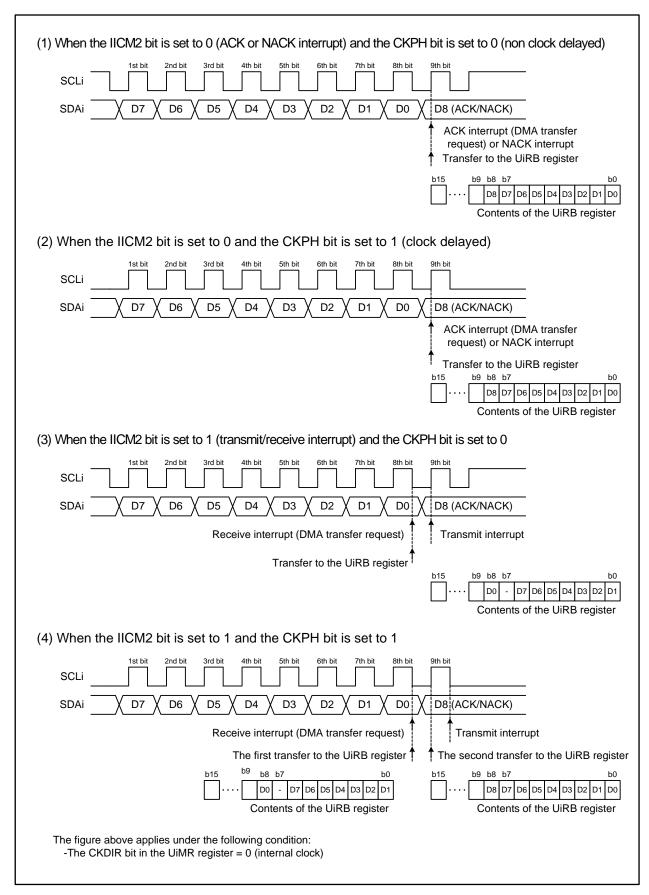

| 18.3    | Special Mode 1 (I <sup>2</sup> C Mode)                 | 281 |

| 18.3.1  | Start Condition and Stop Condition Detection           | 287 |

| 18.3.2  | Start Condition and Stop Condition Generation          | 287 |

| 18.3.3  | Arbitration                                            | 288 |

| 18.3.4  | SCL Control and Clock Synchronization                  | 289 |

| 18.3.5  | SDA Output                                             | 291 |

|         |                                                        |     |

| 18.3.6  | SDA Input                                                          | 291 |

|---------|--------------------------------------------------------------------|-----|

| 18.3.7  | Acknowledge                                                        | 291 |

| 18.3.8  | Initialization of Transmit/Receive Operation                       | 291 |

| 18.4    | Special Mode 2                                                     | 292 |

| 18.4.1  | $\overline{SSi}$ Input Pin Function (i = 0 to 6)                   | 294 |

| 18.4.2  | Clock Phase Setting                                                | 295 |

| 18.5    | Notes on Serial Interface                                          | 297 |

| 18.5.1  | Changing the UiBRG Register (i = 0 to 8)                           | 297 |

| 18.5.2  | Synchronous Serial Interface Mode                                  | 297 |

| 18.5.3  | Special Mode 1 (I <sup>2</sup> C Mode)                             | 297 |

| 18.5.4  | Reset Procedure on Communication Error                             | 298 |

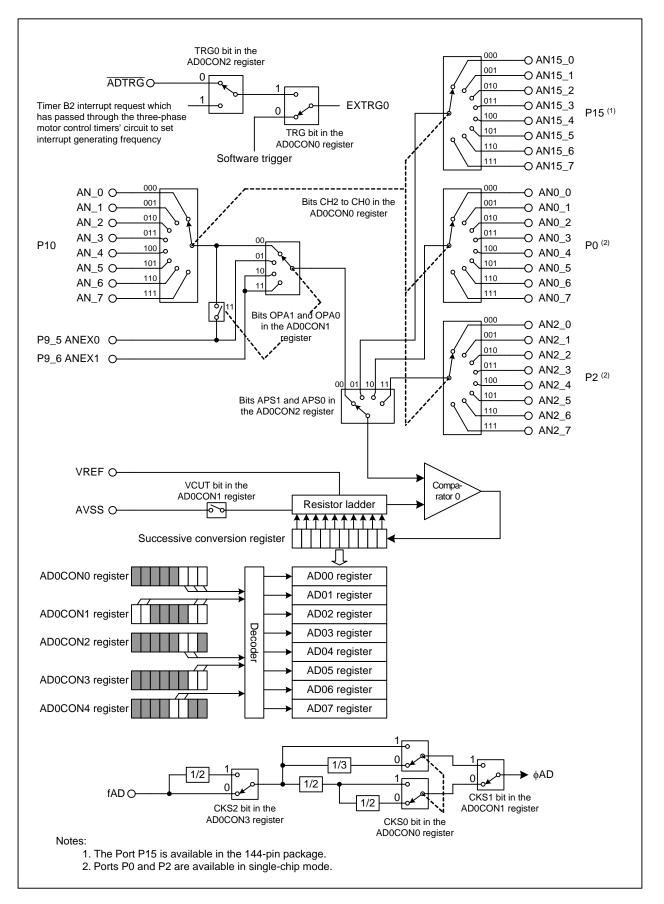

| 19. A/E | ) Converter                                                        | 299 |

| 19.1    | Mode Descriptions                                                  | 307 |

| 19.1.1  | One-shot Mode                                                      | 307 |

| 19.1.2  | Repeat Mode                                                        | 308 |

| 19.1.3  | Single Sweep Mode                                                  | 309 |

| 19.1.4  | Repeat Sweep Mode 0                                                | 310 |

| 19.1.5  | Repeat Sweep Mode 1                                                | 311 |

| 19.1.6  | Multi-port Single Sweep Mode                                       |     |

| 19.1.7  | Multi-port Repeat Sweep Mode 0                                     | 313 |

| 19.2    | Functions                                                          | 314 |

| 19.2.1  | Resolution Selection                                               | 314 |

| 19.2.2  | Sample and Hold Function                                           | 314 |

| 19.2.3  | Trigger Selection                                                  | 314 |

| 19.2.4  | DMAC Operating Mode                                                |     |

| 19.2.5  | Function-extended Analog Input Pins                                | 315 |

| 19.2.6  | External Operating Amplifier (Op-AMP) Connection Mode              | 315 |

| 19.2.7  | Power Saving                                                       | 316 |

| 19.2.8  | Output Impedance of Sensor Equivalent Circuit under A/D Conversion | 316 |

| 19.3    | Notes on A/D Converter                                             | 318 |

| 19.3.1  | Notes on Designing Boards                                          | 318 |

| 19.3.2  | Notes on Programming                                               | 319 |

| 20. D/# | A Converter                                                        | 320 |

| 21. CR  | C Calculator                                                       | 322 |

| 22. X-` | ( Conversion                                                       | 325 |

| 22.1    | Data Conversion on Reading                                         | 326 |

| 22.2    | Data Conversion on Writing                                         | 328 |

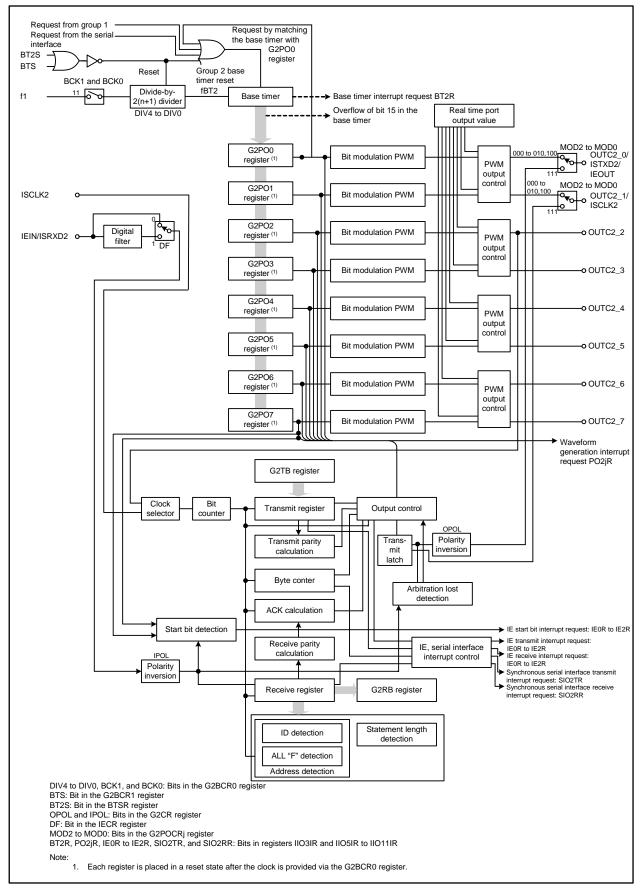

| 23. | Inte  | elligent I/O                                                                 | 329 |

|-----|-------|------------------------------------------------------------------------------|-----|

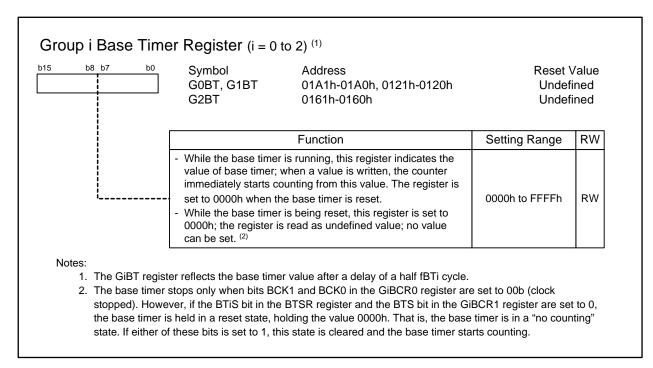

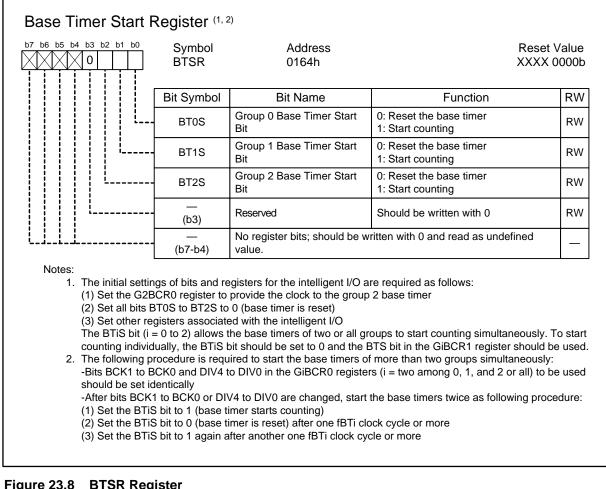

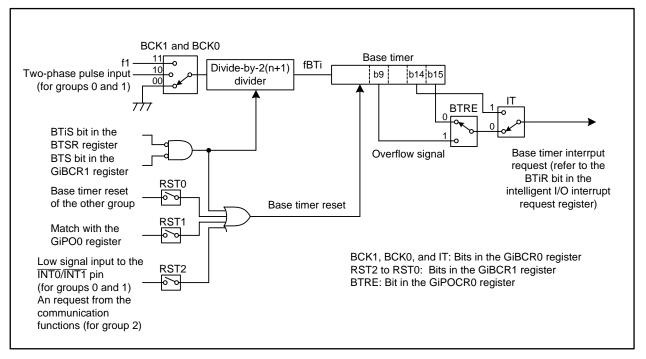

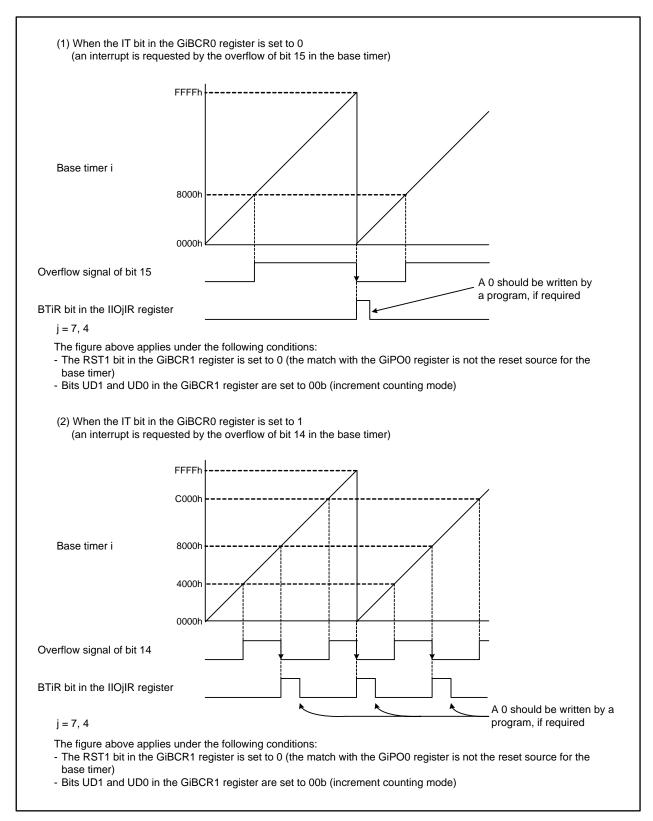

| 23. | 1     | Base Timer (for Groups 0 to 2)                                               | 344 |

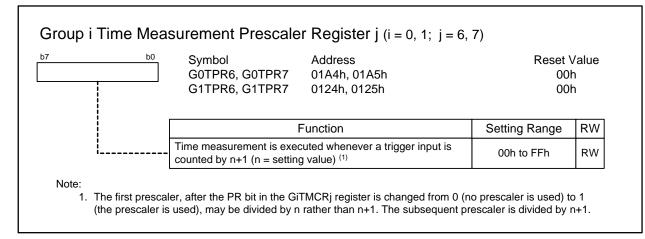

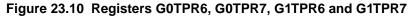

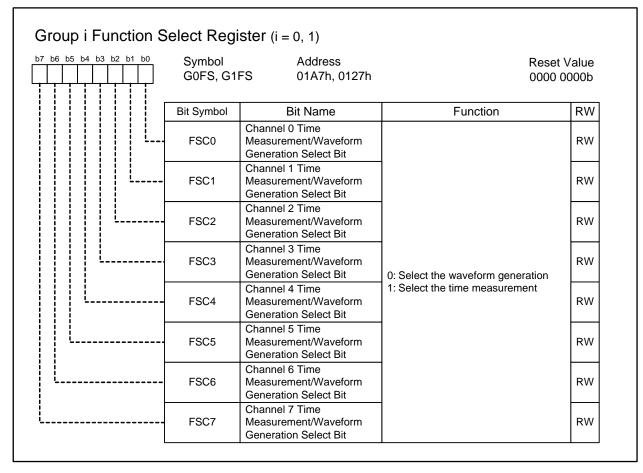

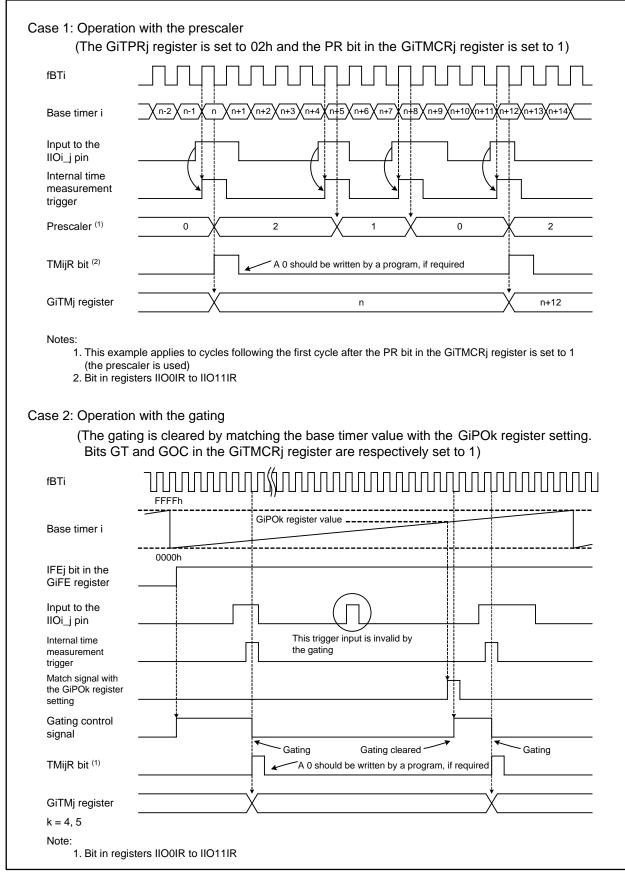

| 23. | 2     | Time Measurement (for Groups 0 and 1)                                        | 350 |

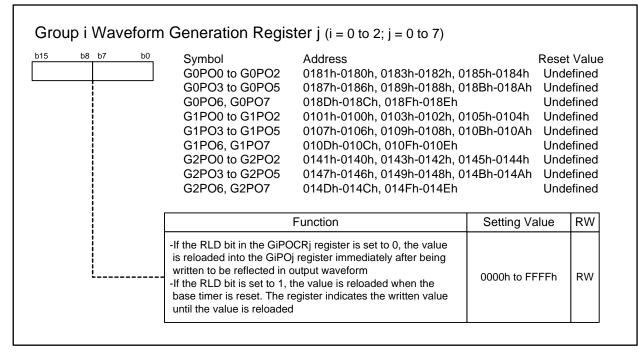

| 23. | 3     | Waveform Generation (for Groups 0 to 2)                                      | 354 |

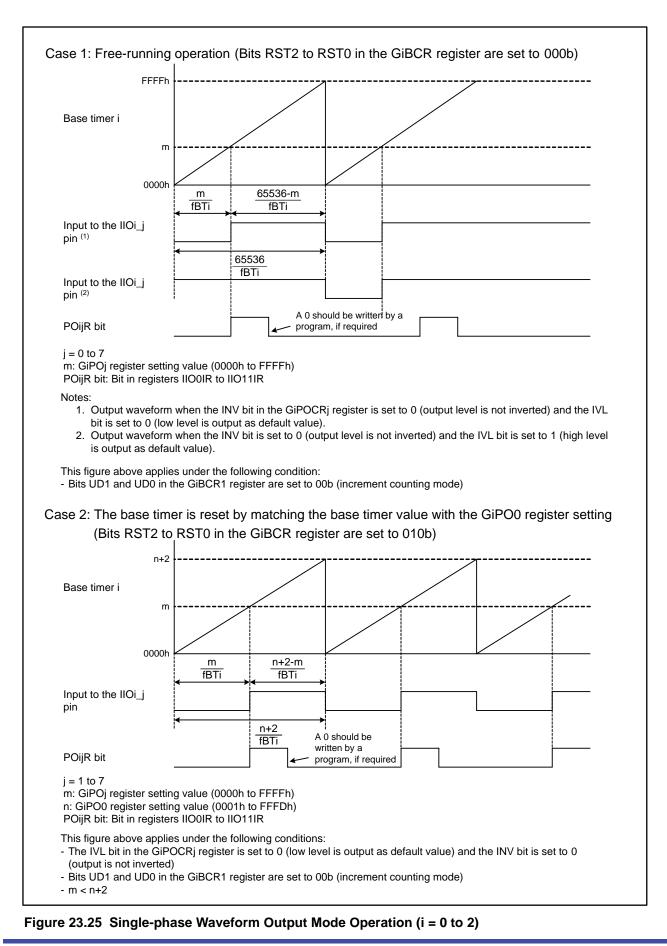

| 2   | 3.3.1 | Single-phase Waveform Output Mode (for Groups 0 to 2)                        | 355 |

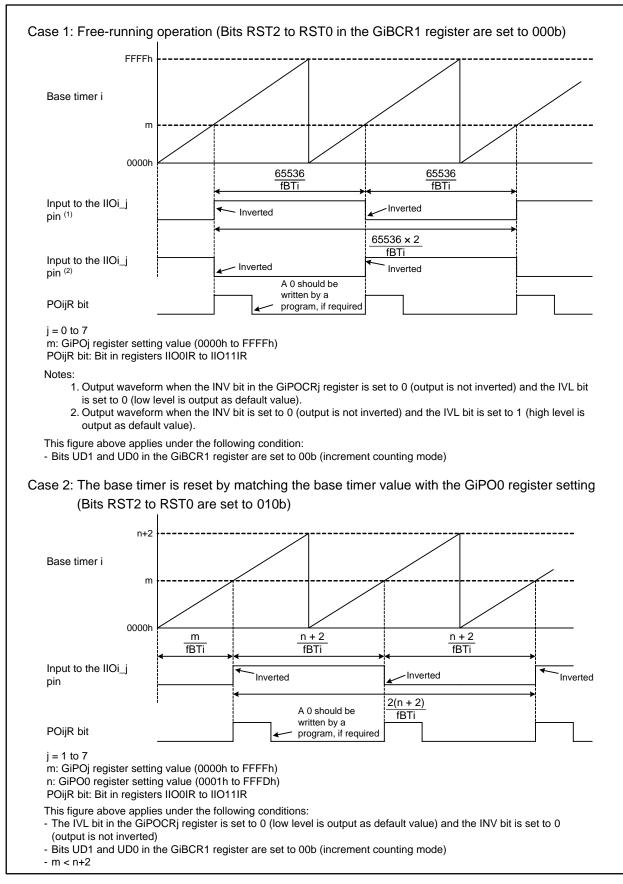

| 2   | 3.3.2 | Inverted Waveform Output Mode (for Groups 0 to 2)                            | 357 |

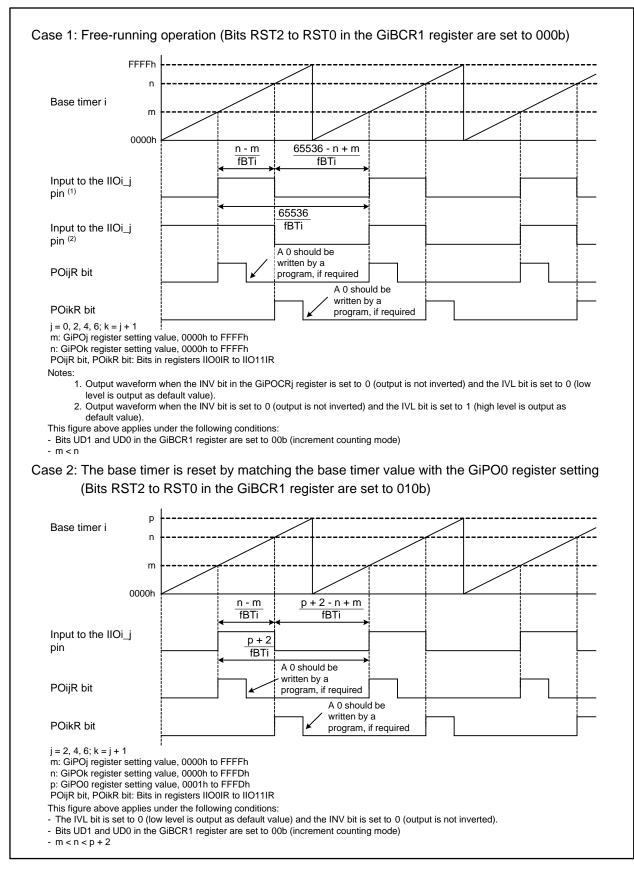

| 2   | 3.3.3 | Set/Reset Waveform Output Mode (SR Waveform Output Mode) (for Groups 0 to 2) | 359 |

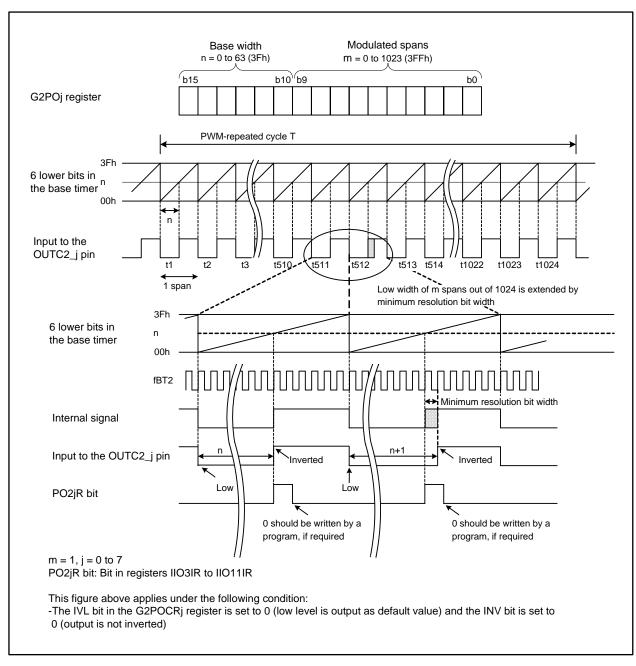

| 2   | 3.3.4 | Bit Modulation PWM Output Mode (for Group 2)                                 | 362 |

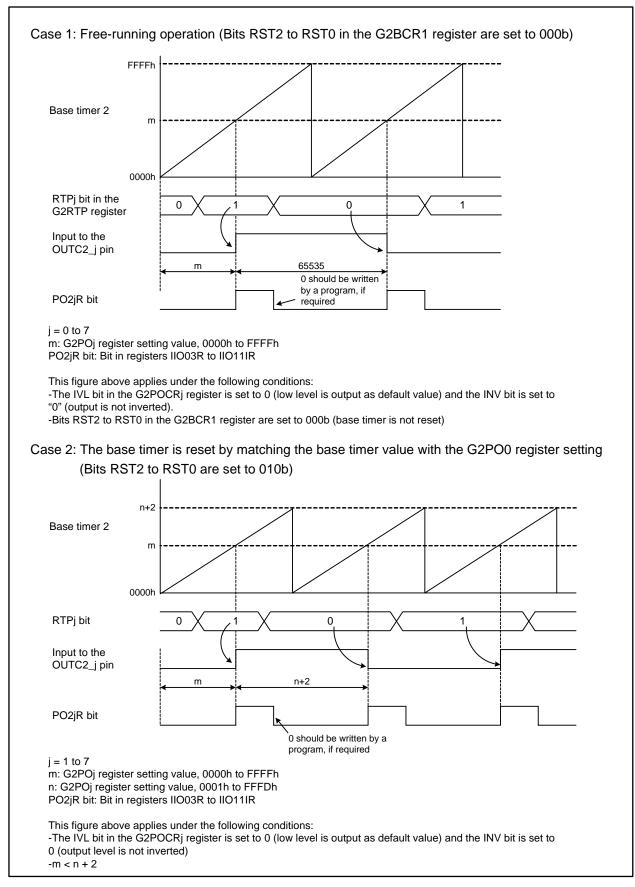

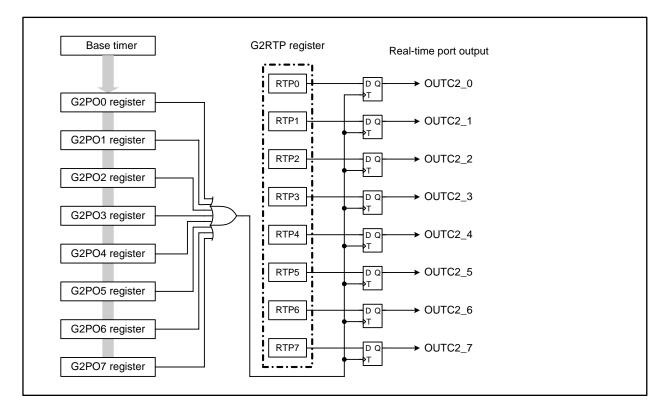

| 2   | 3.3.5 | Real-Time Port Output Mode (RTP Output Mode) (for Group 2)                   | 364 |

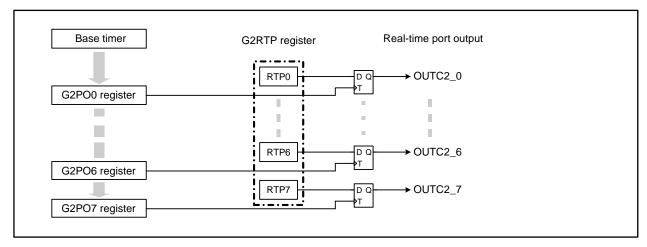

| 2   | 3.3.6 | Parallel Real-Time Port Output Mode (RTP Output Mode) (for Group 2)          | 366 |

| 23. | 4     | Group 2 Serial Interface                                                     | 368 |

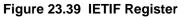

| 2   | 3.4.1 | Variable Synchronous Serial Interface Mode (for Group 2)                     | 373 |

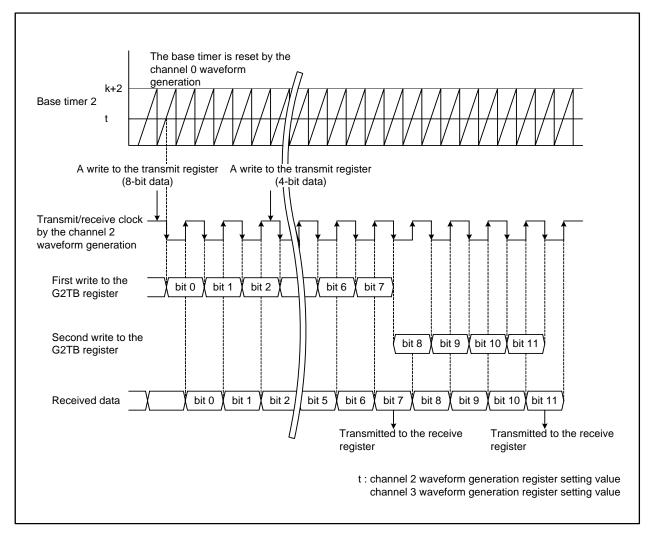

| 24. | Mu    | Iti-master I <sup>2</sup> C-bus Interface                                    | 376 |

| 24. | 1     | Multi-master I <sup>2</sup> C-bus Interface-associated Registers             | 378 |

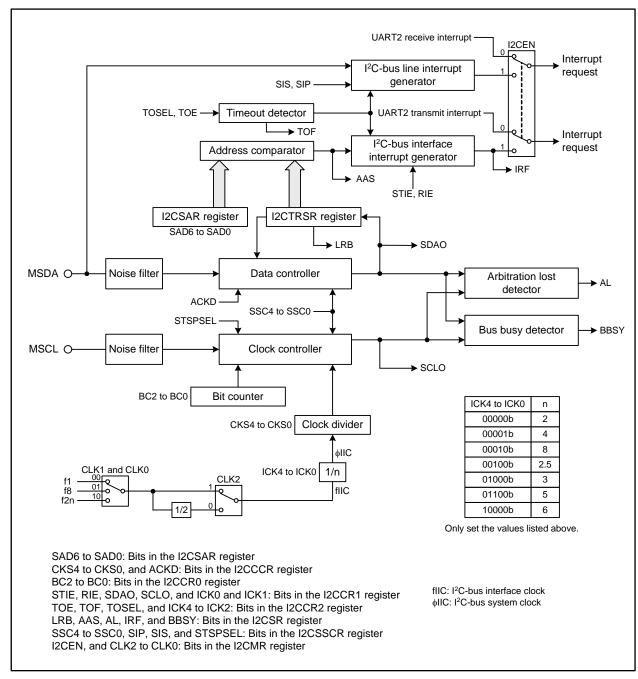

| 2   | 4.1.1 | I <sup>2</sup> C-bus Transmit/Receive Shift Register (I2CTRSR)               | 378 |

| 2   | 4.1.2 | I <sup>2</sup> C-bus Slave Address Register (I2CSAR)                         | 379 |

| 2   | 4.1.3 | I <sup>2</sup> C-bus Control Register 0 (I2CCR0)                             | 380 |

| 2   | 4.1.4 | I <sup>2</sup> C-bus Clock Control Register (I2CCCR)                         | 382 |

| 2   | 4.1.5 | I <sup>2</sup> C-bus START and STOP Conditions Control Register (I2CSSCR)    | 384 |

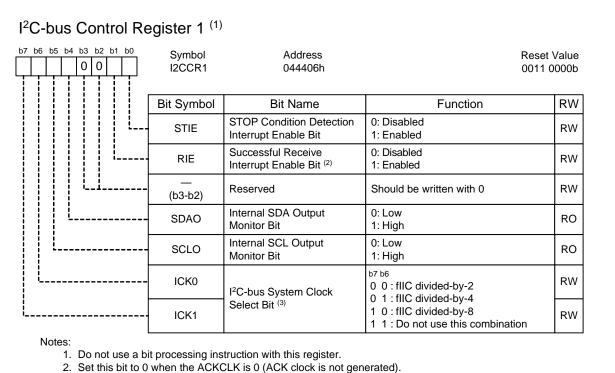

| 2   | 4.1.6 | I <sup>2</sup> C-bus Control Register 1 (I2CCR1)                             | 385 |

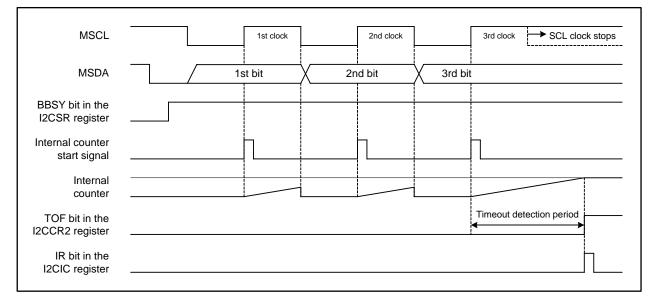

| 2   | 4.1.7 | I <sup>2</sup> C-bus Control Register 2 (I2CCR2)                             | 388 |

| 2   | 4.1.8 | I <sup>2</sup> C-bus Status Register (I2CSR)                                 | 390 |

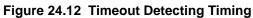

| 2   | 4.1.9 | I <sup>2</sup> C-bus Mode Register (I2CMR)                                   | 394 |

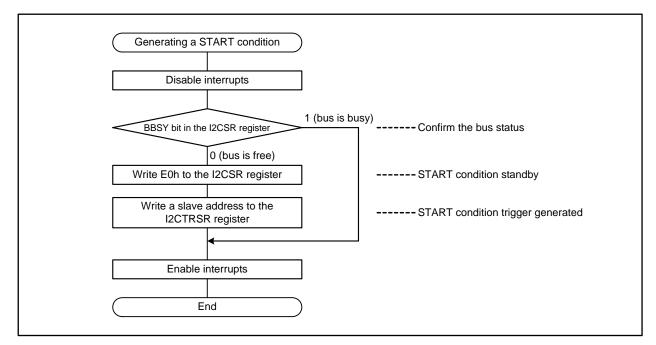

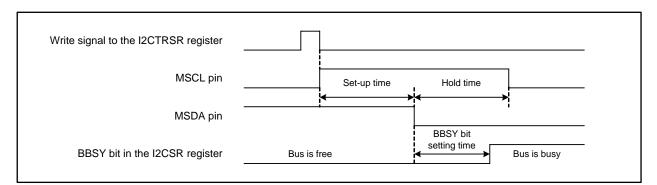

| 24. | 2     | Generating a START Condition                                                 | 395 |

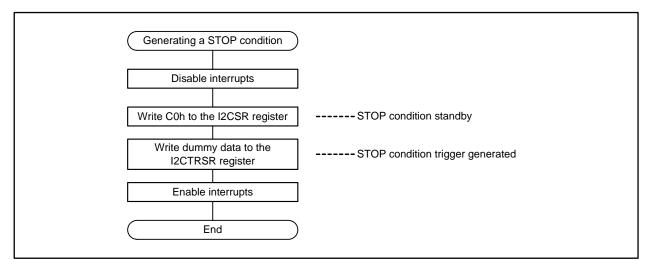

| 24. | 3     | Generating a STOP Condition                                                  | 397 |

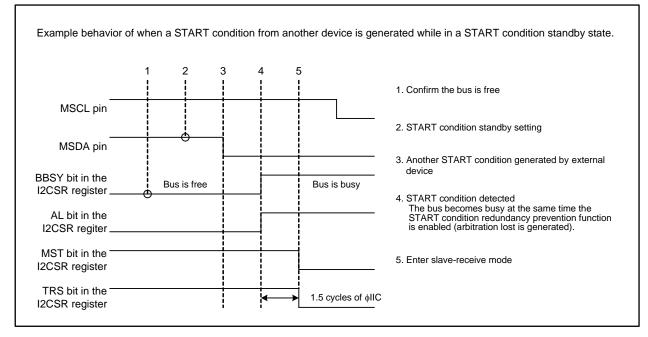

| 24. | 4     | START Condition Redundancy Prevention Function                               | 398 |

| 24. | 5     | Detecting START and STOP Conditions                                          | 399 |

| 24. | 6     | Data Transmission and Reception                                              | 401 |

| 2   | 4.6.1 | Master Transmission                                                          | 402 |

| 2   | 4.6.2 | Slave Reception                                                              | 403 |

| 24. | 7     | Notes on Using Multi-master I <sup>2</sup> C-bus Interface                   | 404 |

| 2   | 4.7.1 | Accessing Multi-master I <sup>2</sup> C-bus Interface-Associated Registers   | 404 |

| 2   | 4.7.2 | Generating a Repeated START condition                                        | 406 |

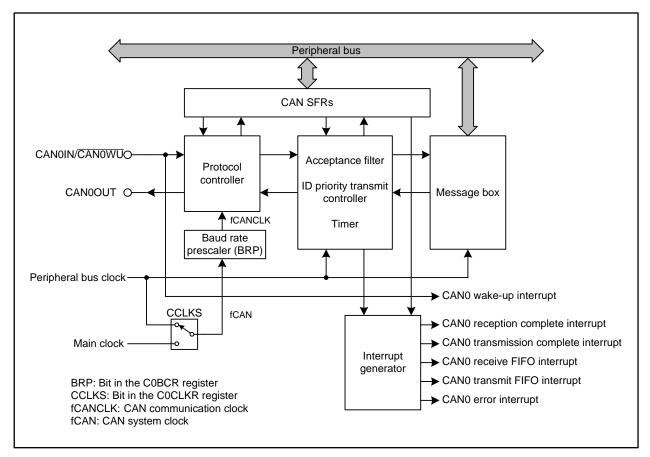

| 25. | CA    | N Module                                                                     | 407 |

| 25. | 1     | CAN SFRs                                                                     | 410 |

| 2   | 5.1.1 | CAN0 Control Register (C0CTLR Register)                                      | 411 |

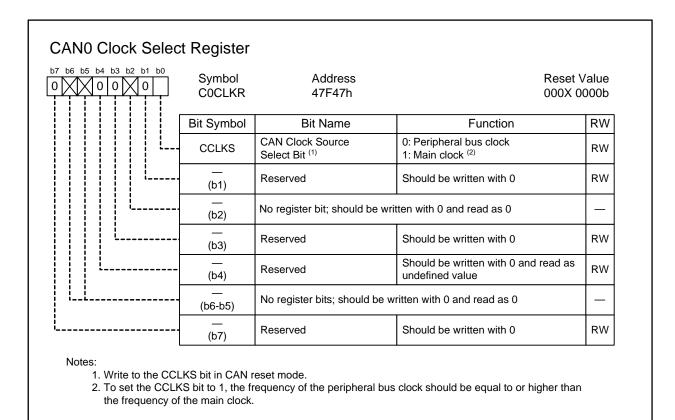

| 2   | 5.1.2 | CAN0 Clock Select Register (C0CLKR Register)                                 | 415 |

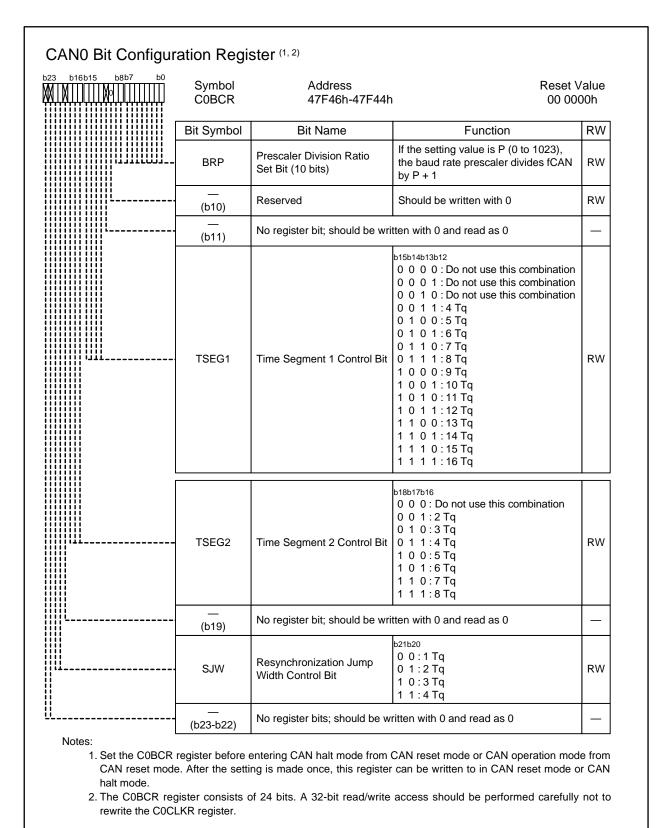

| 2   | 5.1.3 | CAN0 Bit Configuration Register (C0BCR Register)                             | 416 |

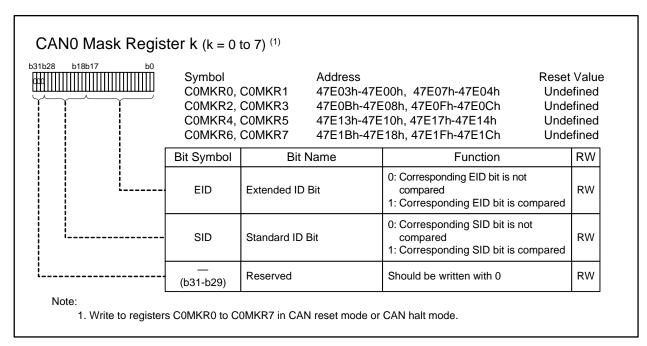

| 2   | 5.1.4 | CAN0 Mask Register k (C0MKRk Register) (k = 0 to 7)                          | 418 |

| 2   | 5.1.5 | CAN0 FIFO Received ID Compare Register n (Registers C0FIDCR0 and C0FIDCR1)   |     |

|         | (n = 0, 1)                                                       | 419 |

|---------|------------------------------------------------------------------|-----|

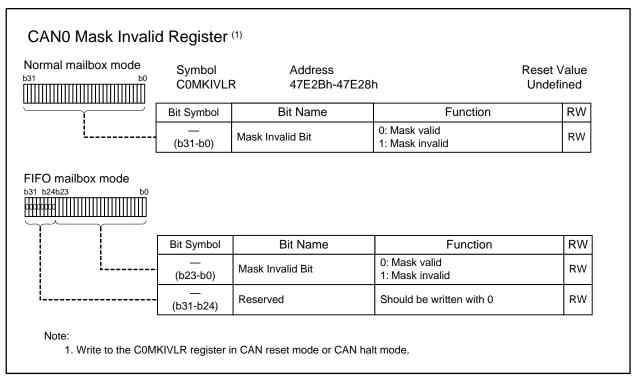

| 25.1.6  | CAN0 Mask Invalid Register (C0MKIVLR Register)                   | 421 |

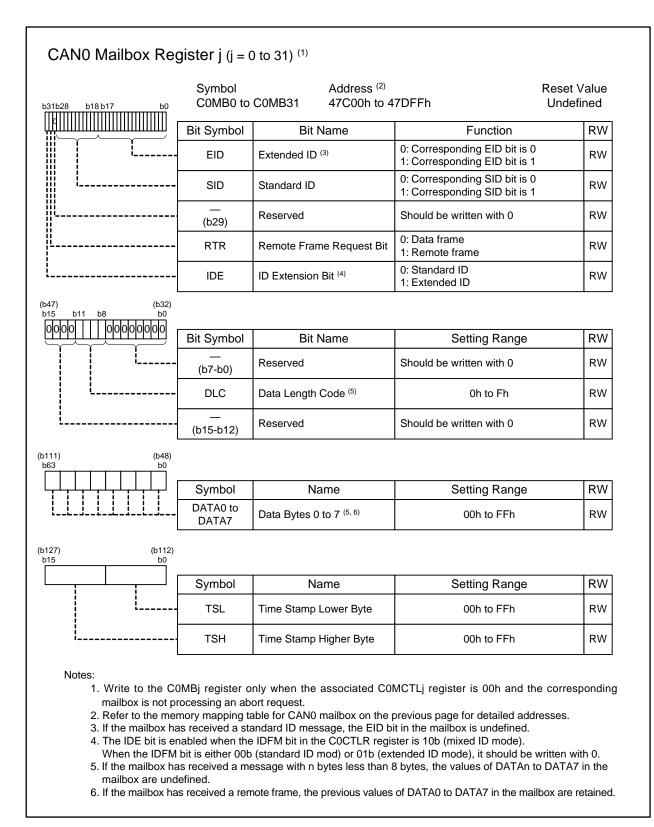

| 25.1.7  | CAN0 Mailbox (C0MBj Register) (j = 0 to 31)                      | 422 |

| 25.1.8  | CAN0 Mailbox Interrupt Enable Register (C0MIER Register)         | 426 |

| 25.1.9  | CAN0 Message Control Register j (C0MCTLj Register) (j = 0 to 31) | 427 |

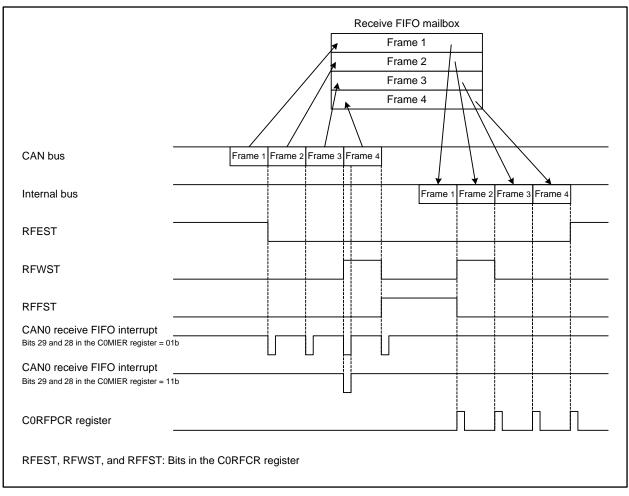

| 25.1.1  | CAN0 Receive FIFO Control Register (C0RFCR Register)             | 430 |

| 25.1.1  | CAN0 Receive FIFO Pointer Control Register (C0RFPCR Register)    | 433 |

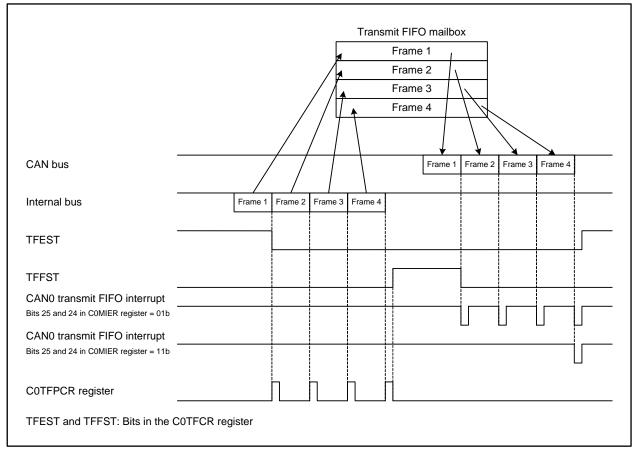

| 25.1.1  | 2 CAN0 Transmit FIFO Control Register (C0TFCR Register)          | 434 |

| 25.1.1  | 3 CAN0 Transmit FIFO Pointer Control Register (C0TFPCR Register) | 436 |

| 25.1.1  | 4 CAN0 Status Register (C0STR Register)                          | 437 |

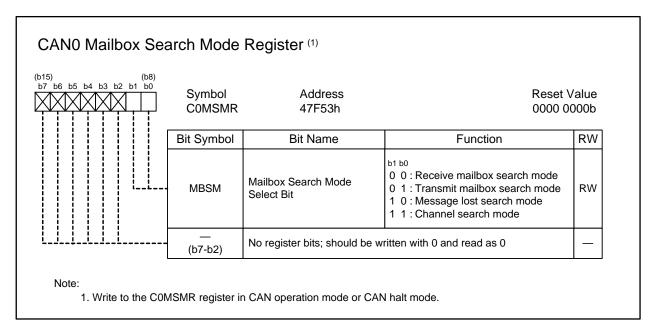

| 25.1.1  | 5 CAN0 Mailbox Search Mode Register (C0MSMR Register)            | 440 |

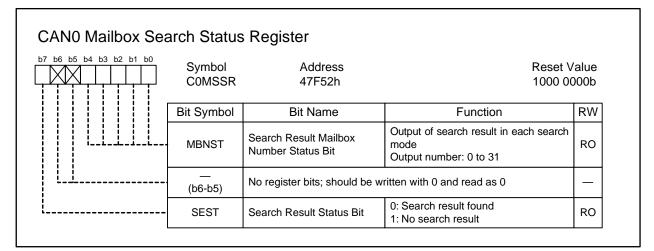

| 25.1.1  | 6 CAN0 Mailbox Search Status Register (C0MSSR Register)          | 441 |

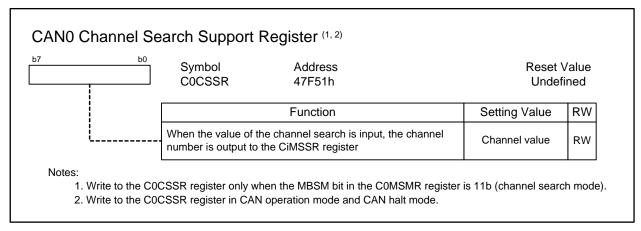

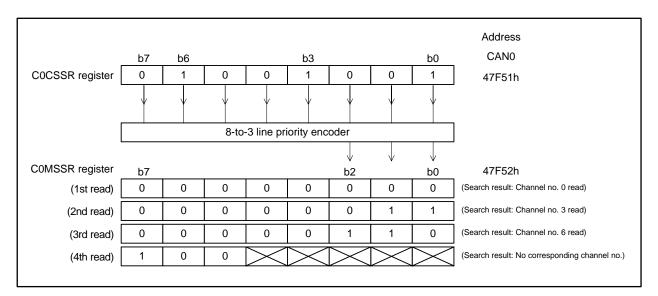

| 25.1.1  | 7 CAN0 Channel Search Support Register (C0CSSR Register)         | 443 |

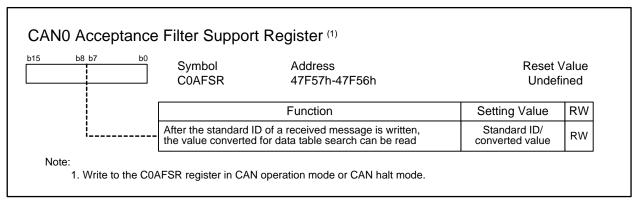

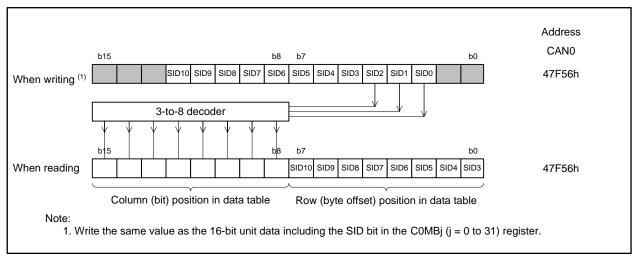

| 25.1.1  | 3 CAN0 Acceptance Filter Support Register (C0AFSR Register)      | 444 |

| 25.1.1  | O CAN0 Error Interrupt Enable Register (C0EIER Register)         | 445 |

| 25.1.2  | CAN0 Error Interrupt Factor Judge Register (C0EIFR Register)     | 447 |

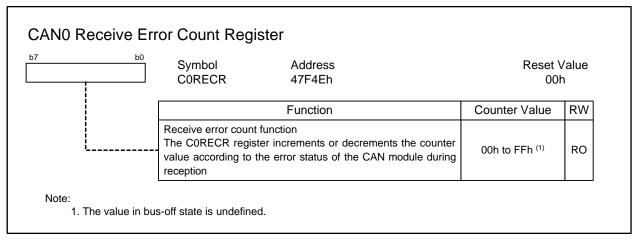

| 25.1.2  | 1 CAN0 Receive Error Count Register (C0RECR Register)            | 450 |

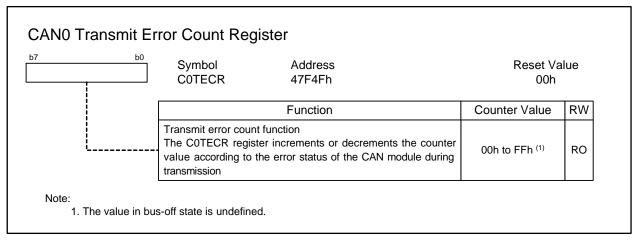

| 25.1.2  | 2 CAN0 Transmit Error Count Register (C0TECR Register)           | 451 |

| 25.1.2  | 3 CAN0 Error Code Store Register (C0ECSR Register)               | 452 |

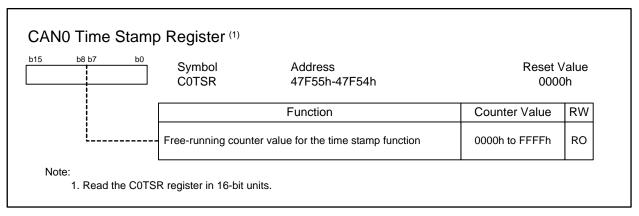

| 25.1.2  | 4 CAN0 Time Stamp Register (C0TSR Register)                      | 454 |

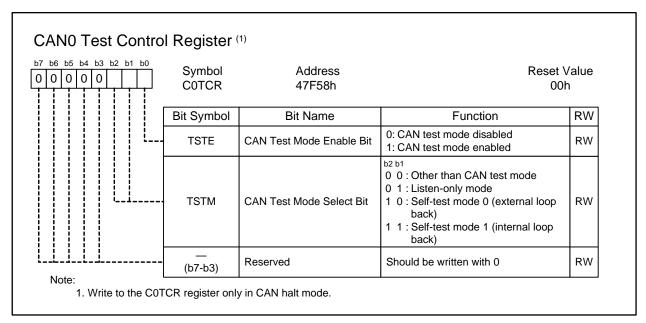

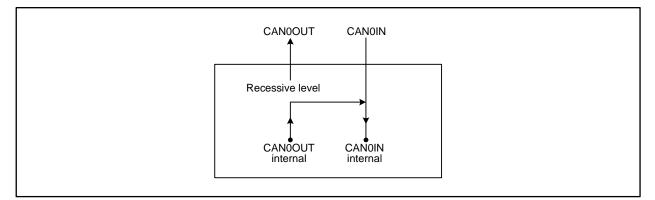

| 25.1.2  | 5 CAN0 Test Control Register (C0TCR Register)                    | 455 |

| 25.2    | Operating Mode                                                   | 458 |

| 25.2.1  | CAN Reset Mode                                                   | 459 |

| 25.2.2  | CAN Halt Mode                                                    | 460 |

| 25.2.3  | CAN Sleep Mode                                                   | 461 |

| 25.2.4  | CAN Operation Mode (Excluding Bus-Off State)                     | 462 |

| 25.2.5  | CAN Operation Mode (Bus-Off State)                               | 463 |

| 25.3    | CAN Communication Speed Configuration                            | 464 |

| 25.3.1  | CAN Clock Configuration                                          | 464 |

| 25.3.2  | Bit Timing Configuration                                         | 464 |

| 25.3.3  | Bit rate                                                         | 465 |

| 25.4    | Mailbox and Mask Register Structure                              | 466 |

| 25.5    | Acceptance Filtering and Masking Function                        | 468 |

| 25.6    | Reception and Transmission                                       | 471 |

| 25.6.1  | Reception                                                        | 472 |

| 25.6.2  | Transmission                                                     | 474 |

| 25.7    | CAN Interrupt                                                    | 475 |

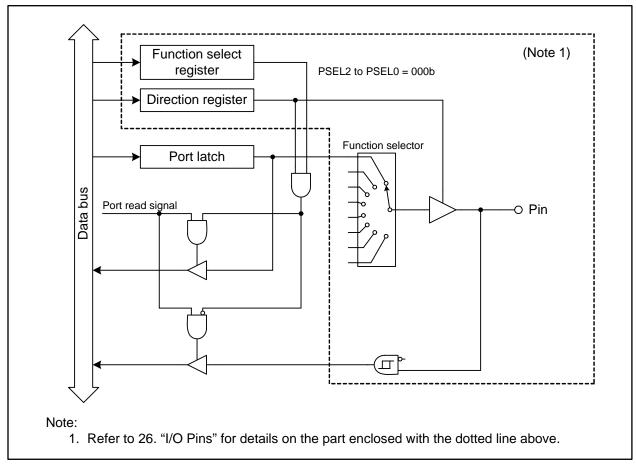

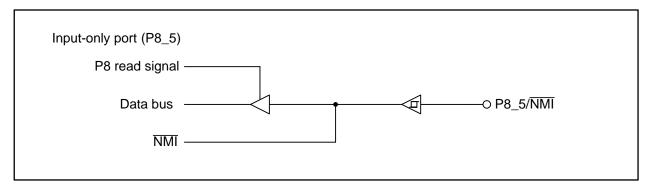

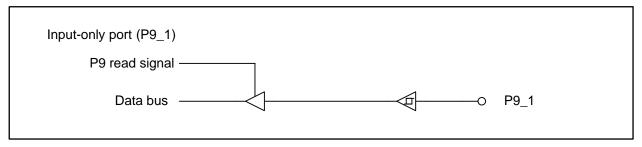

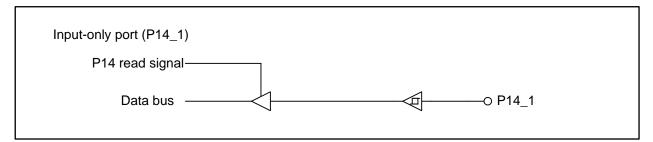

| 26. I/O | Pins                                                             | 476 |

| 26.1    | Port Pi Direction Register (PDi Register, i = 0 to 15)           | 477 |

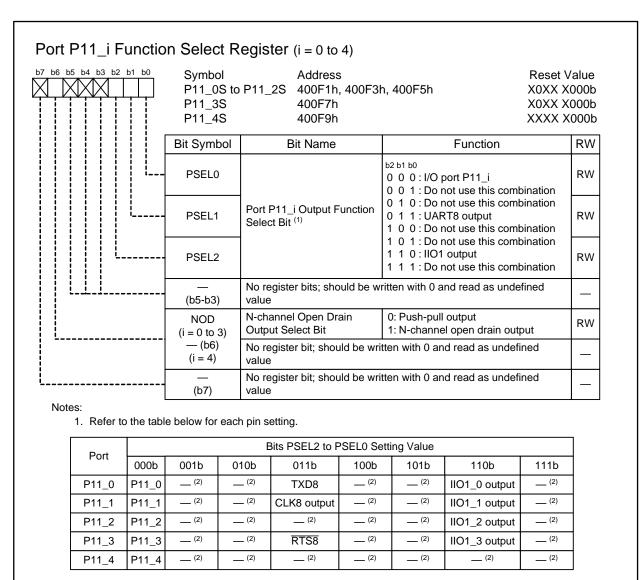

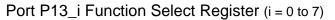

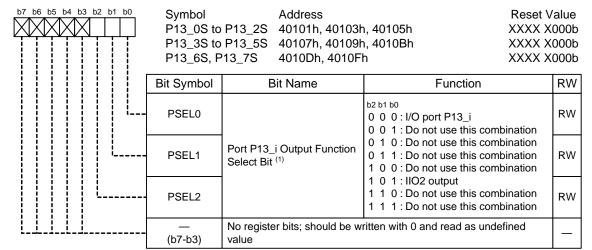

| 26.2    | Output Function Select Register                                  | 478 |

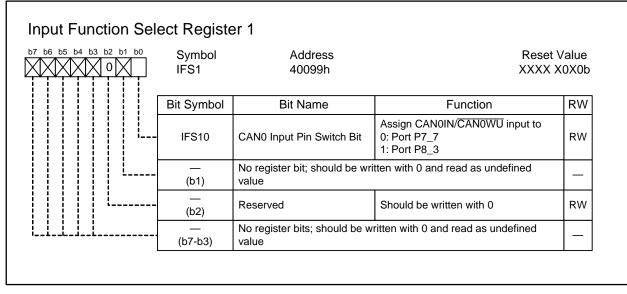

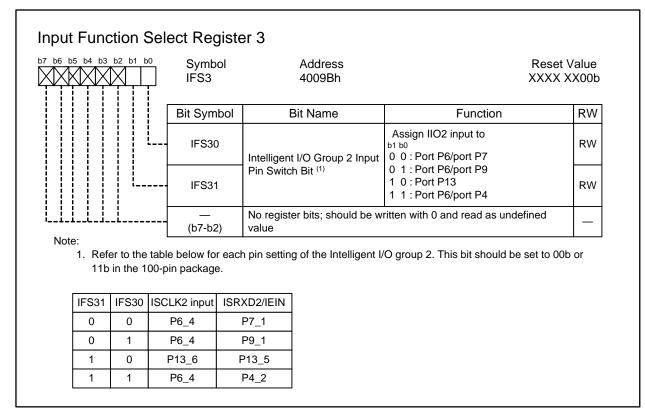

| 26.3    | Input Function Select Register                                             | 496 |

|---------|----------------------------------------------------------------------------|-----|

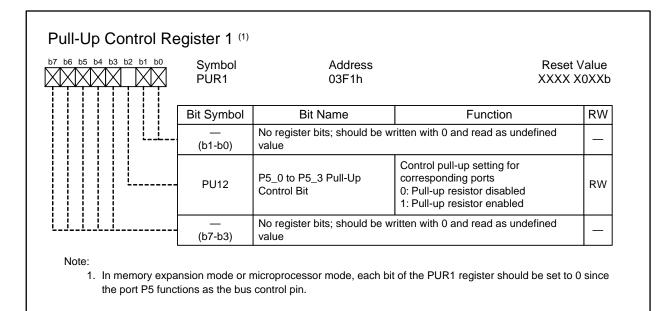

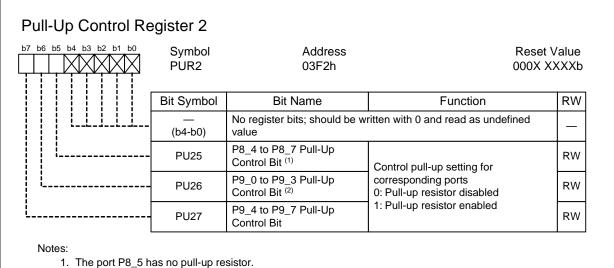

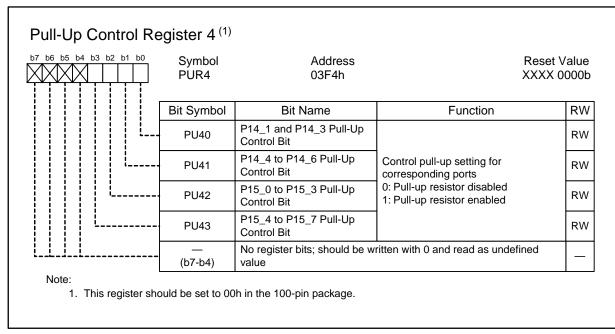

| 26.4    | Pull-up Control Registers 0 to 4 (Registers PUR0 to PUR4)                  | 501 |

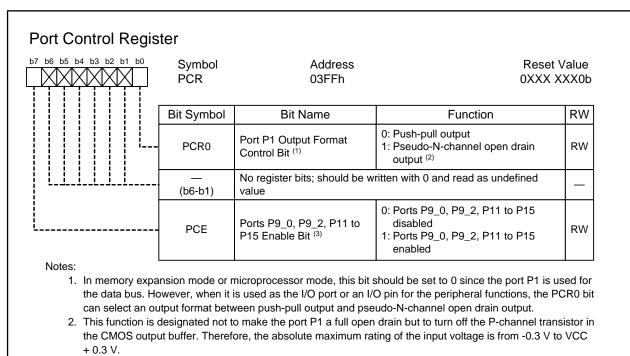

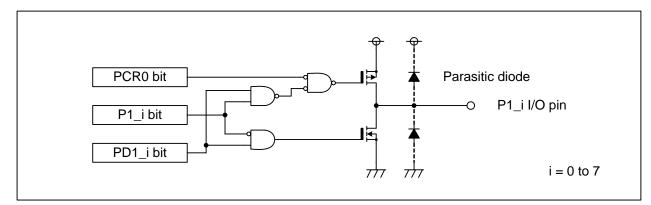

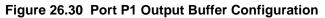

| 26.5    | Port Control Register (PCR Register)                                       | 504 |

| 26.6    | How To Configure Unused Pins                                               | 505 |

| 27. Fla | sh Memory                                                                  | 508 |

| 27.1    | Overview                                                                   | 508 |

| 27.2    | Flash Memory Protection                                                    | 510 |

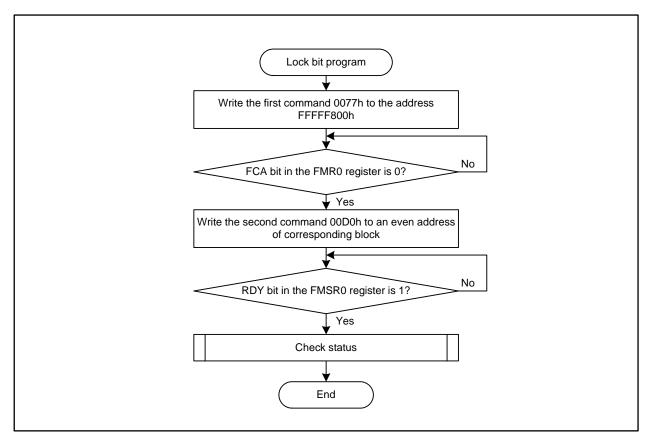

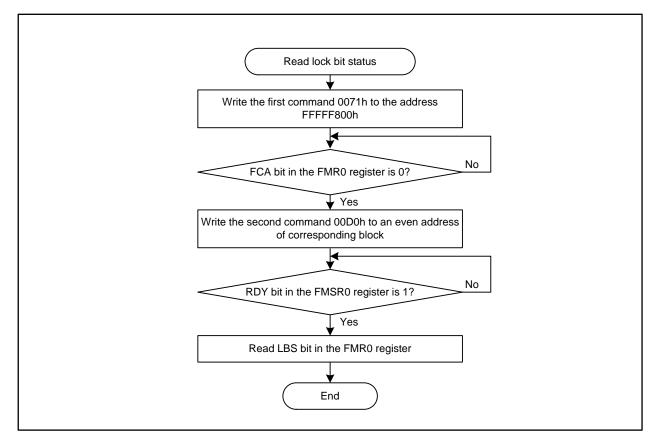

| 27.2.1  | Lock Bit Protection                                                        | 510 |

| 27.2.2  | ROM Code Protection                                                        | 510 |

| 27.2.3  | ID Code Protection                                                         | 511 |

| 27.2.4  | Forcible Erase Function                                                    | 512 |

| 27.2.5  | Standard Serial I/O Mode Disable Function                                  | 513 |

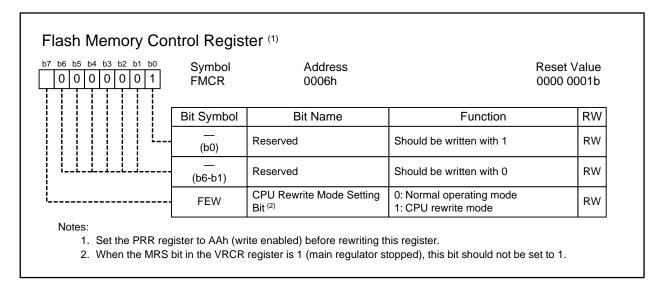

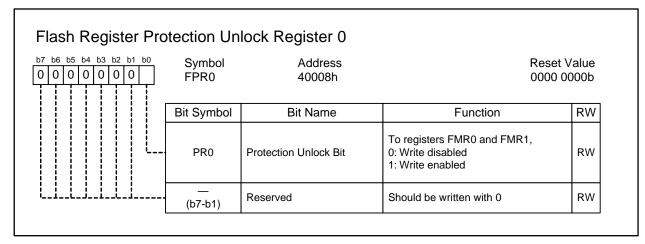

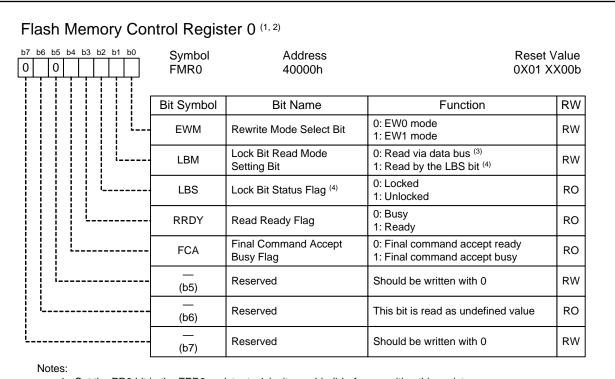

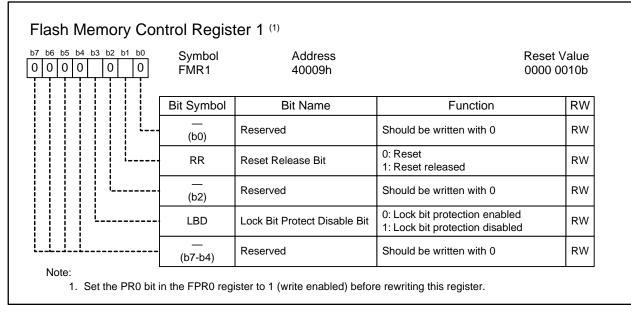

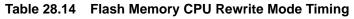

| 27.3    | CPU Rewrite Mode                                                           | 514 |

| 27.3.1  | CPU Operating Mode and Flash Memory Rewrite                                | 522 |

| 27.3.2  | Flash Memory Rewrite Bus Timing                                            | 523 |

| 27.3.3  | Software Commands                                                          | 527 |

| 27.3.4  | Mode Transition                                                            | 528 |

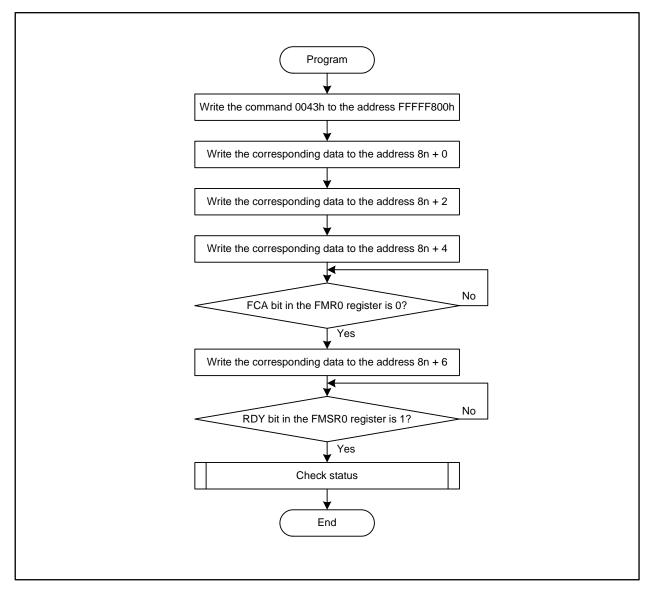

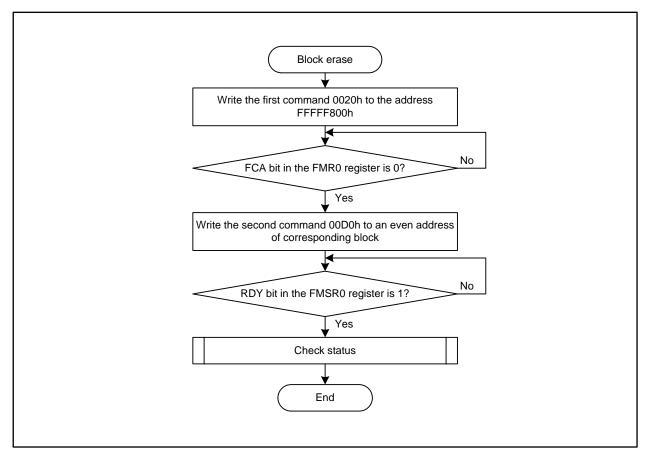

| 27.3.5  | How to Issue Software Commands                                             | 529 |

| 27.3.6  | Status Check                                                               | 535 |

| 27.4    | Standard Serial I/O Mode                                                   | 536 |

| 27.5    | Parallel I/O mode                                                          | 539 |

| 27.6    | Notes on Flash Memory Rewriting                                            | 540 |

| 27.6.1  | Note on Power Supply                                                       | 540 |

| 27.6.2  | Note on Hardware Reset                                                     | 540 |

| 27.6.3  | Note on Flash Memory Protection                                            | 540 |

| 27.6.4  | Notes on Programming                                                       | 540 |

| 27.6.5  | Notes on Interrupts                                                        | 540 |

| 27.6.6  | Notes on Rewrite Control Program                                           | 541 |

| 27.6.7  | Notes on Number of Programming/Erasure and Software Command Execution Time | 541 |

| 27.6.8  | Other Notes                                                                | 541 |

| 28. Ele | ctrical Characteristics                                                    | 542 |

| 29. Usa | age Notes                                                                  | 583 |

| 29.1    | Notes on Board Designing                                                   | 583 |

| 29.1.1  | Power Supply Pins                                                          | 583 |

| 29.1.2  | Supply Voltage                                                             | 583 |

| 29.2    | Notes on Register Setting                                                  | 584 |

| 29.2.1  | Registers with Write-only Bits                                             | 584 |

| 29.3    | Notes on Clock Generator                                                   | 586 |

| 29.3.1  | Sub Clock                                                                  | 586 |

| 29.3.2     | Power Control                                                              | 586 |

|------------|----------------------------------------------------------------------------|-----|

| 29.4 No    | es on Bus                                                                  | 587 |

| 29.4.1     | Notes on System Designing                                                  | 587 |

| 29.4.2     | Notes on Register Settings                                                 | 587 |

| 29.5 No    | es on Interrupts                                                           | 588 |

| 29.5.1     | ISP Setting                                                                | 588 |

| 29.5.2     | NMI                                                                        | 588 |

| 29.5.3     | External Interrupt                                                         | 588 |

| 29.6 No    | es on DMAC                                                                 | 589 |

| 29.6.1     | DMAC-associated Register Settings                                          | 589 |

| 29.6.2     | Read from DMAC-associated Registers                                        | 589 |

| 29.7 No    | es on Timers                                                               | 590 |

| 29.7.1     | Timer A and Timer B                                                        | 590 |

| 29.7.2     | Timer A                                                                    | 590 |

| 29.7.3     | Timer B                                                                    | 592 |

| 29.8 No    | es on Three-phase Motor Control Timers                                     | 593 |

| 29.8.1     | Shutdown                                                                   | 593 |

| 29.8.2     | Register setting                                                           | 593 |

| 29.9 No    | es on Serial Interface                                                     | 594 |

| 29.9.1     | Changing the UiBRG Register (i = 0 to 8)                                   | 594 |

| 29.9.2     | Synchronous Serial Interface Mode                                          | 594 |

| 29.9.3     | Special Mode 1 (I <sup>2</sup> C Mode)                                     | 594 |

| 29.9.4     | Reset Procedure on Communication Error                                     | 595 |

| 29.10 No   | es on A/D Converter                                                        | 596 |

| 29.10.1    | Notes on Designing Boards                                                  | 596 |

| 29.10.2    | Notes on Programming                                                       | 597 |

| 29.11 No   | es on Flash Memory Rewriting                                               | 598 |

| 29.11.1    | Note on Power Supply                                                       | 598 |

| 29.11.2    | Note on Hardware Reset                                                     | 598 |

| 29.11.3    | Note on Flash Memory Protection                                            | 598 |

| 29.11.4    | Notes on Programming                                                       | 598 |

| 29.11.5    | Notes on Interrupts                                                        | 598 |

| 29.11.6    | Notes on Rewrite Control Program                                           | 599 |

| 29.11.7    | Notes on Number of Programming/Erasure and Software Command Execution Time | 599 |

| 29.11.8    | Other Notes                                                                | 599 |

| Appendix 1 | Package Dimensions                                                         | 600 |

| INDEX      |                                                                            | 601 |

RENESAS MCU

### 1. Overview

#### 1.1 Features

The M16C Family offers a robust platform of 32-/16-bit CISC microcomputers (MCUs) featuring high ROM code efficiency, extensive EMI/EMS noise immunity, ultra-low power consumption, high-speed processing in actual applications, and numerous and varied integrated peripherals. Extensive device scalability from low- to high-end, featuring a single architecture as well as compatible pin assignments and peripheral functions, provides support for a vast range of application fields.

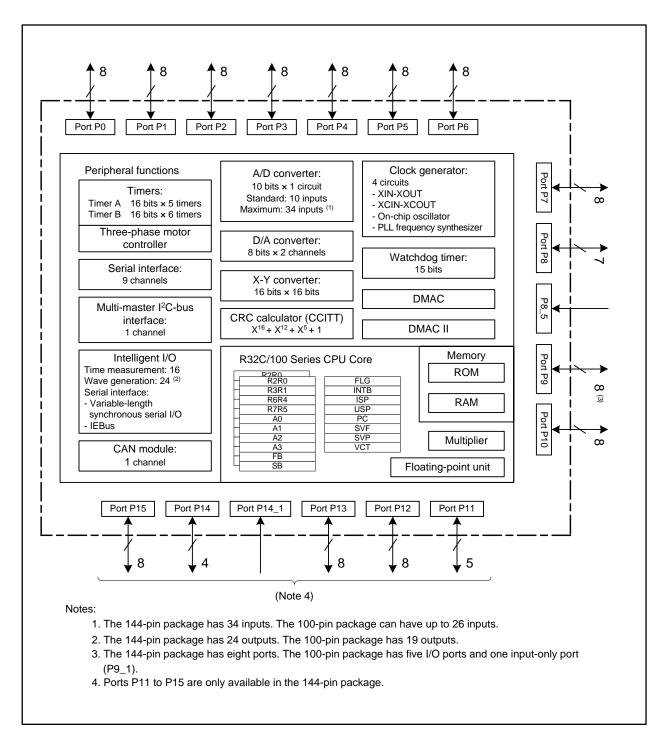

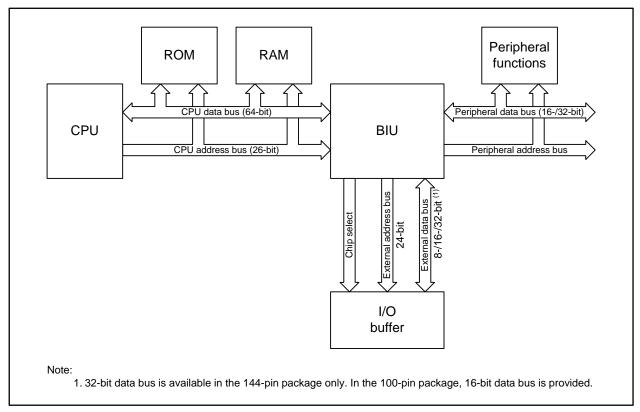

The R32C/100 Series is a high-end microcontroller series in the M16C Family. With a 4-Gbyte memory space, it achieves maximum code efficiency and high-speed processing with 32-bit CISC architecture, multiplier, multiply-accumulate unit, and floating point unit. The selection from the broadest choice of on-chip peripheral devices — UART, CRC, DMAC, A/D and D/A converters, timers, I<sup>2</sup>C, and watchdog timer enables to minimize external components.

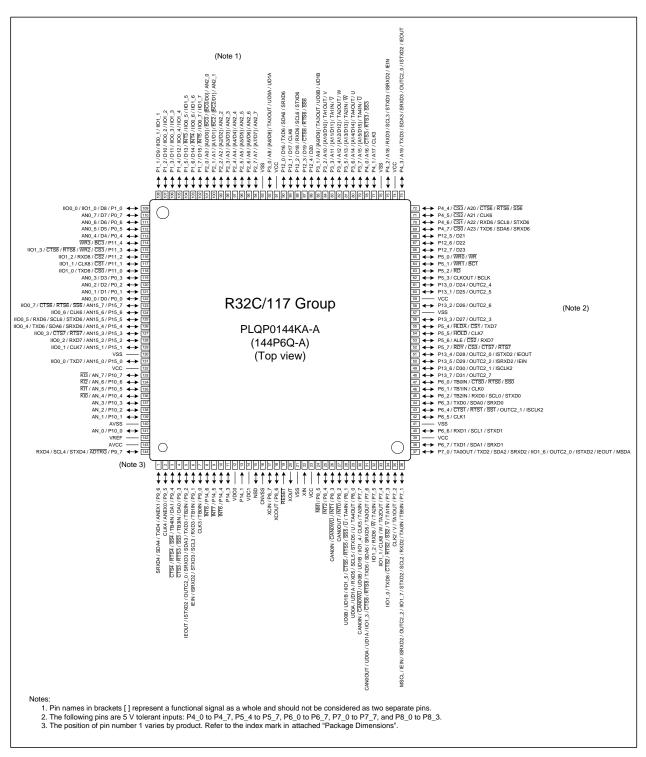

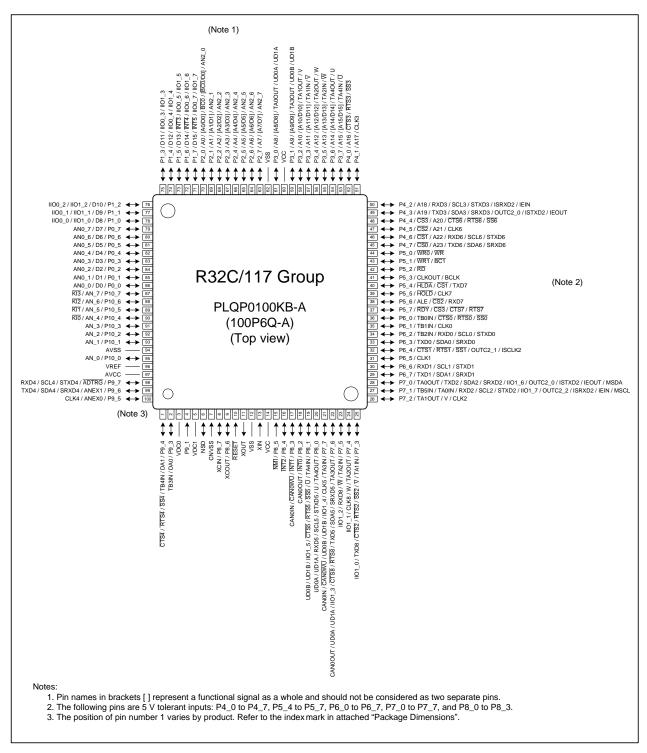

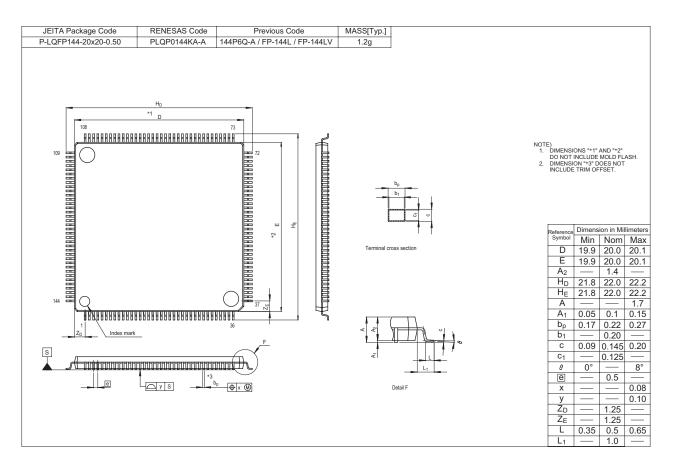

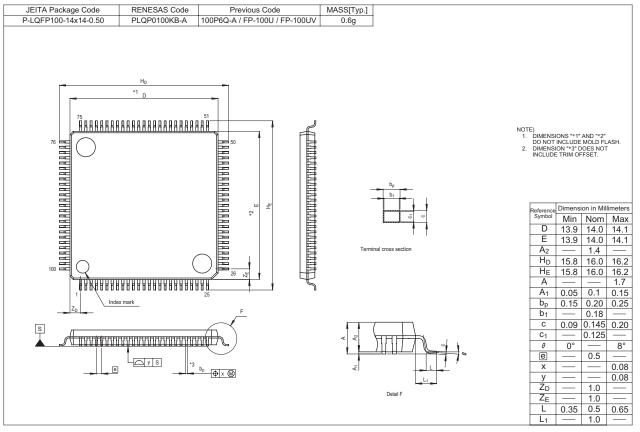

The R32C/117 Group is the standard MCU within the R32C/100 Series. This product, provided as 100-pin and 144-pin plastic molded LQFP packages, configures nine channels of serial interface, one channel of multi-master I<sup>2</sup>C-bus interface, and one channel of CAN module.

#### 1.1.1 Applications

Car audio, audio, printer, office/industrial equipment, etc.

#### 1.1.2 Performance Overview

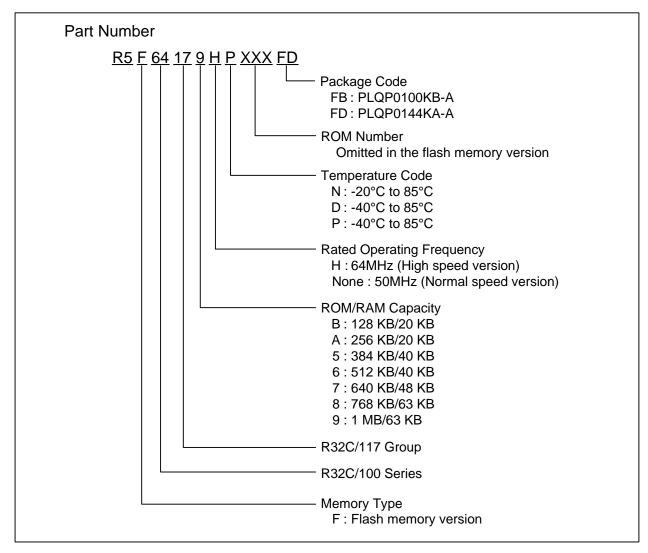

Table 1.1 to Table 1.4 list the performance overview of the R32C/117 Group.

#### Table 1.1Performance Overview for the 144 pin-Package (1/2)

| Unit                | Function                   | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU<br>Memory       | Central<br>processing unit | <ul> <li>R32C/100 Series CPU Core</li> <li>Basic instructions: 108</li> <li>Minimum instruction execution time: 15.625 ns (f(CPU) = 64 MHz)</li> <li>Multiplier: 32-bit × 32-bit → 64-bit</li> <li>Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit</li> <li>IEEE-754 floating point standard: Single precision</li> <li>32-bit barrel shifter</li> <li>Operating mode: Single-chip mode, memory expansion mode, microprocessor mode (optional <sup>(1)</sup>)</li> <li>Flash memory: 384 Kbytes to 1 Mbyte</li> <li>RAM: 40 K/48 K/63 Kbytes</li> <li>Data flash: 4 Kbytes × 2 blocks</li> </ul> |

|                     |                            | Refer to Table 1.5 for each product's memory size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Voltage<br>Detector | Low voltage<br>detector    | Optional <sup>(1)</sup><br>Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

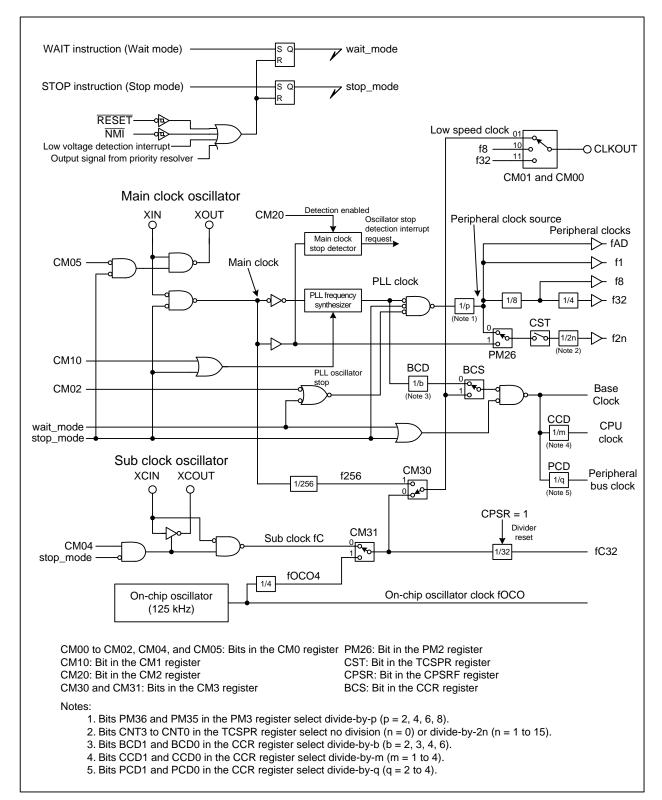

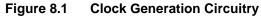

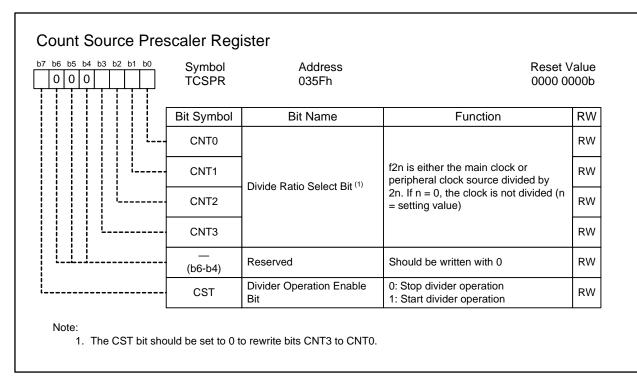

| Clock               | Clock generator            | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| External Bus        | Bus and memory             | Address space: 4 Gbytes (of which up to 64 Mbytes is user                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Expansion           | expansion                  | <ul> <li>accessible)</li> <li>External bus Interface: Support for wait-state insertion, 4 chip select outputs</li> <li>Bus format: Separate bus/Multiplexed bus selectable, data bus width selectable (8/16/32 bits)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |

| Interrupts          |                            | Interrupt vectors: 261<br>External interrupt inputs: $\overline{\text{NMI}}$ , $\overline{\text{INT}} \times 9$ , key input × 4<br>Interrupt priority levels: 7                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Watchdog Tim        | er                         | 15 bits × 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DMA                 | DMAC                       | <ul> <li>4 channels</li> <li>Cycle-steal transfer mode</li> <li>Request sources: 57</li> <li>2 transfer modes: Single transfer, repeat transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     | DMAC II                    | <ul> <li>Can be activated by any peripheral interrupt source</li> <li>3 transfer functions: Immediate data transfer, calculation transfer, chained transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O Ports           | Programmable<br>I/O ports  | <ul> <li>2 input-only ports</li> <li>120 CMOS I/O ports (of which 32 are 5 V tolerant)</li> <li>A pull-up resistor is selectable for every 4 input ports (except 5 V tolerant inputs)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |

Note:

| Unit                        | Function                              | Explanation                                                                                                                                                                                                                         |  |  |  |

|-----------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

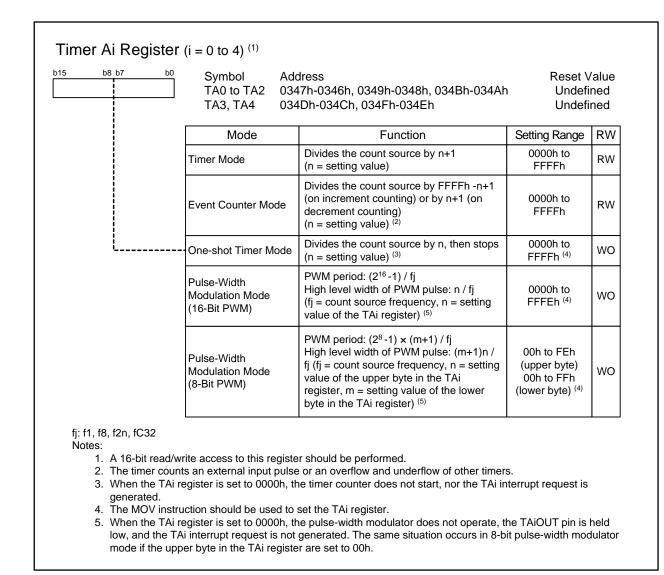

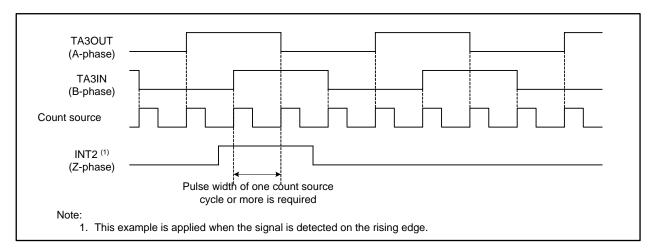

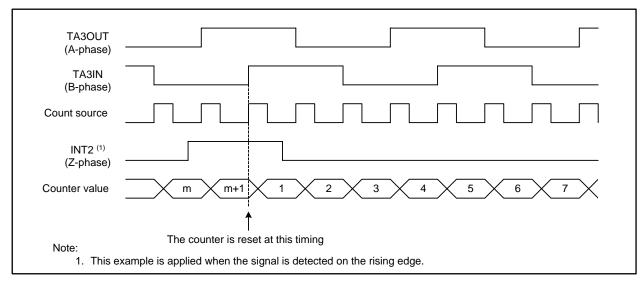

| Timer                       | Timer A                               | <ul> <li>16-bit timer × 5</li> <li>Timer mode, event counter mode, one-shot timer mode, pulse-width modulation (PWM) mode</li> <li>Two-phase pulse signal processing in event counter mode (two-phase encoder input) × 3</li> </ul> |  |  |  |

|                             | Timer B                               | <ul> <li>16-bit timer × 6</li> <li>Timer mode, event counter mode, pulse frequency measurement<br/>mode, pulse-width measurement mode</li> </ul>                                                                                    |  |  |  |

|                             | Three-phase<br>motor control<br>timer | Three-phase motor control timer × 1 (timers A1, A2, A4, and B2 used)<br>8-bit programmable dead time timer                                                                                                                          |  |  |  |

| Serial<br>Interface         | UART0 to UART8                        | Asynchronous/synchronous serial interface × 9 channels<br>• I <sup>2</sup> C-bus (UART0 to UART6)<br>• Special mode 2 (UART0 to UART6)<br>• IEBus (optional <sup>(1)</sup> ) (UART0 to UART6)                                       |  |  |  |

| A/D Converter               |                                       | 10-bit resolution × 34 channels<br>Sample and hold functionality integrated                                                                                                                                                         |  |  |  |

| D/A Converter               |                                       | 8-bit resolution × 2                                                                                                                                                                                                                |  |  |  |

| CRC Calculato               | r                                     | CRC-CCITT (X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1)                                                                                                                                                                  |  |  |  |

| X-Y Converter               |                                       | 16 bits × 16 bits                                                                                                                                                                                                                   |  |  |  |

| Intelligent I/O             |                                       | Time measurement (input capture): 16 bits × 16<br>Waveform generation (output compare): 16 bits × 24<br>Serial interface: Variable-length synchronous serial I/O mode, IEBus<br>mode (optional <sup>(1)</sup> )                     |  |  |  |

| Multi-master I <sup>2</sup> | C-bus Interface                       | 1 channel                                                                                                                                                                                                                           |  |  |  |

| CAN Module                  |                                       | 1 channel<br>CAN functionality compliant with ISO11898-1<br>32 mailboxes                                                                                                                                                            |  |  |  |

| Flash Memory                |                                       | Programming and erasure supply voltage: VCC = 3.0 to 5.5 V<br>Minimum endurance: 1,000 program/erase cycles<br>Security protection: ROM code protect, ID code protect<br>Debugging: On-chip debug, on-board flash programming       |  |  |  |

| Operating Fred<br>Voltage   | uency/Supply                          | 64 MHz (high speed version)/VCC = 3.0 to 5.5 V<br>50 MHz (normal speed version)/VCC = 3.0 to 5.5 V                                                                                                                                  |  |  |  |

| Operating Tem               | perature                              | -20°C to 85°C (N version)<br>-40°C to 85°C (D version)<br>-40°C to 85°C (P version)                                                                                                                                                 |  |  |  |

| Current Consu               | mption                                | 45 mA (VCC = 5.0 V, f(CPU) = 64 MHz)<br>35 mA (VCC = 5.0 V, f(CPU) = 50 MHz)<br>8 μA (VCC = 3.3 V, f(XCIN) = 32.768 kHz, in wait mode)                                                                                              |  |  |  |

| Package                     |                                       | 144-pin plastic molded LQFP (PLQP0144KA-A)                                                                                                                                                                                          |  |  |  |

#### Table 1.2 Performance Overview for the 144-pin Package (2/2)

Note:

| Unit                      | Function                    | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU<br>Memory             | Central<br>processing unit  | <ul> <li>R32C/100 Series CPU Core</li> <li>Basic instructions: 108</li> <li>Minimum instruction execution time: 15.625 ns (f(CPU) = 64 MHz)</li> <li>Multiplier: 32-bit × 32-bit → 64-bit</li> <li>Multiply-accumulate unit: 32-bit × 32-bit + 64-bit → 64-bit</li> <li>IEEE-754 floating point standard: Single precision</li> <li>32-bit barrel shifter</li> <li>Operating mode: Single-chip mode, memory expansion mode, microprocessor mode (optional <sup>(1)</sup>)</li> <li>Flash memory: 128 Kbytes to 1 Mbyte</li> </ul> |

| Memory                    |                             | RAM: 20 K/40 K/48 K/63 Kbytes<br>Data flash: 4 Kbytes × 2 blocks<br>Refer to Table 1.5 for each product's memory size                                                                                                                                                                                                                                                                                                                                                                                                             |

| Voltage<br>Detector       | Low voltage<br>detector     | Optional <sup>(1)</sup><br>Low voltage detection interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Clock                     | Clock generator             | <ul> <li>4 circuits (main clock, sub clock, PLL, on-chip oscillator)</li> <li>Oscillation stop detector: Main clock oscillator stop/restart detection</li> <li>Frequency divide circuit: Divide-by-2 to divide-by-24 selectable</li> <li>Low power modes: Wait mode, stop mode</li> </ul>                                                                                                                                                                                                                                         |

| External Bus<br>Expansion | Bus and memory<br>expansion | <ul> <li>Address space: 4 Gbytes (of which up to 64 Mbytes is user accessible)</li> <li>External bus Interface: Support for wait-state insertion, 4 chip select outputs</li> <li>Bus format: Separate bus/Multiplexed bus selectable, data bus width selectable (8/16 bits)</li> </ul>                                                                                                                                                                                                                                            |

| Interrupts                |                             | Interrupt vectors: 261<br>External interrupt inputs: NMI, INT × 6, key input × 4<br>Interrupt priority levels: 7                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Watchdog Tim              | er                          | 15 bits x 1 (selectable input frequency from prescaler output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DMA                       | DMAC                        | <ul> <li>4 channels</li> <li>Cycle-steal transfer mode</li> <li>Request sources: 51</li> <li>2 transfer modes: Single transfer, repeat transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

|                           | DMAC II                     | <ul> <li>Can be activated by any peripheral interrupt source</li> <li>3 transfer functions: Immediate data transfer, calculation transfer, chained transfer</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| I/O Ports                 | Programmable<br>I/O ports   | <ul> <li>2 input-only ports</li> <li>84 CMOS I/O ports (of which 32 are 5 V tolerant)</li> <li>A pull-up resistor is selectable for every 4 input ports (except 5 V tolerant inputs)</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

#### Table 1.3 Performance Overview for the 100-pin Package (1/2)

Note:

| Unit                        | Function                              | Explanation                                                                                                                                                                                                                         |  |  |  |

|-----------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Timer                       | Timer A                               | <ul> <li>16-bit timer × 5</li> <li>Timer mode, event counter mode, one-shot timer mode, pulse-width modulation (PWM) mode</li> <li>Two-phase pulse signal processing in event counter mode (two-phase encoder input) × 3</li> </ul> |  |  |  |

|                             | Timer B                               | <ul> <li>16-bit timer × 6</li> <li>Timer mode, event counter mode, pulse frequency measurement<br/>mode, pulse-width measurement mode</li> </ul>                                                                                    |  |  |  |

|                             | Three-phase<br>motor control<br>timer | Three-phase motor control timer × 1 (timers A1, A2, A4, and B2 used)<br>8-bit programmable dead time timer                                                                                                                          |  |  |  |

| Serial<br>Interface         | UART0 to UART8                        | Asynchronous/synchronous serial interface × 9 channels<br>• I <sup>2</sup> C-bus (UART0 to UART6)<br>• Special mode 2 (UART0 to UART6)<br>• IEBus (optional <sup>(1)</sup> ) (UART0 to UART6)                                       |  |  |  |

| A/D Converter               |                                       | 10-bit resolution × 26 channels<br>Sample and hold functionality integrated                                                                                                                                                         |  |  |  |

| D/A Converter               |                                       | 8-bit resolution × 2                                                                                                                                                                                                                |  |  |  |

| CRC Calculato               | r                                     | CRC-CCITT (X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1)                                                                                                                                                                  |  |  |  |

| X-Y Converter               |                                       | 16 bits × 16 bits                                                                                                                                                                                                                   |  |  |  |

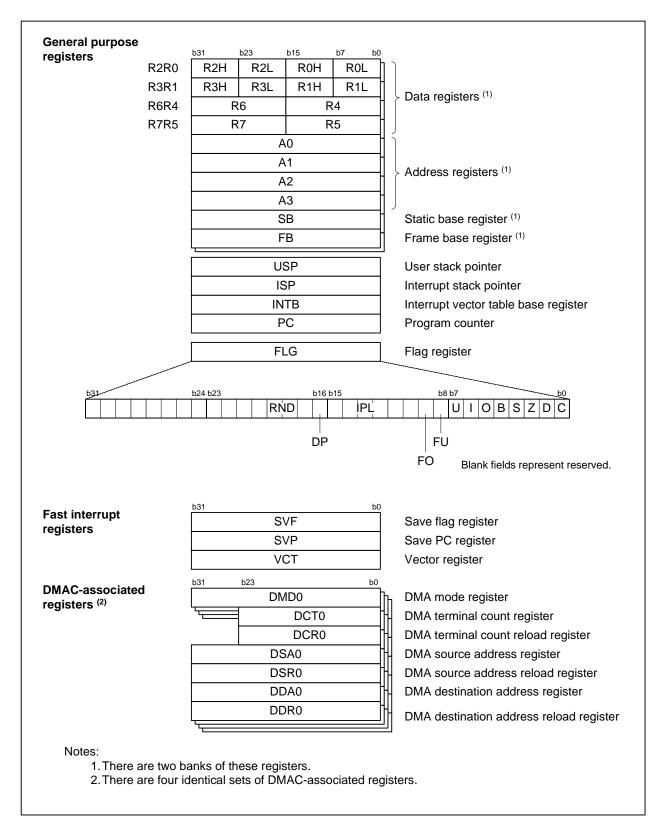

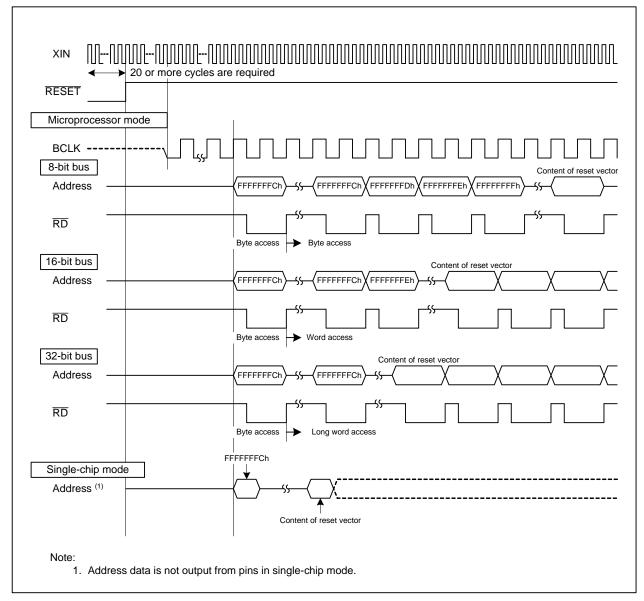

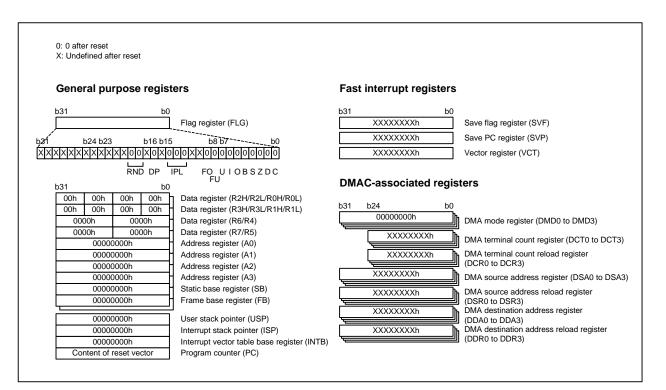

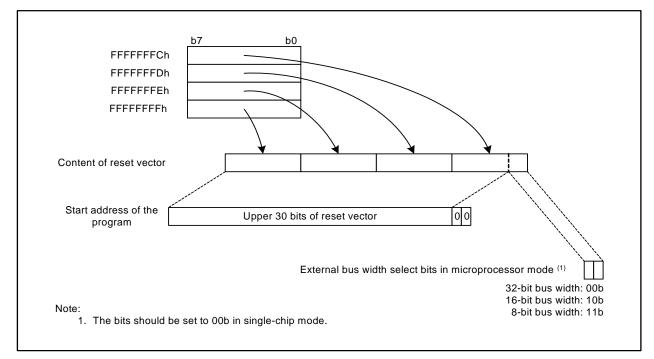

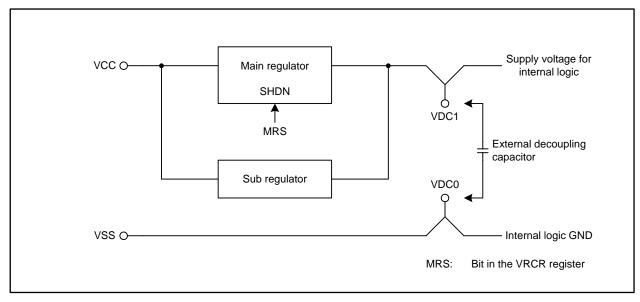

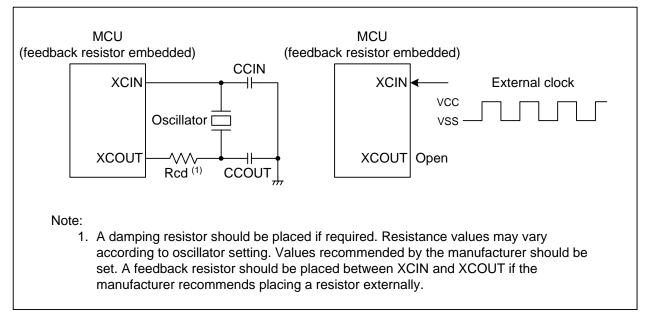

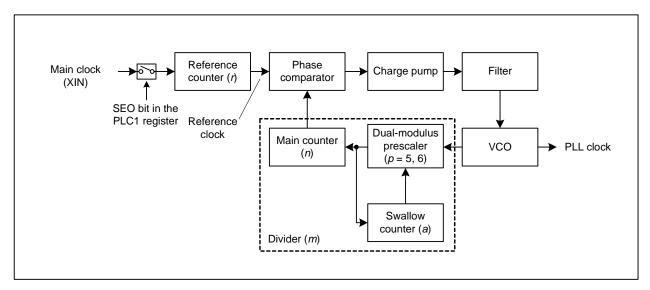

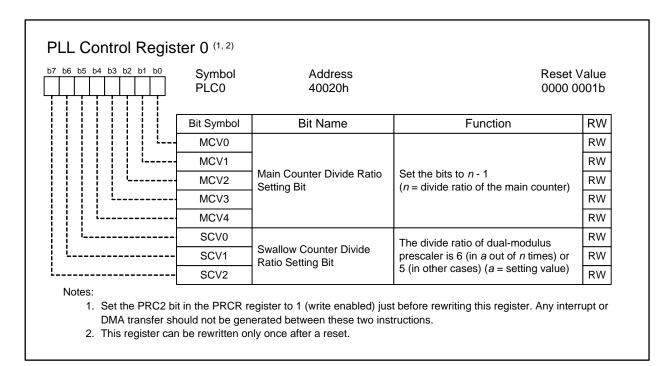

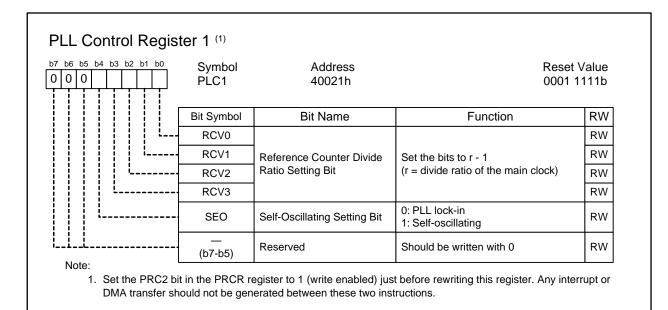

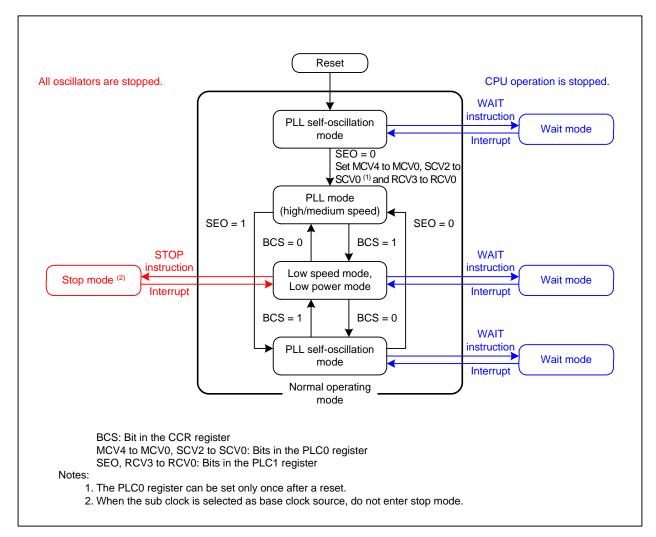

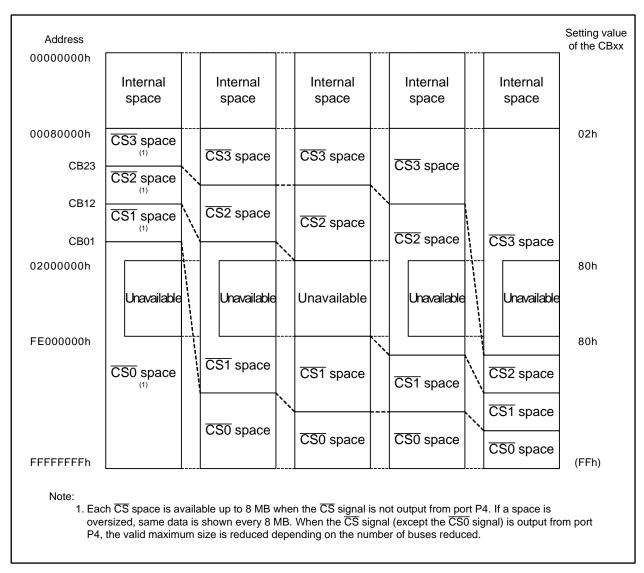

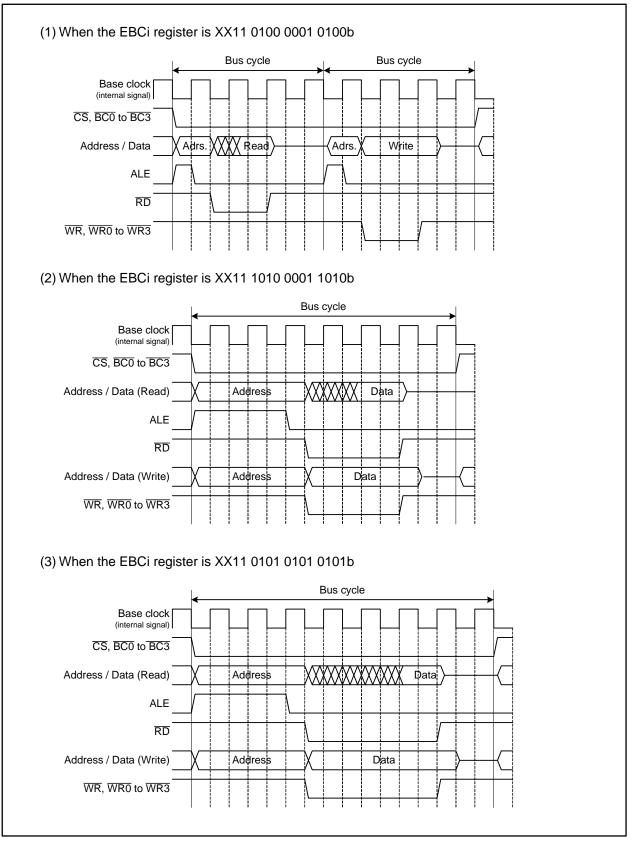

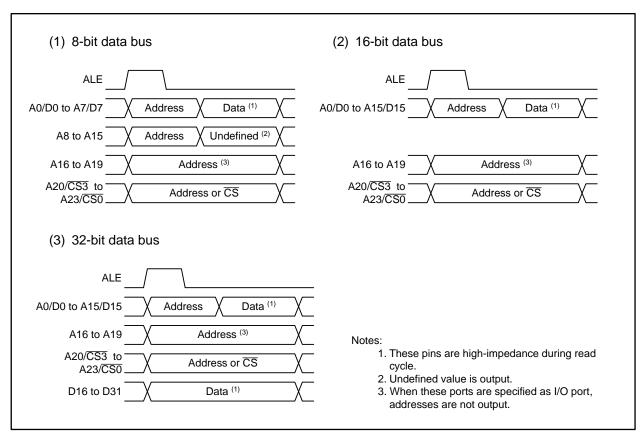

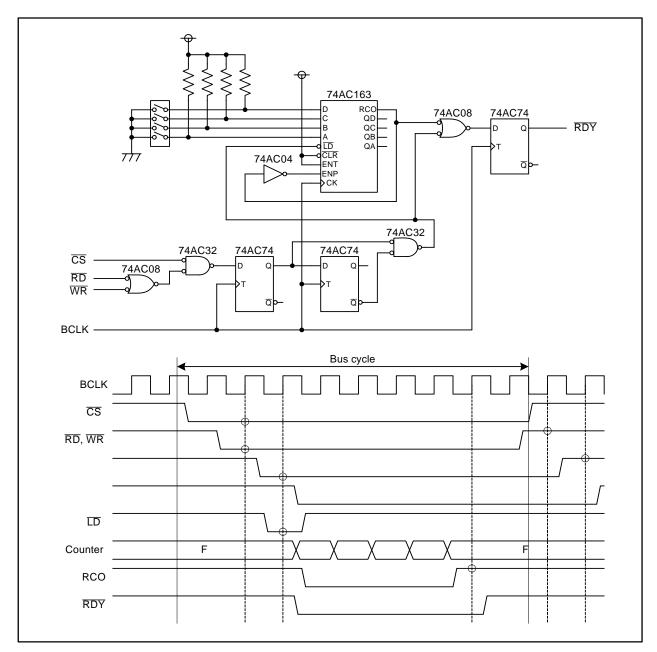

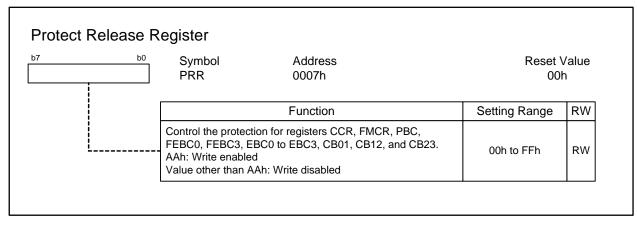

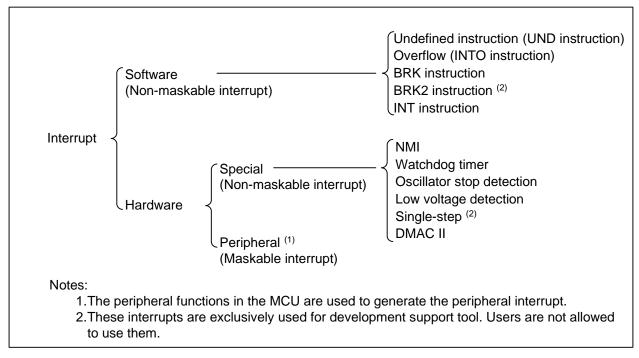

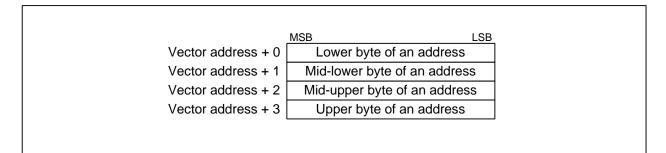

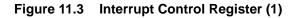

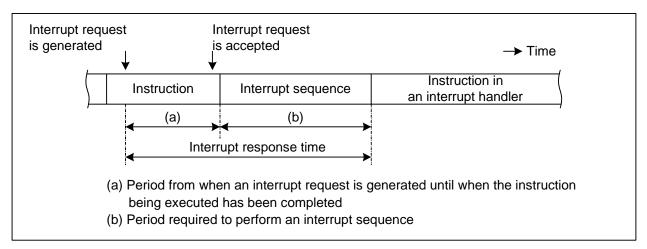

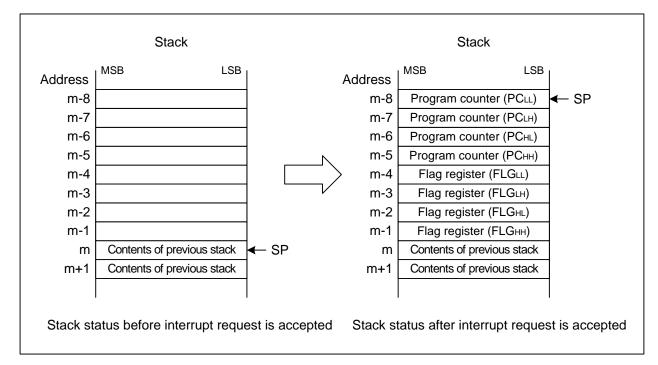

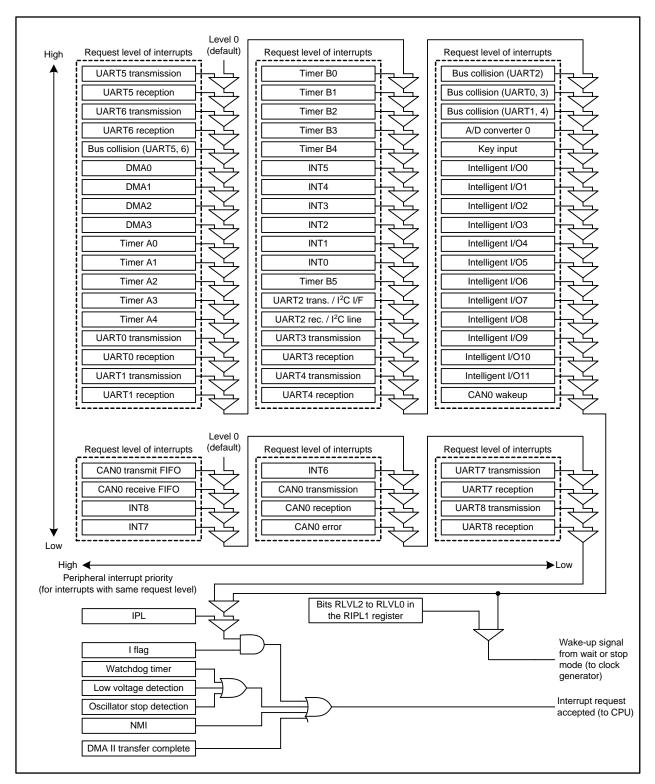

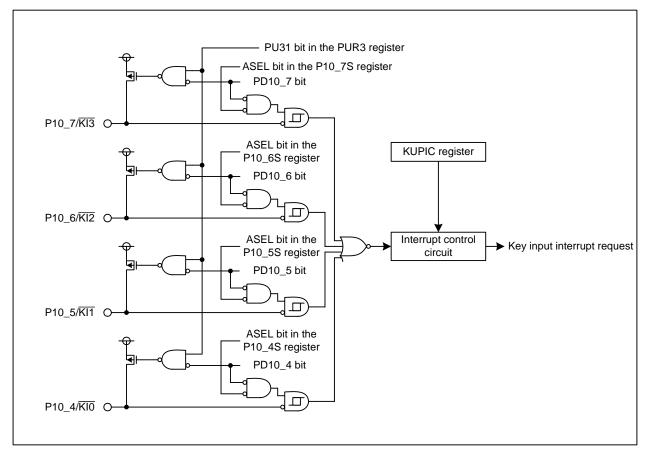

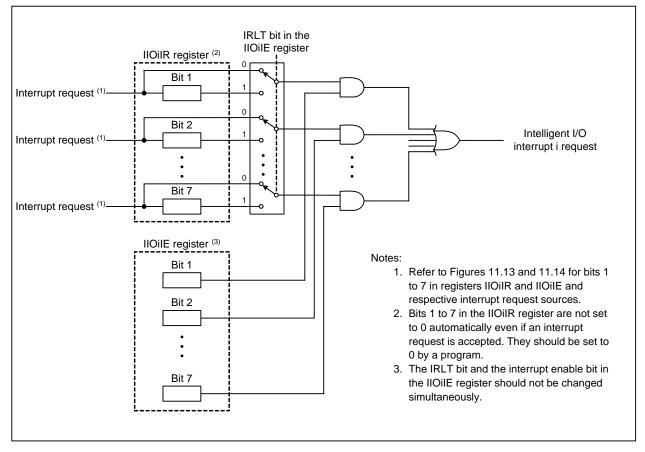

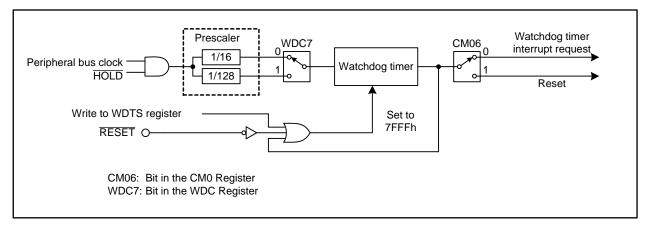

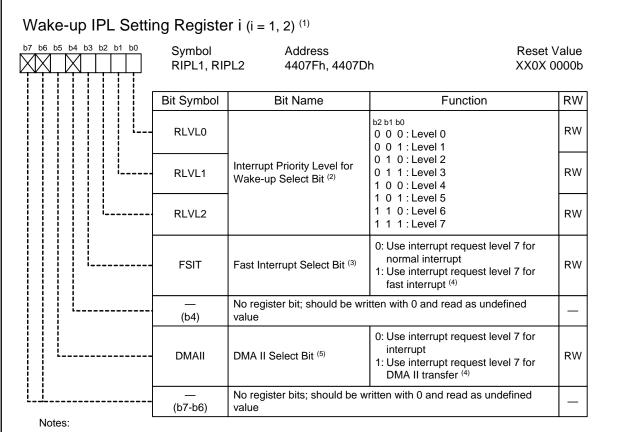

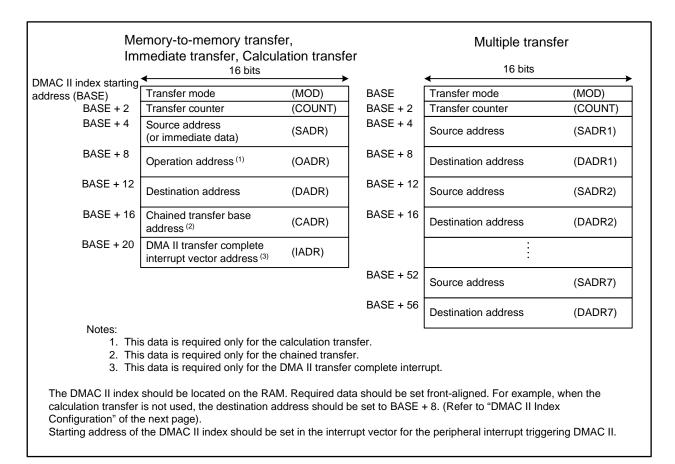

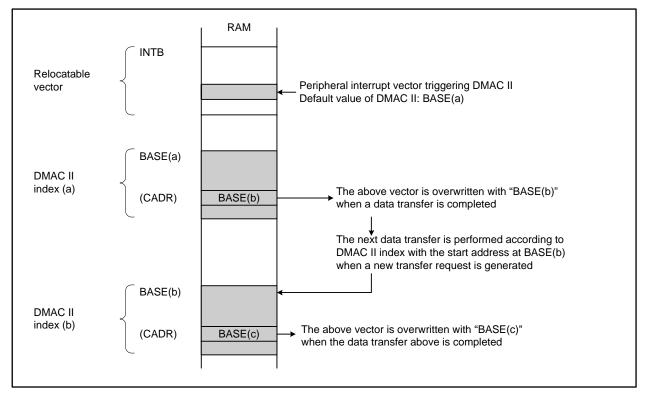

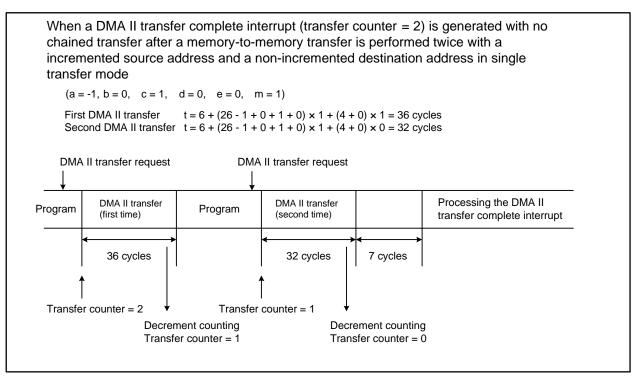

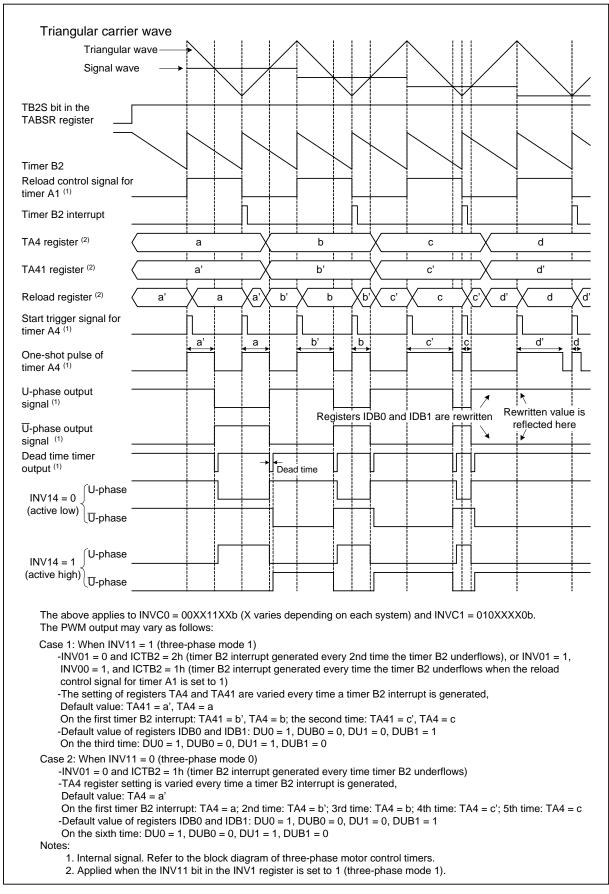

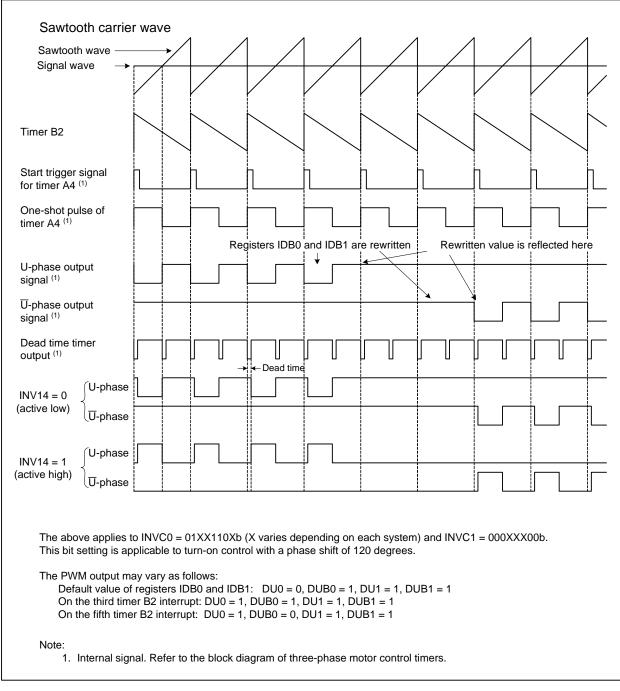

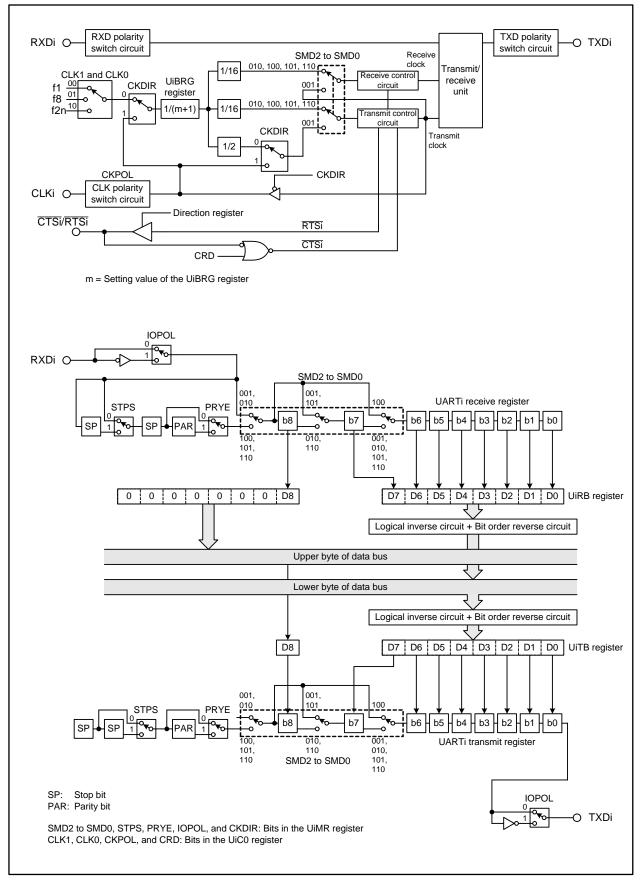

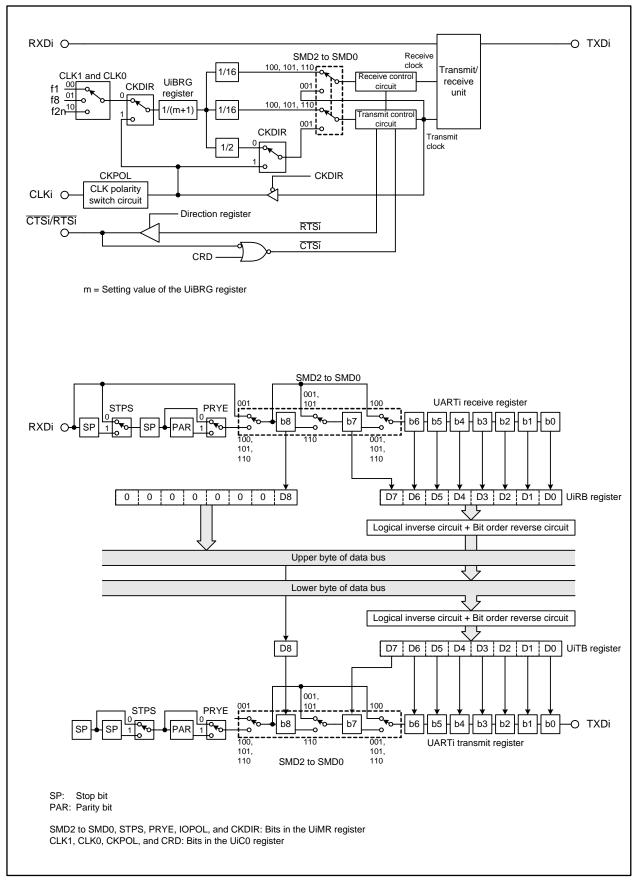

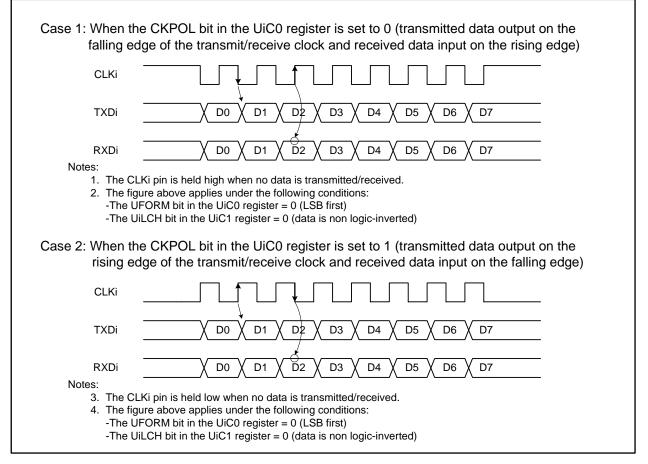

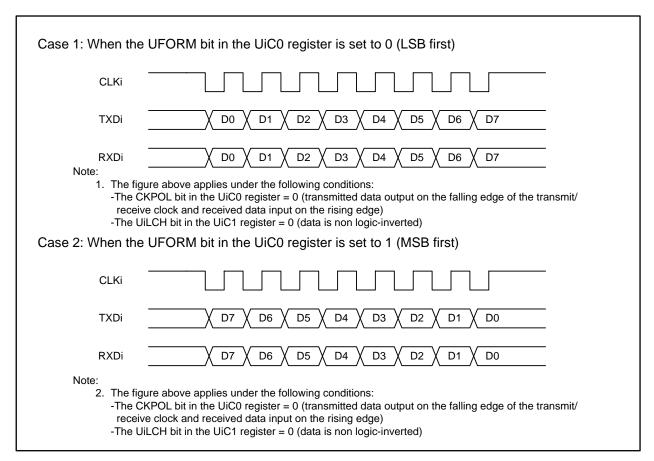

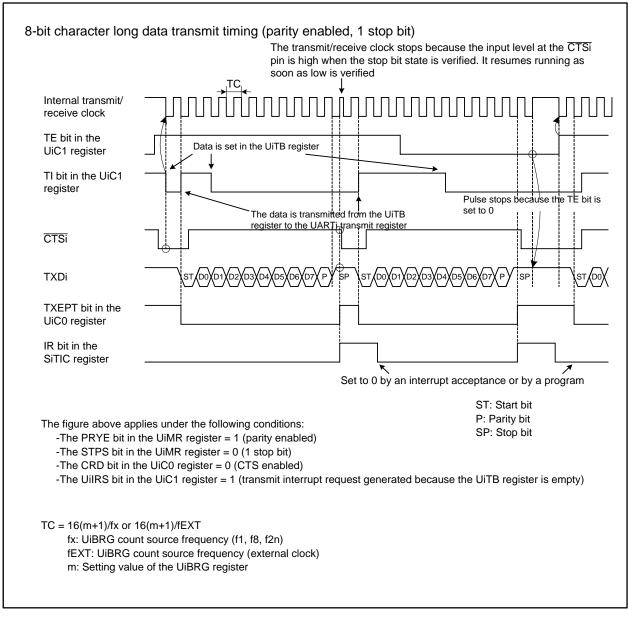

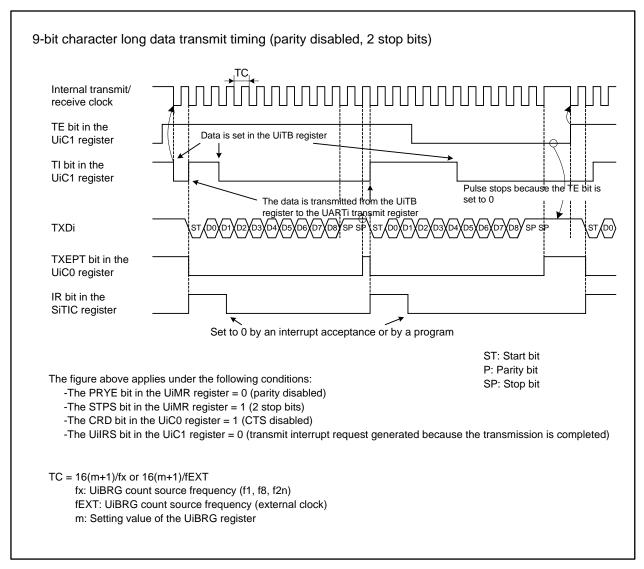

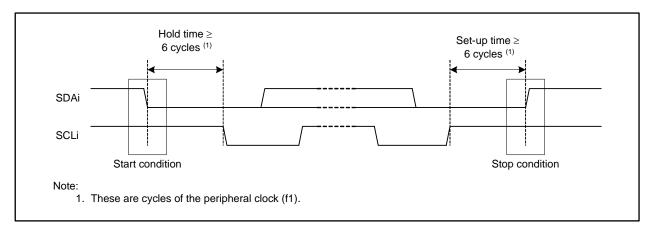

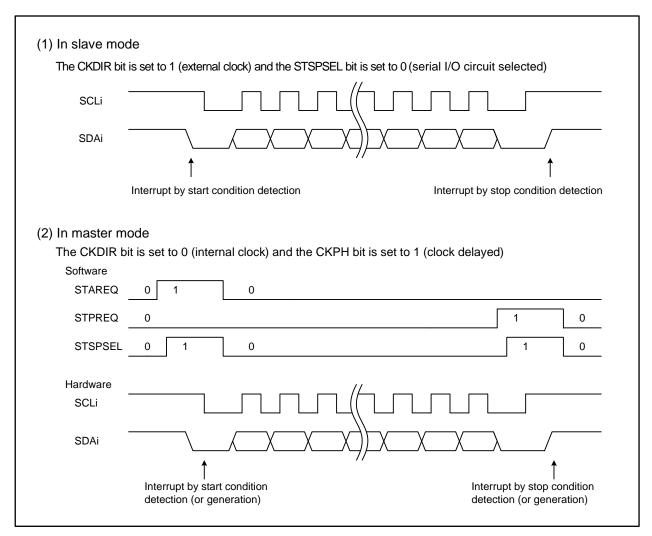

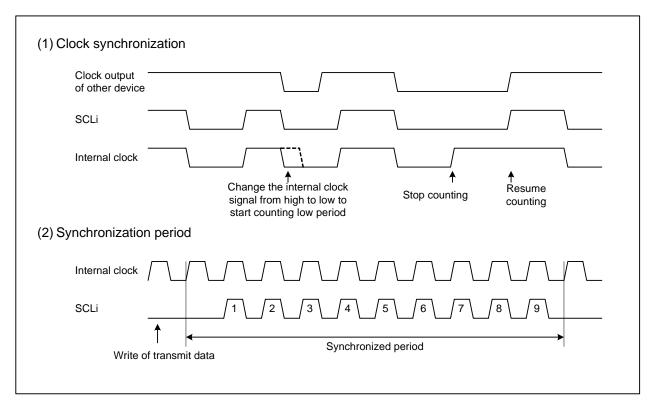

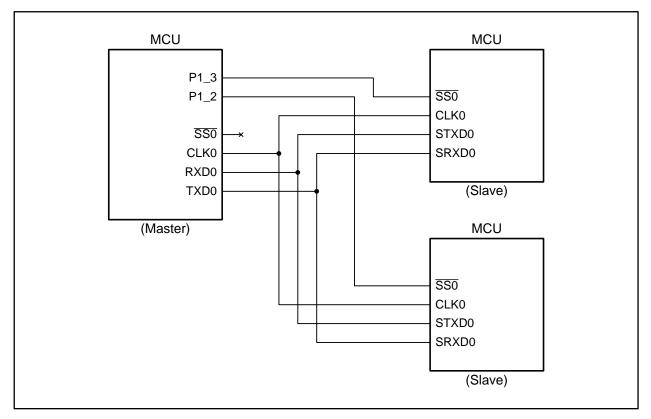

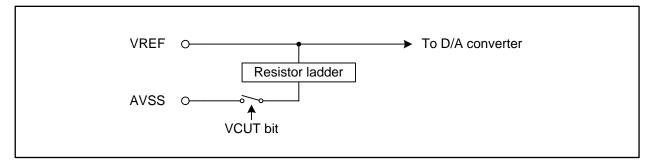

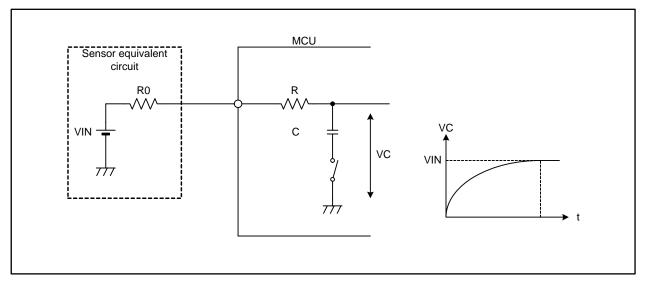

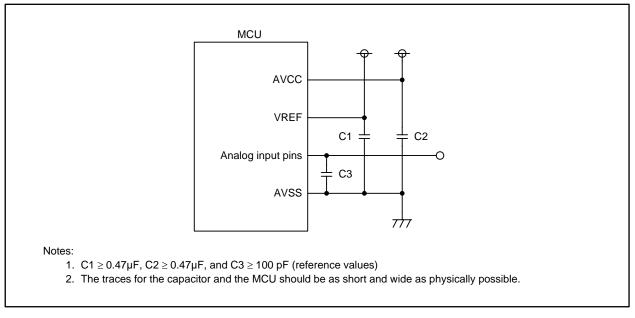

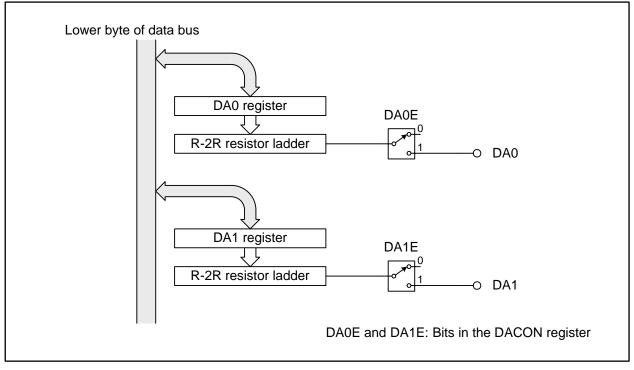

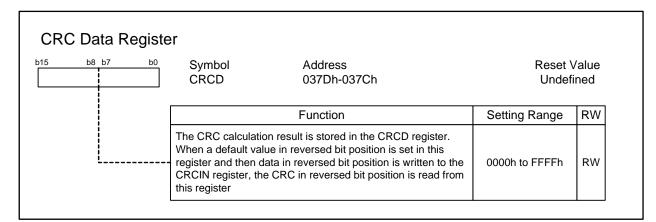

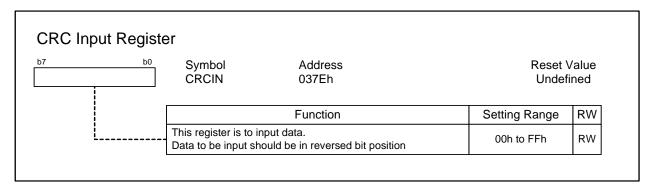

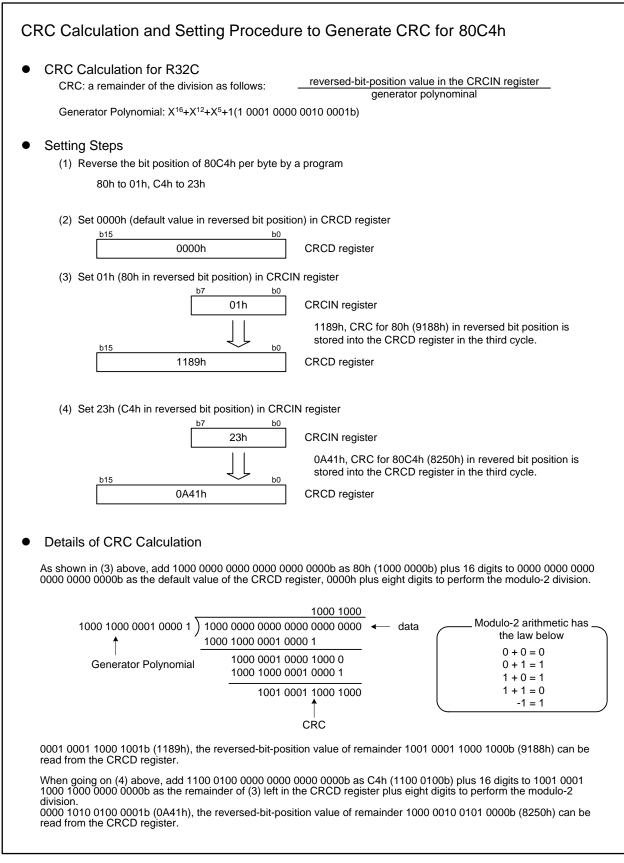

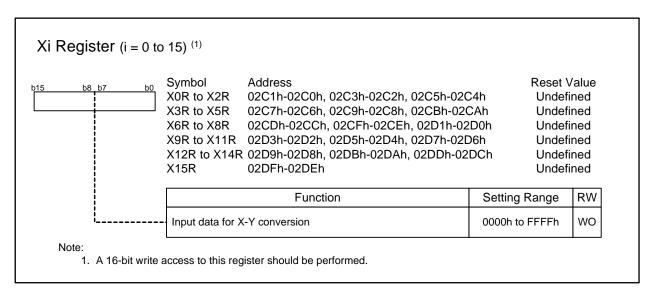

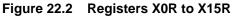

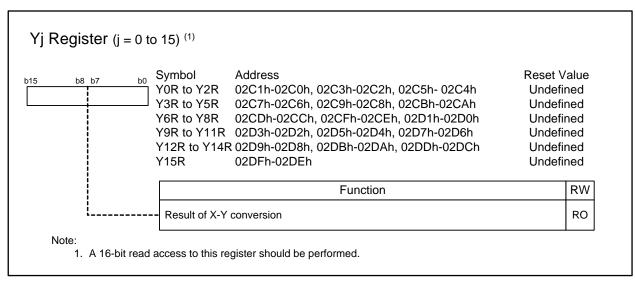

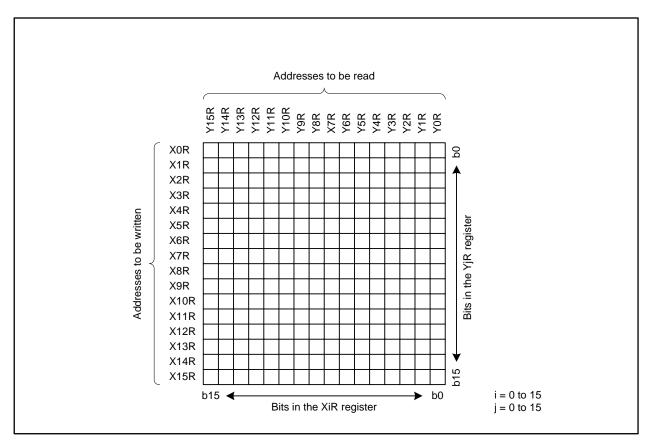

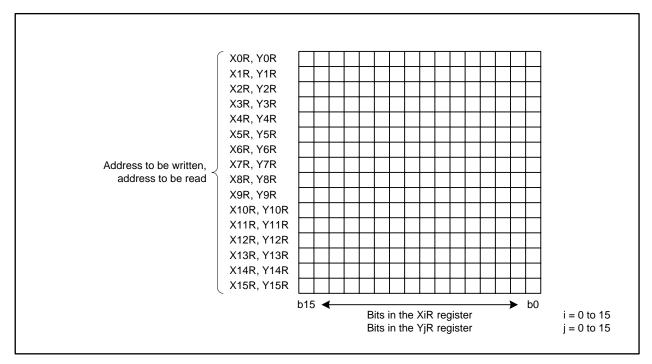

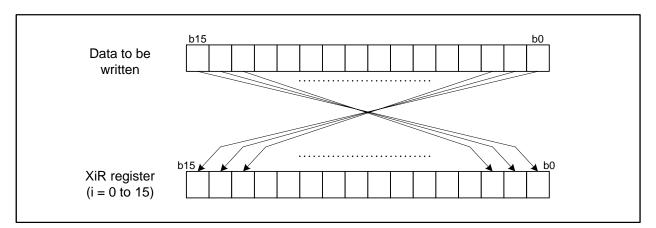

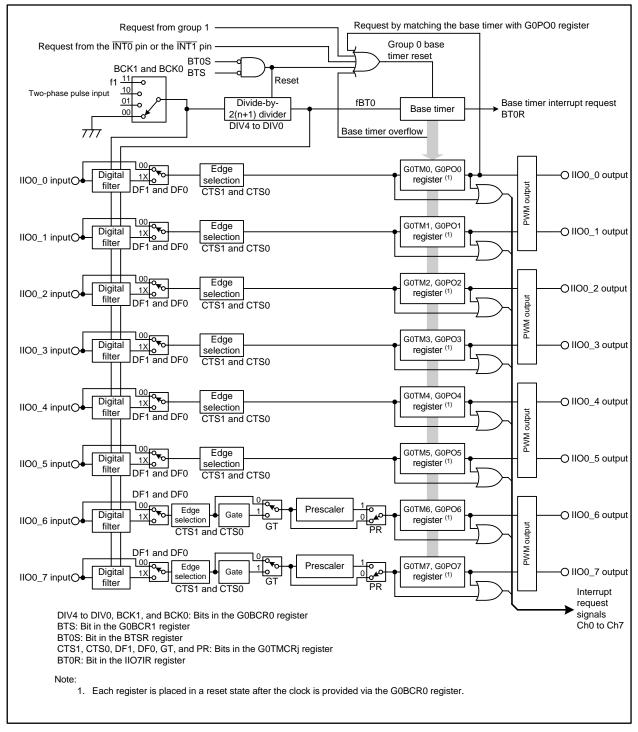

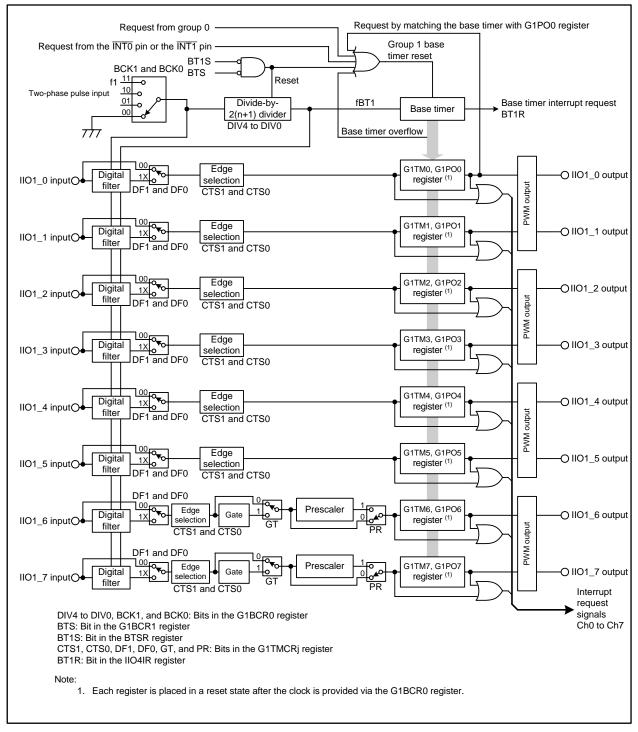

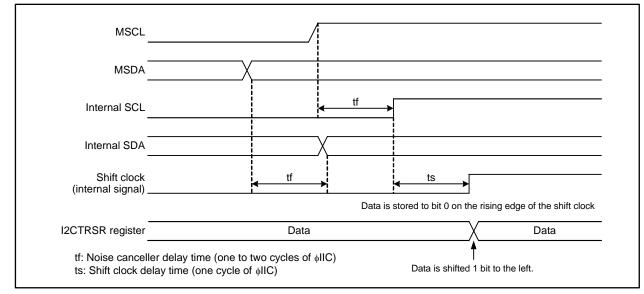

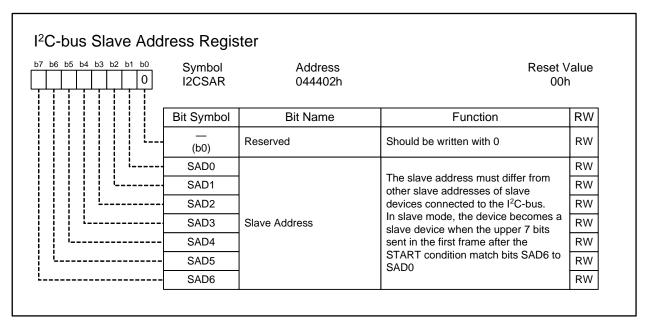

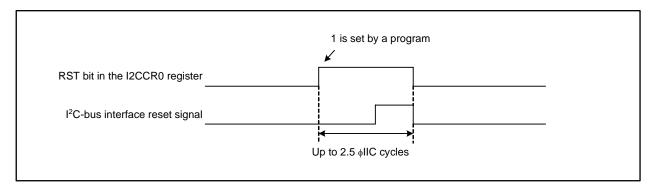

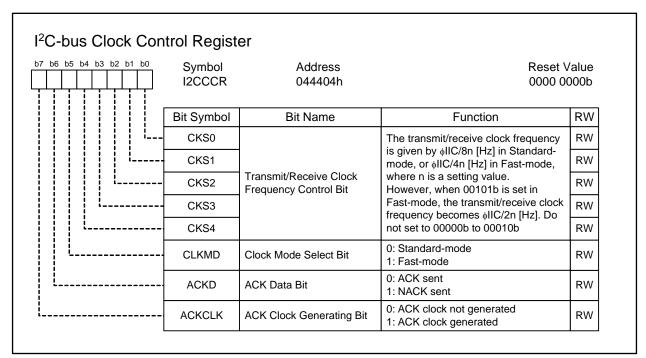

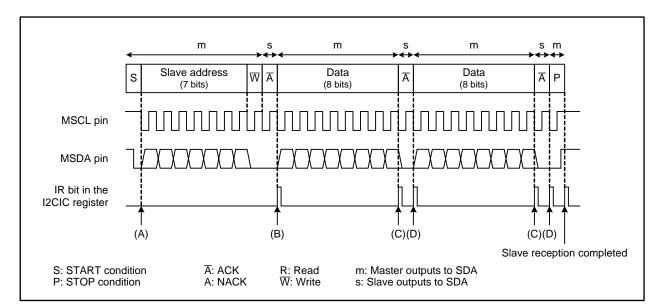

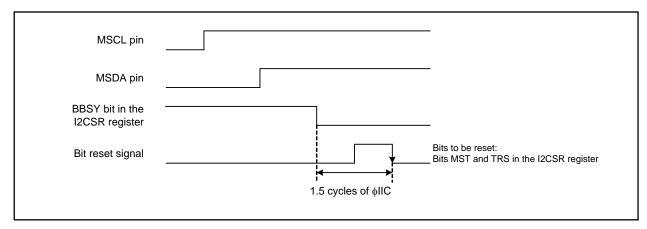

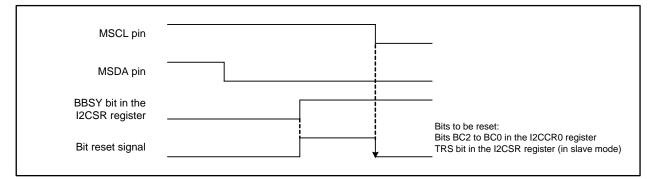

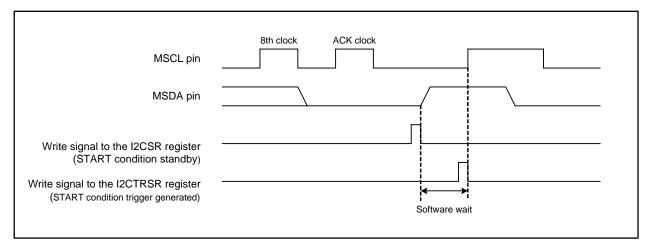

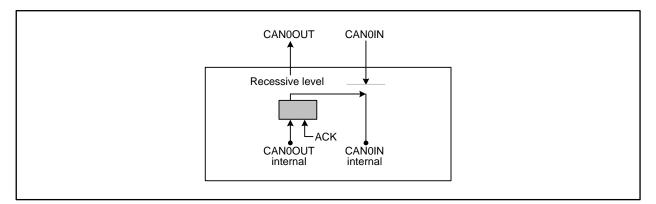

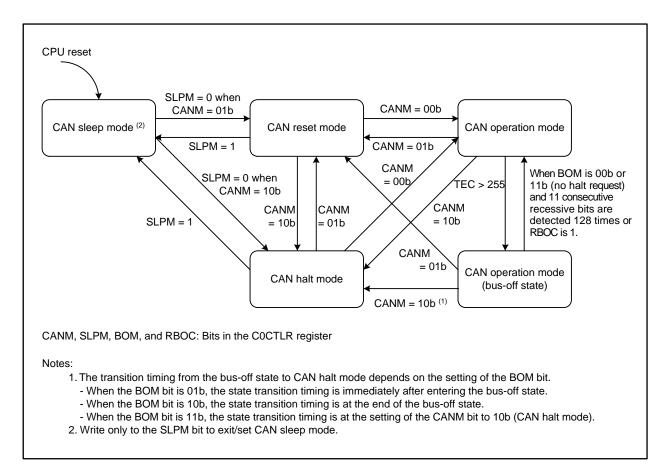

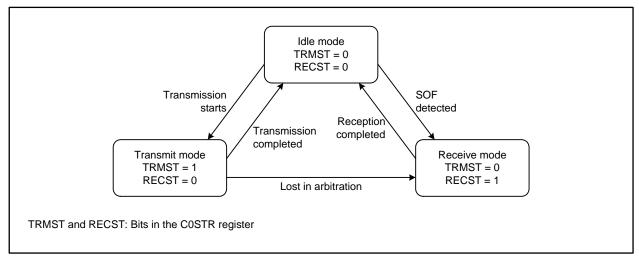

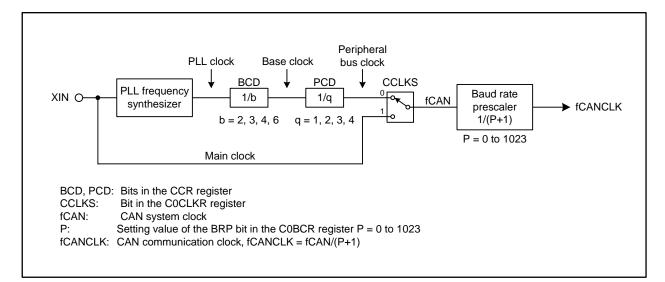

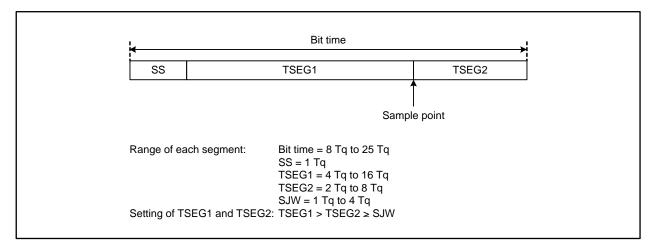

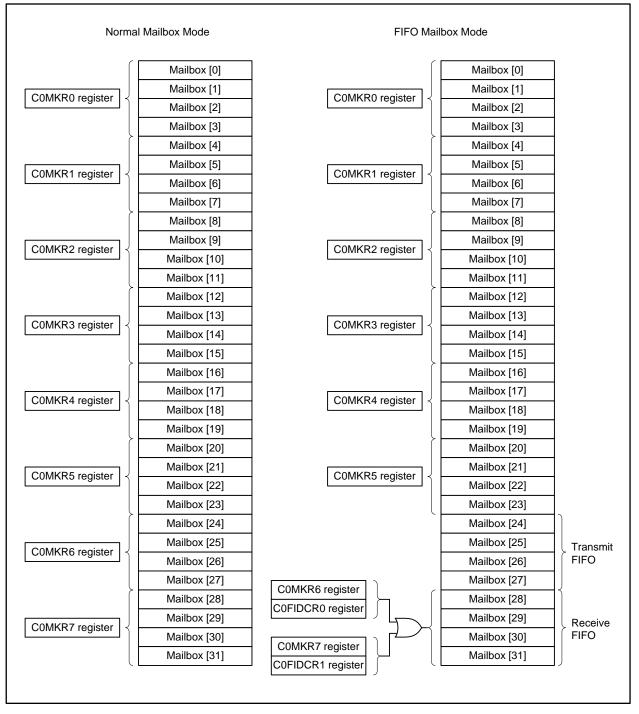

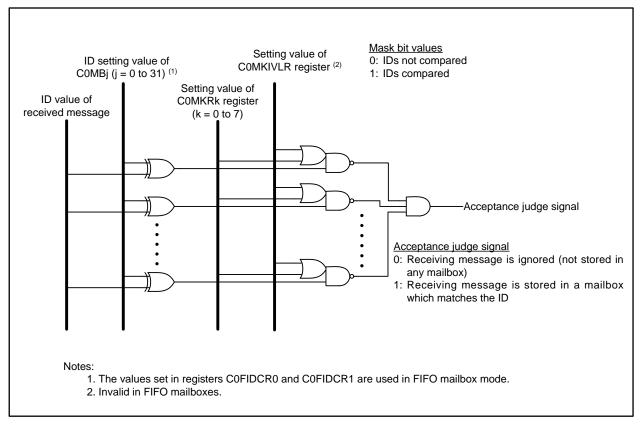

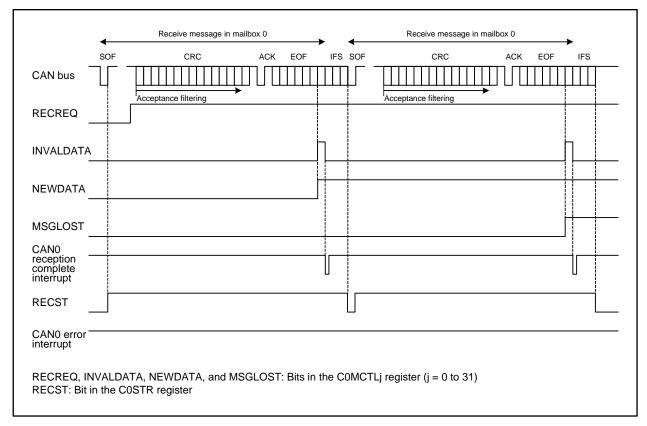

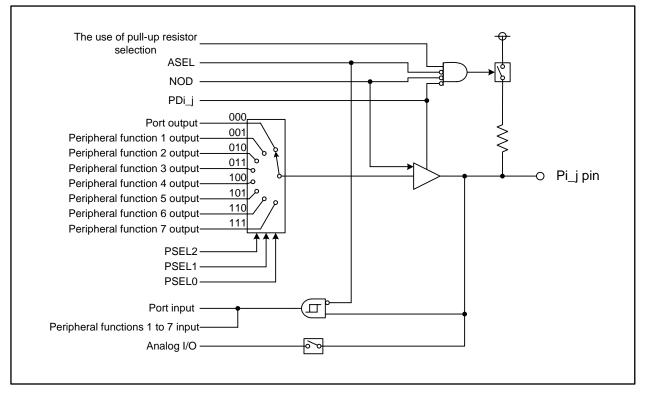

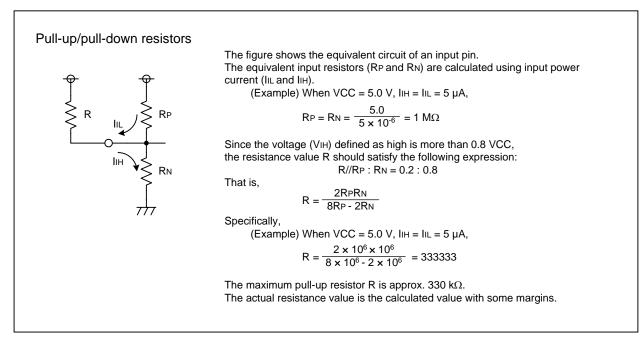

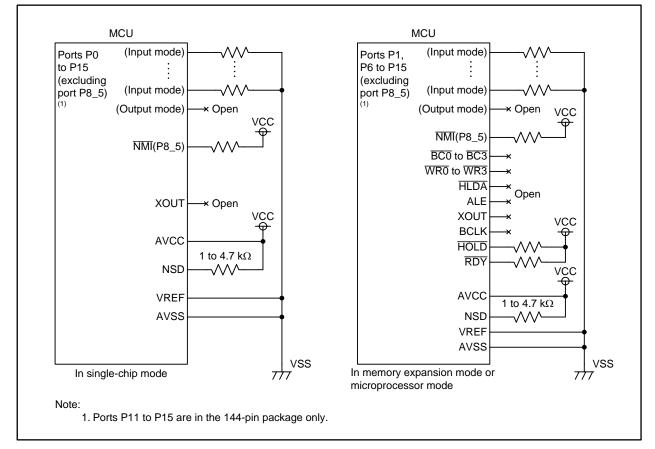

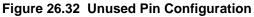

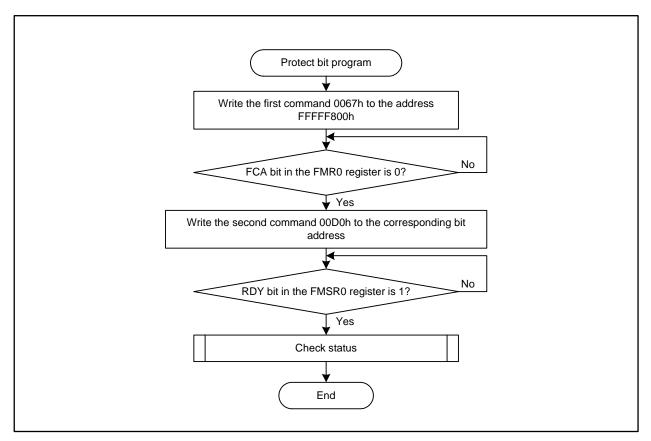

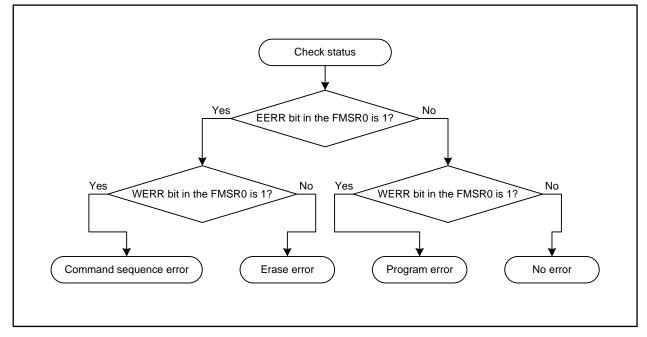

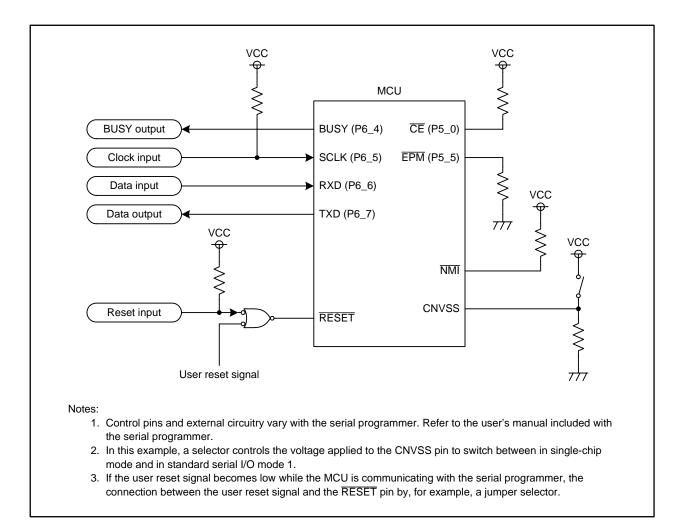

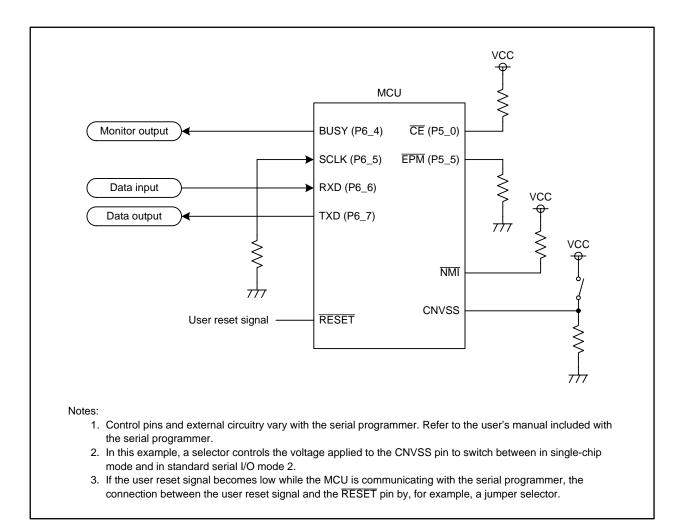

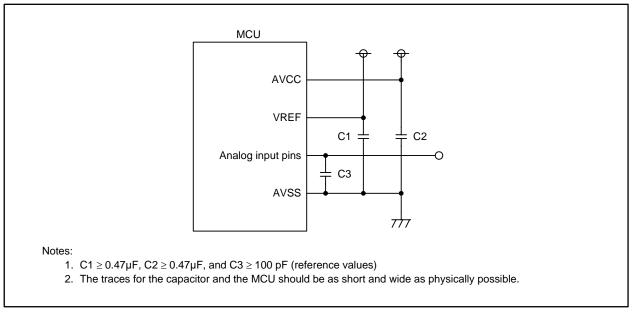

| Intelligent I/O             |                                       | Time measurement (input capture): 16 bits $\times$ 16<br>Waveform generation (output compare): 16 bits $\times$ 19<br>Serial interface: Variable-length synchronous serial I/O mode, IEBus<br>mode (optional <sup>(1)</sup> )       |  |  |  |