# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

# R8A66597FP/DFP/BG

ASSP (USB2.0 2 Port Host/1 Port Peripheral Controller)

REJ03F0229-0101 Rev1.01 Oct 17, 2008

# **1 Overview**

# 1.1 Overview

The R8A66597 is a Universal Serial Bus (USB) Controller equipped with USB Host functions and Peripheral functions applicable for On-The-Go. When selecting the Host Controller function, it has two USB ports available for Hi-Speed, Full-Speed, and Low-Speed transfer compliant with USB Specification Revision 2.0. When selecting the Peripheral Controller function, it has one USB port available for Hi-Speed and Full-Speed transfer compliant with USB Specification Revision 2.0.

This controller has a built-in USB transceiver and is compatible with all the transfer types defined in USB Specification Revision 2.0.

The internal buffer memory is 8.5K, and a maximum ten pipes can be used for transferring data. For Pipe1 to Pipe9, any endpoint address can be assigned matching the peripheral functions for communication or user system. Separate bus or multiplex bus can be selected for the CPU connection. A split bus interface (exclusively for the DMA interface) that is different from the CPU bus interface is provided and is suitable for systems demanding high-performance data transfer.

# 1.2 Features

# 1.2.1 Built-in Host Controller and Peripheral Controller compatible with Hi-Speed USB

- Built-in USB Host Controller and Peripheral Controller

- Toggle between USB Host functions and Peripheral functions is possible according to what is written to the register

- Built-in USB transceiver

# 1.2.2 Low power consumption

- 1.5V core power consumes less power when operating

- With the installed Low Power Sleep Mode functions, less power is consumed when the USB is not in use, which is also applicable for portable devices

- Standby power consumption can be greatly reduced by keeping only the VIF power source ON when not using the USB function.

- Operational with a 3.3V single power supply using the internal 1.5V core power regulator

# 1.2.3 Space-saving package

- Few external devices and space-saving package

- VBUS signal can be connected directly to the controller input pin

- Built-in D+ pull-up resistor (for Peripheral function)

- Built-in D+ and D- pull-down resistors (for Host function)

- · Built-in D+ and D- terminating resistors (for Hi-Speed operations)

- Built-in D+ and D- output resistors (for Full-Speed and Low-Speed operations)

# 1.2.4 Compatible with all USB transfer types

- Compatible with all USB transfer types, including isochronous transfer

- Control transfer

- Bulk transfer

- · Interrupt transfer (not compatible with high-bandwidth)

- Isochronous transfer (not compatible with high-bandwidth)

#### 1.2.5 Bus interface

- 16-bit CPU bus interface

- Compatible with 16-bit separate bus/16-bit multiplex bus

- Compatible with DMA transfer in 8-bit/16-bit access (slave function)

- 8-bit split bus (exclusive for external direct memory access controller (DMAC)) interface

- Built-in two DMA interface channels

- DMA transfer provides 40MB/second high-performance data transfer

#### 1.2.6 Pipe configuration

- Built-in 8.5KB buffer memory for USB communication

- Maximum of ten pipes can be selected (including default control pipe)

- Programmable pipe configuration

- Any endpoint address can be assigned to Pipe1 to Pipe9

- Transfer conditions that can be written for each pipe

- Pipe0: Control transfer, single buffer fixed at 256 bytes

- Pipe1~Pipe2: Bulk transfer/Isochronous transfer, continuous transfer modes.

- programmable buffer size (specifiable up to 2K bytes per side, double buffer also specifiable) • Pipe3~Pipe5: Bulk transfer, continuous transfer modes,

- programmable buffer size (specifiable up to 2K bytes per side, double buffer also specifiable)

- Pipe6~Pipe9: Interrupt transfer, single buffer fixed at 64 bytes

## 1.2.7 Features when selecting Host functions

- Compatible with Hi-Speed (480Mbps), Full-Speed (12Mbps) and Low-Speed transfer (1.5Mbps)

- Several Peripheral devices can be connected through one tier hub

- Reset handshake auto response

- SOF and packet transmission schedule automation

- Transfer interval setup function for Isochronous and Interrupt transfer

#### 1.2.8 Features when selecting Peripheral functions

- Compatible with Hi-Speed (480Mbps) and Full-Speed transfer (12Mbps)

- Auto identification of Hi-Speed or Full-Speed operations according to reset handshake auto response

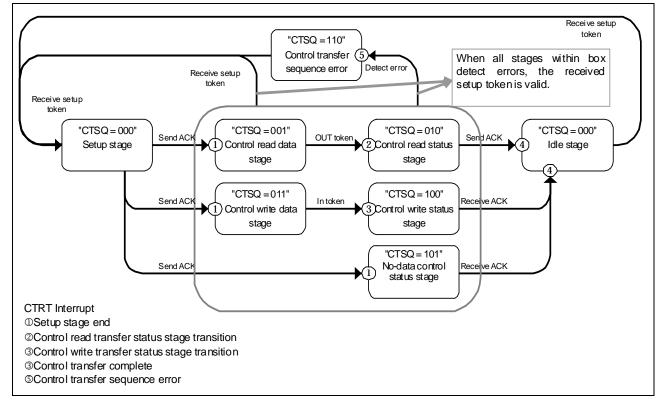

- Control transfer stage management function

- Device state management function

- Auto response function related to SET\_ADDRESS request

- NAK response interrupt function (NRDY)

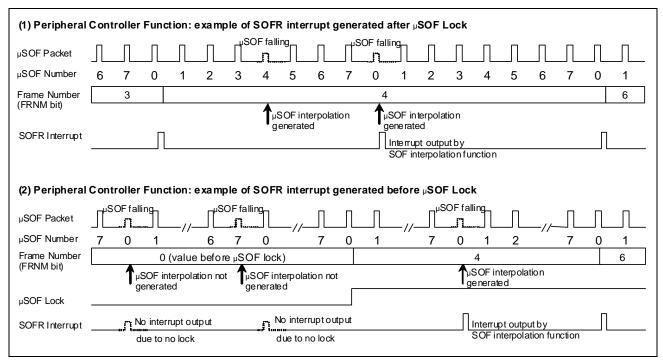

- SOF interpolation function

# 1.2.9 Functions that Provide On-The-Go Support

- Built-in ID pin and ID pin monitor bit enables determination of A-Device/B-Device at start-up

- Built-in control bit facilitates Host Negotiation Protocol

#### 1.2.10 Other functions

- Compatible with the CPU of big-endian or little-endian according to the byte-endian swap function

- Transfer end function according to transaction count

- End function of DMA transfer by external trigger (DEND pin)

- SOF plus output function

- Three types of input clock can be selected by built-in PLL

- Select from 48MHz/24MHz/12MHz

- Function to modify the BRDY interrupt event notification timing (BFRE)

- Function to clear the auto buffer memory after the pipe data specified in the DxFIFO port is read (DCLRM)

- Function to provide the auto clock from clock stop status

- NAK setting function (SHTNAK) for PID response corresponding to transfer end

RENESAS

# 1.2.11 Usage

Navigation systems, DVD recorders, set-top boxes, audio devices, printers, external storage devices and other devices equipped with USB

# 1.3 Package

# 1.3.1 Pin Layout

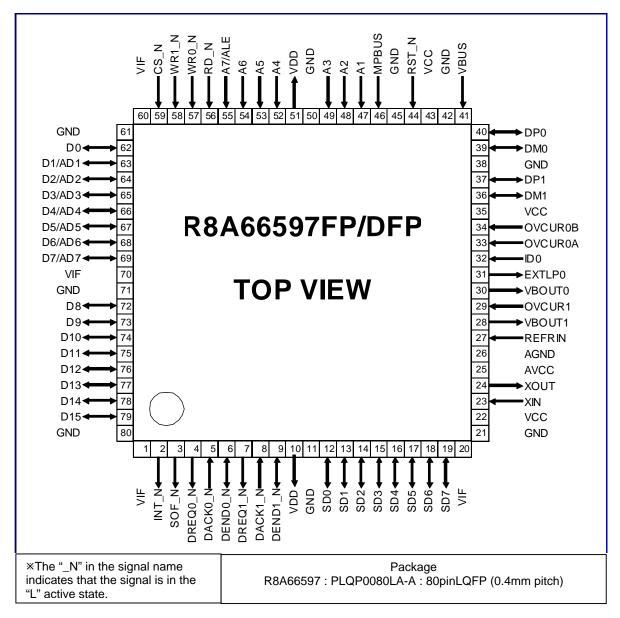

Figure 1.1 shows the pin layout (top view) for this controller.

Figure 1.1 R8A66597FP/DFP Pin Layout

|   | R8A66597BG<br>(TOP VIEW) |         |         |        |        |         |         |       |      |   |  |  |  |  |

|---|--------------------------|---------|---------|--------|--------|---------|---------|-------|------|---|--|--|--|--|

|   | 1                        | 2       | 3       | 4      | 5      | 6       | 7       | 8     | 9    | Т |  |  |  |  |

| A | GND                      | D15     | D14     | D10    | GND    | D5/AD5  | D2/AD2  | D0    | GND  | A |  |  |  |  |

| В | VIF                      | INT_N   | D13     | D11    | VIF    | D4/AD4  | D1/AD1  | CS_N  | VIF  | в |  |  |  |  |

| с | DREQ0_N                  | DACK0_N | SOF_N   | D9     | D7/AD7 | D3/AD3  | WR1_N   | WR0_N | RD_N | с |  |  |  |  |

| D | DREQ1_N                  | DACK1_N | DEND0_N | D12    | D8     | D6/AD6  | A6      | A4    | A5   | D |  |  |  |  |

| E | GND                      | VDD     | DEND1_N | SD0    | GND    | A7/ALE  | AЗ      | VDD   | GND  | E |  |  |  |  |

| F | SD2                      | SD3     | SD4     | SD1    | VBOUT0 | A2      | GND     | MPBUS | A1   | F |  |  |  |  |

| G | SD5                      | SD6     | AVCC    | VBOUT1 | OVCUR1 | EXTLP0  | ID0     | RST_N | VCC  | G |  |  |  |  |

| н | VIF                      | SD7     | XIN     | AGND   | VCC    | OVCUR0B | OVCUR0A | GND   | VBUS | н |  |  |  |  |

| J | GND                      | VCC     | XOUT    | REFRIN | DM1    | DP1     | GND     | D M0  | DP0  | J |  |  |  |  |

|   | 1                        | 2       | 3       | 4      | 5      | 6       | 7       | 8     | 9    | - |  |  |  |  |

| ∗The "_N" in the signal     | Package                                              |

|-----------------------------|------------------------------------------------------|

| name indicates that the     | R8A66597BG : PLBG0081KA-A : 81pinLFBGA (0.5mm pitch) |

| signal is in the "L" active |                                                      |

# Figure 1.2 R8A66597BG Pin Layout

# 1.4 Pin Description

Pin descriptions are given in Table 1.1, and the processing method of unused pins is given in Table 1.2.

| u                        |                      |                            |     |                                                                                                                                                                                                                                 |                   | Pin Sta         | atus *5)                   |

|--------------------------|----------------------|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------------------|

| Classification           | Pin Name             | Name                       | I/O | Function                                                                                                                                                                                                                        | Number<br>of Pins | Being<br>Reset  | Immediately<br>After Reset |

|                          | D15-0                | Data bus                   | I/O | This is a 16-bit data bus.                                                                                                                                                                                                      |                   |                 |                            |

|                          | AD7-1                | Multiplex<br>address bus   | I/O | When selecting to the multiplex bus, these pins are used in the time division as a part of the data bus (D7-D1) or address bus (A7-A1).                                                                                         | 16                | *2)             | *2)                        |

|                          | A7-1                 | Address bus                | IN  | This is the address bus.<br>A0 does not exist for the 16-bit data bus.                                                                                                                                                          | 7                 | Input_<br>*3)   | Input_<br>*3)              |

|                          | ALE                  | Address latch<br>enabled   | IN  | While selecting to the multiplex bus, the A7 pin is used as an ALE signal.                                                                                                                                                      | 7                 | Input           | Input                      |

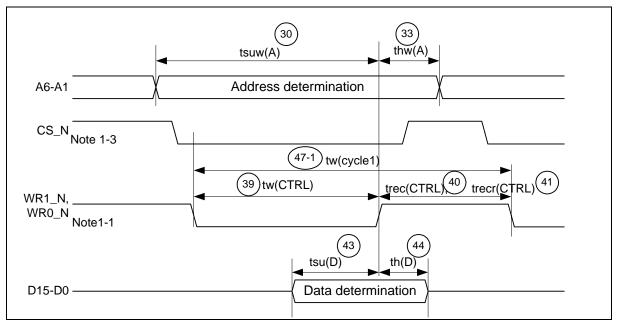

| CPU bus                  | CS_N                 | Chip select                | IN  | The controller is selected in "L" level.                                                                                                                                                                                        | 1                 | Input_<br>*4)   | Input_<br>*4)              |

| interface                | RD_N                 | Read strobe                | IN  | Reads the data from the register of this controller in "L" level.                                                                                                                                                               | 1                 | Input           | Input                      |

|                          | WR0_N                | D7-0 Byte write<br>strobe  | IN  | Writes D7-D0 in the register of this controller at the rising edge.                                                                                                                                                             | 1                 | Input_<br>*4)   | Input_<br>*4)              |

|                          | WR1_N                | D15-8 byte write strobe    | IN  | Writes D15-D8 in the register of this controller at the rising edge.                                                                                                                                                            | 1                 | Input_<br>*4)   | Input_<br>*4)              |

|                          | MPBUS                | Bus mode selection         | IN  | This is a separate bus in "L" level. This is a multiplex bus in "H" Level. Fix either "H" or "L" level.                                                                                                                         | 1                 | Input<br>*1)    | Input<br>*1)               |

| SPLIT bus<br>interface   | SD7-0                | Split data bus             | I/O | When the split bus is selected, it functions as the split data bus.                                                                                                                                                             | 8                 | Input<br>(Hi-Z) | Input<br>(Hi-Z)            |

| [                        | DREQ0_N<br>DREQ1_N   | DMA request                | OUT | Notifies the DMA transfer request of D0FIFO port and D1FIFO port.                                                                                                                                                               | 2                 | H               | Η                          |

| DMA bus                  | DACK0_N<br>DACK1_N   | DMA<br>acknowledgeme<br>nt | IN  | Enter the DMA acknowledgement signal of<br>D0FIFO port and D1FIFO port.                                                                                                                                                         | 2                 | Input           | Input                      |

| interface                | DEND0_N<br>DEND1_N   | DMA transfer<br>end        | I/O | For FIFO port access write direction: Receives<br>transmission completion signal as an input<br>signal from other chips or CPU.<br>For FIFO port access read direction: Shows<br>the last transmitted data as an output signal. | 2                 | Input<br>(Hi-Z) | Input<br>(Hi-Z)            |

| Interrupt/<br>SOF output | INT_N                | Interrupt                  | OUT | Notifies various types of interrupts related to<br>USB communication by "L" active. Active is by<br>default "L" active, however it can be changed<br>to "H" active by modifying the setup value of<br>INTA bit in the software. | 1                 | Н               | Н                          |

|                          | SOF_N                | SOF pluse<br>output        | OUT | For Host function:<br>When the controller issues an SOF, outputs an<br>SOF pulse by "L" active.<br>For Peripheral function:<br>When an SOF is detected, outputs an SOF<br>pulse by "L" active.                                  | 1                 | Н               | Н                          |

| Clock                    | XIN                  | Input for<br>oscillation   | IN  | Connect crystal oscillator between XIN and XOUT. Connect external clock signal to XIN in                                                                                                                                        | 1                 |                 |                            |

| CIUCK                    | XOUT                 | Output for<br>oscillation  | OUT | order to input external clock, and leave open XOUT.                                                                                                                                                                             | 1                 |                 |                            |

| System<br>control        | USB bus<br>interface | Reset signal               | IN  | Resets this controller at "L" level.                                                                                                                                                                                            | 1                 | Input<br>(L)    | Input<br>(H)               |

# Table 1.1 Pin Description

|                                    |                    |                                                              |     |                                                                                                                                                                                                                                                                                                                                                        |                   | Pin Sta         | tatus *5)                  |  |

|------------------------------------|--------------------|--------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------------------|--|

| Classification                     | Pin Name           | Name                                                         | I/O | Function                                                                                                                                                                                                                                                                                                                                               | Number<br>of Pins | Being<br>Reset  | Immediately<br>After Reset |  |

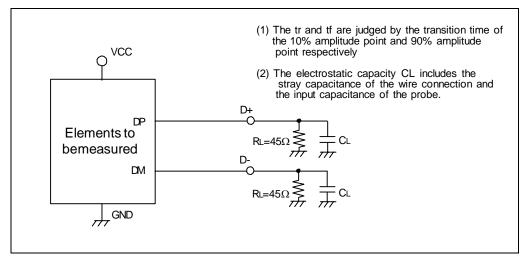

| USB bus                            | DP0<br>DP1         | USB D+ data                                                  | I/O | Connect to D+ pin of USB bus.                                                                                                                                                                                                                                                                                                                          | 2                 | Input<br>(Hi-Z) | Input<br>(Hi-Z)            |  |

| interface                          | DM0<br>DM1         | USB D-data                                                   | I/O | Connect to D- pin of USB bus.                                                                                                                                                                                                                                                                                                                          | 2                 | Input<br>(Hi-Z) | Input<br>(Hi-Z)            |  |

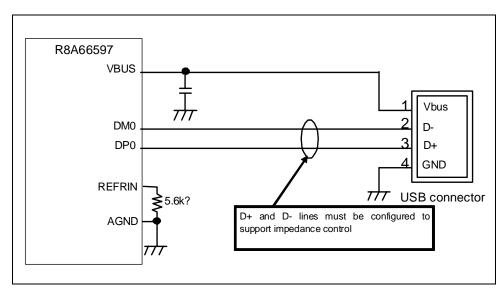

| VBUS<br>monitoring<br>input        | VBUS               | VBUS input                                                   | IN  | When Host Controller function is selected:<br>leave open or connect directly to Vbus of USB<br>bus.<br>*This pin cannot supply Vbus to the connected<br>device.<br>When Peripheral Controller function is<br>selected: Connect directly to Vbus of USB bus.<br>Can detect Vbus connection/disconnection.<br>Connect to 5V when not connecting to Vbus. | 1                 | Input<br>(Hi-Z) | Input<br>(Hi-Z)            |  |

| Reference resistance               | REFRIN             | Reference input                                              | IN  | Connect to analog GND pin through $5.6k\Omega \pm 1\%$ resistor.                                                                                                                                                                                                                                                                                       | 1                 |                 |                            |  |

| On-The-Go<br>related               | ID0                | ID input                                                     | IN  | When using USB Mini-AB receptacle, connect to ID pin.                                                                                                                                                                                                                                                                                                  | 1                 | Input           | Input                      |  |

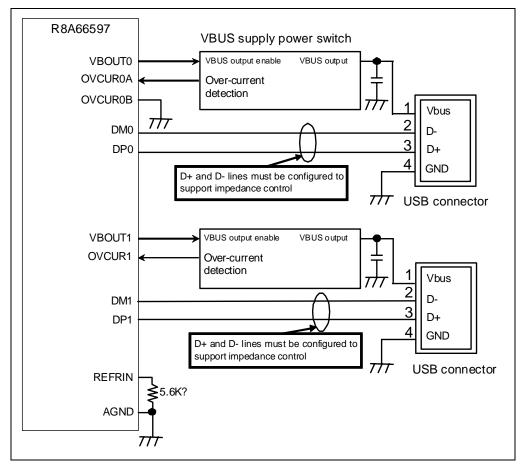

|                                    | VBOUT0<br>VBOUT1   | External power<br>on                                         | OUT | Used for ON/OFF output to external power<br>circuit. Connect to external power circuit for<br>Vbus supply.<br>VBOUT1 pin cannot be used when using<br>DP0/DM0 as OTG.                                                                                                                                                                                  | 2                 | L               | L                          |  |

| Power<br>manageme<br>nt related if | OVCUR0A<br>OVCUR0B | Overcurrent input for Port0                                  | IN  | Used for input of over-current detection from<br>external power circuit. Connect to PORT0<br>external power circuit.<br>When input for over-current detection from<br>external power circuit is one pin, connect to<br>OVCUR0A and fix OVCUR0B to High or Low.                                                                                         | 2                 | Input           | Input                      |  |

| USB Host                           | OVCUR1             | Overcurrent input for Port1                                  | IN  | Used for input of over-current detection from<br>external power circuit. Connect to PORT1<br>external power circuit.<br>OVCUR1 pin cannot be used when using<br>DP0/DM0 as OTG.                                                                                                                                                                        | 1                 | Input           | Input                      |  |

|                                    | EXTLP0             | Control of<br>external power<br>for low power<br>consumption | ουτ | has low-consumption mode. Connect to PORT0 external power circuit.                                                                                                                                                                                                                                                                                     | 1                 | L               | L                          |  |

|                                    | AVCC               | Analog power                                                 | -   | Connect to 3.3V.                                                                                                                                                                                                                                                                                                                                       | 1                 |                 |                            |  |

|                                    | AGND<br>VCC        | Analog GND<br>Power                                          | -   | Connect to 3.3V.                                                                                                                                                                                                                                                                                                                                       | 1<br>3            |                 |                            |  |

| Power                              | GND                | GND                                                          | -   |                                                                                                                                                                                                                                                                                                                                                        | 9 (FP)<br>10(BG)  |                 |                            |  |

| /GND                               | VIF                | IO power                                                     | -   | Connect to 3.3V or 1.8V.                                                                                                                                                                                                                                                                                                                               | 4                 |                 |                            |  |

|                                    | VDD                | Core power                                                   | ουτ | Output 1.5V with internal regulator –generated.                                                                                                                                                                                                                                                                                                        | 2                 |                 |                            |  |

\*1) The input level of MPBUS pin must be fixed. Do not switch the level during controller operations.

\*2) Pin is for OUTPUT when  $\dot{CS} N = "L"$  and RD N="L", otherwise INPUT.

\*3) Hi-Z input (open) is enabled when MPBUS = "H".

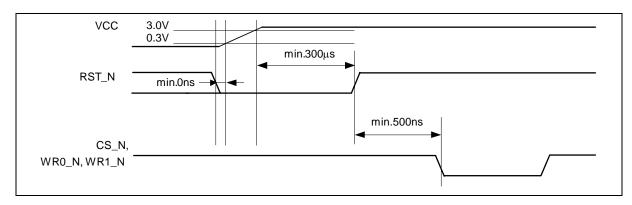

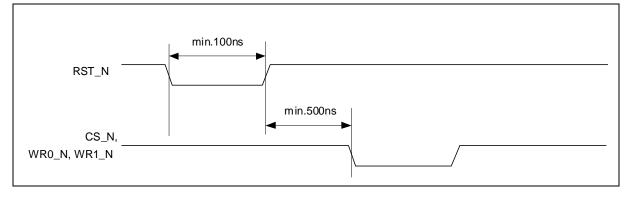

\*4) Maintain status (a) or (b) as described below during reset and immediately after reset release for CS\_N, WR0\_N and WR1\_N signals.

(a) CS\_N = "H"

(b)  $WR0 N = "H" and <math>WR1_N = "H"$

**\*5)** Explanations for "Pin Status" column

(a) input: input port, Hi-Z status (open) disabled

- (b) Input (Hi-Z): input port, Hi-Z status (open) enabled

- (c) H, L, H/L: indicates output port status

| Classification      | Pin Name          | Process Contents                |

|---------------------|-------------------|---------------------------------|

| Split Bus Interface | SD7-0             | Open                            |

|                     |                   | Open                            |

| DMA Bus Interface   | DACK0_N, DACK1_N  | Fixed to VIF "H" level *1)      |

|                     | DEND0_N, DEND1_N  | Open *2)                        |

| SOF Ouptput         | SOF_N             | Open                            |

|                     |                   | When using Host Function:       |

|                     |                   | open                            |

| VBUS Monitor Input  | VBUS              | When using Peripheral function: |

|                     |                   | Connect to VBUS signal on USB   |

|                     |                   | connector                       |

|                     | ID0               | Fixed to "L"                    |

| USB Host:           | VBOUT0, VBOUT1    | Open                            |

| Power Supply        | OVCUR0A, OVCUR0B, | Fixed to "L"                    |

| Management related  | OVCUR1            |                                 |

|                     | EXTLP0            | Open                            |

## Table 1.2 Example of Unused R8A66597 Pin

\*1) When not using DACKn\_N pin, set DMAnCFG register DFROM bit to "000" and DACKA bit to "0" (n=0, 1)

\*2) When not using DENDn\_N pin, set DMAnCFG register DENDE bit to "0" (n=0, 1)

# 1.5 Structure of Pin Functions

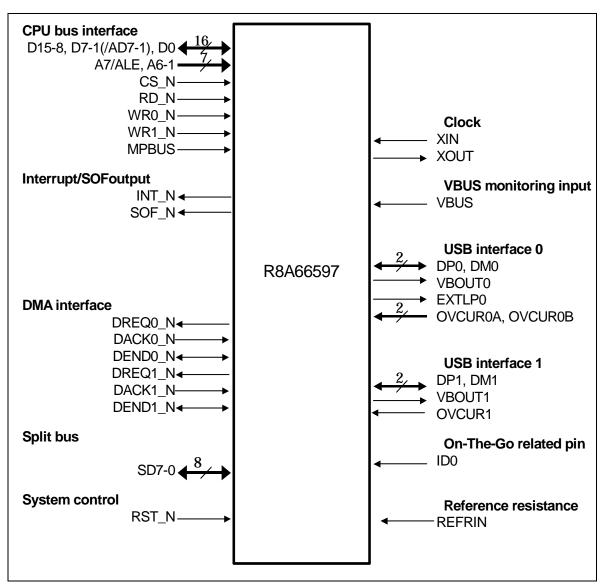

Block diagram of the controller pin functions is shown in Figure 1.3.

Figure 1.3 Block Diagram of Pin Functions

# **1.6 Functional Overview**

#### 1.6.1 Selection of controller functions

The controller can toggle between Host functions and Peripheral functions according to what is written to the register. The hardware can automatically identify the USB transmission speed, irrespective of whether the Host or Peripheral function is selected.

## 1.6.2 Bus interface

The controller is compatible with the bus interfaces given below.

## 1.6.2.1 External bus interface

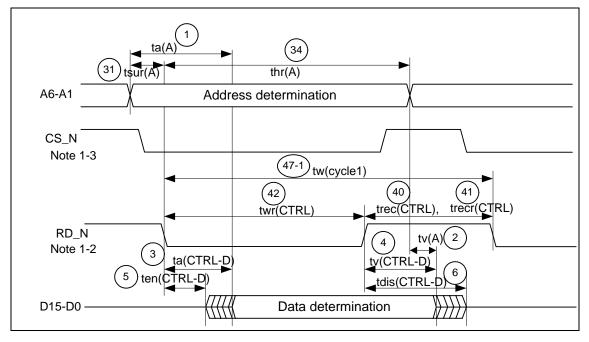

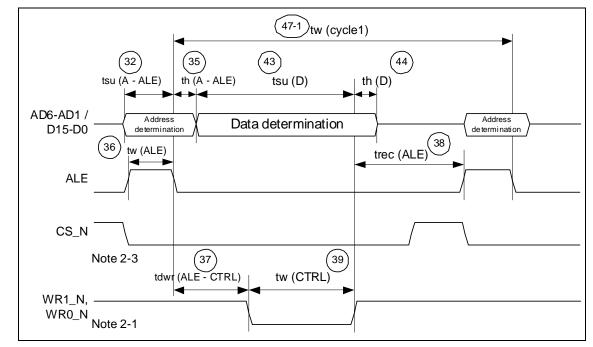

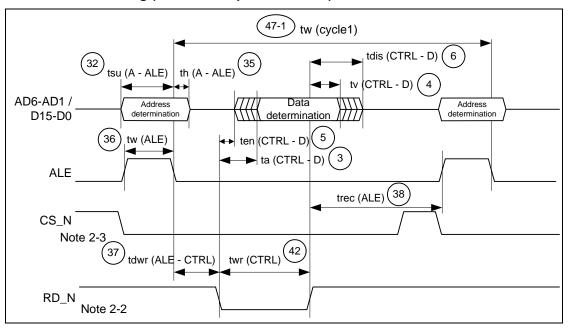

The CPU accesses the control register of the controller using the CPU bus interface. There are two types of access below for the bus interface from the CPU. Access using a chip select pin (CS\_N) and three strobe pins (RD\_N, WR0\_N and WR1\_N).

16-bit separate bus

Seven address buses (A7-1) and sixteen data buses (D15-0) are used.

16-bit multiplex bus

The ALE pin (ALE) and sixteen data buses (D15-0) are used. The data bus uses the address and data in the time division.

Separate bus or multiplex bus are selected at the MPBUS pin signal level while canceling the hardware reset.

## 1.6.2.2 FIFO buffer memory access method

This controller is compatible with the following two access types as an access method of the FIFO buffer memory for USB data transmission. Read (write) of the data from the FIFO buffer memory is possible by accessing (read/write) the FIFO port from the CPU (DMAC).

(1) CPU access

Write the data in, or read the data from, the FIFO buffer memory using the address signal and control signal.

(2) DMA access

Write the data in the FIFO buffer memory from the CPU's built-in DMAC or dedicated DMAC, or read the data from the FIFO buffer memory.

USB communication is executed by a little endian. A byte endian swap function is provided in the FIFO port access. For 16-bit access, the endian can be changed according to what is written to the register.

#### 1.6.2.3 FIFO buffer memory access method from DMAC

To access the FIFO buffer memory through the DMA access, select an access method from the following:

- (1) Method of using common bus with CPU

- (2) Method in which dedicated bus (split bus) is used

# 1.6.3 USB event

The controller notifies the events regarding USB operations to the user system through the interrupt. It also notifies that the DMA interface can access the buffer memory of the selected pipe by asserting the DREQ signal. Depending on what the software writes, interrupt notification activation can be selected for the type and factor.

#### 1.6.4 USB data transfer

All types of data transfer of USB communication, such as control transfer, bulk transfer, interrupt transfer and isochronous transfer, are possible with this controller. The following are the pipe resources for each transfer type:

- (1) Control transfer dedicated pipe 1

- (2) Interrupt transfer dedicated pipes 4

- (3) Bulk transfer dedicated pipes 3

- (4) Bulk transfer or isochronous transfer selection pipes 2

Write the USB transfer requirements for each pipe, such as transfer type, endpoint address, maximum packet size, etc., according to the user system. This controller is equipped with an 8.5KB buffer memory. Allocate the buffer memory according to the user system or execute the settings such as buffer operation mode, for the bulk transfer dedicated pipe, and bulk transfer or isochronous transfer selection pipe. In buffer operations mode, high-performance data transfer with low interrupt frequency is possible by using a double buffer configuration or continuous transfer function of the data packet. A transfer completion function has been added, using the transaction counter function for efficient data transfer rates of bulk and isochronous transfer pipes.

The user system control CPU and DMA controller access the buffer memory through three FIFO port registers.

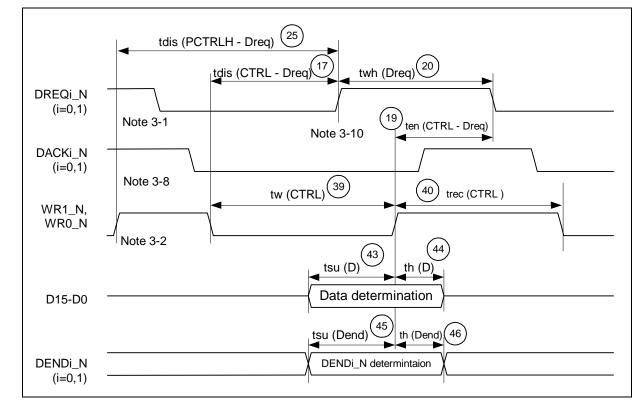

#### 1.6.5 Interface for access from DMAC

The DMA interface is the data transfer between the user system and this controller, in which the DxFIFO port is used, and it is a data transfer that does not use the CPU. This controller is equipped with 2-ch DMA interface and includes the following functions:

- (1) Transfer end notification function corresponding to the transfer end signal (DEND signal)

- (2) FIFO buffer auto clear function while receiving a zero-length packet

This controller is equipped with an interface compatible with the two types of DMA transfers given below:

(1) Cycle Steal Transfer

Assert and negate of the DREQ pin is repeatedly transmitted for one data transmission (1 byte/1 word).

(2) Burst Transmission

This is a transmission in which the DREQ pin is asserted (not negated) until the transmission is completed, due to the pipe buffer memory area allocated to the FIFO port or DEND signal.

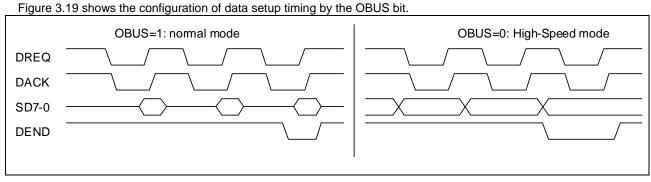

"CS\_N, RD\_N and WR\_N" or DACK\_N can be selected as the handshake signal (pin) of the DMA interface. High-performance DMA transmission is possible in the DMA transmission by a split bus by modifying the data setup timing using an OBUS bit operation of the DMAxCFG register.

#### 1.6.6 SOF pulse output function

This controller is equipped with an SOF pulse output function that notifies the SOF packet send/receive timing. When the Host Controller function is selected, a pulse is output from the SOF\_N pin at sending the SOF packet. When the Peripheral Controller function is selected, a pulse is output from the SOF\_N pin at receiving the SOF packet. When the SOF packet is damaged, a pulse is output within the specified period according to the SOF interpolation timer.

# 1.6.7 Importing the external devices

This controller is equipped with the external devices listed below. Also, as the VBUS pin has 5V-tolerant, the user system can connect the VBUS signal directly to this controller.

- (1) Resistors necessary in D+ and D-line control

- The following D+ and D- resistors necessary for USB communication are installed:

- D+ pull-up resistor (for Peripheral operations)

- D+ pull-down resistor (for host operations)

- D+ and D- termination resistors (for Hi-Speed operations)

- · D+ and D- output resistors (for Full-Speed and Low-Speed operations)

- (2) 48MHz and 480MHz PLL

- Operations can be executed by selecting one of the three types of external clocks (12MHz/24MHz/48MHz).

- (3)  $3.3V \rightarrow 1.5V$  regulator

1.5V core power is generated in this controller. In the system where a 3.3V interface power is used, this controller can be operated on a single power supply.

# 2 Register

|    |                                                   |                                                                                                                                                                                                                  | D                                                               | esigi                                | n of F                                   | Regis                        | ster T                    | able    | <u>.</u> |         |         |          |       |               |          |

|----|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|------------------------------------------|------------------------------|---------------------------|---------|----------|---------|---------|----------|-------|---------------|----------|

| -  | Bit numbe<br>Each regi                            | er:<br>ister is connected to the <sup>-</sup>                                                                                                                                                                    | 16-bit interna                                                  | l bus.                               | Odd a                                    | ddres                        | s are fr                  | om b'   | 15 to b  | 8, and  | l even  | addres   | s are | from b        | 7 to b0. |

|    | A hardwa<br>A USB re<br>Significar<br>"-" indicat | ter reset:<br>the register initial status<br>ire reset is the initialization<br>set is the initialization state<br>to points in the reset oper<br>reset he status of retained<br>tes the status when the version | on status whe<br>atus when a l<br>ation are me<br>user settings | en the<br>JSB b<br>ntione<br>s witho | extern<br>ous res<br>ed in th<br>out any | al rese<br>et is d<br>e note | et signa<br>etecteo<br>s. | d by th | ne con   |         |         | T_N piı  | n.    |               |          |

|    |                                                   | access conditions:<br>s when the register is ac                                                                                                                                                                  | cessed by th                                                    | e soft                               | ware.                                    |                              |                           |         |          |         |         |          |       |               |          |

|    | Condition<br>RRea<br>WWr<br>R/WRe<br>R(0)"0"      | ite only                                                                                                                                                                                                         | cessed by th                                                    | e con                                | troller                                  | during                       | operat                    | tions o | other th | nan re  | set:    |          |       |               |          |

|    | HWher                                             | and detailed description<br>the Host Controller func-<br>the Peripheral Controlle                                                                                                                                | tion is select                                                  | ed                                   | ed                                       |                              |                           |         |          |         |         |          |       |               |          |

| 6  | Name:<br>This is the                              | e bit symbol and bit name                                                                                                                                                                                        | ə.                                                              |                                      |                                          |                              |                           |         |          |         |         |          |       |               |          |

|    |                                                   | e description of the functi<br>or hardware.                                                                                                                                                                      | on. When th                                                     | ere is                               | no pai                                   | ticular                      | rejecti                   | on, th  | ie valu  | e durir | ng read | d is the | value | writter       | n by the |

|    | ample:<br>le shaded                               | portions are unassigned                                                                                                                                                                                          | . Fix to"0".                                                    |                                      |                                          |                              |                           |         |          |         |         |          |       |               |          |

| 1  | Bit Numb                                          |                                                                                                                                                                                                                  | 13 12                                                           | 11                                   | 10                                       | 9                            | 8                         | 7       | 6        | 5       | 4       | 3        | 2     | 1             | 0        |

|    | Bit Syml                                          |                                                                                                                                                                                                                  | B bit C bit                                                     |                                      |                                          |                              |                           |         | -        |         |         |          |       |               |          |

| 2  | Hardware<br>USB rese                              |                                                                                                                                                                                                                  | 0 0                                                             |                                      |                                          |                              |                           |         |          |         |         |          |       |               |          |

|    | Bit                                               | Name                                                                                                                                                                                                             |                                                                 | Fu                                   | Inction                                  |                              |                           |         | Softw    | are     | Hard    | lware    | Rer   | narks         |          |

|    | 15                                                | Unassigned. Fix to "0".                                                                                                                                                                                          |                                                                 |                                      |                                          |                              |                           |         |          |         |         |          | ۱۸/۱  | iting         |          |

|    | 14                                                | A bit<br>AAA enabled                                                                                                                                                                                             | 0: Operation<br>1: Operation                                    |                                      |                                          |                              |                           |         | R/V      | V       | l       | R        | disa  | abled<br>en P |          |

|    | 13                                                | B bit<br>BBB operation                                                                                                                                                                                           | 0: Low outp<br>1: High outp                                     |                                      |                                          |                              |                           |         | R        |         | ١       | N        |       |               |          |

|    | 12                                                | C bit<br>CCC control                                                                                                                                                                                             | 0: •••••<br>1: •••••                                            |                                      |                                          |                              |                           |         | R(0)/V   | V(1)    |         | R        |       |               |          |

|    |                                                   | 6                                                                                                                                                                                                                |                                                                 |                                      | Ø                                        |                              |                           |         | 3        |         | (       | 4        |       | 5             |          |

| Re | emarks                                            |                                                                                                                                                                                                                  |                                                                 |                                      |                                          |                              |                           |         |          |         |         |          |       |               |          |

|    |                                                   |                                                                                                                                                                                                                  |                                                                 |                                      |                                          |                              |                           |         |          |         |         |          |       |               |          |

# 2.1 Register List

The controller register list is shown in Table 2.1.

| Address  | Cumhal            | Name                                        | loclass |

|----------|-------------------|---------------------------------------------|---------|

|          | Symbol            |                                             | Index   |

| 00       | SYSCFG0           | System configuration control register       |         |

| 02       | SYSCFG1           | Port1 System configuration control register |         |

| 04       | SYSSTS0           | Porto System configuration status register  |         |

| 06       | SYSSTS1           | Port1 System configuration status register  |         |

| 08       | DVSTCTR0          | Port0 Device control register               |         |

| 0A       | DVSTCTR1          | Port1 Device control register               |         |

| 0C       | TESTMODE          | Test mode register                          |         |

| 0E       | PINCFG            | Data pin configuration register             |         |

| 10       | DMA0CFG           | DMA0 Pin configuration register             |         |

| 12       | DMA1CFG           | DMA1 Pin configuration register             |         |

| 14       | CFIFO             | CFIFO Port register                         |         |

| 16       |                   |                                             |         |

| 18       | D0FIFO            | D0FIFO Port register                        |         |

| 1A       |                   |                                             |         |

| 1C       | D1FIFO            | D1FIFO Port register                        |         |

| 1E       |                   |                                             |         |

| 20       | CFIFOSEL          | CFIFO Port selection register               |         |

| 22       | CFIFOCTR          | CFIFO Port control register                 |         |

| 24       |                   |                                             |         |

| 24       |                   |                                             |         |

| 28       | D0FIFOSEL         | D0FIFO Port selection register              |         |

| 20<br>2A | DOFIFOCTR         | D0FIFO Port control register                |         |

| 2A<br>2C | D1FIFOSEL         | D1FIFO Port selection register              |         |

|          |                   | D1FIFO Port selection register              |         |

| 2E       | D1FIFOCTR         |                                             |         |

| 30       | INTENB0           | Interrupt enable register 0                 |         |

| 32       | INTENB1           | Interrupt enable register 1                 |         |

| 34       | INTENB2           | Interrupt enable register 2                 |         |

| 36       | BRDYENB           | BRDY Interrupt enable register              |         |

| 38       | NRDYENB           | NRDY Interrupt enable register              |         |

| 3A       | BEMPENB           | BEMP Interrupt enable register              |         |

| 3C       | SOFCFG            | SOF Output configuration register           |         |

| 3E       |                   |                                             |         |

| 40       | INTSTS0           | Interrupt status register0                  |         |

| 42       | INTSTS1           | Interrupt status register1                  |         |

| 44       | INTSTS2           | Interrupt status register2                  |         |

| 46       | BRDYSTS           | BRDY Interrupt status register              |         |

| 48       | NRDYSTS           | NRDY Interrupt status register              |         |

| 4A       | BEMPSTS           | BEMP Interrupt status register              |         |

| 4C       | FRMNUM            | Frame number register                       |         |

| 4E       | UFRMNUM           | Microframe number register                  |         |

| 50       | USBADDR           | USB address register                        |         |

| 54       | USBREQ            | USB request type register                   |         |

| 56       | USBVAL            | USB request value register                  |         |

| 58       | USBINDX           | USB request index register                  |         |

| 5A       | USBLENG           | USB request length register                 |         |

| 5A<br>5C | DCPCFG            | DCP configuration register                  |         |

| 5C<br>5E |                   |                                             |         |

|          | DCPMAXP<br>DCPCTR | DCP maximum packet size register            |         |

| 60       | DUPUIK            | DCP control register                        |         |

| 62       | DIDECE            |                                             |         |

| 64       | PIPESEL           | Pipe window selection register              |         |

| 66       |                   |                                             |         |

| 68       | PIPECFG           | Pipe configuration register                 |         |

| 6A       | PIPEBUF           | Pipe buffer specification register          |         |

| 6C       | PIPEMAXP          | Pipe maximum packet size register           |         |

| 6E       | PIPEPERI          | Pipe period control register                |         |

| 70       | PIPE1CTR          | Pipe1 Control register                      |         |

| 72       | PIPE2CTR          | Pipe2 Control register                      |         |

| 74       | PIPE3CTR          | Pipe3 Control register                      |         |

# Table 2.1 Register List

Rev1.01 Oct 17, 2008 page 14 of 183

RENESAS

| Address | Symbol   | Name                                       | Index |

|---------|----------|--------------------------------------------|-------|

| 76      | PIPE4CTR | Pipe4 Control register                     |       |

| 78      | PIPE5CTR | Pipe5 Control register                     |       |

| 7A      | PIPE6CTR | Pipe6 Control register                     |       |

| 7C      | PIPE7CTR | Pipe7 Control register                     |       |

| 7E      | PIPE8CTR | Pipe8 Control register                     |       |

| 80      | PIPE9CTR | Pipe9 Control register                     |       |

| 82-8E   |          |                                            |       |

| 90      | PIPE1TRE | Pipe1 Transaction counter enabled register |       |

| 92      | PIPE1TRN | Pipe1 Transaction counter register         |       |

| 94      | PIPE2TRE | Pipe2 Transaction counter enabled register |       |

| 96      | PIPE2TRN | Pipe2 Transaction counter register         |       |

| 98      | PIPE3TRE | Pipe3 Transaction counter enabled register |       |

| 9A      | PIPE3TRN | Pipe3 Transaction counter register         |       |

| 9C      | PIPE4TRE | Pipe4 Transaction counter enabled register |       |

| 9E      | PIPE4TRN | Pipe4 Transaction counter register         |       |

| A0      | PIPE5TRE | Pipe5 Transaction counter enabled register |       |

| A2      | PIPE5TRN | Pipe5 Transaction counter register         |       |

| A4-CE   |          |                                            |       |

| D0      | DEVADD0  | Device address 0 configuration register    |       |

| D2      | DEVADD1  | Device address 1 configuration register    |       |

| D4      | DEVADD2  | Device address 2 configuration register    |       |

| D6      | DEVADD3  | Device address 3 configuration register    |       |

| D8      | DEVADD4  | Device address 4 configuration register    |       |

| DA      | DEVADD7  | Device address 5 configuration register    |       |

| DC      | DEVADD6  | Device address 6 configuration register    |       |

| DE      | DEVADD7  | Device address 7 configuration register    |       |

| E0      | DEVADD8  | Device address 8 configuration register    |       |

| E2      | DEVADD9  | Device address 9 configuration register    |       |

| E4      | DEVADDA  | Device address A configuration register    |       |

| E6      |          |                                            |       |

Nothing is assigned to the shaded portions. Do not access.

# 2.2 Bit Symbol List

A list of controller bit symbols is shown in Table 2.2.

| A alaha   | Register             |        |         |       | Oddinu  | umbers    |        |        |              |                |          |                | Evenn        | umbers   |       |       |       |

|-----------|----------------------|--------|---------|-------|---------|-----------|--------|--------|--------------|----------------|----------|----------------|--------------|----------|-------|-------|-------|

| Addr      | name                 | 15     | 14      | 13    | 12      | 11        | 10     | 9      | 8            | 7              | 6        | 5              | 4            | 3        | 2     | 1     | 0     |

|           | SYSCFG0              | XT     | AL      | XCKE  |         | PLLC      | SCKE   |        |              | HSE            | DCFM     | DRPD           | DPRPU        |          |       |       | USBE  |

|           | SYSCFG1              |        |         |       | CNTFLG  |           |        | PCSDIS | LPSME        | HSE            |          | DRPD           |              |          |       |       |       |

|           | SYSSTS0              | OVC    |         |       |         |           |        |        |              |                |          |                | HDDM         |          | IDMON | LN    |       |

|           | SYSSTS1              | OVC    | MON     |       |         |           |        | VEQUE  |              | DIMUNE         | LIODDOT  |                | HDDM         |          |       |       |       |

| -         | DVSTCTR0<br>DVSTCTR1 |        |         |       |         | HNPBTOA   | EXTLP0 | VBOUT  | WKUP         | RWUPE<br>RWUPE |          |                | UACT<br>UACT |          | RHST  |       |       |

|           | UTEST                |        |         |       |         |           |        | VBOUT  |              | RWUPE          | USBRSI   | RESUME         | UACT         |          | UT    | RHST  |       |

|           | PINCFG               | LDRV   |         |       |         |           |        |        |              |                |          |                |              |          | 01    | 51    | INTA  |

|           | DMA0CFG              | EDIT   | DREQA   | BURST |         |           | DACKA  |        | DFORM        |                | DENDA    | PKTM           | DENDE        |          | OBUS  |       | 11177 |

|           | DMA1CFG              |        | DREQA   |       |         |           | DACKA  |        | DFORM        |                | DENDA    | PKTM           | DENDE        |          | OBUS  |       |       |

| 14        | CFIFO                |        |         |       |         |           |        |        | CFP          | ORT            |          |                |              |          |       |       |       |

| 16        |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

| -         | D0FIFO               |        |         |       |         |           |        |        | D0FF         | ORT            |          |                |              |          |       |       |       |

| <b>1A</b> |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

|           | D1FIFO               |        |         |       |         |           |        |        | D1FI         | PORT           |          |                | _            |          |       |       |       |

| 1E        | CFIFOSEL             | RCNT   | REW     |       |         |           | MBW    |        | BIGEND       |                |          | ISEL           |              |          | CUR   |       |       |

| -         | CFIFOSEL             | BVAL   | BCLR    | FRDY  |         |           | IVIDVV |        | עאוםטוס      |                | DT       |                |              | 1        | UUK   |       |       |

| 24        |                      | DVAL   | DOLIN   | TRET  |         |           |        |        |              |                |          |                |              |          |       |       |       |

| 26        |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

|           | D0FIFOSEL            | RCNT   | REW     | DCLRM | DREQE   |           | MBW    |        | BIGEND       |                |          |                |              |          | CUR   | PIPE  |       |

|           | D0FIFOCTR            | BVAL   | BCLR    | FRDY  |         |           |        |        |              |                | DT       | LN             |              |          |       |       |       |

|           | D1FIFOSEL            | RCNT   | REW     | DCLRM | DREQE   |           | MBW    |        | BIGEND       |                |          |                |              |          | CUR   | PIPE  |       |

|           | D1FIFOCTR            | BVAL   | BCLR    | FRDY  |         |           |        |        |              |                | DT       | LN             |              |          |       |       |       |

|           | INTENB0              | VBSE   | RSME    | SOFE  | DVSE    | CTRE      | BEMPE  | NRDYE  | BRDYE        |                |          |                |              |          |       |       |       |

|           | INTENB1              |        | BCHGE   |       |         | ATTCHE    |        |        |              |                | EOFERRE  |                | SACKE        |          |       |       |       |

|           | INTENB2<br>BRDYENB   | OVRCRE | BCHGE   |       | DICHE   | ATTCHE    |        |        |              |                | EOFERRE  | PIPEB          |              |          |       |       |       |

|           | NRDYENB              |        |         |       |         |           |        |        |              |                |          | PIPED          |              |          |       |       |       |

|           | BEMPENB              |        |         |       |         |           |        |        |              |                |          | PIPEB          |              |          |       |       |       |

|           | SOFCFG               |        |         |       |         |           |        |        | TRNENSEL     |                | BRDYM    |                | EDGESTS      | SO       | FM    |       |       |

| 3E        |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

|           | INTSTS0              | VBINT  | RESM    | SOFR  | DVST    | CTRT      | BEMP   | NRDY   | BRDY         | VBSTS          |          | DVSQ           |              | VALID    |       | CTSQ  |       |

|           | INTSTS1              | OVRCR  | BCHG    |       | DTCH    | ATTCH     |        |        |              |                | EOFERR   | SIGN           | SACK         |          |       |       |       |

|           | INTSTS2              | OVRCR  | BCHG    |       | DTCH    | ATTCH     |        |        |              |                | EOFERR   | BIDE           |              |          |       |       |       |

|           | BRDYSTS<br>NRDYSTS   |        |         |       |         |           |        |        |              |                |          | PIPE           |              |          |       |       |       |

|           | BEMPSTS              |        |         |       |         |           |        |        |              |                |          | PIPEI<br>PIPEI |              |          |       |       |       |

|           | FRMNUM               | OVRN   | CRCE    |       |         |           |        |        |              |                |          | FRNM           |              |          |       |       |       |

|           | UFRMNUM              |        |         |       |         |           |        |        |              |                |          |                |              |          |       | UFRNM |       |

| 50        | USBADDR              |        |         |       |         |           |        |        |              |                |          |                |              | USBADDF  | 2     |       |       |

| 52        |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

|           | USBREQ               |        |         |       | bRed    | quest     |        |        |              |                |          |                | bmRequ       | iestType |       |       |       |

|           |                      |        |         |       |         |           |        |        | wVa          |                |          |                |              |          |       |       |       |

|           |                      |        |         |       |         |           |        |        | wln          |                |          |                |              |          |       |       |       |

|           | USBLENG<br>DCPCFG    |        |         |       |         |           |        |        | wLe<br>CNTMD |                |          |                | DIR          |          |       |       |       |

|           | DCPCFG               |        | DEV     | /SEI  |         |           |        |        |              |                |          |                | UK           | MXPS     |       |       |       |

|           | DCPMAAP              | BSTS   |         | CSCLR | CSSTS   | SURFOCI R |        |        | SQCI R       | SQSET          | SQMON    | PBUSY          | PINGE        | WI/AF O  | CCPL  | P     | ID    |

| 62        |                      | 2010   | 55.12.0 | CODEN | 00010   | CONEQUEN  |        |        |              |                | 5 4.1011 | 2001           |              |          |       |       | _     |

|           | PIPESEL              |        |         |       |         |           |        |        |              |                |          |                |              |          | PIPE  | SEL   |       |

| 66        |                      |        |         |       |         |           |        |        |              |                |          |                |              |          |       |       |       |

|           | PIPECFG              | ΤY     | PE      |       |         |           | BFRE   | DBLB   | CNTMD        | SHTNAK         |          |                | DIR          |          | EPN   | IUM   |       |

|           | PIPEBUF              |        |         |       | BUFSIZE |           |        |        |              |                |          |                |              | BUFNMB   |       |       |       |

|           |                      |        | DEV     | SEL   | 1510    |           |        |        |              |                |          | MXPS           | _            |          |       |       |       |

| θE        | PIPEPERI             |        |         |       | IFIS    |           |        |        |              |                |          |                |              |          |       | IITV  |       |

# Table 2.2 Bit Symbol List

Rev1.01 Oct 17, 2008 page 16 of 183

RENESAS

# R8A66597FP/DFP/BG

| Addr      | Register           |                  |        |            | Oddinu  | Imbers  |        |         |       |            |       |       | Evenn | umbers |        |    |                  |

|-----------|--------------------|------------------|--------|------------|---------|---------|--------|---------|-------|------------|-------|-------|-------|--------|--------|----|------------------|

| 700       | name               | 15               | 14     | 13         | 12      | 11      | 10     | 9       | 8     | 7          | 6     | 5     | 4     | 3      | 2      | 1  | 0                |

| 70        | PIPE1CTR           | BSTS             | INBUFM | CSCLR      | CSSTS   | -       | ATREPM | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 72        | PIPE2CTR           | BSTS             | INBUFM | CSCLR      | CSSTS   |         | ATREPM | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 74        | PIPE3CTR           | BSTS             | INBUFM | CSCLR      | CSSTS   |         | ATREPM | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 76        | PIPE4CTR           | BSTS             | INBUFM | CSCLR      | CSSTS   |         | ATREPM | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 78        | PIPE5CTR           | BSTS             | INBUFM | CSCLR      | CSSTS   |         | ATREPM | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 7A        | PIPE6CTR           | BSTS             |        | CSCLR      | CSSTS   |         |        | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 7C        | PIPE7CTR           | BSTS             |        | CSCLR      | CSSTS   |         |        | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 7E        | PIPE8CTR           | BSTS             |        | CSCLR      | CSSTS   |         |        | ACLRM   | SQCLR | SQSET      | SQMON | PBUSY |       |        |        | P  | ID               |

| 80        | PIPE9CTR           | BSTS CSCLR CSSTS |        |            |         |         | ACLRM  | SQCLR   |       | SQMON      | PBUSY |       |       |        | Р      | ID |                  |

| 82-       |                    |                  |        |            |         |         |        |         |       |            |       |       |       |        |        |    |                  |

| 8E        |                    |                  |        |            |         |         |        |         |       |            |       |       |       |        |        |    |                  |

| 90        | PIPE1TRE           |                  |        |            |         |         |        | TRENB   | TRCLR |            |       |       |       |        |        |    |                  |

| 92        | PIPE1TRN           |                  |        |            |         |         | •      |         | TRN   | CNT        |       |       |       |        |        |    |                  |

| 94        | PIPE2TRE           |                  |        |            |         |         |        | TRENB   | TRCLR |            |       |       |       |        |        |    |                  |

| 96        | PIPE2TRN           |                  |        |            |         |         | •      |         | TRN   | CNT        |       |       |       |        |        |    |                  |

| 98        | PIPE3TRE           |                  |        |            |         |         |        | TRENB   | TRCLR |            |       |       |       |        |        |    |                  |

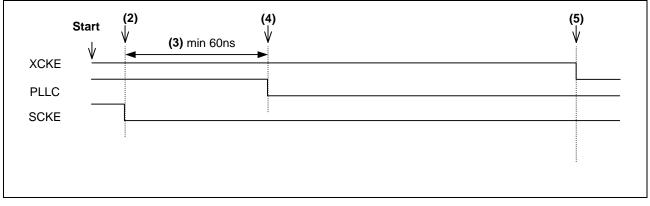

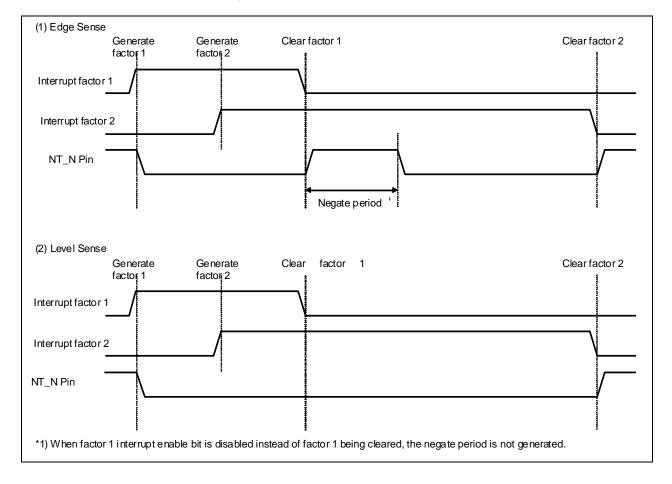

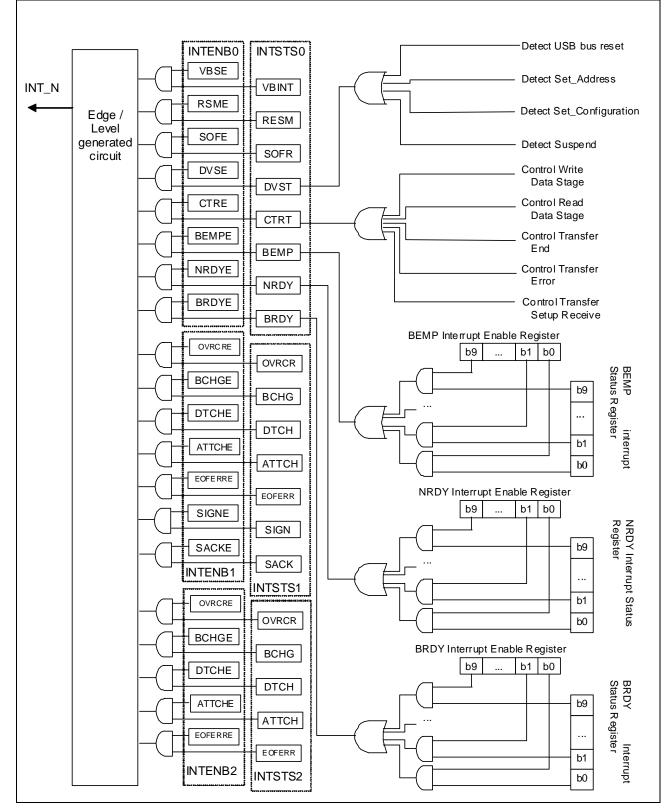

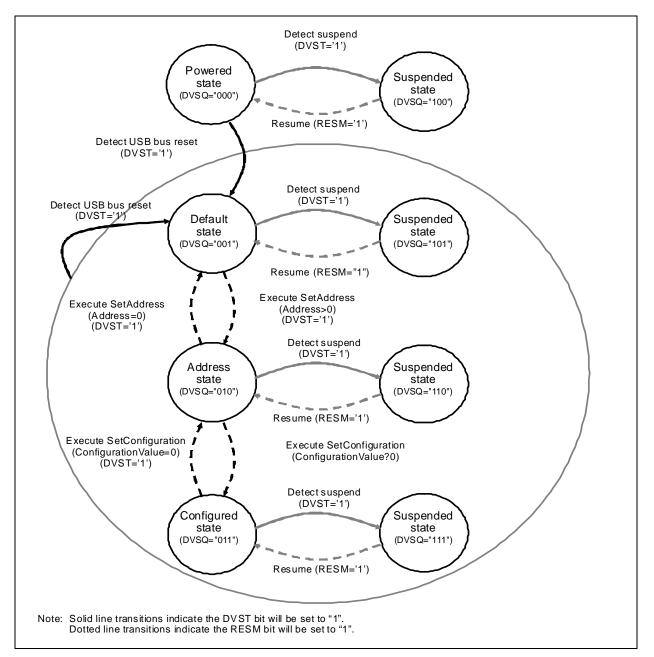

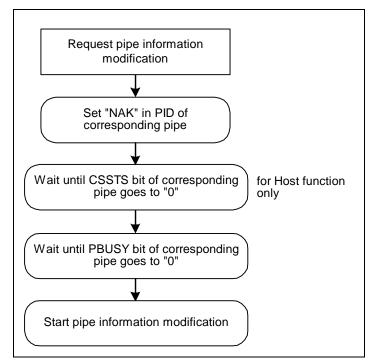

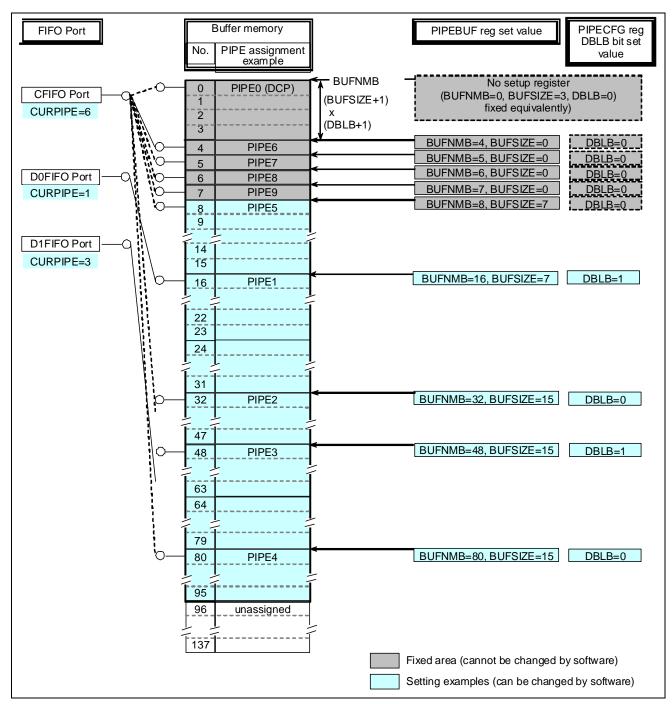

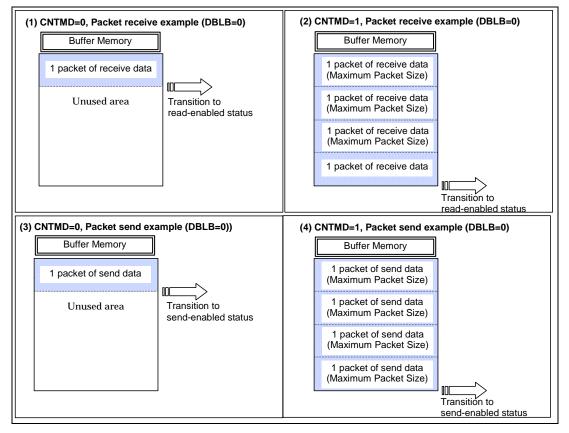

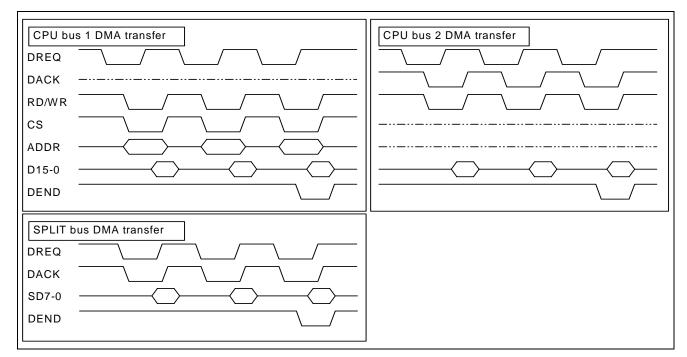

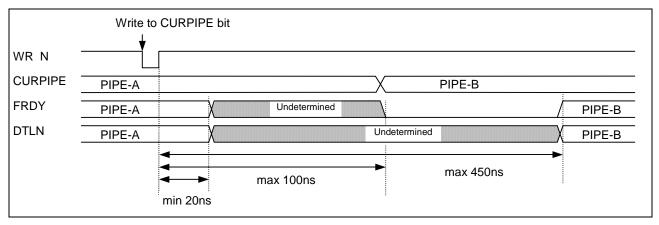

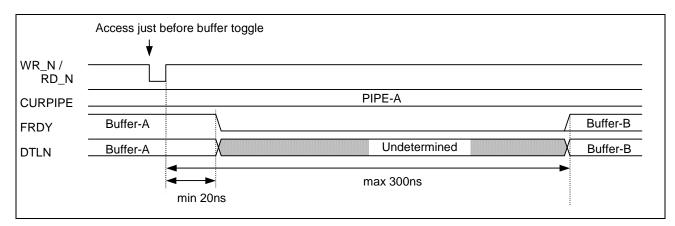

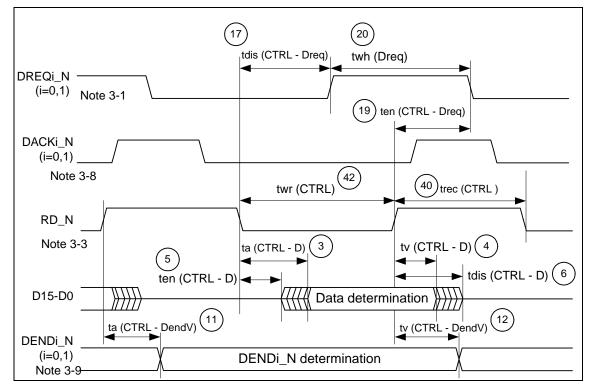

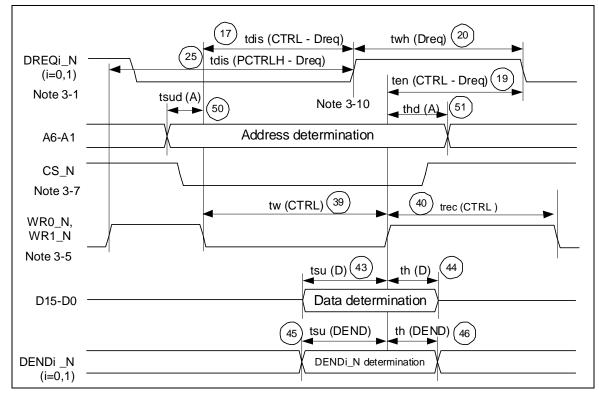

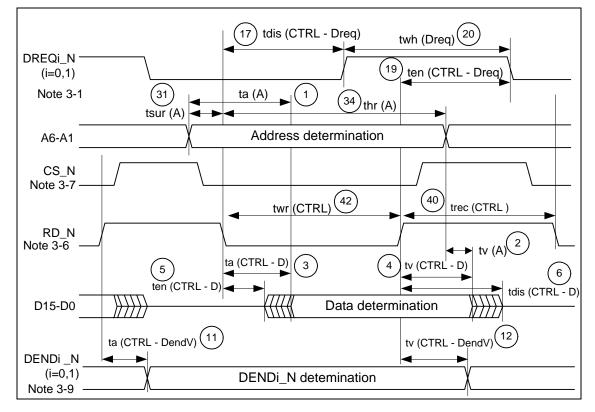

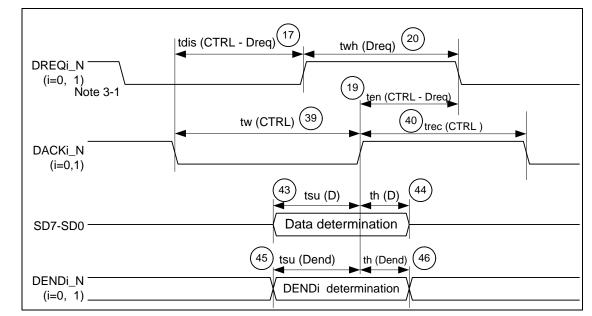

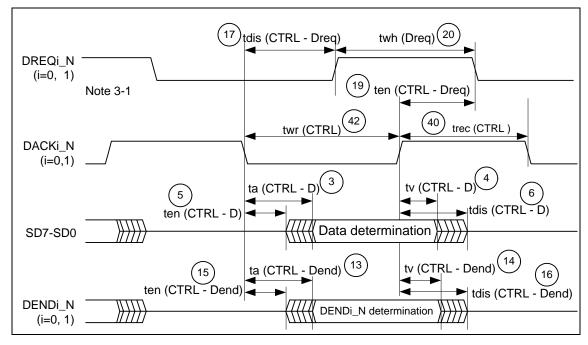

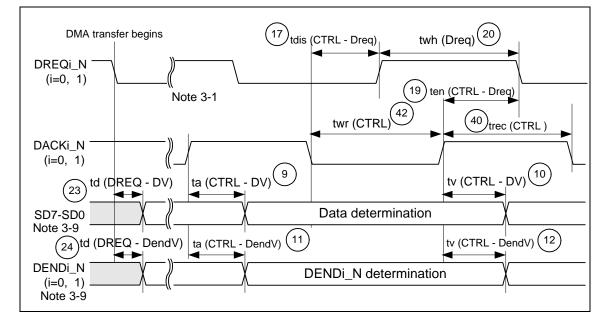

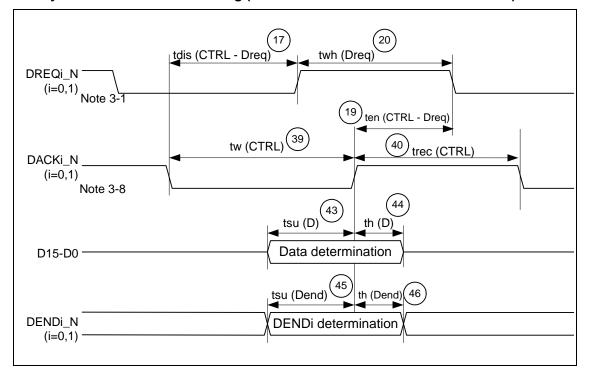

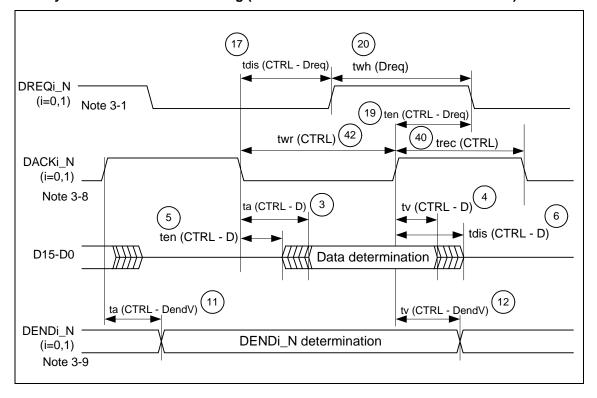

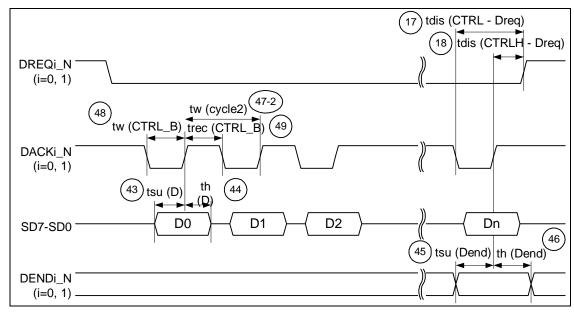

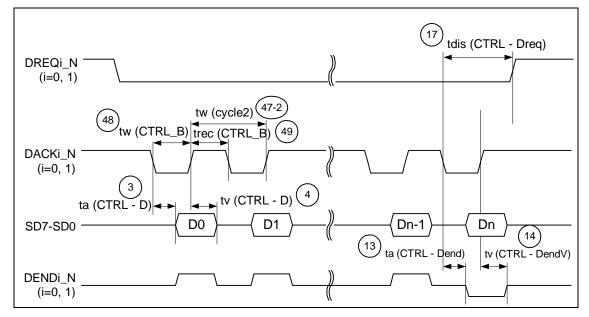

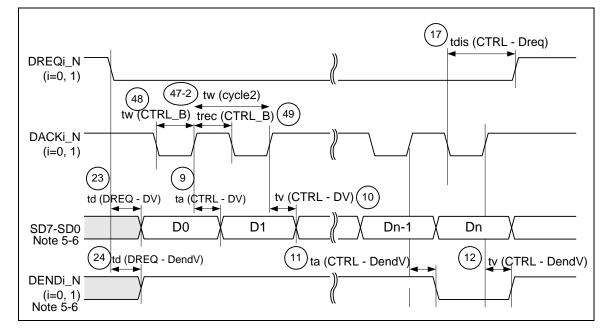

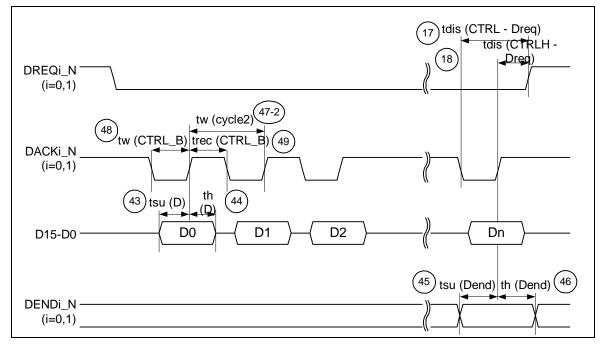

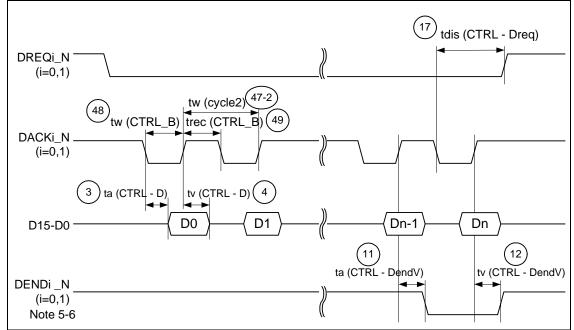

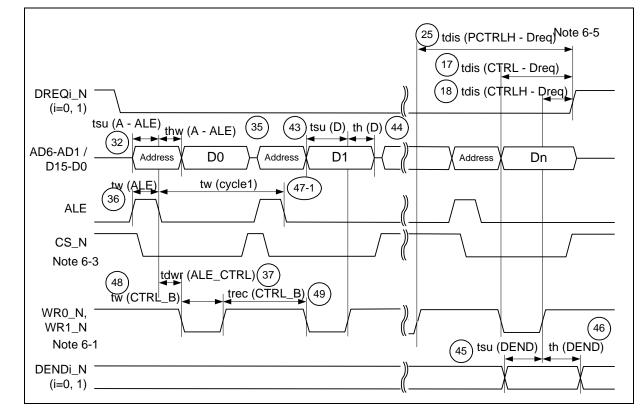

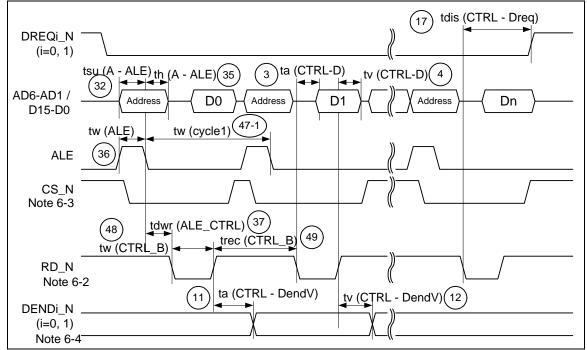

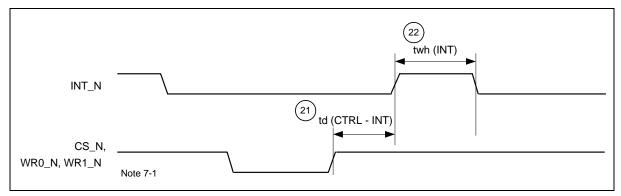

| 9A        | PIPE3TRN           |                  |        |            |         |         |        |         | TRN   | CNT        |       |       |       |        |        |    |                  |