# RNA52A10MM

R03DS0091EJ0600 (Previous code: REJ03D0858-0500) Rev.6.00

Dec 19, 2014

## Dual CMOS system-RESET IC

### **Description**

The RNA52A10MM incorporates two reset circuits, one with and one without a delay function, allowing the generation of separate reset signals for a microprocessor and associated system circuits. The detection voltage of each reset circuit is determined by the value of an external resistor, and the internal reference voltage is 1.0 V. The CMOS process for the RNA52A10MM means that the device draws only 1.1  $\mu$ A (typ.). The reset cancellation delay time is set with a high degree of accuracy by the values of a capacitor and resistor connected with the CD pin. The MR (manual reset) input pin is provided for the reset circuit with the delay function, and the reset signal is output in response to a high level on the MR input pin. The MR pin is pulled down by a 2-M $\Omega$  internal resistor. Output pins Vo1 and Vo2 are open drain.

#### **Features**

• Two CMOS reset circuits, one with and one without the delay function

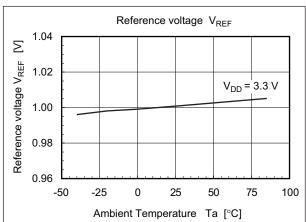

• Reference voltage: 1.0 V

Reference voltage accuracy: ± 50 mV

Reference voltage hysteresis: 6% (typ.)

Low current consumption: 1.1 μA (typ.)

Delay time set by an external CR circuit

- Manual reset input

- · Open-drain output

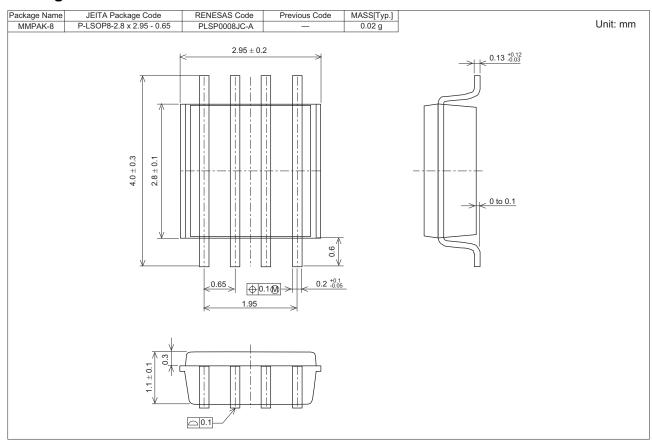

- MMPAK-8 (8-pin) package

- Operating temperature range: 40 to 85°C

- Ordering Information

| Part Name    | Package Type | Package Code | Package<br>Abbreviation | Taping Abbreviation (Quantity) |  |

|--------------|--------------|--------------|-------------------------|--------------------------------|--|

| RNA52A10MMEL | MMPAK-8 pin  | PLSP0008JC-A | MM                      | EL (3,000 pcs / Reel)          |  |

#### **Application**

- Power-supply monitoring and resetting for microprocessors

- Power supply sequence control for microprocessors

- Desktop and laptop PCs

- PC peripheral devices such as printers

- Digital still cameras, digital video cameras, and PDAs

- Battery-driven products

- Wireless communications systems

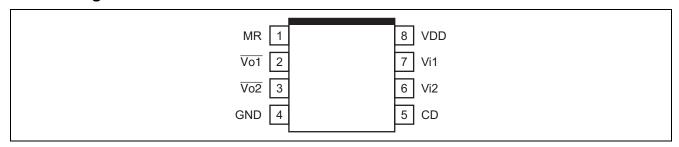

## **Pin Arrangement**

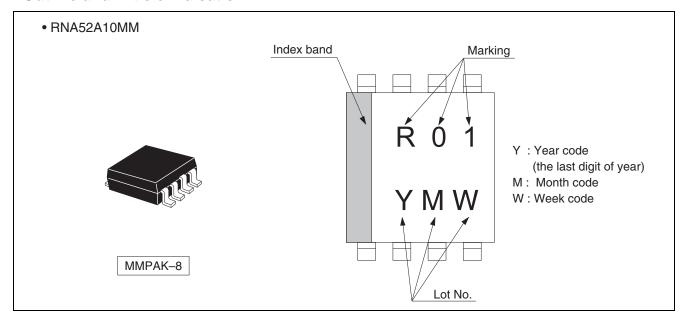

### **Outline and Article Indication**

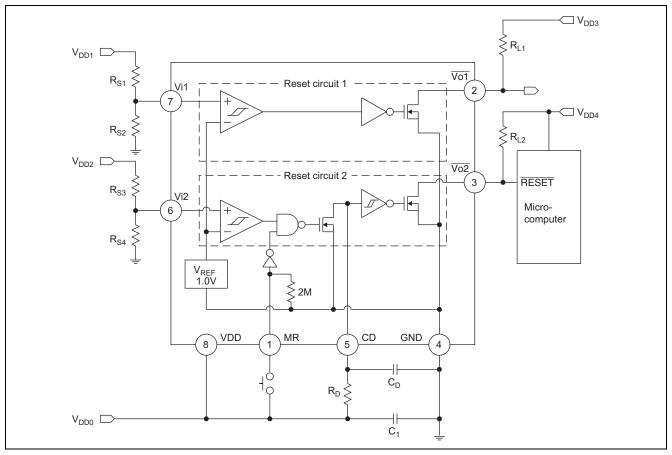

## **Functional Block Diagram and Typical application Circuit**

- Notes: 1. Please refer to the following equations to set up reset-threshold voltages for power supplies  $V_{DD1}$  and  $V_{DD2}$ , and to set up external voltage-dividing resistor pairs  $R_{S1}$  and  $R_{S2}$ , and  $R_{S3}$  and  $R_{S4}$ .

- (1)  $V_{DD1}$  reset-threshold voltage =  $V_{REF} \times (R_{S1}+R_{S2})/R_{S2}$

- (2)  $V_{DD2}$  reset-threshold voltage =  $V_{REF} \times (R_{S3}+R_{S4})/R_{S4}$

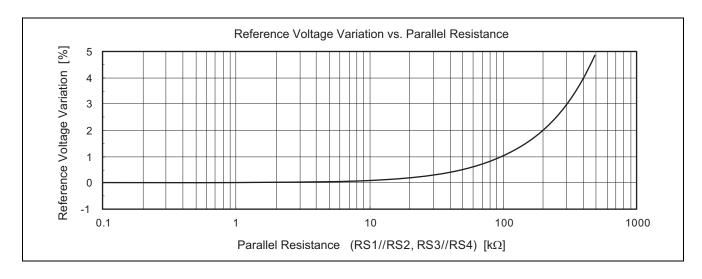

Note that values must be set up within the following range: R<sub>S1</sub>, R<sub>S2</sub>, R<sub>S3</sub>, R<sub>S4</sub>  $\leq$  50 k $\Omega$

See the following graph for the relationship between the reference voltage variation and the value selected for  $R_{S1}$ ,  $R_{S2}$ ,  $R_{S3}$  and  $R_{S4}$ .

- 2. For capacitor C1, select a type which has excellent frequency characteristics. For stable operation, place it between the VDD pin and the GND pin and as close as is possible to the chip.

- 3. The value of capacitor C<sub>1</sub> must suit the system environment in terms of the quality of the power supply and so forth.

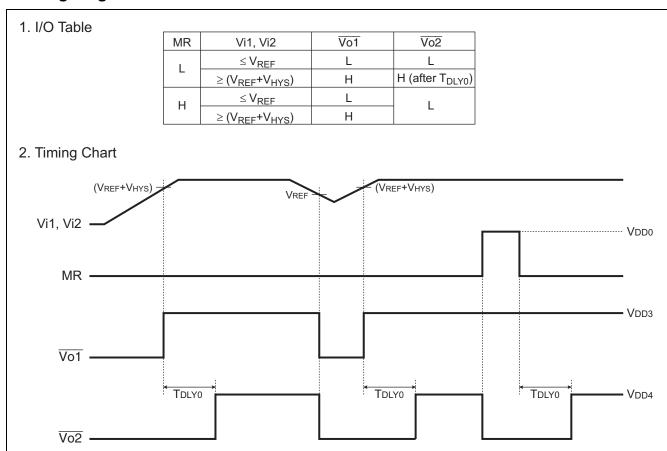

## **Timing Diagram**

## **Absolute Maximum Ratings**

| Item                                                   | Symbol           | Ratings                 | Unit |  |

|--------------------------------------------------------|------------------|-------------------------|------|--|

| Supply voltage (VDD)                                   | $V_{DD}$         | 6.0                     | V    |  |

| Input voltage (Vi1, Vi2, MR, CD)                       | $V_{IN}$         | −0.3 to V <sub>DD</sub> | V    |  |

| Output voltage (Vo1, Vo2)                              | V <sub>OUT</sub> | -0.3 to 6.0             | V    |  |

| Output current (Vo1, Vo2)                              | I <sub>OUT</sub> | 30                      | mA   |  |

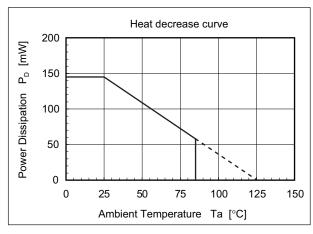

| Continuous power dissipation (Ta = 25°C, in still air) | P <sub>D</sub>   | 145                     | mW   |  |

| Operating temperature                                  | T <sub>OPR</sub> | -40 to 85               | °C   |  |

| Storage temperature T <sub>STG</sub>                   |                  | -55 to 125              | °C   |  |

Note: Refer to the relevant characteristic curve on page 6 for continuous power dissipation.

## **Recommended Operating Conditions**

| Item                             | Symbol           | Min. | Max.     | Unit |

|----------------------------------|------------------|------|----------|------|

| Supply voltage (VDD)             | $V_{DD}$         | 1.4  | 5.5      | V    |

| Input voltage (Vi1, Vi2, MR, CD) | $V_{IN}$         | 0    | $V_{DD}$ | V    |

| Output voltage (Vo1, Vo2)        | V <sub>OUT</sub> | 0    | 5.5      | V    |

| Output current (Vo1, Vo2)        | I <sub>OUT</sub> | 0    | 15       | mA   |

| Operating temperature            | $T_OPR$          | -40  | 85       | °C   |

#### **Electrical Characteristics**

( $Ta = 25^{\circ}C$ , unless otherwise noted)

| ltem                                           |                                         | Symbol                                            | Min.                           | Тур.                         | Max.                           | Unit | Test Conditions                                                                                                                 | Test<br>Circuit |

|------------------------------------------------|-----------------------------------------|---------------------------------------------------|--------------------------------|------------------------------|--------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Supply voltage                                 |                                         | $V_{DD}$                                          | 1.4                            | _                            | 5.5                            | V    |                                                                                                                                 | _               |

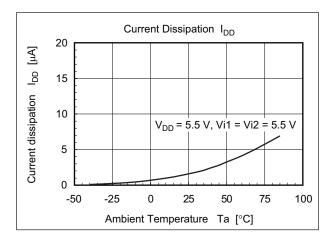

| Current consumption                            |                                         | I <sub>DD</sub>                                   | _                              | 1.1                          | 19                             | μА   | $V_{DD} = 5.5 \text{ V}$<br>$V_{i1} = V_{i2} = 5.5 \text{ V}$                                                                   | 1               |

| Reference voltag                               | е                                       | $V_{REF}$                                         | 0.95                           | 1.00                         | 1.05                           | V    | $V_{DD} = 3.3 \text{ V}$                                                                                                        | 2               |

| Reference voltage coefficient (Reference value | •                                       | $\frac{\Delta V_{REF}}{V_{REF} \cdot \Delta T_a}$ | _                              | ±100                         | _                              | °C   | $T_a = -40 \text{ to } 85^{\circ}\text{C}$                                                                                      | 2               |

| Vi1, Vi2 input<br>hysteresis voltag            | е                                       | V <sub>HYS</sub>                                  | 28.5<br>(V <sub>REF</sub> ×3%) | 60<br>(V <sub>REF</sub> ×6%) | 94.5<br>(V <sub>REF</sub> ×9%) | mV   | V <sub>DD</sub> = 3.3 V                                                                                                         | 2               |

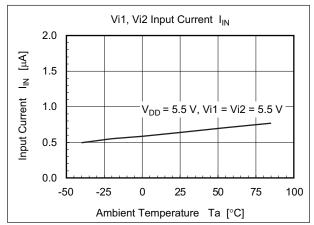

| Vi1, Vi2 input cur                             | rent                                    | I <sub>IN</sub>                                   | _                              | 0.6                          | 2.2                            | μА   | $V_{DD} = 5.5 \text{ V}$<br>$V_{i1} = V_{i2} = 5.5 \text{ V}$                                                                   | 3               |

| CD input thresho                               | ld voltage                              | $V_{DLY}$                                         | V <sub>DD</sub> ×0.43          | V <sub>DD</sub> ×0.63        | V <sub>DD</sub> ×0.83          | V    | $V_{DD} = 3.3 \text{ V}$<br>$V_{i1} = V_{i2} = 1.2 \text{ V}$                                                                   | 4               |

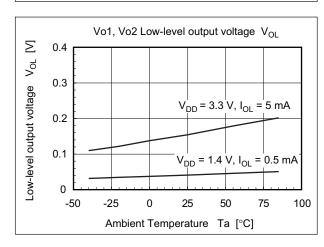

| Vo1, Vo2<br>low-level output voltage           |                                         |                                                   | _                              | 0.05                         | 0.15                           | ٧    | $V_{DD} = 1.4V$ $V_{i1} = V_{i2} = 0 V$ $I_{OL} = 0.5 \text{ mA}$                                                               | 5               |

|                                                |                                         | V <sub>OL</sub>                                   | _                              | 0.15                         | 0.35                           | ٧    | $V_{DD} = 3.3V$ $V_{i1} = V_{i2} = 0 V$ $I_{OL} = 5 \text{ mA}$                                                                 | 6               |

| Vo1, Vo2<br>output leakage current             |                                         | I <sub>LK</sub>                                   | _                              | _                            | 100                            | nA   | $V_{DD} = V_{O1} = V_{O2} = 5.5 \text{ V}$<br>$V_{i1} = V_{i2} = 1.2 \text{ V}$                                                 | 7               |

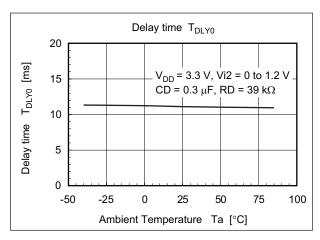

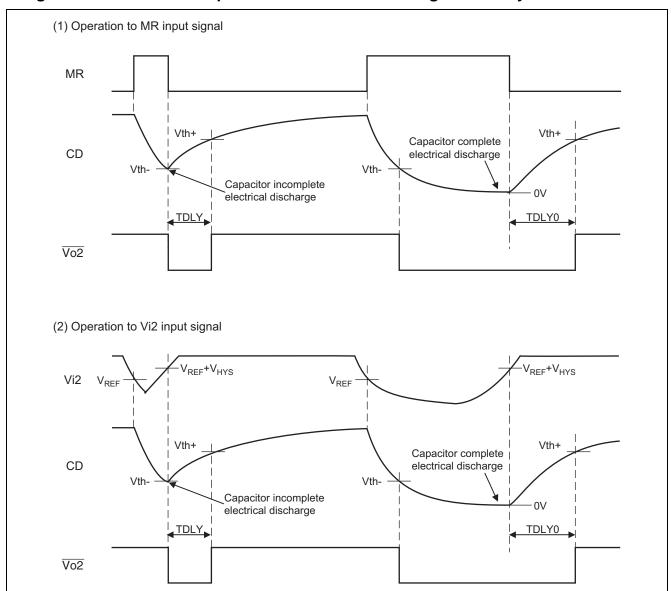

| Vo2<br>Delay time <sup>Note1</sup>             | Incomplete discharge of capacity CD     | T <sub>DLY</sub>                                  | 1.1                            | 11                           | 17                             | ms   | V <sub>DD</sub> = 3.3 V                                                                                                         | 8               |

|                                                | complete<br>discharge of<br>capacity CD | T <sub>DLY0</sub>                                 | 7                              | 11                           | 17                             | ms   | $V_{12} = 0 \text{ V} \rightarrow 1.2 \text{ V}$<br>$C_D = 0.3 \text{ μF}, R_D = 39 \text{ k}\Omega$                            | 8               |

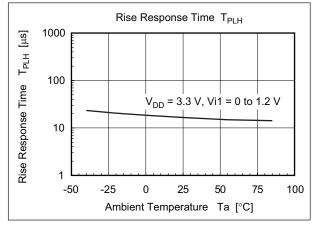

| Vo1 Rise response time                         |                                         | T <sub>PLH</sub>                                  | _                              | 30                           | 300                            | μs   | $V_{DD} = 3.3 \text{ V}$<br>$V_{i1} = 0 \text{ V} \rightarrow 1.2 \text{ V}$                                                    | 9               |

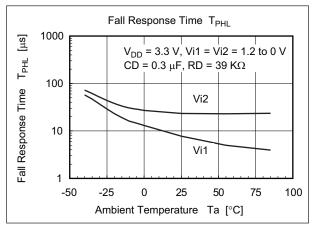

| Vo1, Vo2<br>fall response time                 |                                         | T <sub>PHL</sub>                                  | _                              | 30                           | 800                            | μѕ   | $V_{DD} = 3.3 \text{ V}$ $V_{i1} = V_{i2} = 1.2 \text{ V} \rightarrow 0 \text{ V}$ $C_D = 0.3  \mu\text{F},  R_D = 39  k\Omega$ | 10              |

| MR low-level input voltage                     |                                         | V <sub>IL</sub>                                   | _                              | _                            | V <sub>DD</sub> ×0.2           | V    | $V_{DD} = 3.3 \text{ V}$ $V_{i1} = V_{i2} = 1.2 \text{ V}$                                                                      | 11              |

| MR high-level input voltage                    | V <sub>DD</sub> < 4.5V                  | - V <sub>IH</sub>                                 | V <sub>DD</sub> ×0.75          | _                            | _                              | V    | $V_{DD} = 3.3 \text{ V}$ $V_{i1} = V_{i2} = 1.2 \text{ V}$                                                                      | 11              |

|                                                | V <sub>DD</sub> ≥ 4.5V                  |                                                   | V <sub>DD</sub> ×0.5           | _                            | _                              | V    | $V_{DD} = 5.0 \text{ V}$ $V_{i1} = V_{i2} = 1.2 \text{ V}$                                                                      | 12              |

| MR input pull-down resistance                  |                                         | R <sub>MR</sub>                                   | 0.5                            | 2                            | _                              | МΩ   | V <sub>DD</sub> = 5.5 V<br>V <sub>MR</sub> = 5.5 V                                                                              | 13              |

Notes: 1. When capacitor  $C_D$  is completely discharged and charging starts in the state that  $C_D$  pin voltage is 0 V, the minimum value of delay time  $T_{DLY0}$  is 7 ms. However, when the discharging time is short and charging starts in the state that the voltage does not completely fall to 0 V, the minimum value of delay time  $T_{DLY}$  is 1.1 ms. Then, the minimum value of Low time (reset time) of  $\overline{Vo2}$  is 1.1 ms as the delay time  $T_{DLY}$ . Refer to Regulations for state of capacitor  $C_D$  electrical discharge and delay time on page 10 for details.

- 2. Refer to the characteristic curves on page 6 for temperature dependence of the main characteristics.

- 3. Refer to pages 8 and 9 for the test circuits.

#### Characteristic curves

## **Pin Descriptions**

| Pin No. | Pin Name                                                                                                               | Function                                                                                                                                                                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                        | Manual reset input pin for reset circuit 2 (the circuit with the delay function).                                                                                                                                                                                                     |

|         |                                                                                                                        | The MR signal is active high, so applying a high level to MR sets the Vo2 pin to the low level.                                                                                                                                                                                       |

|         | If Vi2 > V <sub>REF</sub> when the signal on the MR pin is changed back from the high to the low level, the Vo2 pin is |                                                                                                                                                                                                                                                                                       |

| 1       | MR                                                                                                                     | returned from the low to the high level after a delay time T <sub>DLY0</sub> . This can be set as required. The MR pin is                                                                                                                                                             |

|         |                                                                                                                        | pulled down to the GND level via an internal 2-M $\Omega$ resistor . However, we recommend connection of the pin to                                                                                                                                                                   |

|         |                                                                                                                        | the GND line when it is not in use.                                                                                                                                                                                                                                                   |

|         |                                                                                                                        | Reset signal output pin for reset circuit 1 (the circuit with no delay function). The output is open-drain.                                                                                                                                                                           |

|         |                                                                                                                        | The recommended value of the pull-up resistor ( $R_{L1}$ ) is 3 k to 100 k $\Omega$ . When the voltage input on pin Vi1 falls to                                                                                                                                                      |

| 2       | Vo1                                                                                                                    | or below $V_{\text{REF}}$ , the signal output from the $\overline{\text{Vo1}}$ pin is changed from the high to the low level. Since the                                                                                                                                               |

| _       | •••                                                                                                                    | characteristic includes hysteresis, the signal output from the Vo1 pin changes from the low to the high level                                                                                                                                                                         |

|         |                                                                                                                        | when the voltage input on pin Vi1 rises to or above V <sub>REF</sub> +V <sub>HYS</sub> . Refer to the timing diagram on page 4 for                                                                                                                                                    |

|         |                                                                                                                        | details.                                                                                                                                                                                                                                                                              |

|         |                                                                                                                        | Reset signal output pin for reset circuit 2 (the circuit with the delay function). The output is open-drain.                                                                                                                                                                          |

|         |                                                                                                                        | The recommended value for the pull-up resistor ( $R_{L2}$ ) is 3 k to 100 k $\Omega$ . When the voltage input on pin Vi2 falls                                                                                                                                                        |

| 3       | Vo2                                                                                                                    | to or below $V_{REF}$ , the signal output from the $\overline{Vo2}$ pin is changed from the high to the low level. Since the input                                                                                                                                                    |

| 3       | V02                                                                                                                    | characteristic includes hysteresis, the signal output from the $\overline{\text{Vo2}}$ pin changes from the low to the high level when the voltage input on pin Vi2 rises to or above $V_{\text{REF}}$ + $V_{\text{HYS}}$ and the set delay time $T_{\text{DLYO}}$ has elapsed. Refer |

|         |                                                                                                                        | to the timing diagram on page 4 and regulations for state of capacitor $C_D$ electrical discharge and delay time on                                                                                                                                                                   |

|         |                                                                                                                        | page 10 for details.                                                                                                                                                                                                                                                                  |

| 4       | GND                                                                                                                    | GND pin                                                                                                                                                                                                                                                                               |

|         |                                                                                                                        | Pin for connection to the resistor (R <sub>D</sub> ) and capacitor (C <sub>D</sub> ) for setting of the delay time, T <sub>DLY0</sub> . Refer to the Block                                                                                                                            |

|         | Diagram and Typical Application Circuit on page 2 for an example of the connection. The relation by which the          |                                                                                                                                                                                                                                                                                       |

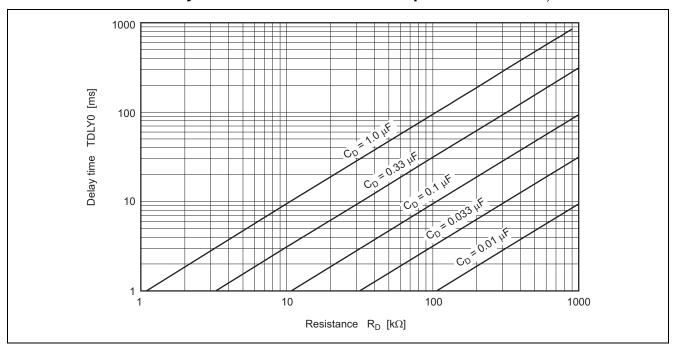

|         |                                                                                                                        | resistance and capacitance set up the delay time can be expressed as $T_{DLY0} = 0.94 \times C_D \times R_D$ . Refer to this                                                                                                                                                          |

| 5       | CD                                                                                                                     | formula in determining the values of resistance and capacitance. Resistance R <sub>D</sub> must use the one within the                                                                                                                                                                |

|         |                                                                                                                        | range of 1 k to 1 M $\Omega$ . Ensure that capacitor $C_D$ has a value no greater than 1.3 $\mu$ F. The dependence of delay                                                                                                                                                           |

|         |                                                                                                                        | time $T_{DLY0}$ on the values of external capacitor $C_D$ and external resistor $R_D$ is illustrated on page 10. To avoid                                                                                                                                                             |

|         |                                                                                                                        | errors due to noise input via the CD pin, this input includes a Schmitt-trigger inverter.  Voltage input pin for reset circuit 2 (the circuit with the delay function). When the input voltage falls to or below                                                                      |

|         |                                                                                                                        | $V_{REF}$ , the signal output from the $\overline{Vo2}$ pin is changed to the low level. Since the input characteristic includes                                                                                                                                                      |

|         |                                                                                                                        | hysteresis, the signal output from the $\overline{\text{Vo2}}$ pin is changed from the low to the high level after the voltage input                                                                                                                                                  |

|         |                                                                                                                        | on pin Vi2 has risen to or above $V_{REF}+V_{HYS}$ and delay time $T_{DLY}$ has elapsed. The reset-threshold voltage is                                                                                                                                                               |

|         |                                                                                                                        | derived from the power-supply voltage V <sub>DD2</sub> according to the division ratio set up by resistors R <sub>S3</sub> and R <sub>S4</sub> as                                                                                                                                     |

| 6       | Vi2                                                                                                                    | described under the block diagram and typical application circuit on page 3. To avoid shifting of the reset                                                                                                                                                                           |

|         |                                                                                                                        | detection voltage being shifted by input current via the Vi2 pin, select a value no greater than 25 k $\Omega$ for parallel                                                                                                                                                           |

|         |                                                                                                                        | resistors R <sub>S3</sub> and R <sub>S4</sub> . Refer to the graph on page 3 for details. Besides, to avoid errors due to noise in power-                                                                                                                                             |

|         |                                                                                                                        | supply voltage V <sub>DD2</sub> , select a capacitor with superior frequency characteristics and connect it between the Vi2                                                                                                                                                           |

|         |                                                                                                                        | and GND pins.                                                                                                                                                                                                                                                                         |

|         |                                                                                                                        | Voltage input pin for reset circuit 1 (the circuit without the delay function). When the input voltage falls to or                                                                                                                                                                    |

|         |                                                                                                                        | below $V_{REF}$ , the signal output from the $\overline{Vo1}$ pin is changed to the low level. Since the input characteristic includes hysteresis, the signal output from the $\overline{Vo1}$ pin is changed from the low to the high level after the                                |

| 7       |                                                                                                                        | voltage input on pin Vi1 has risen to or above $V_{REF}+V_{HYS}$ . The reset-threshold voltage is derived from the                                                                                                                                                                    |

|         | Vi1                                                                                                                    | power-supply voltage $V_{DD1}$ according to the division ratio set up by resistors $R_{S1}$ and $R_{S2}$ as described under the                                                                                                                                                       |

|         |                                                                                                                        | block diagram and typical application circuit on page 3. To avoid shifting of the reset detection voltage being                                                                                                                                                                       |

|         |                                                                                                                        | shifted by input current via the Vi1 pin, select a value no greater than 25 k $\Omega$ for parallel resistors R <sub>S1</sub> and R <sub>S2</sub> .                                                                                                                                   |

|         |                                                                                                                        | Refer to the graph on page 3 for details. Besides, to avoid errors due to noise in power-supply voltage $V_{DD1}$ ,                                                                                                                                                                   |

|         |                                                                                                                        | select a capacitor with superior frequency characteristics and connect it between the Vi2 and GND pins.                                                                                                                                                                               |

| 8       |                                                                                                                        | Power-supply pin for the chip. For stable operation, select a capacitor with superior frequency characteristics                                                                                                                                                                       |

|         |                                                                                                                        | and connect it between the VDD and GND pins and as close to the chip as possible. When selecting the value                                                                                                                                                                            |

|         |                                                                                                                        | of the capacitor, consider aspects of the system environment such as the quality of the power supply. Refer to                                                                                                                                                                        |

|         |                                                                                                                        | the block diagram and typical application circuit on page 3 for details.                                                                                                                                                                                                              |

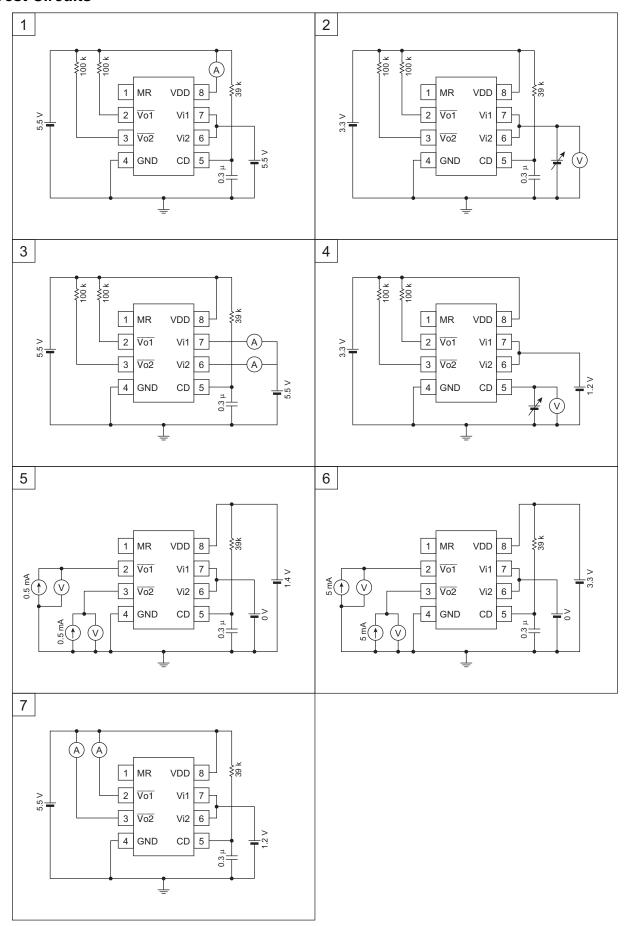

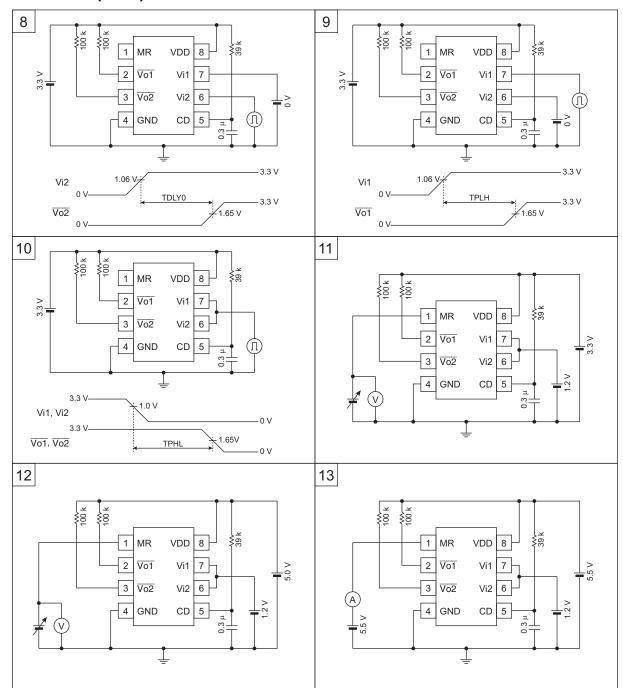

### **Test Circuits**

## **Test Circuits (cont.)**

# Regulations for state of capacitor $\mathbf{C}_{\mathsf{D}}$ electrical discharge and delay time

# Relation between Delay Time $T_{DLY}$ and External Component Values $C_{D,\,}R_{D}$

## **Package Dimensions**

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losse incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the ise of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries. (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

#### SALES OFFICES

#### Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 2801 Scott Boulevard Santa Clara, CA 95050-2549, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited 1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada Tel: +1-905-898-5441, Fax: +1-905-898-3220

Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd. Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tei: +86-10-2035-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333

Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1613, 161F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2856-5688, Fax: +852 2886-9022/9044

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 105-Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 . ipei 10543, Taiwan

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics Korea Co., Ltd. 12F., 234 Teheran-ro, Gangnam-Ku, Seoul, 135-920, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141

© 2014 Renesas Electronics Corporation. All rights reserved.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

NCP304LSQ38T1G NCP304LSQ40T1G NCP304LSQ42T1G NCP304LSQ43T1G NCP304LSQ46T1G NCP305LSQ11T1G NCP305LSQ16T1G NCP305LSQ17T1G NCP305LSQ18T1G NCP305LSQ24T1G NCP305LSQ25T1G NCP305LSQ29T1G NCP305LSQ31T1G NCP305LSQ32T1G NCP308MT250TBG NCP308SN300T1G NCP391FCALT2G NCV303LSN42T1G NCV308SN330T1G CAT1161LI-25-G CAT853STBI-T3 MAX1232CPA MAX705CPA CAT1026LI-30-G CAT1320LI-25-G CAT872-30ULGT3 LA-ispPAC-POWR1014-01TN48E NCP304HSQ18T1G NCP304HSQ29T1G NCP304LSQ27T1G NCP304LSQ29T1G NCP304LSQ45T1G NCP305LSQ35T1G NCP305LSQ35T1G NCP305LSQ37T1G NCP308MT300TBG NCV300LSN36T1G NCV302LSN30T1G NCV303LSN16T1G NCV303LSN22T1G NCV303LSN27T1G NCV30