# **Brief Description**

The SAP5S/SAP51 is a next-generation CMOS integrated circuit for AS-Interface networks. This low-level field bus AS-i (Actuator Sensor Interface) was designed for easy, safe, and cost-effective interconnection of sensors, actuators, and switches. It transports both power and data over the same two-wire unshielded cable.

The SAP5S/SAP51 is used as part of a master or slave node and functions as an interface to the physical bus. It provides the power supply, physical data transfer, and communication protocol handling. The SAP5S/SAP51 is fully compliant with the AS-Interface Complete Specification V3.0. It is function and pin compatible with the SAP4.1 (AS2702).

The SAP5S/SAP51 can be programmed by the user to operate in Standard Slave Mode, Safety Mode (SAP5S only), or Master Mode. The special AS-i Safety Mode (SAP5S only) assures short response times regarding security-related events.

All configuration data are stored in an internal EEPROM that can be easily programmed by a stationary or handheld programming device.

The SAP5S/SAP51 is optimized for harsh environments by its special burst protection circuitry and excellent electromagnetic compatibility.

#### **Features**

- Compliant with the AS-Interface Complete Specification V3.0

- Universal application: slaves, masters, repeaters

- Integrated safety code generator (SAP5S only)

- On-chip electronic inductor: 55mA current drive capability

- Two LED outputs to support all AS-Interface Complete Specification V3.0 status indication modes

- User programmable to operation in Standard Slave Mode, Safety Mode, or Master Mode

- Supports 5.33 and 16 MHz crystals by automatic frequency detection

- Data pre-processing functions

- Clock and communication watchdogs for high system security

#### **Benefits**

- Cost savings due to integrated Safety Code Generator (SAP5S only)

- Special burst protection circuitry

- · Excellent electromagnetic compatibility

# **Physical Characteristics**

- Operational temperature range: -25 to +85°C

- SOP16 and SOP20 package

# **Available Support**

- IDT AS-Interface Programmer Kit USB

- IDT SAP5 Evaluation Board V2.0

## **Related Products**

ASI4U Universal AS-Interface IC

# **SAP5S/SAP51 Basic Application Circuits**

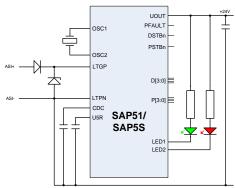

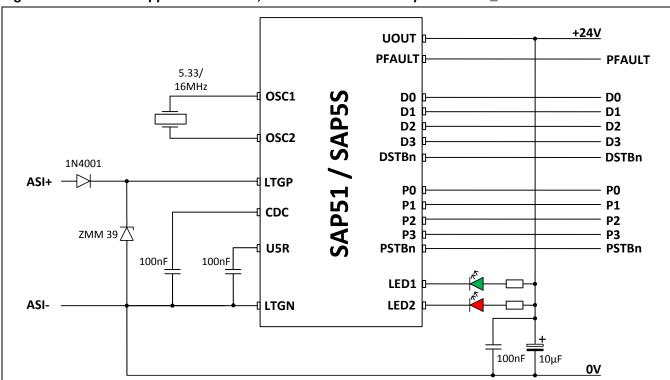

#### Standard Application

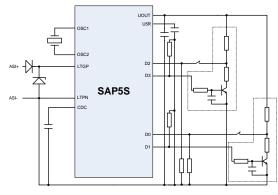

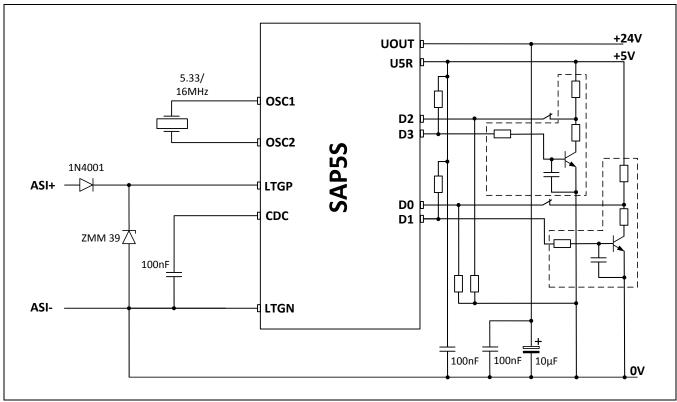

#### Safety Mode Slave Application

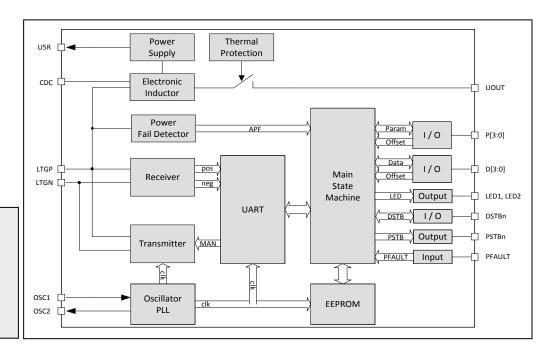

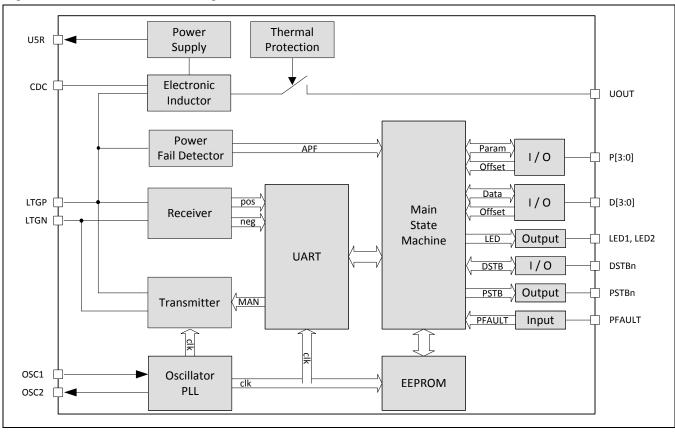

# SAP5S/SAP51 Block Diagram

# **Typical Applications**

- AS-i Master Modules

- AS-i Slave Modules

- AS-i Safety Modules (SAP5S only)

# **Ordering Information**

| Ordering Code | Operating Temperature | Package Type      | RoHS? | Packaging         |  |  |

|---------------|-----------------------|-------------------|-------|-------------------|--|--|

| SAP5SD-A-G1-T | -25°C to +85°C        | SOP20 / 300 mil   | Yes   | Tubes             |  |  |

| SAP51D-A-G1-T | -23 C 10 +63 C        | 30F20 / 300 IIIII | 169   | (37 parts/tube)   |  |  |

| SAP5SD-A-G1-R | 2500 to 10500         | COD20 / 200 il    | V     | Tape and Reel     |  |  |

| SAP51D-A-G1-R | -25°C to +85°C        | SOP20 / 300 mil   | Yes   | (1000 parts/reel) |  |  |

| SAP5SD-B-G1-T | 2500 to 10500         | COD4.0 / 200 mil  | V     | Tubes             |  |  |

| SAP51D-B-G1-T | -25°C to +85°C        | SOP16 / 300 mil   | Yes   | (46 parts/tube)   |  |  |

| SAP5SD-B-G1-R | 0500 1 0500           | 00040 / 000!!     | V     | Tape and Reel     |  |  |

| SAP51D-B-G1-R | -25°C to +85°C        | SOP16 / 300 mil   | Yes   | (1000 parts/reel) |  |  |

# **Contents**

| 1 | Plea | ase   | Read this First                                        | . 7 |

|---|------|-------|--------------------------------------------------------|-----|

|   | 1.1. | Imp   | portant Notice                                         | . 7 |

|   | 1.2. | Silio | con Revision History                                   | . 7 |

| 2 | Gen  | eral  | l Device Specification                                 | . 8 |

|   | 2.1. | Abs   | solute Maximum Ratings (Non-operating)                 | . 8 |

|   | 2.2. | Оре   | erating Conditions                                     | . 9 |

|   | 2.3. | EM    | C Behavior                                             | . 9 |

|   | 2.4. | Qua   | ality Standards                                        | 10  |

|   | 2.5. | Fail  | ure Rate                                               | 10  |

|   | 2.6. | Hur   | midity Class                                           | 10  |

| 3 | Bas  | ic F  | unctional Description                                  | 11  |

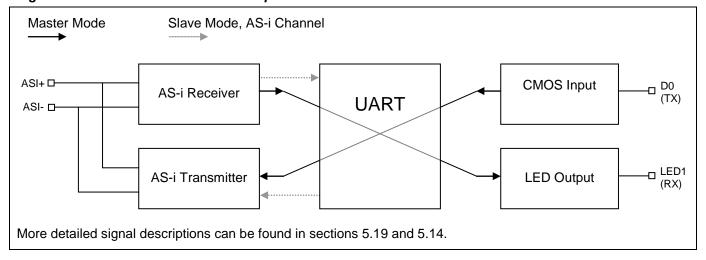

|   | 3.1. | Fun   | nctional Block Diagram                                 | 11  |

|   | 3.2. | Ger   | neral Operational Modes                                | 13  |

|   | 3.2. | 1.    | Slave Mode                                             | 14  |

|   | 3.2. | 2.    | AS-i Communication Channel                             | 14  |

|   | 3.2. | 3.    | Parameter Port Pins                                    | 14  |

|   | 3.2. | 4.    | Data Port Pins                                         | 14  |

|   | 3.2. | 5.    | Data Input Inversion                                   | 15  |

|   | 3.2. | 6.    | Data Input Filtering                                   | 15  |

|   | 3.2. | 7.    | Synchronous Data I/O Mode                              | 15  |

|   | 3.2. | 8.    | 4 Input / 4 Output Processing in Extended Address Mode | 15  |

|   | 3.2. | 9.    | AS-i Safety Mode                                       | 16  |

|   | 3.2. | 10.   | Enhanced LED Status Indication                         | 16  |

|   | 3.2. | 11.   | Communication Monitor/Watchdog                         | 16  |

|   | 3.2. | 12.   | Write Protection of ID_Code_Extension_1                | 16  |

|   | 3.2. | 13.   | Summary of Master Calls                                | 17  |

| 4 | EEF  | PRO   | M                                                      | 20  |

|   | 4.1. | Ove   | erview                                                 | 20  |

|   | 4.2. | Use   | er Area Programming                                    | 21  |

|   |      |       | nware Area Programming                                 |     |

|   | 4.4. | Saf   | ety Area Programming (SAP5S only)                      | 24  |

| 5 | Deta | ailec | d Functional Description                               | 26  |

|   | 5.1. | Pov   | ver Supply                                             | 26  |

|   | 5.1. | 1.    | Voltage Output Pins UOUT and U5R                       | 26  |

|   | 5.1. | 2.    | Input Impedance (AS-Interface Bus Load)                | 27  |

|   | 5.2. | The   | ermal Protection                                       | 28  |

|   | 5.3. | DC    | Characteristics – Digital Inputs                       | 28  |

| 5.4. | DC            | C Characteristics – Digital Outputs                 | 29 |

|------|---------------|-----------------------------------------------------|----|

| 5.5. | AS            | S-i Receiver                                        | 29 |

| 5.6. | AS            | S-i Transmitter                                     | 30 |

| 5.7. | Pa            | rameter Port and PSTBn                              | 30 |

| 5.8. | Da            | ata Port and DSTBn                                  | 32 |

| 5.   | .8.1.         | Timing of Data I/O and DSTBn                        | 32 |

| 5.   | 8.2.          | Input Data Pre-Processing                           | 32 |

| 5.   | 8.3.          | Synchronous Data I/O Mode                           | 34 |

| 5.   | 8.4.          | Support of 4I/4O Signaling in Extended Address Mode | 36 |

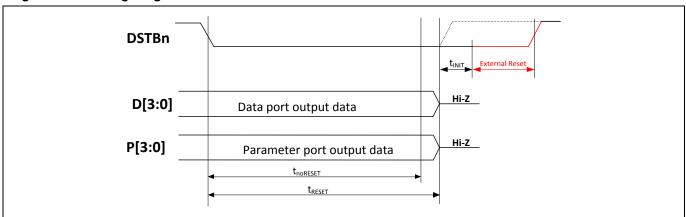

| 5.   | 8.5.          | Special Function of DSTBn                           | 38 |

| 5.9. | Da            | ata and Parameter Port Configuration                | 38 |

| 5.10 | ). Fa         | ult Indication Input PFAULT                         | 39 |

| 5.11 | I. LE         | D Outputs                                           | 40 |

| 5.   | .11.1.        | Slave Mode                                          | 40 |

| 5.   | 11.2.         | Master/Repeater Mode                                | 41 |

| 5.12 | 2. Os         | scillator Pins OSC1 and OSC2                        | 41 |

| 5.13 | B. SA         | NP5 Reset                                           | 41 |

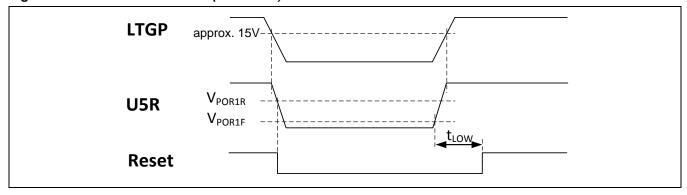

| 5.   | 13.1.         | Power-On Reset                                      | 42 |

| 5.   | 13.2.         | Logic Controlled Reset                              | 43 |

| 5.   | 13.3.         | External Reset                                      | 43 |

| 5.14 | 1. U <i>F</i> | ART                                                 | 43 |

| 5.15 | 5. Ma         | ain State Machine                                   | 45 |

| 5.16 | S. Sta        | atus Registers                                      | 45 |

| 5.17 | 7. Cc         | mmunication Monitor/Watchdog                        | 46 |

| 5.18 | 3. Sa         | fety Mode (SAP5S only)                              | 47 |

| 5.19 | 9. Ma         | aster and Repeater Modes                            | 50 |

| 5.   | 19.1.         | Master/ Repeater Mode Activation                    | 50 |

| 5.   | 19.2.         | Pin Assignment in Master and Repeater Modes         | 51 |

| 5.   | 19.3.         | Functional Description                              | 52 |

| 5.20 | ). W          | rite Protection of ID_Code_Extension_1              | 55 |

| 6 A  | pplica        | ation Circuits                                      | 57 |

| 7 P  | acka          | ge Specifications                                   | 60 |

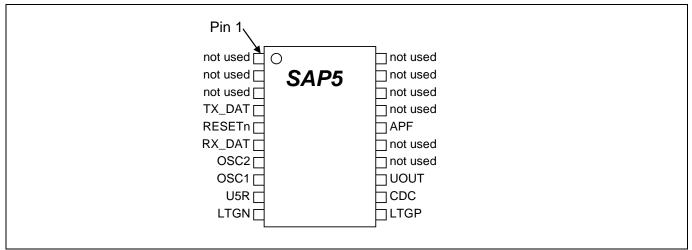

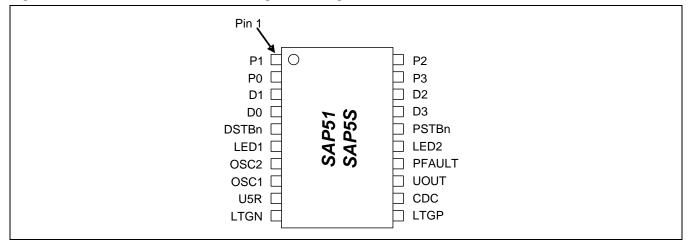

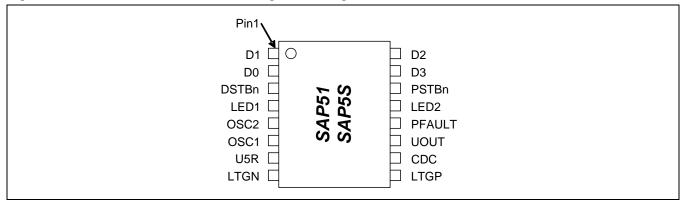

| 7.1. | Pa            | ckage Pin Assignment                                | 60 |

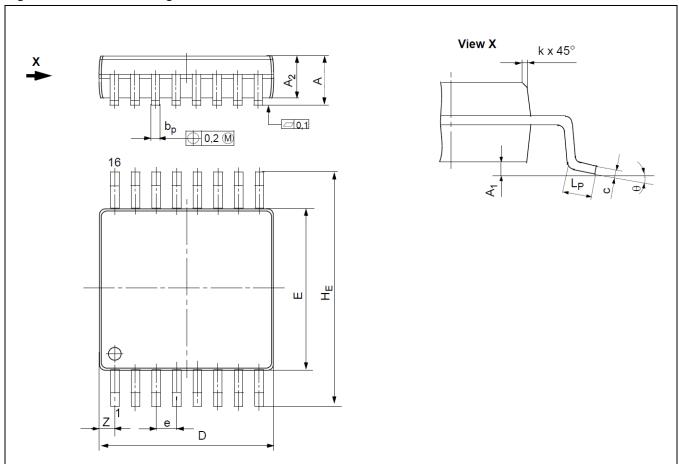

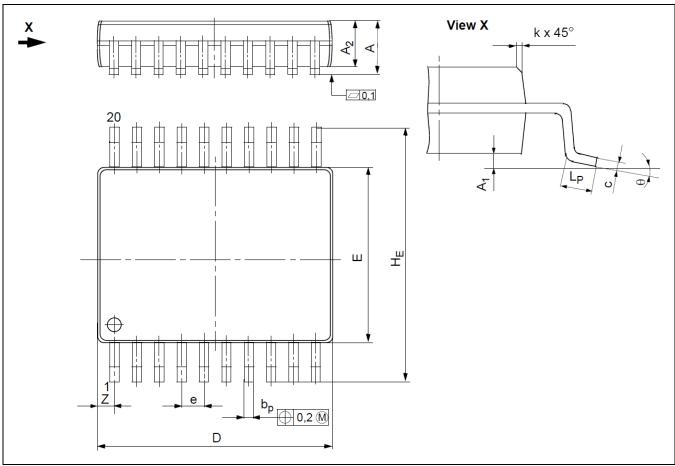

| 7.2. | SC            | DP16 (300 mil) Package Outline                      | 62 |

| 7.3. | SC            | DP20 (300 mil) Package Outline                      | 63 |

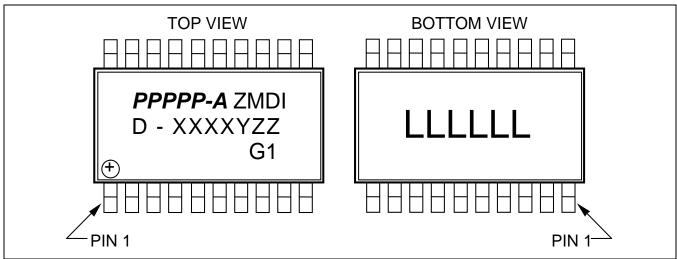

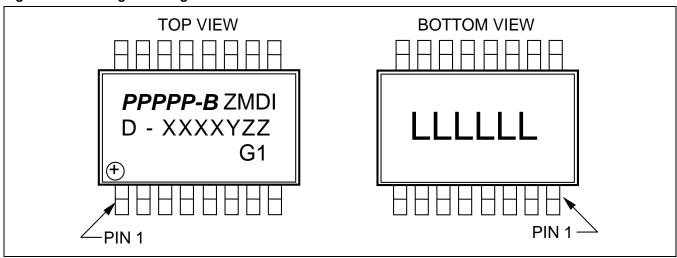

| 7.4. | Pa            | ckage Marking                                       | 64 |

| 8 C  | rderi         | ng Information                                      | 65 |

| 9 R  | elate         | d Documents                                         | 65 |

| 9.1. F     | elated IDT Documents                                                                       | 65 |

|------------|--------------------------------------------------------------------------------------------|----|

| 9.2. F     | elated Third-Party Documents                                                               | 65 |

| 10 Gloss   | ary                                                                                        | 66 |

| 11 Docu    | ment Revision History                                                                      | 66 |

|            |                                                                                            |    |

| List of    | Figures                                                                                    |    |

| Figure 3.1 | Functional Block Diagram                                                                   | 11 |

| Figure 3.2 | Data Path in Master and Repeater Modes                                                     | 14 |

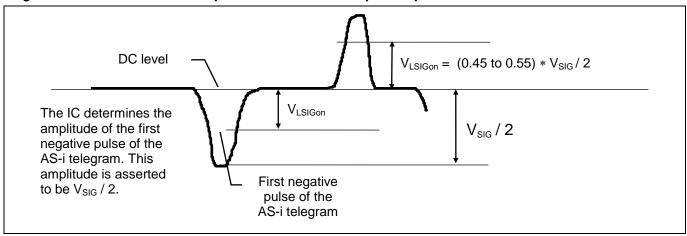

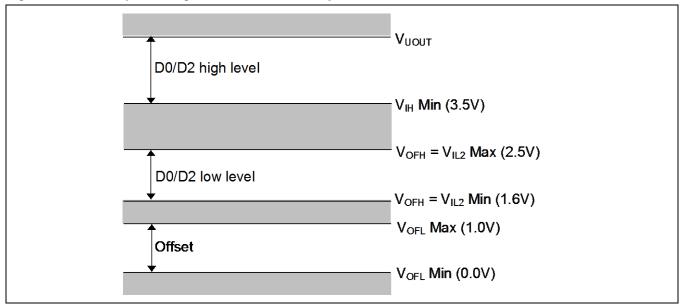

| Figure 5.1 | Basic Receiver Comparator Threshold Set-up Principles                                      | 30 |

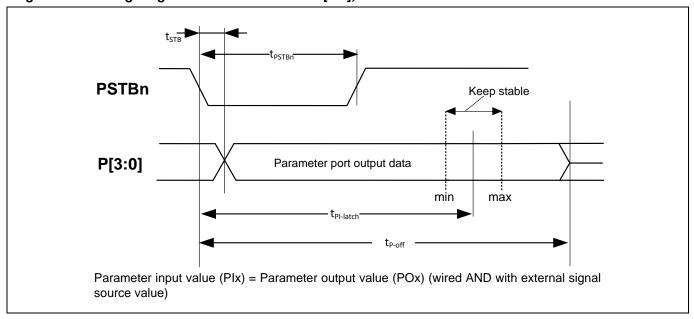

| Figure 5.2 | Timing Diagram for Parameter Port P[3:0], PSTBn                                            | 31 |

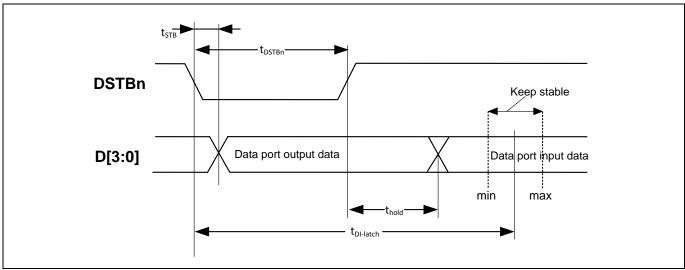

| Figure 5.3 | Timing Diagram for Data Port D[3:0] and DSTBn                                              | 32 |

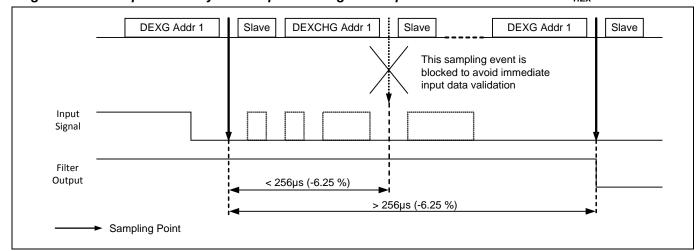

| Figure 5.4 | Principles of Delay Mode Input Filtering – Example for Slave with Address 1 <sub>HEX</sub> | 33 |

| Figure 5.5 | Power-On Behavior (all modes)                                                              | 42 |

| Figure 5.6 | Timing Diagram External Reset via DSTBn                                                    | 43 |

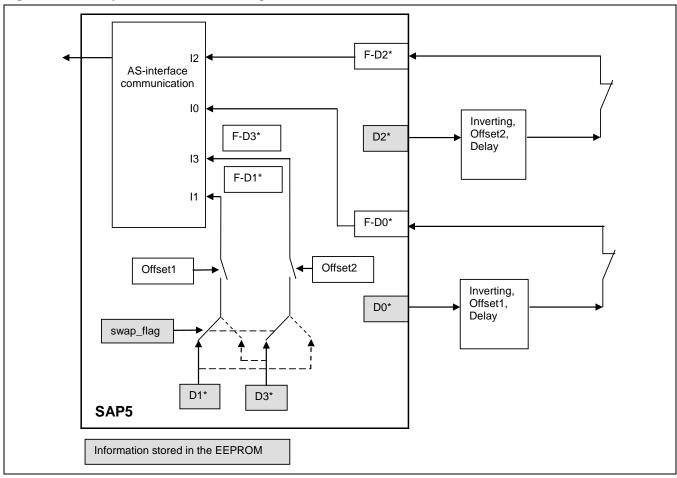

| Figure 5.7 | Safety Mode Data Processing                                                                | 49 |

| Figure 5.8 | Data Input Voltage Constraints in Safety Mode                                              | 50 |

| Figure 5.9 | SAP Package Pin Assignment in Master/Repeater Mode                                         | 51 |

| Figure 6.1 | Standard Application Circuit, Direction of Data I/O Depends on IO_Code                     | 57 |

| Figure 6.2 | Safety Mode Application                                                                    | 58 |

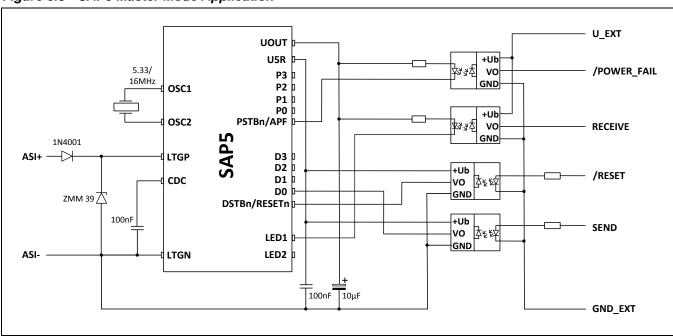

| Figure 6.3 | SAP5 Master Mode Application                                                               | 59 |

| Figure 7.1 | SAP51/SAP5S SOP20 Package Pin Assignment                                                   | 61 |

| Figure 7.2 | · · · · · · · · · · · · · · · · · · ·                                                      |    |

| Figure 7.3 | SOP16 Package Outline Dimensions                                                           | 62 |

| Figure 7.4 | SOP20 Package Outline Dimensions                                                           | 63 |

| Figure 7.5 |                                                                                            | 64 |

| Figure 7.6 | Package Marking 16-Pin Version                                                             | 64 |

|            |                                                                                            |    |

|            |                                                                                            |    |

| List of    | Tables                                                                                     |    |

| Table 2.1  | Absolute Maximum Ratings                                                                   | 8  |

| Table 2.2  | Operating Conditions                                                                       |    |

| Table 2.3  | Crystal Frequency                                                                          |    |

| Table 3.1  | Assignment of Operational Modes                                                            |    |

| Table 3.2  | SAP5 Master Calls and Related Slave Responses                                              |    |

|            | ·                                                                                          |    |

| Table 3.3  | SAP5 Additional Master Calls for Slave Configuration                | 19 |

|------------|---------------------------------------------------------------------|----|

| Table 4.1  | EEPROM Read and Write Times                                         | 20 |

| Table 4.2  | SAP5 EEPROM – User and Firmware Area Content                        | 21 |

| Table 4.3  | SAP5 EEPROM – User and Firmware Area Programming                    | 23 |

| Table 4.4  | SAP5 EEPROM – Safety Area Content                                   | 24 |

| Table 5.1  | Properties of Voltage Output Pins UOUT and U5R                      | 26 |

| Table 5.2  | AS-Interface Bus Load Properties                                    | 27 |

| Table 5.3  | CDC Pin Parameters                                                  | 27 |

| Table 5.4  | Cut-Off Temperature                                                 | 28 |

| Table 5.5  | DC Characteristics of Digital High Voltage Input Pins               | 28 |

| Table 5.6  | DC Characteristics of Digital High Voltage Output Pins              | 29 |

| Table 5.7  | Receiver Parameters                                                 | 29 |

| Table 5.8  | Transmitter Current Amplitude                                       | 30 |

| Table 5.9  | Timing for Parameter Ports                                          | 31 |

| Table 5.10 | Timing for Data Port Outputs                                        | 32 |

| Table 5.11 | Activation of Delay Mode                                            | 33 |

| Table 5.12 | Activation of the Synchronous Data I/O Mode                         | 34 |

| Table 5.13 | Meaning of Master Call Bits I[3:0] with Ext_Addr_4I/4O_Mode = '1'   | 37 |

| Table 5.14 | Data and Parameter Port Configuration for Non-Safety-Mode Operation | 38 |

| Table 5.15 | Data and Parameter Port Configuration in Safety Mode                | 39 |

| Table 5.16 | LED Status Indication                                               | 40 |

| Table 5.17 | Oscillator Pin Parameters                                           | 41 |

| Table 5.18 | SAP5 Initialization Times                                           | 42 |

| Table 5.19 | Power-On Reset (POR) Threshold Voltages                             | 42 |

| Table 5.20 | Timing of External Reset                                            | 43 |

| Table 5.21 | Status Register Content                                             | 45 |

| Table 5.22 | Activation of the SAP5 Communication Watchdog                       | 46 |

| Table 5.23 | Example for Cryptographic Code Table                                | 48 |

| Table 5.24 | Activation of the SAP5 Master/Repeater Mode                         | 51 |

| Table 5.25 | SAP5 Pin Assignment in Master and Repeater Modes                    | 51 |

| Table 5.26 | Functional Differences between SAP5 Master and Repeater Modes       |    |

| Table 5.27 | Programmable Variation of the Loopback Time                         | 53 |

| Table 5.28 | Master/Repeater Mode Parameter                                      |    |

| Table 5.29 | Write Protection of ID_Code_Extension_1                             | 56 |

| Table 7.1  | SAP51/SAP5S Package Pin List                                        | 60 |

| Table 7.2  | SOP16 Package Dimensions (mm)                                       | 62 |

| Table 7.3  | SOP20 Package Dimensions (mm)                                       | 63 |

|            |                                                                     |    |

# 1 Please Read this First

# 1.1. Important Notice

**Important Safety Notice:** This IDT product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support, or life-sustaining equipment, are specifically not recommended without additional mutually agreed upon processing by IDT for such applications.

# 1.2. Silicon Revision History

| Revision | Date           | Technical Changes                                                        | Affected Page in Datasheet |

|----------|----------------|--------------------------------------------------------------------------|----------------------------|

| В        | September 2005 | First marketed silicon version.                                          |                            |

| С        | March 2007     | Modified I <sub>IL</sub> – current range for input low level.            | Table 5.5 on Page 28       |

| С        | March 2007     | Modified Delay Mode activation through parameter port P1.                | Page 33                    |

| С        | March 2007     | Modified Synchronous Data I/O Mode activation through parameter port P2. | Page 35                    |

| С        | March 2007     | Modified Watchdog activation through parameter port P0.                  | Page 46                    |

| С        | March 2007     | Improved burst protection filter and improved ESD behavior.              |                            |

| D        | August 2012    | UART design corrections for End_Bit transmission error detection.        |                            |

|          |                | Improved AS-i telegram pause detection.                                  |                            |

# 2 General Device Specification

**Important note**: The absolute maximum ratings given in section 2.1 are stress ratings only. The SAP5 might not function or be operable above the recommended operating conditions given in section 2.2. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the specifications given under "Absolute Maximum Ratings."

**Important note**: The *operating conditions* given in section 2.2 set the conditions over which IDT specifies device operation. These are the conditions that the application circuit should provide to the device for it to function as intended. Unless otherwise noted, the limits for parameters that appear in the *operating conditions* section are used as test conditions.

## 2.1. Absolute Maximum Ratings (Non-operating)

Table 2.1 Absolute Maximum Ratings

| PARAMETER                                                                                           | SYMBOL                   | MIN  | MAX                     | UNIT |

|-----------------------------------------------------------------------------------------------------|--------------------------|------|-------------------------|------|

| Voltage reference                                                                                   | $V_{LTGN}$               | 0    | 0                       | V    |

| Voltage difference 1) between LTGP and LTGN pins (V <sub>LTGP</sub> - V <sub>LTGN</sub> )           | V <sub>LTGP-LTGN</sub>   | 0    | 40                      | V    |

| Pulse voltage <sup>2), 3)</sup> between LTGP and LTGN (V <sub>LTGP</sub> - V <sub>LTGN</sub> )      | V <sub>LTGP-LTGN_P</sub> | 0    | 50                      | V    |

| Voltage at the CDC, D0, D1, D2, D3, P0, P1, P2, P3, DSTBn, PSTBn, LED1, LED2, PFAULT, and UOUT pins | V <sub>inputs1</sub>     | -0.3 | V <sub>UOUT</sub> + 0.3 | V    |

| Voltage at the OSC1, OSC2, U5R pins                                                                 | V <sub>inputs2</sub>     | -0.3 | 7                       | V    |

| Input current into any pin except supply pins 4)                                                    | I <sub>in</sub>          | -50  | 50                      | mA   |

| Humidity – non-condensing <sup>5)</sup>                                                             | Н                        |      |                         |      |

| Electrostatic discharge 6 – Human Body Model (HBM2)                                                 | V <sub>HBM</sub>         | 1500 |                         | V    |

| Electrostatic discharge 7) – Equipment Discharge Model (EDM)                                        | V <sub>EDM</sub>         | 200  |                         | V    |

| Storage temperature                                                                                 | T <sub>STG</sub>         | -55  | 125                     | °C   |

| Soldering temperature Sn/Pb 8)                                                                      | T <sub>lead</sub>        |      | 240                     | °C   |

| Soldering temperature 100%Sn <sup>8)</sup>                                                          | T <sub>lead</sub>        |      | 260                     | °C   |

| Thermal resistance of SOP 16 package 9)                                                             | R <sub>thj-16</sub>      | 80   | 100                     | K/W  |

| Thermal resistance of SOP 20 package 9)                                                             | R <sub>thj-20</sub>      | 75   | 95                      | K/W  |

- 1) Reverse polarity protection must be performed externally.

- 2)  $V_{LTGP}$ -LTGN and  $V_{LTGP}$ -LTGN\_P must not be violated.

- 3) Pulse with  $\leq 50\mu s$ , repetition rate  $\leq 0.5$  Hz.

- 4) Latch-up resistance, reference pin is 0V.

- Level 4 according to JEDEC-020D is guaranteed.

- 6) HBM: C = 100pF charged to VHBM2 with resistor R = 1.5k $\Omega$  in series, valid for all pins except LTGP-LTGN.

- 7) EDM: C = 200pF charged to VEDM with no resistor in series, valid for LTGP-LTGN only.

- 8) Soldering must comply with the JEDEC-J-STD-020D standard.

- 9) Single layer board,  $P_{tot} = 0.5W$ ; air velocity = 0m/s  $\Rightarrow$  max. value; air velocity = 2.5m/s  $\Rightarrow$  min. value.

## 2.2. Operating Conditions

Table 2.2 Operating Conditions

| Parameter                                      | Symbol            | Conditions                                                                                                                | Min | Max. | Unit |

|------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| Negative supply voltage                        | $V_{LTGN}$        |                                                                                                                           | 0   | 0    | V    |

| DC voltage at LTGP pin 1), 2)                  | $V_{LTGP}$        | Relative to V <sub>LTGN</sub>                                                                                             | 16  | 34   | V    |

| Operating current                              | I <sub>LTGP</sub> | $V_{LTGP} = 30V$ $f_c = 16.000MHz$ No load at any pin; transmitter is turned off; digital state machine is in idle state. |     | 6    | mA   |

| Max. output sink current at pins D[3:0], DSTBn | I <sub>CL1</sub>  |                                                                                                                           |     | 10   | mA   |

| Max. output sink current at pins P[3:0], PSTBn | I <sub>CL2</sub>  |                                                                                                                           |     | 10   | mA   |

| Ambient operating temperature range            | T <sub>amb</sub>  |                                                                                                                           | -25 | 85   | °C   |

<sup>1)</sup> Below V<sub>LTGPmin</sub> the power supply block might not be able to provide the specified output currents at UOUT and U5R.

Table 2.3 Crystal Frequency

| Parameter            | Symbol         | Conditions | Nominal         | Unit |

|----------------------|----------------|------------|-----------------|------|

| Crystal frequency 1) | f <sub>c</sub> |            | 5.333 or 16.000 | MHz  |

<sup>1)</sup> The SAP5 automatically detects whether the crystal frequency is 5.333MHz or 16.000MHz and controls the internal clock circuit accordingly.

#### 2.3. EMC Behavior

The SAP51/SAP5S fulfills the requirements defined in *AS-Interface Complete Specification V3.0* and related test requirements for AS-Interface slave ICs. In addition to the *AS-Interface Complete Specification* and in combination with a reference component circuit, the SAP51/SAP5S achieves a communication failure rate less than 10% of the allowed failure rate according to the "Fast Transient" test method specified in the related AS-Interface association test procedures. The behavior specified above is correct by design and is proven during SAP51/SAP5S characterization.

<sup>2)</sup> Outside of these limits, the send current shape and send current amplitude cannot be guaranteed.

## 2.4. Quality Standards

The quality of the SAP51/SAP5S will be ensured according to the IDT quality standards. IDT is a qualified supplier according to ISO/TS 16949:2002 and ISO 14001:1996.

The following IDT reference documents apply for the development process (available on request; see section 9):

- Management Regulation: 0410 Product Development Procedure

- Process Specification: IDT C7D 0.6µm Technology

Functional device parameters are valid for the device operating conditions specified in section 2.2. Production device tests are performed within the recommended ranges of  $V_{LTGP}$  -  $V_{LTGN}$ ,  $T_{amb}$  = +25°C (+85°C and -25°C on sample basis only) unless otherwise stated.

#### 2.5. Failure Rate

| Symbol | Parameter                | Max. | Unit |

|--------|--------------------------|------|------|

| AQL    | Acceptance Quality Level | 0.1  | %    |

| F55    | Failure Rate at 55°C     | 18   | FIT  |

| F70    | Failure Rate at 70°C     | 60   | FIT  |

| F85    | Failure Rate at 85°C     | 150  | FIT  |

| F125   | Failure Rate at 125°C    | 1400 | FIT  |

# 2.6. Humidity Class

Level 3 humidity tolerance according to JEDEC-020D is guaranteed.

# 3 Basic Functional Description

Note: Unless otherwise noted, the product name SAP5 refers to both the SAP51 and the SAP5S.

The SAP5 is a low-level field bus IC designed for AS-i (Actuator Sensor Interface), which provides a secure interconnection for sensors, actuators, and switches via a two-wire unshielded cable.

The SAP5 is used as part of a master or slave node and functions as an interface to the physical bus. It provides the power supply, physical data transfer, and communication protocol handling. The SAP5 can be programmed by the user to operate in Standard Slave Mode, Safety Mode (SAP5S only), or Master Mode. The special AS-i Safety Mode (SAP5S only) assures short response times regarding security-related events.

Configuration data are stored in a programmable internal EEPROM.

The SAP5 is optimized for harsh environments by its special burst protection circuitry and excellent electromagnetic compatibility.

## 3.1. Functional Block Diagram

Figure 3.1 Functional Block Diagram

Following device functions are handled by the different blocks of the SAP5:

#### **RECEIVER**

The RECEIVE block converts the analog telegram waveform from the AS-i bus to a digital pulse-coded signal that can be processed further by a digital UART circuit.

The RECEIVE block is directly connected to the AS-i line pins LTGP and LTGN. It converts the differential AS-i telegram to a single-ended signal and removes the DC offset by high-pass filtering. To adapt quickly to changing signal amplitudes in telegrams from different network users, the amplitude of the first telegram pulse is measured by a 3-bit flash ADC and the threshold of a positive and a negative comparator is set accordingly to about 50% of the measured level. The comparators generate the *p. pulse* and *n. pulse* signals.

#### **TRANSMITTER**

The transmit block transforms a digital response signal to a correctly shaped send current signal, which is applied to the AS-i bus. Due to the inductive network behavior of the network, the changing send current induces voltage pulses on the network line that overlay the DC operating voltage. The voltage pulses must have sin²-wave shapes; therefore the send current shape must follow the integral of the sin²-wave function.

#### UART / MAIN STATE MACHINE / EEPROM

EEPROM write access and other I/O operations of the Main State Machine are supported in Slave Mode only (see the description of the general SAP5 operational modes below). In Master Mode, the SAP5 is basically equivalent to a physical layer transceiver.

If Slave Mode is activated, the UART demodulates the received telegrams, verifies telegram syntax and timing, and controls a register interface to the Main State Machine. After reception of a correct telegram, the UART generates appropriate Receive Strobe signals, which tell the Main State Machine to start further processing. The Main State Machine decodes the telegram information and starts respective I/O processes or EEPROM access. A second register interface is used to send data back to the UART for construction of a telegram response. The UART modulates the response data into a Manchester-II-coded bit stream that is used to control the TRANSMITTER unit.

# ELECTRONIC INDUCTOR

The electronic inductor is basically a gyrator circuit. It provides an inductive behavior between the SAP5 pins LTGP and UOUT while the inductance is controlled by the capacitor on the CDC pin. The inductor decouples the power regulator of the SAP5 as well as the external load circuit from the AS-i bus and hence prevents crosstalk or switching noise from disturbing the telegram communication on the bus.

The AS-Interface Complete Specification describes the input impedance behavior of a slave module via an equivalent circuit that consists of R, L, and C in parallel. For example, a slave module in Extended Address Mode must have R >  $13.5k\Omega$ , L > 13.5mH, and C < 50pF. The electronic inductor of the SAP5 delivers values that are well within the required ranges for output currents up to 55mA ( $V_{LTGP}$ >24V). More detailed parameters can be found in section 5.1.

The electronic inductor requires an external capacitor of 10µF at the UOUT pin for stability.

# POWER SUPPLY

The power supply block consists of a band-gap referenced 5V-regulator as well as other reverence voltage and bias current generators for internal use. The 5V regulator requires an external capacitor at pin U5R of at least 100nF for stability. It can source up to 4mA for external use, however the power dissipation and the resulting device heating become a major concern if too much current is drawn from the regulator. See section 5.1.

# OSCILLATOR / PLL

The oscillator supports direct connection of 5.333MHz or 16.000MHz crystals with a dedicated load capacity of 12pF and parasitic pin capacities of up to 8pF. The SAP5 automatically detects the oscillation frequency of the connected crystal and controls the internal clock generator circuit accordingly. After power-on reset, the SAP5 is set to 16.000MHz operation by default. After about 200µs, it will either switch to 5.333MHz operation or remain in the 16.000 MHz mode. The frequency detection is active until the first AS-i telegram has been successfully received in order to ensure the SAP5 has found the correct clock frequency setting. The detection result is locked thereafter to increase resistance against burst or other interferences.

The oscillator unit also contains a Clock Watchdog circuit that can generate an unconditioned SAP5 reset if there has been no clock oscillation for more than approximately 20µs. This is to prevent unpredicted SAP5 behavior if the clock signal is lost.

# THERMAL PROTECTION

The SAP5 is self-protected against thermal overload. If the silicon die temperature rises above approximately 140°C for more than 2 seconds, the SAP5 detects thermal overheating, switches off the electronic inductor, performs an SAP5 reset, and sets all analog blocks to power-down mode. The 5V regulator is also turned off in this state; however, there will still remain a voltage of approximately 3 to 3.5 V available at U5R that is derived from the internal start circuitry. If the overtemperature condition is no longer present, the SAP5 resumes operation and performs an initialization.

POWER FAIL DETECTOR

The POWER FAIL DETECTOR observes the voltage at the AS-i line. It signals at the PSTBn/APF pin when the voltage drops below approximately 22.5V. This is active in Master Mode only.

**INPUT STAGE**

All digital inputs, except the oscillator pins, have high voltage capabilities and pull-up features. For more details see sections 5.3, 5.7, 5.8 and 7.1.

**OUTPUT STAGE**

All digital output stages, except the oscillator pins, have high voltage capabilities and are implemented as NMOS open-drain buffers. Each pin can sink up to 10mA of current. See section 5.4.

#### 3.2. General Operational Modes

The SAP5 provides two operational modes: Slave Mode and Master/Repeater Mode. The operational mode that becomes active is defined by programming the flag *Master\_Mode* in the Firmware Area of the EEPROM (also see Table 4.2). The EEPROM is read out at every initialization of the SAP5. Online mode switching is not provided. The configurations in Table 3.1 apply:

Table 3.1 Assignment of Operational Modes

| Selected Operational Mode | Master Mode Flag |

|---------------------------|------------------|

| Slave Mode                | 0                |

| Master/Repeater Mode      | 1                |

In Slave Mode, the SAP5 operates as a fully featured AS-i slave IC according to AS-Interface Complete Specification v3.0.

In Master/Repeater Mode, the SAP5 acts as physical layer transceiver. It translates a digital output signal from the external master control logic (e.g., programmable logic controller (PLC), microprocessor, etc.) to a correctly shaped, analog AS-i pulse sequence and vice versa. Every AS-i telegram received is checked for consistency with the AS-i communication protocol specifications and if no errors were found, an appropriate Receive Strobe signal is generated.

Figure 3.2 shows the different data path configurations.

Figure 3.2 Data Path in Master and Repeater Modes

#### 3.2.1. Slave Mode

The Slave Mode is the most complex operational mode of the SAP5. The SAP5 supports not only all mandatory AS-i slave functions but also a variety of additional features that facilitate the design of AS-i slave modules.

#### 3.2.2. AS-i Communication Channel

The AS-i channel is directly connected to the AS-i bus via the pins LTGP and LTGN. A receiver and a transmitter unit are connected in parallel to the pins, which allows fully bi-directional communication through LTGP and LTGN.

#### 3.2.3. Parameter Port Pins

In the 20-pin package, the SAP5 features a 4-bit wide parameter port (P0, P1, P2, and P3 pins) and a related parameter strobe signal pin PSTBn. AS-Interface Complete Specification V3.0 newly defines a bidirectional mode for parameter data. The SAP5 supports this feature, which can be activated by special EEPROM setting (IO\_Code, see section 5.9).

There is a defined phase relation between a parameter output event, the parameter input sampling, and the activation of the PSTBn signal. Therefore it can be used to trigger external logic or a microcontroller to process the received parameter data or to provide new input data for the AS-i slave response.

See section 5.7 for further details.

#### 3.2.4. Data Port Pins

The SAP5 provides a 4-bit wide data port. The outputs work independently from each other allowing a maximum of 4 output devices to be connected to the SAP5. The directions of the Data Port pins are set through the *IO\_Code*, see section 5.9.

The data port is accompanied by the data strobe signal DSTBn. There is a defined phase relation between a data output event, the input data sampling and the activation of the DSTBn signal. Thus, it can be used to trigger external logic or a microcontroller to process the received data or to provide new input data for the AS-i slave response. See section 5.8 for further details.

#### 3.2.5. Data Input Inversion

By default, the logic signal (HIGH/LOW) that is present at the data input pins during the input sampling phase is transferred without modification to the send register, which is interfaced by the UART. Thus, the signal becomes directly part of the slave response.

Some applications work with inverted logic levels. To avoid additional external inverters, the input signal can be inverted by the SAP5 before transferring it to the send register. The inversion of the input signals can be done jointly for all data input pins. See section 5.8.

## 3.2.6. Data Input Filtering

To prevent input signal bouncing from being transferred to the AS-i master, the data input signals can be digitally filtered. Activation of the filter is done jointly either by EEPROM configuration or by the logic state of parameter port pin P2. For more detailed information, refer to section 5.8.

#### 3.2.7. Synchronous Data I/O Mode

AS-Interface Complete Specification V3.0 newly defines a synchronous data I/O feature, which allows a number of slaves in the network to switch their outputs at the same time and to have their inputs sampled simultaneously. This feature is especially useful if more than 4-bit wide data is to be provided synchronously to an application.

The synchronization point is defined as the data exchange event of the slave with the lowest address in the network. This definition relies on the cyclical slave polling with increasing slave addresses per cycle, which is one of the basic communication principles of AS-i. The SAP5 always monitors the data communication and detects the change from a higher to a lower slave address. If such a change has been recognized, the SAP5 assumes that the slave with the lower address has the lowest address in the network.

There are some special procedures that become active during the start of synchronous I/O mode operation and if more than three consecutive telegrams have been sent to the same slave address. This is described in more detail in section 5.8.3.

#### 3.2.8. 4 Input / 4 Output Processing in Extended Address Mode

A new feature of AS-Interface Complete Specification V3.0 is additional support of 4-bit wide output data in Extended Address Mode. Until AS-Interface Complete Specification V2.11, it was only possible to send three data output bits from the master to the slave in Extended Address Mode because telegram bit I3 was used to select between the A or B slave type for extended slave addressing (up to 62 slaves per network). In normal address mode, bit I3 carries output data for pin D3.

The new definition introduces a multiplexed data transfer so that all 4-bits of the data output port can be used again. A first AS-i cycle transfers the data for a 2-bit output nibble only, and then the second AS-i cycle transfers the data for the complementary 2-bit nibble. Nibble selection is done by the remaining third bit. To ensure continuous alternation of information bit I2 and thus continued data transfer of both nibbles, a special watchdog has been implemented that observes the state of the I2 bit. The watchdog can be activated or deactivated by EEPROM setting. It provides a watchdog filter time of about 327ms.

The multiplexed transfer increases the refresh time per output by a factor of two; however, some applications can tolerate this increase and gain the advantage of less external circuitry and better slave address efficiency. The sampling cycle of the data inputs remains unchanged since the meaning of bit I3 has not been changed in the slave response with the definition of the Extended Address Mode.

More detailed information is given in section 5.8.4.

#### 3.2.9. AS-i Safety Mode

Using the SAP5 Safety Mode makes it easy to implement a safety-related AS-i slave according to the AS-i Safety at Work concept. Slaves complying with the control category 4 according to EN 954 –1 can be implemented even with a minimum of external circuitry.

In Safety Mode, the response of the SAP5 on a *Data\_Exchange* master call (*DEXG*) is different. Instead of responding with the regular input data provided at the data ports, a 4-bit data word from a specific 8\*4 bit code table is transmitted to the master. Cycling the code table is used to transmit another data word with each *DEXG* master call. The data transmission is supervised by a safety monitor.

In Safety Mode, the use of the enhanced data input features described in sections 3.2.5 to 3.2.8 are disabled. In this case, the Safety Mode related inputs act as 3-level inputs. See section 5.18 for further details.

#### 3.2.10. Enhanced LED Status Indication

The SAP5 supports status indication by two LED outputs. More detailed information on the signaling scheme can be found in section 5.11.

## 3.2.11. Communication Monitor/Watchdog

Data and parameter communication is continuously observed by a communication monitor. If neither *Data\_Exchange* nor *Write\_Parameter* calls have been addressed to and received by the SAP5 within a time frame of approximately 41ms, the No Data/Parameter Exchange status is detected and signaled at LED1.

If the respective flags are set in the EEPROM, the communication monitor can also act as a communication watchdog that initiates a complete SAP5 reset after the expiration of the watchdog timer. The watchdog mode can also be activated and deactivated by a signal at parameter port pin P0. For additional detailed information, see section 5.17.

#### 3.2.12. Write Protection of ID\_Code\_Extension\_1

As defined in AS-Interface Complete Specification V3.0 the SAP5 also supports write protection for ID\_Code\_Extension\_1. The feature allows the activation of new manufacturer-protected slave profiles and is enabled by EEPROM setting. It is described in more detail in section 5.20.

## 3.2.13. Summary of Master Calls

Table 3.2 and Table 3.3 on the following pages show the complete set of master calls that are decoded by the SAP5 in Slave Mode. The master calls in Table 3.3 are intended for programming the SAP5 by the slave manufacturer only. They become deactivated as soon as the *Lock\_EE\_PRG* and *Safety\_Program\_Mode\_Disable* flags are set in the Firmware Area of the EEPROM.

The following abbreviations are used in Table 3.2 and Table 3.3 column headings:

ST: Start bitCB: Control bitPB: Parity BitEB: End Bit

Important note regarding full compliance with the AS-Interface Complete Specification: In order to achieve full compliance with the AS-Interface Complete Specification, the Lock\_EE\_PRG flag must be set by the manufacturer of AS-i slave modules during the final manufacturing and configuration process and before an AS-i slave device is delivered to field application users.

# Table 3.2 SAP5 Master Calls and Related Slave Responses

Note: In Extended Address Mode, the "Select Bit" defines whether the A-Slave or B-Slave is being addressed. Depending on the type of n select bit information (Sel) or the inverted select bit information (Sel) in Extended Address Mode. The Extended Address Mode cannot be Lock\_EE\_PRG is at the logic LOW level. Refer to section 4.3 for programming the Lock\_EE\_PRG flag.

|                          |      |    |    |    |    |    | М          | aster l | Reque | st        |     |     |     |    |    |    |    |

|--------------------------|------|----|----|----|----|----|------------|---------|-------|-----------|-----|-----|-----|----|----|----|----|

| Instruction              | Name | ST | СВ | A4 | А3 | A2 | <b>A</b> 1 | Α0      | 14    | 13        | 12  | I1  | 10  | РВ | ЕВ | SB | 13 |

| Data_Exchange            | DEXG | 0  | 0  | A4 | A3 | A2 | A1         | A0      | 0     | D3<br>Sel | D2  | D1  | D0  | PB | 1  | 0  | D: |

| Write_Parameter          | WPAR | 0  | 0  | A4 | A3 | A2 | A1         | A0      | 1     | P3<br>Sel | P2  | P1  | P0  | РВ | 1  | 0  | P; |

| Address_Assignment       | ADRA | 0  | 0  | 0  | 0  | 0  | 0          | 0       | A4    | А3        | A2  | A1  | A0  | PB | 1  | 0  | 0  |

| Write_Extended_ID-Code_1 | WID1 | 0  | 1  | 0  | 0  | 0  | 0          | 0       | 0     | ID3       | ID2 | ID1 | ID0 | PB | 1  | 0  | 0  |

| Delete_Address           | DELA | 0  | 1  | A4 | А3 | A2 | A1         | A0      | 0     | 0<br>Sel  | 0   | 0   | 0   | РВ | 1  | 0  | 0  |

| Reset_Slave              | RES  | 0  | 1  | A4 | A3 | A2 | A1         | A0      | 1     | 1<br>Sel  | 1   | 0   | 0   | РВ | 1  | 0  | 0  |

| Read_I/O-Configuration   | RDIO | 0  | 1  | A4 | A3 | A2 | A1         | A0      | 1     | 0<br>Sel  | 0   | 0   | 0   | РВ | 1  | 0  | Ю  |

| Read_ID-Code             | RDID | 0  | 1  | A4 | А3 | A2 | A1         | A0      | 1     | 0<br>Sel  | 0   | 0   | 1   | РВ | 1  | 0  | ID |

| Read_Extended_ID-Code_1  | RID1 | 0  | 1  | A4 | А3 | A2 | A1         | A0      | 1     | 0<br>Sel  | 0   | 1   | 0   | РВ | 1  | 0  | ID |

| Read_Extended_ID-Code_2  | RID2 | 0  | 1  | A4 | А3 | A2 | A1         | A0      | 1     | 0<br>Sel  | 0   | 1   | 1   | РВ | 1  | 0  | ID |

| Read_Status              | RDST | 0  | 1  | A4 | A3 | A2 | A1         | A0      | 1     | 1<br>Sel  | 1   | 1   | 0   | РВ | 1  | 0  | S  |

| Broadcast (Reset)        | BR01 | 0  | 1  | 1  | 1  | 1  | 1          | 1       | 1     | 0         | 1   | 0   | 1   | 1  | 1  |    |    |

Table 3.3 SAP5 Additional Master Calls for Slave Configuration

|                               |        |    |    |    |    |    | M  | aster | Reque | st |    |    |    |    |    |    |    |

|-------------------------------|--------|----|----|----|----|----|----|-------|-------|----|----|----|----|----|----|----|----|

| Instruction                   | Name   | ST | СВ | A4 | А3 | A2 | A1 | A0    | 14    | 13 | 12 | I1 | 10 | РВ | ЕВ | SB | 13 |

| Set_ID-Code                   | (RDIO) | 0  | 1  | A4 | А3 | A2 | A1 | A0    | 1     | 1  | 0  | 0  | 0  | РВ | 1  | 0  | q  |

| Set_IO_Config                 | (RDID) | 0  | 1  | A4 | А3 | A2 | A1 | A0    | 1     | 1  | 0  | 0  | 1  | РВ | 1  | 0  | q  |

| Set_Extended_ID-Code_2        | (RID1) | 0  | 1  | A4 | А3 | A2 | A1 | A0    | 1     | 1  | 0  | 1  | 0  | РВ | 1  | 0  | q  |

| Set_Control_Code              | (RID2) | 0  | 1  | A4 | А3 | A2 | A1 | A0    | 1     | 1  | 0  | 1  | 1  | РВ | 1  | 0  | q  |

| Set_Control_Code_2            | (RES)  | 0  | 1  | A4 | А3 | A2 | A1 | A0    | 1     | 0  | 1  | 0  | 0  | РВ | 1  | 0  | Q  |

| Enter_Safety_Program_<br>Mode | PRGM   | 0  | 1  | 0  | 0  | 0  | 0  | 0     | 1     | 1  | 1  | 0  | 1  | 1  | 1  |    |    |

## 4 EEPROM

#### 4.1. Overview

The SAP5 features an on-chip EEPROM with typical write and read times according to Table 4.1.

Table 4.1 EEPROM Read and Write Times

| Parameter                                                     | Symbol                 | Min | Max  | Unit |

|---------------------------------------------------------------|------------------------|-----|------|------|

| Initialization read out time 1)                               | t <sub>read_init</sub> |     | 50.0 | μs   |

| Write time after ADRA master request 2)                       | t <sub>wrt_adra1</sub> |     | 38.0 | ms   |

| Write time after ADRA master request 3)                       | t <sub>wrt_adra2</sub> |     | 12.5 | ms   |

| Write time after WID1 master request (user access) 2)         | t <sub>wrt_wid1u</sub> |     | 38.0 | ms   |

| Write time after WID1 master request (manufacturer access) 3) | t <sub>wrt_wid1m</sub> |     | 25.0 | ms   |

| Single cell write time 4)                                     | t <sub>wrt_prgm</sub>  |     | 12.5 | ms   |

<sup>1)</sup> Time includes read out of the configuration block. If running in Safety Mode, the User/Firmware Area and the Safety Area will be read out in parallel.

- 2) The Lock\_EE\_PRG flag is set.

- 3) The Lock\_EE\_PRG flag is not yet set.

- 4) Applies to the programming of data in both Firmware Area and Safety Area.

For security reasons, the memory area is structured in three independent data blocks and a single configuration block containing the *Security\_Flag*. The data blocks are named User Area, Firmware Area, and Safety Area, which are defined in Table 4.2 and Table 4.4.

The Firmware Area contains all manufacturing-related configuration data; e.g., selection of optional features, ID codes, etc. It can be protected against undesired data modification by setting the *Lock\_EE\_PRG* flag to '1'.

The User Area contains only such data that is relevant for changes at the final application (i.e., field installation of slave module). Because the environment where modifications of the user data might become necessary can sometimes be harsh and unpredictable, additional security has been added to the programming of the User Area, ensuring a write access cannot result in an undetected corruption of EEPROM data.

The Safety Area contains the cryptographic code table for the Safety Mode.

The EEPROM cells in the User Area, Firmware Area, and Safety Area have a word width of 6 bits. The sixth bit is not shown in Table 4.2 and Table 4.4. The sixth bit of each cell represents the odd parity of the respective data word, providing an additional data security mechanism. The programming of the parity bit is performed automatically during the EEPROM write process and cannot be influenced by the user. Each EEPROM read process – particularly during initialization of the SAP5 – involves an evaluation of the parity bits. If an incorrect parity bit is found in the User Area, the entire User Area data is treated as corrupted. The SAP5 returns to Slave Address "0" and the *ID\_Code* as well as the *IO\_Code* are set to F<sub>HEX</sub>. If a false parity bit has been found in one or more cells of the Firmware Area or the Safety Area, the status register bit S1 will be set (= '1'), signaling the same state as if the input PFAULT had been set (see section 5.16).

## 4.2. User Area Programming

User Area data can be written by an *ADRA* or *WID1* master request (see Table 3.2). Any such write access is accompanied by two write steps to the *Security\_Flag*, one before and one after the actual modification of user data.

- 1. The following procedure is executed when writing to the User Area of the EEPROM:

- 2. The Security\_Flag is programmed to '1'.

- 3. The content of the Security\_Flag is read back, verifying it was programmed to '1'.

- 4. The user data is modified.

- 5. A read back of the written data is performed.

- 6. If the read back has proven the successful programming of the user data, the Security\_Flag is programmed back to '0'.

- 7. The content of the Security\_Flag is read back, verifying it was programmed to '0'.

Successful execution of the EEPROM write procedure can be observed in the status register contents (refer to Table 5.21). If bit S0 is set (logic HIGH), the write process is not finished yet and the programming data is still volatile. If bit S3 (which is the *Security\_Flag*) is set, the write procedure did not successfully complete either because the write cycle was interrupted or due to an internal error. In order to program the data correctly, the write request should be repeated. The status register can be read using the AS-i master call *Read\_Status* (*RDST*).

In addition to a read out of the data areas, the *Security\_Flag* of the EEPROM is also read and evaluated during SAP5 initialization. If the value of the *Security\_Flag* equals '1' (e.g., due to an undesired interruption of a User Area write access), the entire User Area data is treated as corrupted (see section 5.16). The SAP5 returns to Slave Address "0" and the *ID\_Code* as well as the *IO\_Code* are set to F<sub>HEX</sub>. As a result, the programming of the User Area data can be repeated.

Table 4.2 SAP5 EEPROM – User and Firmware Area Content

| Internal<br>EEPROM<br>Address | Bit Position | EEPROM Cell Contents | Description                                                       |

|-------------------------------|--------------|----------------------|-------------------------------------------------------------------|

| User Area                     |              |                      |                                                                   |

| 0                             | 4 to 0       | A [4:0]              | Slave address                                                     |

| 1                             | 2 to 0       | ID1_Bit [2:0]        | ID_Code_Extension_1 (user-configurable)                           |

|                               | 3            | ID1_Bit3             | ID_Code_Extension_1, A/B slave selection in Extended Address Mode |

|                               | 4            |                      | Not implemented                                                   |

| 2                             | 3 to 0       | ID1_Bit [3:0]        | ID_Code_Extension_1 (manufacturer-configurable)                   |

|                               | 4            |                      | Not implemented                                                   |

| 3                             | 4 to 0       |                      | Not implemented                                                   |

| Internal<br>EEPROM<br>Address | Bit Position | EEPROM Cell Contents          | Description                                                                                                                                          |

|-------------------------------|--------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Firmware A                    | rea          |                               |                                                                                                                                                      |

| 4                             | 4            | Synchronous_Data_IO           | Synchronized Data I/O Mode                                                                                                                           |

|                               | 3 to 0       | ID_Bit [3:0]                  | ID_Code                                                                                                                                              |

| 5                             | 4            | Inhibit_Write_ID1             | <pre>ID_Code_Extension_1 is manufacturer configurable; refer to<br/>section 5.20</pre>                                                               |

|                               | 3 to 0       | ID2_Bit [3:0]                 | ID_Code_Extension_2                                                                                                                                  |

| 6                             | 4            |                               | If flag is set, the logic value at the parameter pin P1 determines whether the <i>Delay_Mode</i> function is active or inactive; refer to Table 5.11 |

|                               | 3 to 0       | IO_Bit [3:0]                  | IO_Code                                                                                                                                              |

| 7                             | 4            | Lock_EE_PRG                   | Programming of the EEPROM Firmware region is possible as long as this flag is <b>not</b> set (logic LOW).                                            |

|                               | 3            | Delay_Mode                    | Activates the <i>Delay_Mode</i> function, refer to Table 5.11                                                                                        |

|                               | 2            | Invert_Data_In                | All Data Port inputs are inverted.                                                                                                                   |

|                               | 1            | Inhibit_BR01                  | If flag is set, the master call BR01 is not executed.                                                                                                |

|                               | 0            | Inhibit_Watchdog              | If flag is set, the watchdog is <b>not</b> activated.                                                                                                |

| 8                             | 4            | P2_Sync_Activation            | The Synchronized Data I/O Mode can be activated by parameter bit P2 as described in Table 5.12.                                                      |

|                               | 3            | Ext_Addr_4I/4O_Mode           | 4 Input/ 4 Output Mode in Extended Address Mode                                                                                                      |

|                               | 2            | Parallel_Out_4l/4O            | Enables the parallel data output option in Extended Address 4I/4O Mode                                                                               |

|                               | 1            | Master_Mode                   | Master / Repeater Mode Flag                                                                                                                          |

|                               | 0            | P0_Watchdog_Activation        | The watchdog can be enabled / disabled by the logic value at the parameter pin P0                                                                    |

| 9                             |              |                               |                                                                                                                                                      |

| 10                            | 4 to 0       | Analog circuitry trim informa | tion                                                                                                                                                 |

| 11                            |              |                               |                                                                                                                                                      |

## 4.3. Firmware Area Programming

In order to program one of the 5-bit cells in addresses 4 to 8 in the Firmware Area, a special master call according to Table 4.3 must be applied, followed immediately by a *DEXG* or *WPAR* call. Write access to the Firmware Area is possible as long as the *Lock\_EE\_PRG* flag is not set. The write procedure is started after receipt of the *DEXG/WPAR* call. Completion of the write procedure can be observed at the status register S0 as described in section 4.2.

The analog circuitry trim information (address 9 to 11) can be written by special test mode operation only.

It is not possible to read out the EEPROM data directly. However, AS-i-related configuration data such as *ID\_Code* can be read by the respective *Read\_ID\_Code* (*RDID*) master request.

Table 4.3 SAP5 EEPROM – User and Firmware Area Programming

Note: See table notes at the end of the table.

| Internal<br>EEPROM<br>Address | EEPROM Cell Content | Programming Master Calls |                                                                    |  |  |  |  |

|-------------------------------|---------------------|--------------------------|--------------------------------------------------------------------|--|--|--|--|

| User Area                     |                     |                          |                                                                    |  |  |  |  |

| 0                             | A[4:0]              | [4:0] ADRA master call   |                                                                    |  |  |  |  |

| 1                             | ID1_Bit [3:0]       | <i>WID1</i> m            | aster call                                                         |  |  |  |  |

| 2                             | ID1_Bit [3:0]       |                          |                                                                    |  |  |  |  |

| 3                             | Not implemented     |                          |                                                                    |  |  |  |  |

| Firmware A                    | rea                 |                          |                                                                    |  |  |  |  |

| 4                             | Synchronous_Data_IO | 14                       | Set ID Code (RDIO) master call 1) + DEXG/WPAR master call 2)       |  |  |  |  |

|                               | ID_Bit [3:0]        | 13 to 10                 |                                                                    |  |  |  |  |

| 5                             | Inhibit_Write_ID1   | 14                       | Set ID Code 2 (RID1) master call 1) + DEXG/WPAR master call 2)     |  |  |  |  |

|                               | ID2_Bit [3:0]       | 13 to 10                 |                                                                    |  |  |  |  |

| 6                             | P1_Delay_Activation | 14                       | Set IO Config (RDID) master call 1) + DEXG/WPAR master call 2)     |  |  |  |  |

|                               | IO_Bit [3:0]        | 13 to 10                 |                                                                    |  |  |  |  |

| 7                             | Lock_EE_PRG         | 14                       | Set Control Code (RID2 ) master call 1) + DEXG/WPAR master call 2) |  |  |  |  |

|                               | Delay_Mode          | 13                       |                                                                    |  |  |  |  |

|                               | Invert_Data_In      | I2                       |                                                                    |  |  |  |  |

|                               | Inhibit_BR01        | I1                       |                                                                    |  |  |  |  |

|                               | Inhibit_Watchdog    | 10                       |                                                                    |  |  |  |  |

| Internal<br>EEPROM<br>Address | EEPROM Cell Content               |          | Programming Master Calls                                                               |

|-------------------------------|-----------------------------------|----------|----------------------------------------------------------------------------------------|

| 8                             | P2_Sync_Activation                | 14       | Set Control Code 2 (RES) master call <sup>1</sup> + DEXG/WPAR master call <sup>2</sup> |

|                               | Ext_Addr_4I/4O_Mode               | 13       |                                                                                        |

|                               | Parallel_Out_4l/4O                | 12       |                                                                                        |

|                               | Master_Mode                       | I1       |                                                                                        |

|                               | P0_Watchdog_Activation            | 10       |                                                                                        |

| 9                             |                                   |          |                                                                                        |

| 10                            | Analog circuitry trim information | Accessil | ole by IDT only                                                                        |

| 11                            |                                   |          |                                                                                        |

<sup>1)</sup> According to Table 3.3.

# 4.4. Safety Area Programming (SAP5S only)

The Safety Area contains the cryptographic code table, which consists of 8 data words and one swap-flag each (refer to section 5.18 for an explanation of the SAP5 Safety Mode). Similar to the Firmware Area, it can be protected against undesired data modification by setting the Safety\_Program\_Mode\_Disable flag; see address 31 in Table 4.4.

**NOTE**: Once the Safety\_Program\_Mode\_Disable flag is set, the Safety Area of the EEPROM is permanently locked; i.e., write access to the Safety Area as described in Table 4.4 is possible only as long as the Safety\_Program\_Mode\_Disable flag is not set.

Table 4.4 SAP5 EEPROM – Safety Area Content

| Logical<br>EEPROM<br>Address | Bit<br>Position | EEPROM Cell Content | Description                              |

|------------------------------|-----------------|---------------------|------------------------------------------|

| 1                            | 4               | S_flag_0            | Swap-flag 0                              |

|                              | 3 to 0          | DI_S0 [3:0]         | Data Input word 0 from Safety Code Table |

| 2                            | 4               | S_flag_1            | Swap-flag 1                              |

|                              | 3 to 0          | DI_S1 [3:0]         | Data Input word 1 from Safety Code Table |

| 3                            | 4               | S_flag_2            | Swap-flag 2                              |

|                              | 3 to 0          | DI_S2 [3:0]         | Data Input word 2 from Safety Code Table |

| 4                            | 4               | S_flag_3            | Swap-flag 3                              |

|                              | 3 to 0          | DI_S3 [3:0]         | Data Input word 3 from Safety Code Table |

| 5                            | 4               | S_flag_4            | Swap-flag 4                              |

|                              | 3 to 0          | DI_S4 [3:0]         | Data Input word 4 from Safety Code Table |

<sup>2)</sup> According to Table 3.2 with information bits corresponding to the left column; DEXG if I4 = '0', WPAR if I4 = '1'. Note: In contrast to regular WPAR/DEXG calls, the slave always returns the received data bits I3 to I0 for these master calls.

| Logical<br>EEPROM<br>Address | Bit<br>Position | EEPROM Cell Content         | Description                                          |

|------------------------------|-----------------|-----------------------------|------------------------------------------------------|

| 6                            | 4               | S_flag_5                    | Swap-flag 5                                          |

|                              | 3 to 0          | DI_S5 [3:0]                 | Data Input word 5 from Safety Code Table             |

| 7                            | 4               | S_flag_6                    | Swap-flag 6                                          |

|                              | 3 to 0          | DI_S6 [3:0]                 | Data Input word 6 from Safety Code Table             |

| 8                            | 4               | S_flag_7                    | Swap-flag 7                                          |

|                              | 3 to 0          | DI_S7 [3:0]                 | Data Input word 7 from Safety Code Table             |

| 31                           | 1               | Safety_Mode_Enable          | If set, Safety Mode is enabled                       |

|                              | 0               | Safety_Program_Mode_Disable | If set, Safety Area is protected against overwriting |

Similar to the Firmware Area programming, Safety Area programming is intended to be used only during production set-up of a slave component at the manufacturer's site. Write access to the Safety Area of the EEPROM is possible in the Safety Program Mode. It can be entered only if the Safety\_Program\_Mode\_Disable flag is not yet set to '1' and if the slave address has been set to 0<sub>HEX</sub>. If the slave address equals 0<sub>HEX</sub>, the reception of the Enter\_Program\_Mode\_Safety (PRGM) call sets the SAP5 device into the Safety Program Mode. It should be noted that no response is generated to the Enter\_Program\_Mode\_Safety call (refer to the AS-Interface Complete Specification).

In the Safety Program Mode, the *Write\_Parameter (WPAR)* and *Data\_Exchange (DEXG)* calls are used to transfer data words to the EEPROM similar to the Firmware Area write procedure described in section 4.3. However, the address bits A[4:0] of the master telegrams are used to address one of the memory locations of the EEPROM (refer to Table 4.4). The information bits I[4:0] (normally used for output data) carry the data to be stored.

Any WPAR or DEXG call initializes an autonomous write process within the SAP5. The status of the write process can be monitored by evaluating the status register of the SAP5 as described in section 4.1. Since the SAP5 is still in Safety Program Mode, the address within the Read\_Status master call has the "don't care" status. In order to execute as many write procedures as desired, do not leave the Safety Program Mode until finished.

Note: The SAP5 will leave the Safety Program Mode and start its initialization procedure if it receives a Reset\_Slave (RES) master call to any desired slave address.

Any attempt to access one of the unavailable EEPROM address locations (0, 9 to 30) of the Safety Area via a Write\_Parameter (WPAR) or Data\_Exchange (DEXG) command will be ignored.

There is no direct read access to the Safety Area data in Safety Program Mode.

After programming the Safety Area, an EEPROM verification procedure should be performed; i.e., by performing one complete AS-i safety cycle (8 *DEXG* calls at intervals of at least 250µs) in Safety Mode operation.

# 5 Detailed Functional Description

## 5.1. Power Supply

The power supply block provides a sensor supply, which is inductively decoupled from the AS-i bus voltage, at the UOUT pin. The decoupling is realized by an electronic inductor circuit, which basically consists of a current source and a controlling low pass filter. The time constant of the low pass, which affects the resulting input impedance at the LTGP pin, can be adjusted by an external capacitor at the CDC pin.

A second function of the power supply block is to generate a regulated 5V supply for operation of the internal logic and some of the analog circuitry. The voltage is provided at the U5R pin and can be used to supply external circuitry as well if the current requirements stay within in the specified limits (see Table 2.2). Because the 5V supply is generated from the decoupled sensor supply at UOUT, the current drawn at U5R must be subtracted from the total available load current at UOUT.

The power supply dissipates most of the power (see Table 5.1):

$$P_{tot} = V_{DROP} * (I_{UOUT} + I_{5V}) + (V_{UOUT} - 5V) * I_{5V}$$

In total, the power dissipation must not exceed the specified values in section 2.1.

To cope with fast internal and external load changes (spikes), external capacitors at UOUT and U5R are required. The LTGN pin defines the ground reference voltage for both UOUT and U5R.

#### 5.1.1. Voltage Output Pins UOUT and U5R

Table 5.1 Properties of Voltage Output Pins UOUT and U5R

| PARAMETER                                                | SYMBOL             | CONDITIONS                     | MIN                                      | MAX                                      | UNIT |

|----------------------------------------------------------|--------------------|--------------------------------|------------------------------------------|------------------------------------------|------|

| Positive supply voltage for SAP5 operation 1)            | $V_{LTGP}$         |                                | 16                                       | 34                                       | V    |

| Voltage drop from LTGP pin to UOUT pin                   | $V_{DROP}$         | V <sub>LTGP</sub> > 22V        | 5.2                                      | 7.8                                      | ٧    |

| UOUT output supply voltage                               | V <sub>UOUT</sub>  | $I_{UOUT} = I_{UOUTmax}$       | V <sub>LTGP</sub> - V <sub>DROPmax</sub> | V <sub>LTGP</sub> - V <sub>DROPmin</sub> | V    |

| UOUT output voltage pulse deviation 2)                   | $V_{UOUTp}$        | C <sub>UOUT</sub> = 10µF       |                                          | 1.5                                      | V    |

| UOUT output voltage pulse deviation width 2)             | t <sub>UOUTp</sub> | C <sub>UOUT</sub> = 10µF       |                                          | 2                                        | ms   |

| 5V supply voltage                                        | $V_{U5R}$          |                                | 4.75                                     | 5.25                                     | V    |

| UOUT output supply current                               | I <sub>UOUT</sub>  | $I_{U5R} = 0$ $V_{LTGP} > 24V$ | 0                                        | 55                                       | mA   |

| U5R output supply current                                | I <sub>U5R</sub>   |                                | 0                                        | 4                                        | mA   |

| Total output current I <sub>UOUT</sub> + I <sub>5V</sub> | Io                 |                                |                                          | 60                                       | mA   |

| Blocking capacitance at UOUT                             | C <sub>UOUT</sub>  |                                | 10                                       | 470                                      | μF   |

| Blocking capacitance at U5R                              | C <sub>U5R</sub>   |                                | 100                                      |                                          | nF   |

<sup>1)</sup> Parameter is also given in Table 2.2.

<sup>2)</sup>  $C_{UOUT} = 10\mu F$ ; output current switches from 0 to  $I_{UOUTmax}$  and vice versa.

# 5.1.2. Input Impedance (AS-Interface Bus Load)

Table 5.2 AS-Interface Bus Load Properties

| PARAMETER                                                                            | SYMBOL           | CONDITIONS | MIN  | MAX                   | UNIT |

|--------------------------------------------------------------------------------------|------------------|------------|------|-----------------------|------|