# RENESAS

# DATASHEET

## TW2837

### 4-Channel Video and Audio Controller for Security Applications

FN7742 Rev. 1.00 August 28, 2012

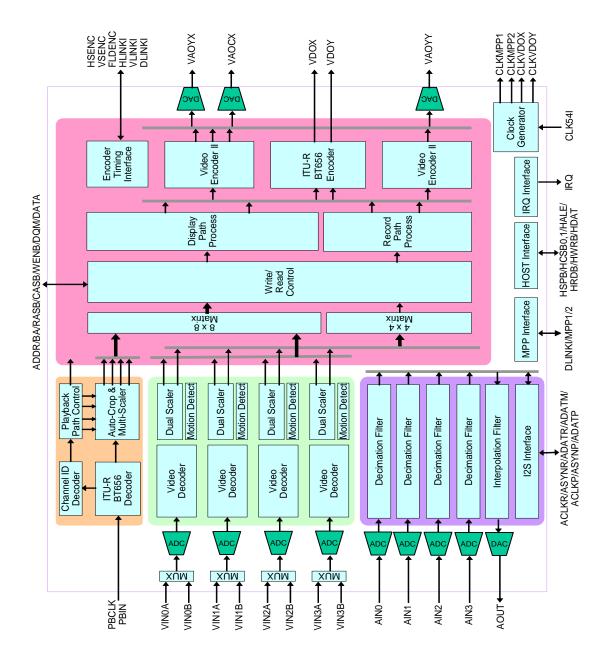

The TW2837 has four high quality NTSC/PAL video decoders, dual color display controllers and dual video encoders. The TW2837 contains four built-in analog anti-aliasing filters, four 10-bit Analog-to-Digital converters, and proprietary digital gain/clamp controller, high quality Y/C separator to reduce crossnoise and high performance free scaler. Four built-in motion, blind and night detectors can increase security system feature.

#### The TW2837 has flexible video

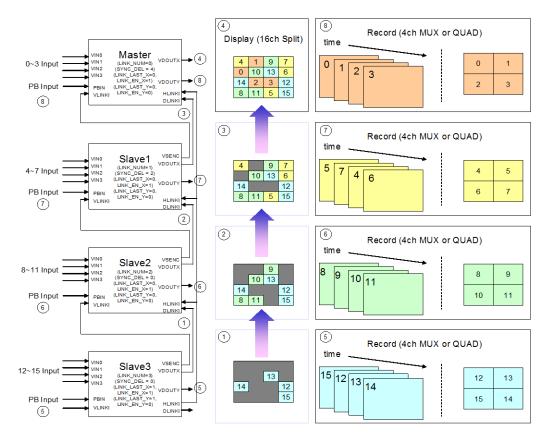

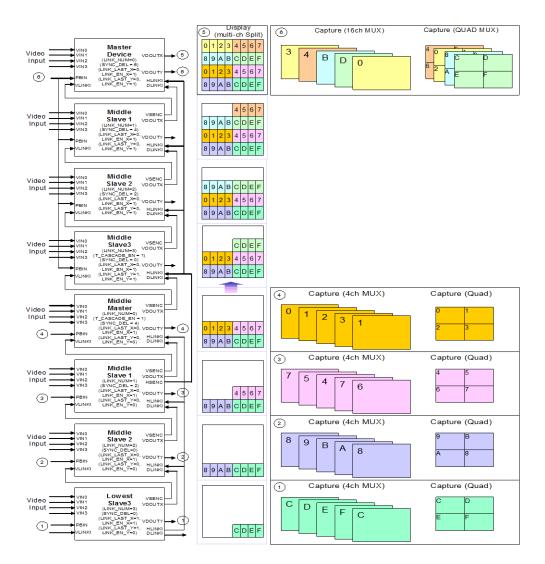

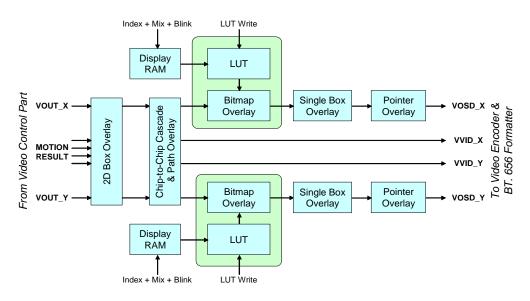

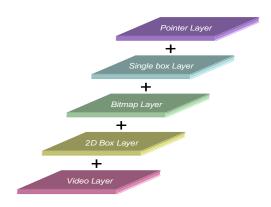

display/record/playback controller including basic display and MUX functions. The TW2837 also has excellent graphic overlay function, which displays bitmap for OSD, single box, 2D array box, and mouse pointer. The built-in channel ID CODEC allows auto decoding and displaying during playback and the additional scaler on the playback supports multicropping function of the same field or frame image. The TW2837 contains two video encoders with three 10-bit Digital-to-Analog converters to provide 2 composite or S-video. The TW2837 also includes audio CODEC that has four audio Analog-to-Digital converters and one Digital-to-Analog converter. A built-in audio controller can generate digital outputs for recording/mixing and accepts digital input for playback. The TW2837 can be extended up to 8/16 channel video controller using chip-to-chip cascade connection.

## **Features**

#### FOUR VIDEO DECODERS

- $\bullet$  Accepts all NTSC(M/N/4.43) / PAL(B/D/G/H/I/K/L/M/N/60) standards with auto detection

- Integrated four video analog anti-aliasing filters and 10-bit CMOS ADCs

- High performance adaptive 4H comb filters for all NTSC/PAL standards

- IF compensation filter for improvement of color demodulation

- Color Transient Improvement (CTI)

- Automatic white peak control

- Programmable hue, saturation, contrast, brightness and sharpness

- Proprietary fast video locking system for non-realtime application

- High performance horizontal and vertical scaler for each path including playback input

- Four built-in motion detectors with 16X12 cells and blind and night detectors

- Additional digital input for playback with ITU-R BT.656 standard

- Auto cropping / strobe for playback input with Channel ID decoder

- Supports four channel full D1 record mode

#### **DUAL VIDEO CONTROLLERS**

- Supports full triplex function with 4 Ch live, 4 Ch playback display and 4 Ch record output

- Analog/Digital channel ID CODEC for record and playback applications

- Supports adaptive median filter for Record

- Supports pseudo 8 channel and/or dual page mode Horizontal/Vertical mirroring for each channel

- Last image captured when video-loss detected

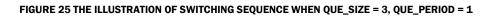

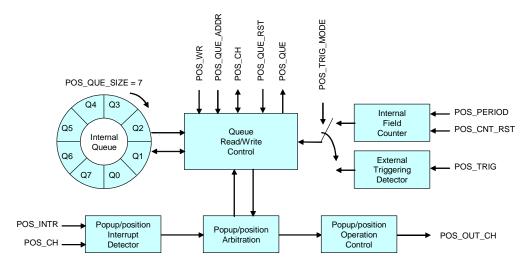

- Auto sequence switch with 128 queues and/or manual switch by interrupt for record path

- Channel skip in auto sequence switch for record path when video-loss detected

- Image enhancement for zoomed or still image in display path

- High performance 2X zoom to horizontal and vertical direction for display path

- Extendable up to 8/16 channel video controller using cascade connection

- Quad MUX switch with 32 queues and/or manual control by interrupt for record path

- 256 color bitmap OSD overlay with 720x480 in NTSC / 720x588 resolution in PAL

- Four programmable single boxes and four 2D arrayed boxes overlay

- Mouse pointer overlay

#### **DUAL VIDEO ENCODERS**

- Dual path digital outputs with ITU-R BT.656 standard

- Dual path analog outputs with all analog NTSC/PAL standards

- Programmable bandwidth of luminance and chrominance signal for each path

- Three 10-bit video CMOS DACs

#### **AUDIO CODEC**

- Integrated four audio ADCs and one audio DAC

- Provides multi-channel audio mixed analog output

- Supports a standard I<sup>2</sup>S interface for record output and playback input

- PCM 8/16-bit and u-Law/A-Law 8-bit for audio word length

- Programmable audio sample rate that covers popular frequencies of 8/16/32/44.1/48kHz

### **Changes from TW2835**

TW2837 is very similar to its previous version chip TW2835. The changes are as follows.

- Provides higher quality video picture with a complete re-design of front-end video decoders

- Provides a new audio decoder with better audio quality and also an extra audio PLL for accurate 8kHz/16kHz sampling rate

- An enhanced OSD with 256 color look up table

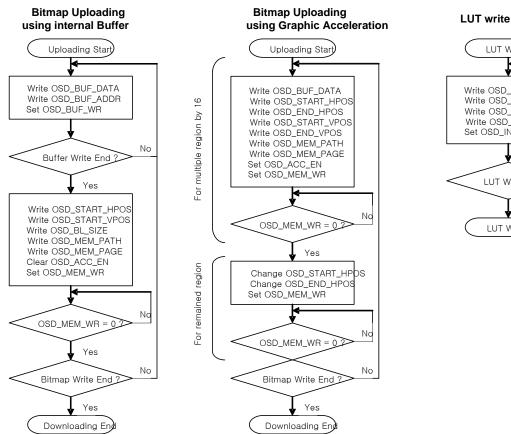

- Provides OSD Block Move / Block Fill / Bitmap Burst Write function to enhance the OSD buffer write performance. With these functions, MCU is relieved from filling the OSD buffer pixel by pixel, therefore achieving much faster OSD buffer update rate

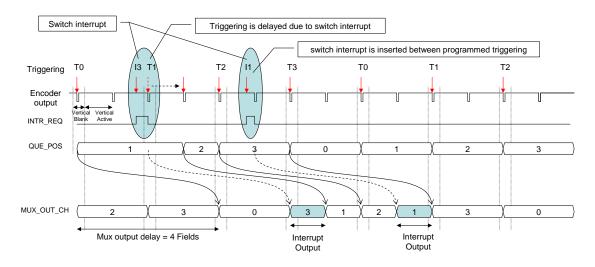

- Maintains backward compatibility to TW2835 on the OSD features. All previous OSD control registers are still available. To use the new feature, however, the SAVE/RECALL feature is limited to 3 frames / 6 fields rather than 4 frames / 8 fields as was in TW2835

## **Applications**

- Analog QUAD/MUX System

- 4/8/16 Channel DVR System

- Car Rear Vision System

- Hair Shop System

- Dental Care System

## **Table of Contents**

| Order Information5                         |

|--------------------------------------------|

| Block Dlagram                              |

| Pin Description7                           |

| Analog Interface Pins7                     |

| Digital Video Interface Pins8              |

| Multi-purpose Pins9                        |

| Digital Audio Interface Pins9              |

| Memory Interface Pins10                    |

| System Control Pins11                      |

| Power / Ground Pins12                      |

| Pin Diagram13                              |

| 208 QFP Pin Diagram (Top -> Bottom View)13 |

| 256 LBGA Pin Diagram (Top->Bottom View)14  |

| Functional Description15                   |

| Video Input15                              |

| Analog Video Inputs16                      |

| Video Input Formats16                      |

| Analog Video Frontend17                    |

| Video Decimation Filter18                  |

| Automatic Gain Control and Clamping18      |

| Sync Processing18                          |

| Y/C Separation19                           |

| Color Decoding20                           |

| Chrominance Processing21                   |

| Luminance Processing21                     |

| Digital Video Input23                      |

| Digital Video Input Format23               |

| Channel ID Decoder24                       |

| Cropping and Scaling Function25            |

| Cropping Function for Live25               |

| Scaling Function for Live26                |

| Cropping and Scaling Function for Playback |

| Motion Detection31                         |

| Mask and Detection Region Selection32      |

| Sensitivity Control                        |

| Level Sensitivity33                        |

| Spatial Sensitivity33                      |

| Temporal Sensitivity33                     |

| Velocity Control                           |

| Blind Detection                            |

| Night Detection                            |

| Video Control                               |

|---------------------------------------------|

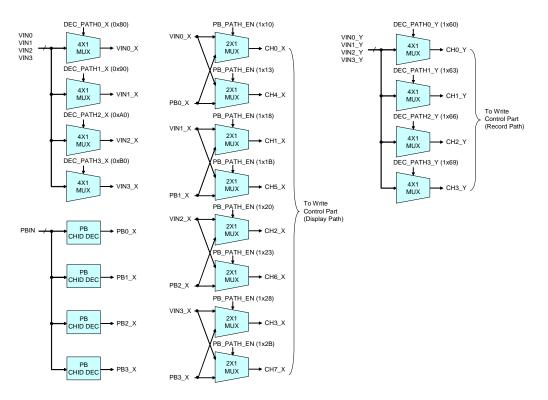

| Channel Input Selection                     |

| Channel Operation Mode                      |

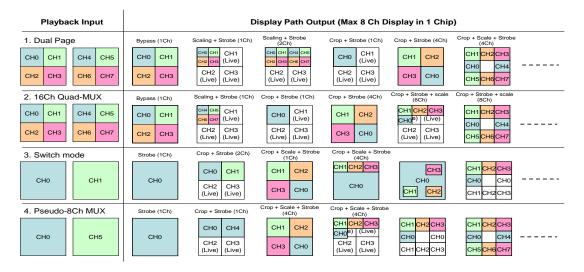

| Live Mode 39                                |

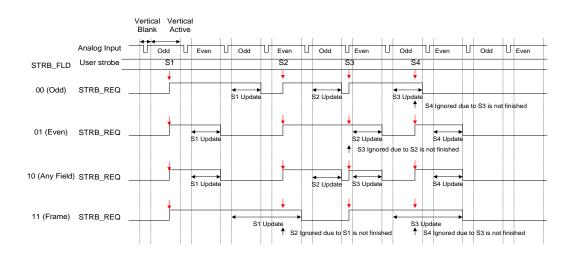

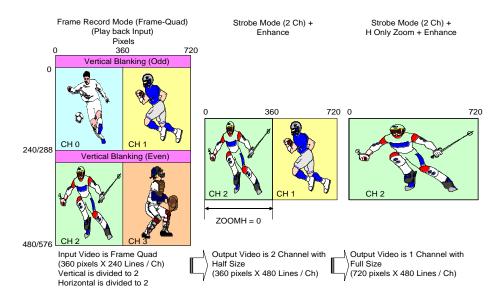

| Strobe Mode 40                              |

| Switch Mode 42                              |

| Channel Attribute46                         |

| Background Control 46                       |

| Boundary Control 46                         |

| Blank Control 46                            |

| Freeze Control 46                           |

| Last Image Captured 47                      |

| Horizontal / Vertical Mirroring             |

| Field to Frame Conversion47                 |

| Display Path Control47                      |

| Save and Recall Function 47                 |

| Image Enhancement 48                        |

| Zoom Function 48                            |

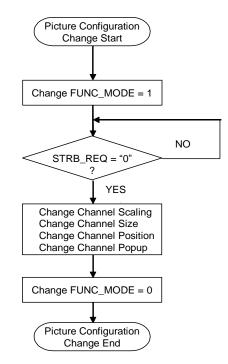

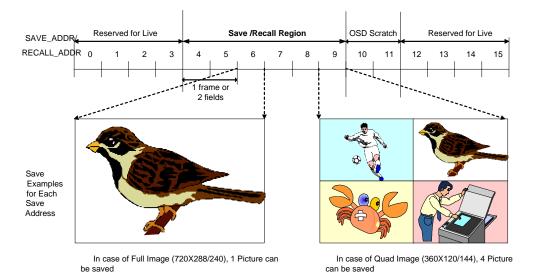

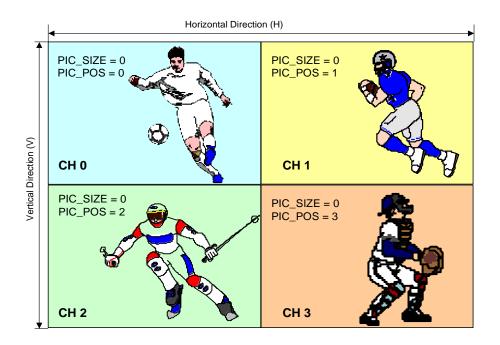

| Picture Size and Popup Control              |

| Full Triplex Function 49                    |

| Playback Path Control50                     |

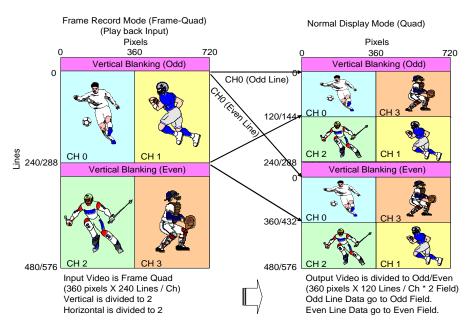

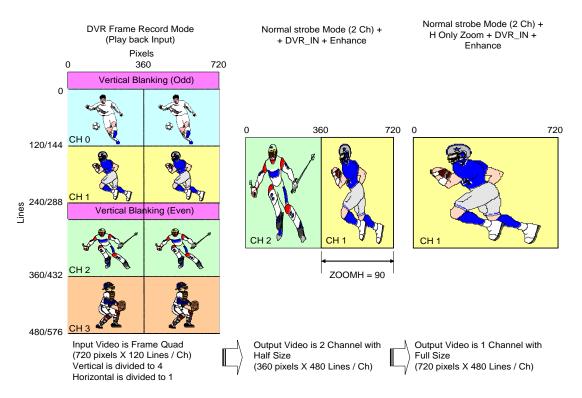

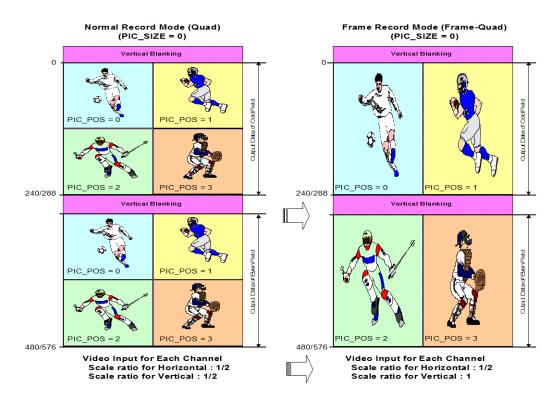

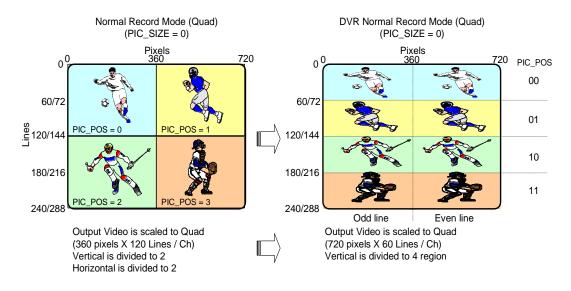

| Normal Record Mode51                        |

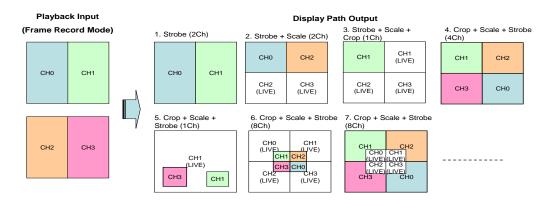

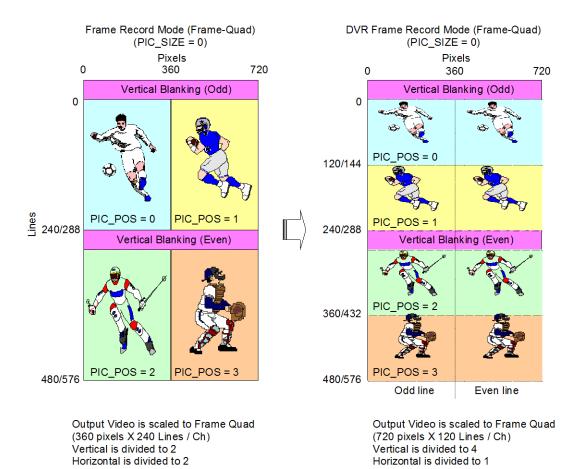

| Frame Record Mode52                         |

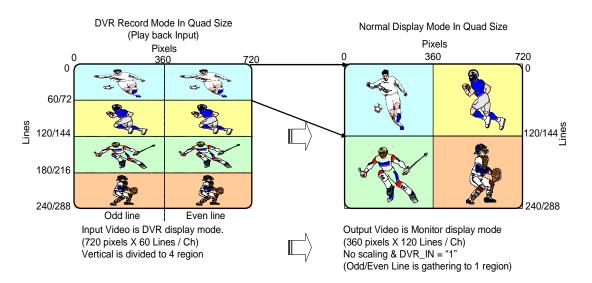

| DVR Normal Record Mode54                    |

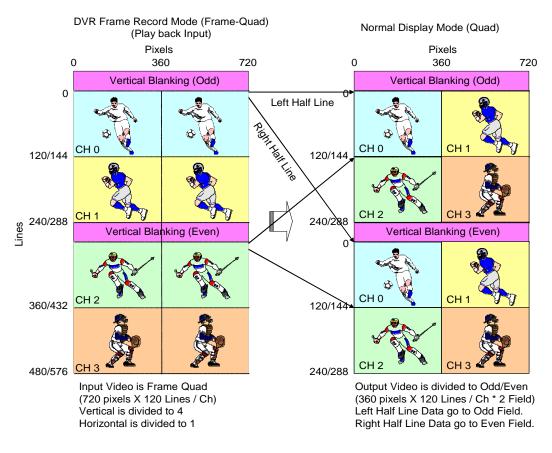

| DVR Frame Record Mode 55                    |

| Record Path Control 56                      |

| Normal Record Mode57                        |

| Frame Record Mode58                         |

| DVR Normal Record Mode 59                   |

| DVR Frame Record Mode 60                    |

| Noise Reduction61                           |

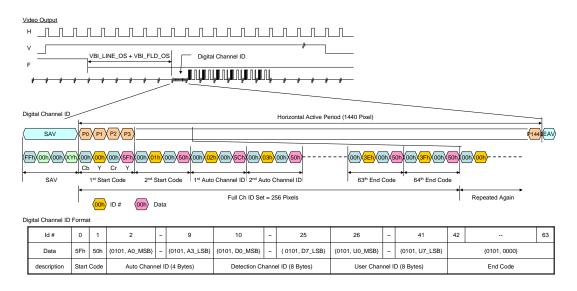

| Channel ID Encoder61                        |

| Channel ID Information 62                   |

| Analog Type Channel ID in VBI               |

| Digital Type Channel ID in VBI              |

| Digital Type Channel ID in Channel Boundary |

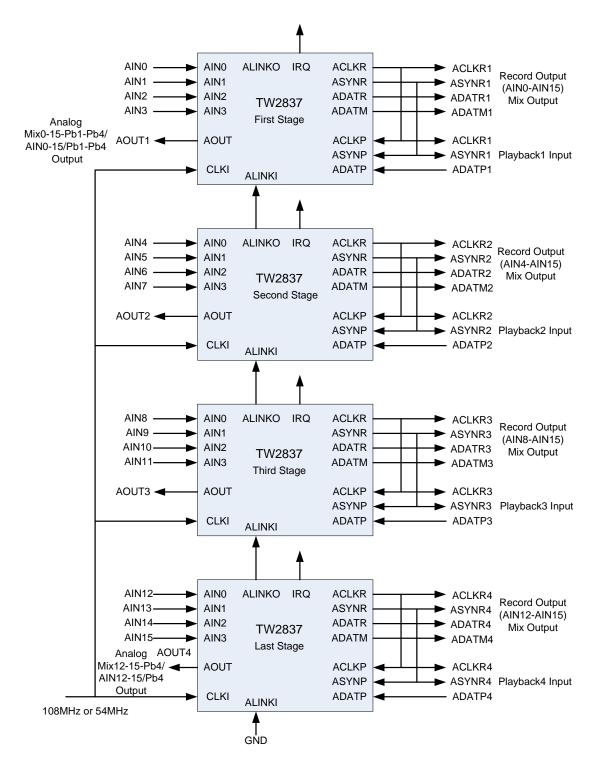

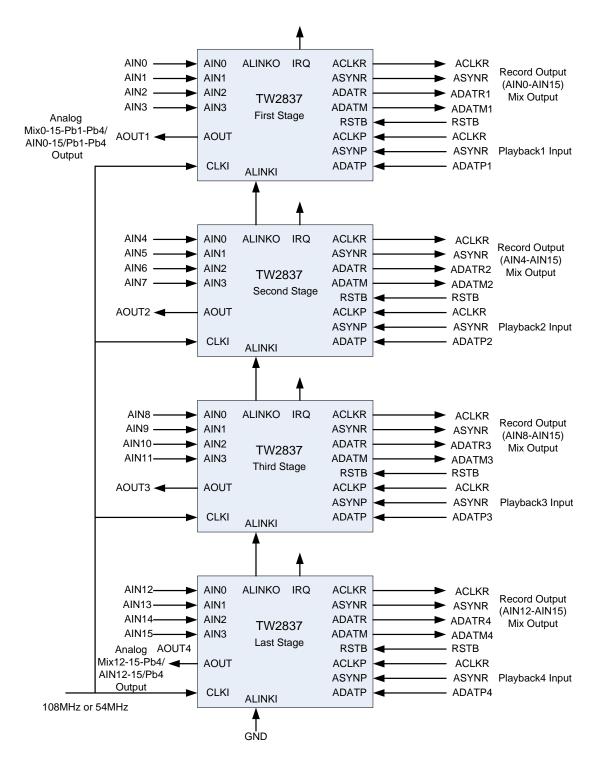

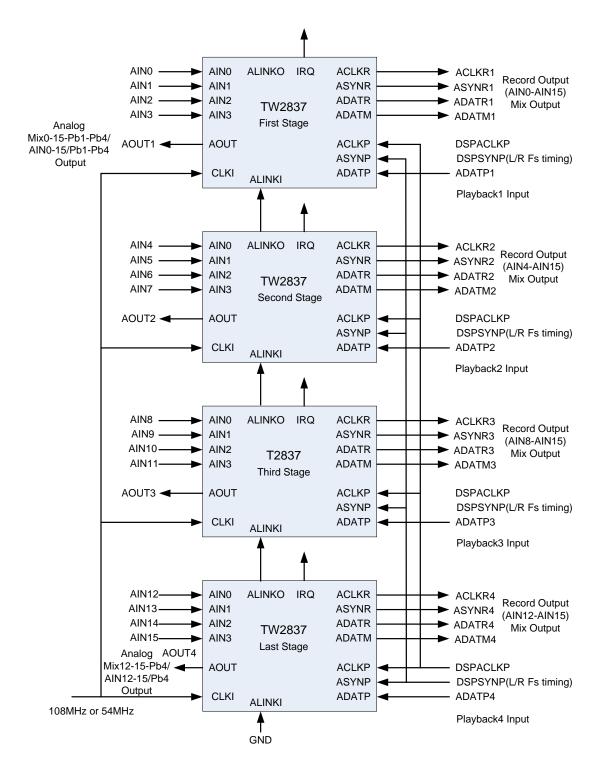

| Chip-to-Chip Cascade Operation67            |

| Channel Priority Control                    |

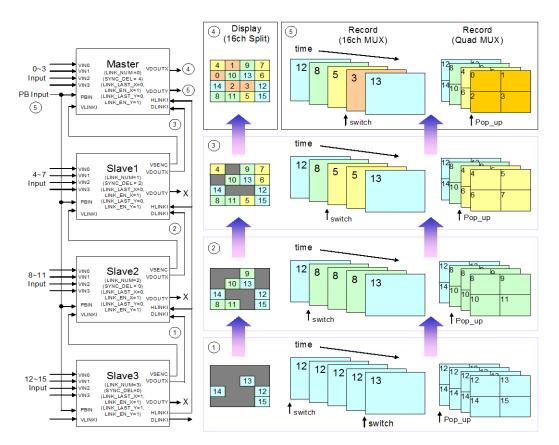

| 120 CIF/Sec Record Mode70                   |

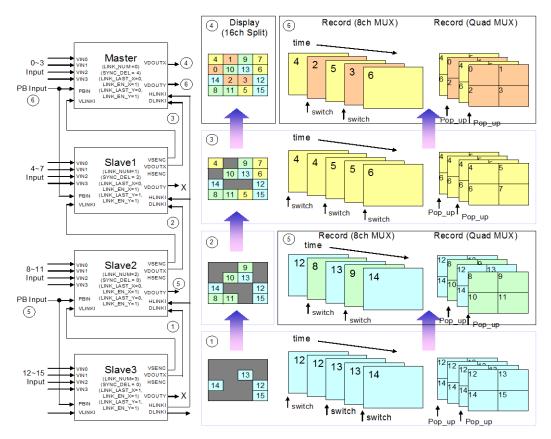

| 240 CIF/Sec Record Mode 71                  |

| 480 CIF/Sec Record Mode 72                  |

| Infinite Cascade Mode for Display Path73 |

|------------------------------------------|

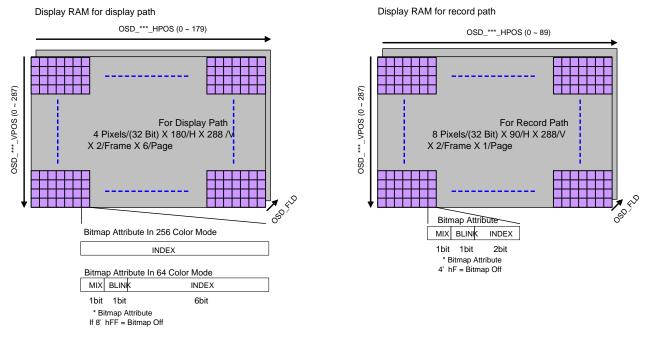

| OSD (On Screen Display) Control74        |

| 2 Dimensional Arrayed Box75              |

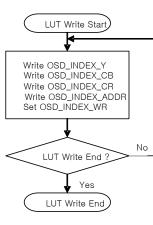

| Bitmap Overlay76                         |

| Single Box81                             |

| Mouse Pointer82                          |

| Video Output83                           |

| Timing Interface and Control83           |

| Analog Video Output85                    |

| Output Standard Selection85              |

| Luminance Filter85                       |

| Chrominance Filter86                     |

| Digital-to-Analog Converter86            |

| Digital Video Output88                   |

| Single Output Mode88                     |

| Dual Output Mode90                       |

| Realtime Record Mode90                   |

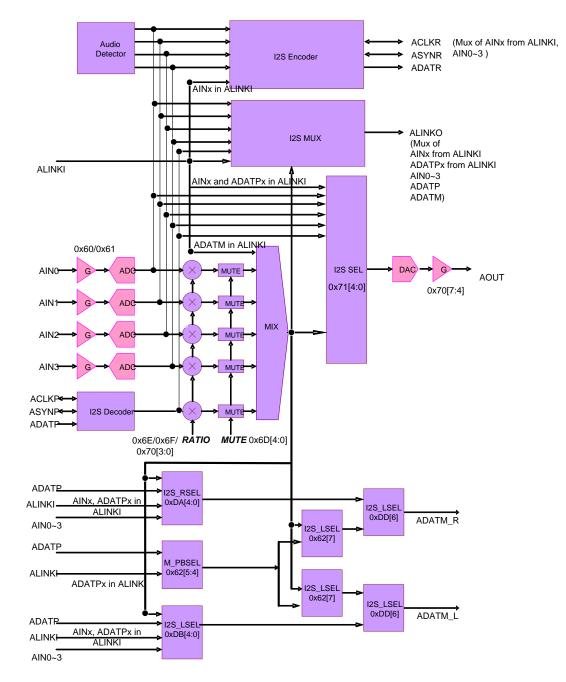

| Audio Codec91                            |

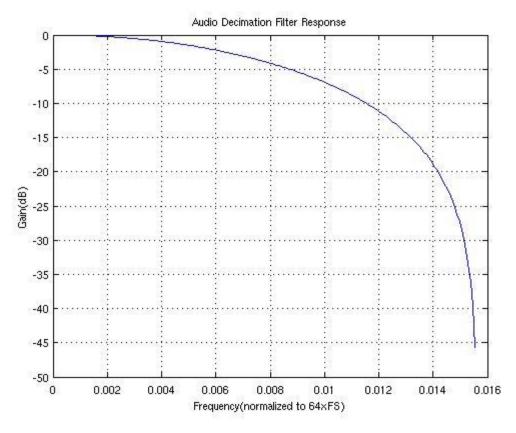

| Audio Decimation Filter Response92       |

| Audio Clock Master/Slave mode92          |

| Multi-Chip Operation93                   |

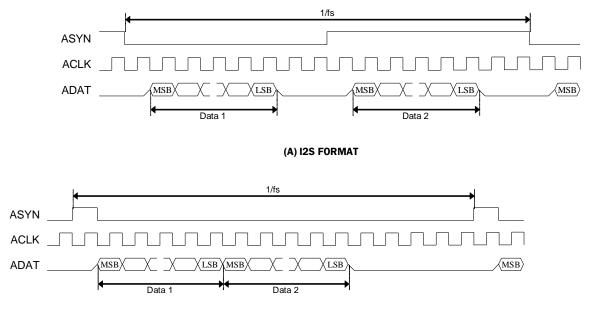

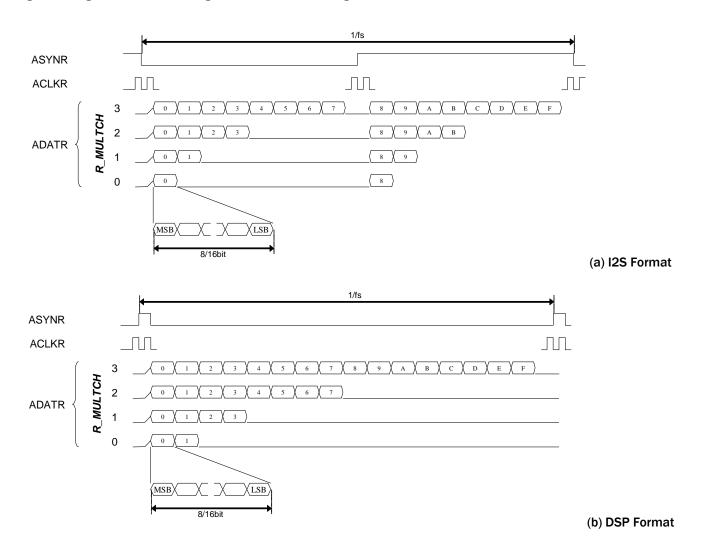

| Serial Audio Interface97                 |

| Playback Input97                         |

| Record Output98             |

|-----------------------------|

| Mix Output                  |

| Audio Clock Generation99    |

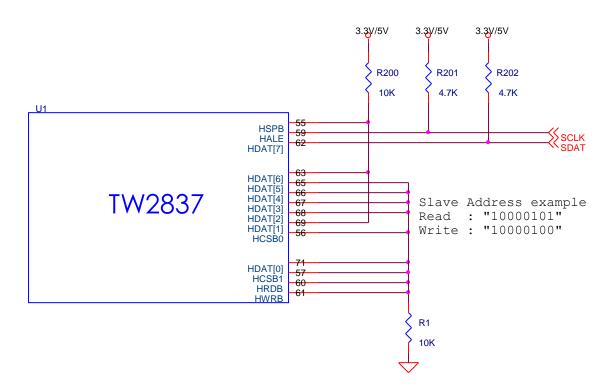

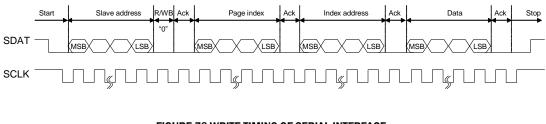

| Host Interface 100          |

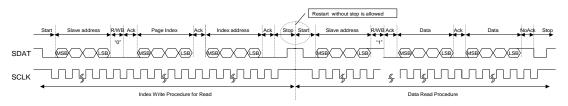

| Serial Interface101         |

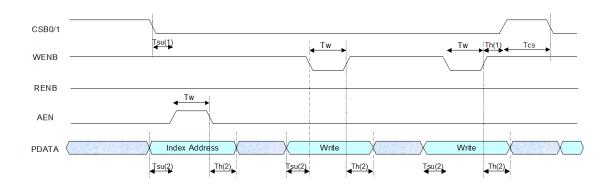

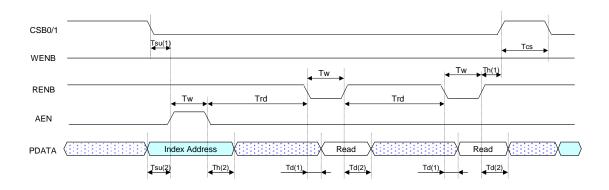

| Parallel Interface103       |

| Interrupt Interface 104     |

| MPP Pin Interface105        |

| Control Register106         |

| Register Map106             |

| Recommended Value 114       |

| For Video Decoder114        |

| For Video Controller117     |

| For Motion Detector119      |

| Register Description120     |

| Parametric Information      |

| DC Electrical Parameters    |

| AC Electrical Parameters221 |

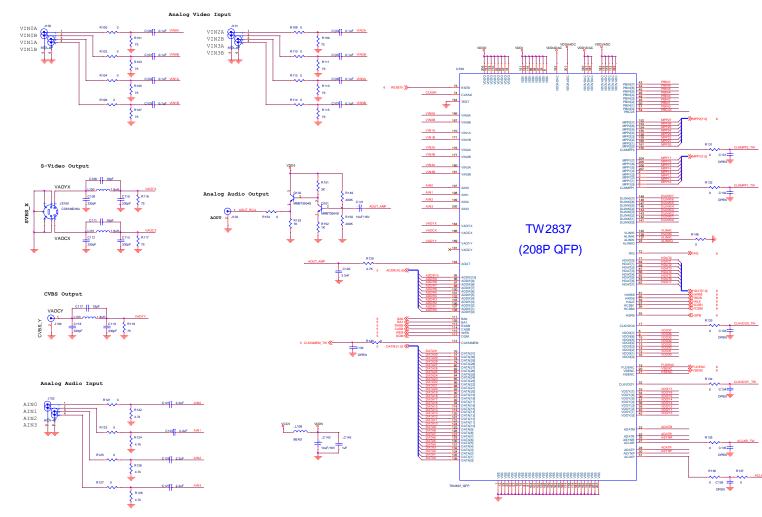

| Application Schematic       |

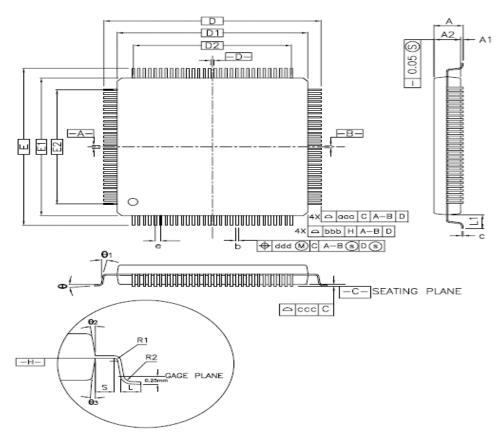

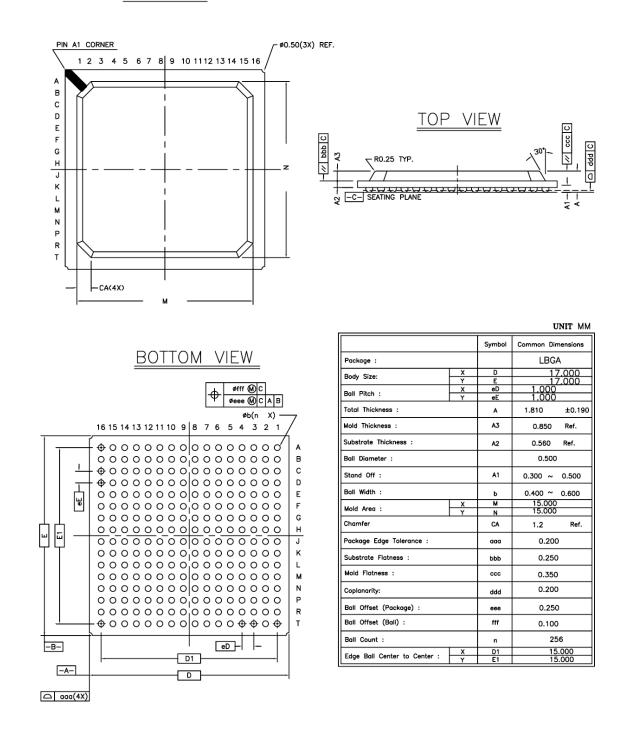

| Package Dimension           |

| 208 QFP229                  |

| 256 LBGA                    |

| Revision History            |

## **Ordering Information**

| PART<br>NUMBER         | PART<br>MARKING | PACKAGE<br>(Pb-free)      |

|------------------------|-----------------|---------------------------|

| TW2837-BB1-GR (Note 1) | TW2837 DABB1-GR | 256 Ld PBGA (17mm x 17mm) |

| TW2837-PB1-GE (Note 2) | TW2837 DAPB1-GE | 208 Ld PQFP (28mm x 28mm) |

NOTE:

- These Intersil Pb-free BGA packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAg -e2 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

TW2837

## **Pin Descriptions**

### **Analog Interface Pins**

| NAME  | NUM | IBER | ТҮРЕ | DESCRIPTION                           |

|-------|-----|------|------|---------------------------------------|

|       | QFP | LBGA |      | DESCRIPTION                           |

| VINOA | 166 | B12  | Α    | Composite video input A of channel 0. |

| VINOB | 167 | C12  | Α    | Composite video input B of channel 0. |

| VIN1A | 170 | B11  | Α    | Composite video input A of channel 1. |

| VIN1B | 171 | C11  | Α    | Composite video input B of channel 1. |

| VIN2A | 176 | B10  | Α    | Composite video input A of channel 2. |

| VIN2B | 177 | C10  | Α    | Composite video input B of channel 2. |

| VIN3A | 180 | B9   | Α    | Composite video input A of channel 3. |

| VIN3B | 181 | C9   | Α    | Composite video input B of channel 3. |

| VAOYX | 184 | C8   | Α    | Analog video output.                  |

| VAOCX | 186 | D8   | Α    | Analog video output.                  |

| VAOYY | 189 | C7   | Α    | Analog video output.                  |

| NC    | 191 | D7   | Α    | No connection.                        |

| AINO  | 197 | B6   | Α    | Audio input of channel 0.             |

| AIN1  | 198 | C6   | Α    | Audio input of channel 1.             |

| AIN2  | 199 | B5   | Α    | Audio input of channel 2.             |

| AIN3  | 200 | C5   | Α    | Audio input of channel 3.             |

| AOUT  | 194 | D5   | Α    | Audio mixing output.                  |

## **Digital Video Interface Pins**

| NAME       | NUM                                 | IBER                                | ТҮРЕ | DESCRIPTION                                                                              |

|------------|-------------------------------------|-------------------------------------|------|------------------------------------------------------------------------------------------|

| NAME       | QFP                                 | LBGA                                |      | DESCRIPTION                                                                              |

| VDOX [7:0] | 8,9,<br>10,11,<br>13,14,<br>15,16   | C1,C2,<br>D2,D3,<br>E1,E2,<br>E3,E4 | 0    | Digital video data output for display path.<br>Or link signal for multi-chip connection. |

| VDOY [7:0] | 33,34,<br>36,37,<br>38,39,<br>40,42 | J4,K2,<br>K3,L1,<br>L2,L3,<br>L4,M1 | 0    | Digital video data output for record path.                                               |

| CLKVDOX    | 17                                  | F1                                  | 0    | Clock output for VDOUTX.                                                                 |

| CLKVDOY    | 32                                  | J3                                  | 0    | Clock output for VDOUTY                                                                  |

| HSENC      | 21                                  | F4                                  | 0    | Encoder horizontal sync.                                                                 |

| VSENC      | 20                                  | F3                                  | ο    | Encoder vertical sync.<br>Or link signal for multi-chip connection.                      |

| FLDENC     | 19                                  | F2                                  | 0    | Encoder field flag.                                                                      |

| PBDIN[7:0] | 43,44,<br>45,46,<br>48,49,<br>50,51 | M2,M3,<br>M4,N2,<br>N3,P1,<br>P2,R1 | I    | Video data of playback input.                                                            |

| PBCLK      | 54                                  | R2                                  | I    | Clock of playback input.                                                                 |

## **Multi-purpose Pins**

| NAME        | NUM                                         | IBER                                        | ТҮРЕ | DESCRIPTION                                                                                                                                            |

|-------------|---------------------------------------------|---------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | QFP                                         | LBGA                                        |      | DESCRIPTION                                                                                                                                            |

| HLINKI      | 138                                         | F14                                         | I/0  | Link signal for multi-chip connection.                                                                                                                 |

| VLINKI      | 140                                         | F13                                         | I    | Link signal for multi-chip connection.                                                                                                                 |

| DLINKI[7:0] | 149,148,<br>147,146,<br>144,143,<br>142,141 | C15,C16,<br>D14,D15,<br>E13,E14,<br>E15,E16 | I/0  | Link signal for multi-chip connection.<br>Or decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output. |

| MPP1[7:0]   | 204,205,<br>206,207,<br>2,3,<br>4,5         | A4,B4,<br>C4,A3,<br>B3,C3,<br>A2,B2         | I/0  | Decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output.                                              |

| MPP2[7:0]   | 152,153,<br>154,155,<br>158,159,<br>160,161 | B16,B15,<br>A15,A14,<br>B14,A13,<br>B13,C13 | I/0  | Decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output.                                              |

| CLKMPP1     | 7                                           | B1                                          | 0    | Clock output for MPP1 data.                                                                                                                            |

| CLKMPP2     | 150                                         | C14                                         | 0    | Clock output for MPP2 data.                                                                                                                            |

## **Digital Audio Interface Pins**

| NAME   | NUM | IBER | TYPE | DESCRIPTION                                  |

|--------|-----|------|------|----------------------------------------------|

| NAME   | QFP | LBGA |      | DESCRIPTION                                  |

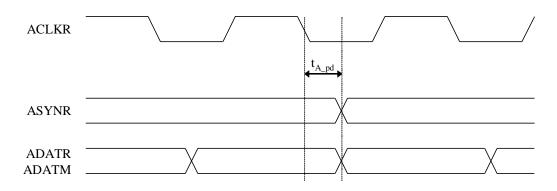

| ACLKR  | 27  | H3   | 0    | Audio serial clock output of record.         |

| ASYNR  | 26  | H2   | 0    | Audio serial sync output of record.          |

| ADATR  | 25  | H1   | 0    | Audio serial data output of record.          |

| ADATM  | 23  | G3   | 0    | Audio serial data output of mixing.          |

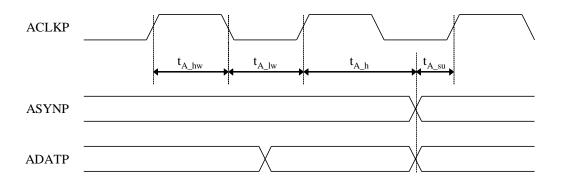

| ACLKP  | 31  | J2   | I/0  | Audio serial clock input/output of playback. |

| ASYNP  | 30  | J1   | I/0  | Audio serial sync input/output of playback.  |

| ADATP  | 28  | H4   | I    | Audio serial data input of playback.         |

| ALINKI | 137 | F15  | I    | Link signal for multi-chip connection.       |

| ALINKO | 22  | G2   | 0    | Link signal for multi-chip connection.       |

## **Memory Interface Pins**

| NAME       | NUM                  | IBER                 | TYPE | DESCRIPTION                        |

|------------|----------------------|----------------------|------|------------------------------------|

|            | QFP                  | LBGA                 |      | DESCRIPTION                        |

|            | 76,77,               | R8,P8,               |      |                                    |

|            | 78,79,               | N8,T9,               |      |                                    |

|            | 80,82,               | R9,P9,               |      |                                    |

|            | 83,84,               | N9,R10,              |      |                                    |

|            | 85,86,               | P10,T11,             |      |                                    |

|            | 88,89,               | R11,P11,             |      |                                    |

|            | 90,91,               | N11,T12,             |      |                                    |

| DATA[31:0] | 92,94,               | R12,P12,             | I/O  | SDRAM data bus.                    |

|            | 118,119,<br>120,121, | L15,L14,<br>L13,K15, |      |                                    |

|            | 120,121,<br>123,124, | K14,J16,             |      |                                    |

|            | 125,124,<br>125,126, | J15,J14,             |      |                                    |

|            | 127,129,             | J13,H16,             |      |                                    |

|            | 130,131,             | H15,H14,             |      |                                    |

|            | 132,134,             | H13,G15,             |      |                                    |

|            | 135,136              | G14,F16              |      |                                    |

|            | 95,96,               | N12,R13,             |      |                                    |

|            | 97,98,               | P13,T14,             |      | SDRAM address bus. ADDR[10] is AP. |

| ADDR[10:0] | 100,101,             | R14,P14,             | ο    |                                    |

| ADDR[10.0] | 102,103,             | T15,R15,             | 0    |                                    |

|            | 106,107,             | R16,P16,             |      |                                    |

|            | 108                  | P15                  |      |                                    |

| BA1        | 109                  | N15                  | 0    | SDRAM bank1 selection.             |

| BAO        | 111                  | N14                  | 0    | SDRAM bank0 selection.             |

| RASB       | 113                  | M15                  | 0    | SDRAM row address selection.       |

| CASB       | 114                  | M14                  | 0    | SDRAM column address selection.    |

| WEB        | 115                  | M13                  | 0    | SDRAM write enable.                |

| DQM        | 117                  | L16                  | 0    | SDRAM write mask.                  |

| CLK54MEM   | 112                  | M16                  | 0    | SDRAM clock.                       |

## **System Control Pins**

| NAME      | NUM                                 | IBER                                | ТҮРЕ | DESCRIPTION                                                                                                                               |

|-----------|-------------------------------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | QFP                                 | LBGA                                | ITPE | DESCRIPTION                                                                                                                               |

| TEST      | 164                                 | D12                                 | I    | Only for the test purpose.<br>Must be connected to VSSO.                                                                                  |

| RSTB      | 73                                  | P7                                  | I    | System reset. Active low.                                                                                                                 |

| IRQ       | 72                                  | R7                                  | 0    | Interrupt request signal.                                                                                                                 |

| HDAT[7:0] | 62,63,<br>65,66,<br>67,68,<br>69,71 | T5,R5,<br>P5,N5,<br>T6,R6,<br>P6,N6 | I/0  | Data bus for parallel interface.<br>HDAT[7] is serial data for serial interface.<br>HDAT[6:1] is slave address[6:1] for serial interface. |

| HWRB      | 61                                  | P4                                  | I    | Write enable for parallel interface.<br>VSSO for serial interface.                                                                        |

| HRDB      | 60                                  | R4                                  | I    | Read enable for parallel interface.<br>VSSO for serial interface.                                                                         |

| HALE      | 59                                  | P3                                  | I    | Address line enable for parallel interface.<br>Serial clock for serial interface.                                                         |

| HCSB1     | 57                                  | R3                                  | I    | Chip select 1 for parallel interface.<br>VSSO for serial interface.                                                                       |

| HCSB0     | 56                                  | тз                                  | I    | Chip select 0 for parallel interface.<br>Slave address[0] for serial interface.                                                           |

| HSPB      | 55                                  | T2                                  | I    | Select serial/parallel host interface.                                                                                                    |

| CLK54I    | 74                                  | Т8                                  | I    | 54MHz system clock.                                                                                                                       |

## **Power / Ground Pins**

| NAME    | NUMBER                                                                                                   |                                                                                                | TYPE | DESCRIPTION                            |

|---------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|----------------------------------------|

|         | QFP                                                                                                      | LBGA                                                                                           |      | DESCRIPTION                            |

| VDDO    | 18,47,<br>64,93,<br>110,139,<br>157,208                                                                  | A1,A16,<br>K1,K16,<br>T1,T7,<br>T10,T16                                                        | Ρ    | Digital power for output driver 3.3V.  |

| VDDI    | 6,24,<br>41,58,<br>99,116,<br>133,151,                                                                   | D1,D16,<br>G1,G16,<br>N1,N16,<br>T4,T13                                                        | Ρ    | Digital power for internal logic 1.8V. |

| VDDVADC | 165,172,<br>173,175,<br>182                                                                              | A8,A9,<br>A10,A11,<br>A12                                                                      | Ρ    | Analog power for Video ADC 1.8V.       |

| VSSVADC | 168,169,<br>174,178,<br>179                                                                              | D10,D11,<br>D13, E11,<br>E12                                                                   | G    | Analog ground for Video ADC 1.8V.      |

| VDDVDAC | 185,187,<br>190                                                                                          | A7,B7,<br>B8                                                                                   | Р    | Analog power for Video DAC 1.8V.       |

| VSSVDAC | 183,188,<br>192                                                                                          | D9,E7,<br>E8,E9,<br>E10                                                                        | G    | Analog ground for Video DAC 1.8V.      |

| VDDAADC | 201                                                                                                      | A6                                                                                             | Р    | Analog power for Audio ADC 1.8V.       |

| VSSAADC | 196                                                                                                      | D6,E6                                                                                          | G    | Analog ground for Audio ADC 1.8V.      |

| VDDADAC | 193                                                                                                      | A5                                                                                             | Р    | Analog power for Audio DAC 1.8V.       |

| VSSADAC | 195                                                                                                      | D4,E5                                                                                          | G    | Analog ground for Audio DAC 1.8V.      |

| VSS     | 1,12,<br>29,35,<br>52,53,<br>70,75,<br>81,87,<br>104,105,<br>122,128,<br>145,156,<br>162,163,<br>202,203 | F5~F12,<br>G4~G13,<br>H5~H12,<br>J5~J12,<br>K4~K13,<br>L5~L12,<br>M5~M12,<br>N4,N7,<br>N10,N13 | G    | Ground.                                |

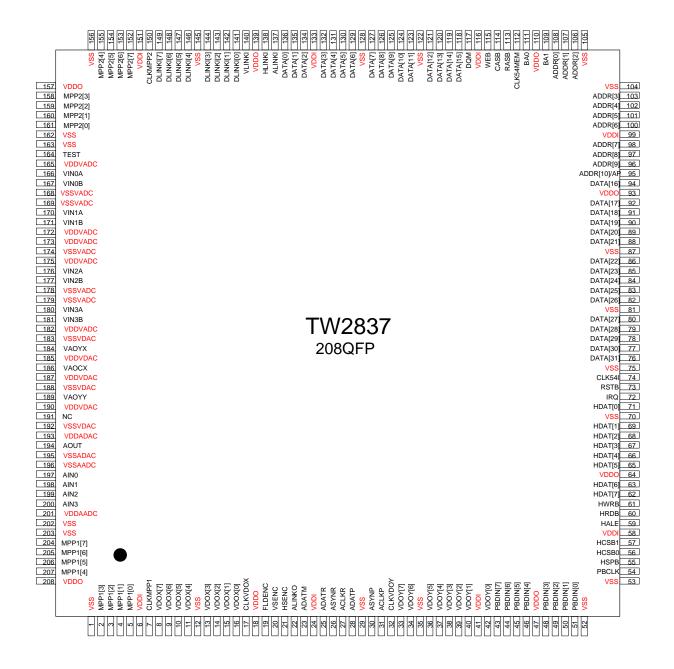

## **Pin Configuration**

### 208 QFP Pin Diagram (Top -> Bottom View)

## 256 LBGA Pin Diagram (Top->Bottom View)

|    | A           | в           | С             | D             | Е             | F           | G           | н           | J            | к            | L            | М            | Ν               | Р            | R            | Т            |    |

|----|-------------|-------------|---------------|---------------|---------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|-----------------|--------------|--------------|--------------|----|

| 16 | VDDO        | MPP2<br>[7] | DLINKI<br>[6] | VDDI          | DLINKI<br>[0] | DATA<br>[0] | VDDI        | DATA<br>[6] | DATA<br>[10] | VDDO         | DQM          | CLK<br>54MEN | VDDI            | ADDR<br>[1]  | ADDR<br>[2]  | VDDO         | 16 |

| 15 | MPP2<br>[5] | MPP2<br>[6] | DLINKI<br>[7] | DLINKI<br>[4] | DLINKI<br>[1] | ALINKI      | DATA<br>[2] | DATA<br>[5] | DATA<br>[9]  | DATA<br>[12] | DATA<br>[15] | RASB         | BA1             | ADDR<br>[0]  | ADDR<br>[3]  | ADDR<br>[4]  | 15 |

| 14 | MPP2<br>[4] | MPP2<br>[3] | CLK<br>MPP2   | DLINKI<br>[5] | DLINKI<br>[2] | HLINKI      | DATA<br>[1] | DATA<br>[4] | DATA<br>[8]  | DATA<br>[11] | DATA<br>[14] | CASB         | BA0             | ADDR<br>[5]  | ADDR<br>[6]  | ADDR<br>[7]  | 14 |

| 13 | MPP2<br>[2] | MPP2<br>[1] | MPP2<br>[0]   | VSSV<br>ADC   | DLINKI<br>[3] | VLINKI      | VSS         | DATA<br>[3] | DATA<br>[7]  | VSS          | DATA<br>[13] | WEB          | VSS             | ADDR<br>[8]  | ADDR<br>[9]  | VDDI         | 13 |

| 12 | VDD<br>VADC | VIN0A       | VIN0B         | TEST          | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | ADDR<br>[10]/AP | DATA<br>[16] | DATA<br>[17] | DATA<br>[18] | 12 |

| 11 | VDD<br>VADC | VIN1A       | VIN1B         | VSSV<br>ADC   | VSSV<br>ADC   | VSSV<br>ADC | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[19]    | DATA<br>[20] | DATA<br>[21] | DATA<br>[22] | 11 |

| 10 | VDD<br>VADC | VIN2A       | VIN2B         | VSSV<br>ADC   | VSSV<br>DAC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | VSS             | DATA<br>[23] | DATA<br>[24] | VDDO         | 10 |

| 9  | VDD<br>VADC | VIN3A       | VIN3B         | VSSV<br>DAC   | VSSV<br>DAC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[25]    | DATA<br>[26] | DATA<br>[27] | DATA<br>[28] | 9  |

| 8  | VDD<br>VADC | VDD<br>VDAC | VAOYX         | VAOCX         | VSSV<br>DAC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[29]    | DATA<br>[30] | DATA<br>[31] | CLK54I       | 8  |

| 7  | VDD<br>VDAC | VDD<br>VDAC | VAOYY         | NC            | VSSV<br>DAC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | VSS             | RSTB         | IRQ          | VDDO         | 7  |

| 6  | VDD<br>AADC | AIN0        | AIN1          | VSSA<br>ADC   | VSSA<br>ADC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | HDAT<br>[0]     | HDAT<br>[1]  | HDAT<br>[2]  | HDAT<br>[3]  | 6  |

| 5  | VDD<br>ADAC | AIN2        | AIN3          | AOUT          | VSSA<br>DAC   | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | HDAT<br>[4]     | HDAT<br>[5]  | HDAT<br>[6]  | HDAT<br>[7]  | 5  |

| 4  | MPP1<br>[7] | MPP1<br>[6] | MPP1<br>[5]   | VSSA<br>DAC   | VDOX<br>[0]   | HS<br>ENC   | VSS         | ADATP       | VDOY<br>[7]  | VSS          | VDOY<br>[1]  | PBDIN<br>[5] | VSS             | HWRB         | HRDB         | VDDI         | 4  |

| 3  | MPP1<br>[4] | MPP1<br>[3] | MPP1<br>[2]   | VDOX<br>[4]   | VDOX<br>[1]   | VS<br>ENC   | ADATN       | ACLKR       | CLK<br>VDOY  | VDOY<br>[5]  | VDOY<br>[2]  | PBDIN<br>[6] | PBDIN<br>[3]    | HALE         | HCSB1        | HCSB0        | 3  |

| 2  | MPP1<br>[1] | MPP1<br>[0] | VDOX<br>[6]   | VDOX<br>[5]   | VDOX<br>[2]   | FLD<br>ENC  | ALINKC      | ASYNF       | ACLKP        | VDOY<br>[6]  | VDOY<br>[3]  | PBDIN<br>[7] | PBDIN<br>[4]    | PBDIN<br>[1] | PB<br>CLK    | HSPB         | 2  |

| 1  | VDDO        | CLK<br>MPP1 | VDOX<br>[7]   | VDDI          | VDOX<br>[3]   | CLK<br>VDOX | VDDI        | ADATR       | ASYNF        | VDDO         | VDOY<br>[4]  | VDOY<br>[0]  | VDDI            | PBDIN<br>[2] | PBDIN<br>[0] | VDDO         | 1  |

| L  | Α           | В           | С             | D             | Е             | F           | G           | н           | J            | к            | L            | М            | N               | Р            | R            | т            |    |

## **Functional Description**

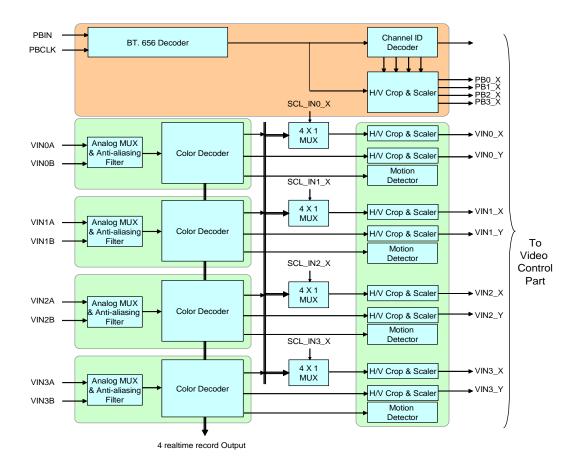

### **Video Input**

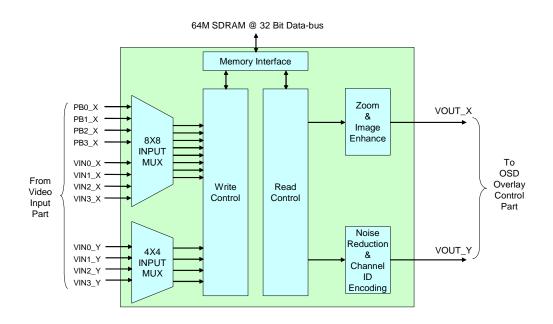

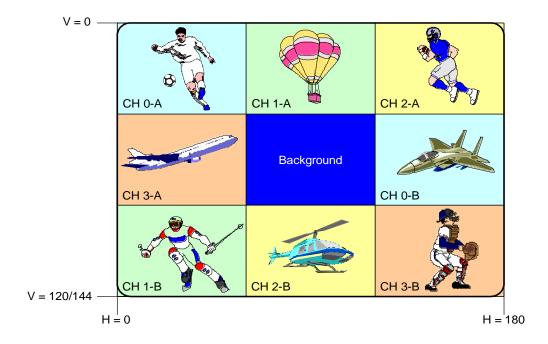

The TW2837 has 5 input interfaces that consist of 1 digital video input and 4 analog composite video inputs. Four analog video inputs are converted to digital video stream through 10 bits ADC and luminance/chrominance processor in built-in four video decoders. One digital input for playback application are decoded by internal ITU-R BT656 decoder and then fed to video control part and channel ID decoder. Each built-in video decoder has its own motion detector and dual scaler. Four additional scalers are also embedded for playback display application. The structure of video input is shown in the following Figure 1.

FIGURE 1 THE STRUCTURE OF VIDEO INPUT

For the special 4ch real-time record application, the TW2837 supports 4 realtime video decoder outputs through the multi-purpose output pins (MPP1[7:0] and MPP2[7:0]).

#### **ANALOG VIDEO INPUTS**

#### **Video Input Formats**

The TW2837 has build-in automatic standard discrimination circuitry. The circuit uses burst-phase, burst-frequency and frame rate to identify NTSC, PAL or SECAM color signals. The standards that can be identified are NTSC (M), NTSC (4.43), PAL (B, D, G, H, I), PAL (M), PAL (N), PAL (60) and SECAM (M). Each standard can be included or excluded in the standard recognition process by software control. The exceptions are the base standard NTSC and PAL, which are always enabled. The identified standard is indicated by the Standard Selection (SDT) register. Automatic standard detection can be overridden by software controlled standard selection.

TW2837 supports all common video formats as shown in Table 1.

| FORMAT         | LINES | FIELDS | FSC               | COUNTRY                                        |

|----------------|-------|--------|-------------------|------------------------------------------------|

| NTSC-M         | 525   | 60     | 3.579545 MHz      | U.S., many others                              |

| NTSC-Japan (1) | 525   | 60     | 3.579545 MHz      | Japan                                          |

| PAL-B, G, N    | 625   | 50     | 4.433619 MHz      | Many                                           |

| PAL-D          | 625   | 50     | 4.433619 MHz      | China                                          |

| PAL-H          | 625   | 50     | 4.433619 MHz      | Belgium                                        |

| PAL-I          | 625   | 50     | 4.433619 MHz      | Great Britain, others                          |

| PAL-M          | 525   | 60     | 3.575612 MHz      | Brazil                                         |

| PAL-CN         | 625   | 50     | 3.582056 MHz      | Argentina                                      |

| SECAM          | 625   | 50     | 4.406MHz 4.250MHz | France, Eastern Europe, Middle<br>East, Russia |

| PAL-60         | 525   | 60     | 4.433619 MHz      | China                                          |

| NTSC (4.43)    | 525   | 60     | 4.433619 MHz      | Transcoding                                    |

TABLE 1 VIDEO INPUT FORMATS SUPPORTED BY THE TW2837

NOTE:

3. NTSC-Japan has 0 IRE setup.

#### **Analog Video Frontend**

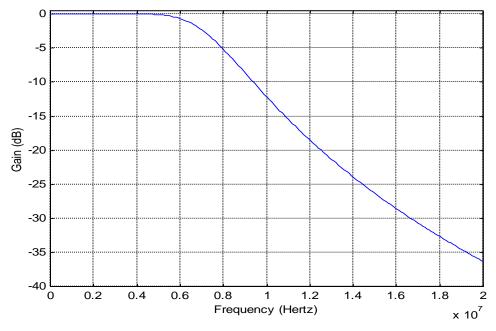

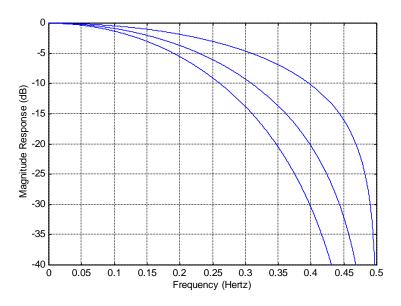

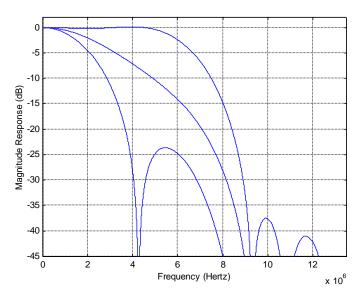

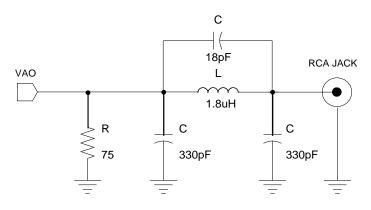

The TW2837 contains four 10-bit ADC (Analog to Digital Converters) to digitize the analog video inputs. The ADC can be put into power-down mode by the V\_ADC\_PWDN register. The TW2837 also contains an anti-aliasing filter to prevent out-of-band frequency in analog video input signal. So there is no need of external components in analog input pin except ac coupling capacitor and termination resistor. The following Figure 2 shows the frequency response of the anti-aliasing filter.

FIGURE 2 THE FREQUENCY RESPONSE OF ANTI-ALIASING FILTER

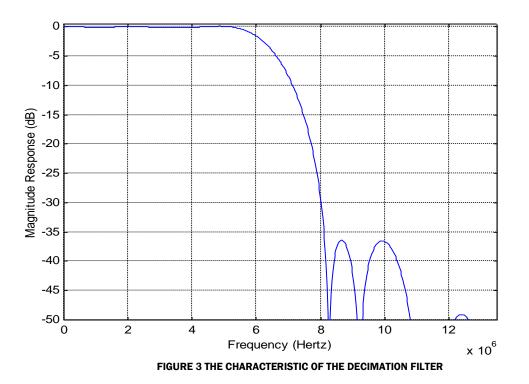

#### **Video Decimation Filter**

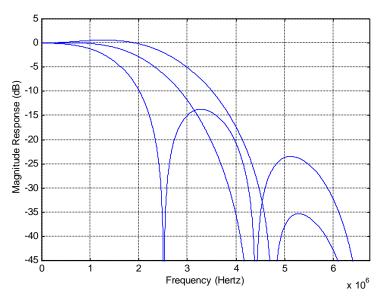

The digitized composite video data are over-sampled to simplify the design of analog filter. The decimation filter is required to achieve optimum performance and prevent high frequency components from being aliased back into the video image when down-sampled. Figure 3 shows the characteristic of the decimation filter.

#### **Automatic Gain Control and Clamping**

All four analog channels have built-in clamping circuit that restores the signal DC level. The Y channel restores the back porch of the digitized video to a level of 60. This operation is automatic through internal feedback loop. The Automatic Gain Control (AGC) of the Y channel adjusts input gain so that the sync tip is at a desired level. Programmable white peak protection logic is included to prevent saturation in the case of abnormal signal proportion between sync and white peak level.

#### Sync Processing

The sync processor of TW2837 detects horizontal synchronization and vertical synchronization signals in the composite video or in the Y signal of an S-video or component signal. The processor contains a digital phase-locked-loop and decision logic to achieve reliable sync detection in stable signal as well as in unstable signals such as those from VCR fast forward or backward.

The vertical sync separator detects the vertical synchronization pattern in the input video signals. In addition, the actual sync determination is controlled by a detection window to provide more reliable synchronization. An option is available to provide faster responses for certain applications. The field status is determined at vertical synchronization time. The field logic can also be controlled to toggle automatically while tracking the input

#### Y/C Separation

The color-decoding block contains the luma/chroma separation for the composite video signal and multi-standard color demodulation. For NTSC and PAL standard signals, the luma/chroma separation can be done either by comb filter or notch/band-pass filter combination. For SECAM standard signals, adaptive notch/band-pass filter is used. The default selection for NTSC/PAL is comb filter.

In the case of comb filter, the TW2837 separates luma (Y) and chroma (C) of a NTSC/PAL composite video signal using a proprietary 4H adaptive comb filter. The filter uses a four-line buffer. Adaptive logic combines the upper-comb and the lower-comb results based on the signal changes among the previous, current and next lines. This technique leads to excellent Y/C separation with small cross luma and cross color at both horizontal and vertical edges

Due to the line buffer used in the comb filter, there are always two lines processing delay at the output except for the component input mode which has only one line delay.

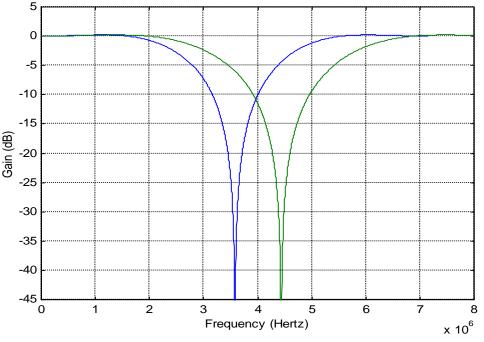

If notch/band-pass filter is selected, the characteristics of the filters are shown in the filter curve section.

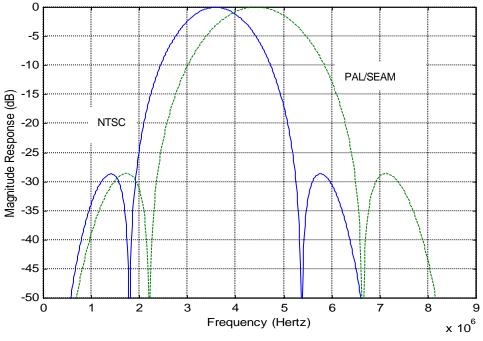

The Figure 4 show the frequency response of notch filter for each system NTSC and PAL. The Figure 5 shows the frequency response of Chroma Band Pass Filter Curves.

FIGURE 4 THE CHARACTERISTICS OF LUMINANCE NOTCH FILTER FOR PAL

FIGURE 5 CHROMA BAND PASS FILTER CURVES

#### **Color Decoding**

#### **Chrominance Demodulation**

The color demodulation for NTSC and PAL standard is done by first quadrature mixing the chroma signal to the base band. A low-pass filter is then used to remove carrier signal and yield chroma components. The low-pass filter characteristic can be selected for optimized transient color performance. For the PAL system, the PAL ID or the burst phase switching is identified to aid the PAL color demodulation.

For SECAM, the color information is FM modulated onto different carrier. The demodulation process therefore consists of FM demodulator and de-emphasis filter. During the FM demodulation, the chroma carrier frequency is identified and used to control the SECAM color demodulation.

The sub-carrier signal for use in the color demodulator is generated by direct digital synthesis PLL that locks onto the input sub-carrier reference (color burst). This arrangement allows any sub-standard of NTSC and PAL to be demodulated easily with single crystal frequency.

Figure 5 and Figure 6 show the frequency response of Chrominance Band Pass and Low-Pass Filter Curves.

FIGURE 6 CHROMINANCE LOW-PASS FILTER CURVES

#### ACC (Automatic Color gain control)

The Automatic Chroma Gain Control (ACC) compensates for reduced amplitudes caused by high-frequency loss in video signal. In the NTSC/PAL standard, the color reference signal is the burst on the back porch. It is measured to control the chroma output gain. The range of ACC control is –6db to +24db.

#### **Chrominance Processing**

#### **Chrominance Gain, Offset and Hue Adjustment**

When decoding NTSC signals, TW2837 can adjust the hue of the chroma signal. The hue is defined as a phase shift of the subcarrier with respect to the burst. This phase shift of NTSC decoding can be programmed through a control register. For the PAL standard, the PAL delay line is provided to compensate any hue error; therefore, there is no hue adjustment available. The color saturation can be adjusted by changing the gain of Cb and Cr signals for all NTSC, PAL and SECAM formats. The Cb and Cr gain can be adjusted independently for flexibility.

#### **CTI (Color Transient Improvement)**

The TW2837 provides the Color Transient Improvement function to further enhance the image quality. The CTI enhance the color edge transient without any overshoot or under-shoot.

#### Luminance Processing

The TW2837 adjusts brightness by adding a programmable value (in register BRIGHTNESS) to the Y signal. It adjusts the picture contrast by changing the gain (in register CONTRAST) of the Y signal.

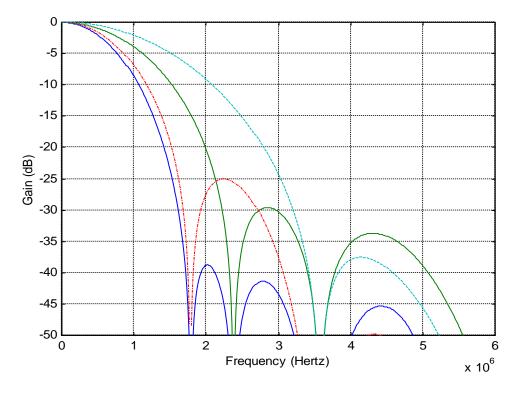

The TW2837 also provide programmable peaking function to further enhance the video sharpness. The peaking control has built-in coring function to prevent enhancement of noise.

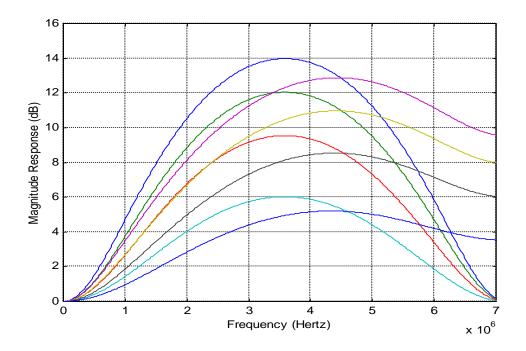

The Figure 7 shows the characteristics of the peaking filter for four different gain modes and different center frequencies.

FIGURE 7 THE CHARACTERISTIC OF LUMINANCE PEAKING FILTER

#### **DIGITAL VIDEO INPUT**

The TW2837 supports digital video input with 8bit ITU-R BT.656 standard for playback. This digital input is decoded in built-in ITU-R BT 656 decoder and fed to the scaler block in order to display the scaled video data. The TW2837 supports error correction mode for decoding ITU-R BT.656. The decoded video data are also transferred to channel ID decoder part for auto cropping and strobe function.

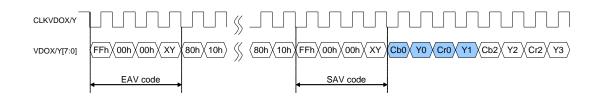

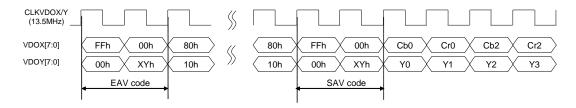

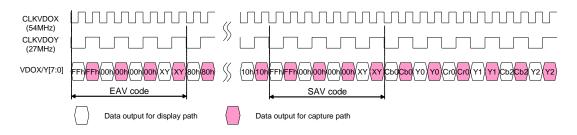

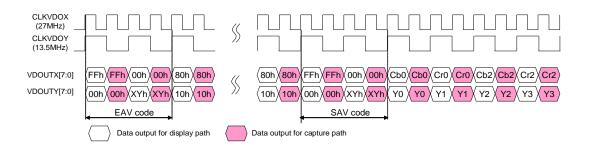

#### **Digital Video Input Format**

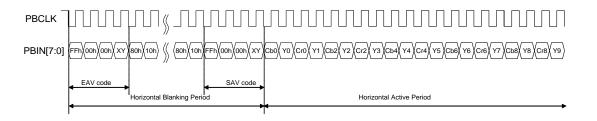

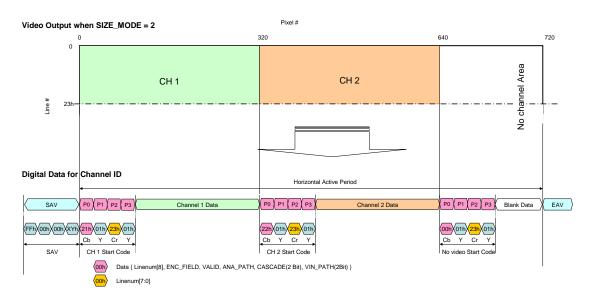

The timing of digital video input is illustrated in Figure 8.

#### FIGURE 8 TIMING DIAGRAM OF ITU-R BT.656 FORMAT FOR DIGITAL VIDEO INPUT

The SAV and EAV sequences are shown in Table 2.

|       | CONDITIC | N          | 656 | FVH VA | LUE | SAV/EAV CODE SEQUENCE |        |       |        |  |

|-------|----------|------------|-----|--------|-----|-----------------------|--------|-------|--------|--|

| FIELD | VERTICAL | HORIZONTAL | F   | v      | Н   | FIRST                 | SECOND | THIRD | FOURTH |  |

|       | Blank    | EAV        | 1   | 1      | 1   | OxFF                  |        |       | 0xF1   |  |

| EVEN  | DIdlik   | SAV        |     |        | 0   |                       |        |       | OxEC   |  |

| EVEN  | Active   | EAV        | 1   | 0      | 1   |                       |        |       | 0xDA   |  |

|       | Active   | SAV        |     |        | 0   |                       | 0x00   | 0x00  | 0xC7   |  |

| ODD   | Blank    | EAV        | 0   | 1      | 1   |                       | 0,00   | 0,00  | 0xB6   |  |

| 000   | DIAIIK   | SAV        | U   | -      | 0   |                       |        |       | OxAB   |  |

| ODD   | Active   | EAV        | 0   | 0      | 1   |                       |        |       | 0x9D   |  |

|       | Active   | SAV        | 0   |        | 0   |                       |        |       | 0x80   |  |

#### TABLE 2 ITU-R BT.656 SAV AND EAV CODE SEQUENCE

#### **Channel ID Decoder**

The TW2837 provides channel ID decoding function for playback input. The TW2837 supports three kinds of channel ID such as User channel ID, Detection channel ID, and auto channel ID. The User channel ID is used for customized information like system information and date. The Detection channel ID is used for detected information of current live input such as motion, video loss, blind and night detection information. The auto channel ID is employed for automatic identification of picture configuration which includes the channel number, analog switch, event, region enable and field/frame mode information. The TW2837 also supports both analog and digital type channel ID during VBI period. The digital channel ID has priority over analog channel ID. The analog type channel ID decoding is enabled via the VBI\_ENA (1x86) register and the digital type channel ID decoding is operated via VBI\_CODE\_EN (1x86) register. Additionally to detect properly the analog channel ID against noise such as VCR source, the channel ID LPF can be enabled via the VBI\_FLT\_EN (1x86) register. The decoded channel ID information is used for auto cropping / strobe function and can also be read through the host interface. The detailed auto cropping / strobe function for playback input will be described at "Cropping Function for Playback" section (page 30) and "Playback Path Control" section (page 50).

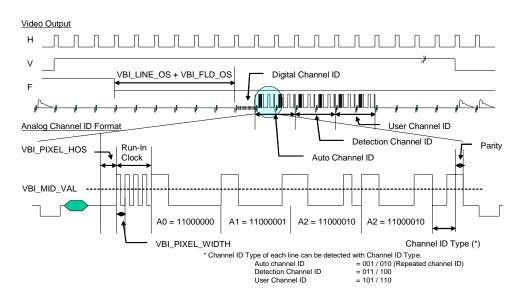

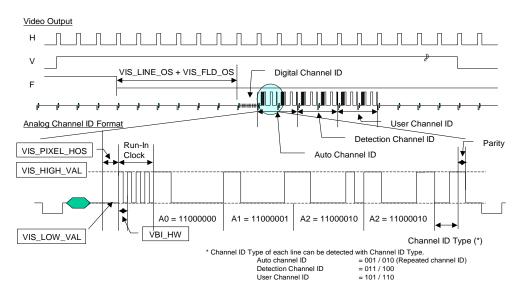

For channel ID detection mode, the TW2837 supports both automatic channel ID detection mode and manual channel ID detection mode. For an automatic channel ID detection mode, the playback input should include a run-in clock. But for a manual channel ID detection mode, the playback input can include a run-in clock or not via VBI\_RIC\_ON (1x86) register. In a manual detection mode, the TW2837 has several related register such as the VBI\_PIXEL\_HOS (1x87) to define horizontal start offset, the VBI\_FLD\_OS (1x88) to define line offset between odd and even field, the VBI\_PIXEL\_HW (1x88) to define pulse width for 1 bit data, the VBI\_LINE\_SIZE (1x89) to define channel ID line size and the VBI\_LINE\_OS (1x89) to define line offset for channel ID. The VBI\_MID\_VAL (1x8A) register is used to define the threshold level between high and low. Even in automatic channel ID detection mode, the line size and bit width can be discriminated by reading the VBI\_LINE\_SIZE and VBI\_PIXEL\_HW register. The **Error! Reference source ot found.** shows the relationship between channel ID and register setting.

This channel ID information can be read through the CHID\_TYPE or CHID\_VALID (1x8B), AUTO\_CHID 0/1/2/3 (1x8C~ 1x8F), DET\_CHID 0/1/2/3/4/5/6/7 (1x98~1x9F), and USER\_CHID 0/1/2/3/4/5/6/7 (1x90~1x97) registers. The CHID\_TYPE register discriminates between the Auto channel ID (CHID\_TYPE = "1") and User channel ID (CHID\_TYPE = "0"). The CHID\_VALID register indicates whether the detected channel ID type is valid or not. The AUTO\_CHID, DET\_CHID and USER\_CHID registers are used to check the decoded channel ID data when the VBI\_RD\_CTL (1x86) register value is "1".

Basically the channel ID is located in VBI period and auto strobe and cropping is executed after channel ID decoding. But for some case, the channel ID can be placed in vertical active period instead of VBI period. For this mode, the TW2837 also supports the channel ID decoding function within vertical active period via the VAV\_CHK (1x88) register and manual cropping function via the MAN\_PBCROP (0xC0) register with proper VDELAY value.

FIGURE 9 THE RELATED REGISTER FOR MANUAL CHANNEL ID DETECTION

#### **CROPPING AND SCALING FUNCTION**

The TW2837 provides two methods to reduce the amount of video pixel data, scaling and cropping. The scaling function provides video image at lower resolution while the cropping function supplies only a portion of the video image. The TW2837 also supports an auto cropping function for playback input with channel ID decoding. The TW2837 has a free scaler for a variable image size in display path, but has a limitation of image size in record path such as Full / QUAD / CIF format.

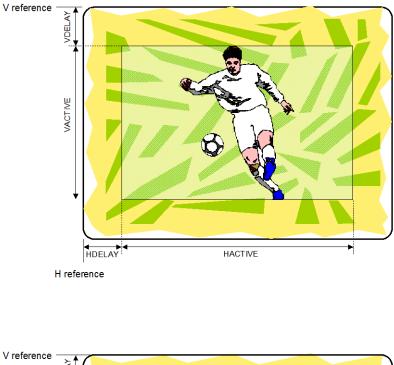

#### **Cropping Function for Live**

The cropping function allows only subsection of a video image to be output. The active video region is determined by the HDELAY, HACTIVE, VDELAY and VACTIVE (0x02 ~ 0x06, 0x12 ~ 0x16, 0x22 ~ 0x26, 0x32 ~ 0x36) register. The first active line is defined by the VDELAY register and the first active pixel is defined by the HDELAY register. The VACTIVE register can be programmed to define the number of active lines in a video field, and the HACTIVE register can be programmed to define the number of active pixels in a video line. This function is used to implement for panning and tilt.

The horizontal delay register HDELAY determines the number of pixel delays between the horizontal reference and the leading edge of the active region. The horizontal active register HACTIVE determines the number of active pixels to be processed. Note that these values are referenced to the pixel number before scaling. Therefore, even if the scaling ratio is changed, the active video region used for scaling remains unchanged as set by the HDEALY and HACTIVE register. In order for the cropping to work properly, the following equation should be satisfied.

HDELAY + HACTIVE < Total number of pixels per line

Where the total number of pixels per line is 858 for NTSC and 864 for PAL

To process full size region, the HDELAY should be set to 32 and HACTIVE set to 720 for both NTSC and PAL system.

The vertical delay register (VDELAY) determines the number of line delays from the vertical reference to the start of the active video lines. The vertical active register (VACTIVE) determines the number of lines to be processed. These values are referenced to the incoming scan lines before the vertical scaling. In order for the vertical cropping to work properly, the following equation should be satisfied.

VDELAY + VACTIVE < Total number of lines per field

Where the total number of lines per field is 262 for NTSC and 312 for PAL

To process full size region, the VDELAY should be set to 6 and VACTIVE set to 240 for NTSC and the VDELAY should be also set to 5 and VACTIVE set to 288 for PAL.

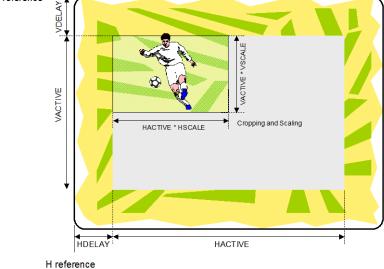

#### **Scaling Function for Live**

The TW2837 includes a high quality free horizontal and vertical down scaler for display path. But the TW2837 cannot use a free scaler function in record path because channel size definition for record path has a limitation such as Full / QUAD / CIF (Please refer to "Record Path Control" section, page 56).

The video images can be downscaled in both horizontal and vertical direction to an arbitrary size. The luminance horizontal scaler includes an anti-aliasing filter to reduce image artifacts in the resized image via the HSFLT (0x80/90/A0/B0, 0x85/95/A5/B5 and 0x8A/9A/AA/BA) register and a 32 poly-phase filter to accurately interpolate the value of a pixel. This results in more aesthetically pleasing video as well as higher compression ratio in bandwidth-limited application.

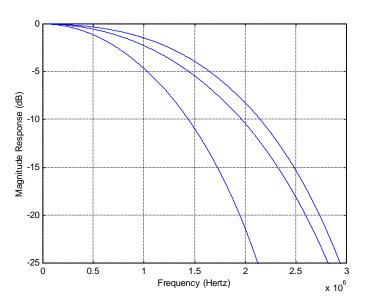

The following Figure 10 shows the frequency response of anti-aliasing filter for horizontal scaling.

FIGURE 10 THE FREQUENCY RESPONSE OF ANTI-ALIASING FILTER FOR HORIZONTAL SCALING

Similarly, the vertical scaler also contains an anti-aliasing filter controlled via the VSFLT (0x80/90/A0/B0, 0x85/95/A5/B5 and 0x8A/9A/AA/BA) register and 16 poly-phase filters for down scaling. The filter characteristics are shown in the Figure 11.

FIGURE 11 THE CHARACTERISTICS OF ANTI-ALIASING FILTER FOR VERTICAL SCALING

Down scaling is achieved by programming the scaling register HSCALE and VSCALE (0x81 ~ 0x84, 0x91 ~ 0x94, 0xA1 ~ 0xA4, 0xB1 ~ 0xB4) register. When no scaled video image, the TW2837 will output the number of pixels as specified by the HACTIVE and VACTIVE (0x02 ~ 0x06, 0x12 ~ 0x16, 0x22 ~ 0x26, 0x32 ~ 0x36) register. If the number of output pixels required is smaller than the number specified by the HACTIVE/VACTIVE register, the 16bit HSCALE/VSCALE register is used to reduce the output pixels to the desired number.

The following equation is used to determine the horizontal scaling ratio to be written into the 16bit HSCALE register.

HSCALE =  $[N_{pixel\_desired} / HACTIVE] * (2^16 - 1)$

Where N<sub>pixel\_desired</sub> is the desired number of active pixels per line

For example, to scale picture from full size (HACTIVE = 720) to CIF (360 pixels), the HSCALE value can be found as:

$$HSCALE = [360/720] * (2^{16} - 1) = 0x7FFF$$

The following equation is used to determine the vertical scaling ratio to be written into the 16bit VSCALE register.

VSCALE =  $[N_{line\_desired} / VACTIVE] * (2^16 - 1)$

Where  $N_{\text{line\_desired}}$  is the desired number of active lines per field

For example, to scale picture from full size (VACTIVE = 240 lines for NTSC and 288 lines for PAL) to CIF (120 lines for NTSC and 144 lines for PAL), the VSCALE value can be found as:

VSCALE =  $[120 / 240] * (2^16 - 1) = 0x7FFF$  for NTSC

VSCALE = [144 / 288] \* (2^16 - 1) = 0x7FFF for PAL

The scaling ratios of popular case are listed in Table 3.

| SCALING RATIO | FORMAT | OUTPUT RESOLUTION | HSCALE | VSCALE |

|---------------|--------|-------------------|--------|--------|

| 1             | NTSC   | 720x480           | OxFFFF | OxFFFF |

| ±             | PAL    | 720x576           | OxFFFF | OxFFFF |

| 1 /0 (CIE)    | NTSC   | 360x240           | 0x7FFF | 0x7FFF |

| 1/2 (CIF)     | PAL    | 360x288           | 0x7FFF | 0x7FFF |

| 1 (4 (OCIE)   | NTSC   | 180x120           | 0x3FFF | 0x3FFF |

| 1/4 (QCIF)    | PAL    | 180x144           | 0x3FFF | 0x3FFF |

The effect of scaling and cropping is shown in Figure 12.

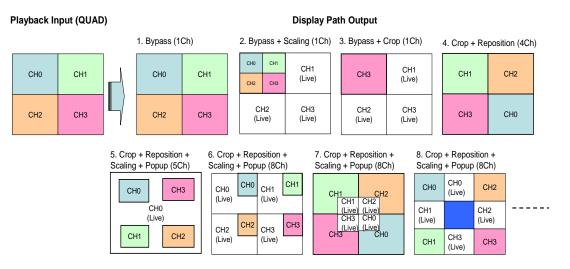

#### **Cropping and Scaling Function for Playback**

The TW2837 supports an auto cropping function with channel ID decoding for playback input. Each channel with the multiplexed playback input can be mapped into the desired position with the auto cropping function.

If the PB\_AUTO\_EN (1x16) = "0", the TW2837 is set to a manual cropping mode so that user can control cropping with VDELAY\_PB and HDELAY\_PB ( $0x8B \sim 0x8F$ ,  $0x9B \sim 9F$ ,  $0xAB \sim AF$  and  $0xBB \sim BF$ ) register. If the PB\_AUTO\_EN = "1", the TW2837 is set into an auto cropping mode. In this mode, the desired channel can be chosen by PB\_CH\_NUM register (1x16, 1x1E, 1x26, 1x2E) and it will be cropped automatically to horizontal and vertical direction in playback input. The TW2837 has several related registers for this mode such as PB\_CROP\_MD, PB\_ACT\_MD and MAN\_PBCROP (0xC0). The PB\_CROP\_MD defines the record mode of the playback input such as normal record mode or DVR record mode (Please refer to "Record Path Control" section, page 56). The PB\_ACT\_MD defines an active pixel size of horizontal direction such as 720 / 704 / 640 pixels. The MAN\_PBCROP controls the horizontal and vertical starting offset in the auto cropping mode with HDELAY\_PB and VDELAY\_PB registers. It is useful in case that the encoded channel ID is located at vertical active area in ITU-R BT.656 data stream.

CH0 : PB\_CH\_NUM0 = 0, (cropping H/V) CH1 : PB\_CH\_NUM1 = 1, (cropping V) CH2 : PB\_CH\_NUM2 = 2, (cropping H) CH3 : PB\_CH\_NUM3 = 3, (No cropping)

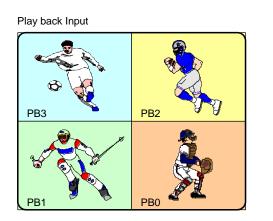

FIGURE 13 THE EFFECT OF AUTO CROPPING FUNCTION

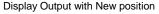

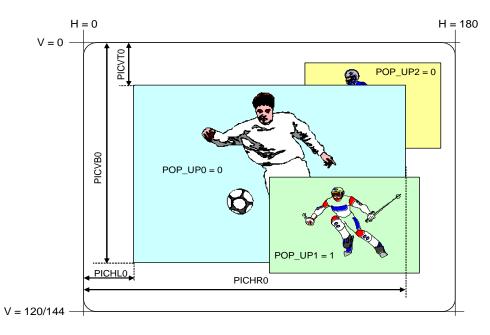

The TW2837 includes four additional free down scaler for playback path so that the video image from playback input can be downscaled to an arbitrary size in both horizontal and vertical direction. Therefore, using this cropping and scaling function, the TW2837 supports free size and positioning function for both live and playback input in display path. The following Figure 14 shows the effect of scaling and cropping operation in playback.

PB0 : PB\_CH\_NUM0 = 0, (cropping H/V + Scaling) PB2 : PB\_CH\_NUM2 = 2, (cropping H)

Display Scaling Output with New position

PB1 : PB\_CH\_NUM1 = 1, (cropping V + Scaling) PB3 : PB\_CH\_NUM3 = 3, (No cropping)

#### FIGURE 14 THE EFFECT OF SCALING FUNCTION IN PLAYBACK

### **Motion Detection**

The TW2837 supports motion detector individually for 4 analog video inputs. The built-in motion detection algorithm uses the difference of luminance level between current and reference field. The TW2837 also supports blind and night input detection for 4 analog video inputs.

To detect motion properly according to situation, the TW2837 provides several sensitivity and velocity control parameters for each motion detector. The TW2837 supports manual strobe function to update motion detection so that it is more appropriate for user-defined motion sensitivity control.

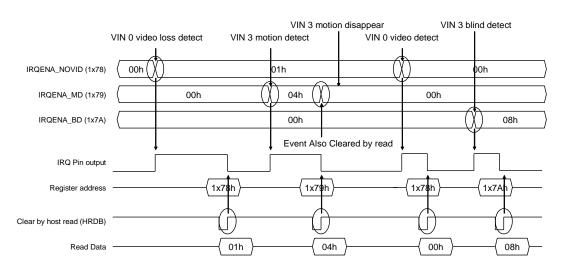

When motion, blind and night input are detected in any video inputs, the TW2837 provides the interrupt request to host via the IRQ pin. The host processor can take the information of motion, blind or night detection by accessing the IRQENA\_MD (1x79), IRQENA\_BD (1x7A) and the IRQENA\_ND (1x7B) register. This status information is updated in the vertical blank period of each input.

The TW2837 also provides the motion, blind and night detection result through the DLINKI and MPP0/1 pin with the control of MPP\_MD (1xB0) and MPP\_SET (1xB1, 1xB3 and 1xB5) register. The TW2837 supports an overlay function to display the motion detection result in the picture with 2D arrayed box.

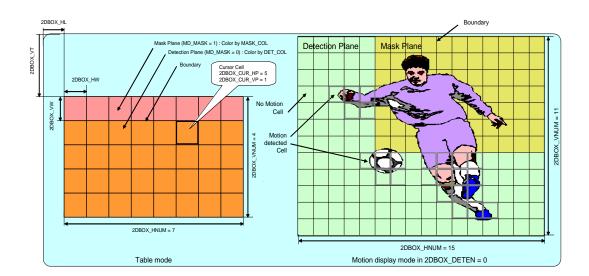

#### MASK AND DETECTION REGION SELECTION

The motion detection algorithm utilizes the full screen video data and detects individual motion of 16x12 cells. This full screen for motion detection consists of 704 pixels and 240 lines for NTSC and 288 lines for PAL. Starting pixel in horizontal direction can be shifted from 0 to 15 pixels using the MD\_ALIGN (2x82, 2xA2, 2xC2, and 2xE2) register.

Each cell can be masked via the MD\_MASK (2x86 ~ 2x9D, 2xA6 ~ 2xBD, 2xC6 ~ 2xDD, 2xE6 ~ 2xFD) register as illustrated in Figure 15. If the mask bit in specific cell is programmed to high, the related cell is ignored for motion detection.

|              | 704 Pixels (44 Pixels/Cell) |                     |                     |                     |                            |                     |                     |                     |                     |                     |                      |                      |                      |                      |                      |                      |

|--------------|-----------------------------|---------------------|---------------------|---------------------|----------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| (je          | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK0                       | MASK0               | MASK0               | MASK0               | MASK0                      | MASK0               | MASK0               | MASK0               | MASK0               | MASK0               | MASK0                | MASK0                | MASK0                | MASK0                | MASK0                | MASK0                |

|              | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| Lines/Cell)  | MD_<br>MASK1<br>[0]         | MD_<br>MASK1<br>[1] | MD_<br>MASK1<br>[2] | MD_<br>MASK1<br>[3] | [4]<br>MD_<br>MASK1<br>[4] | MD_<br>MASK1<br>[5] | MD_<br>MASK1<br>[6] | MD_<br>MASK1        | MD_<br>MASK1<br>[8] | MD_<br>MASK1<br>[9] | MD_<br>MASK1<br>[10] | MD_<br>MASK1<br>[11] | MD_<br>MASK1<br>[12] | MD_<br>MASK1<br>[13] | MD_<br>MASK1<br>[14] | MD_<br>MASK1<br>[15] |

| (24          | MD_<br>MASK2<br>[0]         | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2               | MD_<br>MASK2        | MD_<br>MASK2        | [7]<br>MD_<br>MASK2 | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         |

| 50Hz         | MD_                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MASK3                       | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | [0]                         | MASK3               | MASK3               | MASK3               | MASK3                      | MASK3               | MASK3               | MASK3               | MASK3               | MASK3               | MASK3                | MASK3                | MASK3                | MASK3                | MASK3                | MASK3                |

| Lines for    | MD_                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MASK4                       | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | [0]                         | MASK4               | MASK4               | MASK4               | MASK4                      | MASK4               | MASK4               | MASK4               | MASK4               | MASK4               | MASK4                | MASK4                | MASK4                | MASK4                | MASK4                | MASK4                |

| 288 Li       | MD_<br>MASK5                | [1]<br>MD_<br>MASK5 | [2]<br>MD_<br>MASK5 | [3]<br>MD_<br>MASK5 | [4]<br>MD_<br>MASK5        | [5]<br>MD_<br>MASK5 | [6]<br>MD_<br>MASK5 | [7]<br>MD_<br>MASK5 | [8]<br>MD_<br>MASK5 | [9]<br>MD_<br>MASK5 | [10]<br>MD_<br>MASK5 | [11]<br>MD_<br>MASK5 | [12]<br>MD_<br>MASK5 | [13]<br>MD_<br>MASK5 | [14]<br>MD_<br>MASK5 | [15]<br>MD_<br>MASK5 |

| Lines/Cell), | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK6                       | MASK6               | MASK6               | MASK6               | MASK6                      | MASK6               | MASK6               | MASK6               | MASK6               | MASK6               | MASK6                | MASK6                | MASK6                | MASK6                | MASK6                | MASK6                |

|              | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK7                       | MASK7               | MASK7               | MASK7               | MASK7                      | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7                | MASK7                | MASK7                | MASK7                | MASK7                | MASK7                |

| 60Hz (20     | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK8                       | MASK8               | MASK8               | MASK8               | MASK8                      | MASK8               | MASK8               | MASK8               | MASK8               | MASK8               | MASK8                | MASK8                | MASK8                | MASK8                | MASK8                | MASK8                |

| for          | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK9                       | MASK9               | MASK9               | MASK9               | MASK9                      | MASK9               | MASK9               | MASK9               | MASK9               | MASK9               | MASK9                | MASK9                | MASK9                | MASK9                | MASK9                | MASK9                |

|              | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK10                      | MASK10              | MASK10              | MASK10              | MASK10                     | MASK10              | MASK10              | MASK10              | MASK10              | MASK10              | MASK10               | MASK10               | MASK10               | MASK10               | MASK10               | MASK10               |

| 240          | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|              | MD_                         | MD_                 | MD_                 | MD_                 | MD_                        | MD_                 | MD_                 | MD_                 | MD_                 | MD_                 | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  | MD_                  |

|              | MASK11                      | MASK11              | MASK11              | MASK11              | MASK11                     | MASK11              | MASK11              | MASK11              | MASK11              | MASK11              | MASK11               | MASK11               | MASK11               | MASK11               | MASK11               | MASK11               |

| _            | [0]                         | [1]                 | [2]                 | [3]                 | [4]                        | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

#### FIGURE 15 MOTION MASK AND DETECTION CELL

The MD\_MASK register has different function for reading and writing mode. For writing mode, setting "1" to MD\_MASK register inhibits the specific cell from detecting motion. For reading mode, the MD\_MASK register has three kinds of information depending on the MASK\_MODE (2x82, 2xA2, 2xC2, and 2xE2) register. For MASK\_MODE = "0", the state of MD\_MASK register means the result of VIN\_A motion detection that "1" indicates detecting motion and "0" denotes no motion detection in the cell. For MASK\_MODE = "1", the state of MD\_MASK register means the result of VIN\_B motion detection. For MASK\_MODE = "2 or 3", the state of MD\_MASK register means masking information of cell.

#### **SENSITIVITY CONTROL**

The motion detector has 4 sensitivity parameters to control threshold of motion detection such as the level sensitivity via the MD\_LVSENS (2x83, 2xA3, 2xC3, and 2xE3) register, the spatial sensitivity via the MD\_SPSENS (2x85, 2xA5, 2xC5, 2xE5) and MD\_CELSENS (2x83, 2xA3, 2xC3, and 2xE3) register, and the temporal sensitivity parameter via the MD\_TMPSENS (2x85, 2xA5, 2xC5, and 2xE5) register.

#### **Level Sensitivity**

In built-in motion detection algorithm, the motion is detected when luminance level difference between current and reference field is greater than MD\_LVSENS value. Motion detector is more sensitive for the smaller MD\_LVSENS value and less sensitive for the larger. When the MD\_LVSENS is too small, the motion detector may be weak in noise.

#### **Spatial Sensitivity**

The TW2837 uses 192 (16x12) detection cells in full screen for motion detection. Each detection cell is composed of 44 pixels and 20 lines for NTSC and 24 lines for PAL. Motion detection from only luminance level difference between two fields is very weak in spatial random noise. To remove the fake motion detection from the random noise, the TW2837 supports a spatial filter via the MD\_SPSENS register which defines the number of detected cell to decide motion detection in full size image. The large MD\_SPSENS value increases the immunity of spatial random noise.

Each detection cell has 4 sub-cells also. Actually motion detection of each cell comes from comparison of sub-cells in it. The MD\_CELSENS defines the number of detected sub-cell to decide motion detection in cell. That is, the large MD\_CELSENS value increases the immunity of spatial random noise in detection cell.

#### **Temporal Sensitivity**

Similarly, temporal filter is used to remove the fake motion detection from the temporal random noise. The MD\_TMPSENS regulates the number of taps in the temporal filter to control the temporal sensitivity so that the large MD\_TMPSENS value increases the immunity of temporal random noise.

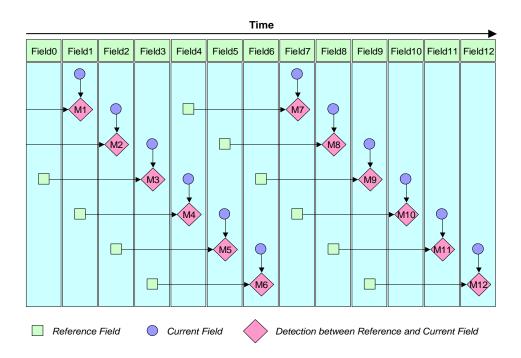

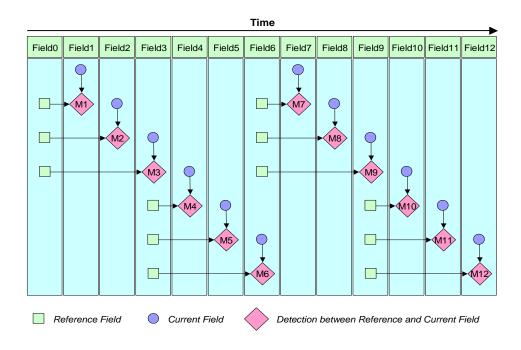

#### **VELOCITY CONTROL**

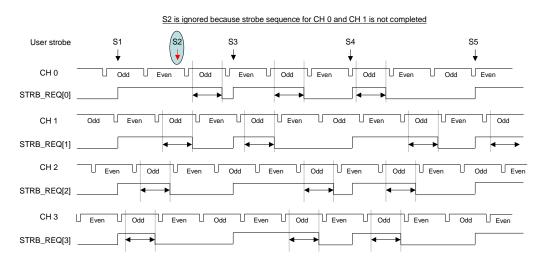

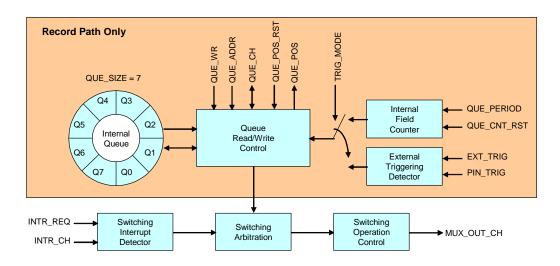

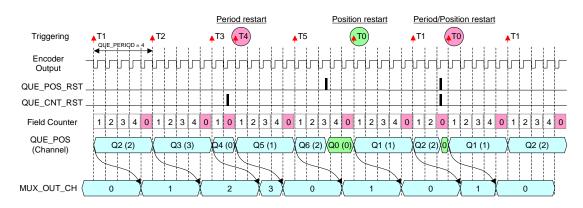

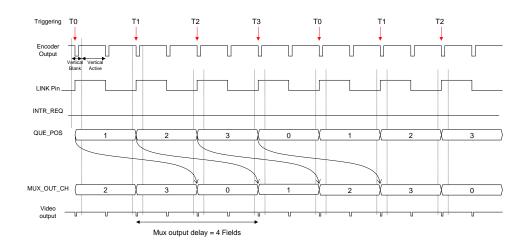

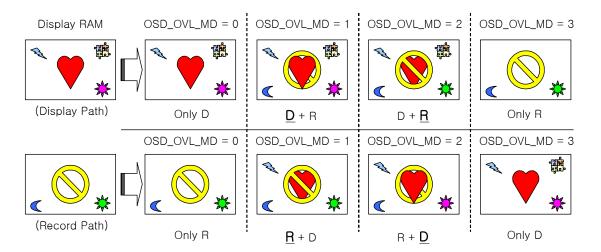

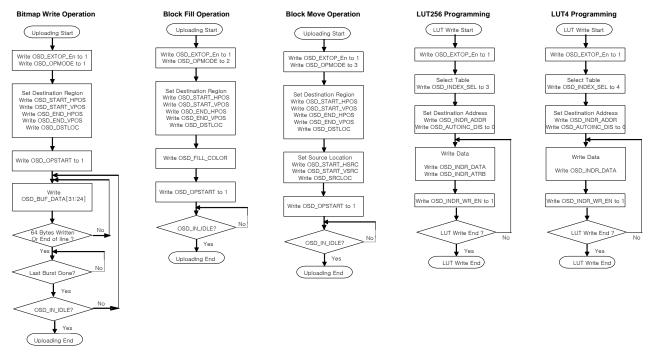

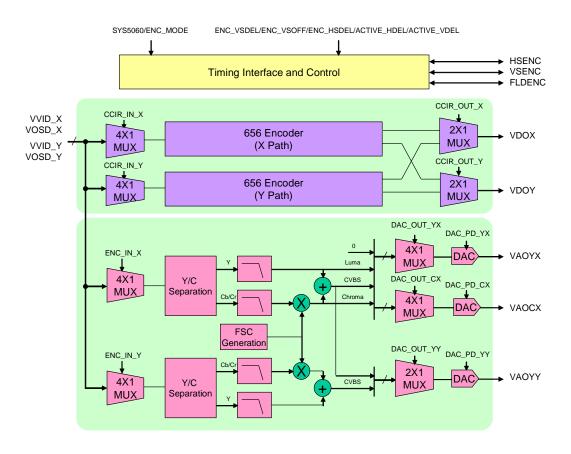

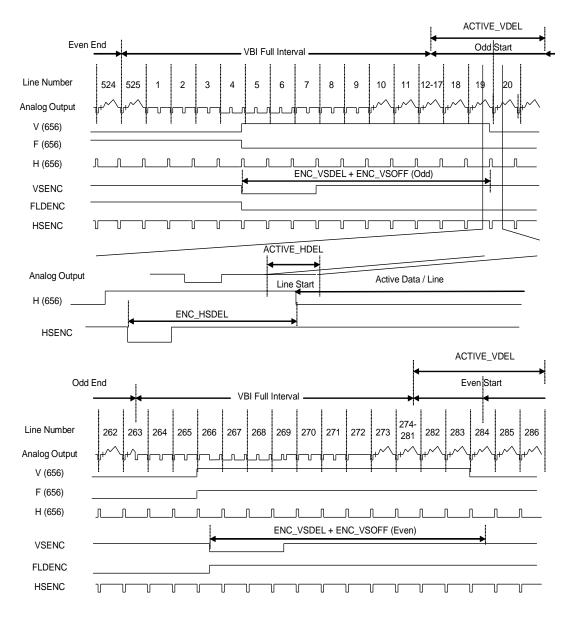

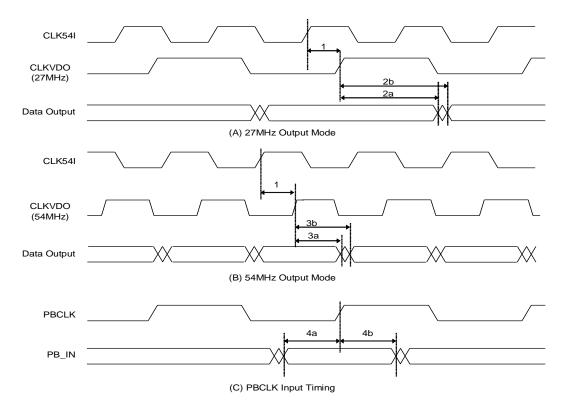

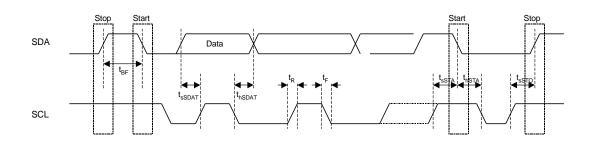

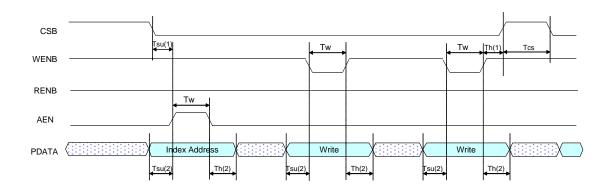

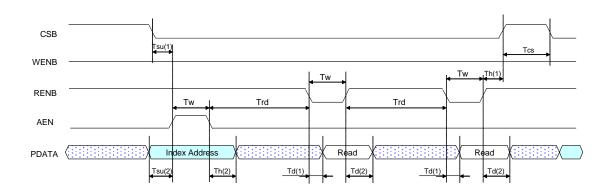

The motion has various velocities. That is, in a fast motion an object appears and disappears rapidly between the adjacent fields while in a slow motion it is to the contrary. As the built-in motion detection algorithm uses the only luminance level difference between two adjacent fields, a slow motion is inferior in detection rate to a fast motion. To compensate this weakness, MD\_SPEED (2x84, 2xA4, 2xC4, and 2xE4) parameter is used which is controllable up to 64 fields. MD\_SPEED parameter adjusts the field interval in which the luminance level is compared. Thus, for detection of a fast motion a small value is needed and for a slow motion a large value is required. The parameter MD\_SPEED value should be greater than MD\_TMPSENS value.