# V850ES/JG3-L (on-chip USB controller)

User's Manual: Hardware

RENESAS MCU V850ES/Jx3-L Microcontrollers

μPD70F3794 μPD70F3795 μPD70F3796

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

## Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

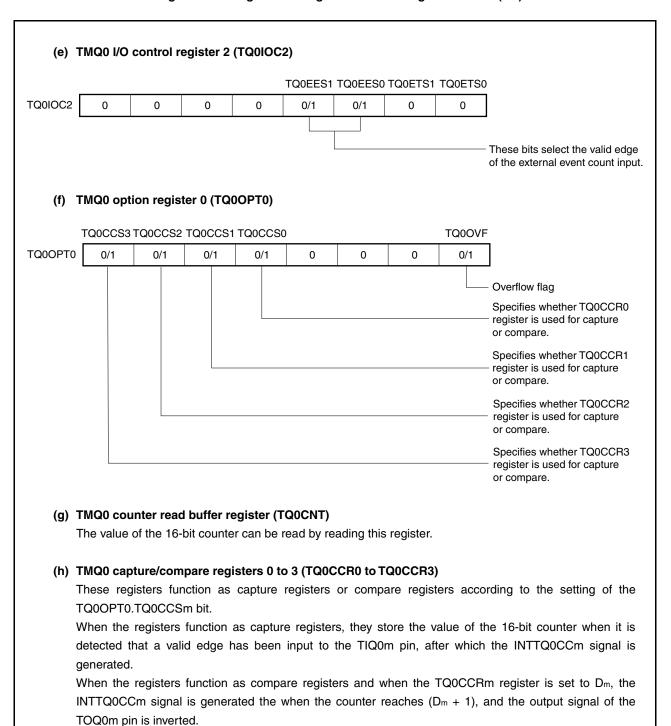

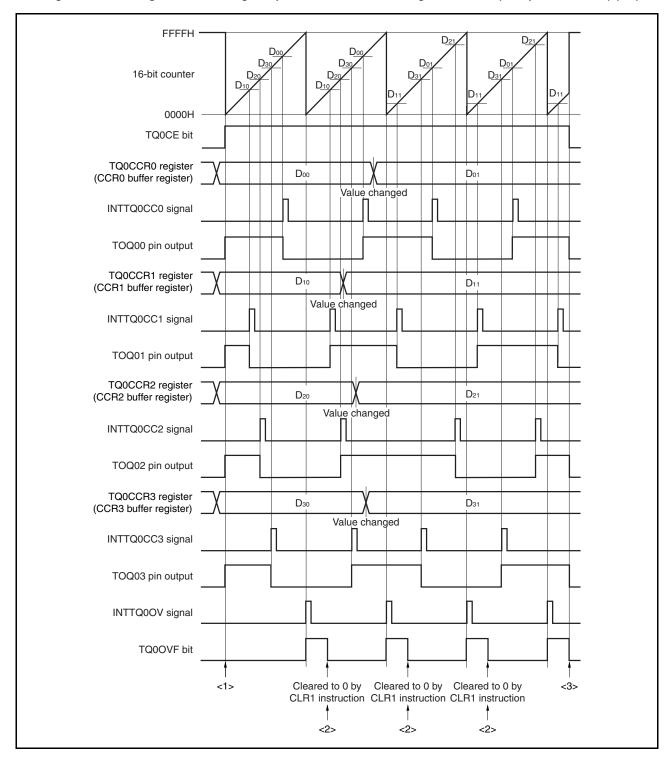

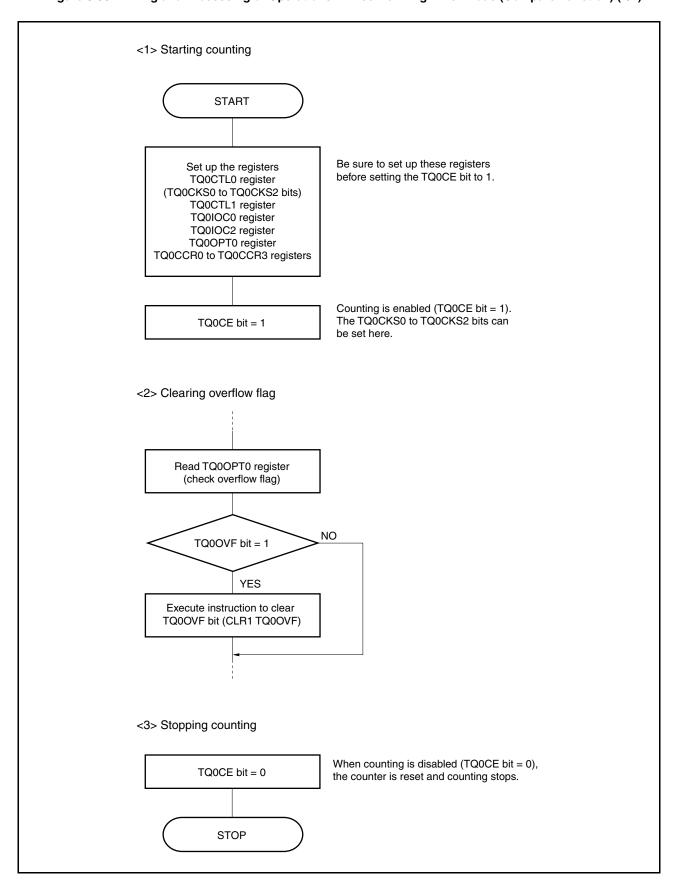

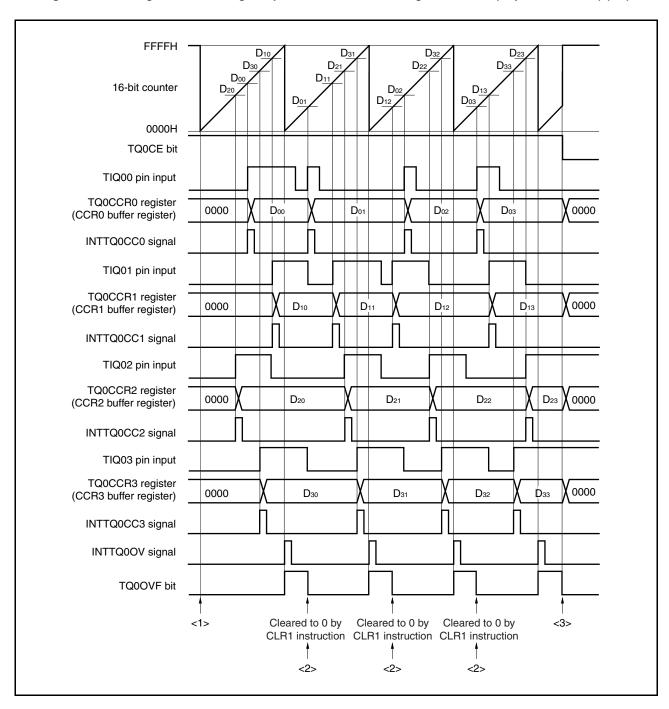

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

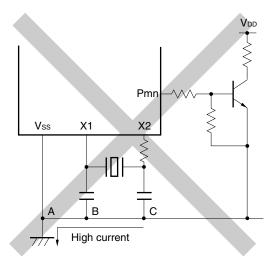

#### NOTES FOR CMOS DEVICES -

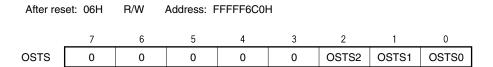

# (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

## ③ PRECAUTION AGAINST ESD

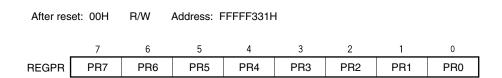

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

# **4** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

## (6) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

# How to Use This Manual

Readers

This manual is intended for users who wish to understand the functions of the V850ES/JG3-L and design application systems using these products.

**Purpose**

This manual is intended to give users an understanding of the hardware functions of the V850ES/JG3-L shown in the **Organization** below.

Organization

This manual is divided into two parts: Hardware (this manual) and Architecture (V850ES Architecture User's Manual).

## Hardware

- Pin functions

- CPU function

- On-chip peripheral functions

- Flash memory programming

- Electrical specifications

## Architecture

- Data types

- Register set

- Instruction format and instruction set

- · Interrupts and exceptions

- Pipeline operation

#### **How to Read This Manual**

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To understand the overall functions of the V850ES/JG3-L

$\rightarrow\!\mbox{Read}$  this manual according to the <code>CONTENTS</code>.

To find the details of a register where the name is known

→ Use APPENDIX C REGISTER INDEX.

# Register format

→The name of the bit whose number is in angle brackets (<>) in the figure of the register format of each register is defined as a reserved word in the device file.

To understand the details of an instruction function

→ Refer to the **V850ES Architecture User's Manual** available separately.

To know the electrical specifications of the V850ES/JG3-L

$\rightarrow$  See CHAPTER 33 ELECTRICAL SPECIFICATIONS ( $\mu$  PD70F3794, 70F3795, 70F3796)

The "yyy bit of the xxx register" is described as the "xxx.yyy bit" in this manual. Note with caution that if "xxx.yyy" is described as is in a program, however, the compiler/assembler cannot recognize it correctly.

The mark <R> shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what: " field.

**Conventions** Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on the

bottom

**Note**: Footnote for item marked with **Note** in the text

Caution: Information requiring particular attention

**Remark**: Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory capacity):

K (kilo):  $2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$

G (giga):  $2^{30} = 1,024^3$

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Documents related to V850ES/JG3-L

| Document Name                                                | Document No. |

|--------------------------------------------------------------|--------------|

| V850ES Architecture User's Manual                            | U15943E      |

| V850ES/JG3-L (on-chip USB controller) Hardware User's Manual | This manual  |

# Documents related to development tools

| Document Name                               | Document Name                                   |         |

|---------------------------------------------|-------------------------------------------------|---------|

| QB-V850ESJX3L In-Circuit Emulator           | To be prepared                                  |         |

| QB-V850MINI, QB-V850MINIL On-Chip Debu      | g Emulator                                      | U17638E |

| QB-MINI2 On-Chip Debug Emulator with Prog   | ramming Function                                | U18371E |

| CA850 Ver. 3.20 C Compiler Package          | Operation                                       | U18512E |

|                                             | C Language                                      | U18513E |

|                                             | Assembly Language                               | U18514E |

|                                             | Link Directives                                 | U18415E |

| PM+ Ver. 6.30 Project Manager               |                                                 | U18416E |

| ID850QB Ver. 3.40 Integrated Debugger       | Operation                                       | U18604E |

| SM850 Ver. 2.50 System Simulator            | Operation                                       | U16218E |

| SM850 Ver. 2.00 or Later System Simulator   | External Part User Open Interface Specification | U14873E |

| SM+ System Simulator                        | Operation                                       | U18601E |

|                                             | User Open Interface                             | U18212E |

| RX850 Ver. 3.20 Real-Time OS                | 20 Real-Time OS Basics                          |         |

|                                             | Installation                                    | U17419E |

|                                             | Technical                                       | U13431E |

|                                             | Task Debugger                                   | U17420E |

| RX850 Pro Ver. 3.21 Real-Time OS            | Basics                                          | U18165E |

|                                             | Installation                                    | U17421E |

|                                             | Task Debugger                                   | U17422E |

| AZ850 Ver. 3.30 System Performance Analyzer |                                                 | U17423E |

| PG-FP5 Flash Memory Programmer              |                                                 | U18865E |

## **Other Documents**

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| RENESAS MICROCOMPUTER GENERAL CATALOG                                              | R01CS0001E   |

| Semiconductor Package Mount Manual                                                 | Note         |

| Quality Grades on Renesas Semiconductor Devices                                    | C11531E      |

| Renesas Semiconductor Device Reliability/Quality Control<br>System                 | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

**Note** See the "Semiconductor Package Mount Manual" website (http://www.renesas.com/products/package/manual/index.jsp).

Caution The related documents listed above are subject to change without notice.

Be sure to use the latest version of each document when designing.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

IECUBE is a registered trademark of Renesas Electronics Corporation in Japan and Germany.

MINICUBE is a registered trademark of Renesas Electronics Corporation in Japan and Germany or a trademark in the United States of America.

**EEPROM** is a trademark of Renesas Electronics Corporation

Applilet is a registered trademark of Renesas Electronics in Japan, Germany, Hong Kong, China, the Republic of Korea, the United Kingdom, and the United States of America.

Windows and Windows NT are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

PC/AT is a trademark of International Business Machines Corporation.

SPARCstation is a trademark of SPARC International, Inc.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

TRON is an abbreviation of The Realtime Operating System Nucleus.

ITRON is an abbreviation of Industrial TRON.

# Table of Contents

| CHAPTE | R 1 INTRODUCTION                                                                | 21  |

|--------|---------------------------------------------------------------------------------|-----|

| 1.1    | General                                                                         | 21  |

| 1.2    | Features                                                                        | 23  |

| 1.3    | Application Fields                                                              | 25  |

| 1.4    | Ordering Information                                                            | 25  |

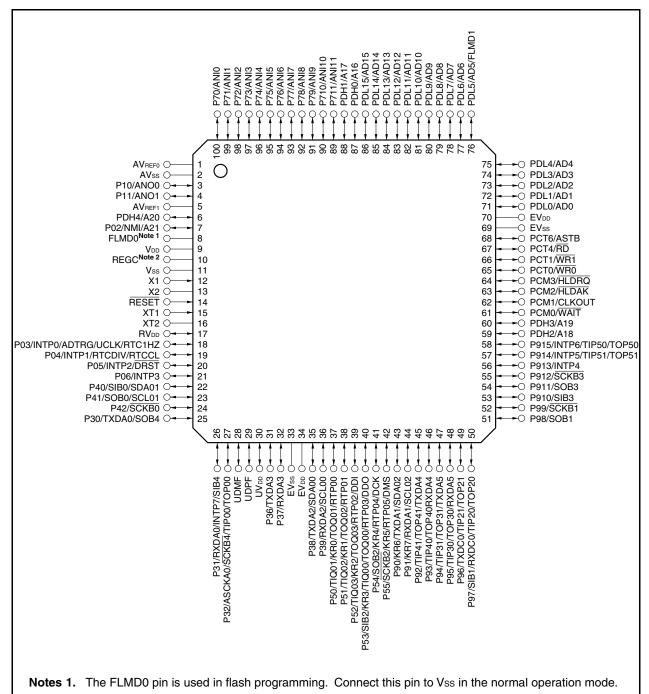

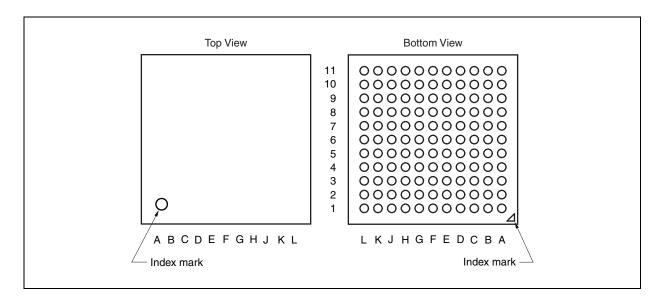

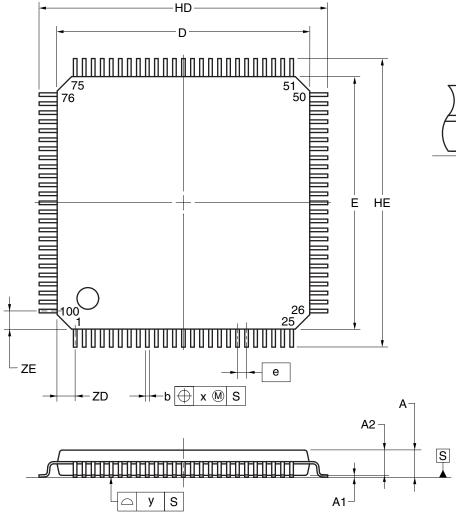

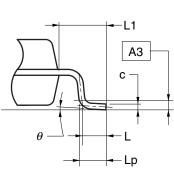

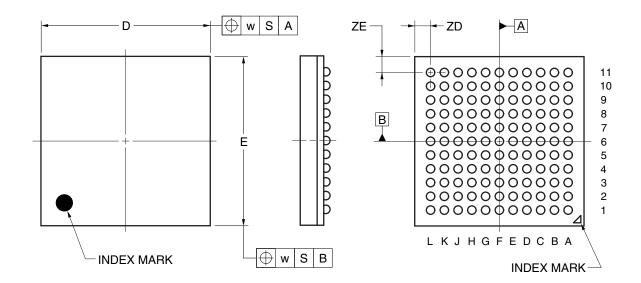

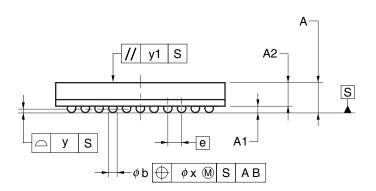

| 1.5    | Pin Configuration (Top View)                                                    | 26  |

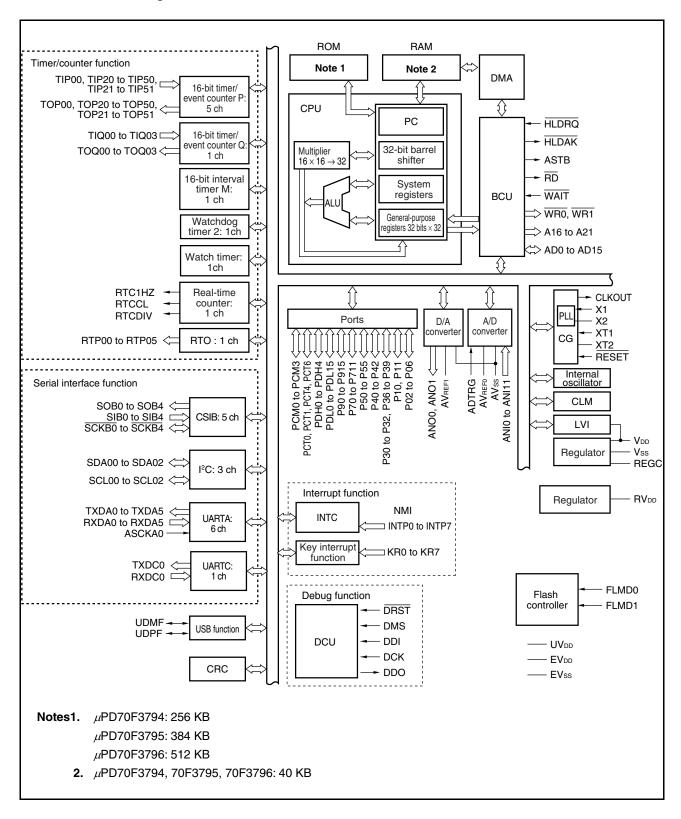

| 1.6    | Function Block Configuration                                                    | 30  |

|        | 1.6.1 Internal block diagram                                                    | 30  |

|        | 1.6.2 Internal units                                                            | 31  |

| СНАРТЕ | ER 2 PIN FUNCTIONS                                                              | 34  |

| 2.1    | List of Pin Functions                                                           | 34  |

| 2.2    | Pin States                                                                      | 44  |

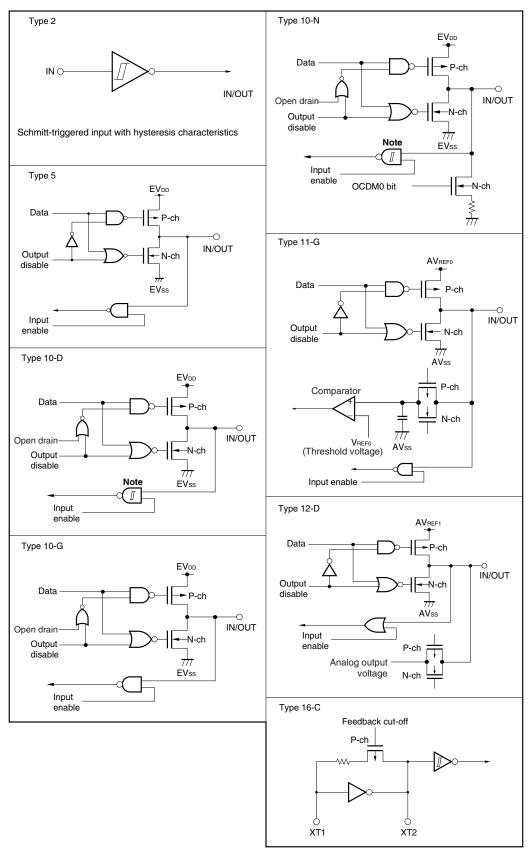

| 2.3    | Pin I/O Circuit Types, I/O Buffer Power Supplies, and Connection of Unused Pins | 45  |

| 2.4    | Cautions                                                                        | 49  |

| СНАРТЕ | ER 3 CPU FUNCTION                                                               | 50  |

| 3.1    | Features                                                                        | 50  |

| 3.2    | CPU Register Set                                                                | 51  |

|        | 3.2.1 Program register set                                                      | 52  |

|        | 3.2.2 System register set                                                       | 53  |

| 3.3    | Operation Modes                                                                 | 59  |

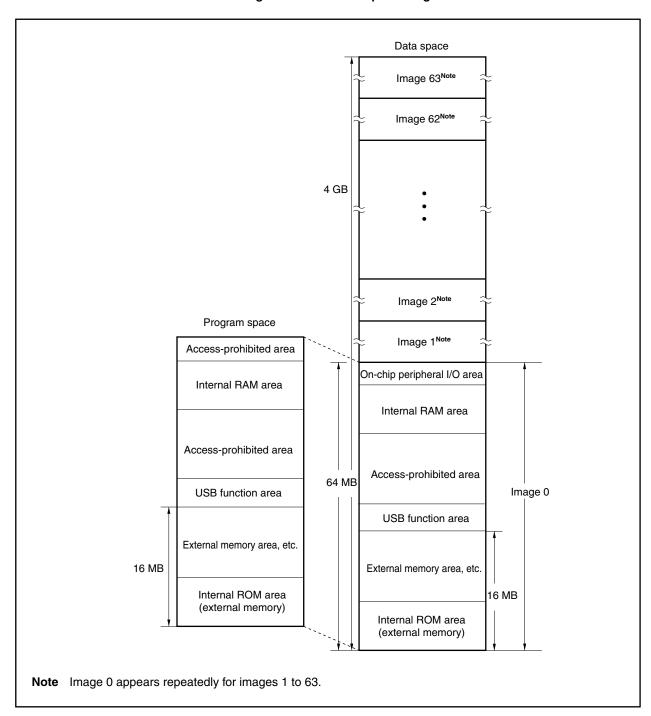

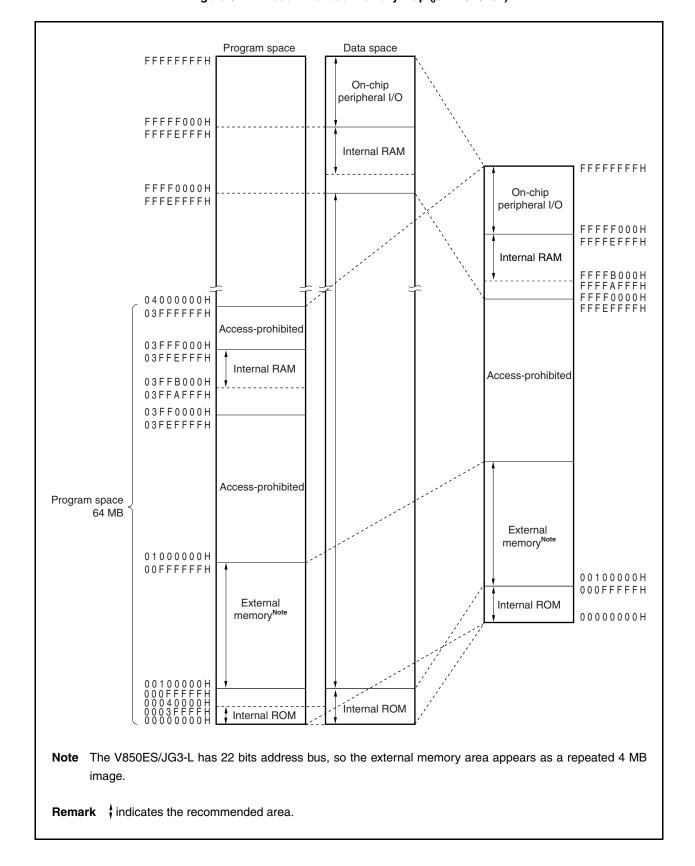

| 3.4    | Address Space                                                                   | 60  |

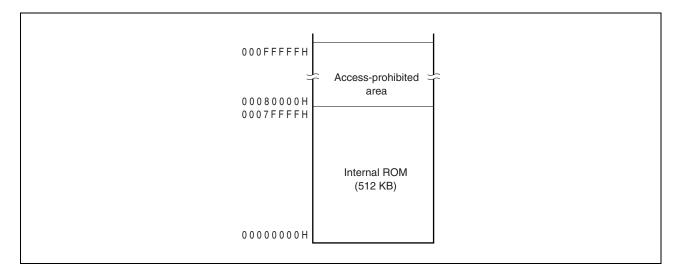

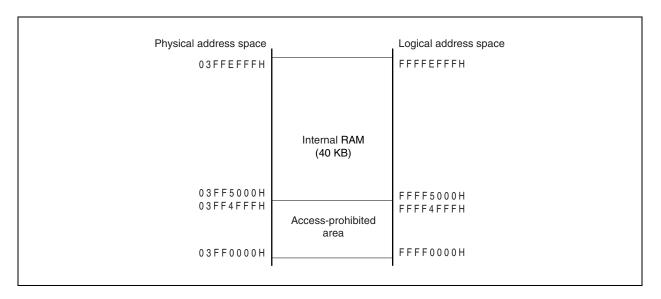

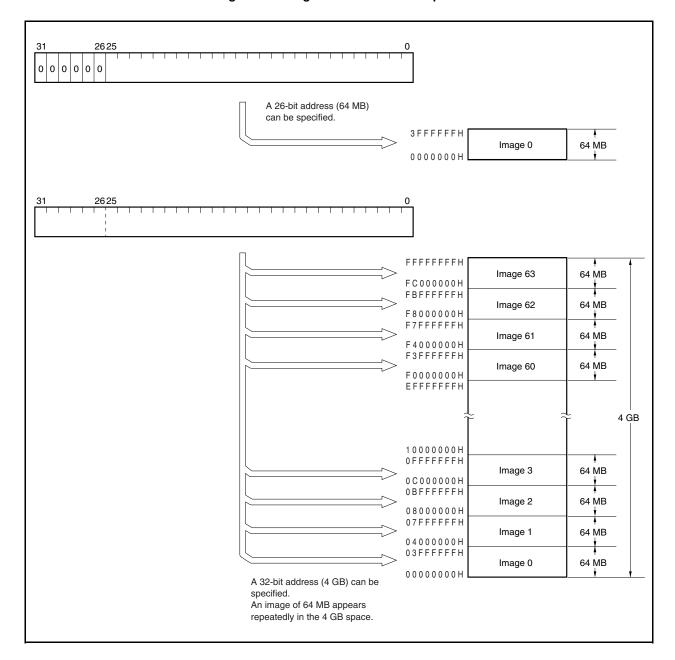

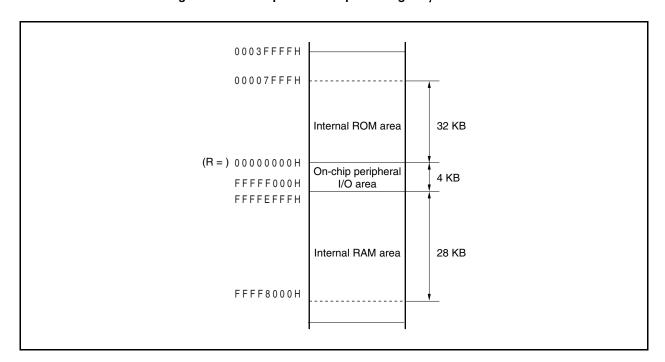

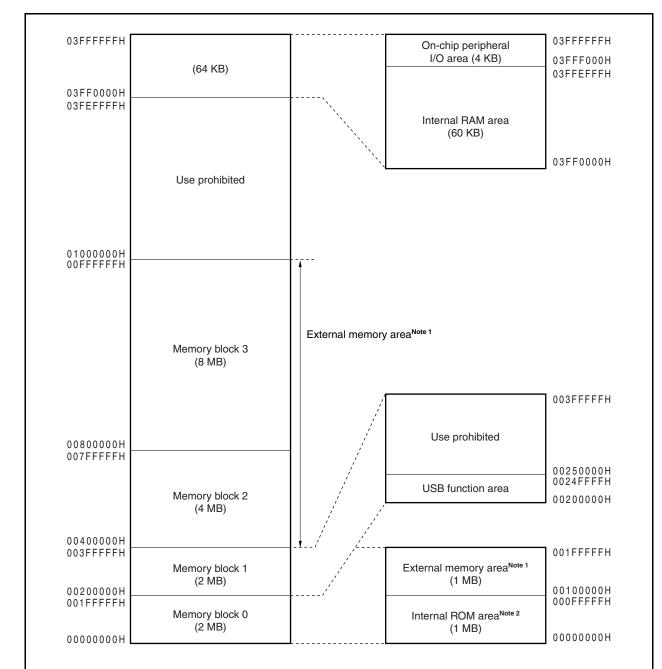

|        | 3.4.1 CPU address space                                                         | 60  |

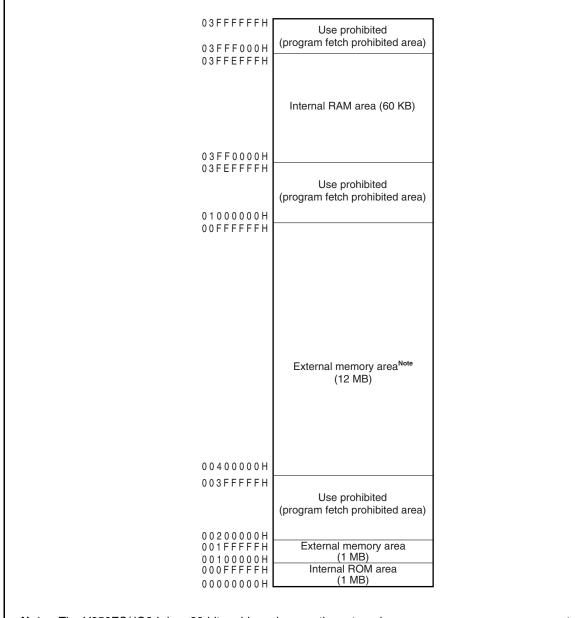

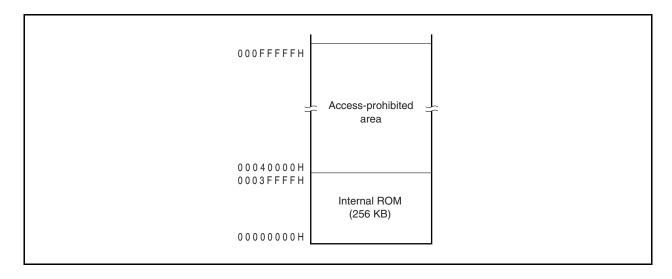

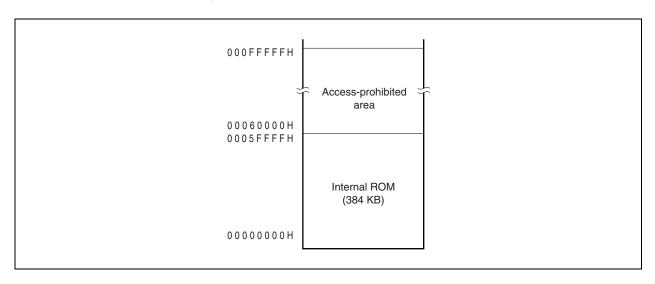

|        | 3.4.2 Memory map                                                                | 61  |

|        | 3.4.3 Areas                                                                     | 63  |

|        | 3.4.4 Wraparound of data space                                                  | 67  |

|        | 3.4.5 Recommended use of address space                                          | 67  |

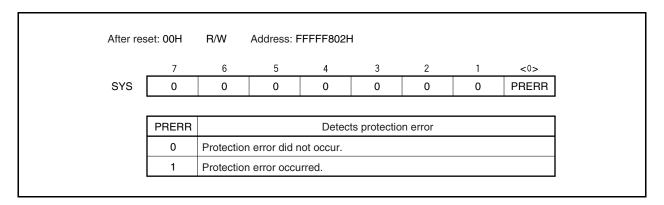

|        | 3.4.6 Peripheral I/O registers                                                  | 71  |

|        | 3.4.7 Special registers                                                         | 82  |

|        | 3.4.8 Registers to be set first                                                 | 86  |

|        | 3.4.9 Cautions                                                                  | 87  |

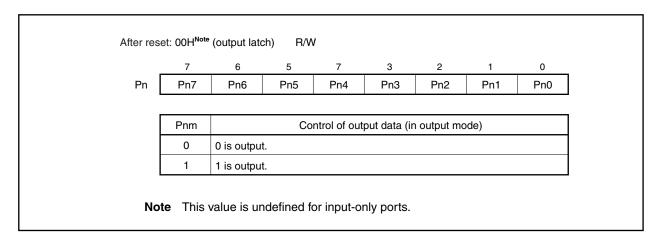

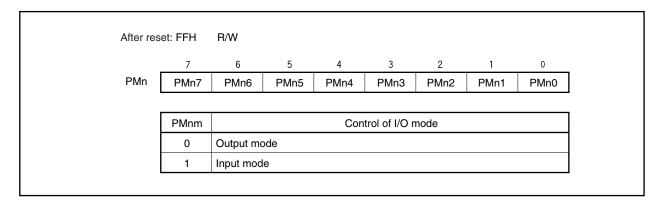

| СНАРТЕ | ER 4 PORT FUNCTIONS                                                             | 89  |

| 4.1    | Features                                                                        | 89  |

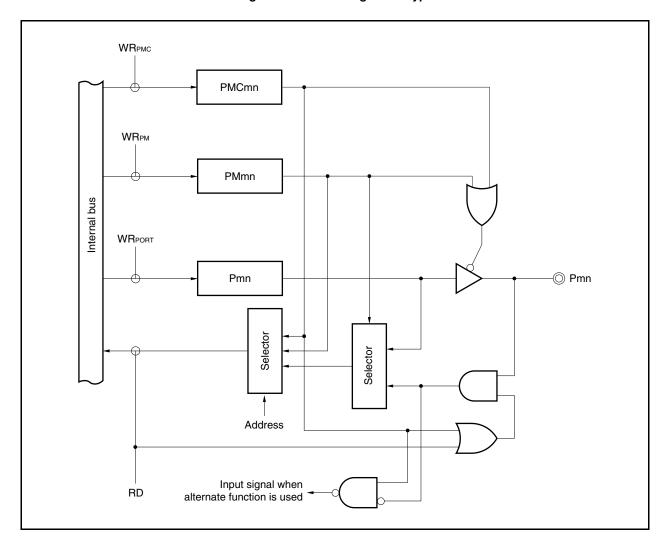

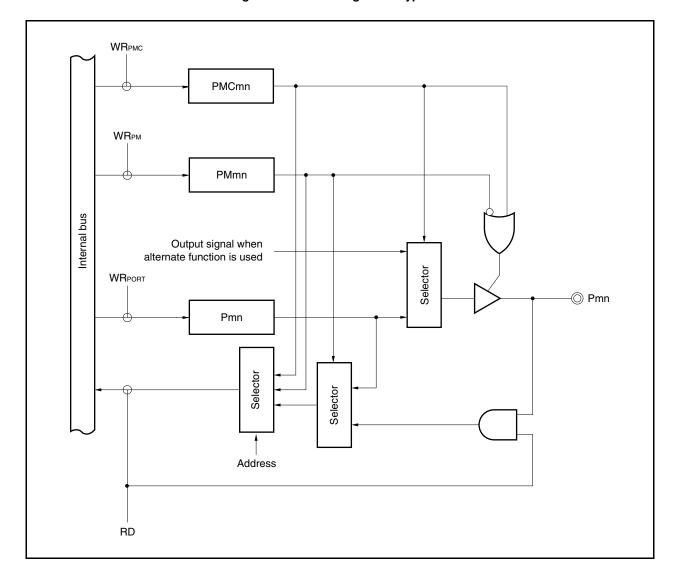

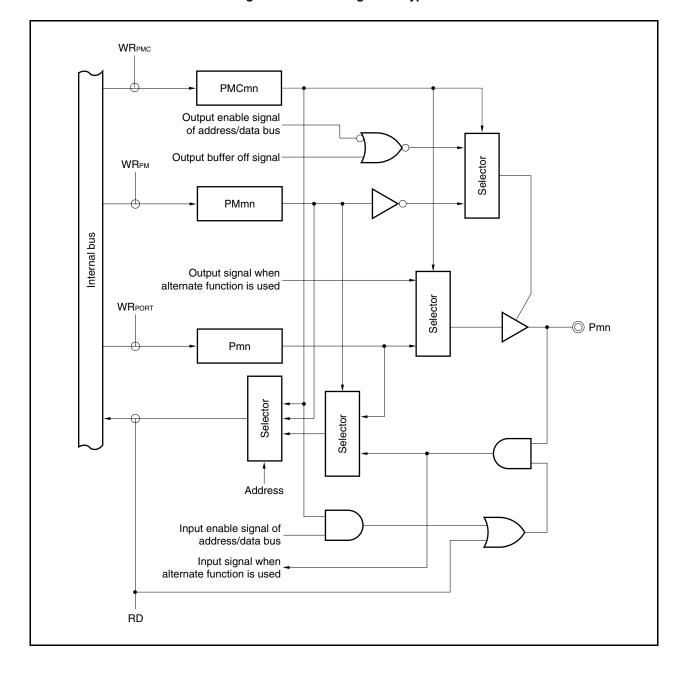

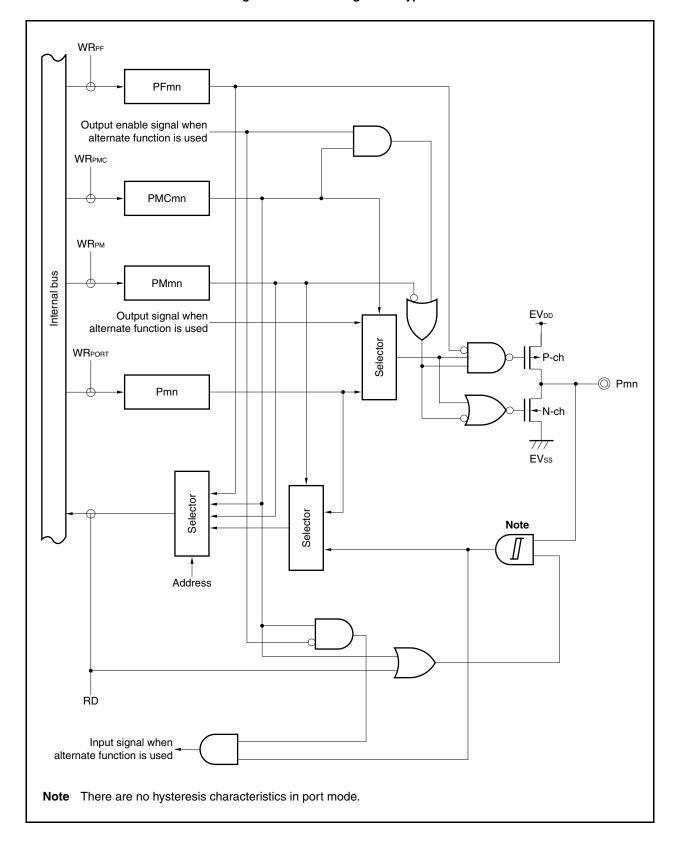

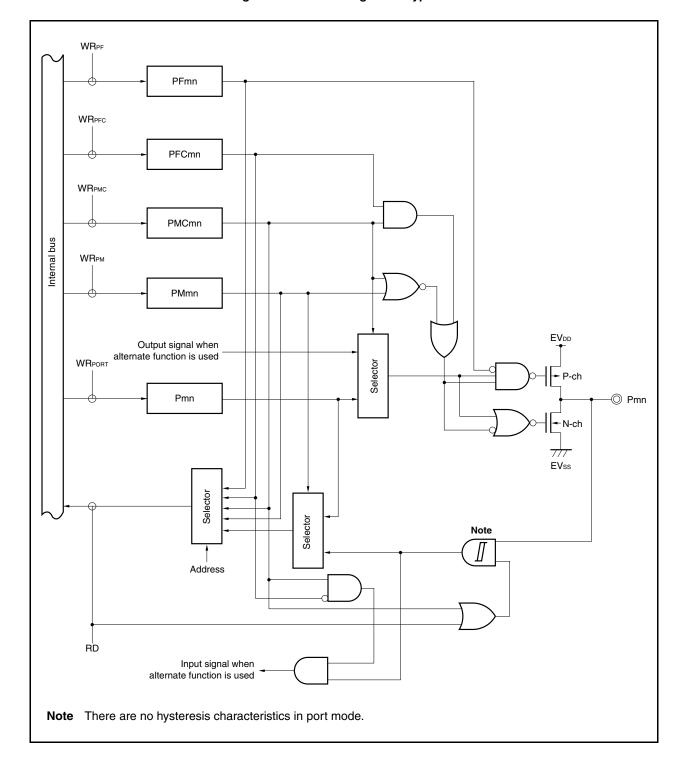

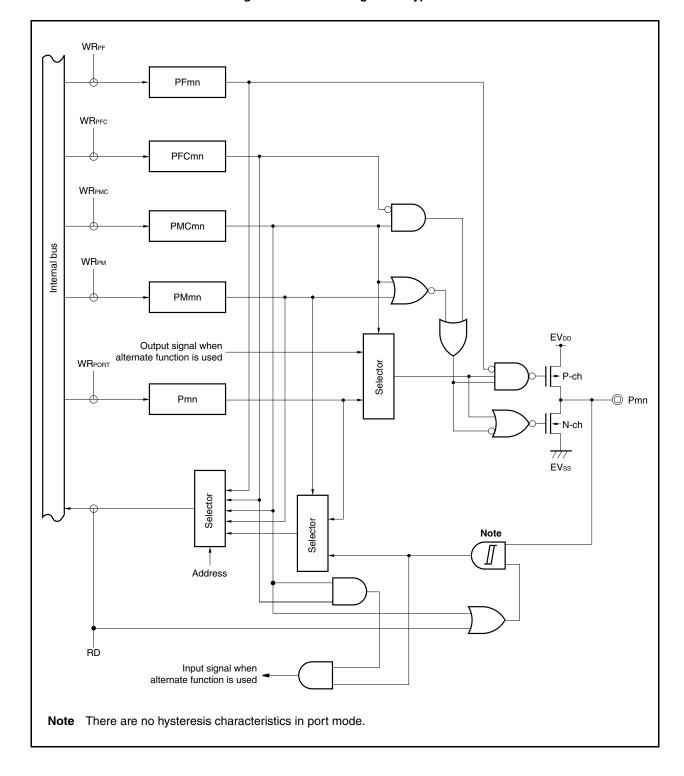

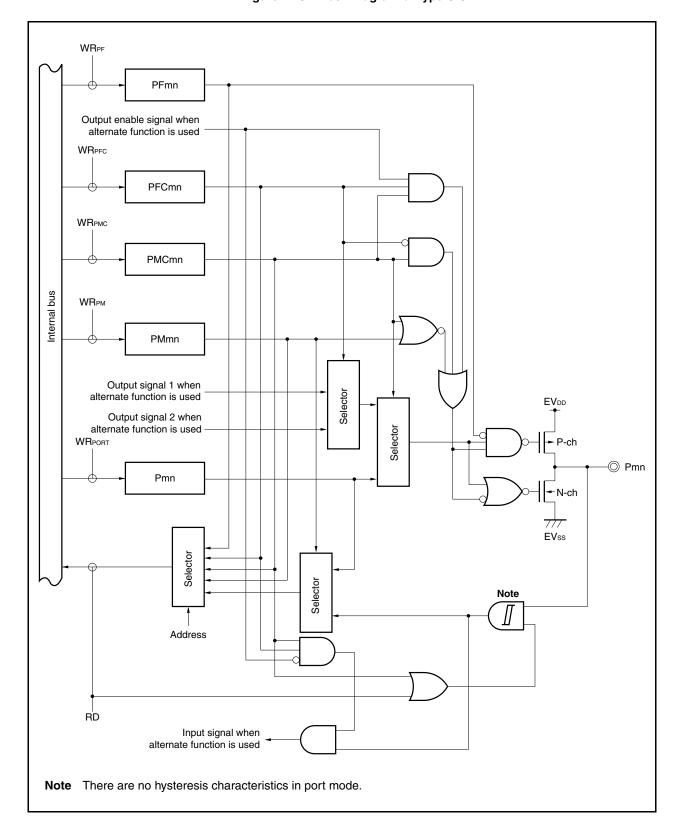

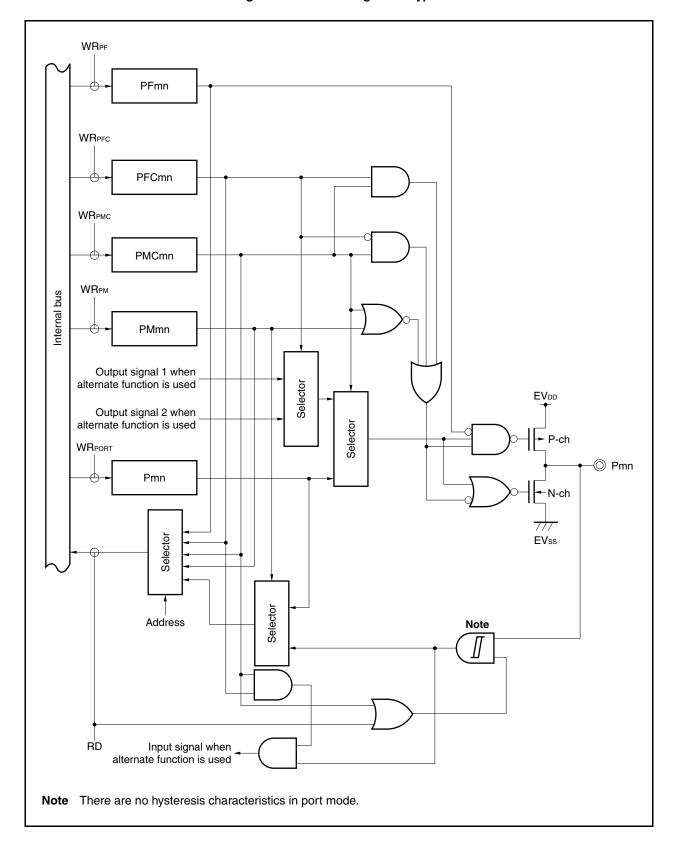

| 4.2    | Basic Port Configuration                                                        | 89  |

| 4.3    | Port Configuration                                                              | 90  |

|        | 4.3.1 Port 0                                                                    | 96  |

|        | 4.3.2 Port 1                                                                    | 100 |

|        | 4.3.3 Port 3                                                                    | 102 |

|        | 4.3.4 Port 4                                                                    | 108 |

|      |      | 4.3.5 Port 5                                                                            | 110 |

|------|------|-----------------------------------------------------------------------------------------|-----|

|      |      | 4.3.6 Port 7                                                                            | 115 |

|      |      | 4.3.7 Port 9                                                                            | 117 |

|      |      | 4.3.8 Port CM                                                                           | 125 |

|      |      | 4.3.9 Port CT                                                                           | 127 |

|      |      | 4.3.10 Port DH                                                                          | 129 |

|      |      | 4.3.11 Port DL                                                                          | 131 |

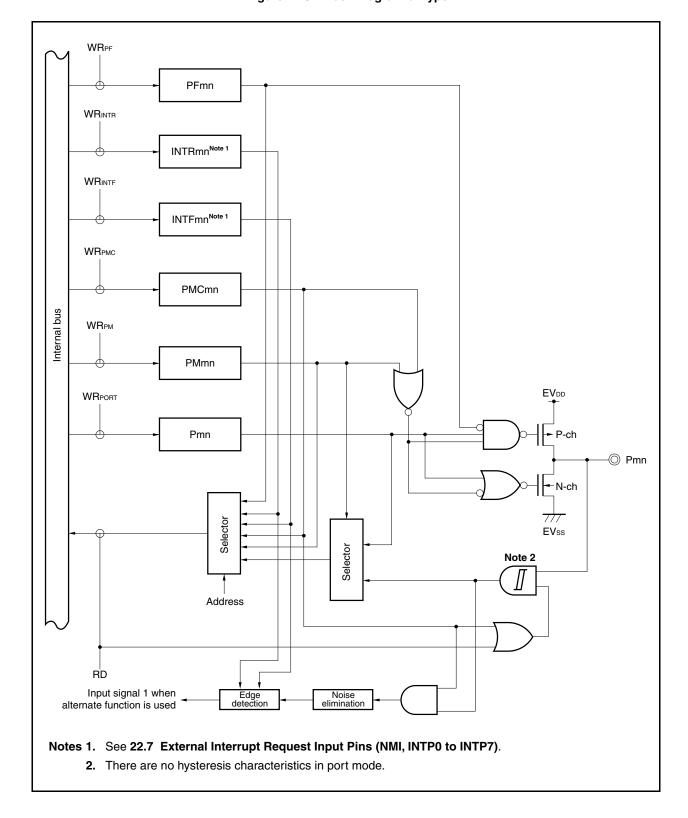

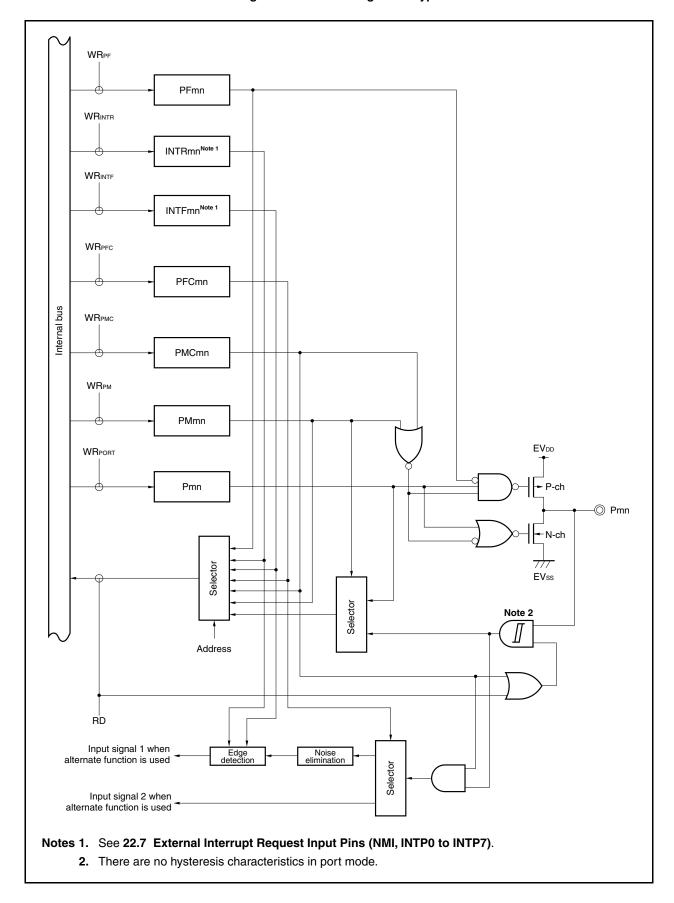

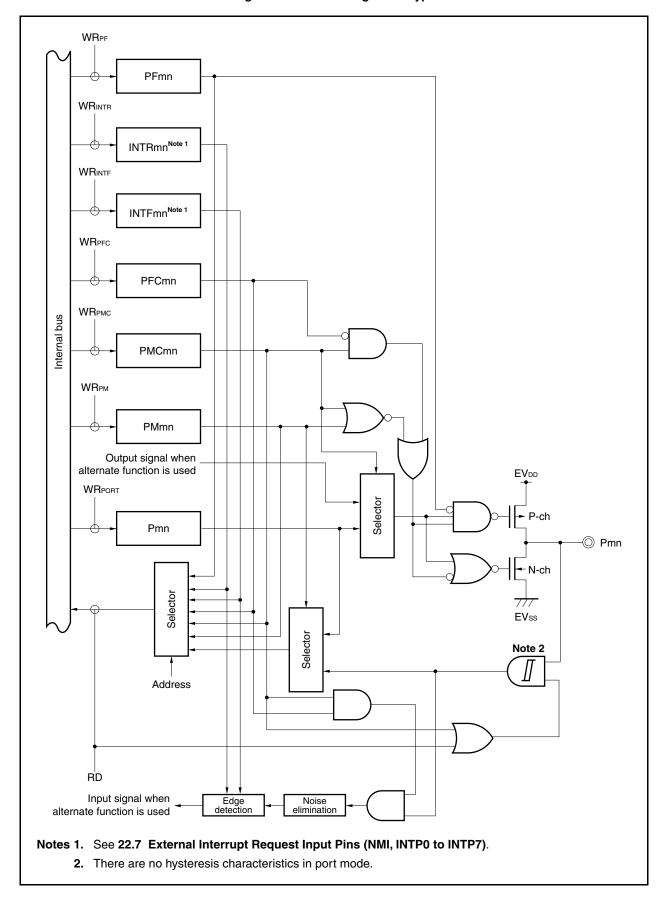

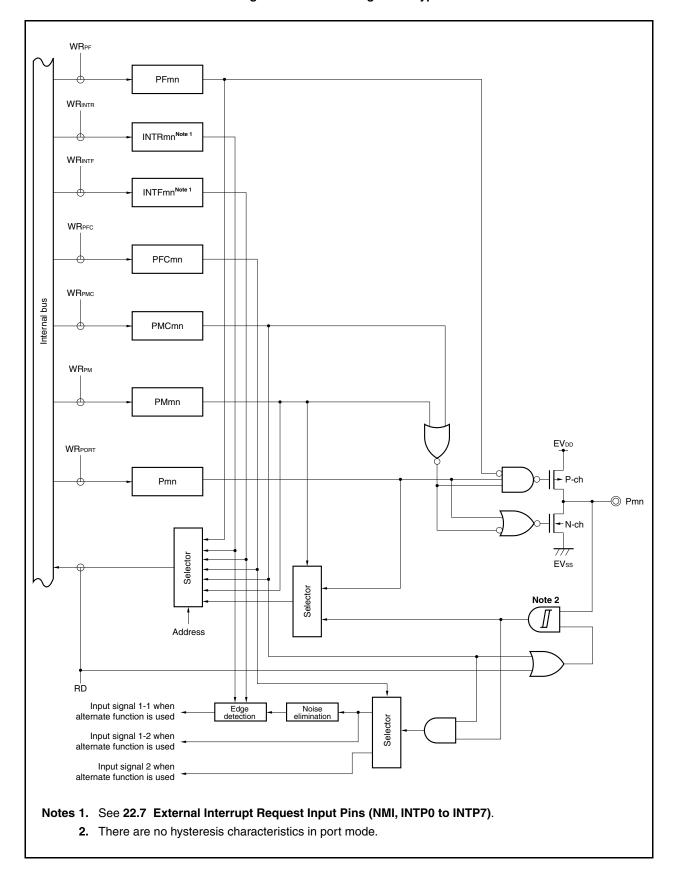

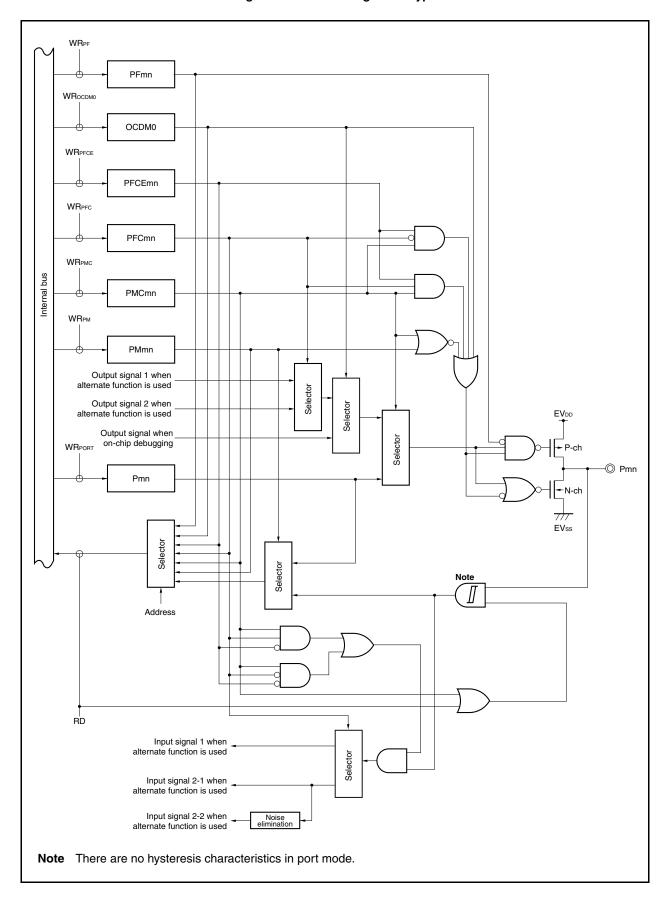

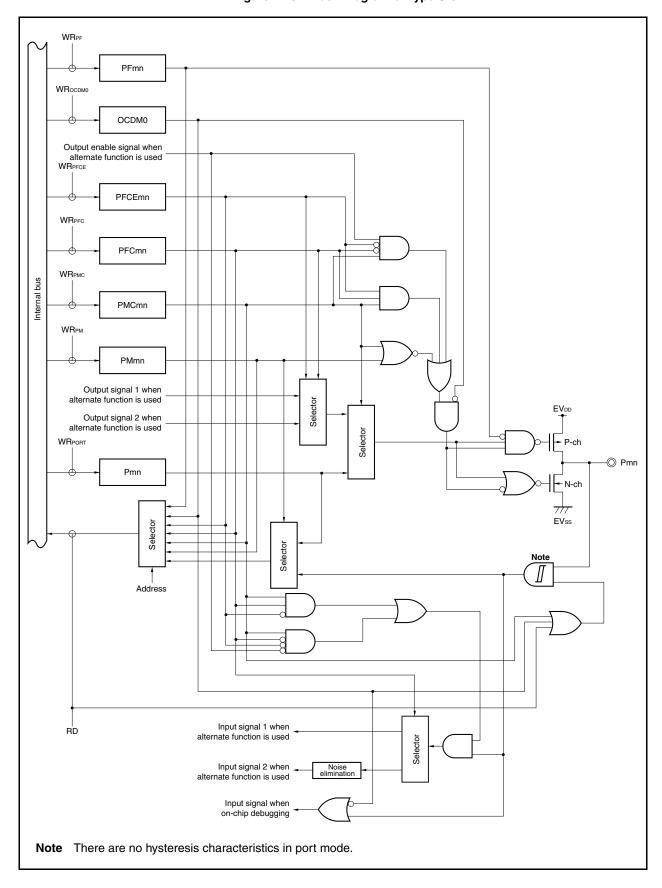

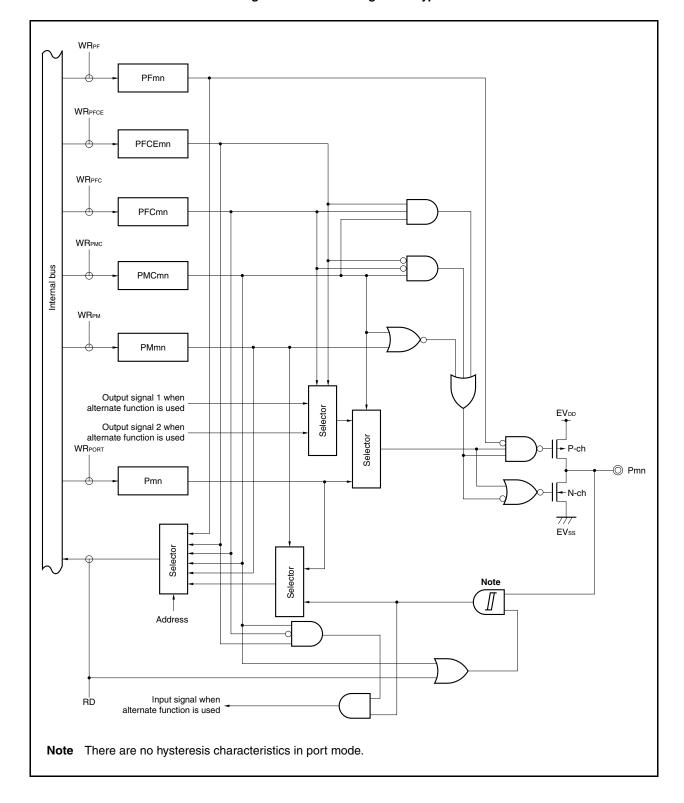

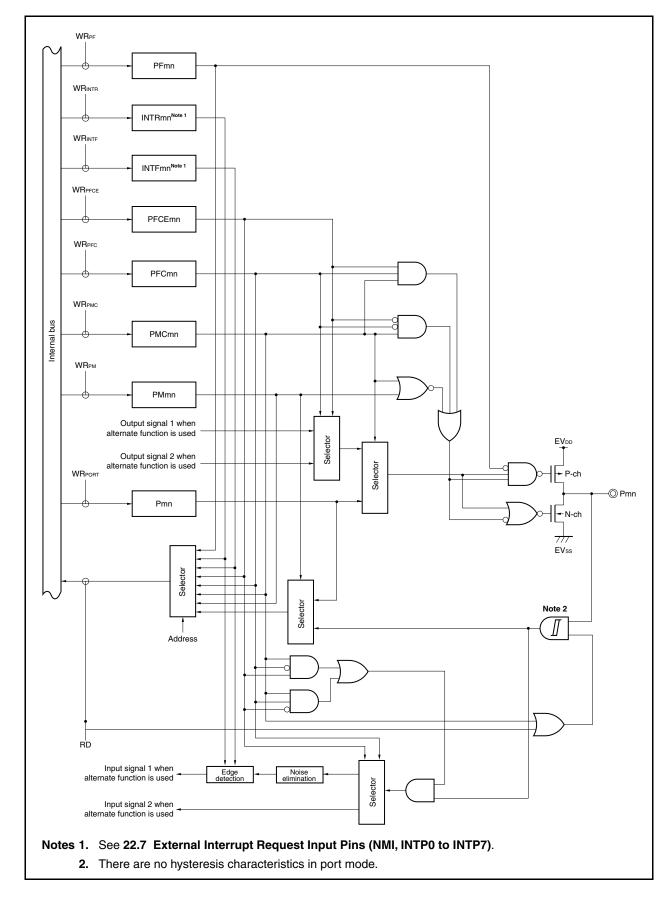

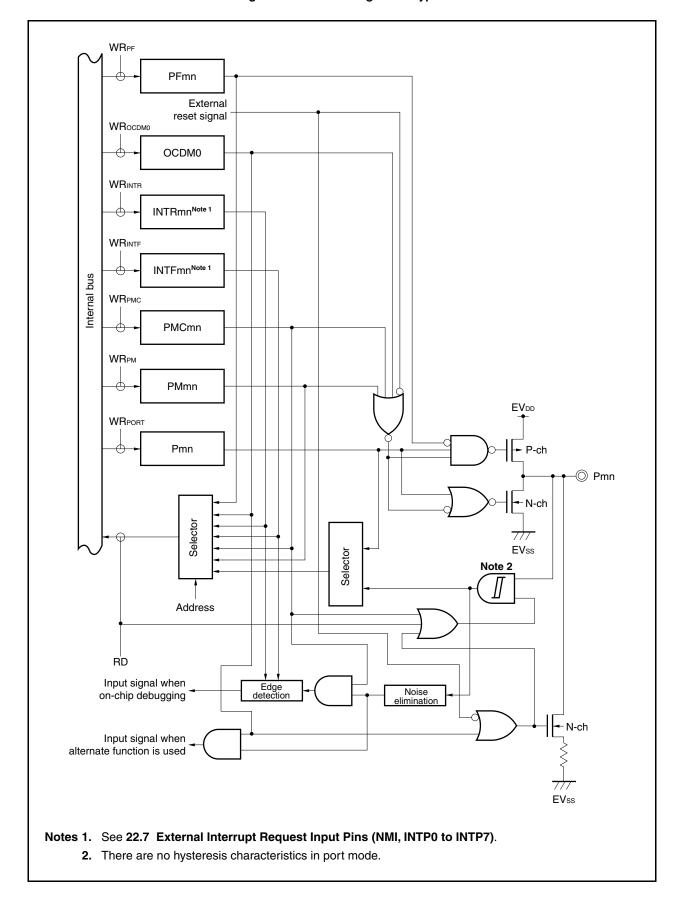

| 4    | 4.4  | Block Diagrams                                                                          | 134 |

| 4    | 4.5  | Port Register Settings When Alternate Function Is Used                                  | 166 |

| 4    | 4.6  | Cautions                                                                                | 174 |

|      |      | 4.6.1 Cautions on setting port pins                                                     | 174 |

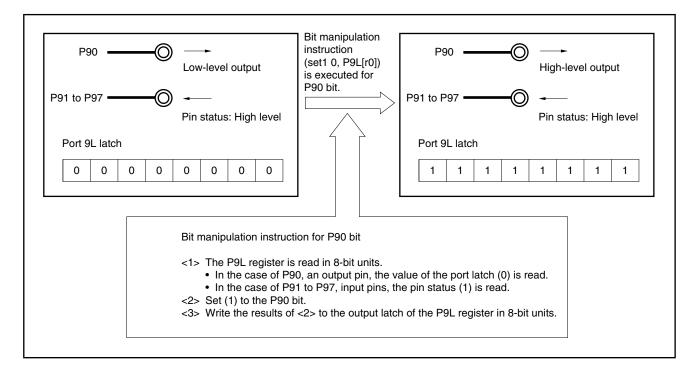

|      |      | 4.6.2 Cautions on bit manipulation instruction for port n register (Pn)                 | 177 |

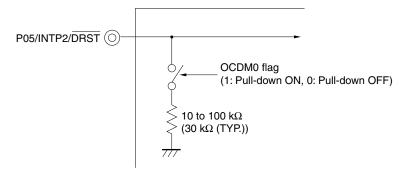

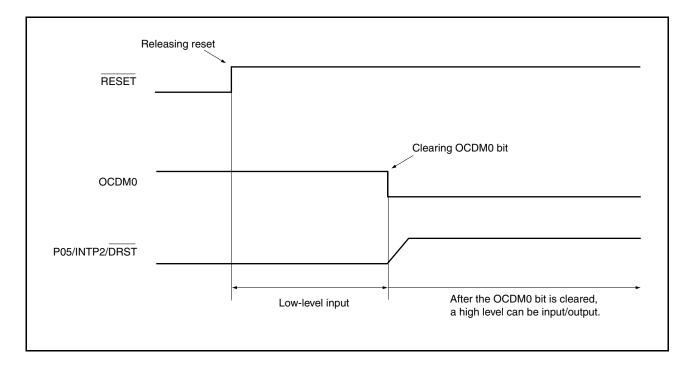

|      |      | 4.6.3 Cautions on on-chip debug pins                                                    | 178 |

|      |      | 4.6.4 Cautions on P05/INTP2/DRST pin                                                    | 178 |

|      |      | 4.6.5 Cautions on P10, P11, and P53 pins when power is turned on                        | 178 |

|      |      | 4.6.6 Hysteresis characteristics                                                        | 178 |

| CHAF | PTER | R 5 BUS CONTROL FUNCTION                                                                | 179 |

| į    | 5.1  | Features                                                                                | 179 |

| į    | 5.2  | Bus Control Pins                                                                        | 180 |

|      |      | 5.2.1 Pin status when internal ROM, internal RAM, or on-chip peripheral I/O is accessed | 180 |

|      |      | 5.2.2 Pin status in each operation mode                                                 | 180 |

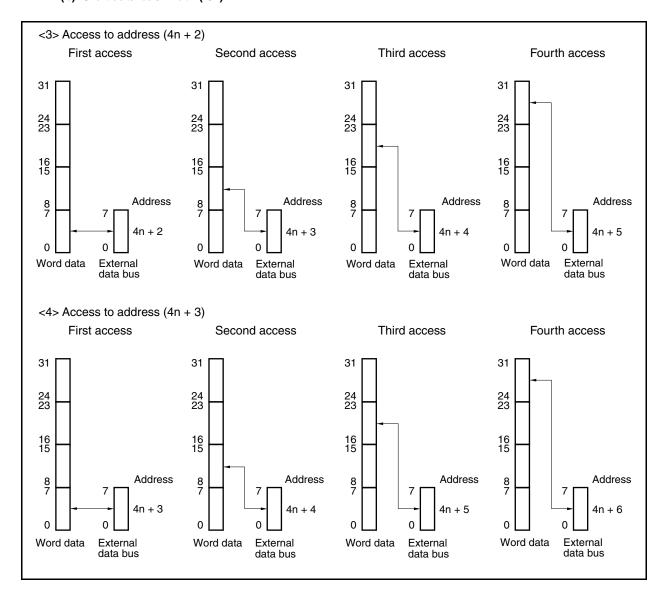

| ţ    | 5.3  | Memory Block Function                                                                   | 181 |

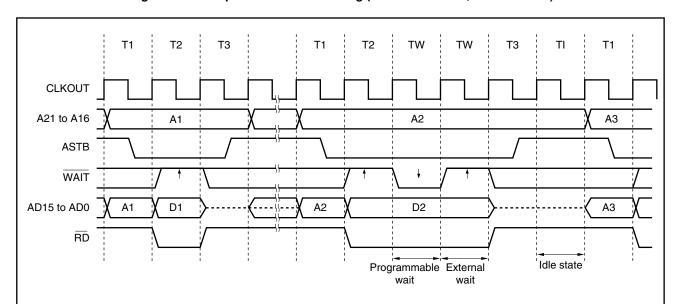

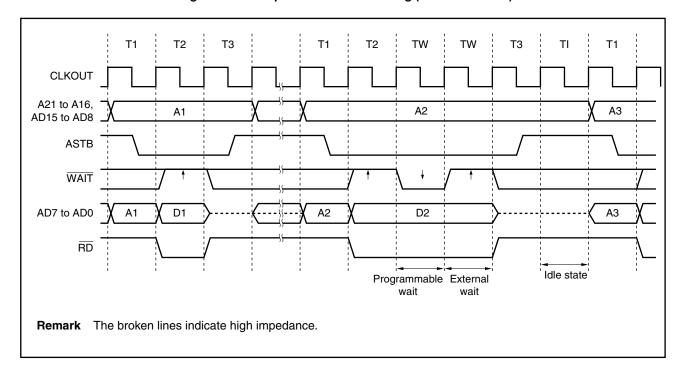

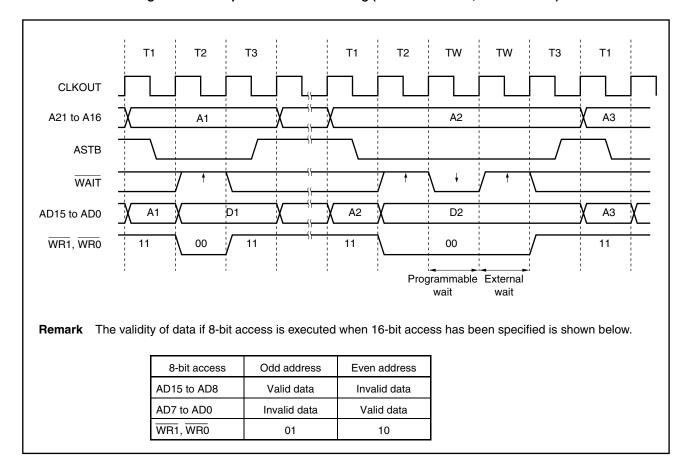

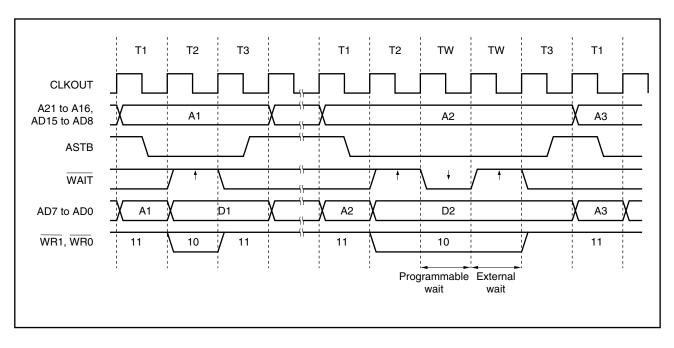

| į    | 5.4  | Bus Access                                                                              | 182 |

|      |      | 5.4.1 Number of clock cycles required for access                                        | 182 |

|      |      | 5.4.2 Bus size setting function                                                         | 183 |

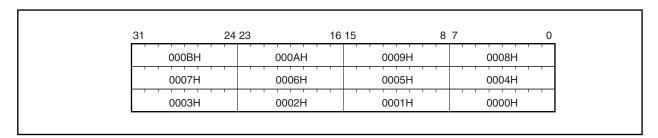

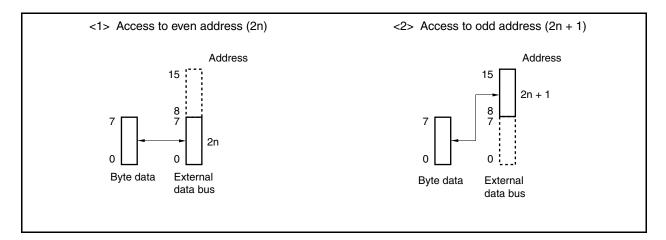

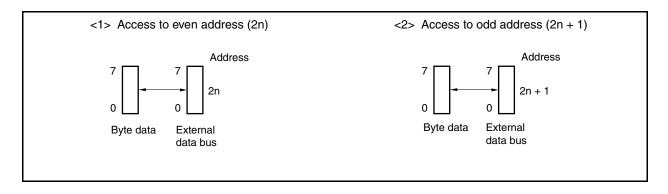

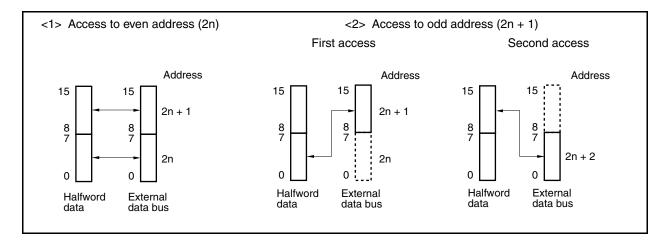

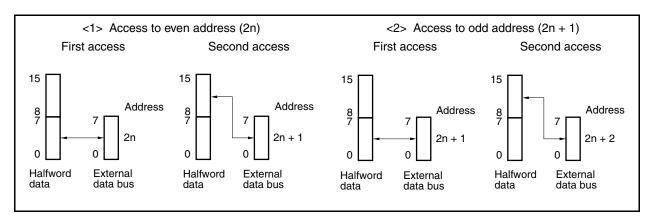

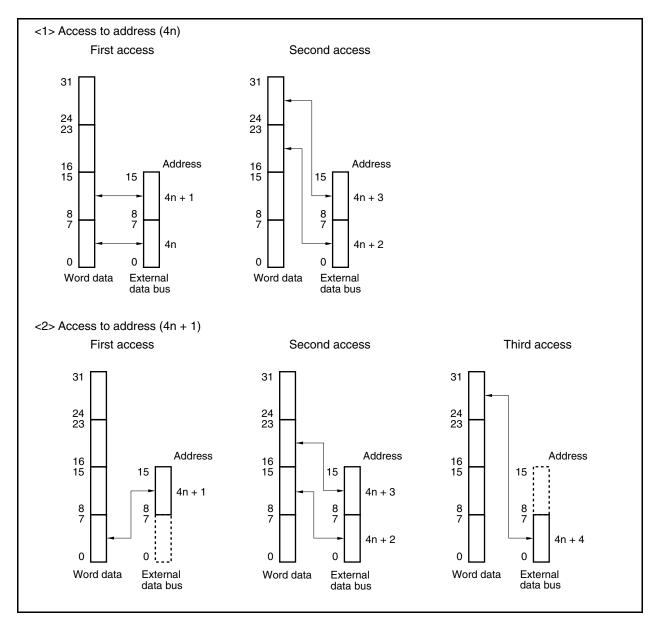

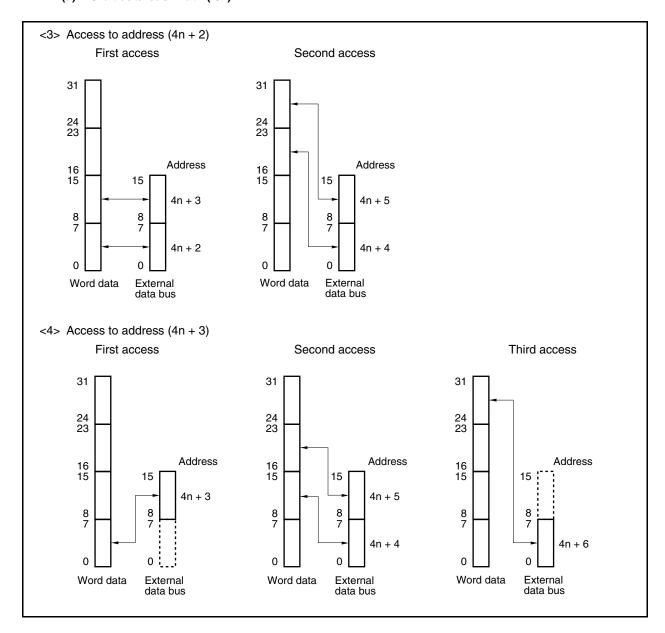

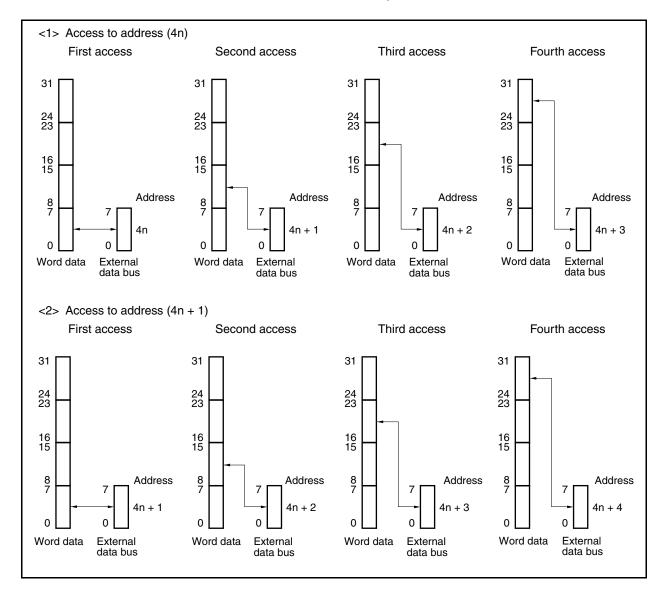

|      |      | 5.4.3 Access according to bus size                                                      | 184 |

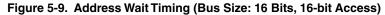

| ;    | 5.5  | Wait Function                                                                           | 191 |

|      |      | 5.5.1 Programmable wait function                                                        | 191 |

|      |      | 5.5.2 External wait function                                                            | 192 |

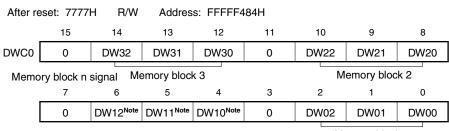

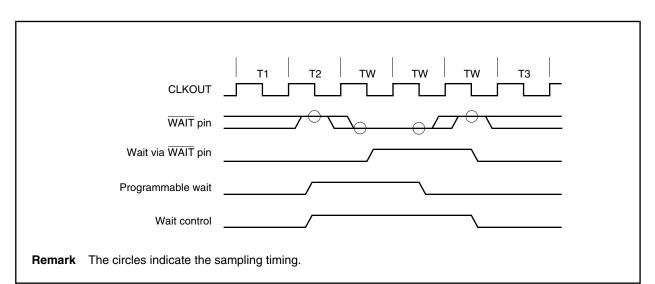

|      |      | 5.5.3 Relationship between programmable wait and external wait                          | 193 |

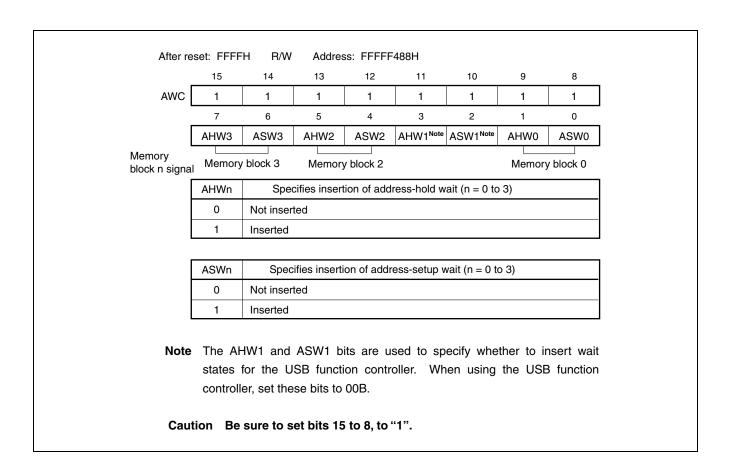

|      |      | 5.5.4 Programmable address wait function                                                | 194 |

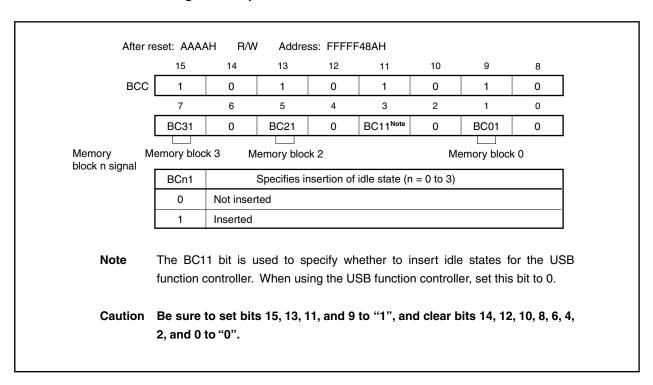

| ;    | 5.6  | Idle State Insertion Function                                                           | 195 |

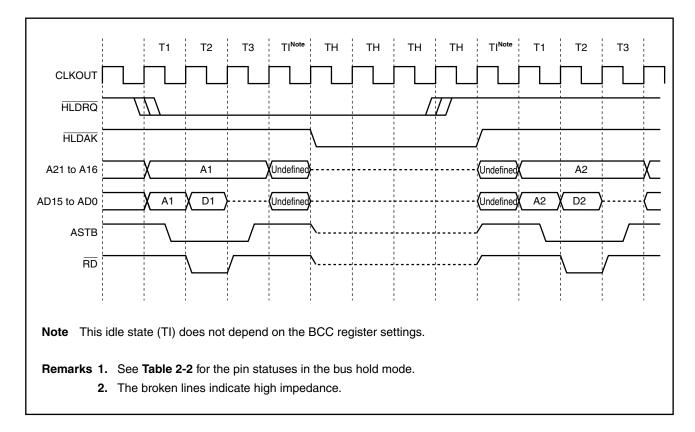

| ;    | 5.7  | Bus Hold Function                                                                       | 196 |

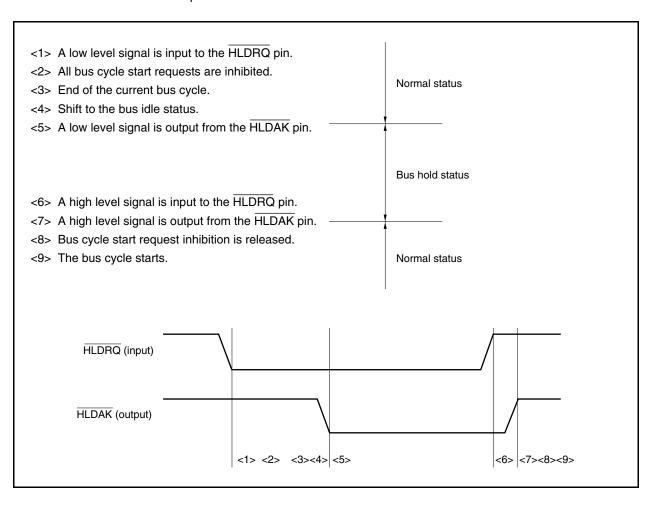

|      |      | 5.7.1 Functional outline                                                                | 196 |

|      |      | 5.7.2 Bus hold procedure                                                                | 197 |

|      |      | 5.7.3 Operation in power save mode                                                      | 197 |

| ţ    | 5.8  | Bus Priority                                                                            | 198 |

| ţ    | 5.9  | Bus Timing                                                                              | 199 |

| CHAF | PTER | R 6 CLOCK GENERATOR                                                                     | 203 |

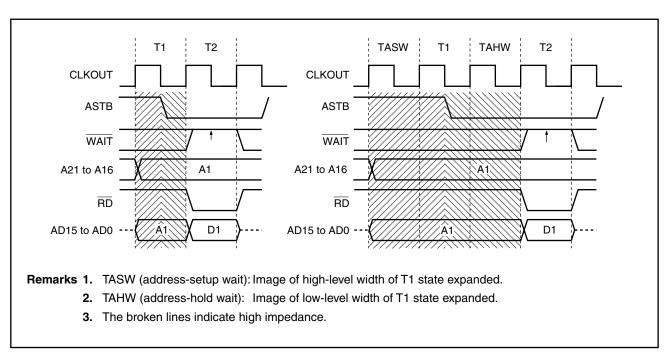

| (    | 6.1  | Overview                                                                                | 203 |

| (    | 6.2  | Configuration                                                                           | 204 |

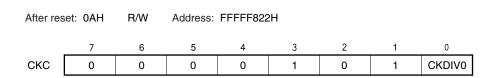

| (    | 6.3  | Registers                                                                               | 207 |

| 6.4    | Operations                                                             | 213 |

|--------|------------------------------------------------------------------------|-----|

|        | 6.4.1 Operation of each clock                                          | 213 |

|        | 6.4.2 Clock output function                                            | 214 |

|        | 6.4.3 External clock signal input                                      | 214 |

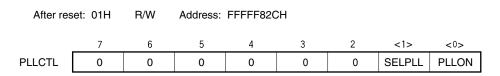

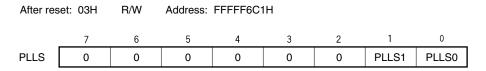

| 6.5    | PLL Function                                                           | 214 |

|        | 6.5.1 Overview                                                         | 214 |

|        | 6.5.2 Registers                                                        | 215 |

|        | 6.5.3 Usage                                                            | 219 |

| 6.6    | How to Connect a Resonator                                             | 220 |

|        | 6.6.1 Main clock oscillator                                            | 220 |

|        | 6.6.2 Subclock oscillator                                              | 220 |

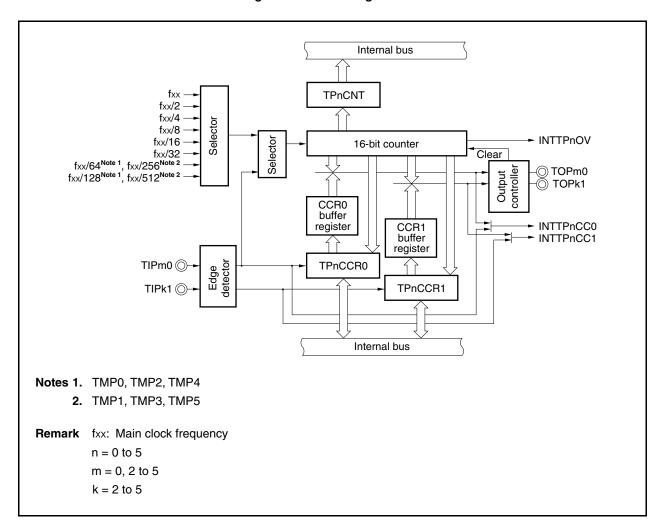

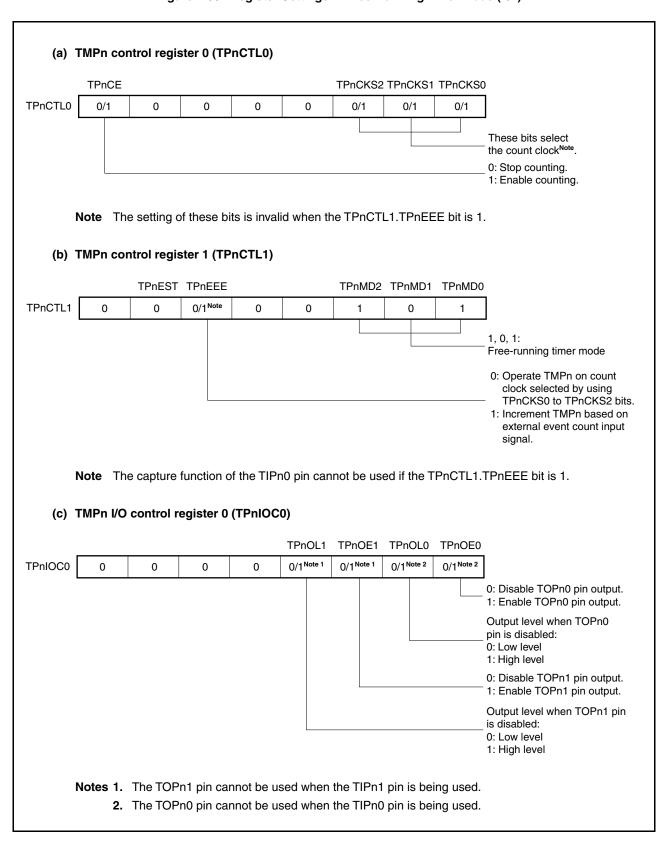

| CHAPTE | ER 7 16-BIT TIMER/EVENT COUNTER P (TMP)                                | 223 |

| 7.1    | Overview                                                               | 223 |

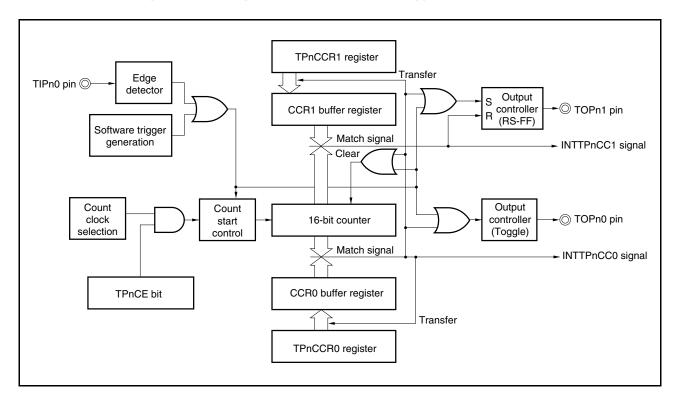

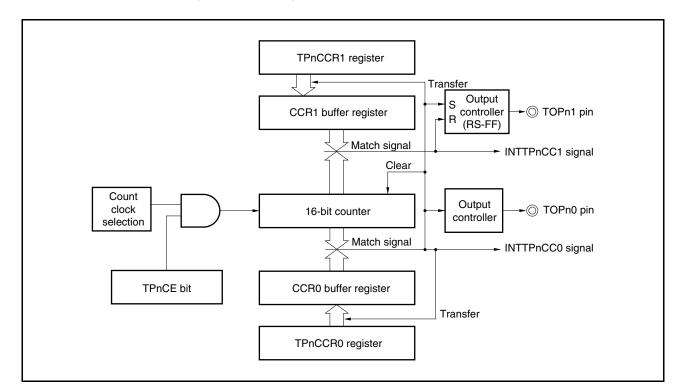

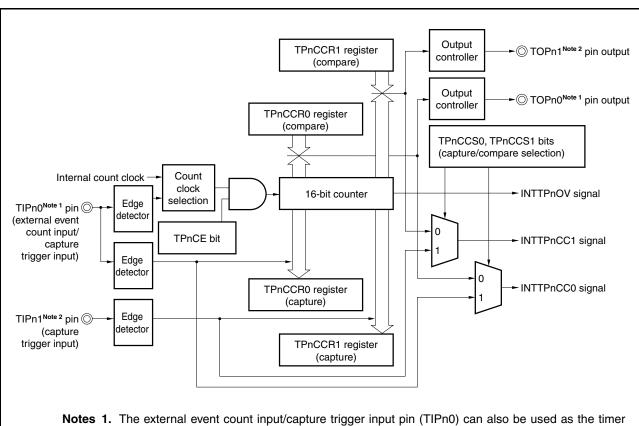

| 7.2    | Configuration                                                          | 224 |

|        | 7.2.1 Pins used by TMPn                                                | 226 |

|        | 7.2.2 Interrupts                                                       | 227 |

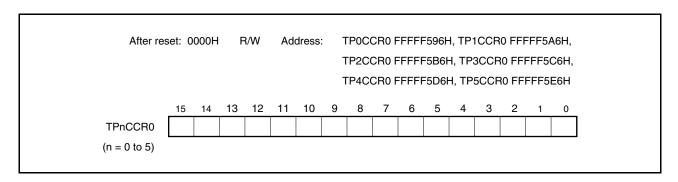

| 7.3    | Registers                                                              | 228 |

| 7.4    | Operations                                                             | 240 |

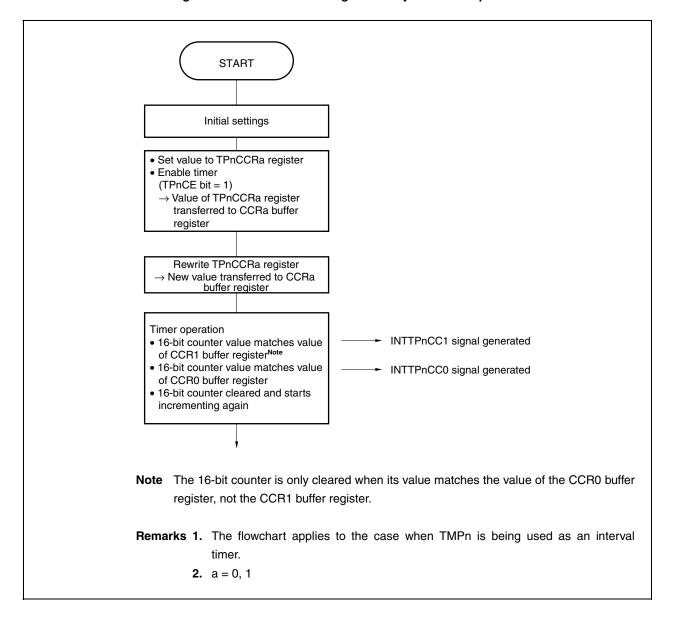

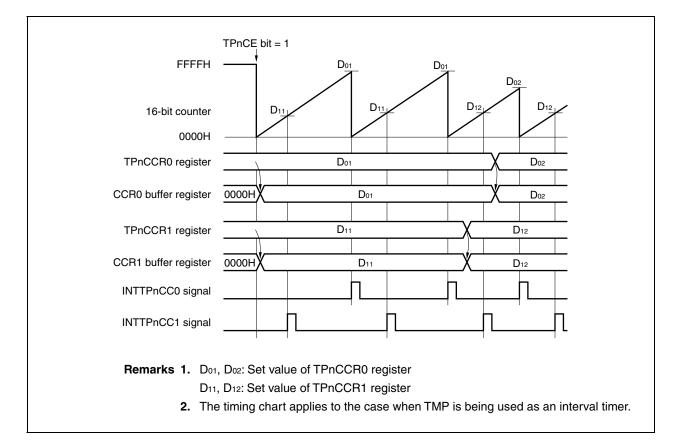

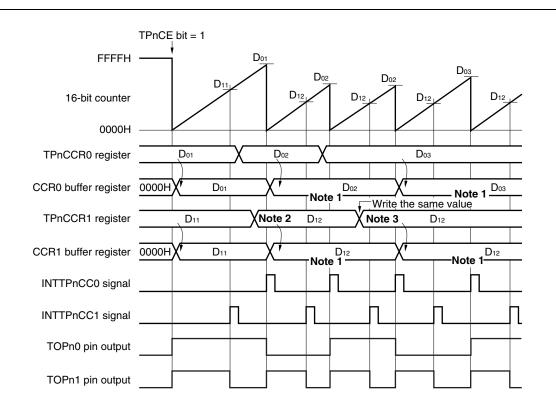

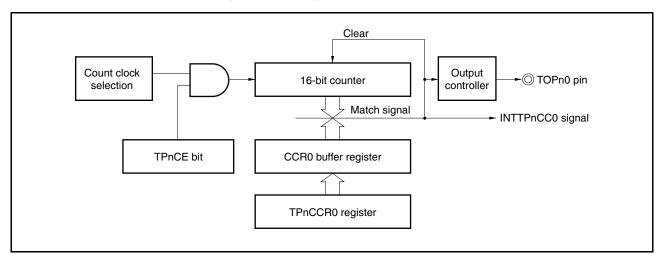

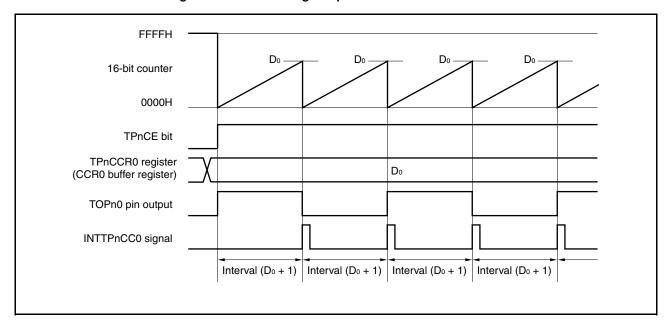

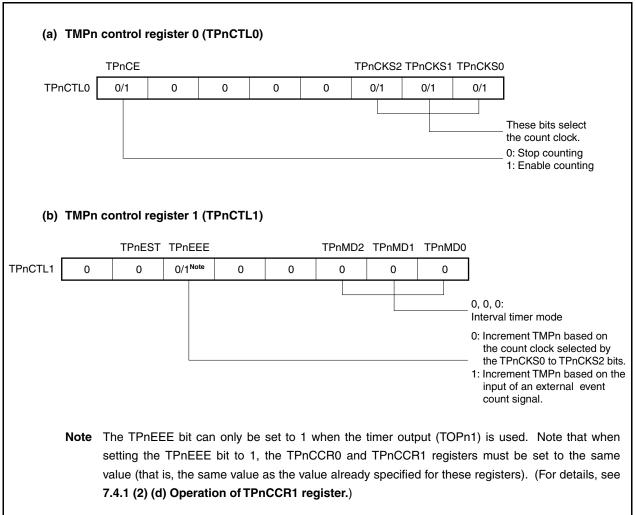

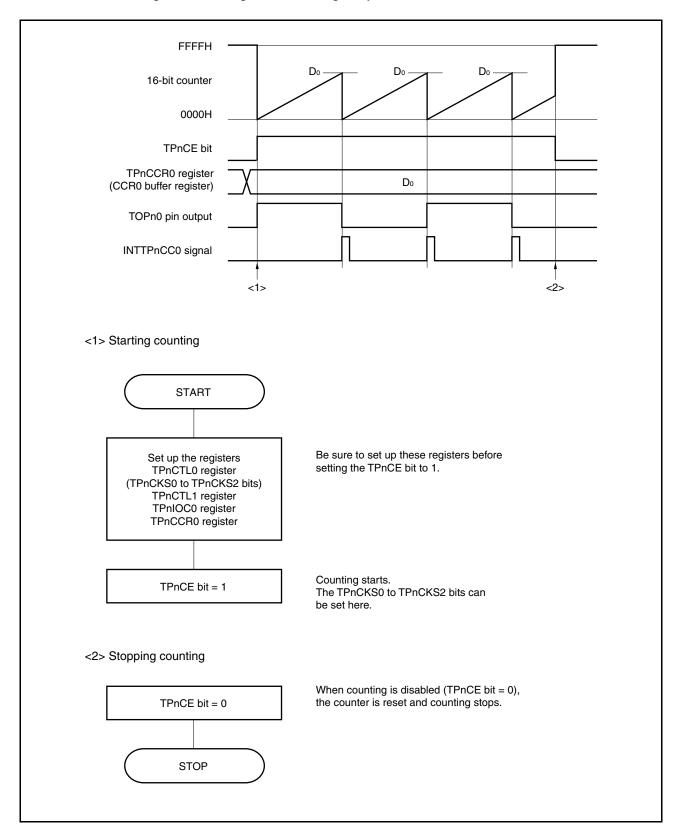

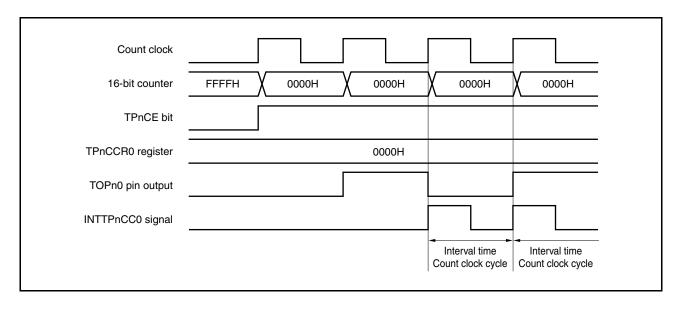

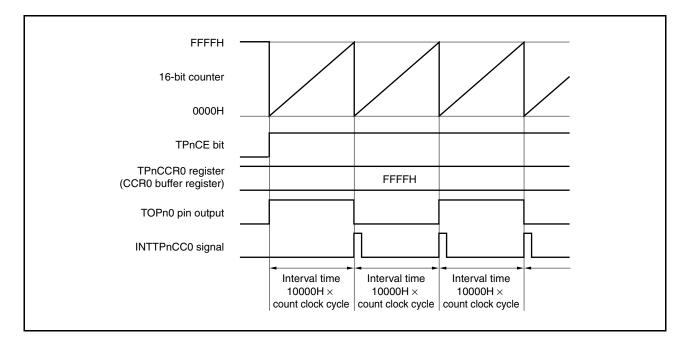

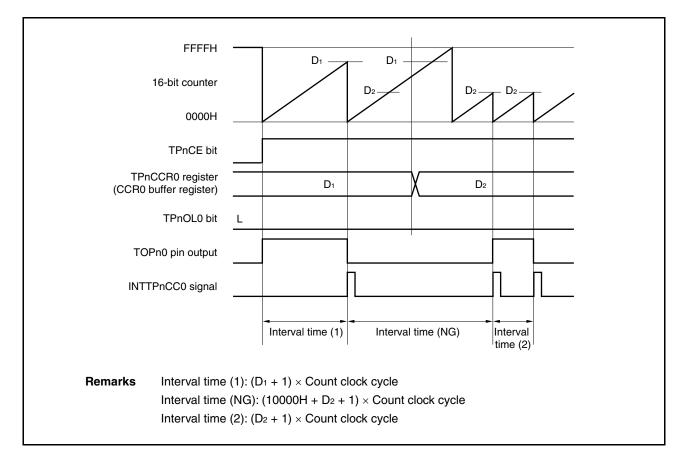

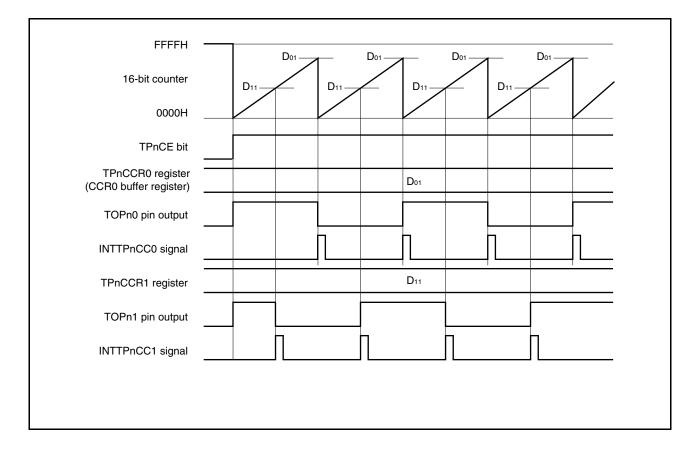

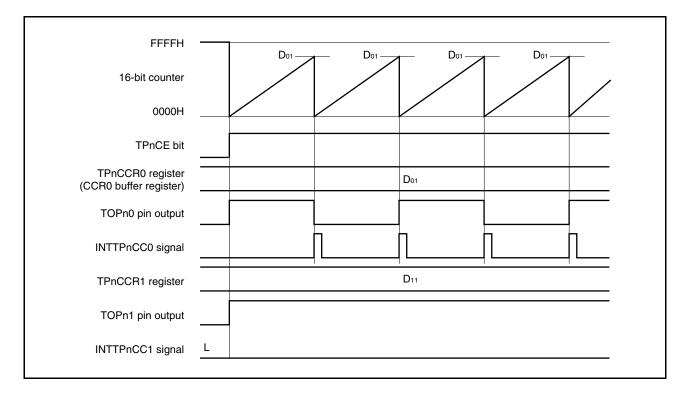

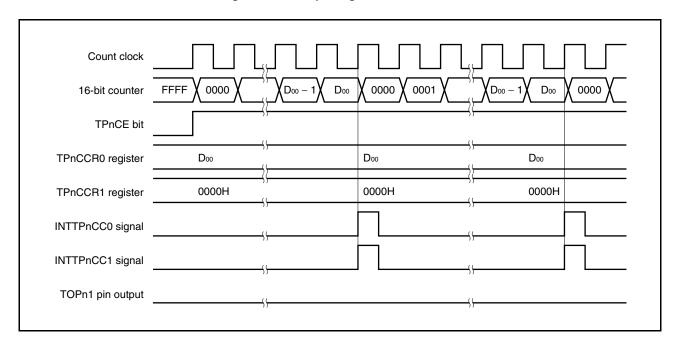

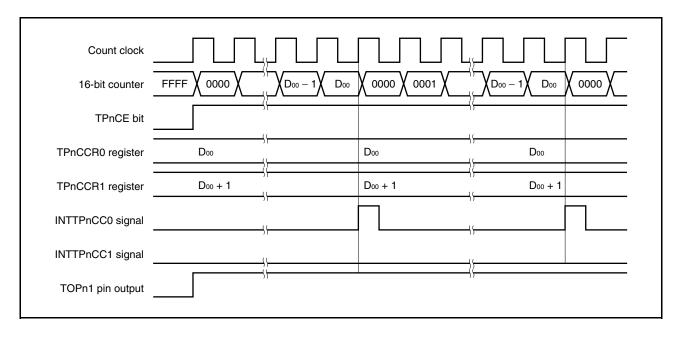

|        | 7.4.1 Interval timer mode (TPnMD2 to TPnMD0 bits = 000)                | 247 |

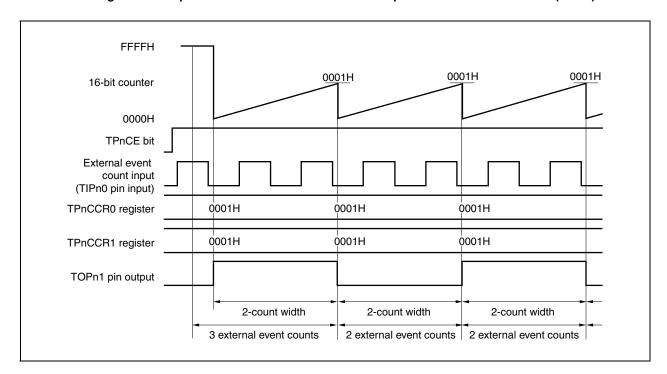

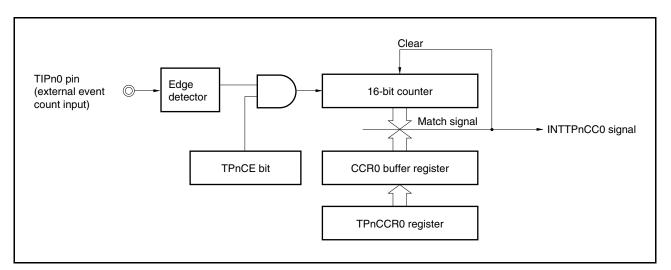

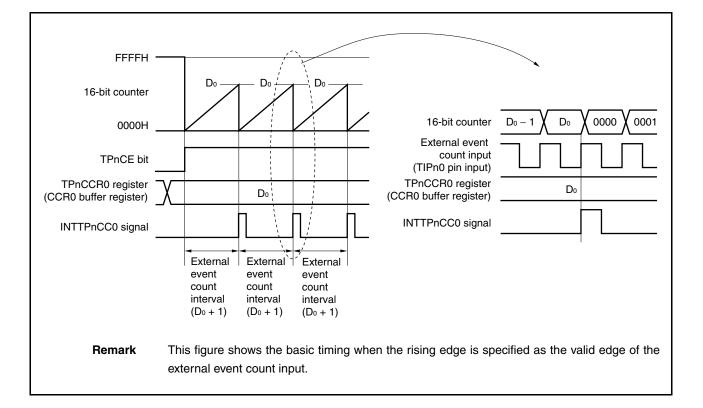

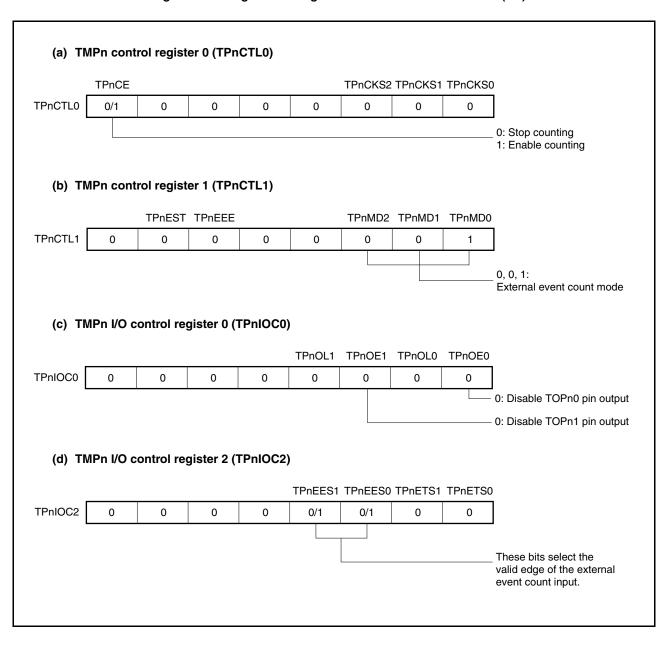

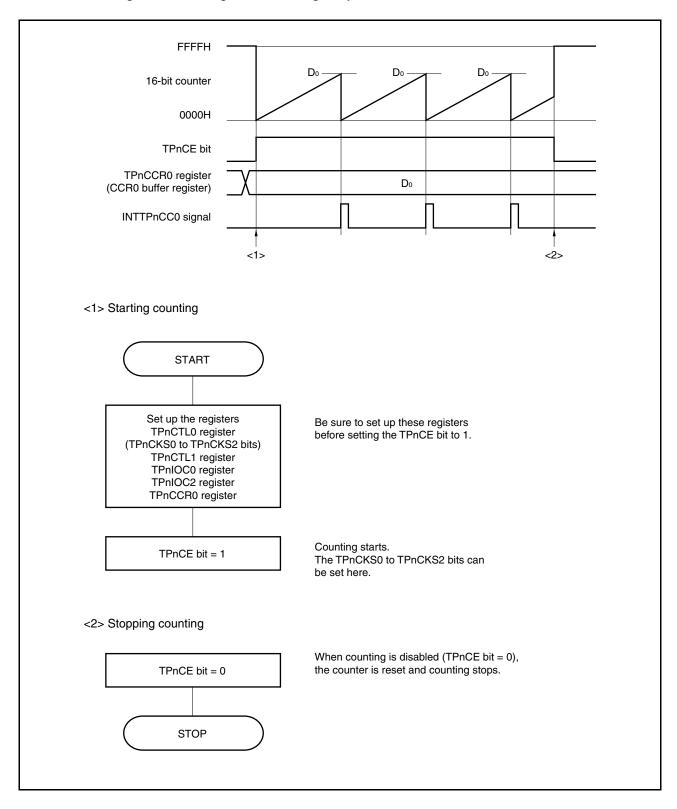

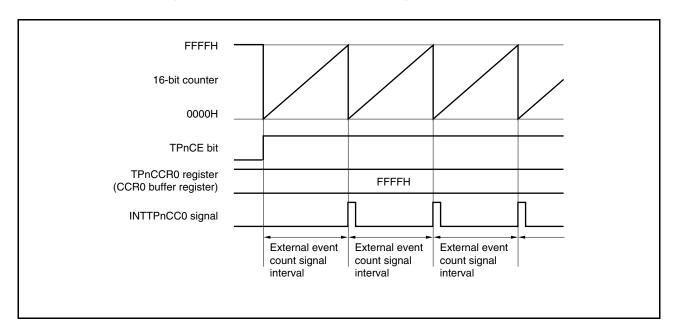

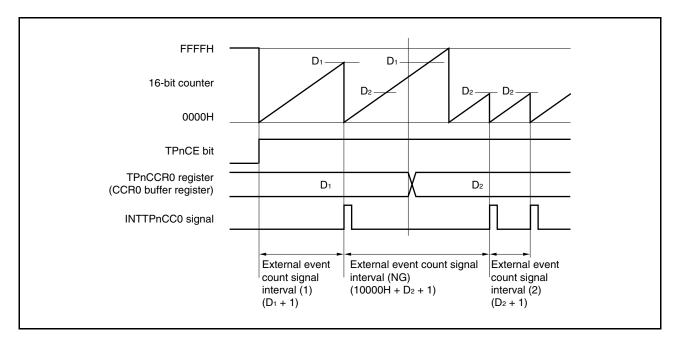

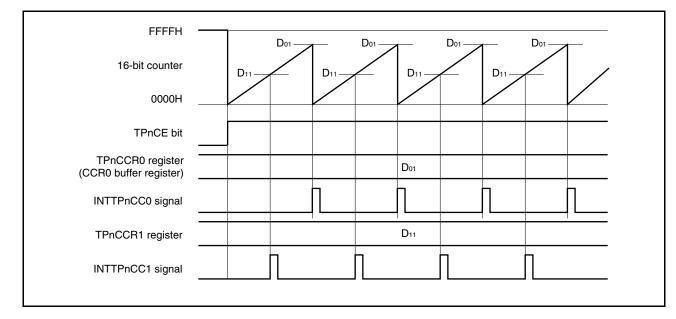

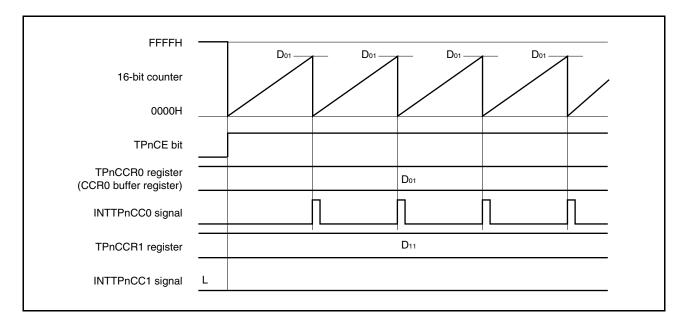

|        | 7.4.2 External event count mode (TPnMD2 to TPnMD0 bits = 001)          | 258 |

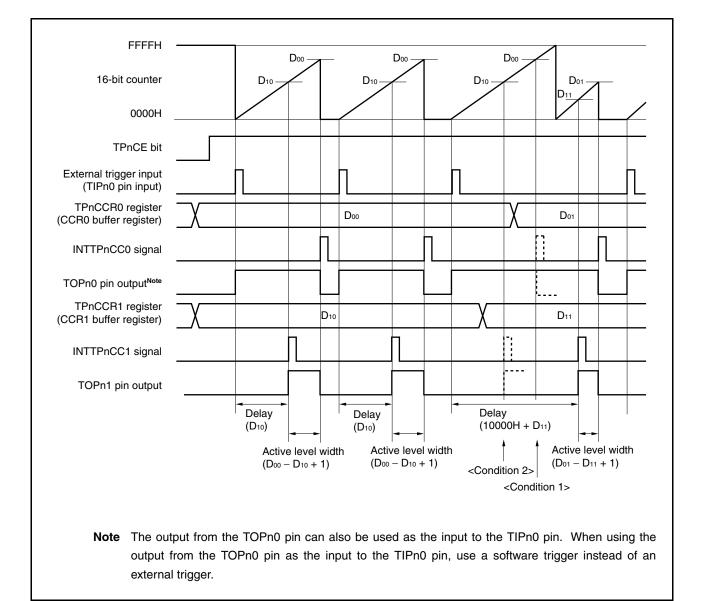

|        | 7.4.3 External trigger pulse output mode (TPnMD2 to TPnMD0 bits = 010) | 267 |

|        | 7.4.4 One-shot pulse output mode (TPnMD2 to TPnMD0 bits = 011)         | 279 |

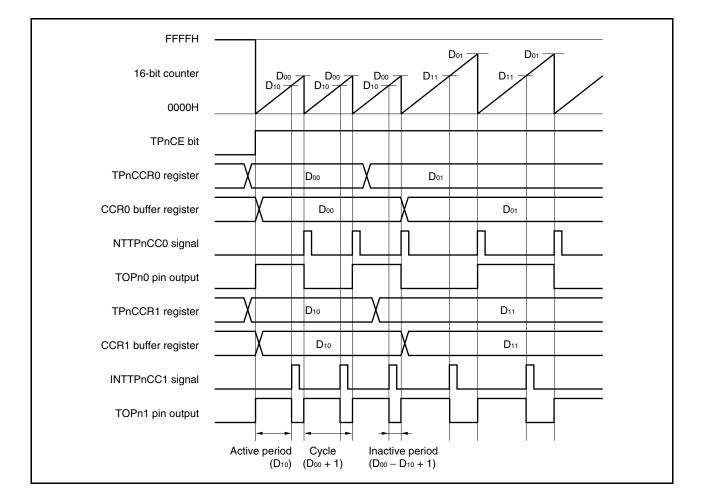

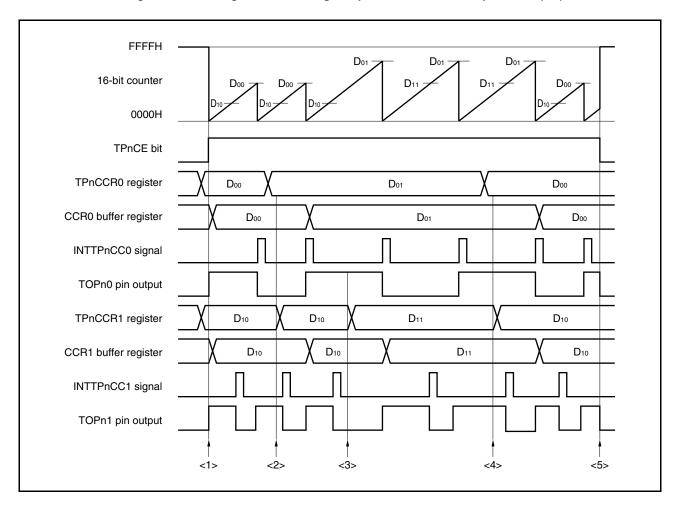

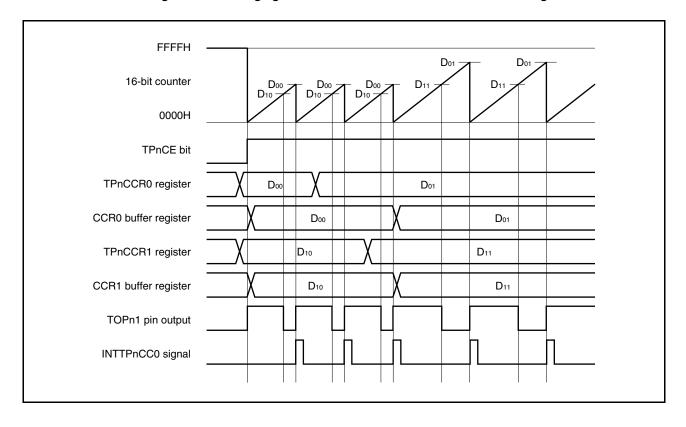

|        | 7.4.5 PWM output mode (TPnMD2 to TPnMD0 bits = 100)                    | 287 |

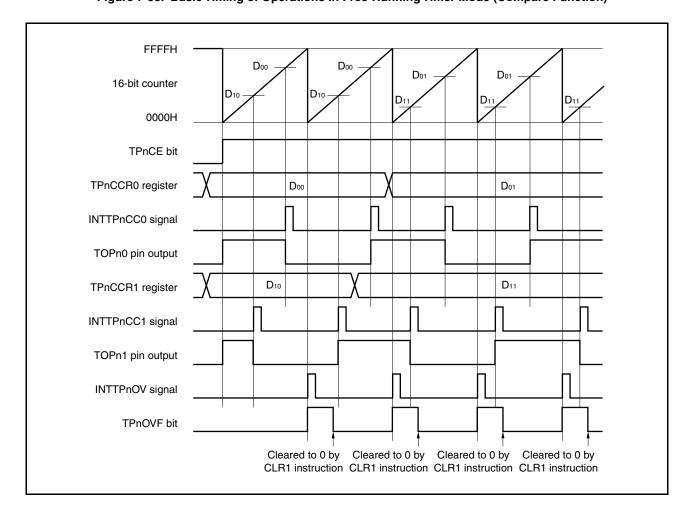

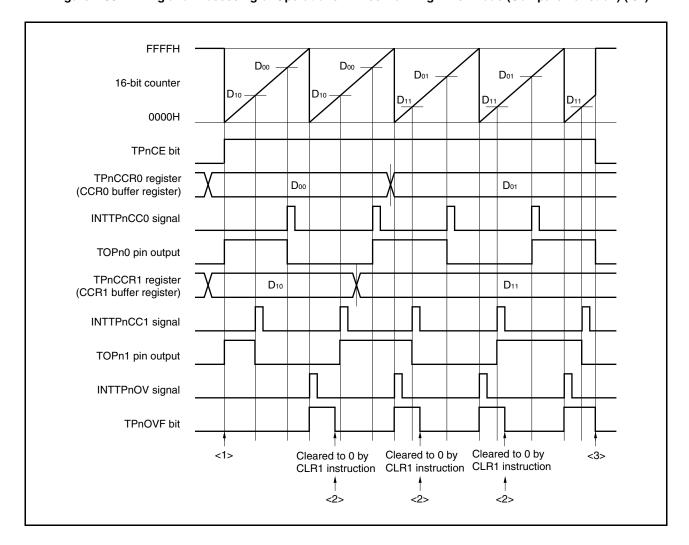

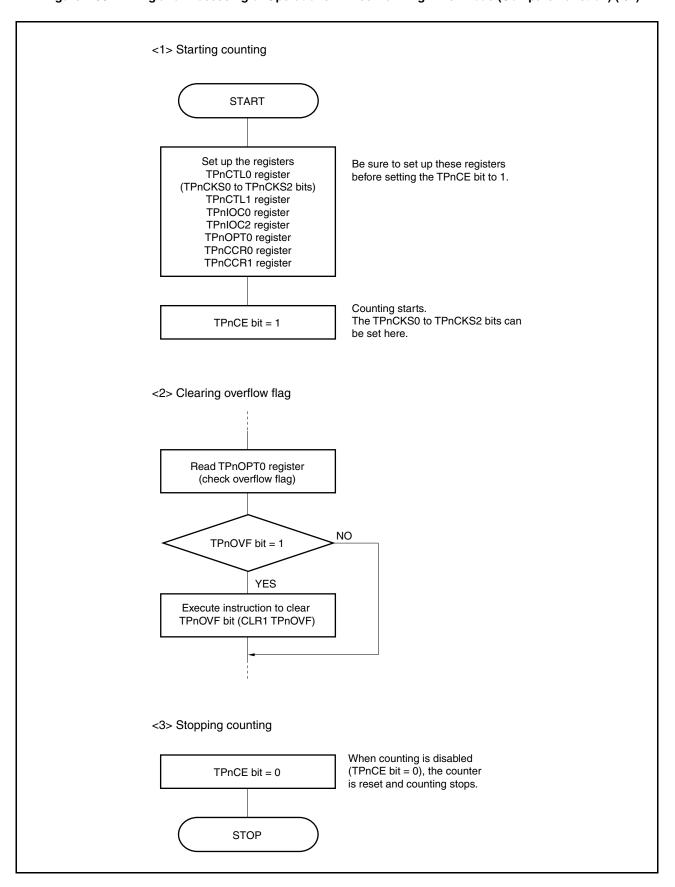

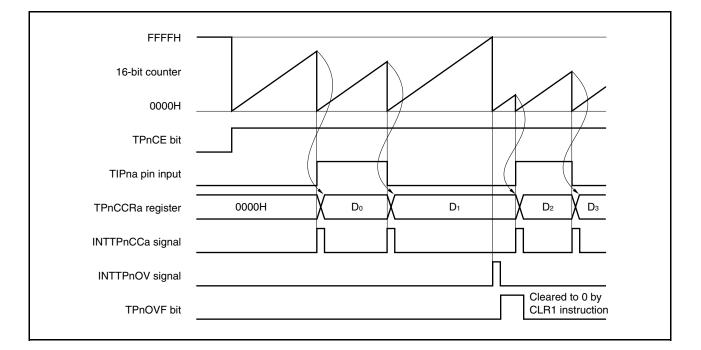

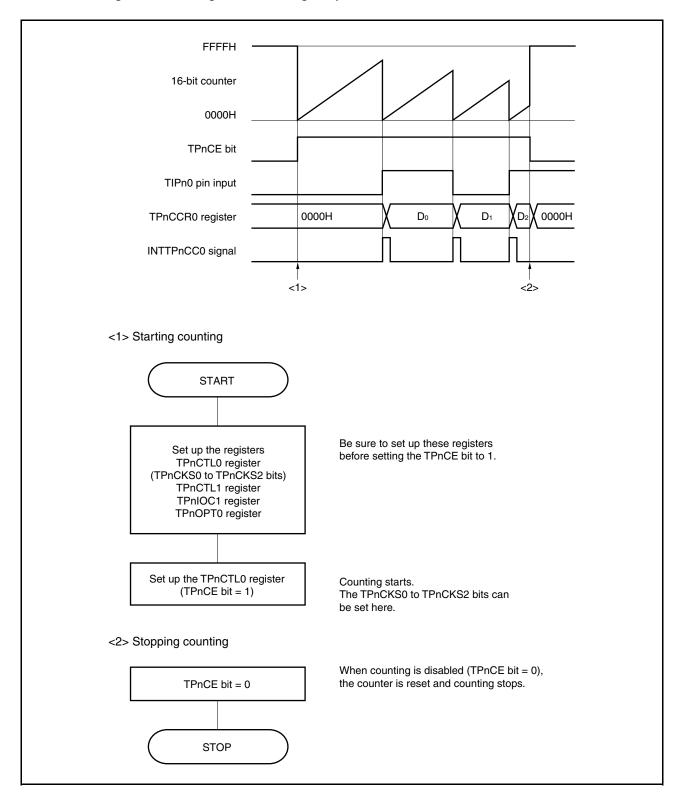

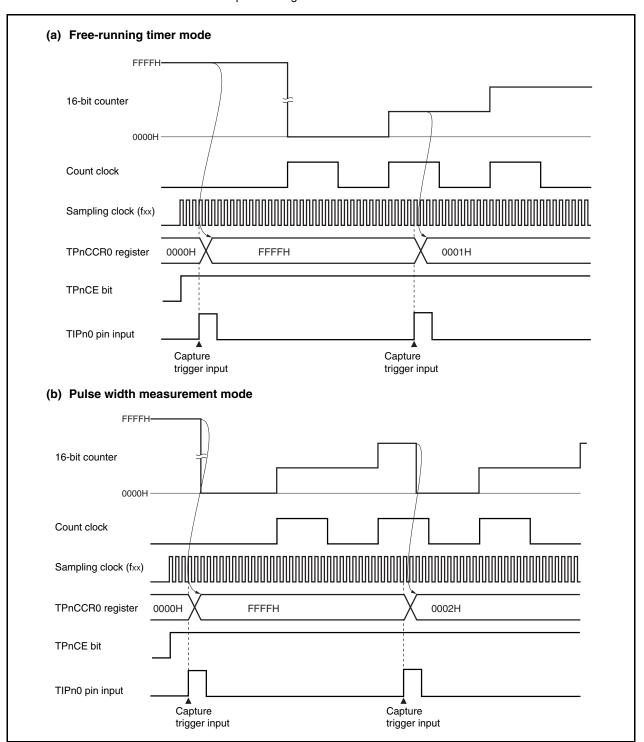

|        | 7.4.6 Free-running timer mode (TPnMD2 to TPnMD0 bits = 101)            | 296 |

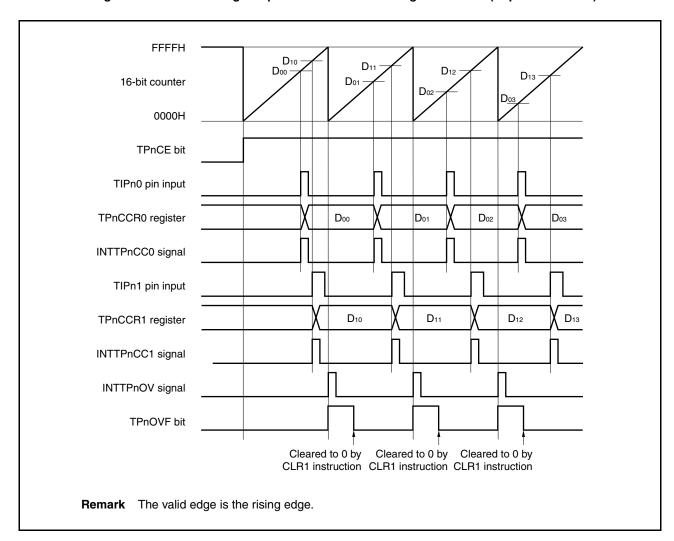

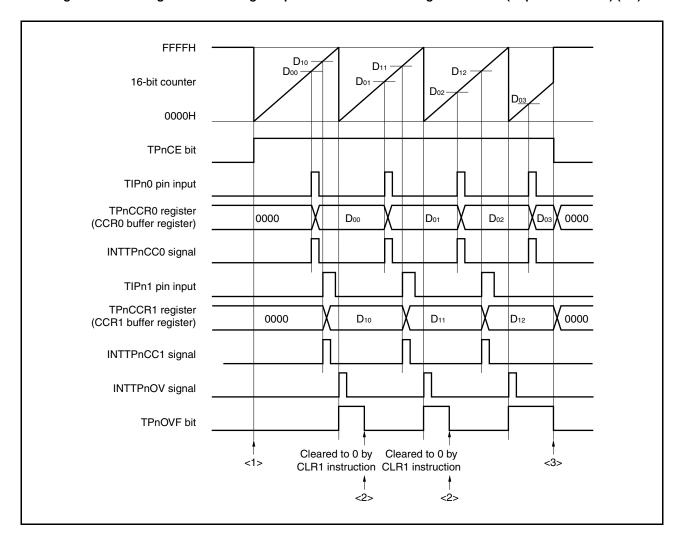

|        | 7.4.7 Pulse width measurement mode (TPnMD2 to TPnMD0 bits = 110)       | 312 |

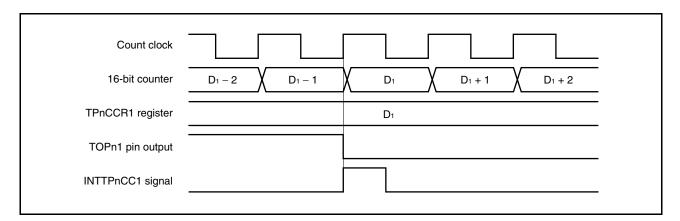

|        | 7.4.8 Timer output operations                                          | 316 |

| 7.5    | Selector                                                               | 317 |

| 7.6    | Cautions                                                               | 318 |

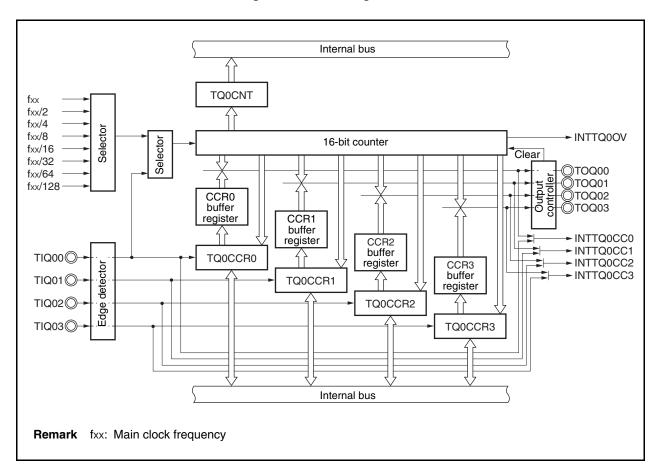

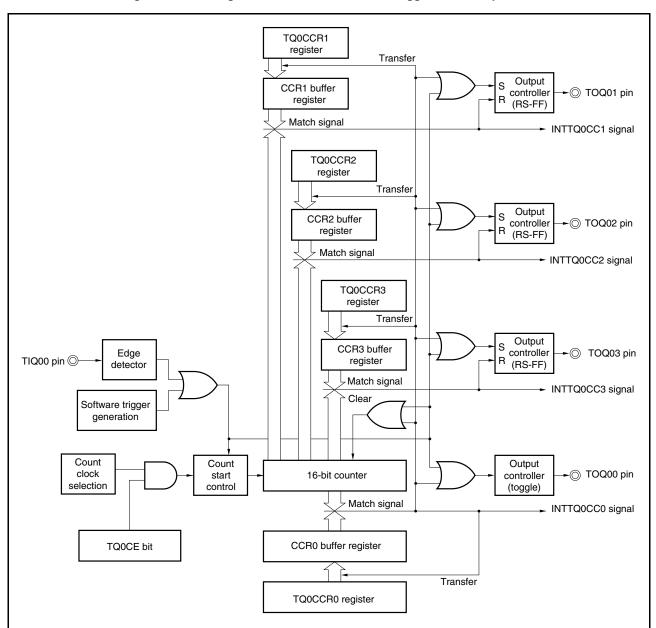

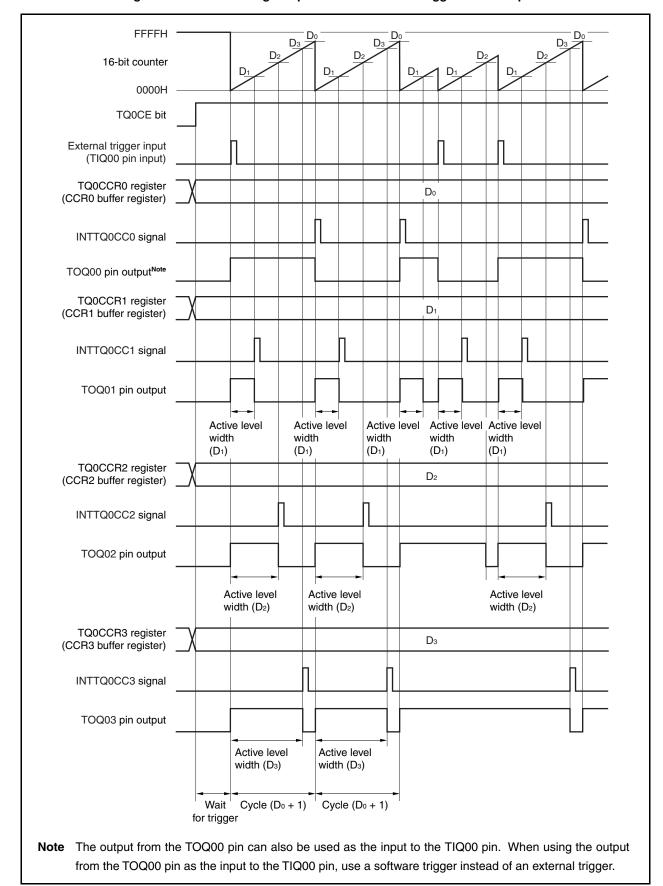

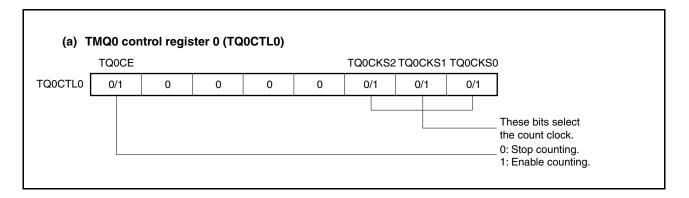

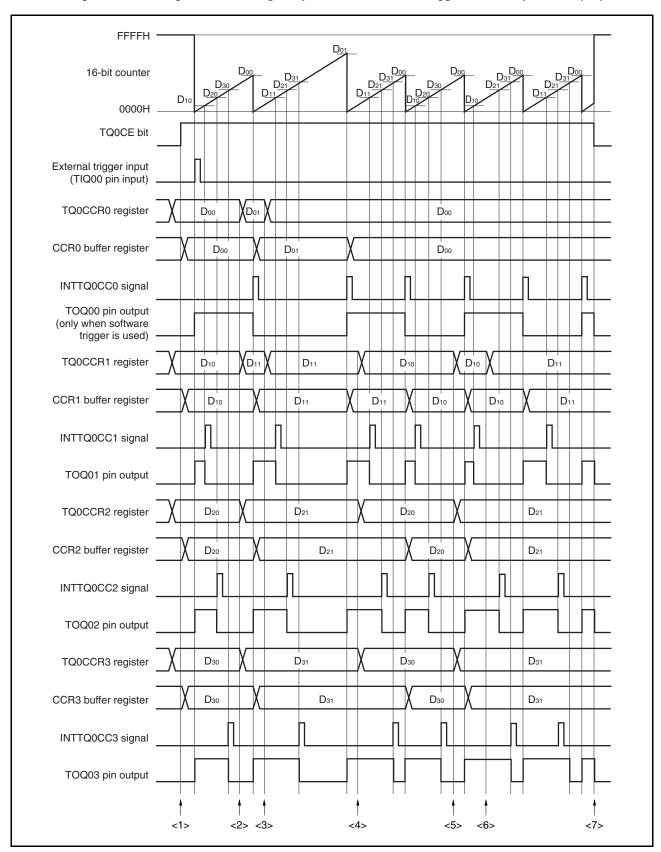

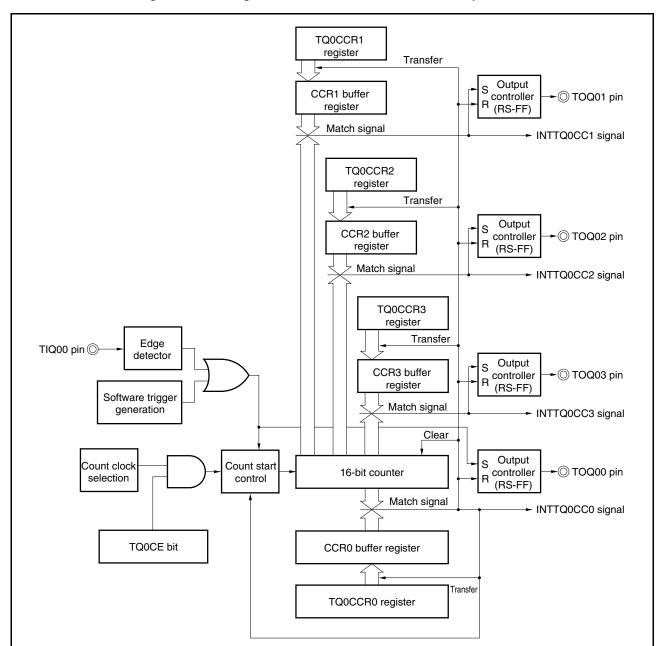

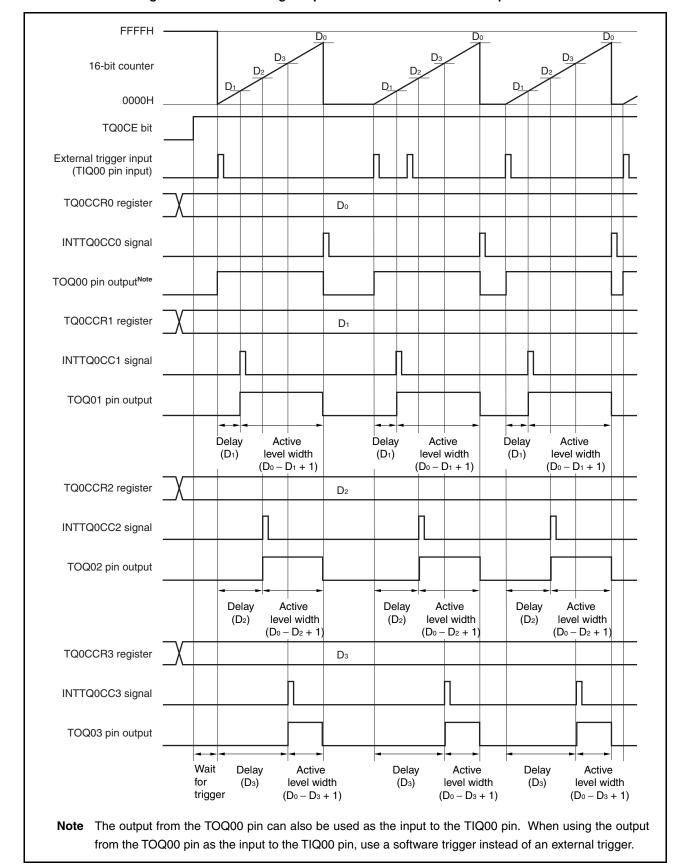

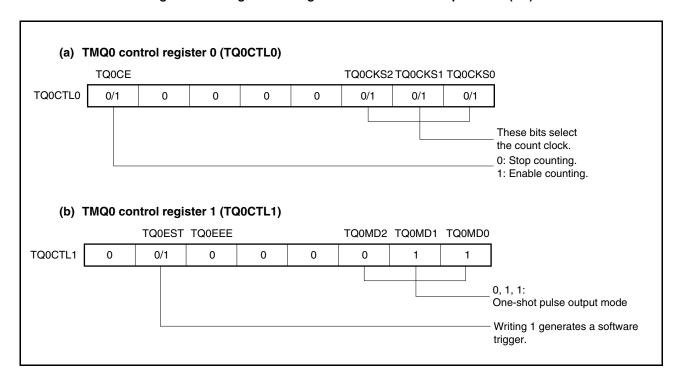

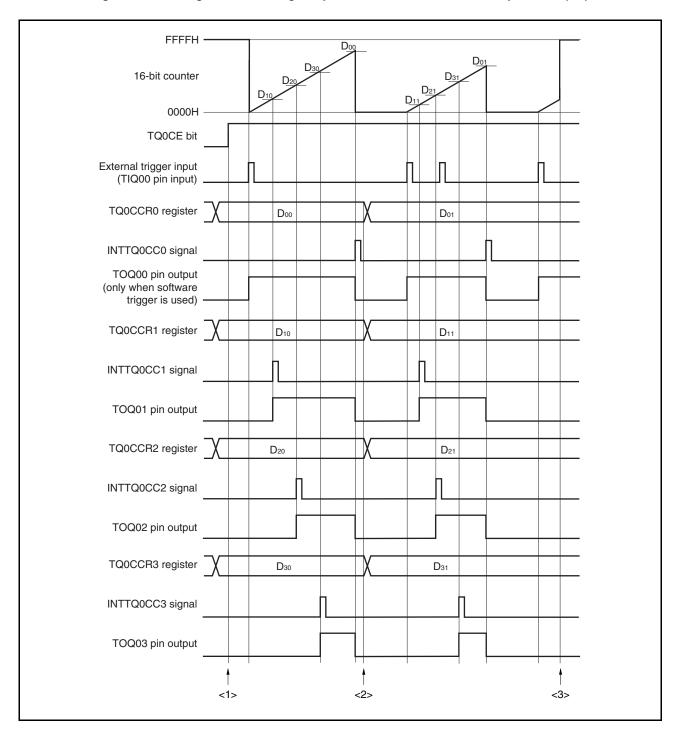

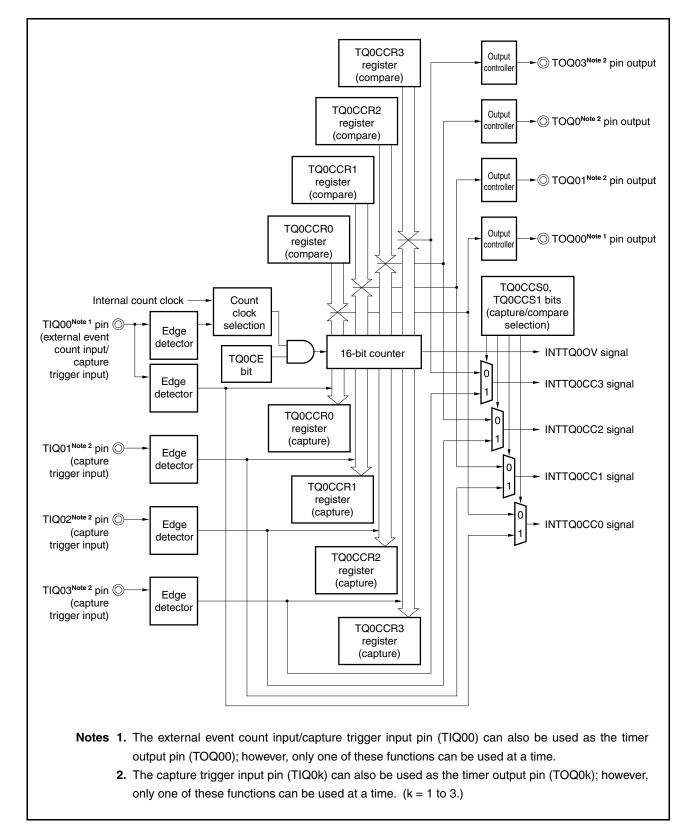

| CHAPTE | ER 8 16-BIT TIMER/EVENT COUNTER Q (TMQ)                                | 319 |

| 8.1    | Functions                                                              | 319 |

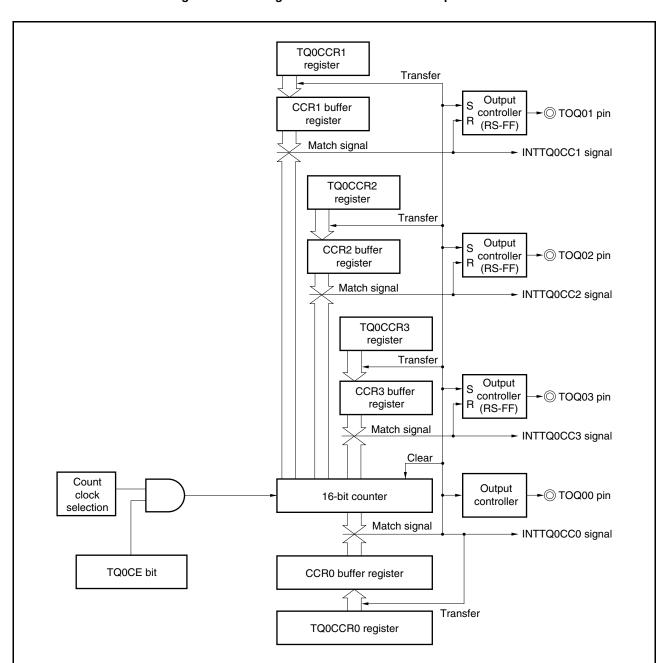

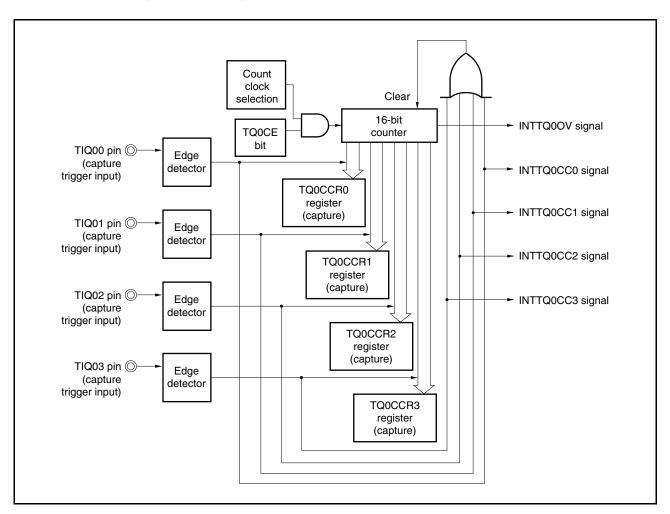

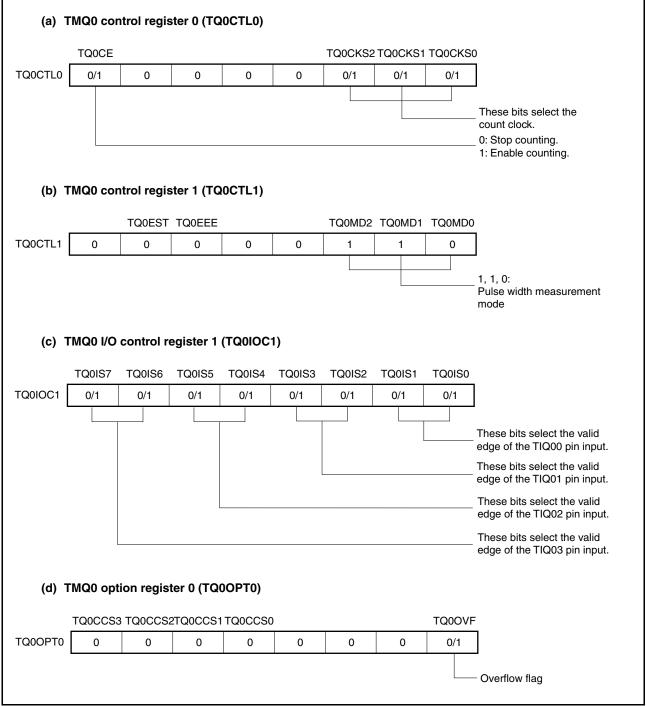

| 8.2    | Configuration                                                          | 320 |

|        | 8.2.1 Pins used by TMQ0                                                | 322 |

|        | 8.2.2 Interrupts                                                       | 322 |

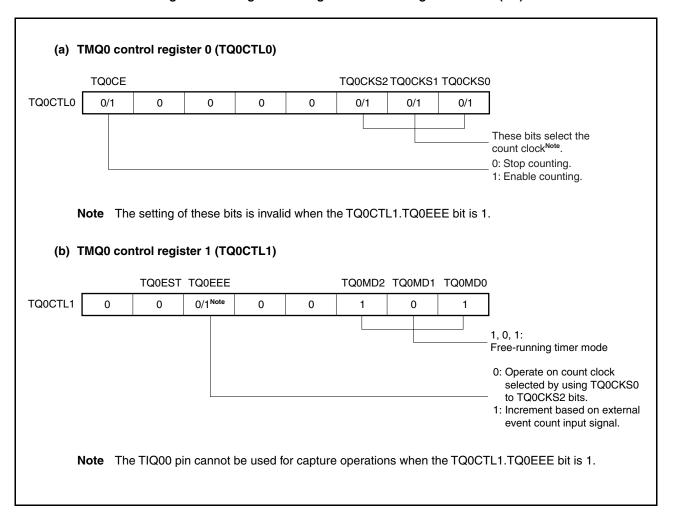

| 8.3    | Registers                                                              | 323 |

| 8.4    | Operations                                                             | 338 |

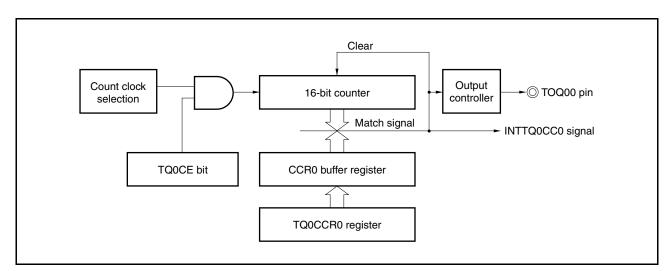

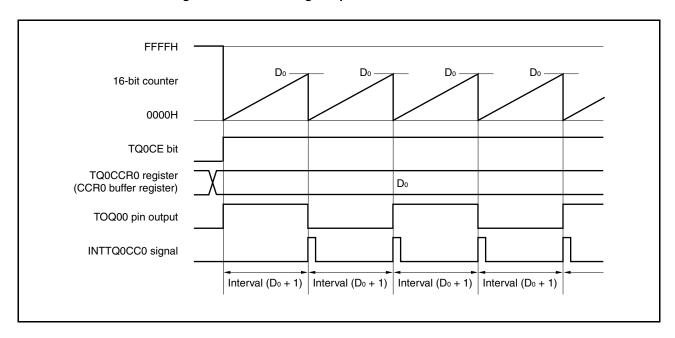

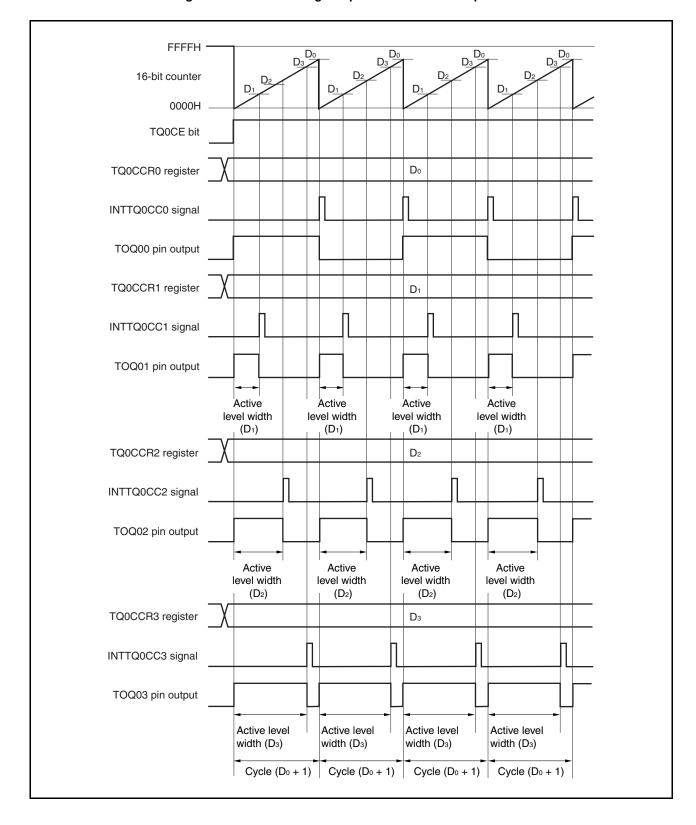

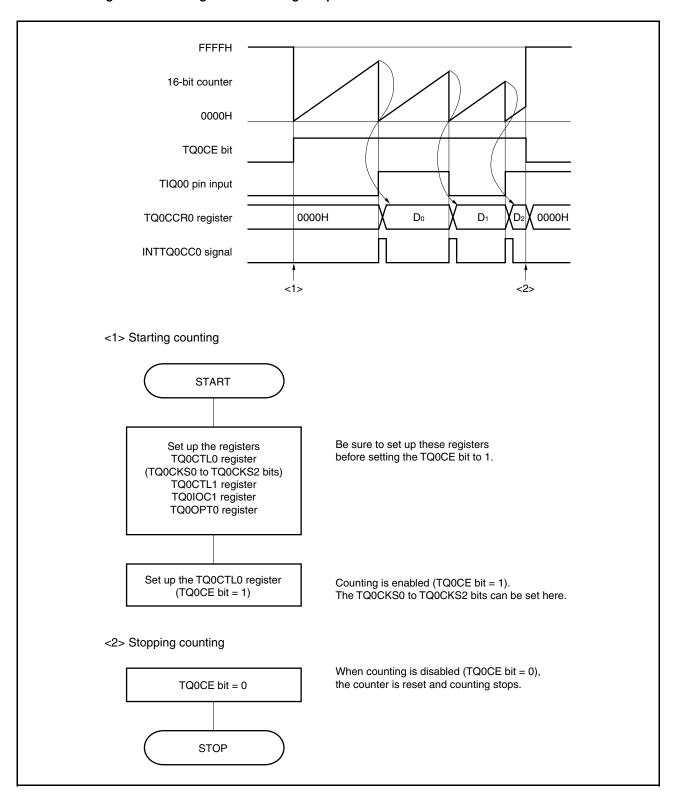

|        | 8.4.1 Interval timer mode (TQ0MD2 to TQ0MD0 bits = 000)                | 345 |

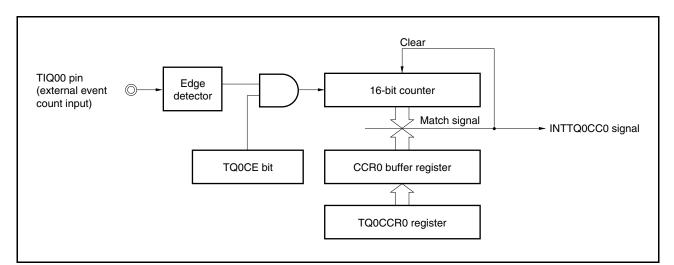

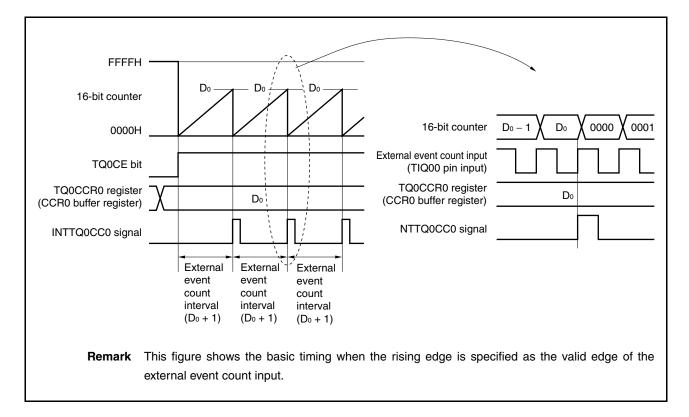

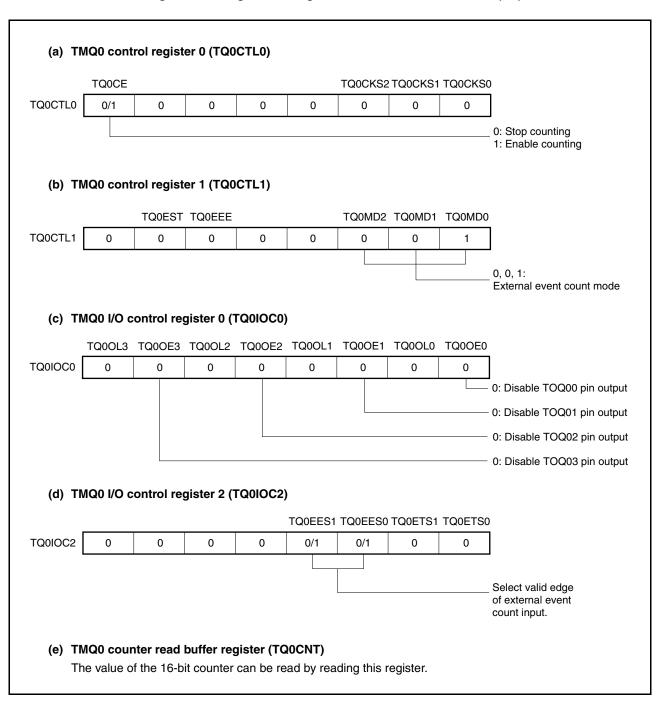

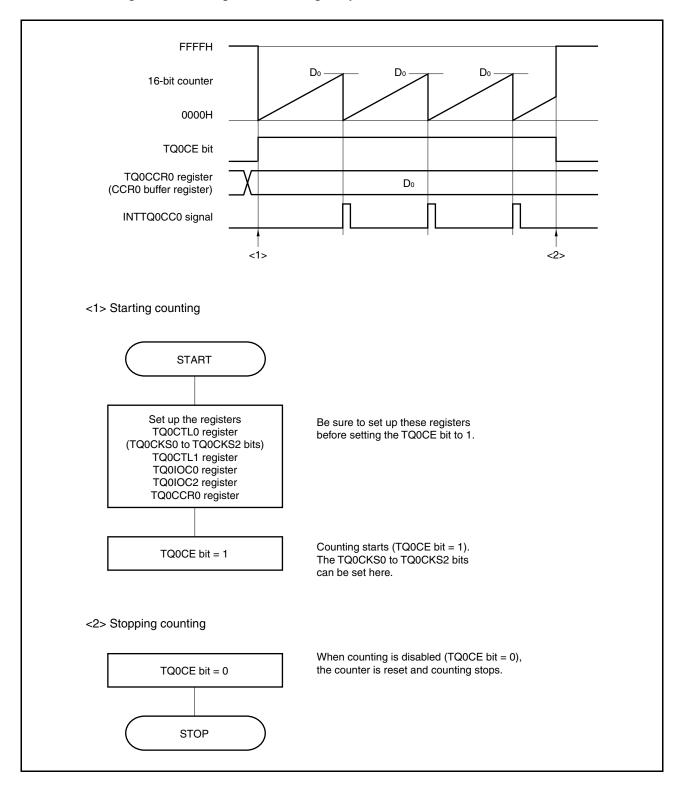

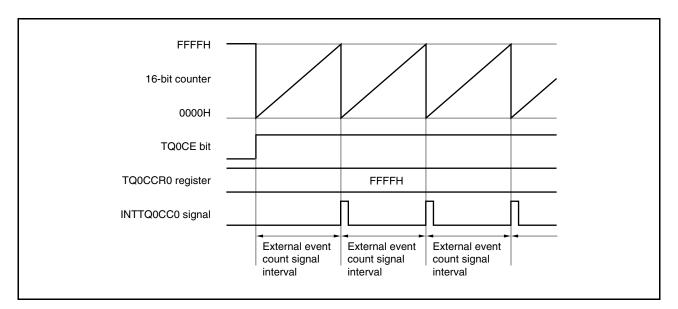

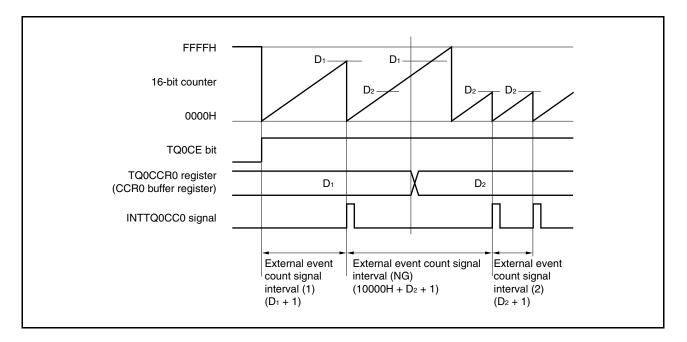

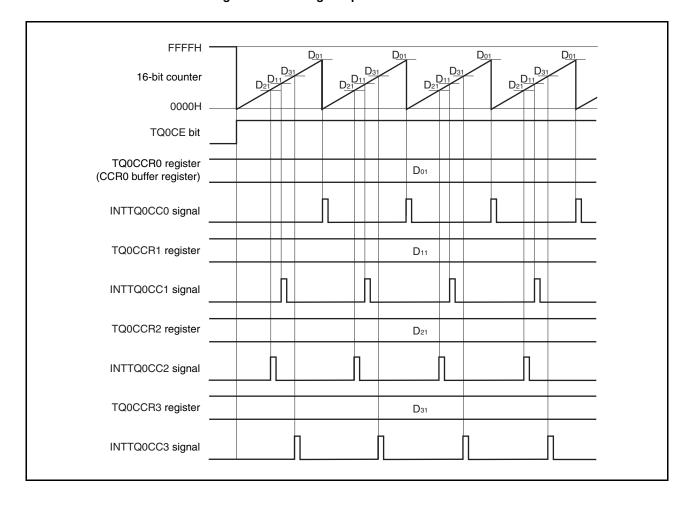

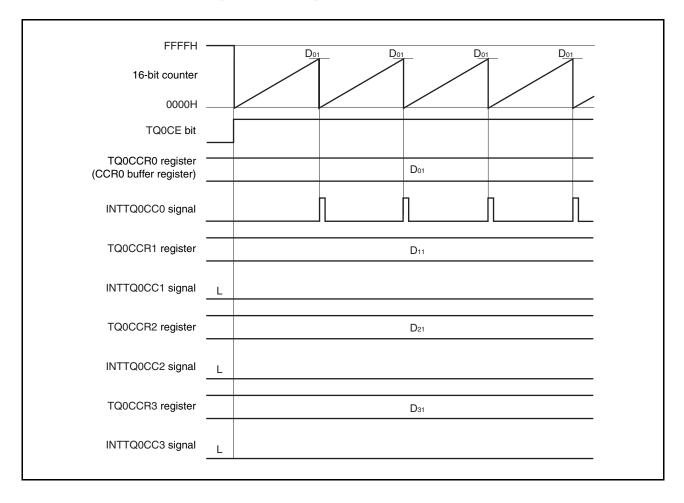

|        | 8.4.2 External event count mode (TQ0MD2 to TQ0MD0 bits = 001)          | 357 |

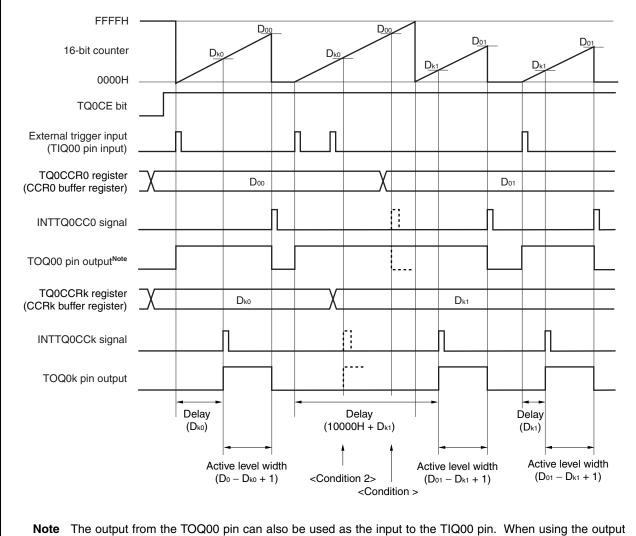

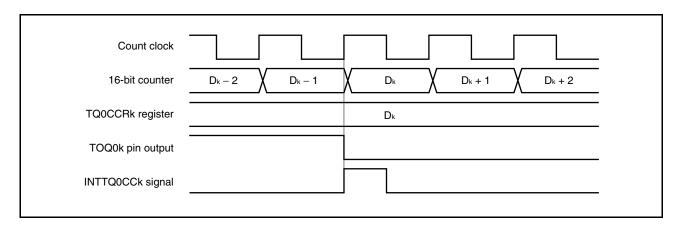

|        | 8.4.3 External trigger pulse output mode (TQ0MD2 to TQ0MD0 bits = 010) | 367 |

|        | 8.4.4 One-shot pulse output mode (TQ0MD2 to TQ0MD0 bits = 011)         | 382 |

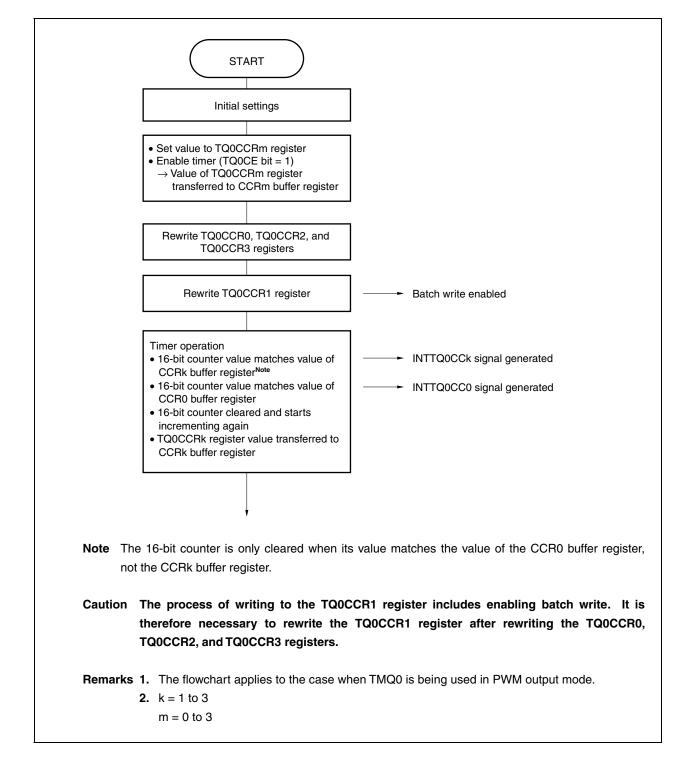

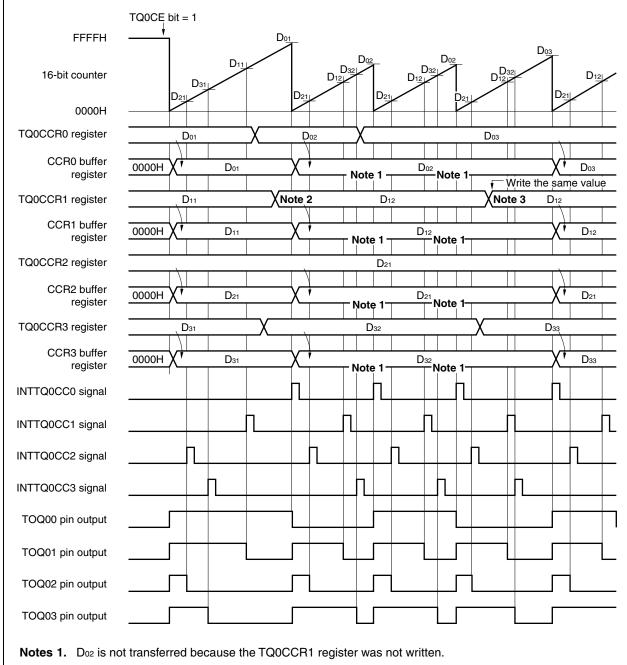

|        | 8.4.5 PWM output mode (TQ0MD2 to TQ0MD0 bits = 100)                    | 392 |

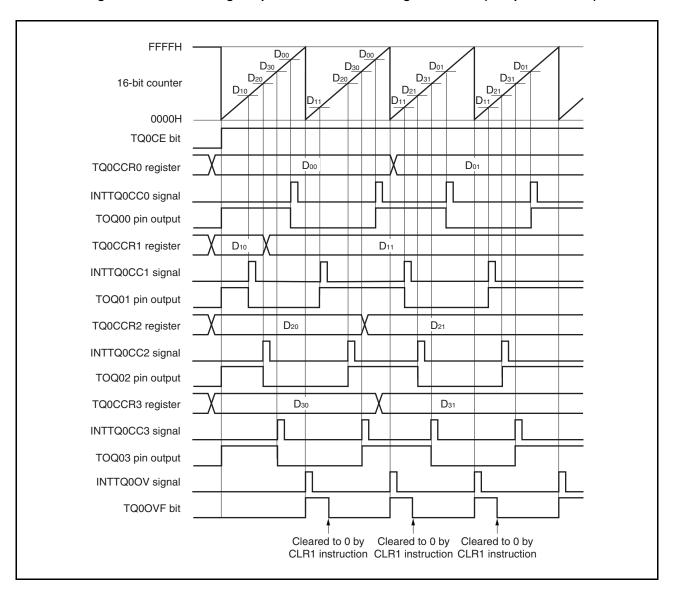

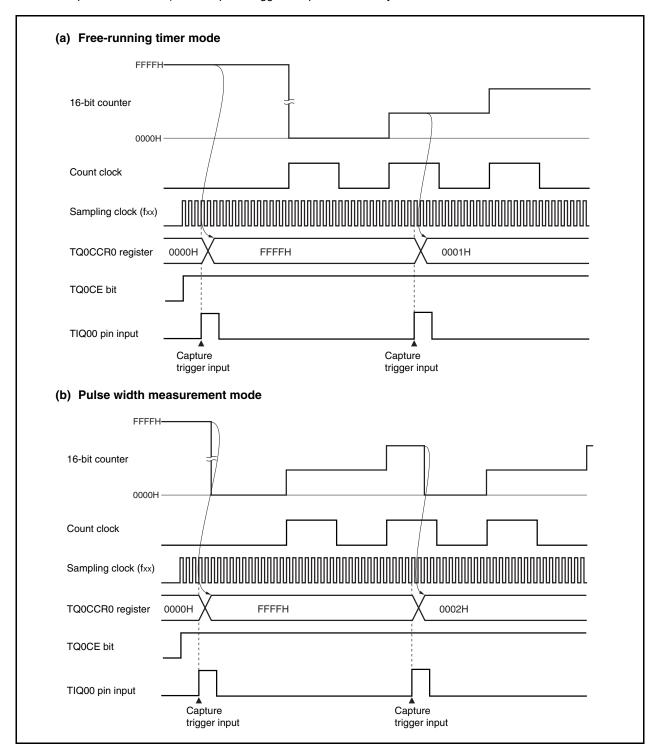

|        | 8.4.6 Free-running timer mode (TQ0MD2 to TQ0MD0 bits = 101)            | 403 |

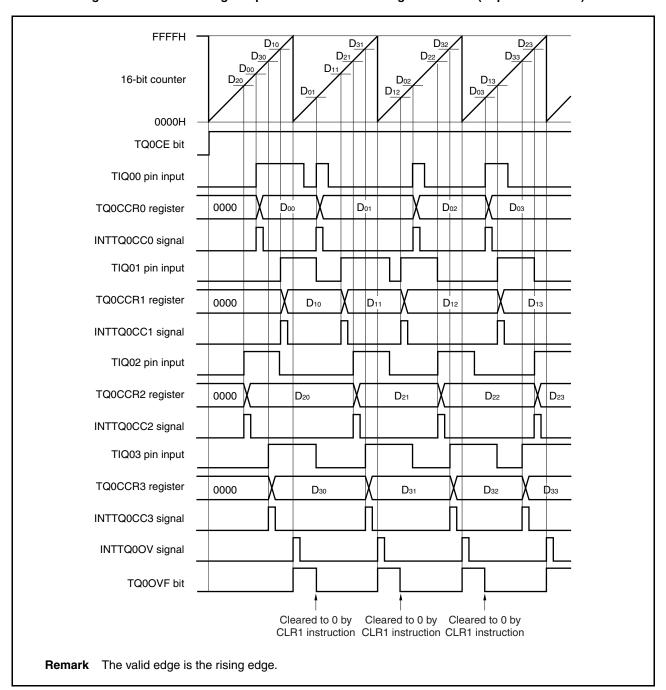

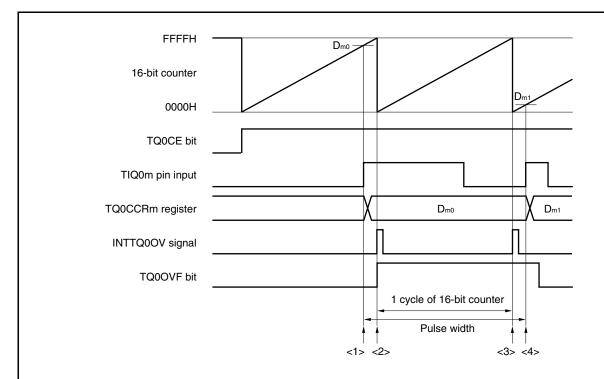

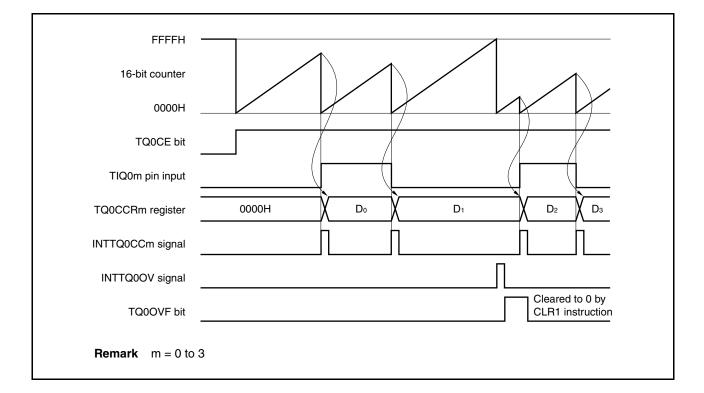

|        | 8.4.7 Pulse width measurement mode (TQ0MD2 to TQ0MD0 bits = 110)       | 423 |

|       |             | 8.4.8 Timer output operations                                                | 428         |

|-------|-------------|------------------------------------------------------------------------------|-------------|

| 8     | .5          | Cautions                                                                     | 429         |

| OLIAD | TED         | O 40 DIT INTEDVAL TIMED M (TMM)                                              | 400         |

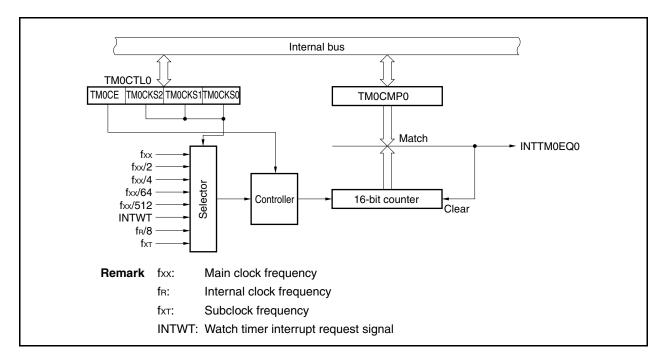

|       | 1 E K<br>.1 | 9 16-BIT INTERVAL TIMER M (TMM)Features                                      |             |

| ·     | .1          | Configuration                                                                |             |

|       |             | •                                                                            |             |

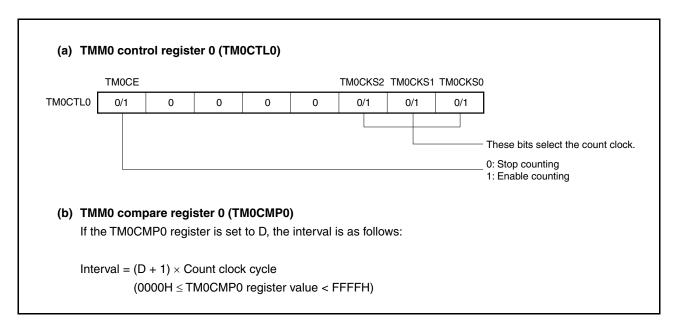

| _     | .3          | Registers                                                                    |             |

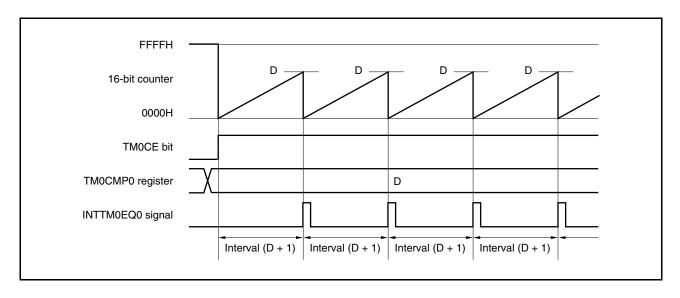

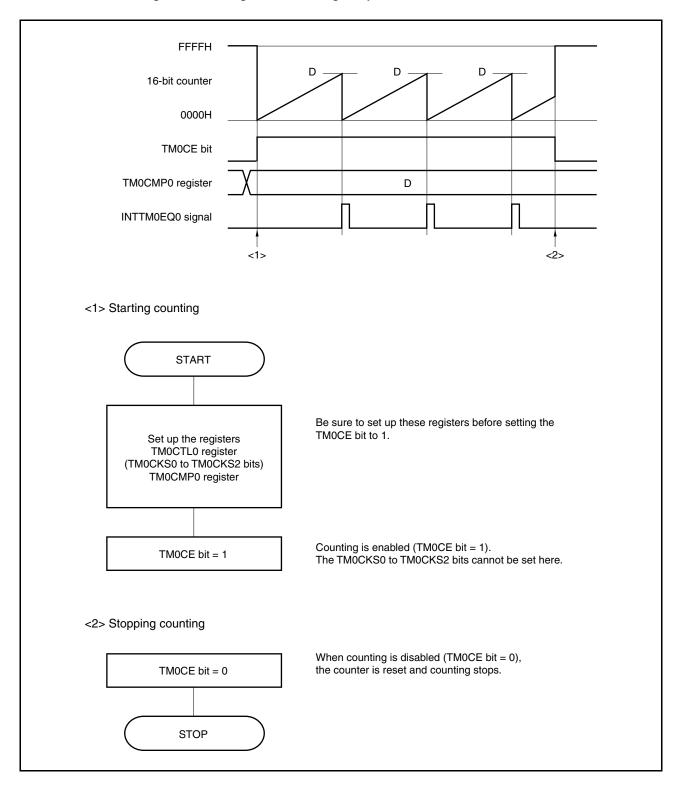

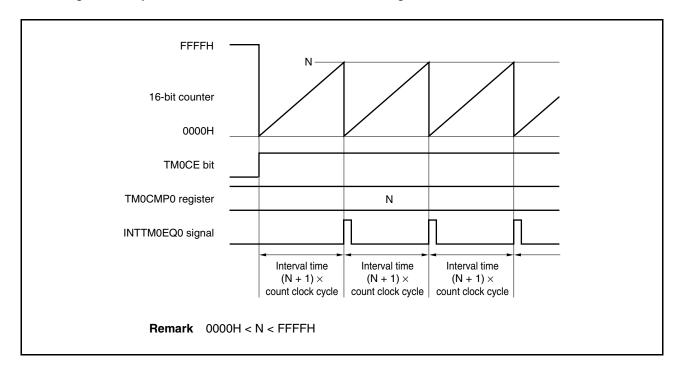

| 9     | .4          | Operation                                                                    |             |

|       |             | 9.4.1 Interval timer mode                                                    |             |

|       |             | 9.4.2 Cautions                                                               | 438         |

| СНАР  | TER         | 10 WATCH TIMER                                                               | 439         |

| 1     | 0.1         | Functions                                                                    | 439         |

| 1     | 0.2         | Configuration                                                                | 440         |

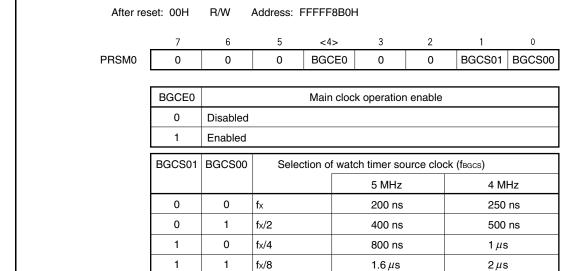

| 1     | 0.3         | Control Registers                                                            | 442         |

| 1     | 0.4         | Operation                                                                    | 446         |

|       |             | 10.4.1 Watch timer operations                                                | 446         |

|       |             | 10.4.2 Interval timer operations                                             | 447         |

| 1     | 0.5         | Cautions                                                                     |             |

|       |             |                                                                              |             |

|       |             | 11 REAL-TIME COUNTER                                                         |             |

|       |             | Functions                                                                    |             |

| 1     | 1.2         | Configuration                                                                |             |

|       |             | 11.2.1 Pin configuration                                                     | 453         |

|       |             | 11.2.2 Interrupt functions                                                   |             |

|       |             | Registers                                                                    |             |

| 1     | 1.4         | Operation                                                                    | 469         |

|       |             | 11.4.1 Initial settings                                                      | 469         |

|       |             | 11.4.2 Rewriting each counter during real-time counter operation             | 470         |

|       |             | 11.4.3 Reading each counter during real-time counter operation               | 471         |

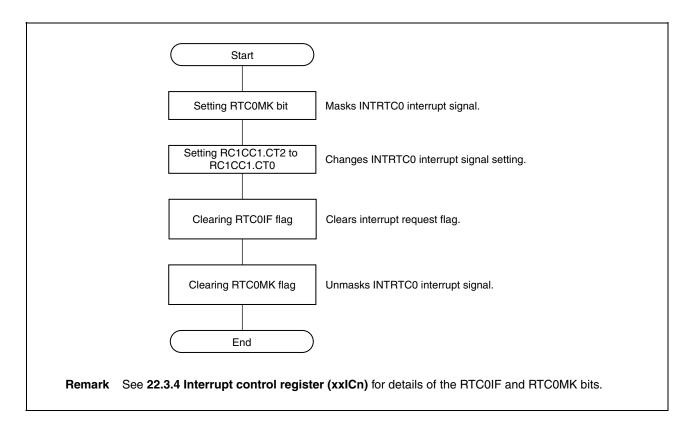

|       |             | 11.4.4 Changing INTRTC0 interrupt setting during real-time counter operation | 472         |

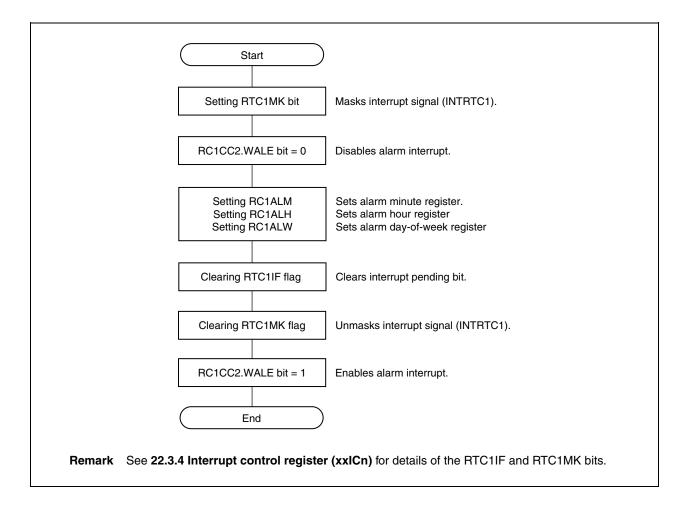

|       |             | 11.4.5 Changing INTRTC1 interrupt setting during real-time counter operation | 473         |

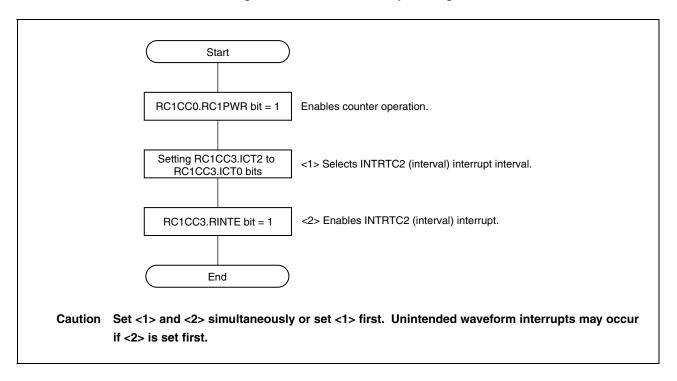

|       |             | 11.4.6 Initial INTRTC2 interrupt settings                                    | 474         |

|       |             | 11.4.7 Changing INTRTC2 interrupt setting during real-time counter operation | 475         |

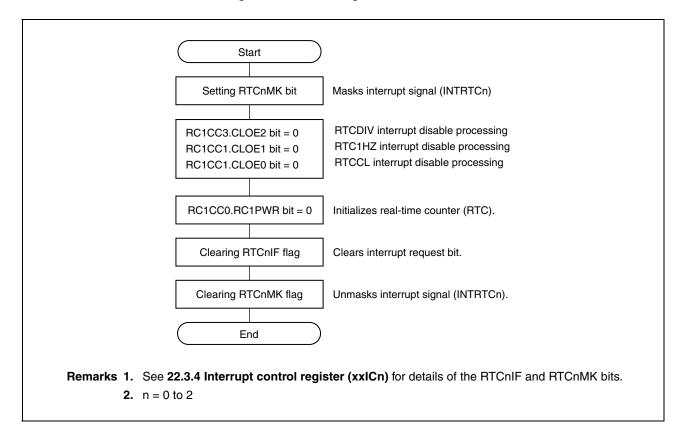

|       |             | 11.4.8 Initializing real-time counter                                        | 476         |

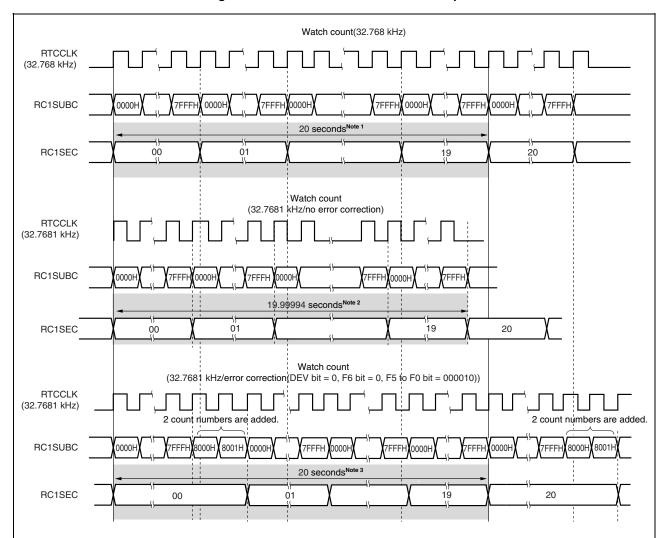

|       |             | 11.4.9 Watch error correction example of real-time counter                   | 477         |

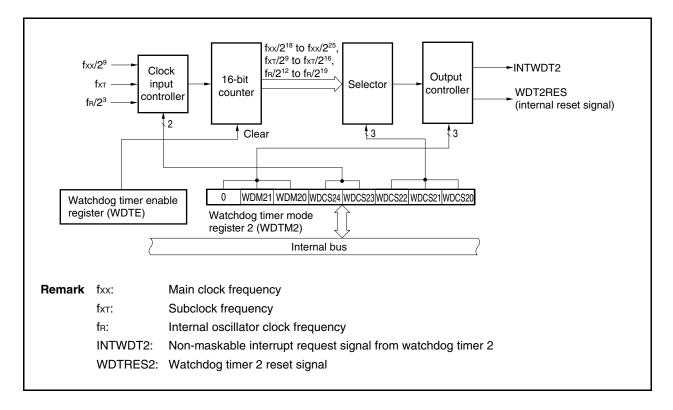

| СНФБ  | TFP         | 12 WATCHDOG TIMER 2                                                          | <u>/</u> Ω1 |

|       |             | Functions                                                                    |             |

|       |             | Configuration                                                                |             |

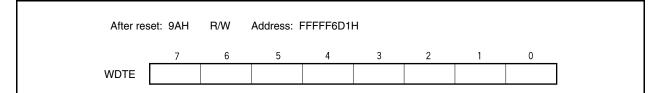

|       |             | Registers                                                                    |             |

|       |             | Operation                                                                    |             |

|       | ∠.→         | Oporacio:                                                                    | 403         |

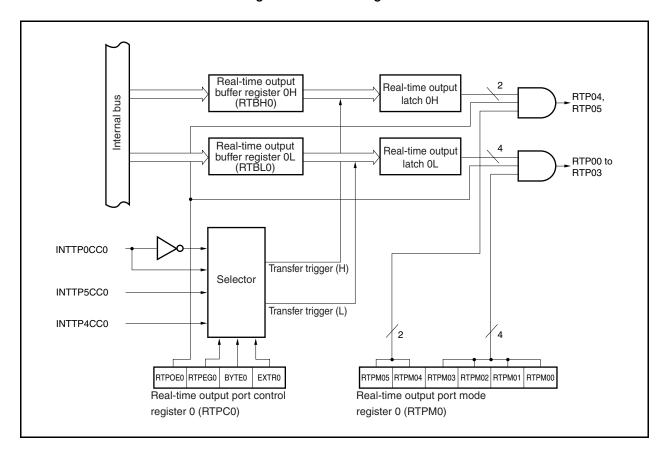

| CHAP  | TER         | 13 REAL-TIME OUTPUT FUNCTION (RTO)                                           | 486         |

| 1     | 3.1         | Function                                                                     | 486         |

|                                         | 13.2  | Configuration                                       | 487 |

|-----------------------------------------|-------|-----------------------------------------------------|-----|

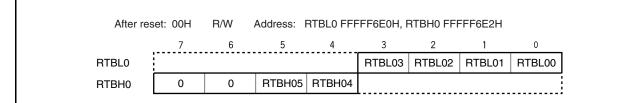

|                                         | 13.3  | Registers                                           | 489 |

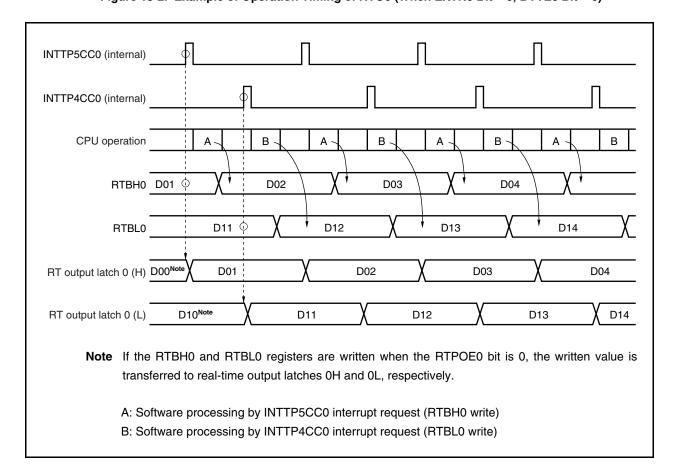

|                                         | 13.4  | Operation                                           | 491 |

|                                         | 13.5  | Usage                                               | 492 |

|                                         | 13.6  | Cautions                                            | 492 |

|                                         |       |                                                     |     |

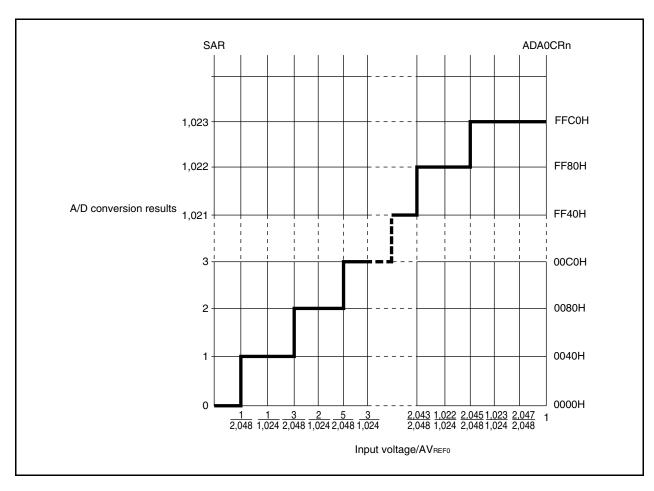

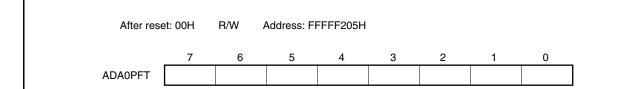

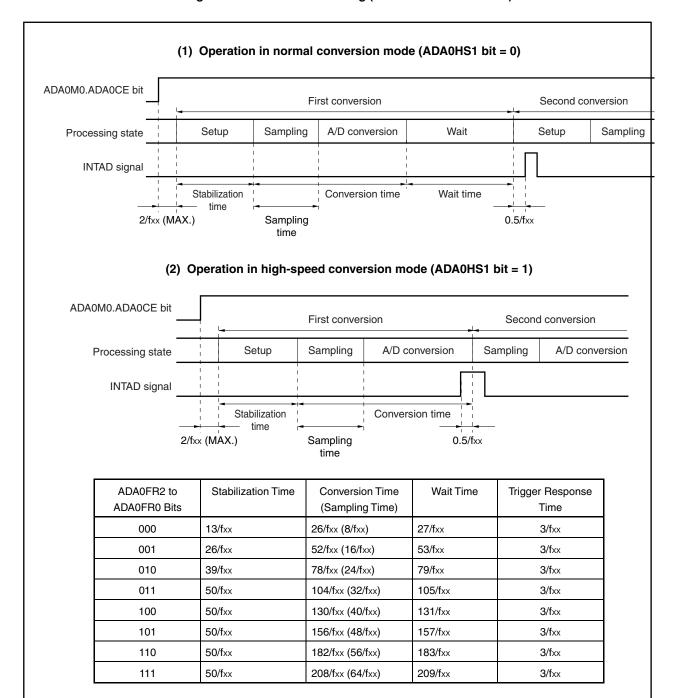

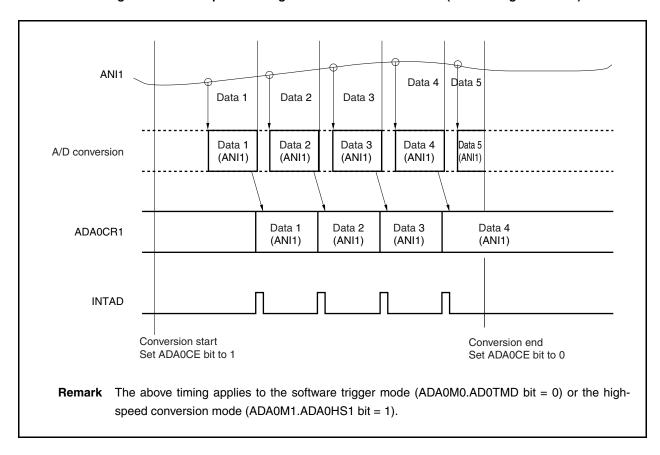

| CHA                                     |       | R 14 A/D CONVERTER                                  |     |

|                                         |       | Overview                                            |     |

|                                         |       | Functions                                           |     |

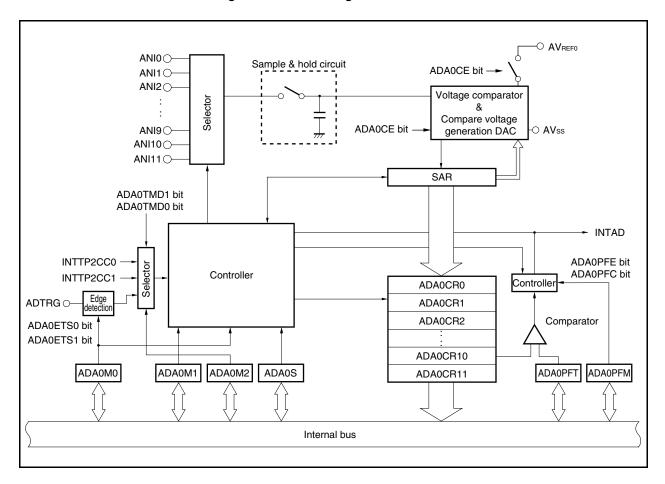

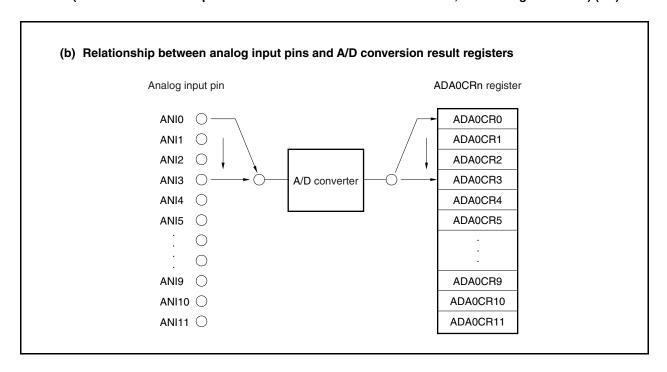

|                                         |       | Configuration                                       |     |

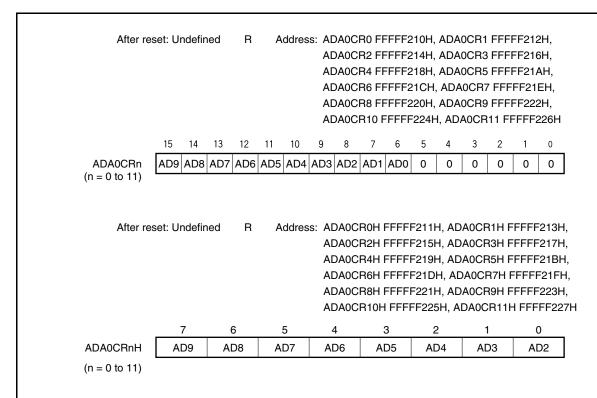

|                                         |       | Registers                                           |     |

|                                         | 14.5  | Operation                                           |     |

|                                         |       | 14.5.1 Basic operation                              |     |

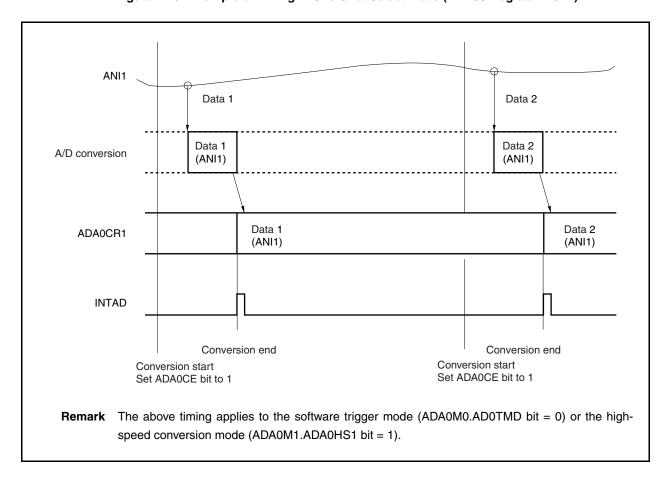

|                                         |       | 14.5.2 Conversion timing                            |     |

|                                         |       | 14.5.3 Trigger modes                                |     |

|                                         |       | 14.5.4 Operation mode                               |     |

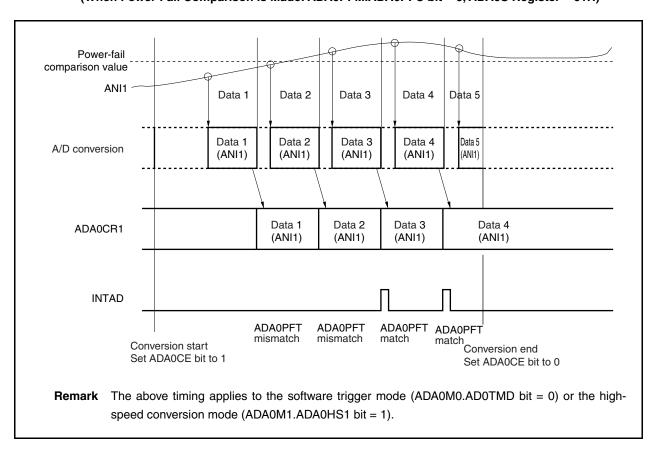

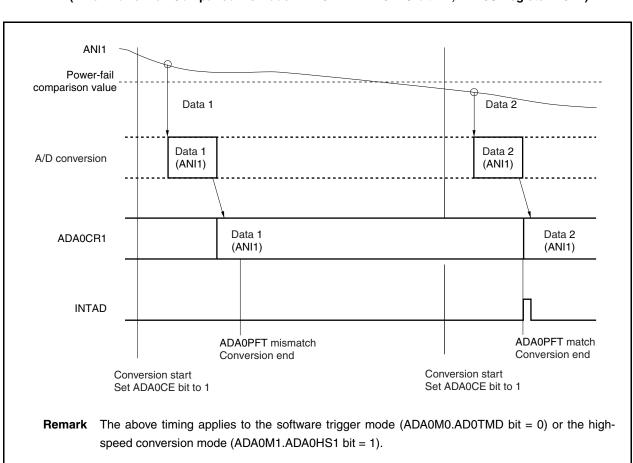

|                                         |       | 14.5.5 Power-fail compare mode                      |     |

|                                         |       | Cautions                                            |     |

|                                         | 14.7  | How to Read A/D Converter Characteristics Table     | 530 |

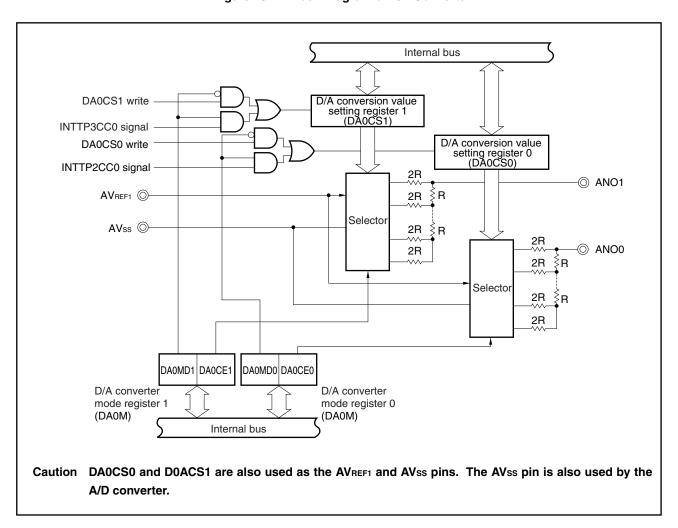

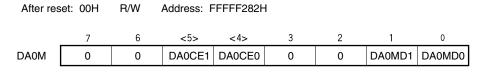

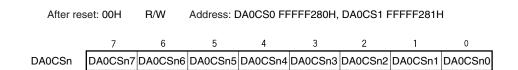

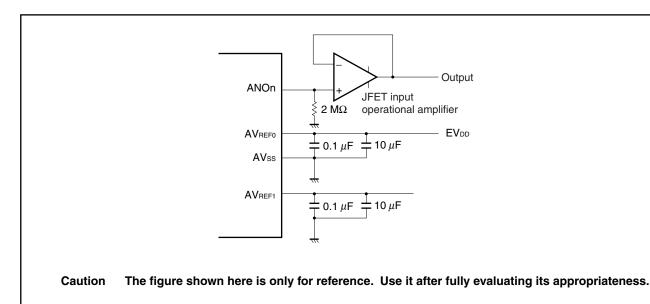

| CHA                                     | APTEF | R 15 D/A CONVERTER                                  | 534 |

| • • • • • • • • • • • • • • • • • • • • |       | Functions                                           |     |

|                                         |       | Configuration                                       |     |

|                                         |       | Registers                                           |     |

|                                         |       | Operation                                           |     |

|                                         |       | 15.4.1 Operation in normal mode                     |     |

|                                         |       | 15.4.2 Operation in real-time output mode           |     |

|                                         |       | 15.4.3 Cautions                                     |     |

|                                         |       |                                                     |     |

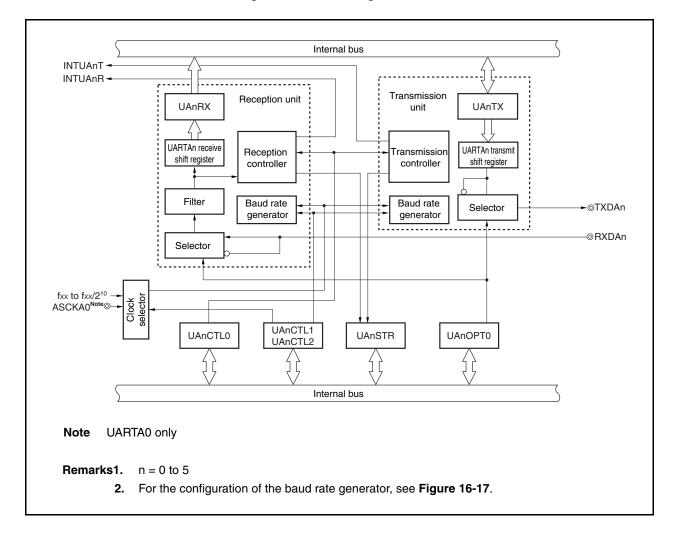

| CHA                                     | APTEF | R 16 ASYNCHRONOUS SERIAL INTERFACE A (UARTA)        | 540 |

|                                         | 16.1  | Features                                            | 540 |

|                                         | 16.2  | Configuration                                       | 541 |

|                                         |       | 16.2.1 Pin functions of each channel                | 543 |

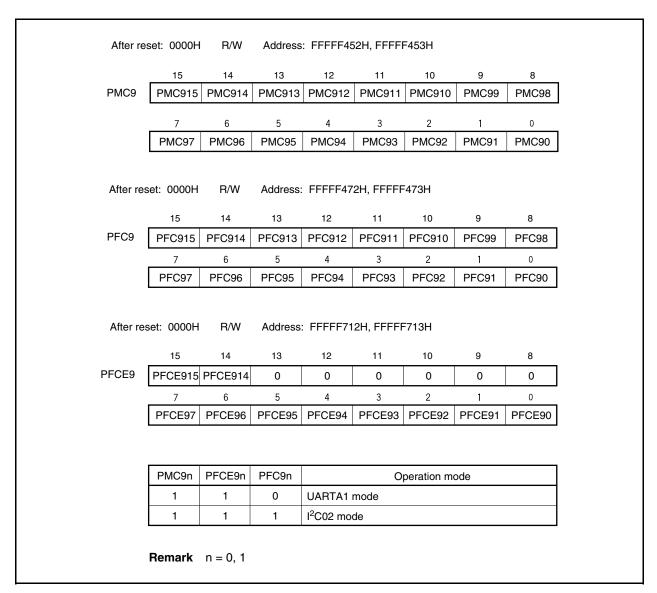

|                                         | 16.3  | Mode Switching of UARTA and Other Serial Interfaces | 544 |

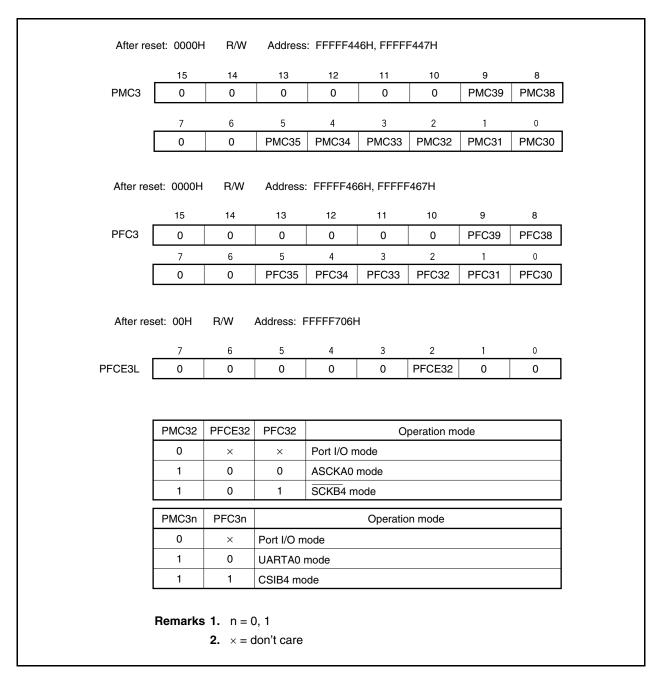

|                                         |       | 16.3.1 UARTA0 and CSIB4 mode switching              | 544 |

|                                         |       | 16.3.2 UARTA1 and I <sup>2</sup> C02 mode switching | 545 |

|                                         |       | 16.3.3 UARTA2 and I <sup>2</sup> C00 mode switching | 546 |

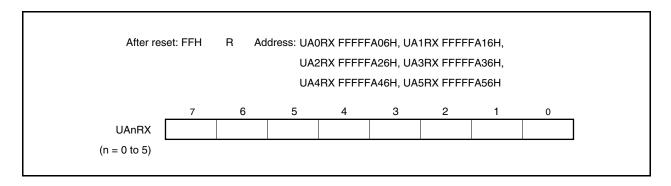

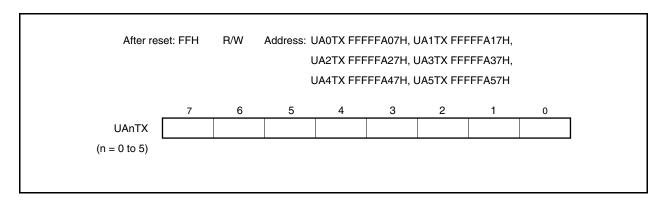

|                                         | 16.4  | Registers                                           | 547 |

|                                         | 16.5  | Interrupt Request Signals                           | 554 |

|                                         | 16.6  | Operation                                           | 555 |

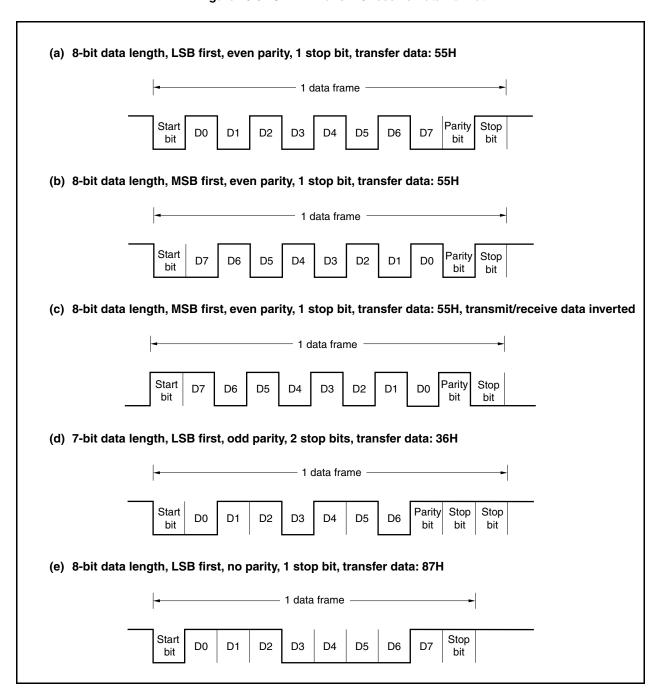

|                                         |       | 16.6.1 Data format                                  | 555 |

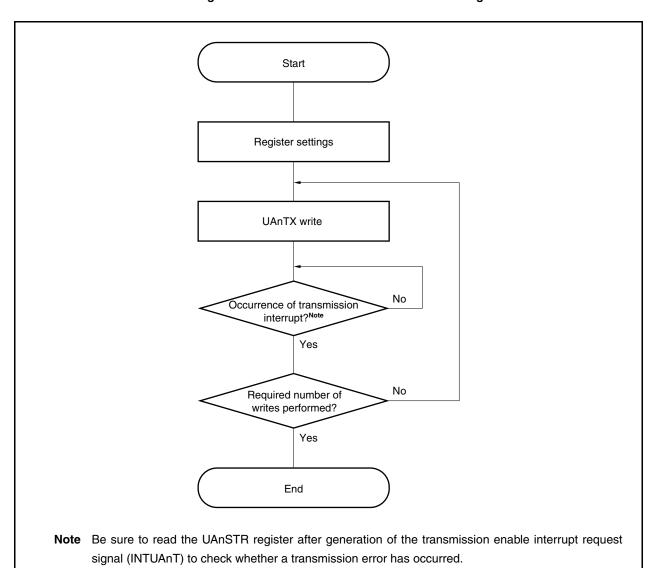

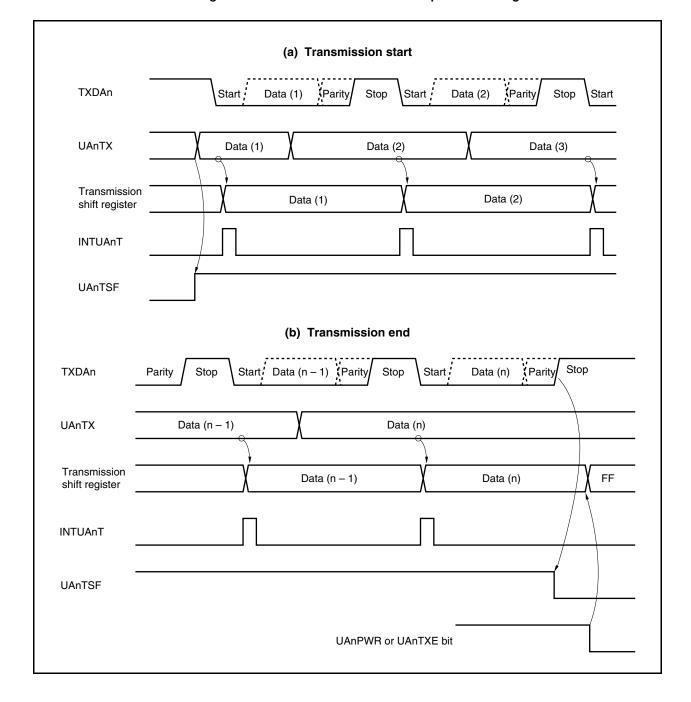

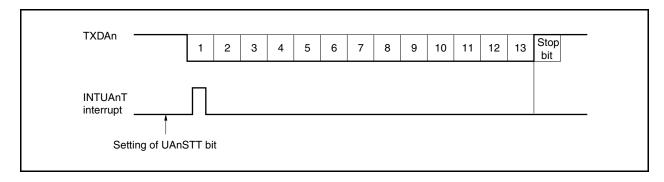

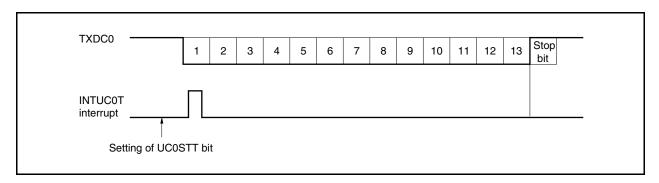

|                                         |       | 16.6.2 UART transmission                            | 557 |

|                                         |       | 16.6.3 Continuous transmission procedure            | 558 |

|                                         |       | ·                                                   |     |

|     |       | 16.6.5 Reception errors                                                | 562 |

|-----|-------|------------------------------------------------------------------------|-----|

|     |       | 16.6.6 Parity types and operations                                     | 564 |

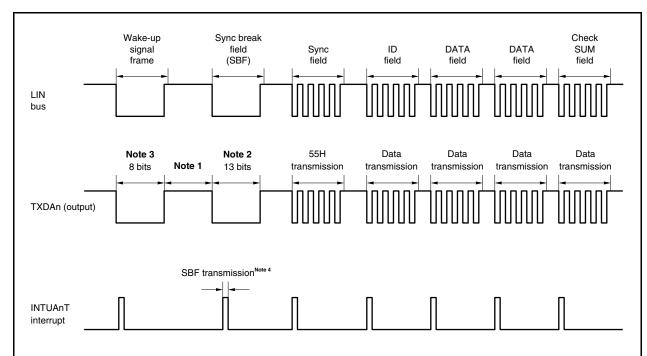

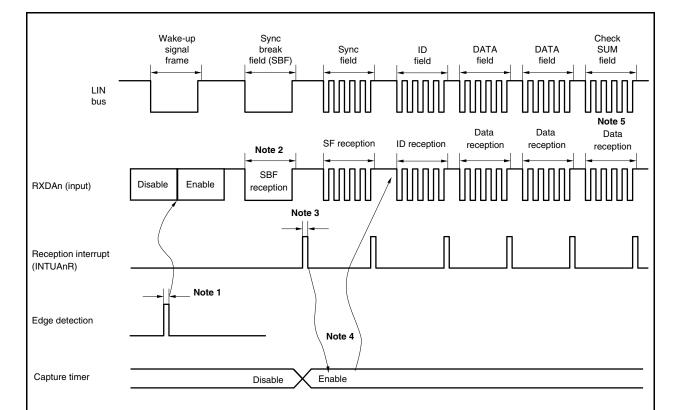

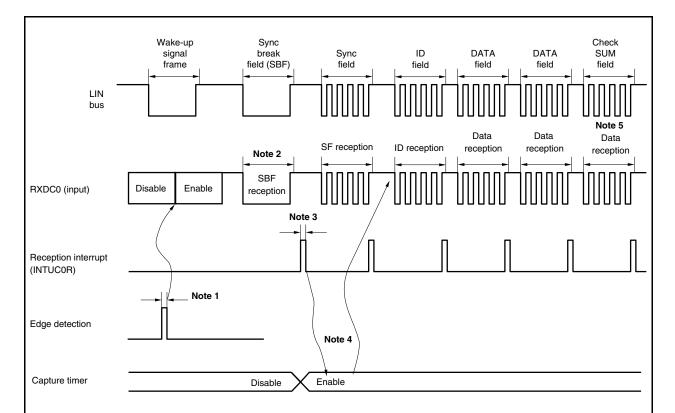

|     |       | 16.6.7 LIN transmission/reception format                               | 565 |

|     |       | 16.6.8 SBF transmission                                                | 567 |

|     |       | 16.6.9 SBF reception                                                   | 568 |

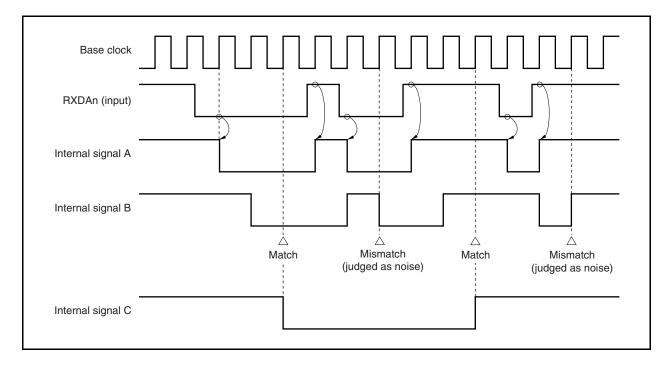

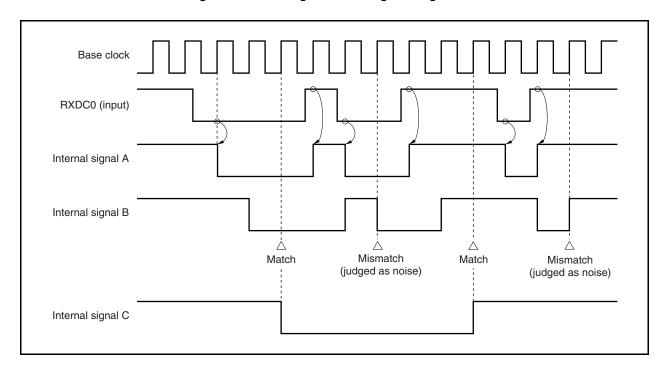

|     |       | 16.6.10 Receive data noise filter                                      | 569 |

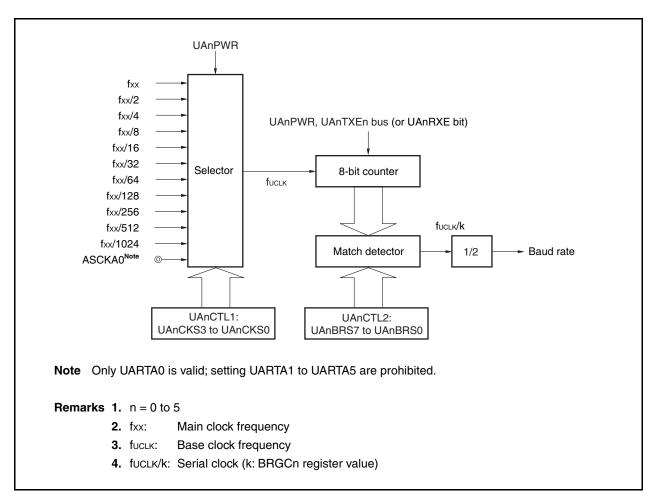

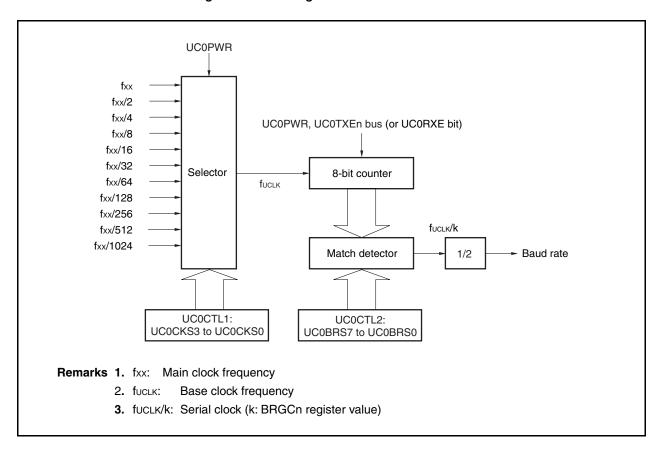

|     | 16.7  | Dedicated Baud Rate Generator                                          | 570 |

|     | 16.8  | Cautions                                                               | 578 |

| СНУ | DTEC  | R 17 ASYNCHRONOUS SERIAL INTERFACE C (UARTC)                           | 570 |

|     |       | Features                                                               |     |

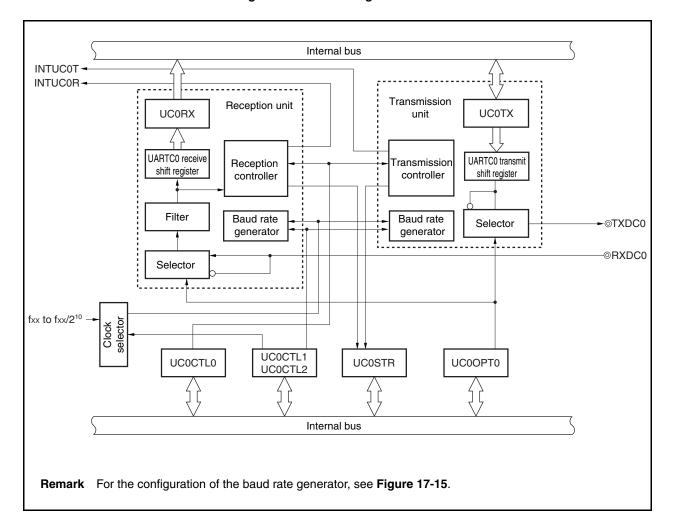

|     |       | Configuration                                                          |     |

|     |       | 17.2.1 Pin functions of each channel                                   |     |

|     | 17.3  | Mode Switching of UARTC and Other Serial Interfaces                    |     |

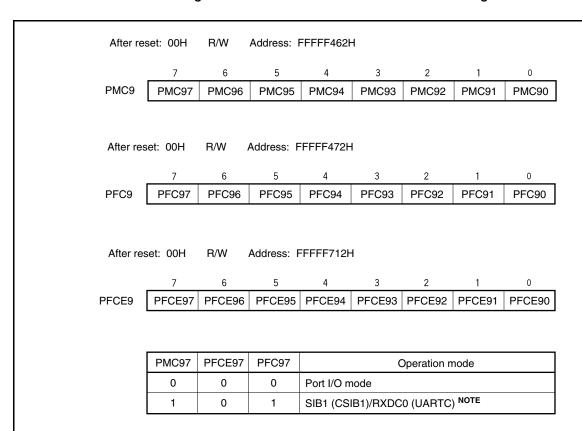

|     |       | 17.3.1 UARTC0 and CSIB1 mode switching                                 |     |

|     | 17.4  | Registers                                                              |     |

|     |       | Interrupt Request Signals                                              |     |

|     |       | Operation                                                              |     |

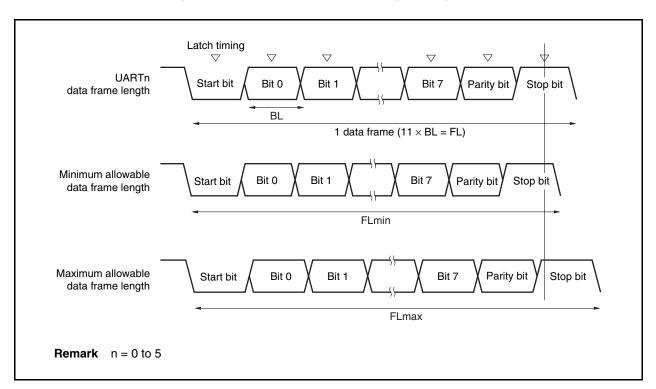

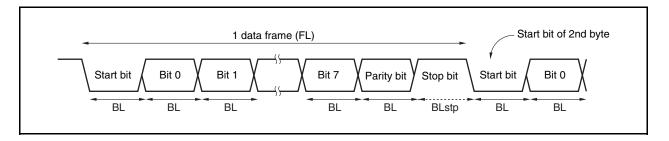

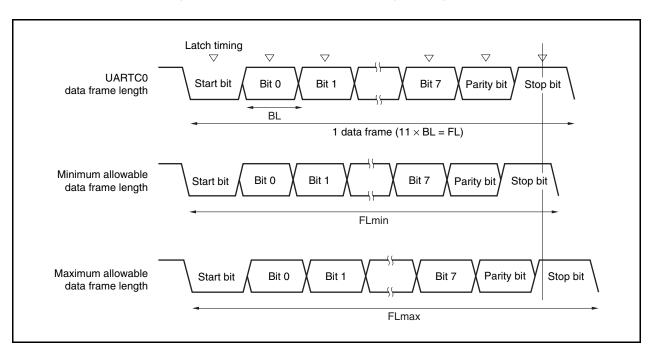

|     |       | 17.6.1 Data format                                                     | 594 |

|     |       | 17.6.2 UART transmission                                               | 596 |

|     |       | 17.6.3 Continuous transmission procedure                               | 597 |

|     |       | 17.6.4 UART reception                                                  | 599 |

|     |       | 17.6.5 Reception errors                                                | 601 |

|     |       | 17.6.6 Parity types and operations                                     | 603 |

|     |       | 17.6.7 LIN transmission/reception format                               | 604 |

|     |       | 17.6.8 SBF transmission                                                | 606 |

|     |       | 17.6.9 SBF reception                                                   | 607 |

|     |       | 17.6.10 Receive data noise filter                                      | 608 |

|     | 17.7  | Dedicated Baud Rate Generator                                          | 609 |

|     | 17.8  | Cautions                                                               | 617 |

|     | DTEE  | A AL OLOOKED CERIAL INTERFACE R (COID)                                 | 640 |

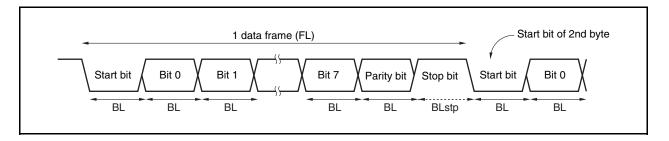

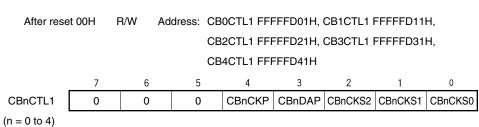

|     |       | R 18 CLOCKED SERIAL INTERFACE B (CSIB)                                 |     |

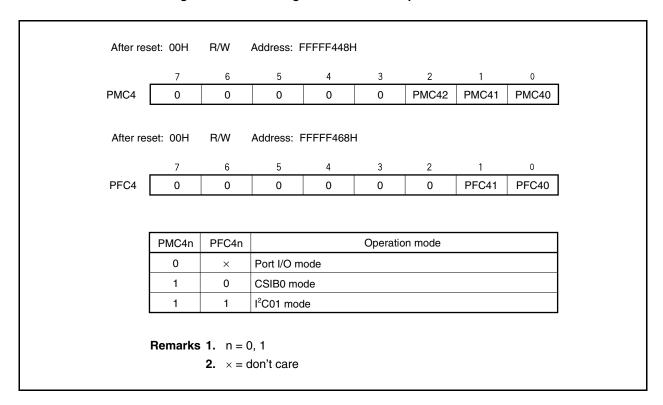

|     | _     | Configuration                                                          |     |

|     | 10.2  | 18.2.1 Pin functions of each channel                                   |     |

|     | 12.3  | Mode Switching of CSIB and Other Serial Interfaces                     |     |

|     | 10.5  | 18.3.1 CSIB0 and I <sup>2</sup> C01 mode switching                     |     |

|     |       | 18.3.2 CSIB4 and UARTA0 mode switching                                 |     |

|     | 18 4  | Registers                                                              |     |

|     |       | Interrupt Request Signals                                              |     |

|     |       | Operation                                                              |     |

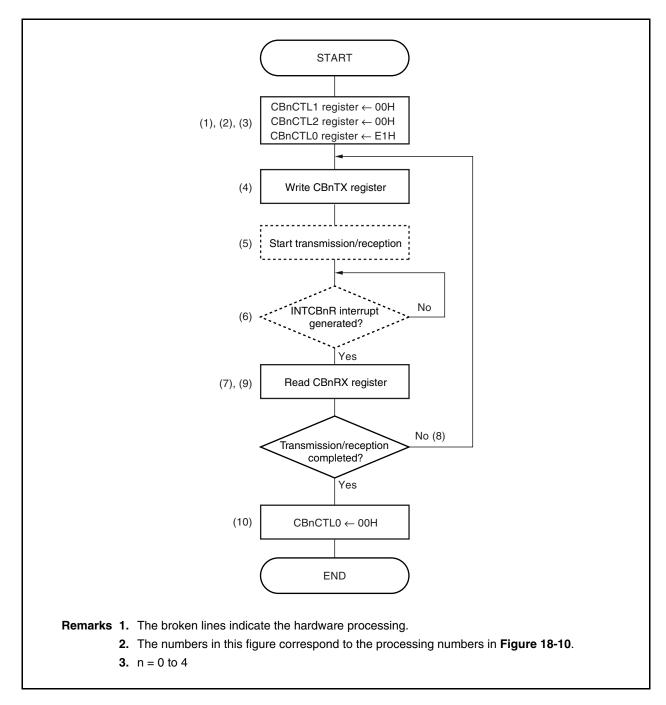

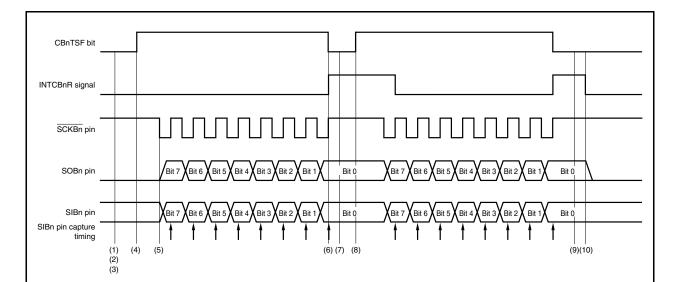

|     | . 5.0 | 18.6.1 Single transfer mode (master mode, transmission mode)           |     |

|     |       | 18.6.2 Single transfer mode (master mode, reception mode)              |     |

|     |       | 18.6.3 Single transfer mode (master mode, transmission/reception mode) |     |

|     |       |                                                                        |     |

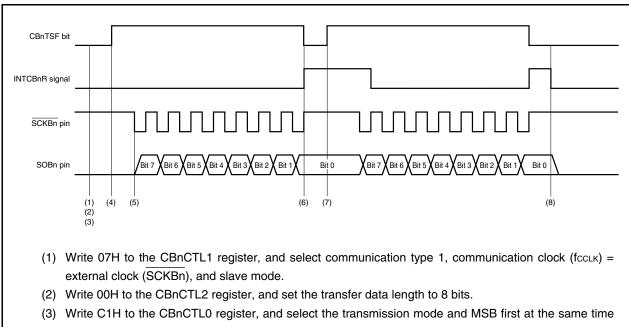

|      |       | 18.6.4 Single transfer mode (slave mode, transmission mode)                               | 639 |

|------|-------|-------------------------------------------------------------------------------------------|-----|

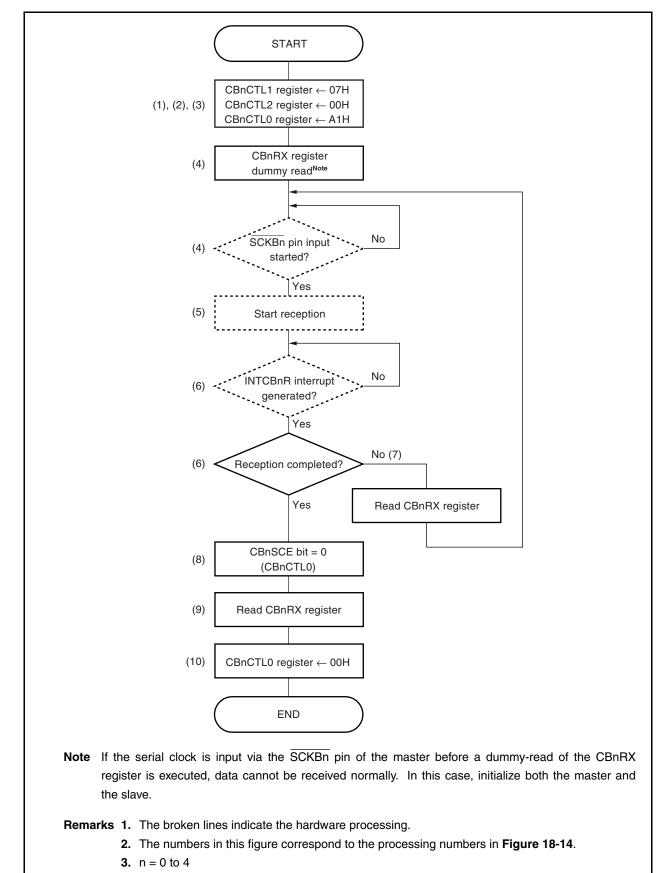

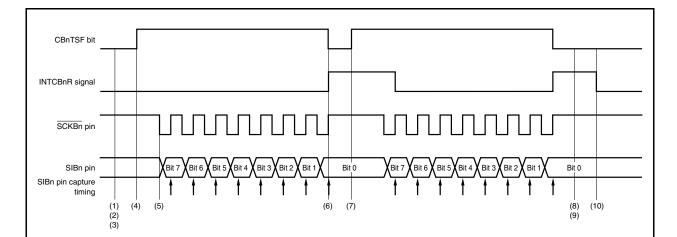

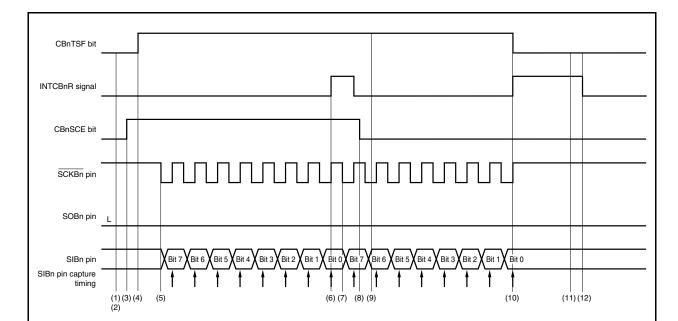

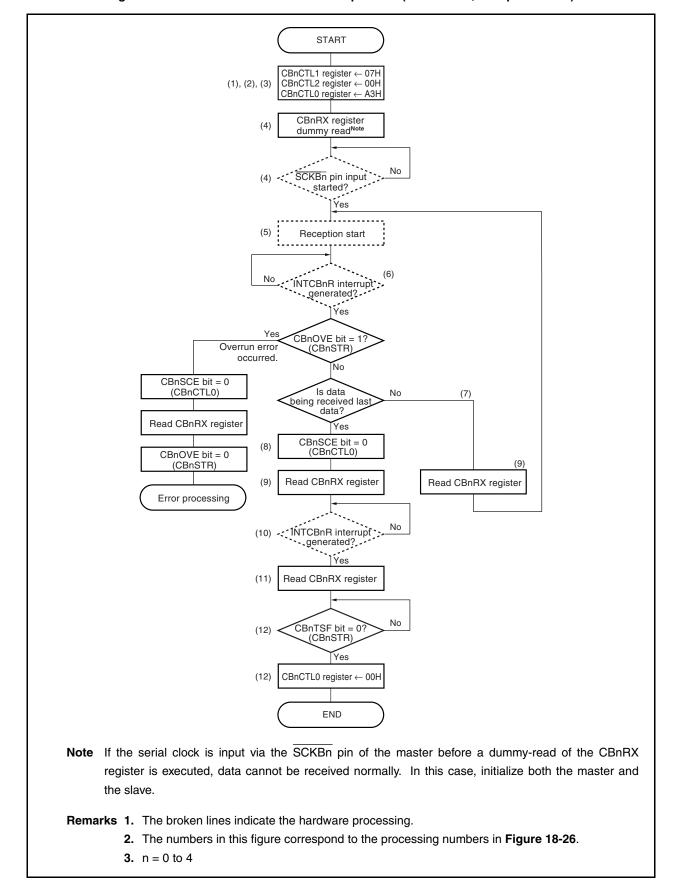

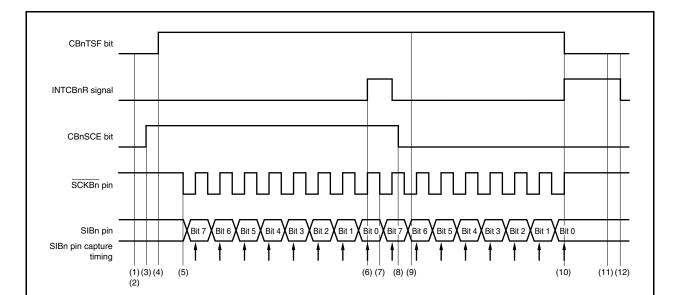

|      |       | 18.6.5 Single transfer mode (slave mode, reception mode)                                  | 641 |

|      |       | 18.6.6 Single transfer mode (slave mode, transmission/reception mode)                     | 644 |

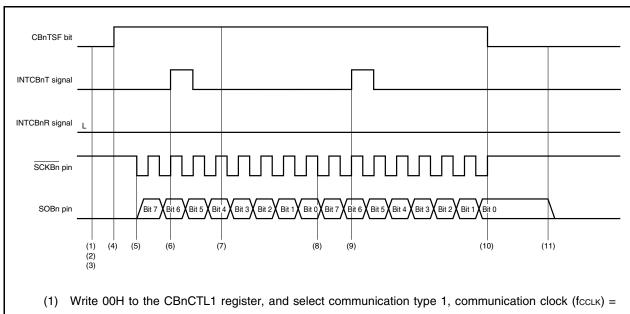

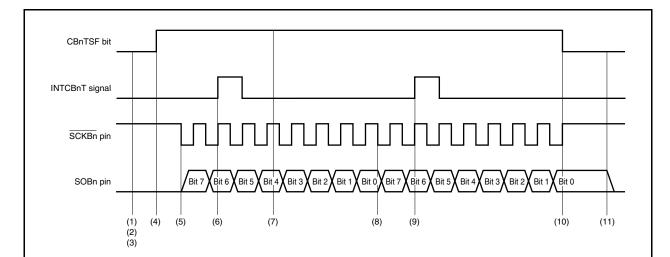

|      |       | 18.6.7 Continuous transfer mode (master mode, transmission mode)                          | 646 |

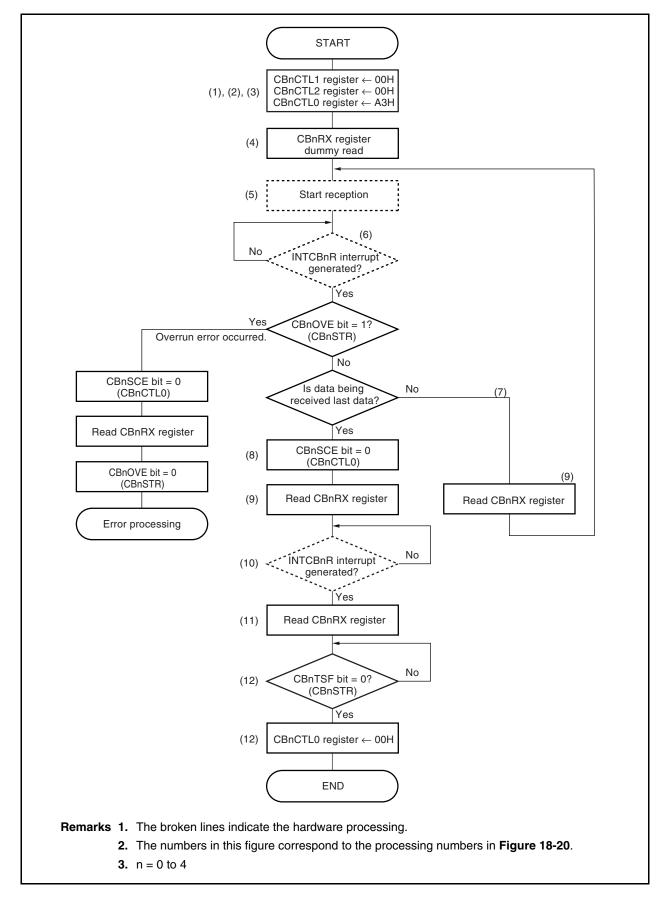

|      |       | 18.6.8 Continuous transfer mode (master mode, reception mode)                             | 648 |

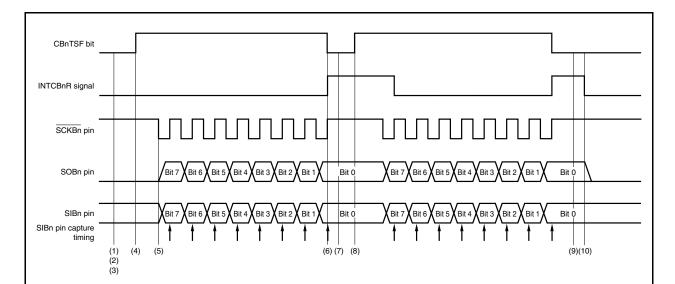

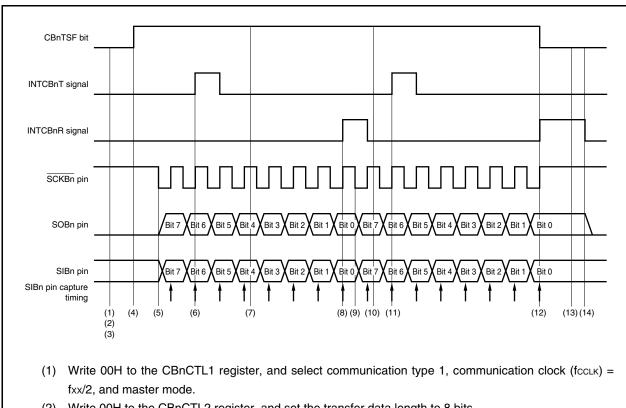

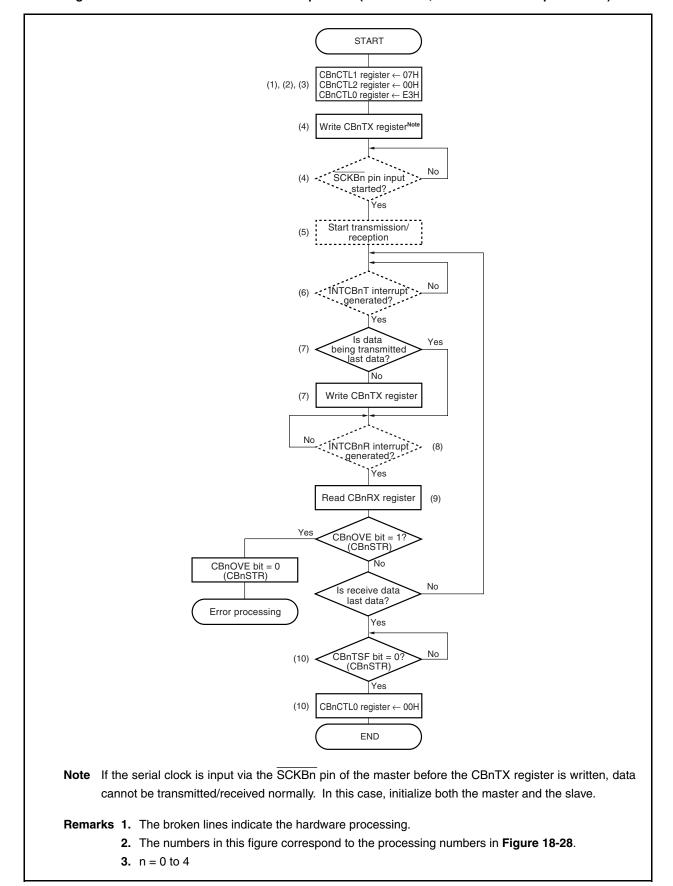

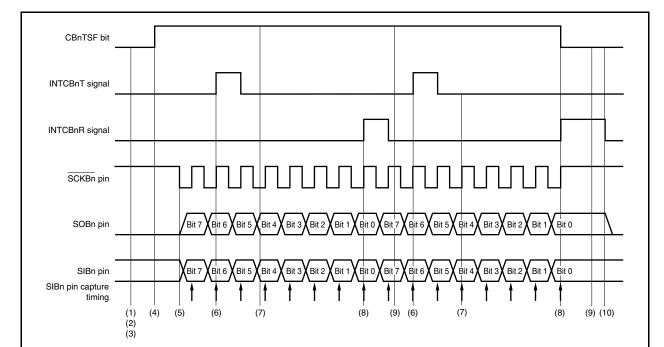

|      |       | 18.6.9 Continuous transfer mode (master mode, transmission/reception mode)                | 651 |

|      |       | 18.6.10 Continuous transfer mode (slave mode, transmission mode)                          | 655 |

|      |       | 18.6.11 Continuous transfer mode (slave mode, reception mode)                             | 657 |

|      |       | 18.6.12 Continuous transfer mode (slave mode, transmission/reception mode)                | 660 |

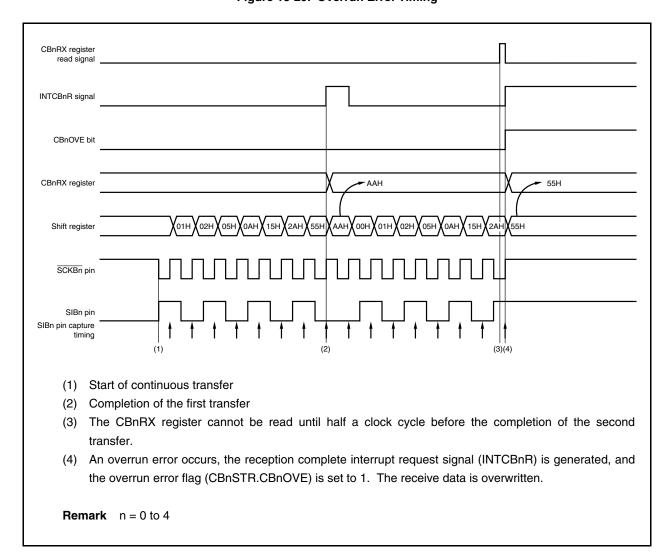

|      |       | 18.6.13 Reception errors                                                                  | 663 |

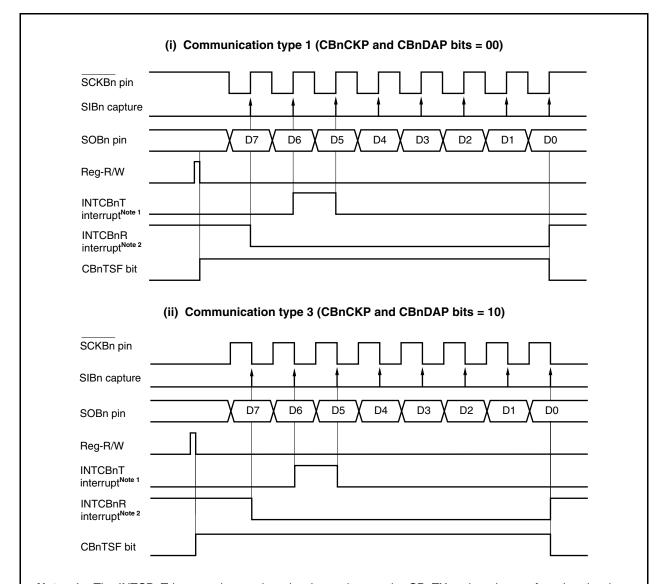

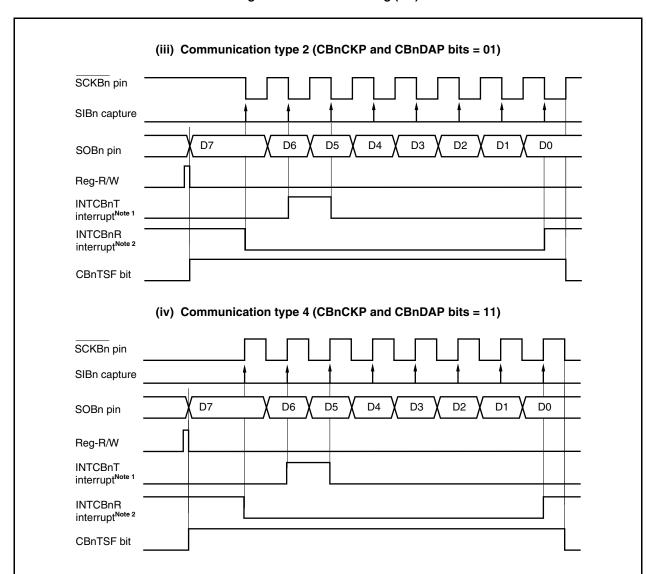

|      |       | 18.6.14 Clock timing                                                                      | 664 |

| 1    | 18.7  | Output Pins                                                                               | 666 |

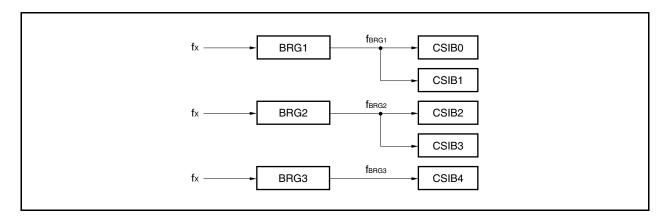

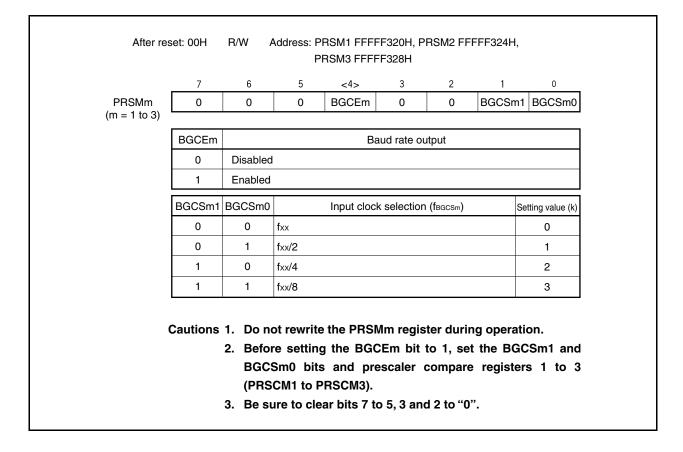

| 1    | 18.8  | Baud Rate Generator                                                                       | 667 |

|      |       | 18.8.1 Baud rate generation                                                               | 668 |

| 1    | 18.9  | Cautions                                                                                  | 669 |

| СНАЕ | TFF   | R 19 I <sup>2</sup> C BUS                                                                 | 670 |

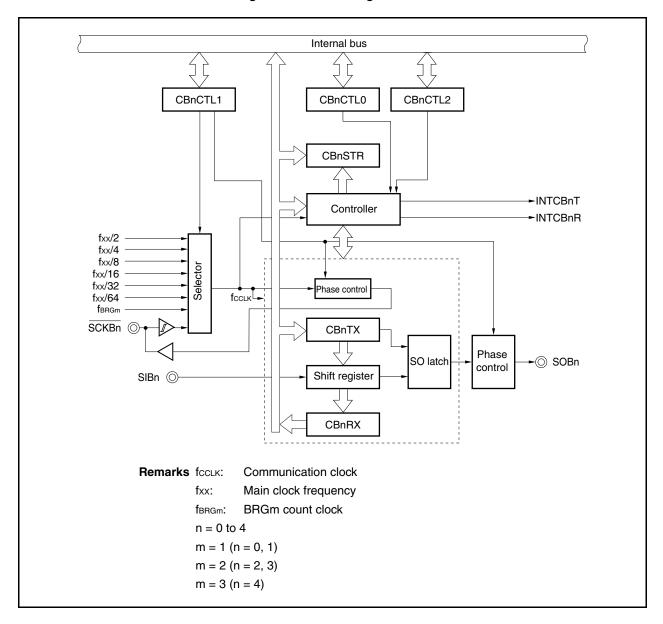

|      |       | Mode Switching of I <sup>2</sup> C Bus and Other Serial Interfaces                        |     |

|      |       | 19.1.1 UARTA2 and I <sup>2</sup> C00 mode switching                                       | 670 |

|      |       | 19.1.2 CSIB0 and I <sup>2</sup> C01 mode switching                                        | 671 |

|      |       | 19.1.3 UARTA1 and I <sup>2</sup> C02 mode switching                                       |     |

| 1    | 19.2  | Features                                                                                  | 673 |

|      |       | Configuration                                                                             |     |

| 1    | 19.4  | Registers                                                                                 | 678 |

| 1    | 19.5  | I <sup>2</sup> C Bus Mode Functions                                                       | 694 |

|      |       | 19.5.1 Pin configuration                                                                  | 694 |

| 1    | 19.6  | I <sup>2</sup> C Bus Definitions and Control Methods                                      | 695 |

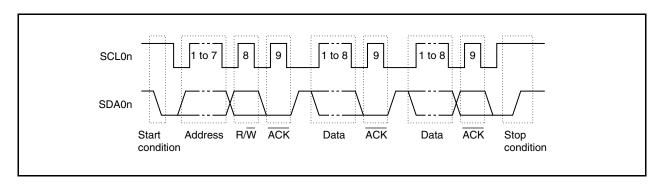

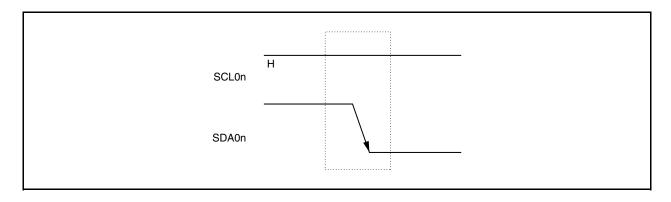

|      |       | 19.6.1 Start condition                                                                    | 695 |

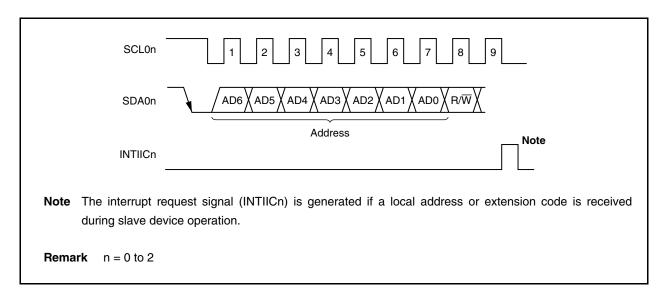

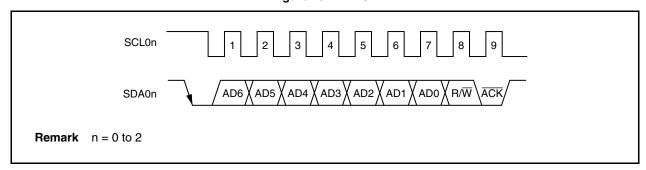

|      |       | 19.6.2 Addresses                                                                          | 696 |

|      |       | 19.6.3 Transfer direction specification                                                   | 697 |

|      |       | 19.6.4 ACK                                                                                | 698 |

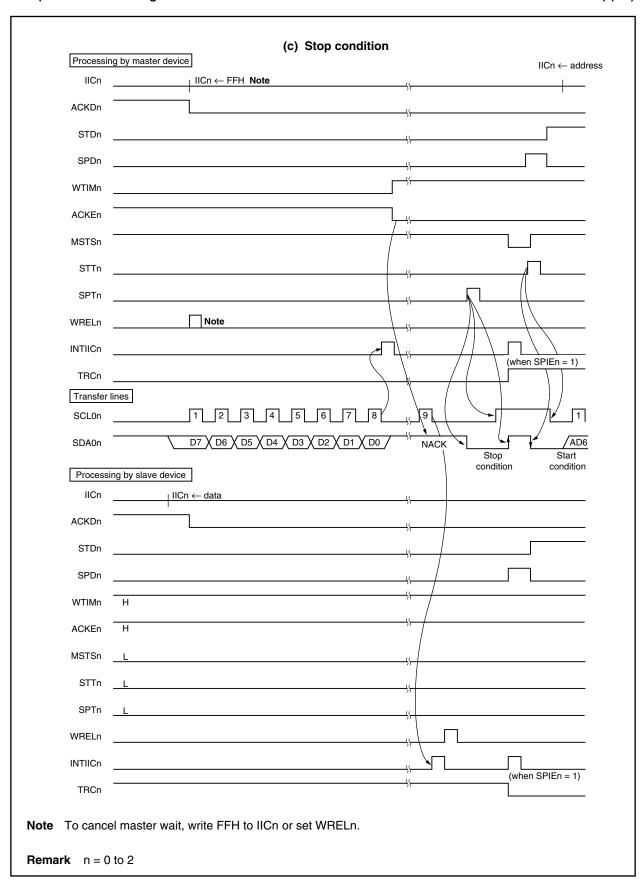

|      |       | 19.6.5 Stop condition                                                                     | 699 |

|      |       | 19.6.6 Wait state                                                                         | 700 |

|      |       | 19.6.7 Wait state cancellation method                                                     | 702 |

| 1    | 19.7  | I <sup>2</sup> C Interrupt Request Signals (INTIICn)                                      | 703 |

|      |       | 19.7.1 Master device operation                                                            | 703 |

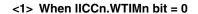

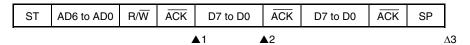

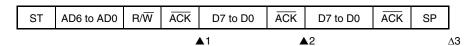

|      |       | 19.7.2 Slave device operation (when receiving slave address data (address match))         | 706 |

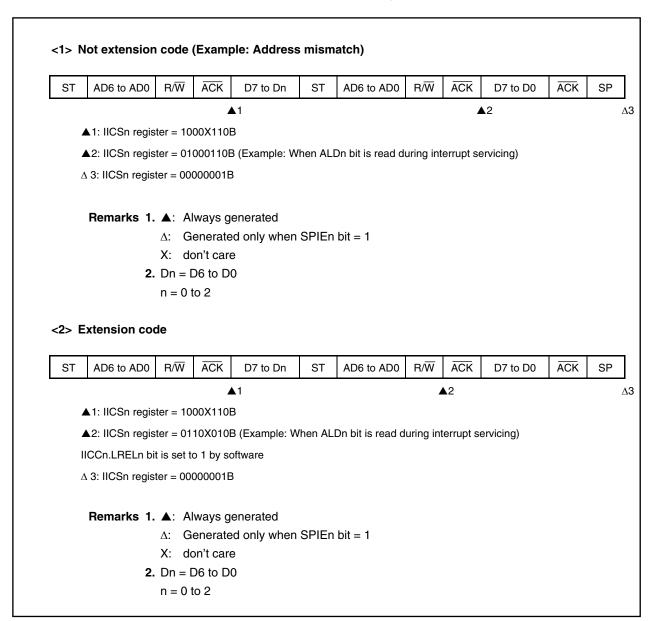

|      |       | 19.7.3 Slave device operation (when receiving extension code)                             | 710 |

|      |       | 19.7.4 Operation without communication                                                    | 714 |

|      |       | 19.7.5 Operation when arbitration loss occurs (operation as slave after arbitration loss) | 714 |

|      |       | 19.7.6 Operation when arbitration loss occurs (no communication after arbitration loss)   | 716 |

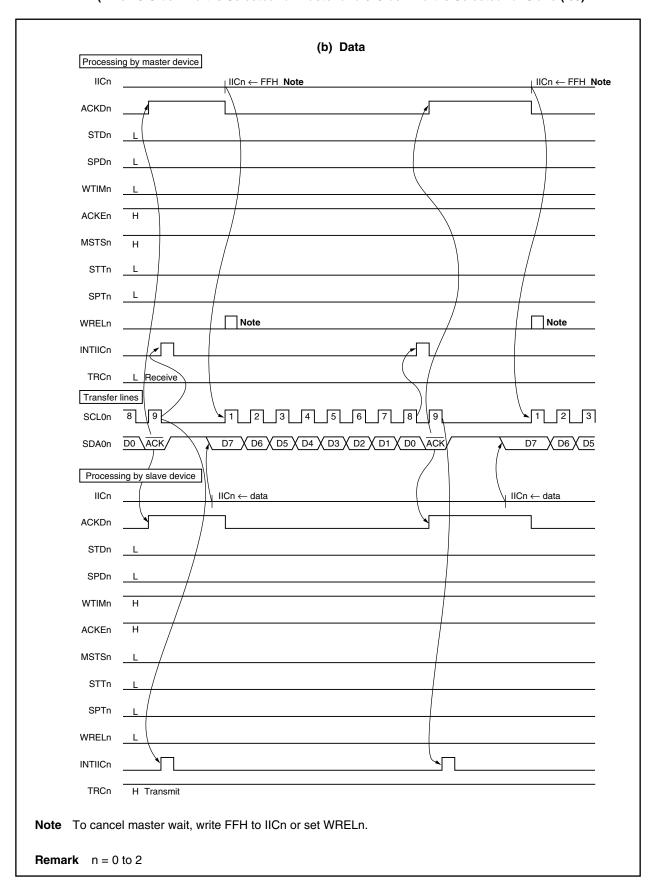

| 1    | 19.8  | Interrupt Request Signal (INTIICn) Generation Timing and Wait Control                     | 723 |

| 1    | 19.9  | Address Match Detection Method                                                            | 725 |

| 1    | 19.10 | Error Detection                                                                           | 725 |

|          | 19.11 | Extension Code                                                                      | 725 |

|----------|-------|-------------------------------------------------------------------------------------|-----|

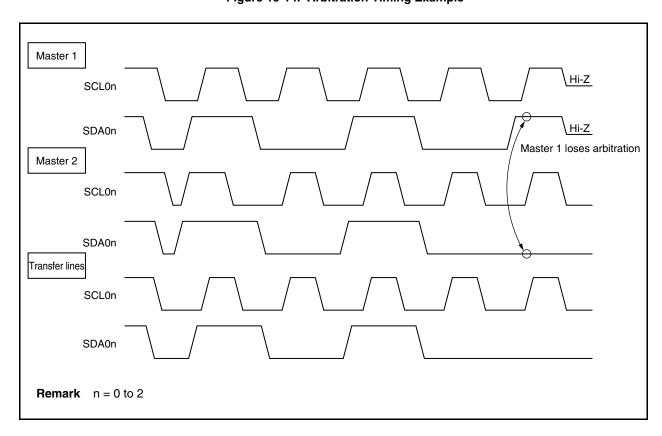

|          | 19.12 | Arbitration                                                                         | 726 |

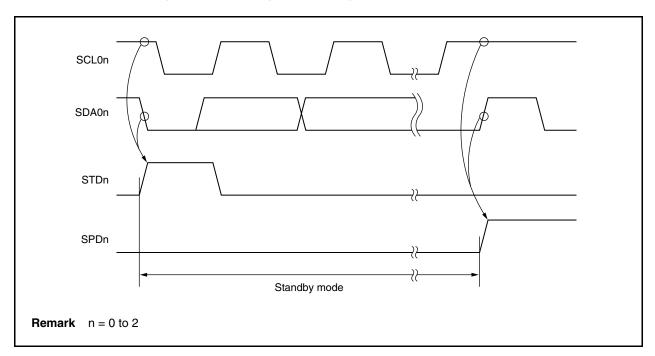

|          | 19.13 | Wakeup Function                                                                     | 727 |

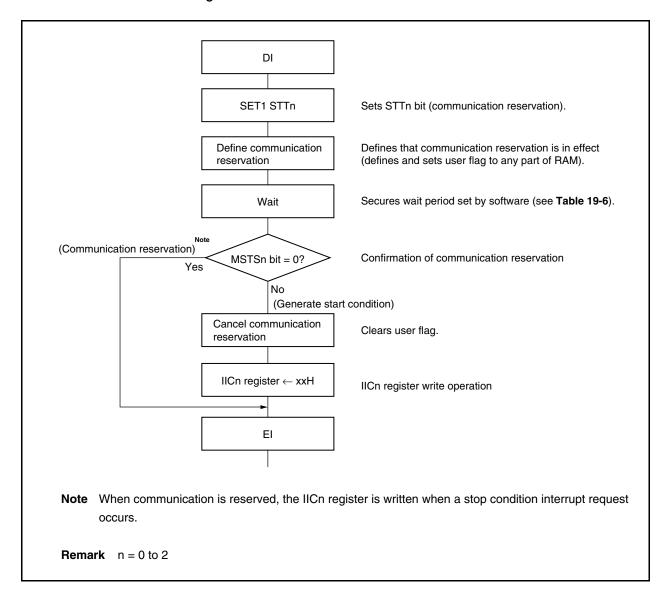

|          | 19.14 | Communication Reservation                                                           | 728 |

|          |       | 19.14.1 When communication reservation function is enabled (IICFn.IICRSVn bit = 0)  | 728 |

|          |       | 19.14.2 When communication reservation function is disabled (IICFn.IICRSVn bit = 1) | 732 |

|          | 19.15 | Cautions                                                                            | 733 |

|          | 19.16 | Communication Operations                                                            | 734 |

|          |       | 19.16.1 Master operation in single master system                                    | 735 |

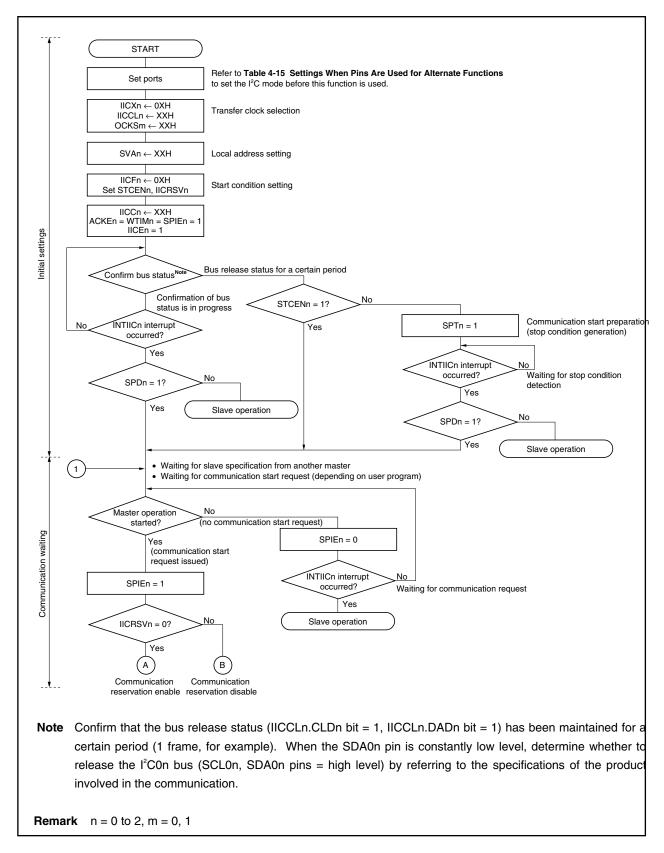

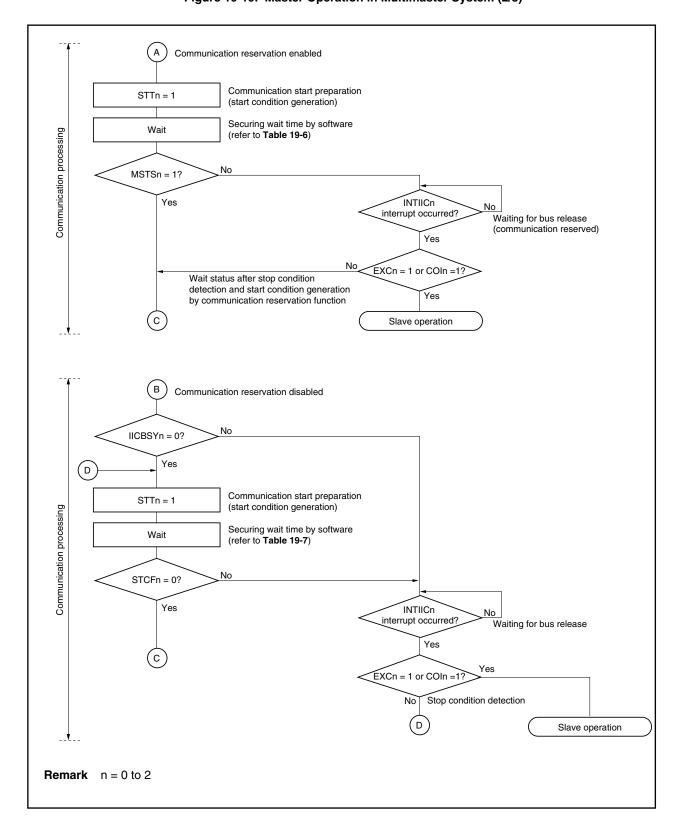

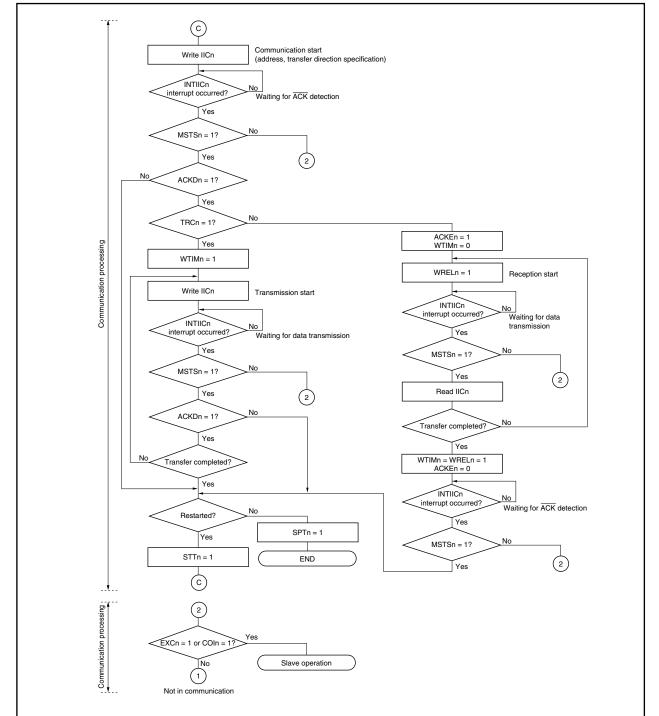

|          |       | 19.16.2 Master operation in multimaster system                                      | 736 |

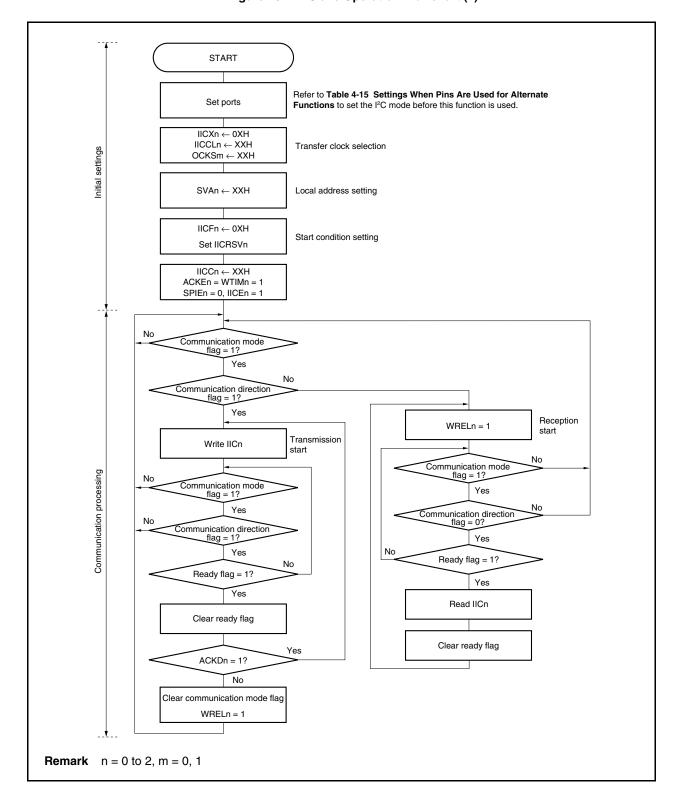

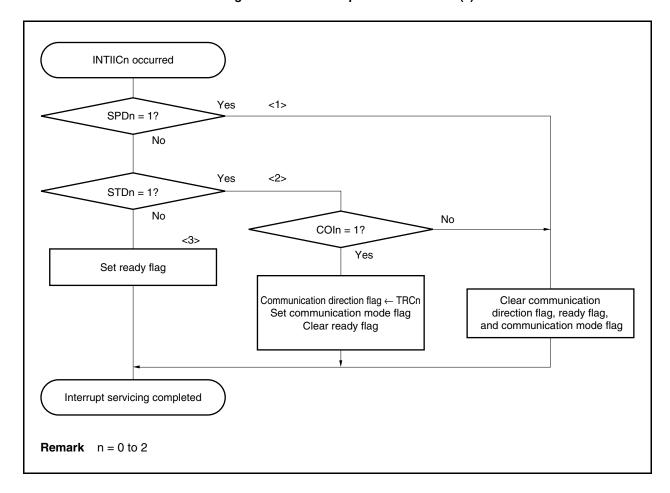

|          |       | 19.16.3 Slave operation                                                             | 739 |

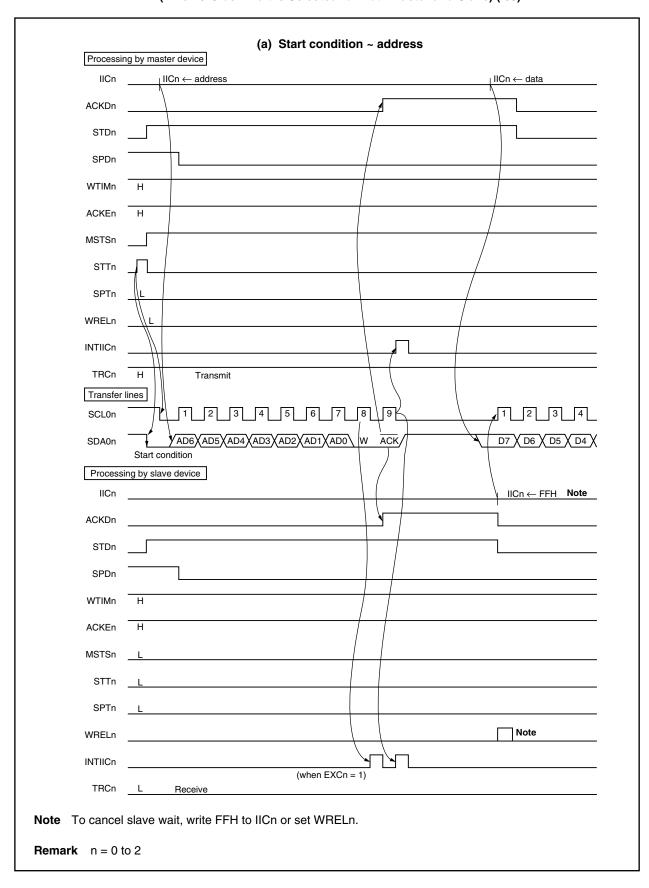

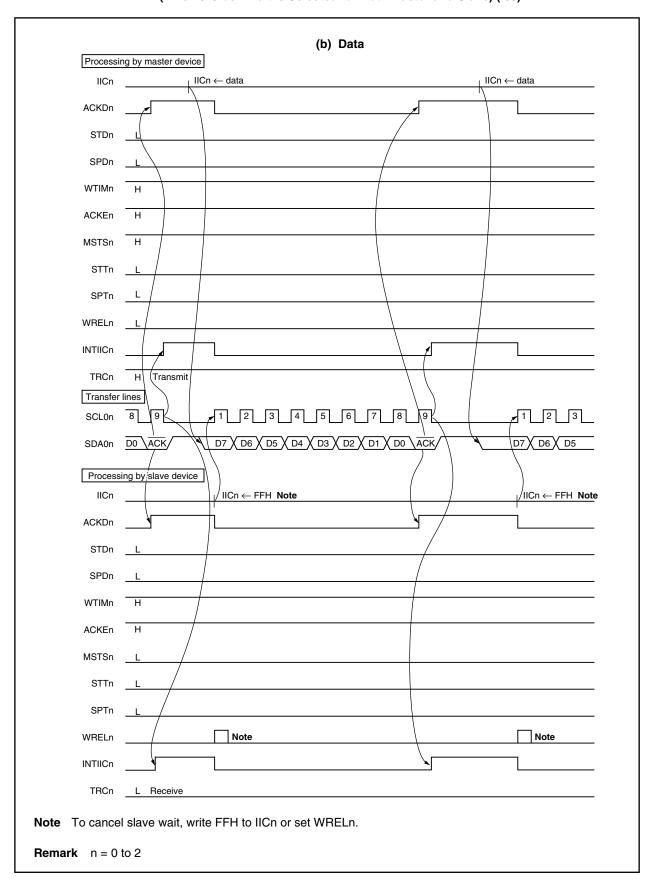

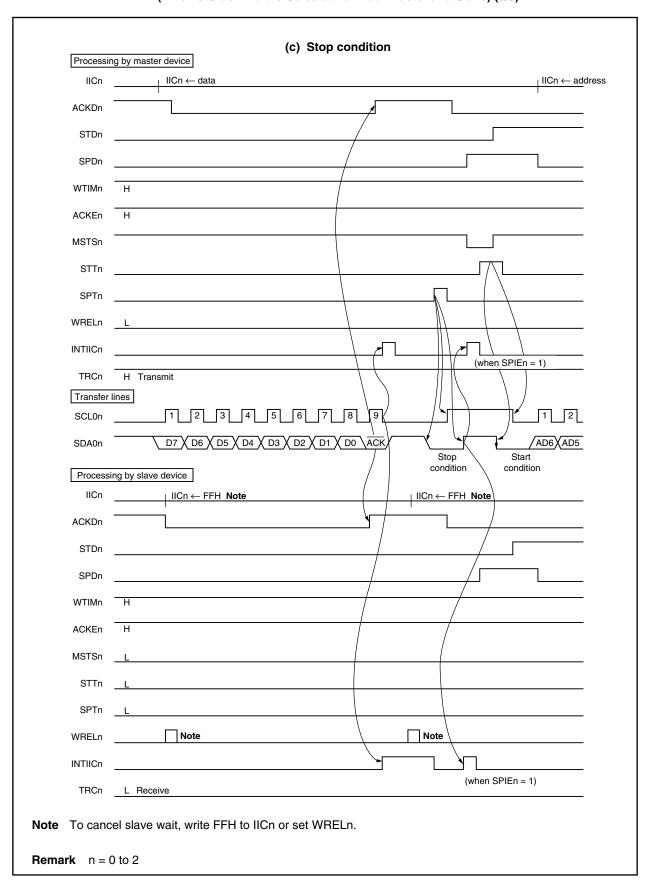

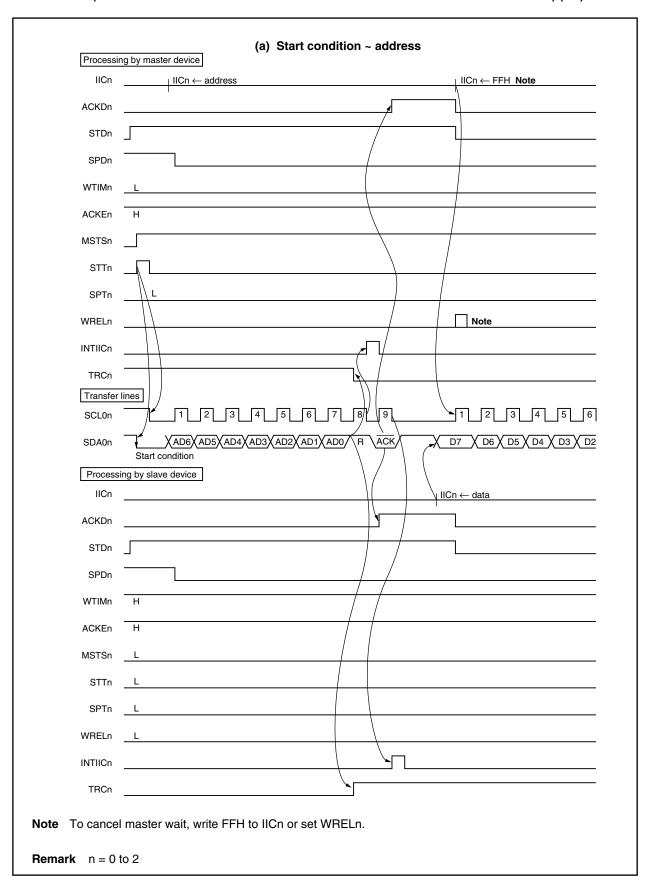

|          | 19.17 | Timing of Data Communication                                                        | 742 |

| <b>~</b> | DTEE  | A CO. LIGH FUNCTION CONTROLLED (LIGHE)                                              | 740 |

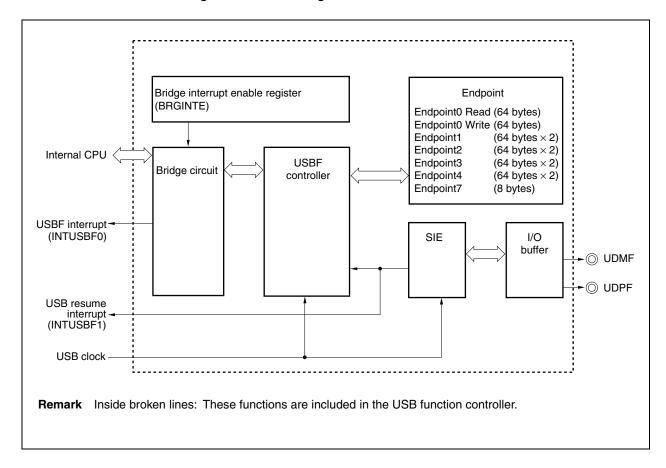

| СНА      |       | 20 USB FUNCTION CONTROLLER (USBF)                                                   |     |

|          |       | Overview                                                                            |     |

|          | 20.2  | Configuration                                                                       |     |

|          |       | 20.2.1 Block diagram                                                                |     |

|          | 00.0  | 20.2.2 USB memory map                                                               |     |

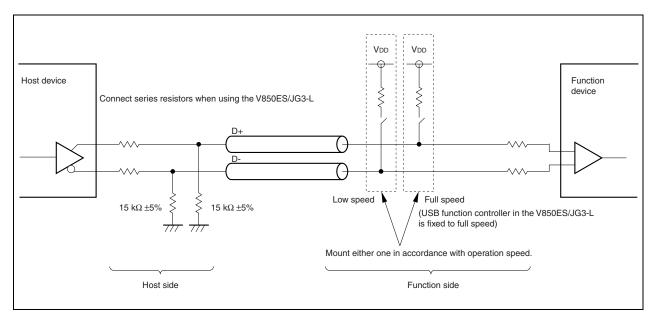

|          | 20.3  | External Circuit Configuration                                                      |     |

|          |       | 20.3.1 Outline                                                                      |     |

|          | 20.4  | 20.3.2 Connection configuration                                                     |     |

|          |       | Requests                                                                            |     |

|          | 20.5  | 20.5.1 Automatic requests                                                           |     |

|          |       | 20.5.2 Other requests                                                               |     |

|          | 20.6  | ·                                                                                   |     |

|          | 20.0  | Register Configuration                                                              |     |

|          |       | 20.6.1 USB function controller register list                                        |     |

|          |       | 20.6.3 EPC control registers                                                        |     |

|          |       | 20.6.4 Data hold registers                                                          |     |

|          |       | 20.6.5 EPC request data registers                                                   |     |

|          |       | 20.6.6 Bridge register                                                              |     |

|          |       | 20.6.7 DMA register                                                                 |     |

|          |       | 20.6.8 Bulk-in register                                                             |     |

|          |       | 20.6.9 Bulk-out register                                                            |     |

|          |       | 20.6.10 Peripheral control registers                                                |     |

|          | 20.7  | STALL Handshake or No Handshake                                                     |     |

|          | 20.8  | Register Values in Specific Status                                                  | 887 |

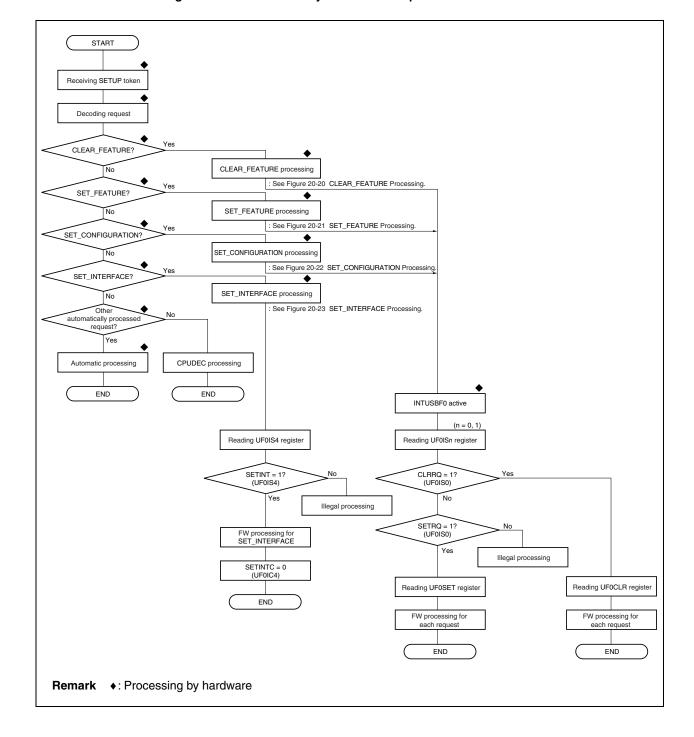

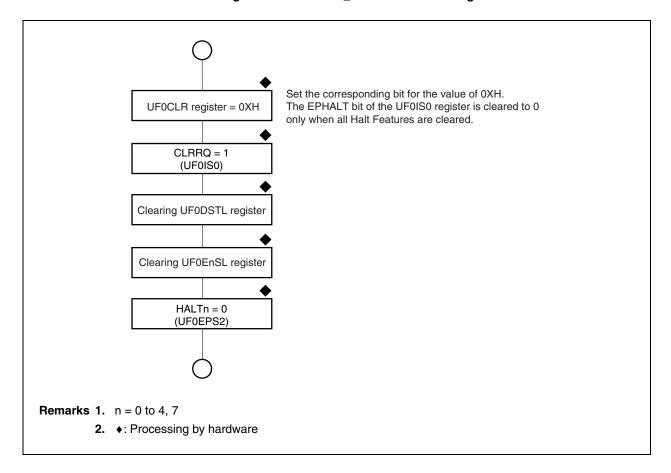

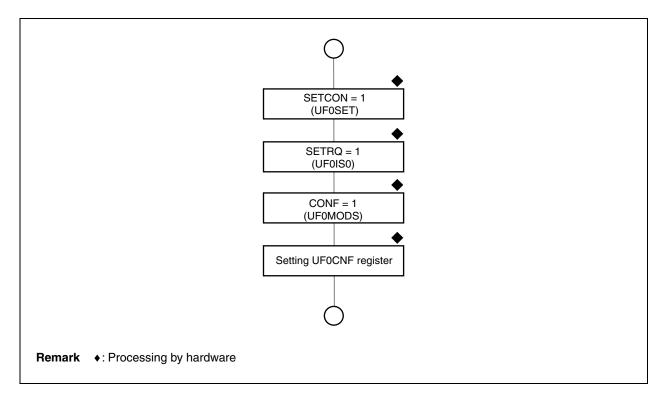

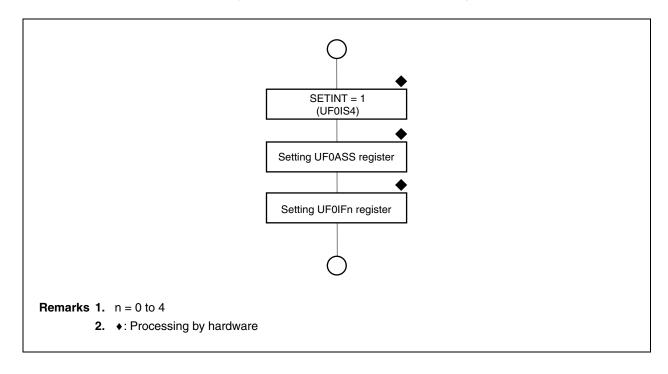

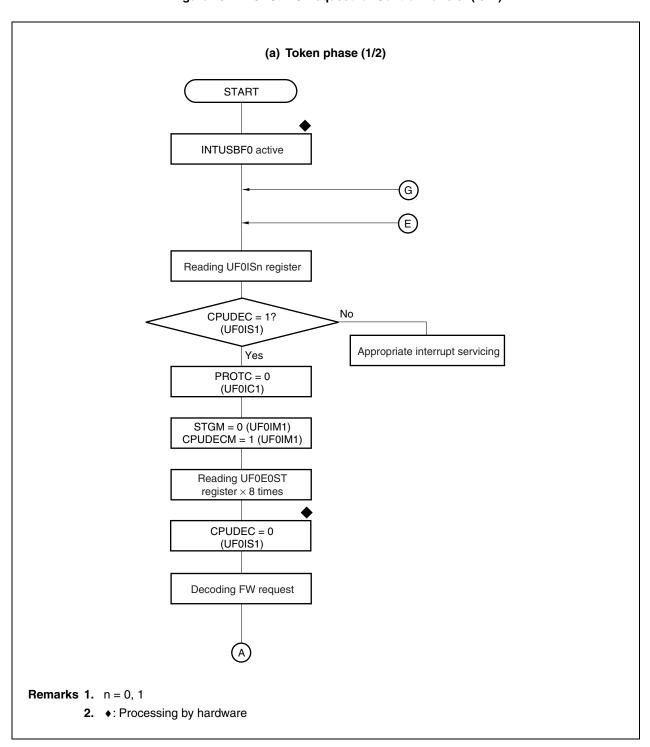

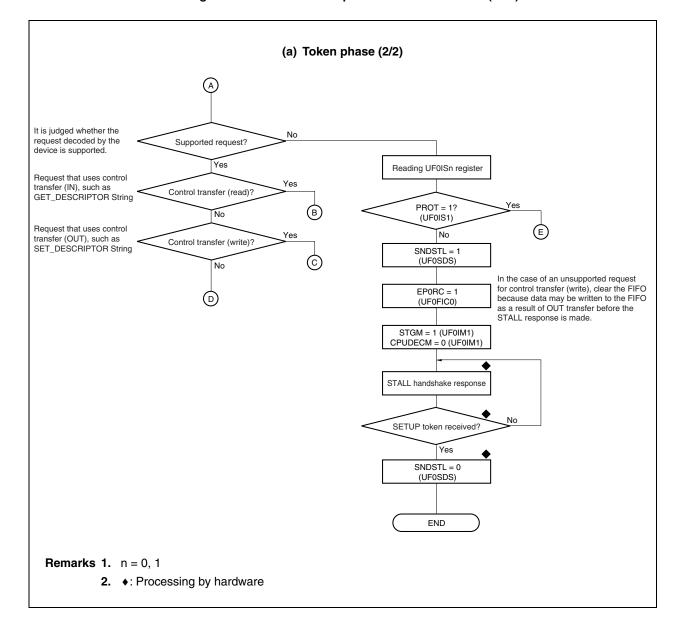

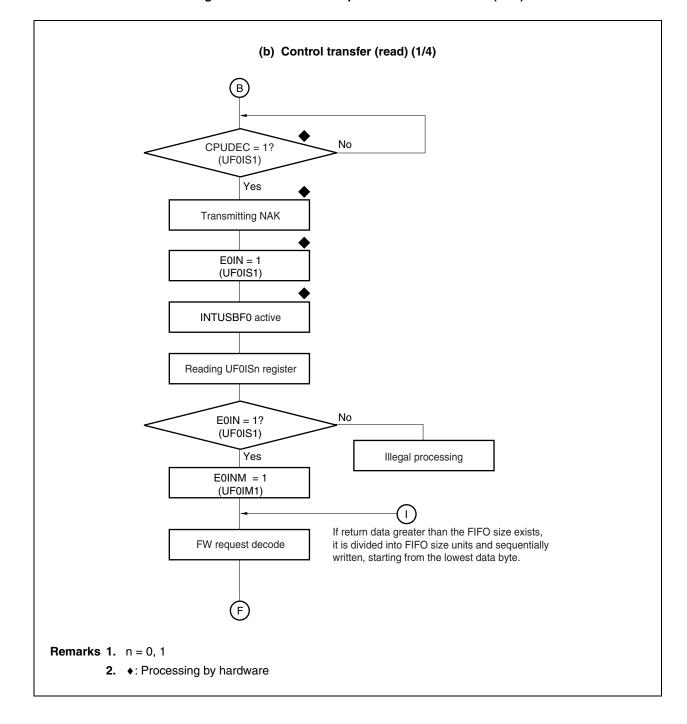

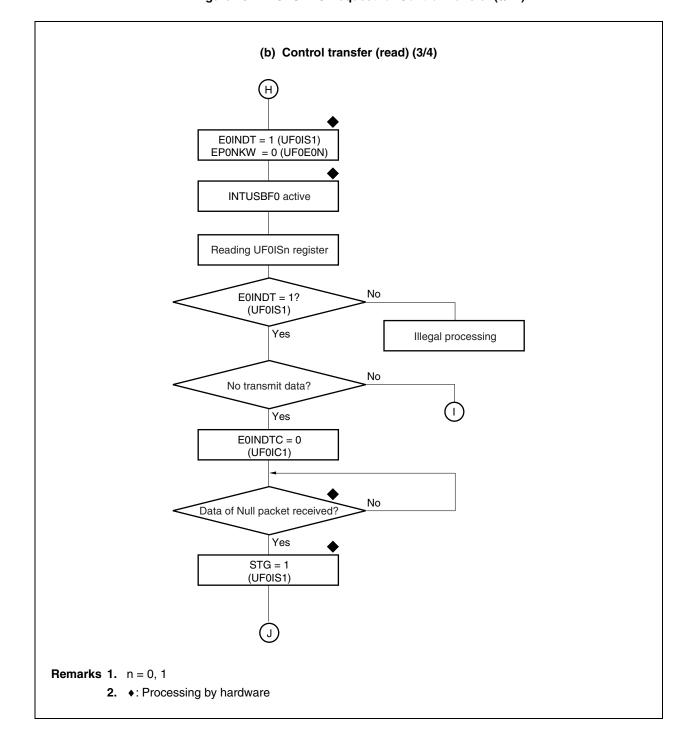

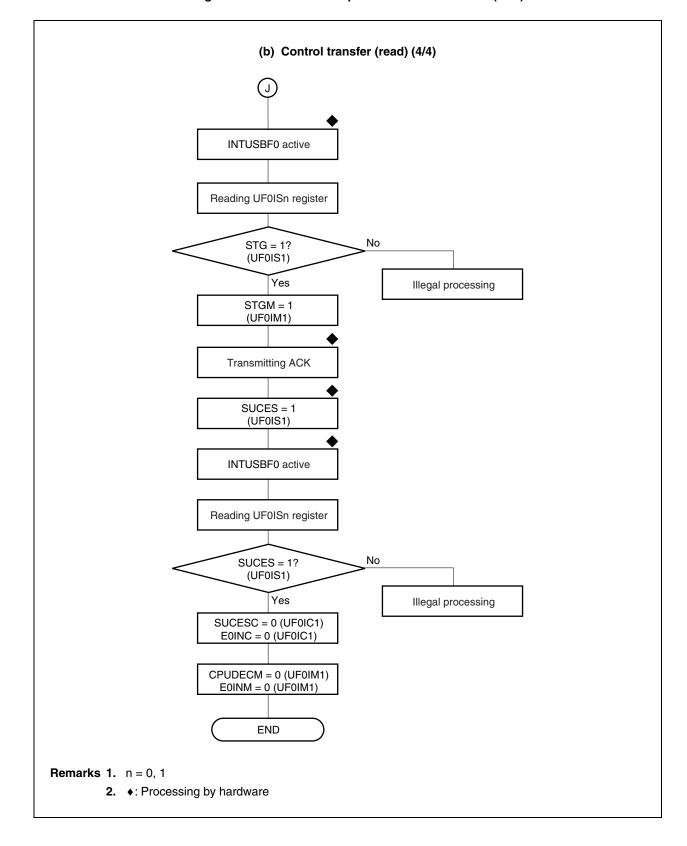

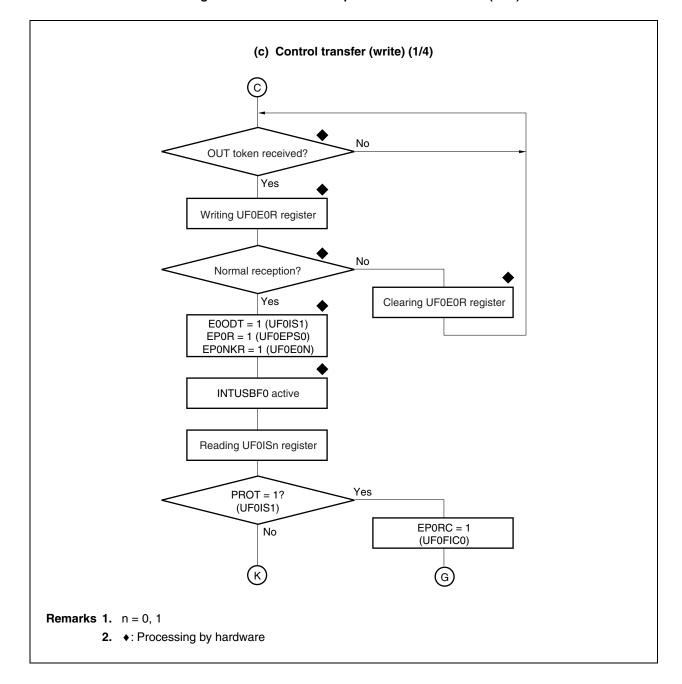

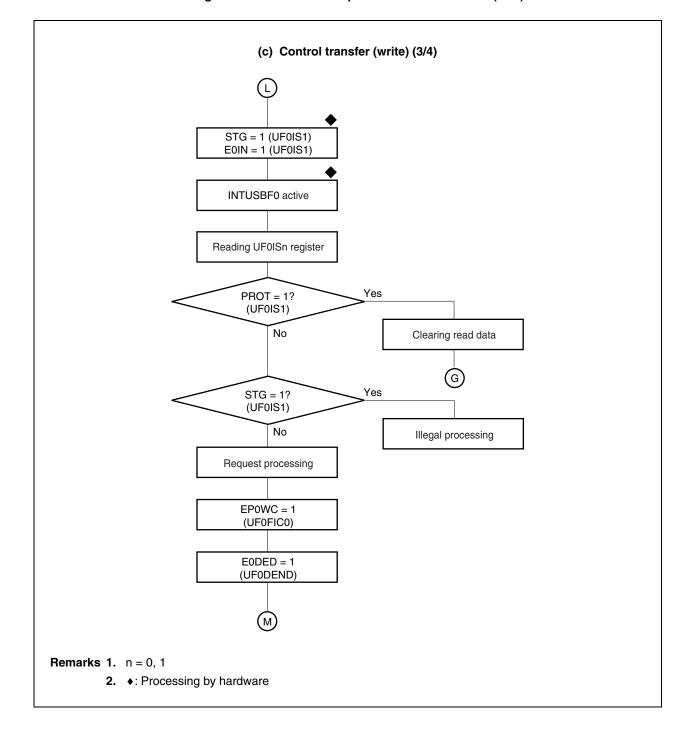

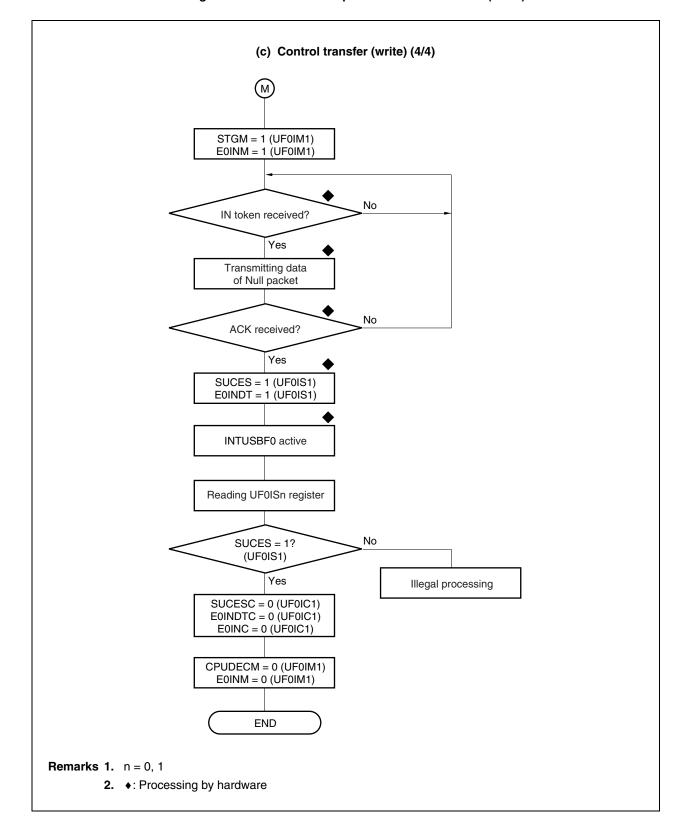

|          | 20.9  | FW Processing                                                                       | 889 |

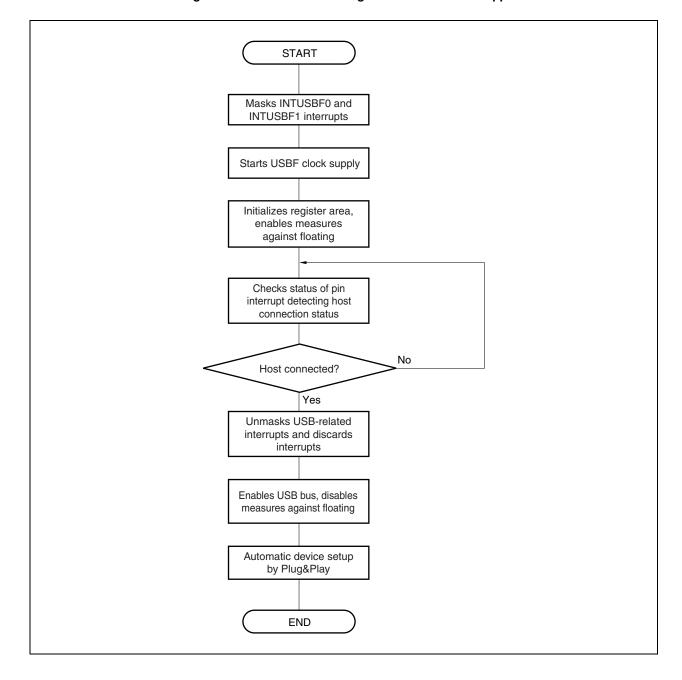

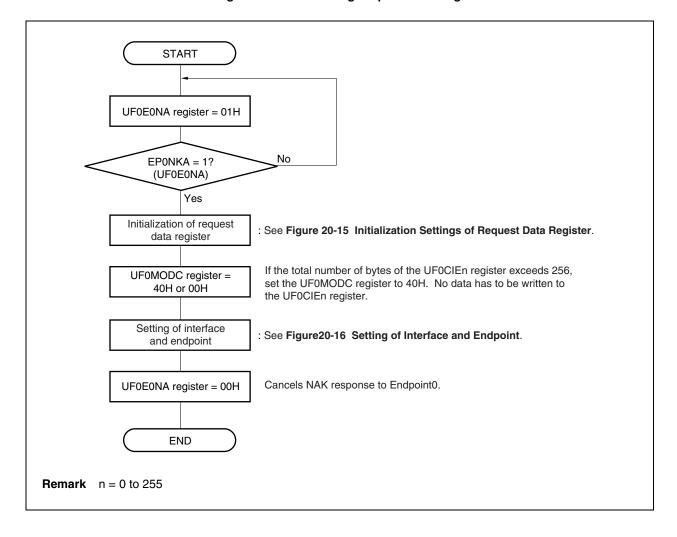

|          |       | 20.9.1 Initialization processing                                                    |     |

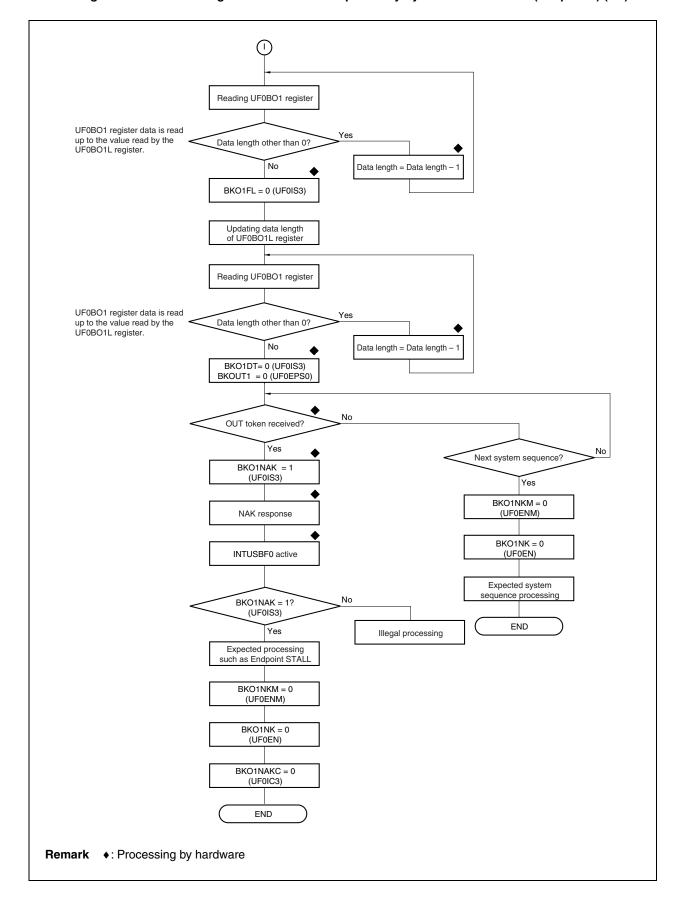

|          |       | 20.9.2 Interrupt servicing                                                          | 894 |

|          |       | 20.9.3 USB main processing                                                          | 895 |

|          |       | 20.9.4 Suspend/Resume processing                                                    | 921 |

|          |       | 20.9.5 Processing after power application                                           | 924 |

|          |       |                                                                                     |     |

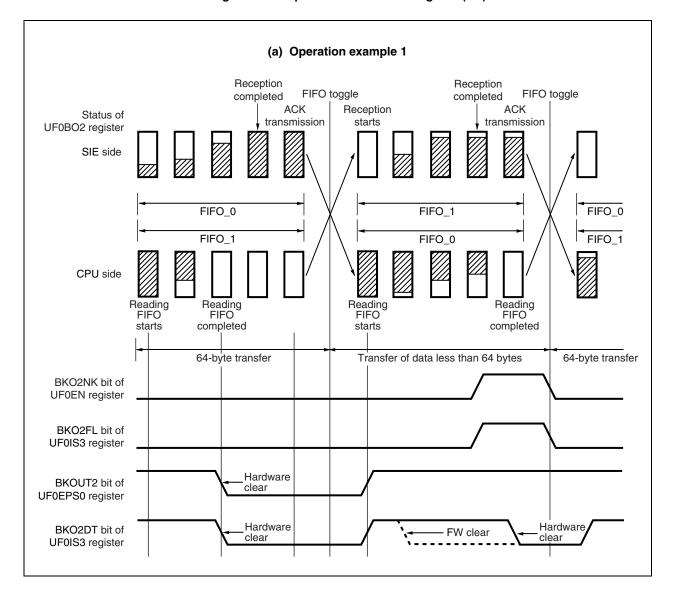

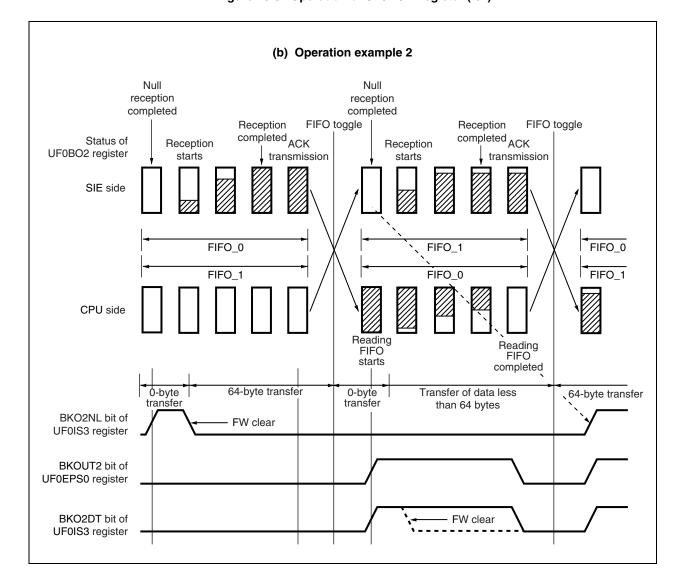

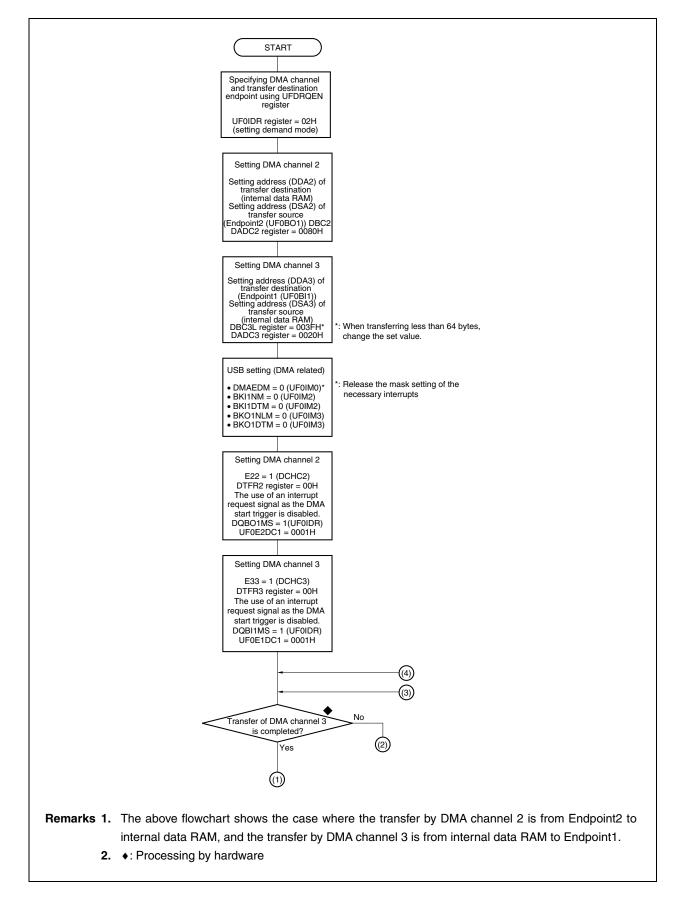

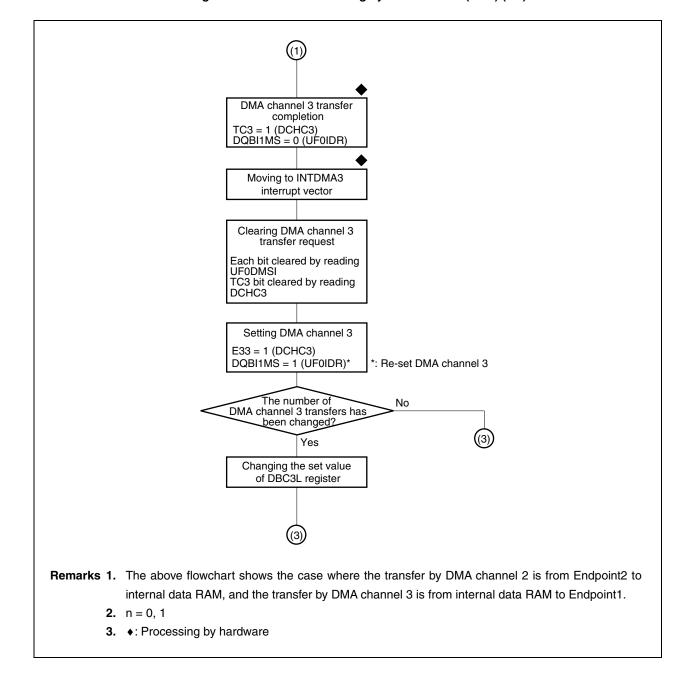

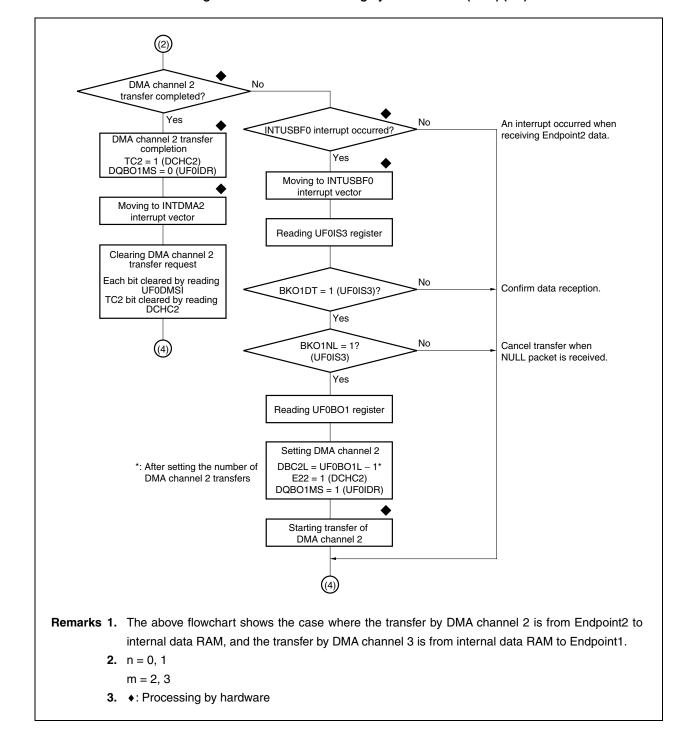

|        | 20.9.6 Receiving data for bulk transfer (OUT) in DMA mode   | 927 |

|--------|-------------------------------------------------------------|-----|

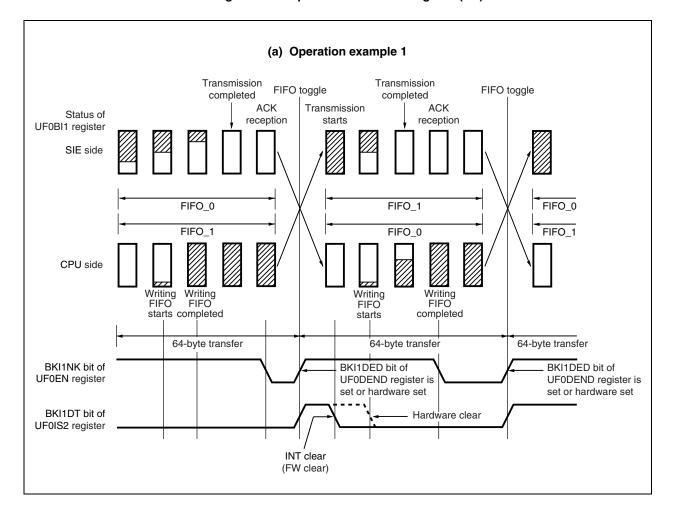

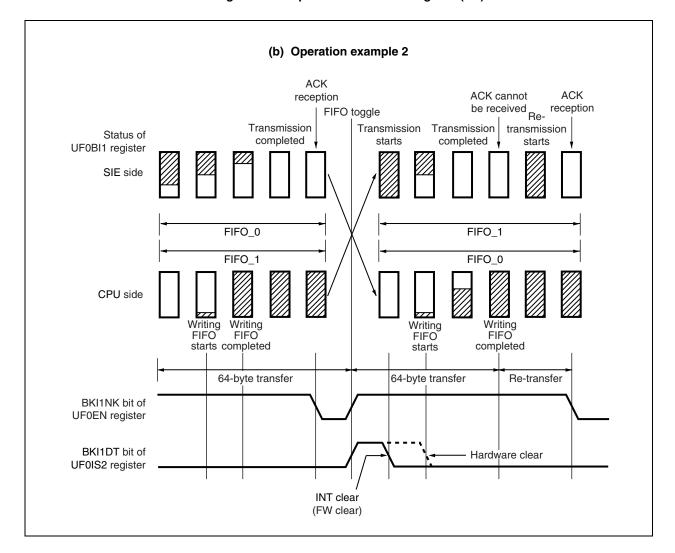

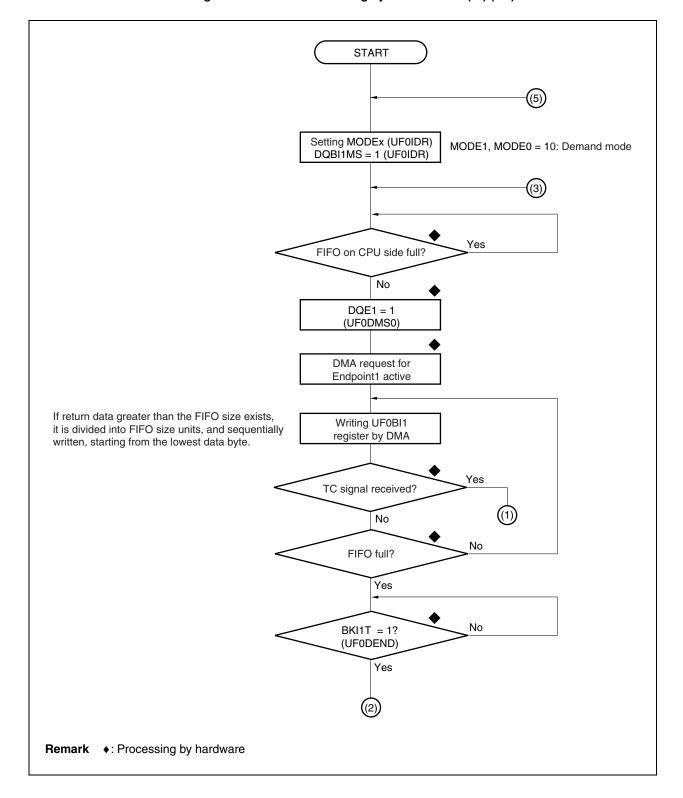

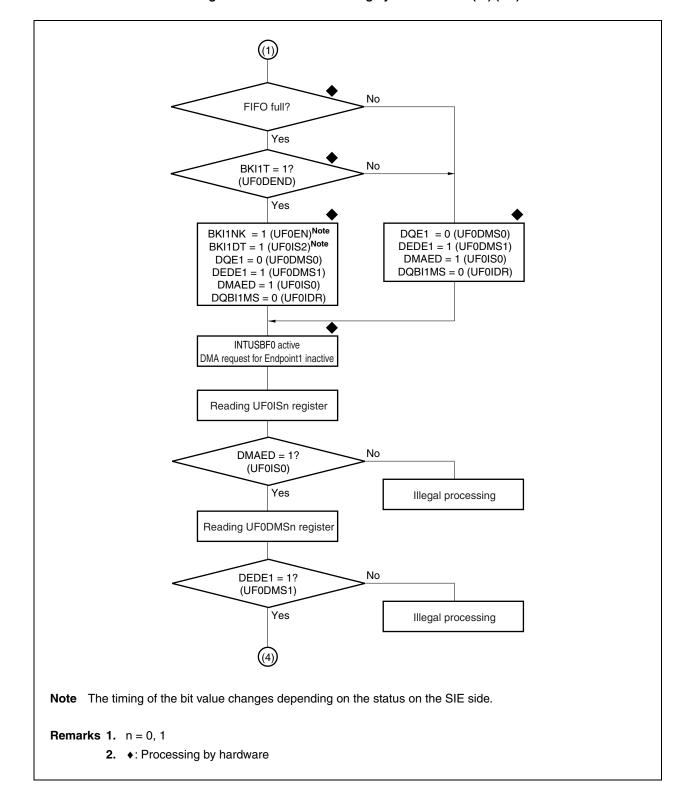

|        | 20.9.7 Transmitting data for bulk transfer (IN) in DMA mode | 932 |

|        |                                                             |     |

|        | R 21 DMA FUNCTION (DMA CONTROLLER)                          |     |

|        | Features                                                    |     |

|        | Configuration                                               |     |

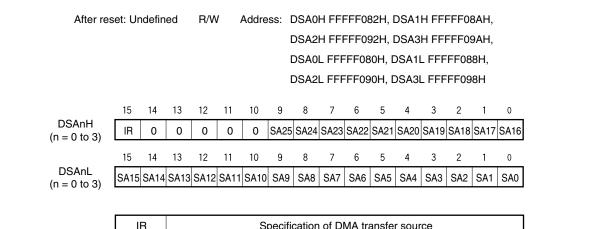

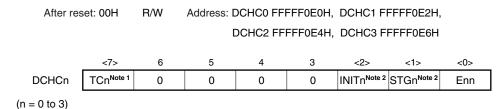

|        | Registers                                                   |     |

|        | Transfer Sources and Destinations                           |     |

|        | Transfer Modes                                              |     |

|        | Transfer Types                                              |     |

|        | DMA Channel Priorities                                      |     |

|        | Time Related to DMA Transfer                                |     |

| _      | DMA Transfer Start Factors                                  |     |

|        | DDMA Abort Factors                                          |     |

|        | 1 End of DMA Transfer                                       |     |

|        | 2 Operation Timing                                          |     |

| 21.13  | 3 Cautions                                                  | 958 |

| CHADTE | R 22 INTERRUPT SERVICING/EXCEPTION PROCESSING FUNCTION      | 063 |

| _      | Features                                                    |     |

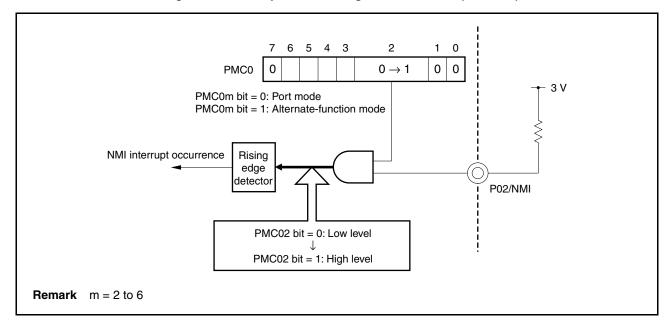

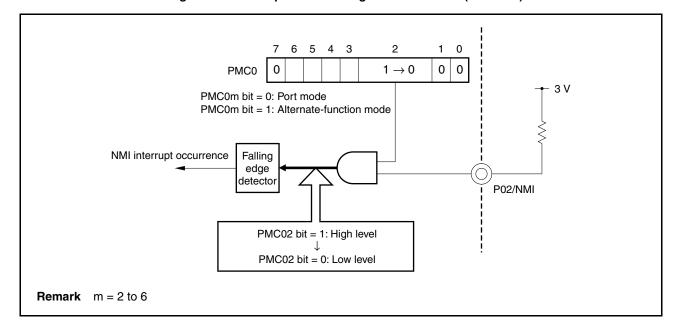

|        | Non-Maskable Interrupts                                     |     |

| 22.2   | 22.2.1 Operation                                            |     |

|        | 22.2.2 Restoration                                          |     |

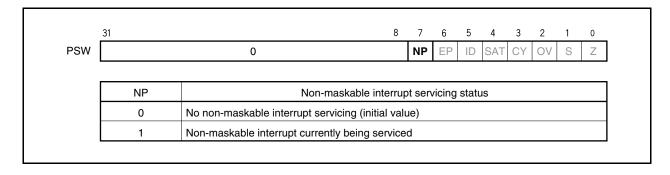

|        | 22.2.3 NP flag                                              |     |

| 22.3   | Maskable Interrupts                                         |     |

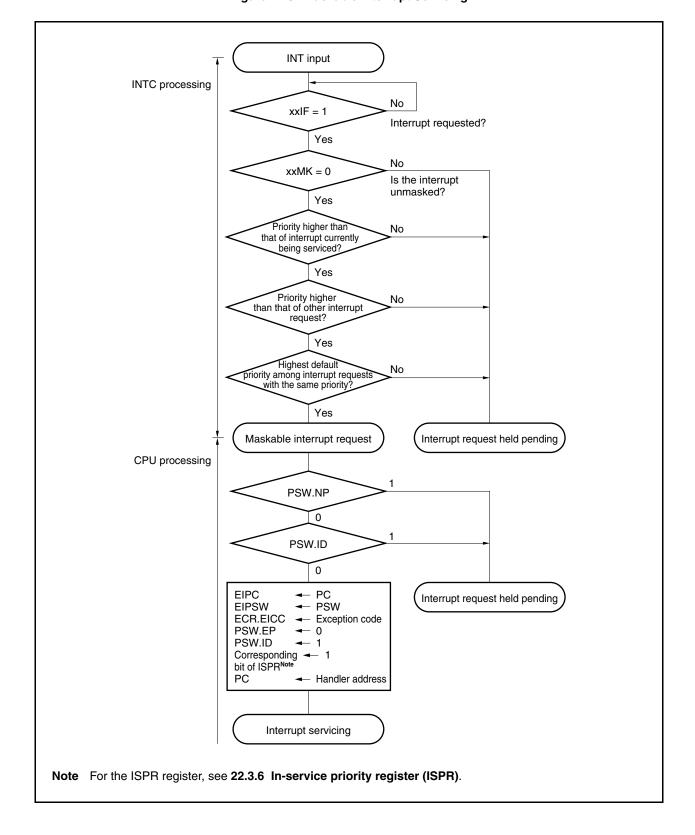

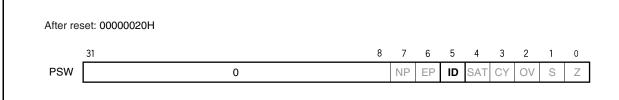

| 22.5   | 22.3.1 Operation                                            |     |

|        | 22.3.2 Restoration                                          |     |

|        | 22.3.3 Priorities of maskable interrupts                    |     |

|        | 22.3.4 Interrupt control register (xxICn)                   |     |

|        |                                                             |     |

|        | 22.3.5 Interrupt mask registers 0 to 3 (IMR0 to IMR3)       |     |

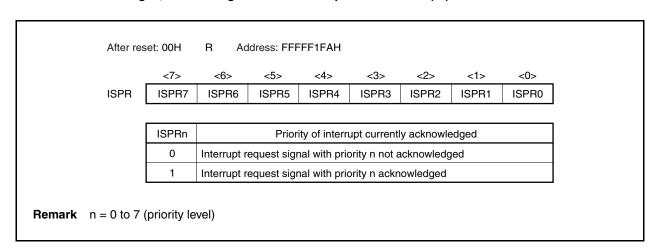

|        | 22.3.6 In-service priority register (ISPR)                  |     |

|        | •                                                           |     |

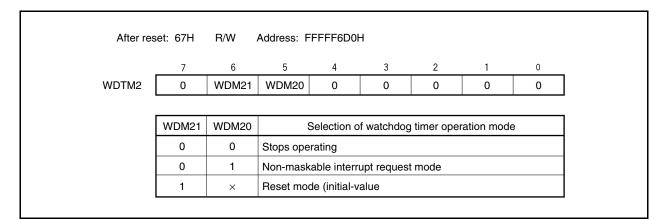

| 22.4   | 22.3.8 Watchdog timer mode register 2 (WDTM2)               |     |

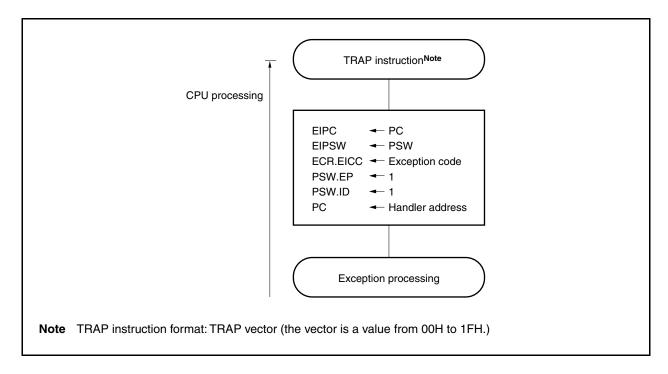

| 22.4   | 22.4.1 Operation                                            |     |

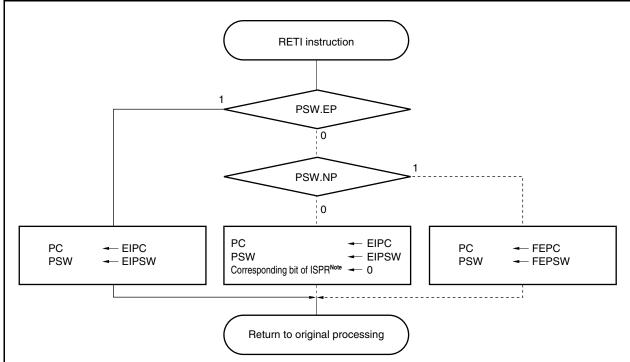

|        | 22.4.2 Restoration                                          |     |

|        |                                                             |     |

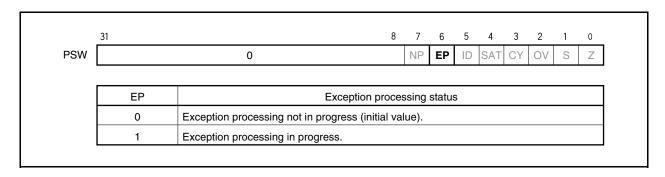

| 22.5   | 22.4.3 EP flag  Exception Trap                              |     |

| 22.3   | 22.5.1 Illegal opcode                                       |     |

|        | •                                                           |     |

| 22 E   | 22.5.2 Debug trap  Multiple Interrupt Servicing Control     |     |

|        | External Interrupt Request Input Pins (NMI, INTP0 to INTP7) |     |

| 22.1   |                                                             |     |

|        | 22.7.1 Noise elimination                                    |     |

|        | 22.7.2 Edge detection                                       | 993 |

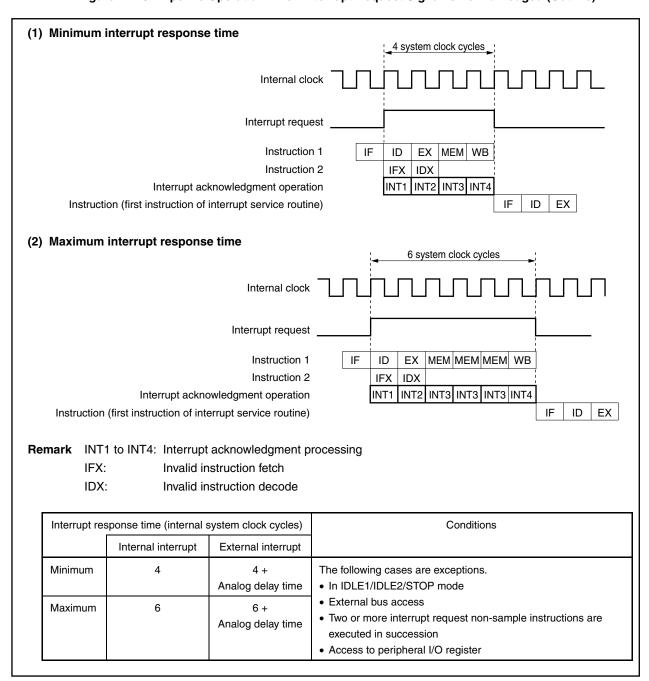

| 22    | 2.8             | Interrupt Response Time of CPU                                          | 999  |

|-------|-----------------|-------------------------------------------------------------------------|------|

| 22    | 2.9             | Periods in Which Interrupts Are Not Acknowledged by CPU                 | 1000 |

| 22    | 2.10            | Cautions                                                                | 1000 |

|       |                 | 22.10.1 Restored PC                                                     | 1000 |

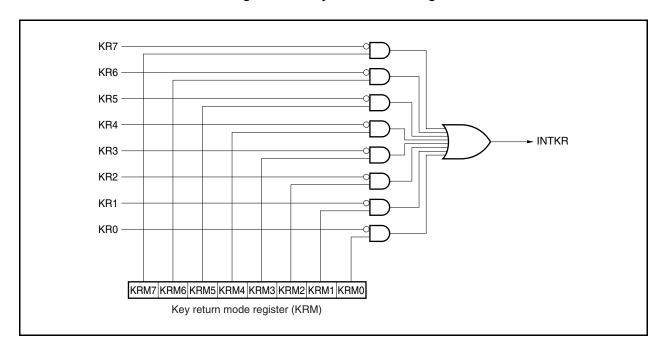

| CHVD  | TED             | 23 KEY INTERRUPT FUNCTION                                               | 1001 |

|       |                 | Function                                                                |      |

|       |                 | Pin Functions                                                           |      |

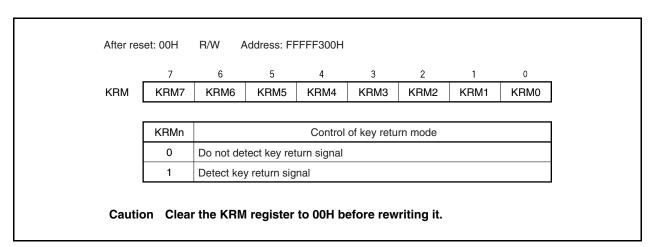

|       | _               | Registers                                                               |      |

|       |                 | Cautions                                                                |      |

| 20    | J. <del>T</del> | Odutions                                                                |      |

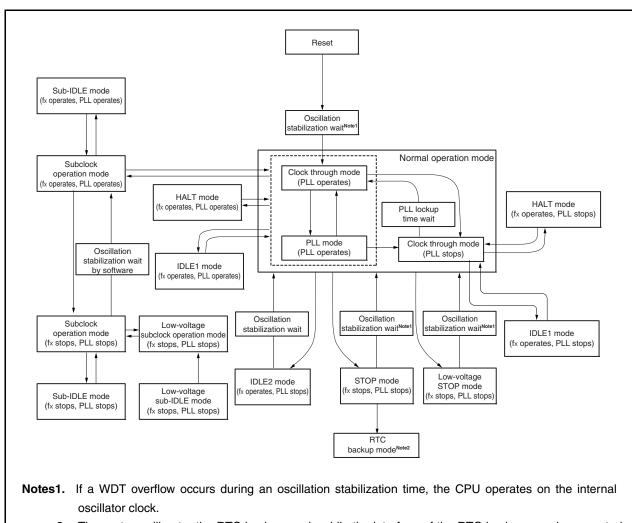

| CHAP  | TER             | 24 STANDBY FUNCTION                                                     | 1004 |

| 24    | 4.1             | Overview                                                                | 1004 |

| 24    | 4.2             | Registers                                                               | 1006 |

| 24    | 4.3             | HALT Mode                                                               | 1011 |

|       |                 | 24.3.1 Setting and operation status                                     | 1011 |

|       |                 | 24.3.2 Releasing HALT mode                                              | 1011 |

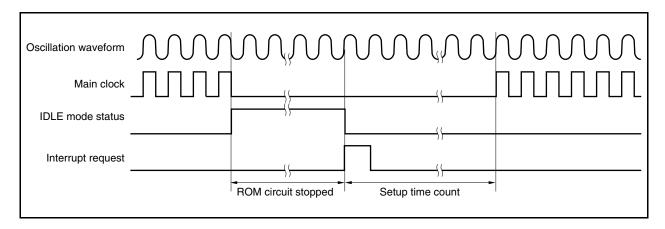

| 24    | 4.4             | IDLE1 Mode                                                              | 1013 |

|       |                 | 24.4.1 Setting and operation status                                     | 1013 |

|       |                 | 24.4.2 Releasing IDLE1 mode                                             | 1014 |

| 24    | 4.5             | IDLE2 Mode                                                              | 1016 |

|       |                 | 24.5.1 Setting and operation status                                     | 1016 |

|       |                 | 24.5.2 Releasing IDLE2 mode                                             | 1017 |

|       |                 | 24.5.3 Securing setup time when releasing IDLE2 mode                    | 1019 |

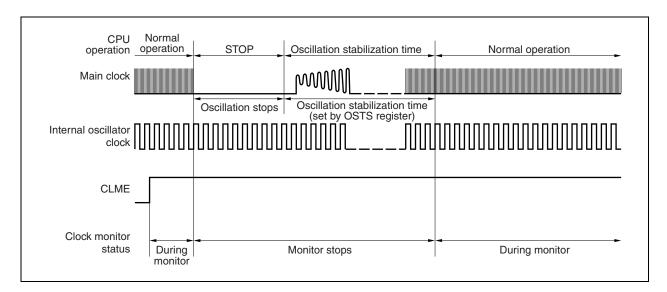

| 24    | 4.6             | STOP Mode/Low-Voltage STOP Mode                                         | 1020 |

|       |                 | 24.6.1 Setting and operation status                                     | 1020 |

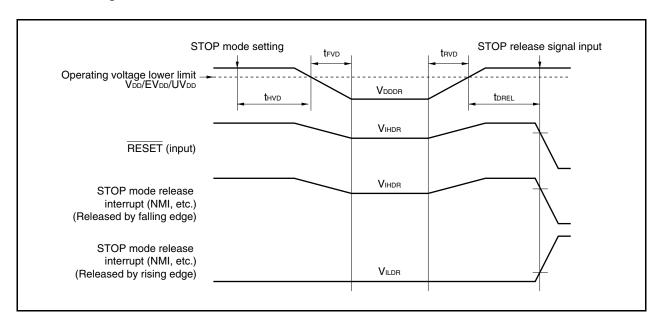

|       |                 | 24.6.2 Releasing STOP mode/low-voltage STOP mode                        | 1024 |

|       |                 | 24.6.3 Re-setting after release of low-voltage STOP mode                | 1025 |

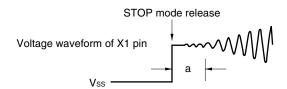

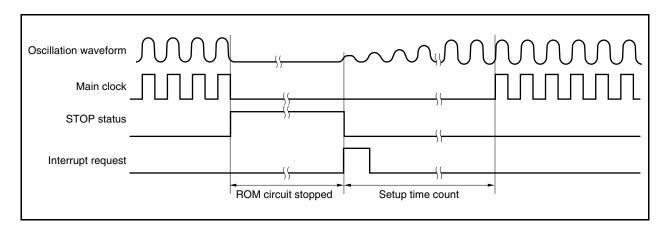

|       |                 | 24.6.4 Securing oscillation stabilization time when releasing STOP mode | 1026 |

| 24    | 4.7             | Subclock Operation Mode/Low-Voltage Subclock Operation Mode             | 1027 |

|       |                 | 24.7.1 Setting and operation status                                     | 1027 |

|       |                 | 24.7.2 Releasing subclock operation mode                                | 1031 |

|       |                 | 24.7.3 Releasing low-voltage subclock operation mode                    | 1031 |

| 24    | 4.8             | Sub-IDLE Mode/Low-Voltage Sub-IDLE Mode                                 | 1032 |

|       |                 | 24.8.1 Setting and operation status                                     | 1032 |

|       |                 | 24.8.2 Releasing sub-IDLE mode/low-voltage sub-IDLE mode                | 1035 |

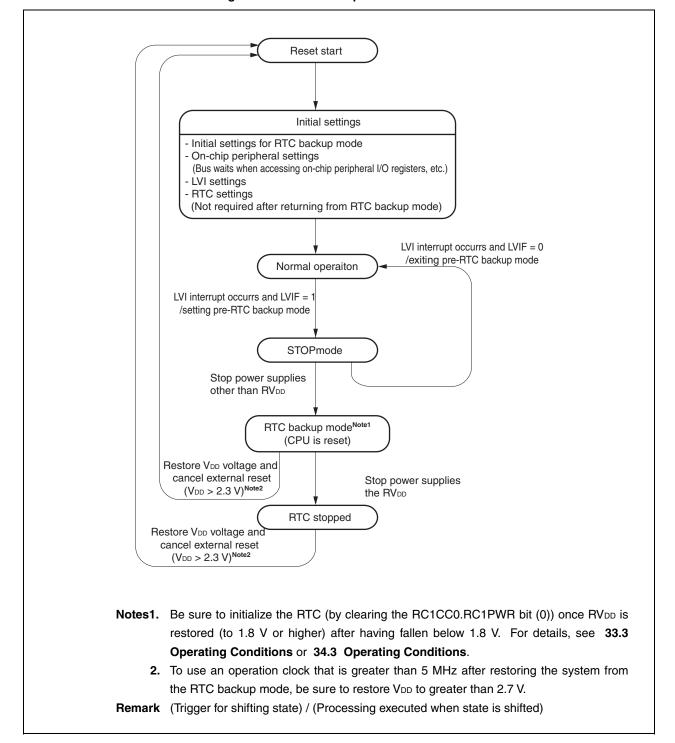

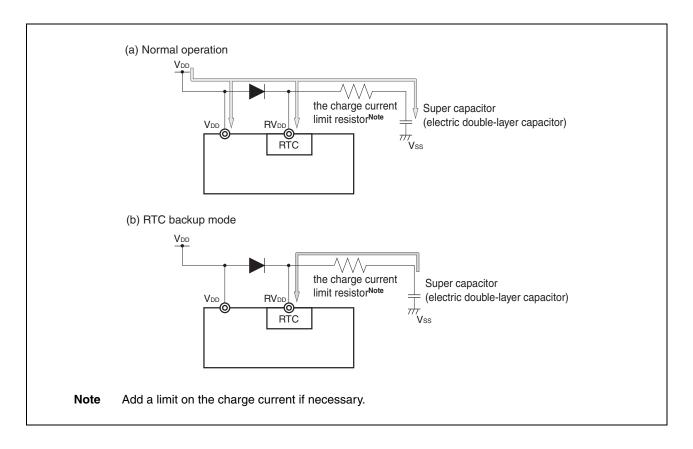

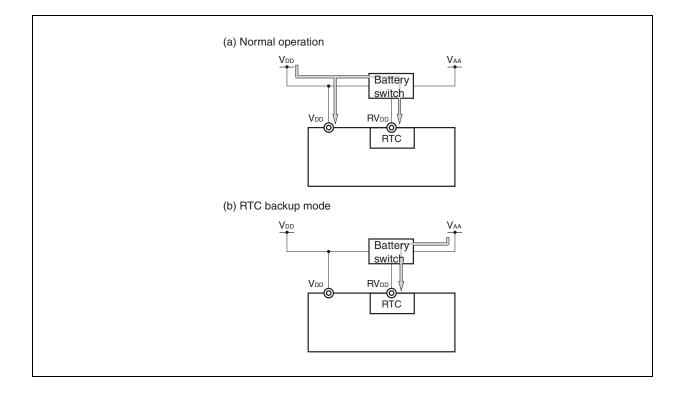

| 24    | 4.9             | RTC backup Mode                                                         | 1036 |

|       |                 | 24.9.1 Registers                                                        | 1036 |

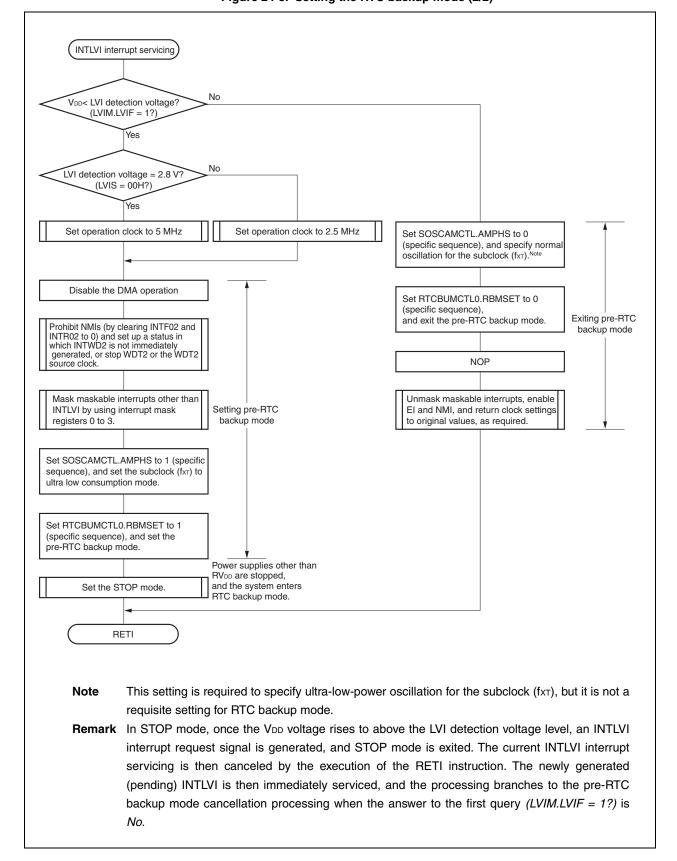

|       |                 | 24.9.2 RTC backup mode setting conditions                               | 1038 |

|       |                 | 24.9.3 RTC backup mode setting procedure                                | 1039 |

| СНФРТ | TFR             | 25 RESET FUNCTION                                                       | 1046 |

|       |                 | Overview                                                                |      |

|       |                 | Configuration                                                           |      |

|       |                 |                                                                         |      |

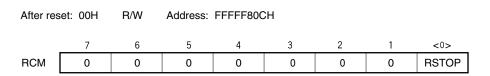

| 25.3    | Register to Check Reset Source                 | 1048 |

|---------|------------------------------------------------|------|

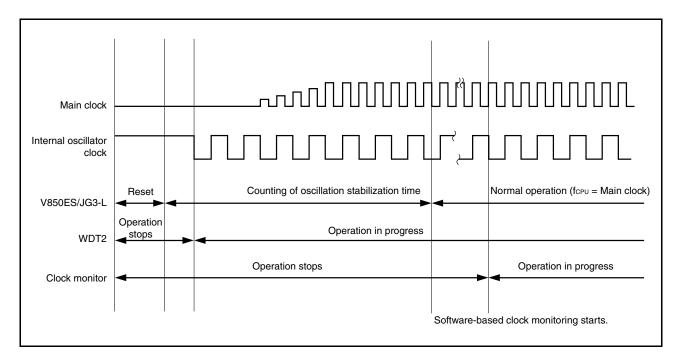

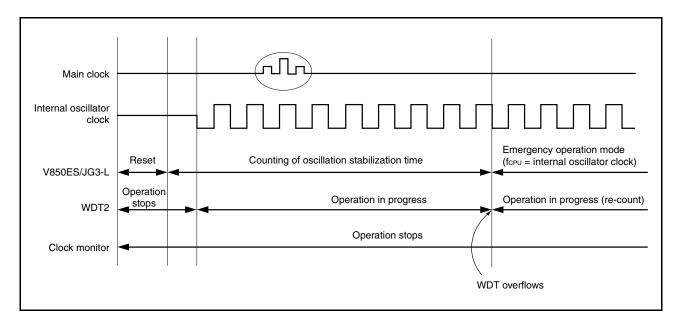

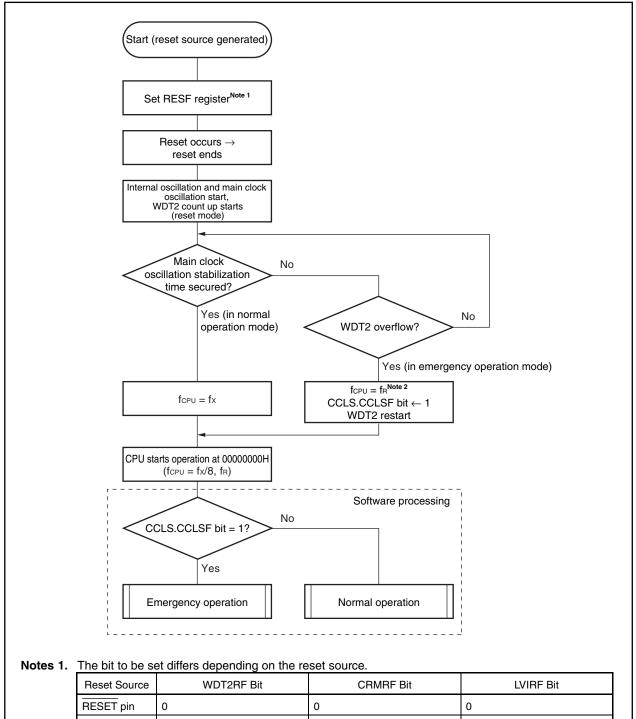

| 25.4    | Operation                                      | 1049 |

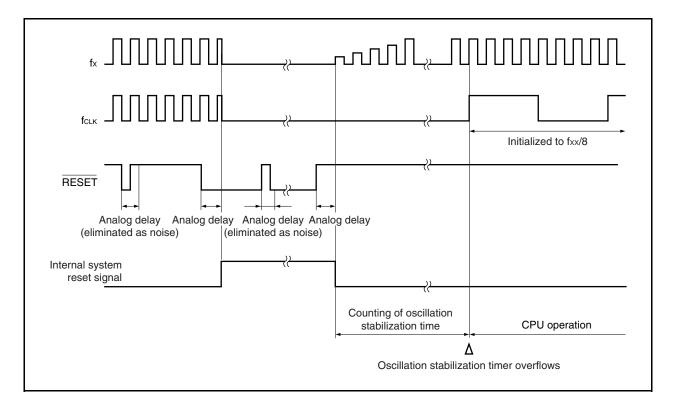

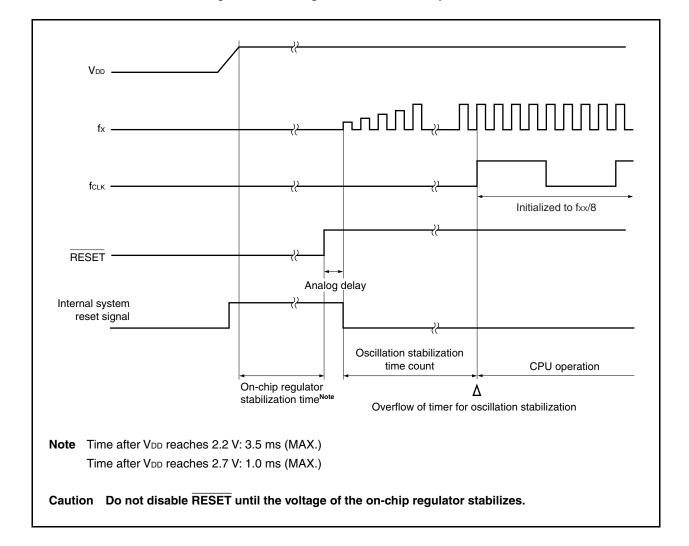

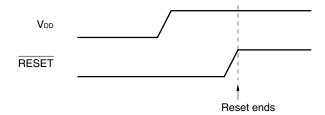

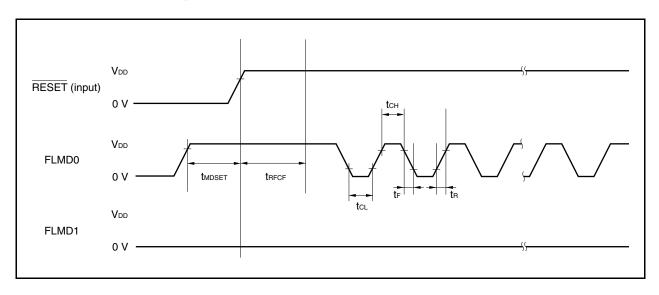

|         | 25.4.1 Reset operation via RESET pin           | 1049 |

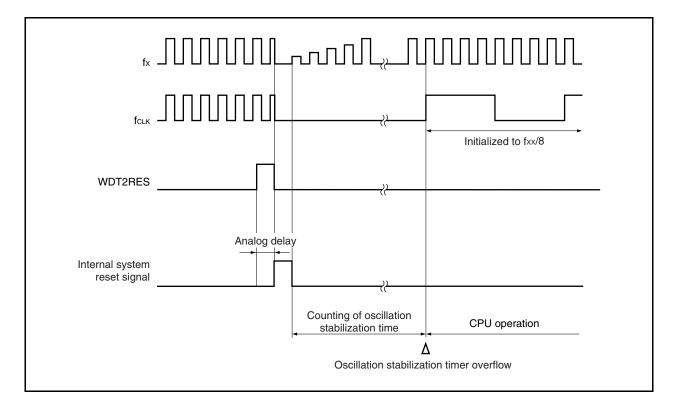

|         | 25.4.2 Reset operation by watchdog timer 2     | 1052 |

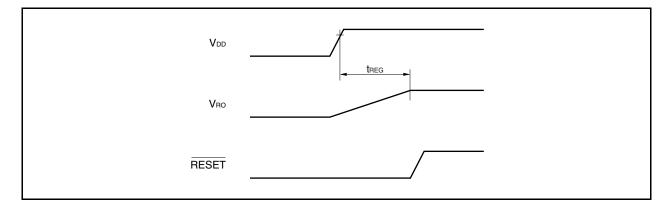

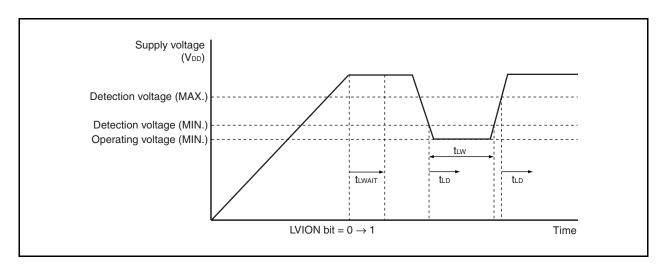

|         | 25.4.3 Reset operation by low-voltage detector | 1054 |

|         | 25.4.4 Operation immediately after reset ends  | 1055 |

|         | 25.4.5 Reset function operation                | 1057 |

| 25.5    | Cautions                                       | 1058 |

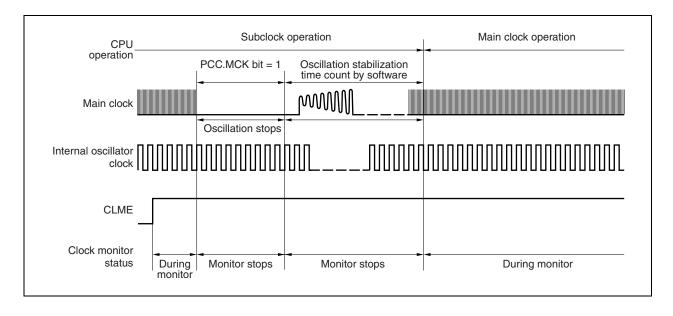

| CHAPTER | R 26 CLOCK MONITOR                             | 1059 |

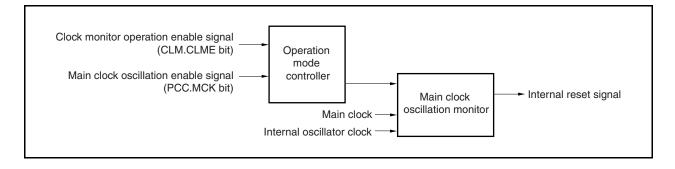

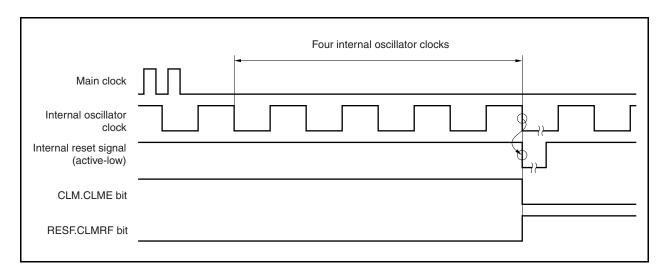

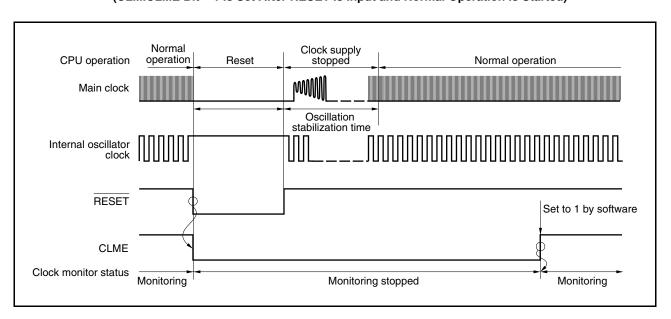

| 26.1    | Functions                                      | 1059 |

| 26.2    | Configuration                                  | 1059 |

| 26.3    | Registers                                      | 1060 |

| 26.4    | Operation                                      | 1061 |

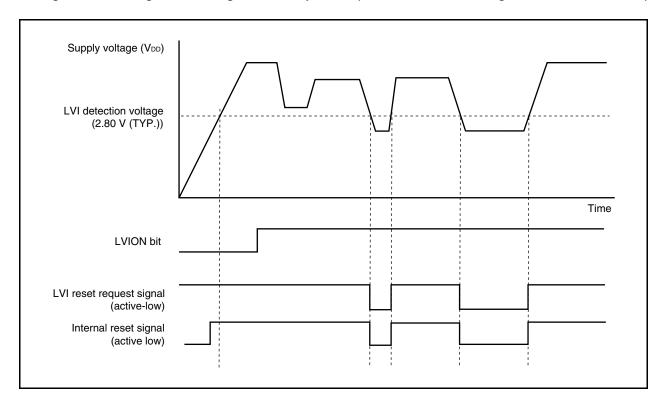

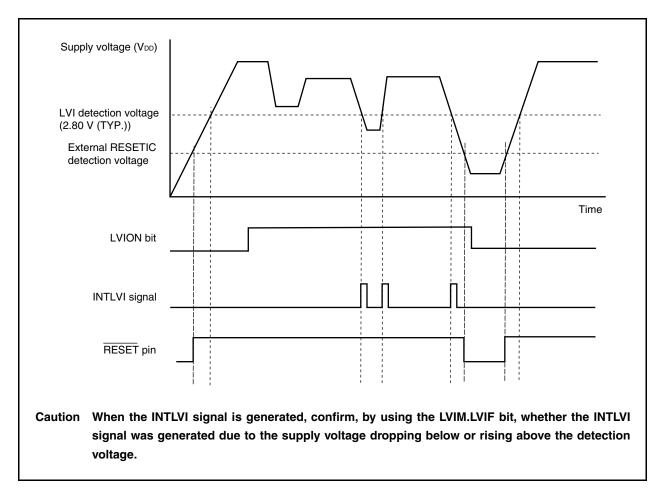

| CHAPTER | R 27 LOW-VOLTAGE DETECTOR (LVI)                | 1064 |

| 27.1    | Functions                                      | 1064 |

| 27.2    | Configuration                                  | 1064 |

| 27.3    | Registers                                      | 1065 |

| 27.4    | Operation                                      | 1067 |

|         | 27.4.1 To use for internal reset signal        | 1067 |

|         | 27.4.2 To use for interrupt                    | 1068 |

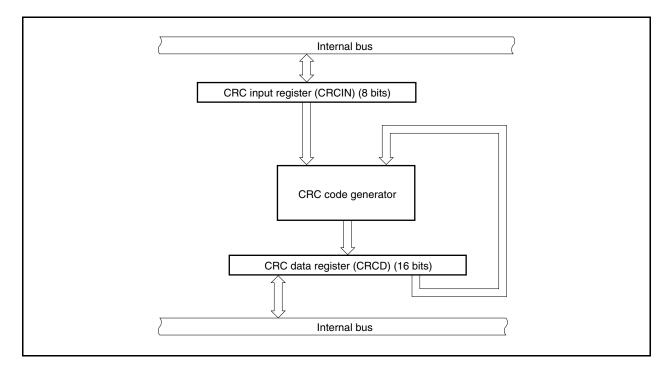

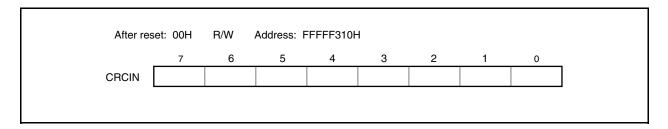

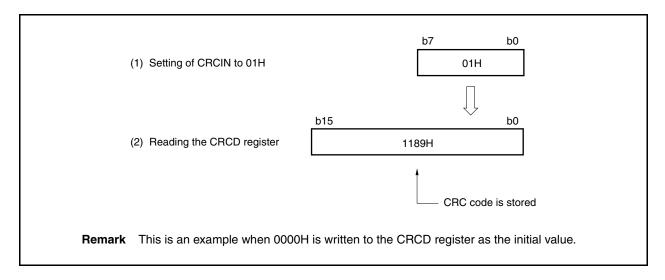

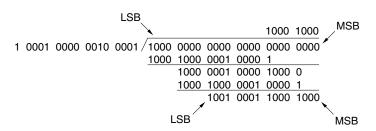

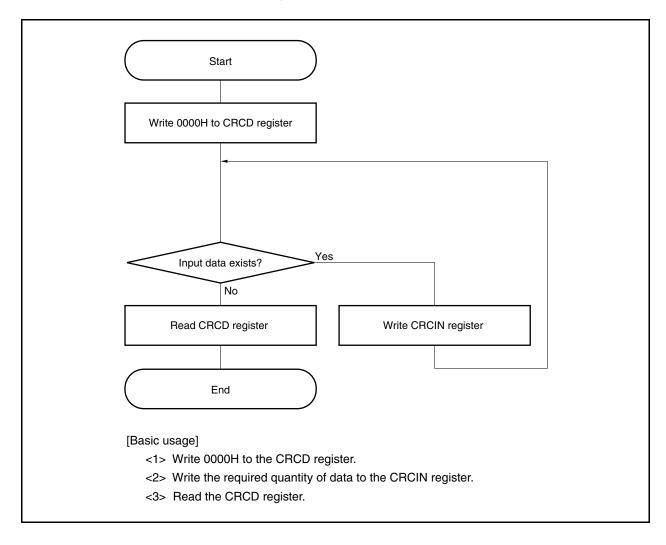

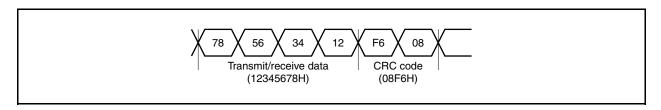

| CHAPTER | R 28 CRC FUNCTION                              | 1069 |

| 28.1    | Functions                                      | 1069 |

| 28.2    | Configuration                                  | 1069 |

| 28.3    | Registers                                      | 1070 |

| 28.4    | Operation                                      | 1071 |

| 28.5    | Usage                                          | 1072 |

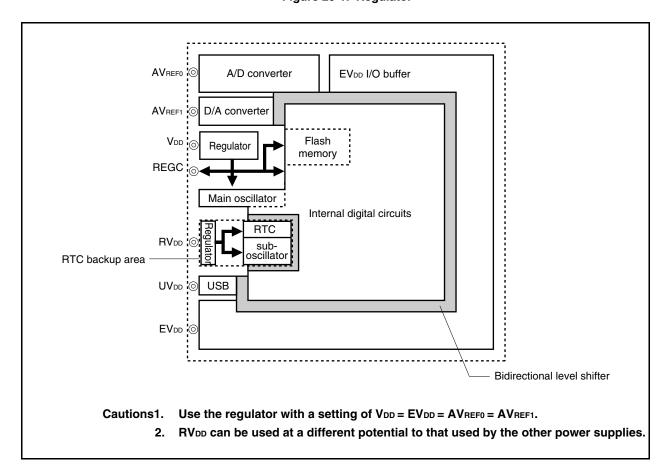

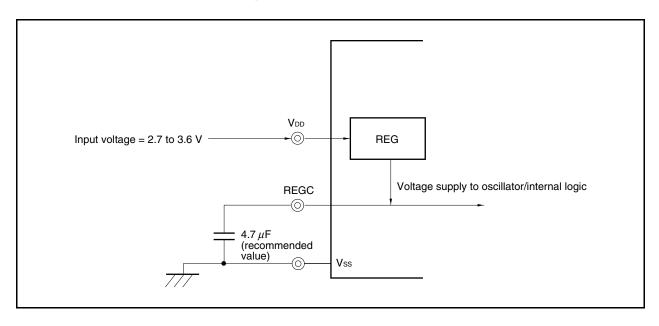

| CHAPTER | R 29 REGULATOR                                 | 1074 |

| 29.1    | Outline                                        | 1074 |

| 29.2    | Operation                                      | 1075 |

| CHAPTER | R 30 OPTION BYTE                               | 1076 |

| 30.1    | Program Example                                | 1078 |

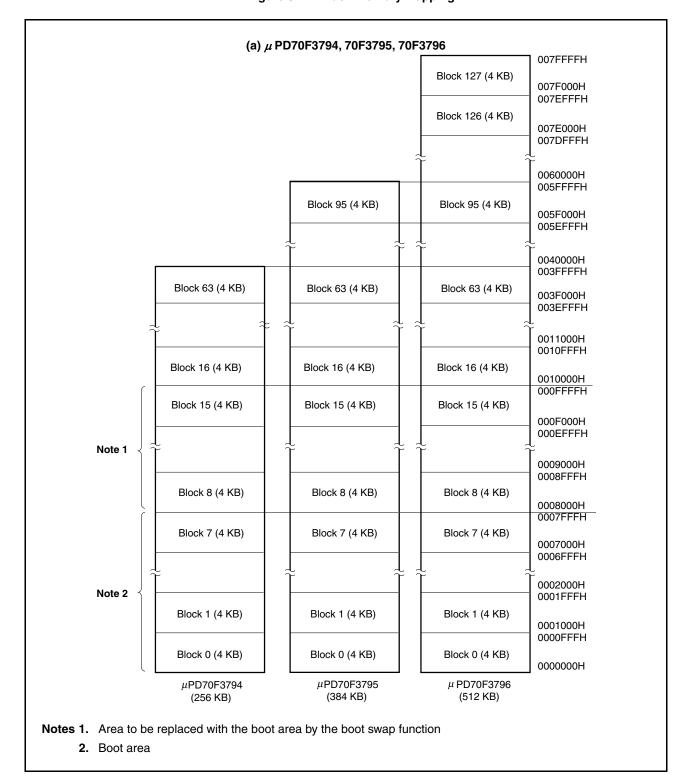

| CHAPTER | R 31 FLASH MEMORY                              | 1079 |

| 31.1    | Features                                       | 1079 |

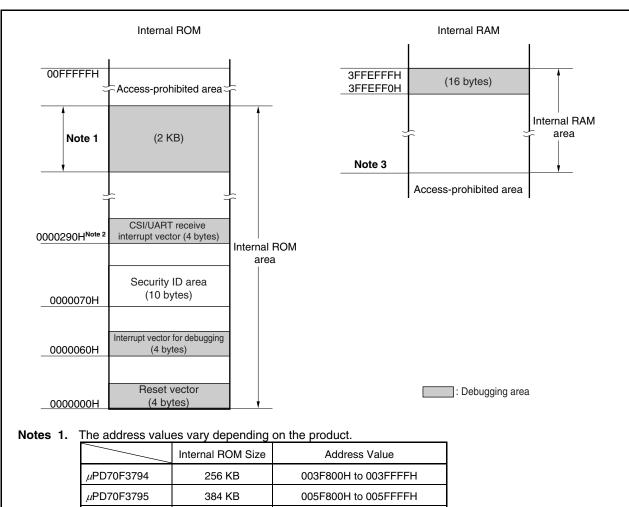

| 31.2    | Memory Configuration                           | 1080 |

| 31.3    | Functional Outline                             | 1081 |

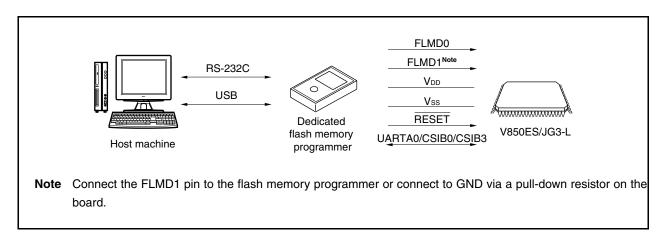

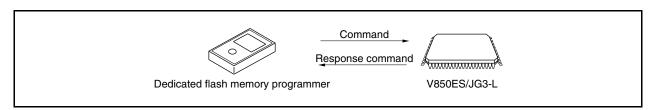

| 31.4    | Rewriting by Dedicated Flash Memory Programmer | 1084 |

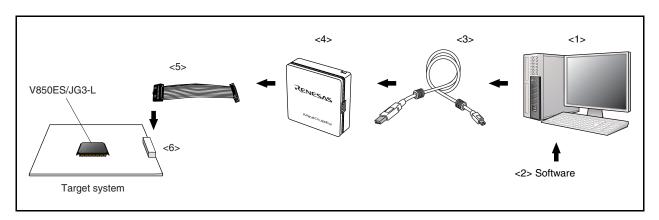

|         | 31.4.1 Programming environment                 | 1084 |

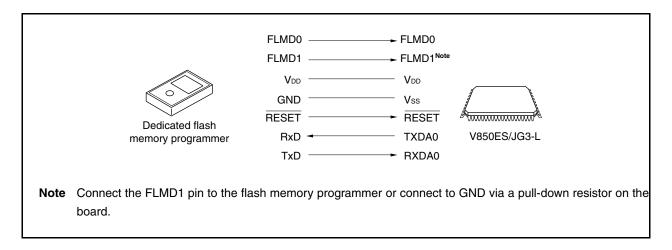

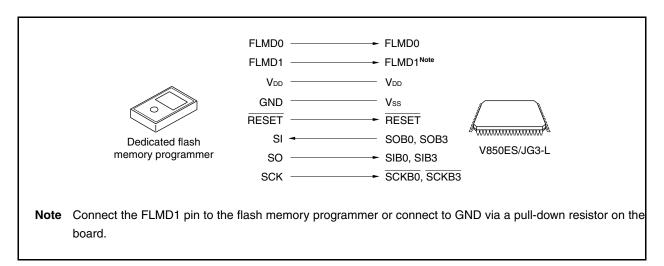

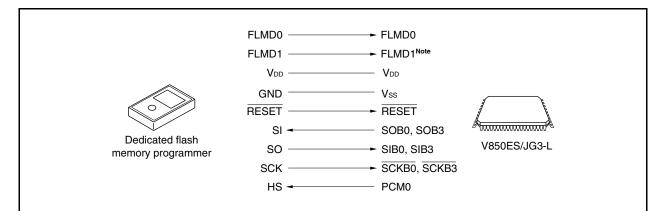

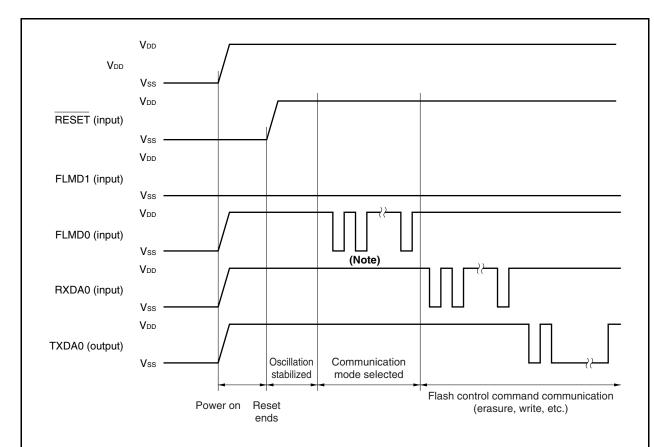

|         | 31.4.2 Communication mode                      | 1085 |

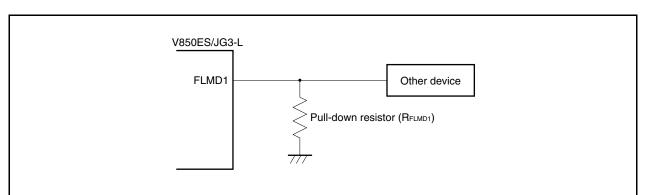

|         | 31.4.3 Interface                               | 1087 |

|      |      | 31.4.4 Flash memory control                                    | 1092 |

|------|------|----------------------------------------------------------------|------|

|      |      | 31.4.5 Selection of communication mode                         | 1093 |

|      |      | 31.4.6 Communication commands                                  | 1094 |

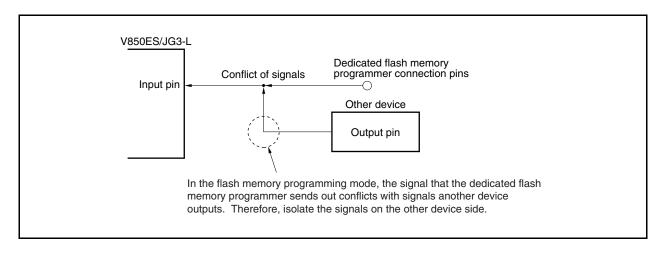

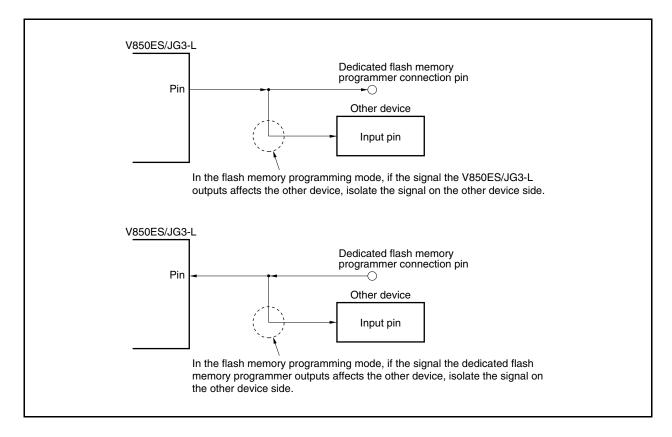

|      |      | 31.4.7 Pin connection in on-board programming                  | 1095 |

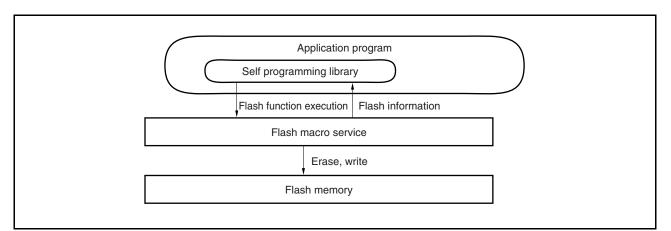

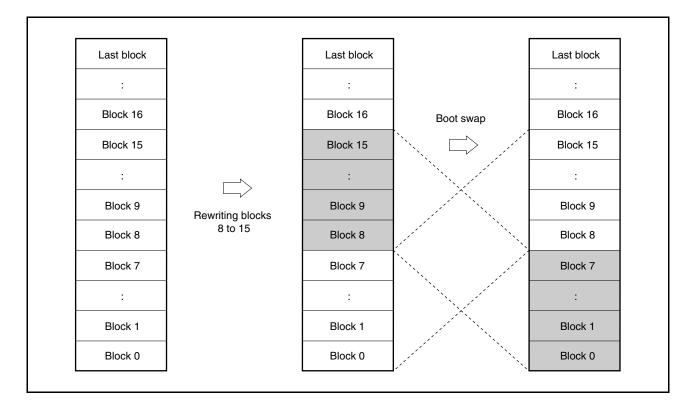

| 3    | 31.5 | Rewriting by Self Programming                                  | 1099 |

|      |      | 31.5.1 Overview                                                | 1099 |

|      |      | 31.5.2 Features                                                | 1100 |

|      |      | 31.5.3 Standard self programming flow                          | 1101 |

|      |      | 31.5.4 Flash functions                                         | 1102 |

|      |      | 31.5.5 Pin processing                                          | 1102 |

|      |      | 31.5.6 Internal resources used                                 | 1103 |

| CHAF | PTEF | 32 ON-CHIP DEBUG FUNCTION                                      | 1104 |

| 3    | 32.1 | Debugging with DCU                                             | 1106 |

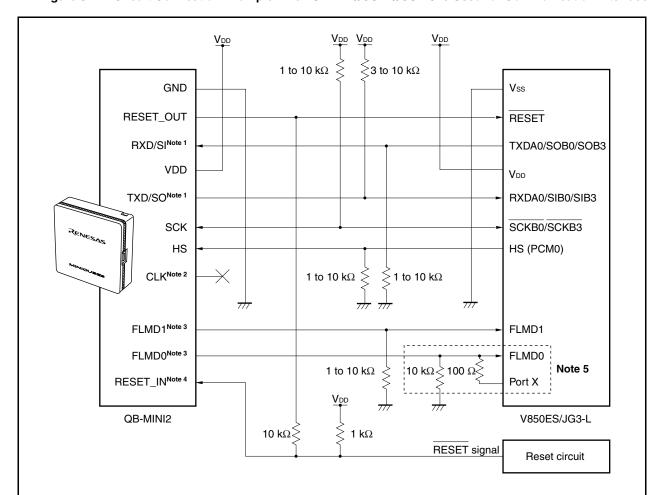

|      |      | 32.1.1 Connection circuit example                              | 1106 |

|      |      | 32.1.2 Interface signals                                       | 1107 |

|      |      | 32.1.3 Mask function                                           | 1108 |

|      |      | 32.1.4 Registers                                               | 1109 |

|      |      | 32.1.5 Operation                                               | 1110 |

|      |      | 32.1.6 Cautions                                                | 1111 |

| 3    | 32.2 | Debugging Without Using DCU                                    | 1112 |

|      |      | 32.2.1 Circuit connection examples                             | 1112 |

|      |      | 32.2.2 Mask function                                           | 1114 |

|      |      | 32.2.3 Allocation of user resources                            | 1115 |

|      |      | 32.2.4 Cautions                                                | 1122 |

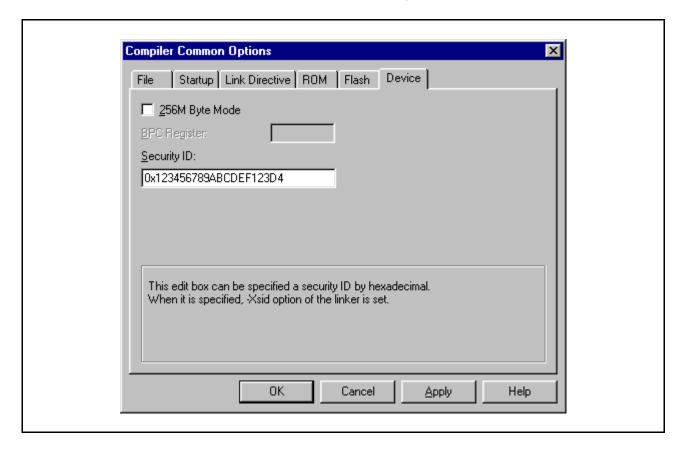

| 3    | 32.3 | ROM Security Function                                          | 1123 |

|      |      | 32.3.1 Security ID                                             | 1123 |

|      |      | 32.3.2 Setting                                                 | 1124 |

| CHAF | PTEF | R 33 ELECTRICAL SPECIFICATIONS (μ PD70F3794, 70F3795, 70F3796) | 1125 |

| 3    | 33.1 | Absolute Maximum Ratings                                       | 1125 |

| 3    | 33.2 | Capacitance                                                    | 1126 |

| 3    | 33.3 | Operating Conditions                                           | 1127 |

| 3    | 33.4 | Oscillator Characteristics                                     | 1128 |

|      |      | 33.4.1 Main clock oscillator characteristics                   | 1128 |

|      |      | 33.4.2 Subclock oscillator characteristics                     | 1132 |

|      |      | 33.4.3 PLL characteristics                                     | 1134 |

|      |      | 33.4.4 Internal oscillator characteristics                     | 1134 |

| 3    | 33.5 | Regulator Characteristics                                      | 1135 |

| 3    | 33.6 | DC Characteristics                                             | 1136 |

|      |      | 33.6.1 Pin characteristics                                     | 1136 |

|      |      | 33.6.2 Supply current characteristics                          | 1138 |

|      |      | 33.6.3 Data retention characteristics (in STOP mode)           | 1139 |

| 3    | 33.7 | AC Characteristics                                             | 1140 |

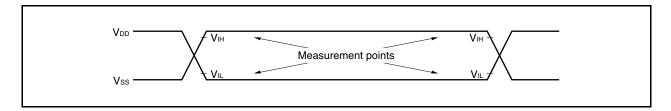

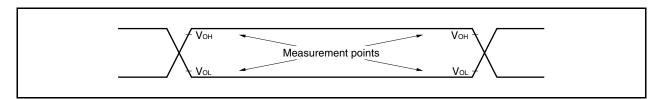

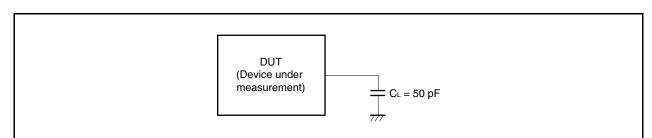

|                                                   | 33.7.1 Measurement conditions                                                                                                                                                                                                                                                                                                       | 1140                                 |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

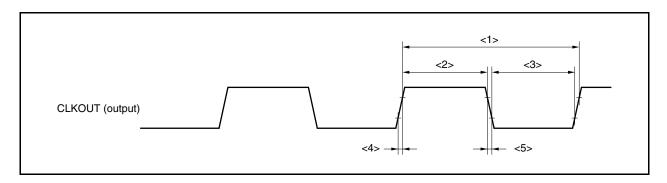

|                                                   | 33.7.2 CLKOUT output timing                                                                                                                                                                                                                                                                                                         | 1141                                 |

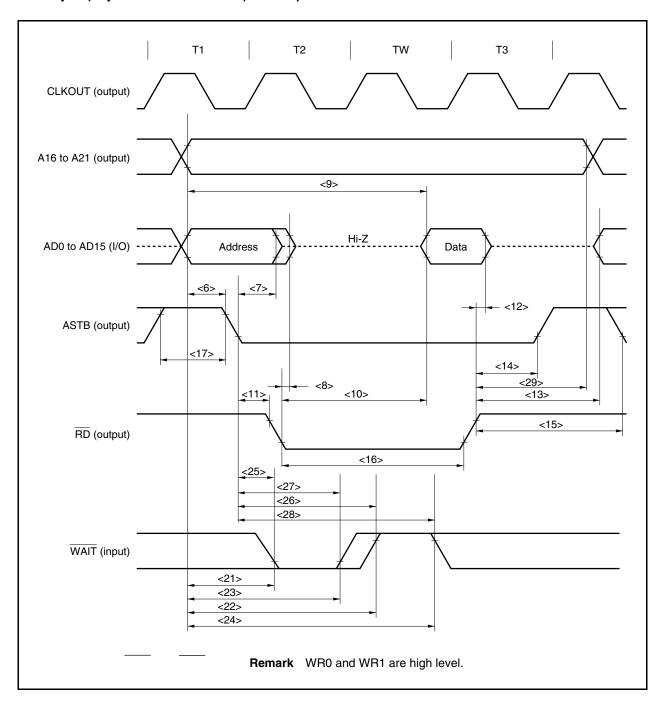

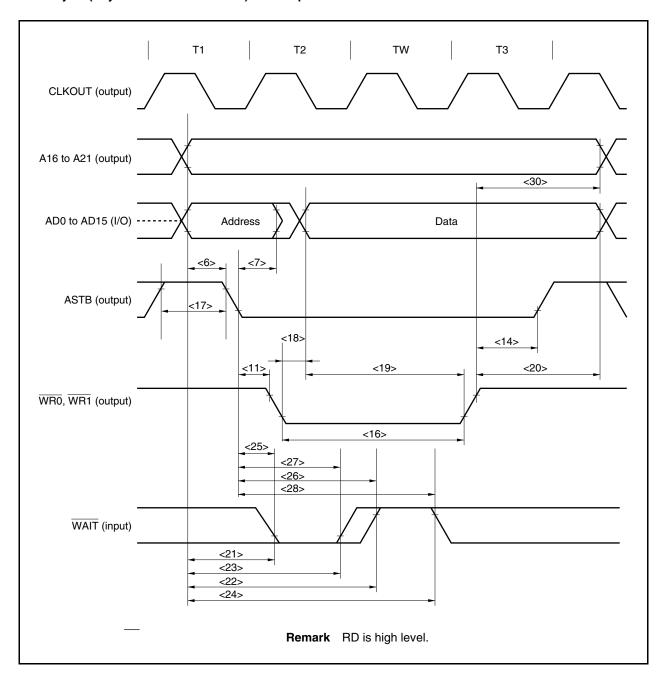

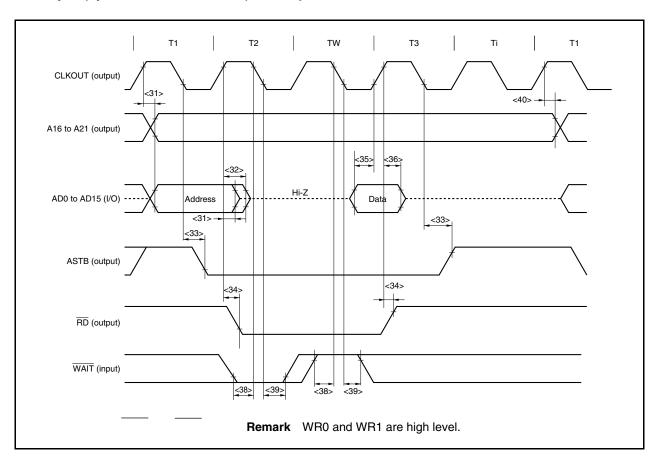

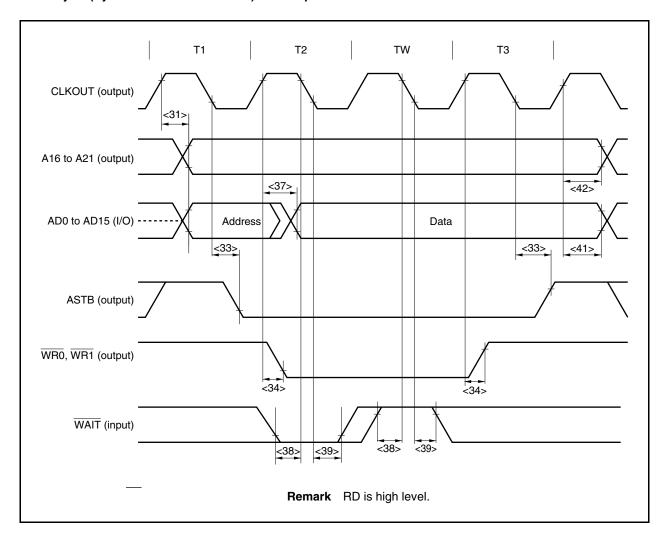

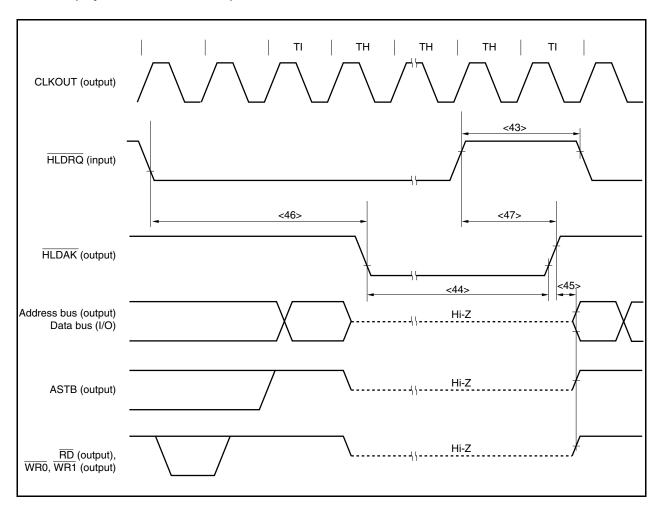

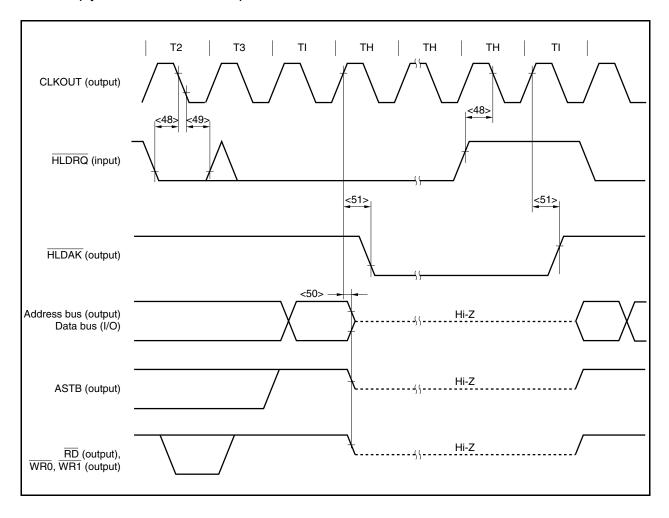

|                                                   | 33.7.3 Bus timing                                                                                                                                                                                                                                                                                                                   | 1142                                 |

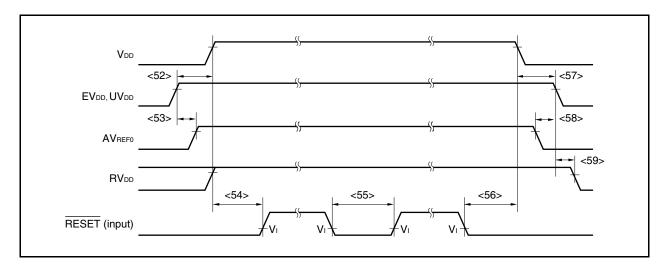

|                                                   | 33.7.4 Power on/power off/reset timing                                                                                                                                                                                                                                                                                              | 1149                                 |

| 33.8                                              | Peripheral Function Characteristics                                                                                                                                                                                                                                                                                                 | 1150                                 |

|                                                   | 33.8.1 Interrupt timing                                                                                                                                                                                                                                                                                                             | 1150                                 |

|                                                   | 33.8.2 Key return timing                                                                                                                                                                                                                                                                                                            | 1150                                 |

|                                                   | 33.8.3 Timer timing                                                                                                                                                                                                                                                                                                                 | 1150                                 |

|                                                   | 33.8.4 UART timing                                                                                                                                                                                                                                                                                                                  | 1151                                 |

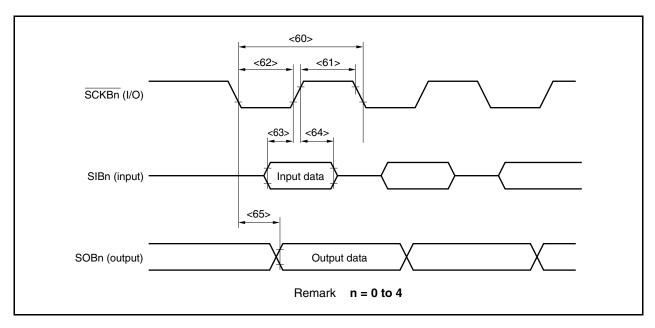

|                                                   | 33.8.5 CSIB timing                                                                                                                                                                                                                                                                                                                  | 1151                                 |

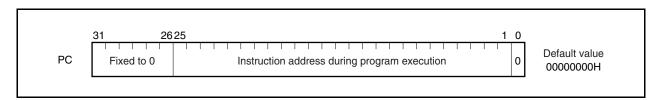

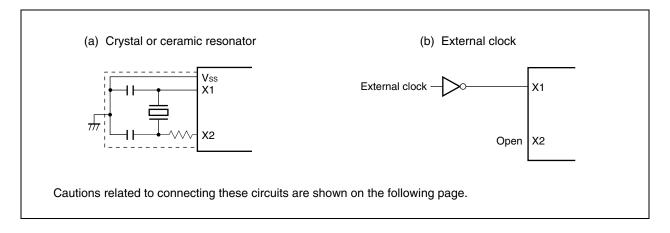

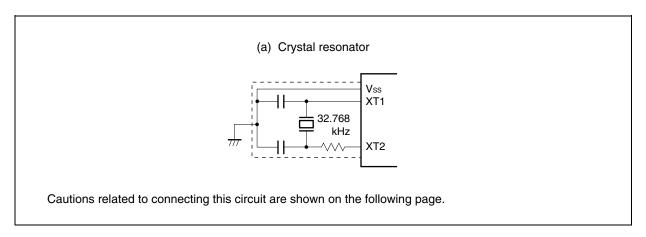

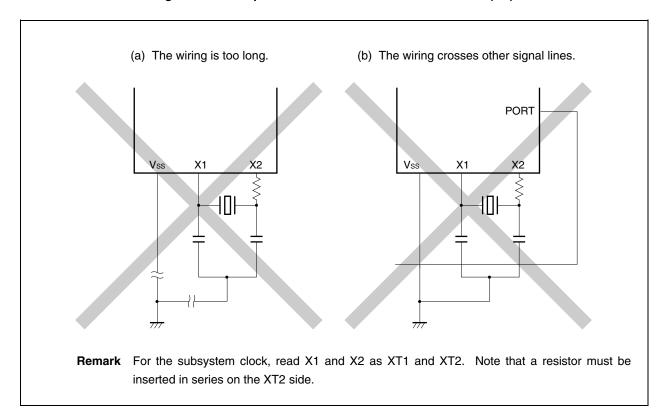

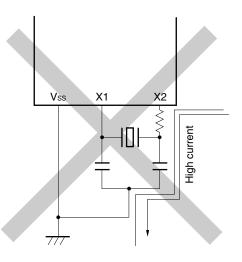

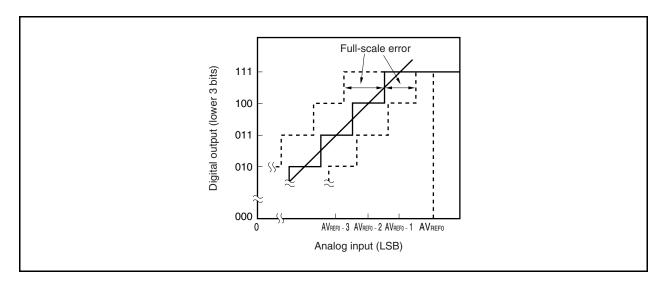

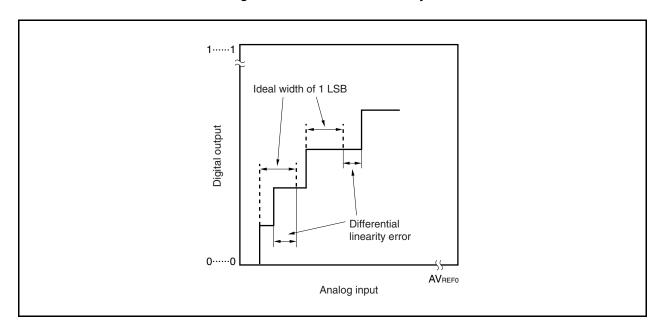

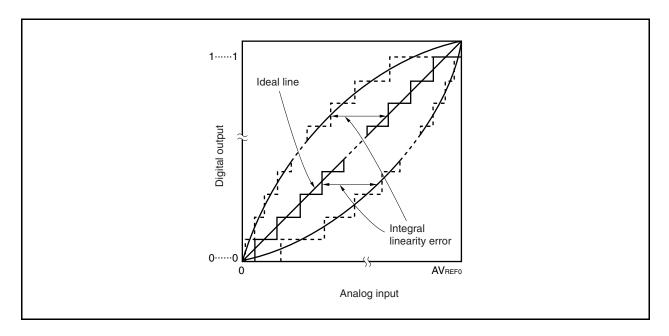

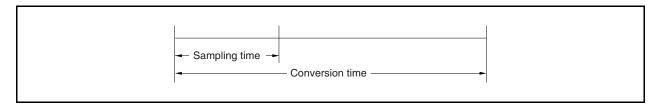

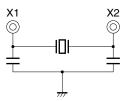

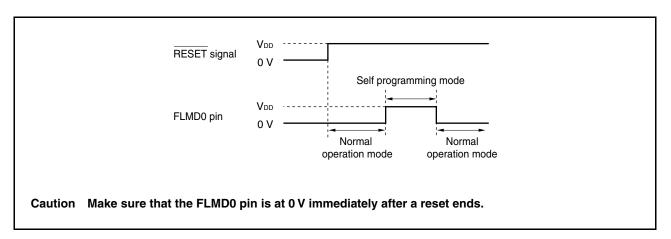

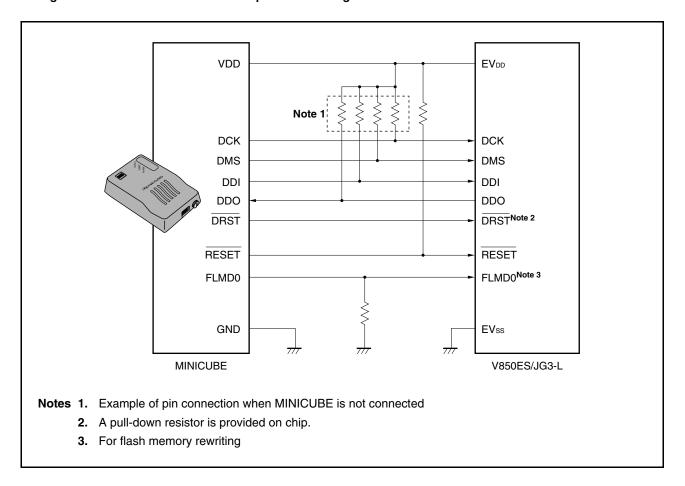

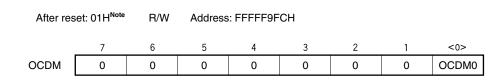

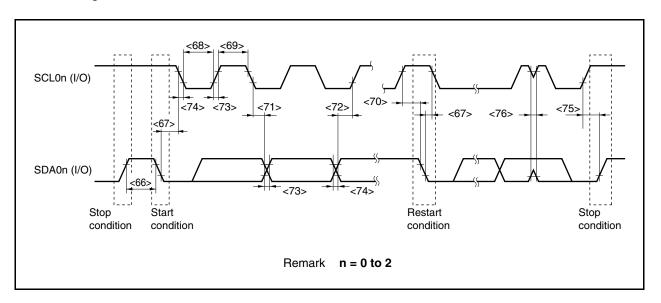

|                                                   | 33.8.6 I <sup>2</sup> C bus mode                                                                                                                                                                                                                                                                                                    | 1153                                 |