### **Description**

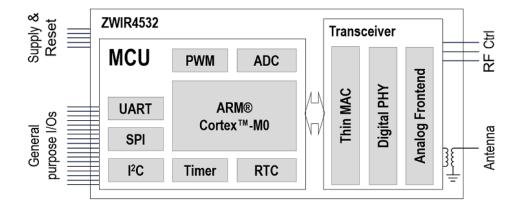

The ZWIR4532 is a programmable low-power secure IPv6 communication module for internet of things (IOT) device networks. Sensors and devices can operate autonomously or connect to local or global IPv6 networks using the ZWIR4532. The ZWIR4532 serves as a universal secure radio communication module for applications with low bandwidth requirements.

The module incorporates an ultra-low-power ARM® Cortex™-M0+32-bit microcontroller which is running the network stack. In addition, the user application can run on the microcontroller. This helps minimizing the size, complexity and overall BOM. A rich set of digital and analog peripherals is available for interfacing with external application components. Approximately 128kB of flash and 4kB of RAM are available for user applications.

IDT offers the SensorShare user programmable royalty-free 6LoWPAN network stack with mesh routing capability for the ZWIR4532. 6LoWPAN is an Internet Engineering Task Force (IETF) standard for wireless low-power IPv6-based sensor and device networks.

Secure communication is provided by a standard-compliant implementation of the Internet Protocol Security (IPSec) protocol suite.

## Typical Applications

- Industrial automation

- Home and building automation

- Health monitoring

- Telemetry

#### **Features**

- License-free 868/915 MHz frequency bands

- 4 channels in EU frequency band (865.3 868.3 MHz)

- 10 channels in US frequency band (906 924 MHz)

- · BPSK or O-QPSK modulation selectable

- BPSK with 20kBps EU and 40kBps U

- ARM® Cortex™-M0+ 32-bit ultra-low-power microcontroller

- 192kB flash and 20kB RAM

- 6kByte EEPROM

- 5 UART interfaces

- 1 SPI interface

- 3 I<sup>2</sup>C interfaces

- 10 PWM outputs

- 12 bit ADC with 10 input channels

- 2 analog comparators

- 31 GPIOs

- Network Stack

- UDP/IPv6 communication

- Mesh networking with hundreds of nodes

- Self-healing defective routes

- Over-the-Air update capable

- Network layer security

- Ultra-low power stop mode: < 1µA with full RAM retention</li>

- Supply voltage: 1.8V to 3.3V

- -40°C to +85°C ambient operating temperature

- 15.6 × 12 mm 43-LGA Package

## **Block Diagram**

## **Contents**

| 1.     | Pin / | Assignments                                                                        | 3  |

|--------|-------|------------------------------------------------------------------------------------|----|

| 2.     | Pin I | Descriptions                                                                       | 3  |

| 3.     | Abso  | olute Maximum Ratings                                                              | 7  |

| 4.     | Rec   | ommended Operating Conditions                                                      | 8  |

| 5.     | Fund  | ctional Overview                                                                   | 9  |

|        | 5.1   | Low Power Modes                                                                    | 10 |

|        | 5.2   | Device Programming and Debugging                                                   | 10 |

| 6.     | Pack  | kage Outline Drawing                                                               | 11 |

| 7.     | Sold  | dering Information                                                                 | 12 |

| 8.     | Cert  | tification                                                                         | 13 |

|        | 8.1   | European RED Statement                                                             | 13 |

|        | 8.2   | Federal Communication Commission Certification Statements                          | 13 |

|        |       | 8.2.1 Statements                                                                   | 13 |

|        |       | 8.2.2 Requirements                                                                 | 13 |

|        |       | 8.2.3 Supported Antennas                                                           | 14 |

| 9.     | Orde  | ering Information                                                                  | 15 |

| 10.    | Revi  | ision History                                                                      | 15 |

| Lis    | t c   | of Figures                                                                         |    |

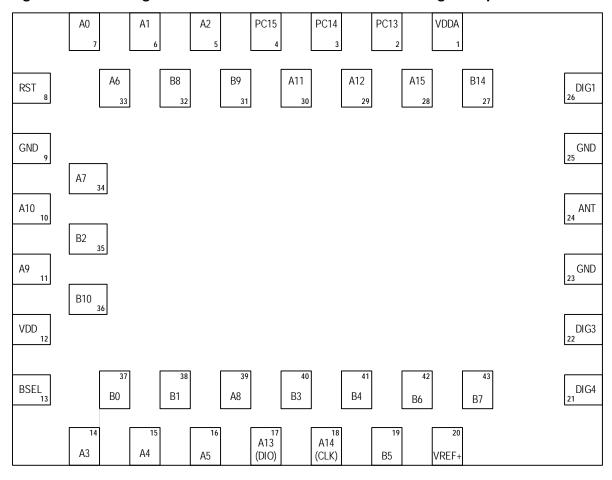

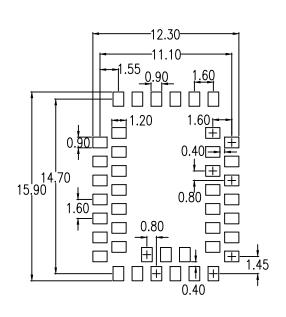

| Figure | e 1.  | Pin Assignments for 15.6mm × 12.0mm LGA Package – Top View                         | 3  |

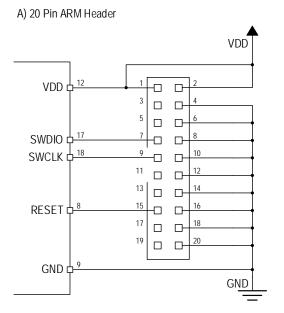

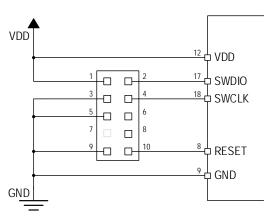

| Figure | e 2.  | Serial Wire Debug Connection with Standard ARM Connectors                          | 10 |

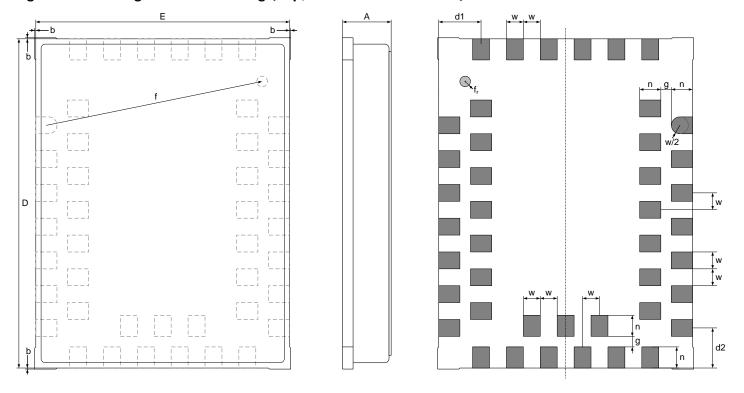

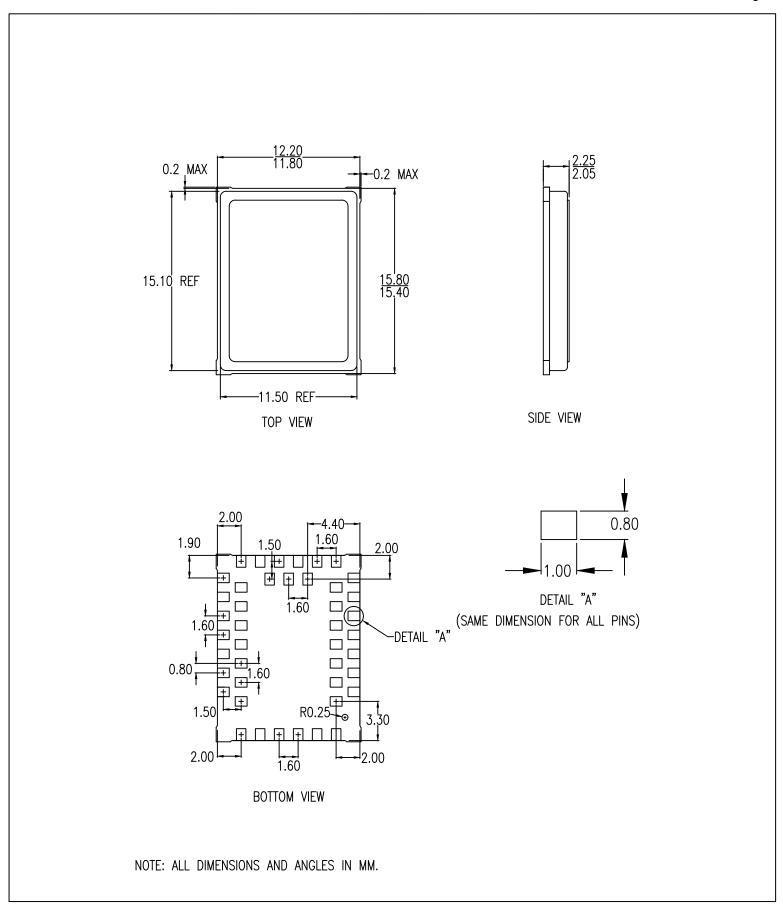

| Figure | e 3.  | Package Outline Drawing (Top, Left and Bottom View)                                | 11 |

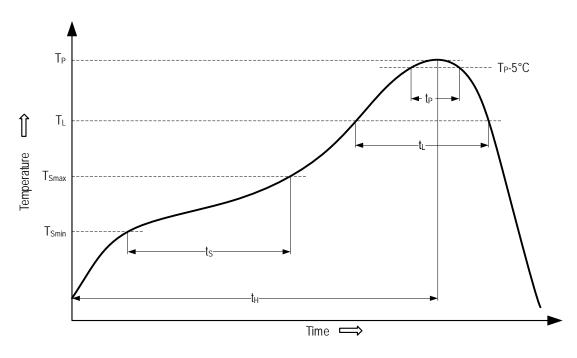

| Figure | e 5.  | Recommended Temperature Profile for Reflow Soldering (according to J-STD-020D)     | 12 |

| Figure | e 6.  | FCC Compliance Statement to be Printed on Equipment Incorporating ZWIR4532 Devices | 14 |

| Lis    | t c   | of Tables                                                                          |    |

| Table  | 1.    | Pin Descriptions                                                                   | 3  |

| Table  | 2.    | Module Pins Peripheral Function Mapping                                            | 6  |

| Table  | 3.    | Absolute Maximum Ratings                                                           | 7  |

| Table  | 4.    | Recommended Operating Conditions                                                   | 8  |

| Table  | 5.    | ZWIR4532 Physical Dimensions and Tolerances                                        | 11 |

| Table  | 6.    | Soldering Profile Parameters (according to J-STD-020D)                             | 12 |

# 1. Pin Assignments

Figure 1. Pin Assignments for 15.6mm imes 12.0mm LGA Package - Top View

## 2. Pin Descriptions

Table 1. Pin Descriptions

| Pin<br>Number | Name | Туре   | 5V | Description                                                                                              |

|---------------|------|--------|----|----------------------------------------------------------------------------------------------------------|

| 1             | VDDA | Supply |    |                                                                                                          |

| 2             | PC13 | GPIO   | Υ  | RTC Tamper, TRC Timestamp, RTC output, Wakeup 2.                                                         |

| 3             | PC14 | GPIO   | Υ  | OSC32 In.                                                                                                |

| 4             | PC15 | GPIO   | TC | OSC32 Out.                                                                                               |

| 5             | PA2  | GPIO   | Υ  | Timer21 Ch1, Timer2 Ch3, USRT2 TX, LPUART1 TX, COMP2 Output, COMP2 INM, ADC Ch2.                         |

| 6             | PA1  | GPIO   | Υ  | Event Out, Timer2 Ch2, USART2 RTS/DE, TIM21 ETR, USART4 RX, COMP1 Input, ADC Ch1.                        |

| 7             | PA0  | GPIO   |    | Timer 2 Ch1, Timer 2 ETR, USART2 CTS, USART4 TX, COMP1 OUT, COMP1 INM, ADC Ch 0, RTC Tamper 2, Wakeup 1. |

| Pin<br>Number | Name  | Туре    | 5 <b>V</b> | Description                                                                                                  |

|---------------|-------|---------|------------|--------------------------------------------------------------------------------------------------------------|

| 8             | RST   | I/O     |            | Device reset, low active.                                                                                    |

| 9             | GND   | Ground  |            |                                                                                                              |

| 10            | PA10  | GPI0    | Υ          | USART1 RX, I2C1 SDA.                                                                                         |

| 11            | PA9   | GPIO    | Υ          | MCO, USART1 TX, I2C1 SCL, I2C3 SMBA.                                                                         |

| 12            | VDD   | Supply  |            |                                                                                                              |

| 13            | BSEL  | I       |            |                                                                                                              |

| 14            | PA3   | GPIO    | Υ          | Timer21 Ch2, Timer2 Ch4, USART2 RX, LPUART1 RX, COMP2 INP, ADC Ch3.                                          |

| 15            | PA4   | GPIO    | N          | SPI1 NSS, USART2 CK, Timer22 ETR, COMP1 INM, COMP2 INM, ADC Ch4.                                             |

| 16            | PA5   | GPI0    | N          | SPI1 SCK, Timer2 ETR, Timer2 Ch1, COMP1 INM, COMP2 INM, ADC Ch5.                                             |

| 17            | PA13  | GPIO    | Υ          | SWDIO, LPUART1 RX.                                                                                           |

| 18            | PA14  | GPIO    | Υ          | SWCLK, USART2 TX, LPUART1 TX.                                                                                |

| 19            | PB5   | GPIO    | Υ          | SPI1 MOSI, LPTimer1 In1, I2C1 SMBA, Timer3 Ch2, Timer22 Ch2, USART1 CK, USART5 CK, USART5 RTS/DE, Comp2 INP. |

| 20            | VREF+ | Supply  |            |                                                                                                              |

| 21            | PA-   | 0       |            | Differential power amplifier control output, internally tied to ground if not used.                          |

| 22            | PA+   | 0       |            | Leave unconnected if not used.                                                                               |

| 23            | GND   | Ground  |            |                                                                                                              |

| 24            | ANT   | Antenna |            | Antenna pin.                                                                                                 |

| 25            | GND   | Ground  |            |                                                                                                              |

| 26            | DIG1  | 0       |            |                                                                                                              |

| 27            | PB14  | GPIO    | Υ          | SPI2 MISO, I2S2 MCK, RTC Out, LPUART1 RTS/DE, I2C2 SDA, Timer21 Ch2.                                         |

| 28            | PA15  | GPIO    | Υ          | SPI1 NSS, Timer2 ETR, Event Out, USART2 RX, Timer2 Ch1, USART4 RTS/DE.                                       |

| 29            | PA12  | GPIO    | Υ          | SPI1 MOSI, Event Out, USART1 RTS/DE, COMP2 Out.                                                              |

| 30            | PA11  | GPIO    | Υ          | SPI1 MISO, Event Out, USART1 CTS, COMP1 Out.                                                                 |

| 31            | PB9   | GPIO    | Υ          | Event Out, I2C1 SDA, SPI2 NSS, I2S2 WS.                                                                      |

| 32            | PB8   | GPIO    | Υ          | I2C1 SCL.                                                                                                    |

| 33            | PA6   | GPIO    | Υ          | SPI1 MISO, Timer3 Ch1, LPUART1 CTS, Timer22 Ch1, Event Out, COMP1 Out, ADC Ch6.                              |

| 34            | PA7   | GPIO    | Υ          | SPI1 MOSI, Timer3 Ch2, Timer22 Ch2, Event Out, COMP2 Out, ADC Ch7.                                           |

| 35            | PB2   | GPIO    | Υ          | LPTimer 1 Out, I2C3 SMBA.                                                                                    |

| 36            | PB10  | GPIO    | Υ          | Timer 2 Ch3, LPUART1 TX, SPI2 SCK, I2C2 SCL, LPUART1 RX.                                                     |

| 37            | PB0   | GPIO    | Υ          | Event Out, Timer3 Ch3, ADC Ch8, VREF Out.                                                                    |

| 38            | PB1   | GPIO    | Υ          | Timer3 Ch4, LPART1 RTS/DE, ADC Ch9, VREF Out.                                                                |

| 39            | PA8   | GPIO    | Υ          | MCO, Event Out, USART1 CK, I2C3 SCL.                                                                         |

| 40            | PB3   | GPIO    | Υ          | SPI1 SCK, Timer2 Ch2, Event Out, USART2 RTS/DE, USART5 TX, COMP2 INM.                                        |

|               |       | •       | •          |                                                                                                              |

| Pin<br>Number | Name | Туре | 5V | Description                                                                     |

|---------------|------|------|----|---------------------------------------------------------------------------------|

| 41            | PB4  | GPIO | Υ  | SPI1 MISO, Timer3 Ch1, Timer22 Ch1, USART1 CTS, USART5 RX, I2C3 SDA, COMP2 INP. |

| 42            | PB6  | GPIO | Υ  | USART1 TX, I2C1 SCL, LPTimer1 ETR, COMP2 INP.                                   |

| 43            | PB7  | GPIO | Υ  | USART1 RX, I2C1 SDA, LPTimer1 In2, USART4 CTS, COMP2 INP, VREF PVD In.          |

**Table 2.** Module Pins Peripheral Function Mapping

| MCU F         | Port       |    |          |     |    |    |    |          | Poi | rt A |    |     |    |    |    |    |    |    |    |    |    |    | Po | rt B |    |    |          |                                                  |              |

|---------------|------------|----|----------|-----|----|----|----|----------|-----|------|----|-----|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----------|--------------------------------------------------|--------------|

|               | Port Pin   | 0  | 1        | 2   | 3  | 4  | 5  | 6        | 7   | 8    | 9  | 10  | 11 | 12 | 13 | 14 | 15 | 0  | 1  | 2  | 3  | 4  | 5  | 6    | 7  | 8  | 9        | 10                                               | 14           |

| Modul         |            | 7  | 6        | 5   | 14 | 15 | 16 | 33       | 34  | 39   | 11 | 10  | 30 | 29 | 17 | 18 | 28 | 37 | 38 | 35 | 40 | 41 | 19 | 42   | 43 | 32 | 31       | 36                                               | 27           |

|               | TX         |    |          |     |    |    |    |          |     |      | 4  |     |    |    |    |    |    |    |    |    |    |    |    | 0    |    |    |          |                                                  |              |

| $\sqsubseteq$ | RX         |    |          |     |    |    |    |          |     |      |    | 4   |    |    |    |    |    |    |    |    |    |    |    |      | 0  |    |          |                                                  |              |

| USART1        | RTS        |    |          |     |    |    |    |          |     |      |    |     |    | 4  |    |    |    |    |    |    | 5  |    |    |      |    |    |          |                                                  |              |

| S             | CTS        |    |          |     |    |    |    |          |     |      |    |     | 4  |    |    |    |    |    |    |    |    | 5  |    |      |    |    |          |                                                  |              |

|               | CK         |    |          |     |    |    |    |          |     | 4    |    |     |    |    |    |    |    |    |    |    |    |    | 5  |      |    |    |          |                                                  |              |

|               | TX         |    |          | 4   |    |    |    |          |     |      |    |     |    |    |    | 4  |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| 2T2           | RX         |    |          |     | 4  |    |    |          |     |      |    |     |    |    |    |    | 4  |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| USART2        | RTS        | L. | 4        |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          | $\vdash$                                         | $\vdash$     |

|               | CTS        | 4  |          |     |    | 4  |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          | <del></del>                                      |              |

|               | CK         | ,  |          |     |    | 4  |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| T4            | TX<br>RX   | 6  | 4        |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  | _            |

| USART4        | RTS        |    | 6        |     |    |    |    |          |     |      |    |     |    |    |    |    | 6  |    |    |    |    |    |    |      |    |    |          |                                                  | $\vdash$     |

| ñ             | CTS        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    | U  |    |    |    |    |    |    |      | 6  |    |          |                                                  | $\vdash$     |

| -10           | TX         |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    | 6  |    |    |      | U  |    |          |                                                  |              |

| USART5        | RX         |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    | 0  | 6  |    |      |    |    |          |                                                  |              |

| ns/           | CK         |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    | 0  | 6  |      |    |    |          |                                                  |              |

|               | TX         |    |          | 6   |    |    |    |          |     |      |    |     |    |    |    | 6  |    |    |    |    |    |    | ,  |      |    |    |          | 4                                                |              |

| RT1           | RX         |    | 1        | - 3 | 6  |    |    |          |     |      |    |     |    |    | 6  | J  |    |    |    |    |    |    |    |      |    |    |          | ŕ                                                |              |

| LPUART1       | RTS        |    |          |     | Ť  |    |    |          |     |      |    |     |    |    |    |    |    |    | 4  |    |    |    |    |      |    |    |          | 7                                                |              |

| 4             | CTS        |    |          |     |    |    |    | 4        |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  | $\Box$       |

|               | MOSI       |    |          |     |    |    |    |          | 0   |      |    |     |    | 0  |    |    |    |    |    |    |    |    | 0  |      |    |    |          |                                                  |              |

| Ξ             | MISO       |    |          |     |    |    |    | 0        |     |      |    |     | 0  |    |    |    |    |    |    |    |    | 0  |    |      |    |    |          |                                                  |              |

| SPI1          | SCK        |    |          |     |    |    | 0  |          |     |      |    |     |    |    |    |    |    |    |    |    | 0  |    |    |      |    |    |          |                                                  |              |

|               | NSS        |    |          |     |    | 0  |    |          |     |      |    |     |    |    |    |    | 0  |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| 5             | SCL        |    |          |     |    |    |    |          |     |      | 6  |     |    |    |    |    |    |    |    |    |    |    |    | 1    |    | 4  |          |                                                  |              |

| I2C1          | SDA        |    |          |     |    |    |    |          |     |      |    | 6   |    |    |    |    |    |    |    |    |    |    |    |      | 1  |    | 4        |                                                  |              |

| 12C2          | SCL        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          | 6                                                |              |

| 120           | SDA        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  | 5            |

| 12C3          | SCL        |    |          |     |    |    |    |          |     | 7    |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| 12            | SDA        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    | 7  |    |      |    |    |          |                                                  |              |

|               | Ch1        | 2  |          |     |    |    | 5  |          |     |      |    |     |    |    |    |    | 5  |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| 12            | Ch2        |    | 2        |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    | 2  |    |    |      |    |    |          |                                                  |              |

| TIM2          | Ch3        |    |          | 2   |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          | 2                                                |              |

|               | Ch4        | _  |          |     | 2  |    | 2  |          |     |      |    |     |    |    |    |    | 2  |    |    |    |    |    |    |      |    |    |          | $\vdash$                                         | _            |

|               | ETR        | 5  | <u> </u> |     |    |    | 2  |          |     |      |    |     |    |    |    |    | 2  |    |    |    |    | 0  |    |      |    |    |          |                                                  | $\vdash$     |

| ~             | Ch1        |    |          |     |    |    |    | 2        | 2   |      |    |     |    |    |    |    |    |    |    |    |    | 2  | 4  |      |    |    |          | <del>                                     </del> |              |

| TIM3          | Ch2<br>Ch3 |    |          |     |    |    |    |          | 2   |      |    |     |    |    |    |    |    | 2  |    |    |    |    | 4  |      |    |    |          |                                                  |              |

| , i           | Ch4        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    | 2  |    |    |    |    |      |    |    |          |                                                  |              |

|               | Ch1        |    | <u> </u> | 0   |    |    |    | <u> </u> |     |      |    |     |    |    |    |    |    |    | _  |    |    |    |    |      |    |    |          |                                                  | =            |

| TIM21         | Ch2        |    | 1        | -   | 0  |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| =             | ETR        |    | 5        |     | Ė  |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

| C.            | Ch1        |    |          |     |    |    |    | 5        |     |      |    |     |    |    |    |    |    |    |    |    |    | 4  |    |      |    |    |          |                                                  |              |

| TIM22         | Ch2        |    |          |     |    |    |    |          | 5   |      |    |     |    |    |    |    |    |    |    |    |    |    | 4  |      |    |    |          |                                                  |              |

| F             | ETR        |    |          |     |    | 5  |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |          |                                                  |              |

|               | IN1        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    | 2  |      |    |    |          |                                                  |              |

| M             | IN2        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    |      | 2  |    |          |                                                  |              |

| LPTIM1        | OUT        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    | 2  |    |    |    |      |    |    |          |                                                  |              |

|               | ETR        |    |          |     |    |    |    |          |     |      |    |     |    |    |    |    |    |    |    |    |    |    |    | 2    |    |    |          |                                                  |              |

| COMP<br>1     | IN         | М  | Р        |     | P* | М  | М  |          |     |      |    |     |    |    |    |    |    |    |    |    |    | P* | P* | P*   | P* |    |          |                                                  |              |

| 00            | OUT        | 7  | <u> </u> |     |    |    |    | 7        |     |      |    |     | 7  |    |    |    |    |    |    |    |    |    |    |      |    |    |          | igsquare                                         |              |

| COMP (2       | IN         | -  | <u> </u> | M   | Р  | М  | М  | ļ        |     |      |    |     |    |    |    |    |    |    |    |    | М  | Р  | Р  | Р    | Р  |    |          | igsquare                                         | Щ            |

| S             | OUT        |    | <u> </u> | 7   |    |    |    | <u> </u> | 7   |      |    |     |    | 7  |    |    |    |    |    |    |    |    |    |      |    |    |          | $oxed{oxed}$                                     | $\square$    |

| ADC_          | _IN        | 0  | 1        | 2   | 3  | 4  | 5  | 6        | 7   |      |    |     |    |    |    |    |    | 8  | 9  |    |    |    |    |      |    |    | <u> </u> | $oxed{oxed}$                                     | $\square$    |

| EVEN          | TUOTV      |    | 0        |     |    |    |    | 6        | 6   | 3    | _  |     | 2  | 2  |    |    | 3  | 0  |    |    | 4  |    |    |      |    |    | 2        | $oxed{igwedge}$                                  | $\mathbf{H}$ |

| IVICO         | _OUT<br>IO |    |          |     |    |    |    | -        | -   | 0    | 0  | -   |    |    | 0  |    |    |    |    |    |    |    |    |      |    |    | -        | $\vdash\vdash\vdash$                             | $\vdash$     |

| SWD           | CLK        |    | 1        |     |    |    |    |          |     |      |    |     |    |    | 0  | 0  |    |    |    |    |    |    |    |      |    |    |          |                                                  | $\vdash$     |

| 5,            | GLK        |    | l        |     |    |    | L  |          |     |      |    | l . |    |    |    | U  |    |    |    |    |    |    |    |      |    |    |          | ш                                                | ш            |

# 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the ZWIR4532 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 3. Absolute Maximum Ratings**

| Symbol                               | Parameter                                                                            | Minimum               | Maximum               | Units |

|--------------------------------------|--------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| Ts                                   | Storage temperature                                                                  | -50                   | 150                   | °C    |

| V <sub>ESD</sub>                     | ESD – Human Body Model                                                               | -                     | 2000                  | V     |

|                                      | ESD – Charged Device Model                                                           | -                     | 500                   |       |

| $V_{DD} - V_{SS}$                    | External supply voltage                                                              | -0.3                  | 3.6                   |       |

| V <sub>IN</sub>                      | Voltage on 5V tolerant input pin                                                     | V <sub>SS</sub> – 0.3 | V <sub>DD</sub> + 4.0 |       |

|                                      | Voltage on BSEL                                                                      | V <sub>SS</sub>       | V <sub>DD</sub> + 4.0 |       |

|                                      | Voltage on any other input pin                                                       | V <sub>SS</sub> – 0.3 | 4                     |       |

| V <sub>DDA</sub> - V <sub>DD</sub>   | Variation between V <sub>DDA</sub> and V <sub>DD</sub> power pins                    | -                     | 300                   | mV    |

| V <sub>REF+</sub> – V <sub>DDA</sub> | Allowed voltage difference for V <sub>REF+</sub> > V <sub>DDA</sub>                  | -                     | 400                   |       |

| lvdd                                 | Maximum total current consumption                                                    |                       | 140                   | mA    |

| I <sub>GPIO</sub>                    | Output current sunk by any I/O and control pin except FTf pins                       |                       | 16                    |       |

|                                      | Output current sunk by FTf pins                                                      |                       | 22                    |       |

|                                      | Output current sourced by any I/O and control pin                                    |                       | -16                   |       |

| ∑I <sub>GPIO</sub>                   | Total output current sunk by sum of all IOs and control pins except PA11 and PA12(2) |                       | 90                    |       |

|                                      | Total output current sunk by PA11 and PA12                                           |                       | 25                    |       |

|                                      | Total output current sourced by sum of all IOs and control pins(2)                   |                       | -90                   |       |

| I <sub>INJ</sub>                     | Injected current on FT, FFf, RST and B pins                                          |                       | -5 / +0               |       |

|                                      | Injected current on TC pin                                                           |                       | ±5                    |       |

| ΣI <sub>IN</sub> J                   | Total injected current (sum of all I/O and control pins)(5)                          |                       | ±25                   |       |

# 4. Recommended Operating Conditions

**Table 4. Recommended Operating Conditions**

| Parame                              | ter               | Symbol            | Minimum               | Typical | Maximum            | Units  |

|-------------------------------------|-------------------|-------------------|-----------------------|---------|--------------------|--------|

|                                     |                   | Electrical Charac | cteristics            |         |                    |        |

| Main supply voltage – ADC use       | ed                | $V_{DD}$          | 1.8                   |         | 3.6                | V      |

| Digital I/O high level input volta  | ige               | VIH               | 0.7V <sub>DD</sub>    |         |                    |        |

| Digital I/O low level input voltage | ge                | VIL               |                       |         | 0.3V <sub>DD</sub> |        |

| Digital I/O high level output volt  | tage              | Vон               | V <sub>DD</sub> - 0.4 |         |                    |        |

| Digital I/O low level output volta  | age               | V <sub>OL</sub>   |                       |         | 0.4                |        |

|                                     |                   | MCU Clock Chara   | octeristics           |         |                    |        |

| MCU core clock frequency 1)         | f <sub>АНВ</sub>  | 8                 |                       | 32      | MHz                |        |

| MCU core clock frequency acc        | uracy range       | $\Delta f_{AHB}$  | -2                    |         | 2.5                | %      |

| MCU peripheral bus 1 clock fre      | f <sub>APB1</sub> |                   | 4                     |         | N.41.1             |        |

| MCU peripheral bus 2 clock fre      | f <sub>APB2</sub> |                   | 8                     |         | MHz                |        |

|                                     |                   | RF Parame         | ters                  |         |                    |        |

| Frequency range                     | f <sub>RF</sub>   | 865               |                       | 928     | MHz                |        |

| Output power                        |                   |                   | -11                   |         |                    | dBm    |

| Output power tolerance              |                   |                   | -3                    |         | +3                 | dB     |

| Receiver sensitivity                | BPSK, EU Mode     |                   |                       | -110    |                    |        |

|                                     | BPSK, US Mode     |                   |                       | -108    |                    | dD     |

|                                     | QPSK, EU Mode     |                   |                       | -101    |                    | dBm    |

|                                     | QPSK, US Mode     |                   |                       | -101    |                    |        |

| Gross data rate                     | BPSK, EU Mode     |                   |                       | 20      |                    |        |

|                                     | BPSK, US Mode     |                   |                       | 40      |                    | I.D#/- |

|                                     | QPSK, EU Mode     |                   |                       | 100     |                    | kBit/s |

|                                     | QPSK, US Mode     |                   |                       | 250     |                    |        |

| Channel spacing                     | EU Mode           |                   |                       | 1       |                    | N.41.1 |

|                                     | US Mode           |                   |                       | 2       |                    | MHz    |

| Number of channels                  | EU Mode 3)        |                   |                       | 1 (+3)  |                    |        |

|                                     | US Mode           |                   |                       | 10      |                    |        |

| Input/output impedance              |                   |                   |                       | 50      |                    | Ω      |

| Frequency offset                    |                   |                   | -10                   |         | +10                | kHz    |

<sup>1)</sup> The  $f_{CORE}$  clock can be configured to be 8, 16 or 32 MHz. After reset, the clock is set to 8MHz.

<sup>2)</sup>  $f_{APB1}$  and  $f_{APB2}$  are derived from  $f_{AHB}$ . Therefore, the same tolerances apply to these clocks.

<sup>3)</sup> The IEEE802.15.4 standard defines only 1 channel for EU Mode, but extension channels are available in almost all EU countries.

#### 5. Functional Overview

The ZWIR4532 is a programmable wireless IPv6 communication module which can host the user application. This removes the need for an external application processor, consequently minimizing space requirements, BOM cost and the potential for communication errors. Applications benefit from the mesh networking functionality, which allows covering large areas with a single network, even if the communicating nodes have no direct radio link. The mesh network stack takes care of routing packets through the network transparently for the application. Routing failures are detected and repaired automatically, thus, a failing node will not impair the overall network.

ZWIR4532 modules communicate using the User Datagram Protocol (UDP) over IPv6 (Internet Protocol version 6). They are interoperable with ZWIR45xx based networks. ZWIR45xx networks operate autonomously or integrate with nearly any existing computer network or the Internet. If integrated in an existing network, ZWIR45xx based devices are accessible in the same way as any other IPv6 networking device. Opposed to many competing solutions gateway devices connecting ZWIR45xx, networks are application independent and do not limit the network functionality to a certain scope.

IDT provides a C-based Application Programming Interface (API) which is linked with the user application. Besides standard networking, different supplemental and advanced functionalities are provided using a modular approach. This allows tailoring the network stack to the applications requirements. The list of features below summarizes the functionalities provided by IDTs network stack components.

- UDP/IPv6 network layer

- Packet oriented communication with arbitrary number of communication partners

- Support for multicast communication (communication targeted at more than one receiver)

- Event based reception incoming packets are handled in dedicated user defined callbacks1

- Highly configurable mesh-layer

- Allows hundreds of nodes per network

- Works out of the box for simple networks; allows tailoring for complex networks

- IPSec based security

- Authentication and encryption

- Allows real end-to-end secure communication (ZWIR-to-ZWIR, ZWIR-to-LAN or ZWIR-to-Internet)

- Same technology as typically used in Virtual Private Networks (VPNs)

- Over-the-Air Updates

- Updates enabled simply by linking OTAU library into application

- Host library provided for easy update transmission from own applications

- Standalone graphical frontend for update transmission provided

- Network monitoring and administration protocol

- IDT protocol to analyze network topology and query device parameters and status

- Extended version allows remote configuration of devices

- Hardware abstraction libraries

- Different libraries providing a high level interfaces for the MCU hardware components

The prime design goal of the API has been ease of use. Detailed documentation of all network stack features can be found in the ZWIR45xx Programming Guide and the accompanying application notes.

The application firmware is executed on an ARM Cortex-M0+ 32 bit microcontroller (MCU). Applications have full access to the rich set of peripherals provided by this microcontroller. The list below summarizes the MCU features. Table 2 provides a detailed mapping of peripherals to GPIO pins.

- Internal RC or external crystal clock with up to 32MHz frequency

- 192kB of flash and 20kB of RAM memory approximately 128kB flash and 4kB RAM available for user applications

- Communication interfaces: 4x U(S)ART, 1x UART, 1x SPI, 3x I2C

- 4 timers with up to 12 PWM inputs/outputs

- 12-bit ADC (10 channels accessible), 2 comparators

- RTC and Watchdog timer

- 7-channel DMA controller

#### 5.1 Low Power Modes

The network stack provided for ZWIR4532 modules is designed to consume minimal power, even in active mode. If the module is idle in active operating mode, the MCU enters a low power mode to minimize its current consumption. All peripherals and the transceiver remain active and wake up the MCU from sleep mode as soon as an event occurs that needs to be serviced. Power consumption in active mode can be optimized further by adapting the clock frequency to the application needs.

For battery operated devices the ultra-low-power Suspend Mode is provided. In this mode the transceiver and most of the MCUs peripherals are turned off. The MCU core resides in the ARM Corex-M0 stop mode. The total power consumption is lowered to less than 1µA while all RAM contents and application state is retained. Wake-up from Suspend mode is possible through external GPIOs or the internal Real-Time-Clock.

### 5.2 Device Programming and Debugging

In system programming and debugging is supported through ARMs Serial Wire Debug (SWD) interface. SWD is a two wire interface designed as an alternative to the 4 wire JTAG interface. Figure 2 shows how SWD is connected to the ARM standard connectors. These connectors are supported by a wide variety of debug adaptors. Alternatively the microcontroller can be programmed using its embedded serial boot loader which allows programming through UART or SPI. However, no debugging functionality is available through this interface.

Figure 2. Serial Wire Debug Connection with Standard ARM Connectors

B) 10 Pin Cortex Debug Connector

# 6. Package Outline Drawing

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

www.idt.com/document/psc/zwir4532-package-outline-drawing-120-x-156-x-215-mm-body08mm-pitch-mod0

Figure 3. Package Outline Drawing (Top, Left and Bottom View)

Table 5. ZWIR4532 Physical Dimensions and Tolerances

| Symbol |         | Millimeters |         | Symbol            | Millimeters |         |         |  |

|--------|---------|-------------|---------|-------------------|-------------|---------|---------|--|

|        | Minimum | Typical     | Maximum |                   | Minimum     | Typical | Maximum |  |

| Α      | 2.4     | 2.5         | 2.6     | d1                |             | 2.0     |         |  |

| D      | 15.4    | 15.6        | 15.8    | d2                |             | 1.9     |         |  |

| Е      | 11.8    | 12.0        | 12.2    | g                 |             | 0.5     |         |  |

| W      |         | 0.8         |         | f <sub>x</sub> 1) |             | 10.2    |         |  |

| n      |         | 1           |         | f <sub>y</sub> 1) |             | 2.08    |         |  |

| b      |         |             | 0.3     | f <sub>r</sub>    |             | 0.25    |         |  |

Fiducial mark position is relative to center point of pad 1.

# 7. Soldering Information

To ensure that soldered connections do not break during the reflow soldering process of the application PCB, the soldering profile described in and Figure 4 must be maintained. This profile is aligned with the profile defined in the IPC/JEDEC standard J-STD-020D.

Table 6. Soldering Profile Parameters (according to J-STD-020D)

| Profile Feature                      | Symbol                           | Minimum | Maximum | Units |

|--------------------------------------|----------------------------------|---------|---------|-------|

| Time 25°C to T <sub>P</sub>          | t <sub>H</sub>                   |         | 8       | min   |

| Peak package body temperature        | T <sub>P</sub>                   |         | 260     | °C    |

| Preheat / Soak                       |                                  |         |         |       |

| Soak temperature                     | Ts                               | 100     | 150     | °C    |

| Soak time                            | ts                               | 60      | 120     | S     |

| Ramp-up                              |                                  |         |         |       |

| Ramp-up rate                         | T <sub>L</sub> to T <sub>P</sub> |         | 3       | °C/s  |

| Time maintained above T <sub>L</sub> | tL                               |         | 150     | S     |

| Time within 5°C of T <sub>P</sub>    | tp                               |         | 30      | S     |

| Ramp-down                            |                                  |         |         |       |

| Ramp-down rate                       | T <sub>P</sub> to T <sub>L</sub> |         | 6       | °C/s  |

Figure 4. Recommended Temperature Profile for Reflow Soldering (according to J-STD-020D)

#### 8. Certification

### 8.1 European RED Statement

The ZWIR4532 module has been tested and found to comply with the Radio Equipment Directive and is subject of a notified body opinion. The module has been approved for antennas with gains of 4 dBi or less. If the module should be used with antennas with higher gain, the modular approval is void and the end product must be fully certified.

Important Notice: End products targeted at geographic regions which are covered by the RED must ensure that a transmission duty cycle of less than 1% is maintained during normal operation. The duty cycle observation period is one hour. That means the cumulated transmission time of all transmissions during normal operation must not exceed 36 seconds when observed over one hour. IDTs network stack provides duty cycle monitoring and alarm mechanisms to support software developers in meeting the duty cycle requirements. For detailed information please refer to the ZWIR45xx Programming Guide.

#### 8.2 Federal Communication Commission Certification Statements

#### 8.2.1 Statements

This equipment has been tested and found to comply with the limits for a **Class B Digital Device**, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from where the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Modifications not expressly approved by ZMD AG could void the user's authority to operate the equipment.

The internal/external antennas used for this mobile transmitter must provide a separation distance of at least 20cm from all persons and must not be co-located or operating in conjunction with any other antenna or transmitter.

#### 8.2.2 Requirements

The ZWIR4532 complies with Part 15 of the FCC rules and regulations. In order to retain compliance with the FCC certification requirements, the following conditions must be met:

- 1. Modules must be installed by original equipment manufacturers (OEM) only.

- 2. The module must only be operated with antennas adhering to the requirements defined in section 8.2.3

- The OEM must place a clearly visible text label on the outside of the end-product containing the text shown in Figure 5, below.

**IMPORTANT:** The compliance statement as shown in Figure 5 must be used without modifications for the ZWIR4532 product.

#### Figure 5. FCC Compliance Statement to be Printed on Equipment Incorporating ZWIR4532 Devices

Contains FCC ID: COR-ZWIR4532

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

#### 8.2.3 Supported Antennas

The FCC compliance testing of the ZWIR4532 has been carried out using the MEXE902RPSM antenna from PCTEL Inc. This antenna has an omnidirectional radiation pattern at an antenna gain of 2 dBi. In order to be allowed to use the module without re-certification, the product incorporating the ZWIR4532 module must either use the antenna mentioned above or must use an antenna with an omnidirectional radiation pattern and a gain being less than or equal to 2 dBi.

### 9. Ordering Information

| Orderable Part Number | Description and Package                                                                                | Carrier Type | Temperature    |

|-----------------------|--------------------------------------------------------------------------------------------------------|--------------|----------------|

| ZWIR4532-U            | 6LoWPAN wireless radio module, unprogrammed 15.6 × 12 × 2.5 mm 43-LGA                                  | Tape/Reel    | -40°C to +85°C |

| ZWIR4532-S001         | 6LoWPAN wireless radio module, standard firmware $15.6 \times 12 \times 2.5 \text{ mm } 43\text{-LGA}$ | Tape/Reel    | -40°C to +85°C |

### 10. Revision History

| Revision Date   | Description of Change |

|-----------------|-----------------------|

| August 30, 2018 | Initial release.      |

Corporate Headquarters

6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775

www.IDT.com/go/sales

**Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="www.idt.com/go/glossary">www.idt.com/go/glossary</a>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

## **ZWIR4532 Package Outline Drawing**

12.0 x 15.6 x 2.15 mm Body,0.8mm Pitch MOD0, PSC-4747-01, Rev 00, Page 1

## **ZWIR4532 Package Outline Drawing**

12.0 x 15.6 x 2.15 mm Body,0.8mm Pitch MOD0, PSC-4747-01, Rev 00, Page 2

LAND PATTERN DIMENSION

NOTE:

1. ALL DIMENSIONS AND ANGLES IN MM.

|                                  | Package Revision History |                 |  |  |  |  |  |  |  |  |

|----------------------------------|--------------------------|-----------------|--|--|--|--|--|--|--|--|

| Date Created Rev No. Description |                          |                 |  |  |  |  |  |  |  |  |

|                                  |                          |                 |  |  |  |  |  |  |  |  |

| July 13, 2018                    | Rev 00                   | Initial Release |  |  |  |  |  |  |  |  |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Sub-GHz Modules category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

HMC-C024 nRF24L01P-MODULE-SMA CMD-KEY2-418-CRE V640-A90 SM1231E868 HMC-C582 SM-MN-00-HF-RC HMC-C031 LoRa Node Kit(US) Sierra HL7588 4G KIT(US) WISE-4610-S672NA EC21AUFA-MINIPCIE EC21EUGA-MINIPCIE CS-EASYSWITCH-25 EC21JFB-MINIPCIE DL-RFM96-433M Ra-07H-V1.1 Ra-07 Ra-01SH Ra-01S-T Ra-01SH-T CMD-HHCP-418-MD CMD-HHCP-433-MD CMD-HHLR-418-MD 2095000000200 XB9X-DMRS-031 20911051101 COM-13909 HMC-C033 COM-13910 WRL-14498 SX1276RF1KAS HMC-C011 HMC-C014 HMC-C050 HMC-C001 HMC-C006 HMC-C030 HMC-C021 HMC-C041 HMC-C042 HMC-C048 HMC-C051 HMC-C071 HMC-C072 HMC-C088 A2500R24C00GM 702-W HUM-900-PRC ISP4520-EU-ST