# 6V 1A, ACOT® Buck Converter in Thin SOT-563 Package

# **General Description**

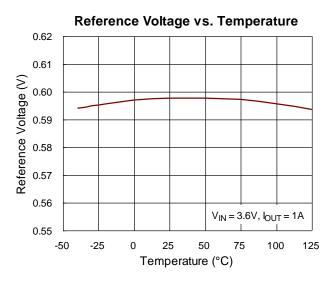

The RT5760A/B/C/D is a simple, easy-to-use, 1A synchronous step-down DC-DC converter with an input supply voltage range from 2.5V to 6V. The device build-in an accurate 0.6V reference voltage and integrates low R<sub>DS(ON)</sub> power MOSFETs to achieve high efficiency in a SOT-563 (FC) package.

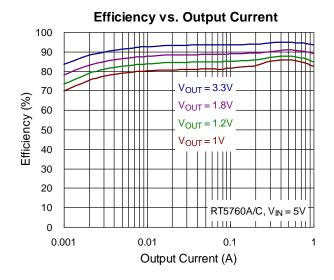

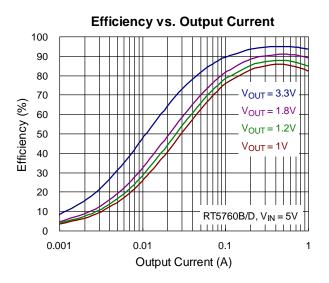

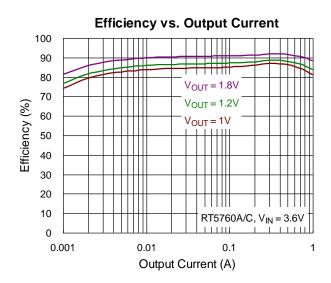

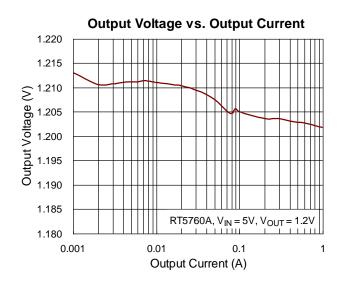

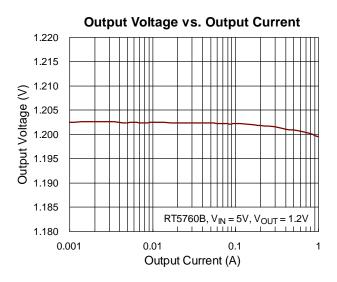

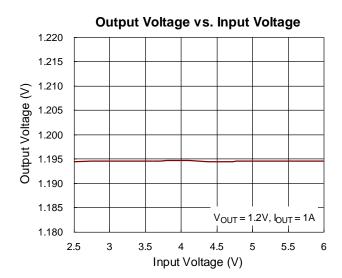

The RT5760A/B/C/D adopts Advanced Constant On-Time (ACOT®) control architecture to provide an ultrafast transient response with few external components and to operate in nearly constant switching frequency over the line, load, and output voltage range. The RT5760A/C operate in automatic PSM that maintain high efficiency during light load operation. The RT5760B/D operate in Forced PWM that help to meet tight voltage regulation accuracy requirements.

The RT5760A/B/C/D senses both FETs current for a robust over-current protection. The device features cycle-by-cycle current limit protection and prevent the device from the catastrophic damage in output short circuit, over current or inductor saturation. A built-in soft-start function prevents inrush current during start-up. The device also includes input under-voltage lockout, output under-voltage protection, and over-temperature protection to provide safe and smooth operation in all operating conditions.

# **Features**

- Input Voltage Range from 2.5V to 6V

- Integrated 120m $\Omega$  and 80m $\Omega$  FETs

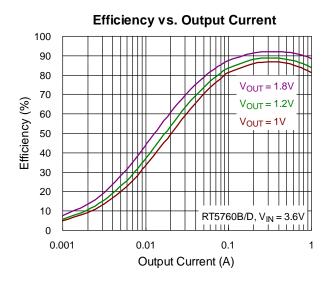

- 1A Output Current, up to 95% Efficiency

- 100% Duty Cycle for Lowest Dropout

- 1% Internal Reference Voltage

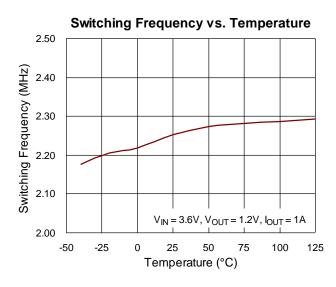

- 2.2MHz Typical Switching Frequency

- Power Saving Mode for Light Loads (RT5760A/C)

- Low Quiescent Current: 25µA (Typ.)

- Fast Advanced Constant On-Time (ACOT<sup>®</sup>)

Control

- Internal Soft Startup (0.6ms)

- Enable Control Input

- Power Good Indicator (RT5760A/B)

- Both FETs Over-Current Protection

- Negative Over-Current Protection (RT5760B/D)

- Input Under-Voltage Lockout Protection

- Hiccup-Mode Output Under-Voltage Protection

- Over-Temperature Protection

- RoHS Compliant and Halogen Free

# **Applications**

- Mobile Phones and Handheld Devices

- STB, Cable Modem, and xDSL Platforms

- WLAN ASIC Power / Storage (SSD and HDD)

- General Purpose for POL LV Buck Converter

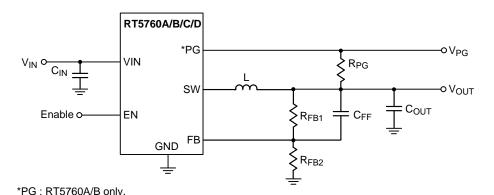

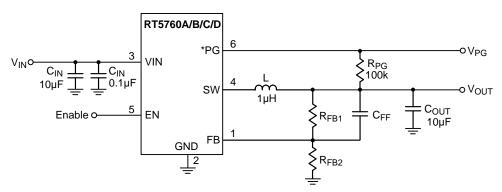

# **Simplified Application Circuit**

# **Ordering Information**

# RT5760 🗆 🗆 🗆 Package Type H6F: SOT-563 (FC) Lead Plating System G: Green (Halogen Free and Pb Free) **UVP** Option H: Hiccup **PWM Operation Mode** A: Automatic PSM B: Forced PWM C: Automatic PSM D: Forced PWM

### Note:

# Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# PG ΕN

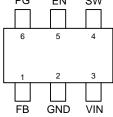

(TOP VIEW)

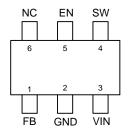

**Pin Configuration**

SOT-563 (FC) (RT5760A/B)

SOT-563 (FC) (RT5760C/D)

# **Marking Information**

### RT5760AHGH6F

03: Product Code W: Date Code

### RT5760BHGH6F

02: Product Code W: Date Code

# RT5760CHGH6F

0B: Product Code W : Date Code

# RT5760DHGH6F

0A : Product Code W: Date Code

# **Functional Pin Description**

| Pin No.   |           | Pin Name | Pin Function                                                                                                                                                                                                                                                       |  |  |

|-----------|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RT5760A/B | RT5760C/D | rin Name | Fill Fullction                                                                                                                                                                                                                                                     |  |  |

| 1         | 1         | FB       | Feedback voltage input. Connect this pin to the midpoint of the external feedback resistive divider to set the output voltage of the converter to the desired regulation level. The device regulates the FB voltage at Feedback Reference Voltage, typically 0.6V. |  |  |

| 2         | 2         | GND      | Signal and power ground pin. Place the bottom resistor of the feedback network as close as possible to this pin.                                                                                                                                                   |  |  |

| 3         | 3         | VIN      | Power input. The input voltage range is from 2.5V to 6V. Connect in capacitors directly to this pin and GND pins. MLCC with capacita higher than $10\mu F$ is recommended.                                                                                         |  |  |

| 4         | 4         | SW       | Switch node between the internal switch. Connect this pin to the inductor.                                                                                                                                                                                         |  |  |

| 5         | 5         | EN       | Enable control input. Connect this pin to logic high enables the device and connect this pin to GND disables the device. Do not leave this pin floating.                                                                                                           |  |  |

| 6         |           | PG       | Power good indicator. The output of this pin is an open-drain with external pull-up resistor. After soft startup, PG is pulled up when the FB voltage is within 90% (typ.). The PG status is low while EN is disable.                                              |  |  |

|           | 6         | NC       | No internal connection.                                                                                                                                                                                                                                            |  |  |

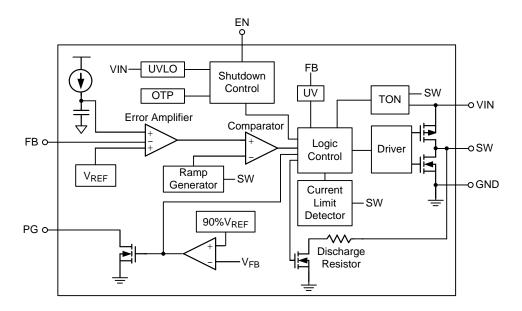

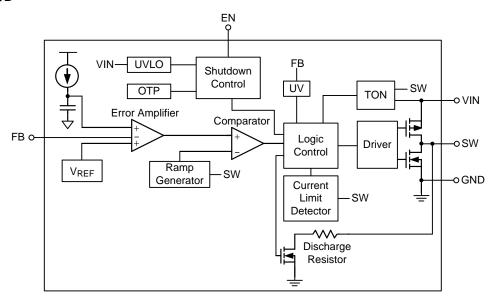

# **Functional Block Diagram**

# For RT5760A/B

# For RT5760C/D

# **Operation**

The RT5760A/B/C/D is a high-efficiency, synchronous step-down DC-DC converter that can deliver up to 1A output current from a 2.5V to 6V input supply.

# Advanced Constant On-Time Control and PWM Operation

The RT5760A/B/C/D adopts ACOT® control for its ultrafast transient response, low external component counts and stable with low ESR MLCC output capacitors. When the feedback voltage falls below the feedback reference voltage, the minimum off-time one-shot (80ns, typ.) has timed out and the inductor current is below the current limit threshold, then the internal on-time one-shot circuitry is triggered and the high-side switch is turn-on. Since the minimum off-time is short, the device exhibits ultrafast transient response and enables the use of smaller output capacitance.

The on-time is inversely proportional to input voltage and directly proportional to output voltage to achieve pseudo-fixed frequency over the input voltage range. After the on-time one-shot timer expired, the high-side switch is turn-off and the low-side switch is turn-on until the on-time one-shot is triggered again. In the steady state, the error amplifier compares the feedback voltage  $V_{FB}$  and an internal reference voltage. If the virtual inductor current ramp voltage is lower than the output of the error amplifier, a new pre-determined fixed on-time will be triggered by the on-time one-shot generator.

# Power Saving Mode (RT5760A/C)

The RT5760A/C automatically enters power saving mode (PSM) at light load to maintain high efficiency. As the load current decreases and eventually the inductor current ripple valley touches the zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The low-side switch is turned off when the zero inductor current is detected. As the load current is further decreased, it takes longer time to discharge the output capacitor to the level that requires the next on-time. The switching frequency decreases and is proportional to the load current to maintain high efficiency at light load.

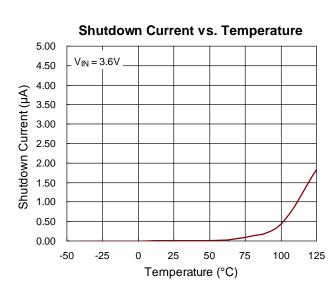

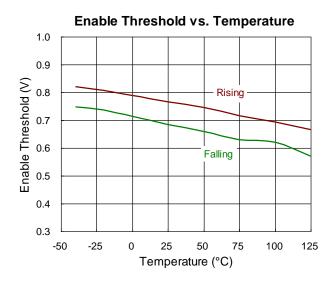

# **Enable Control**

The RT5760A/B/C/D provides an EN pin, as an external chip enable control, to enable or disable the device. If  $V_{EN}$  is held below a logic-low threshold voltage ( $V_{EN_L}$ ) of the enable input (EN), the converter will disable output voltage, that is, the converter is disabled and switching is inhibited even if the VIN voltage is above VIN under-voltage lockout threshold ( $V_{UVLO}$ ). During shutdown mode, the supply current can be reduced to  $I_{SHDN}$  ( $I_{\mu}A$  or below). If the EN voltage rises above the logic-high threshold voltage ( $V_{EN_H}$ ) while the VIN voltage is higher than UVLO threshold, the device will be turned on, that is, switching being enabled and soft-start sequence being initiated. Do not leave this pin floating.

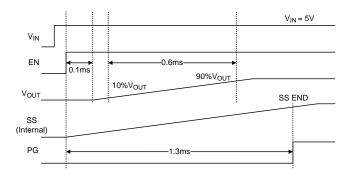

# Soft-Start (SS)

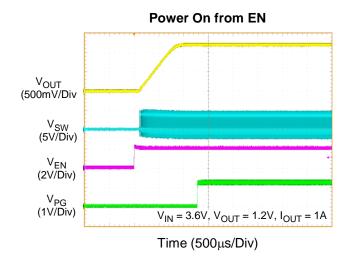

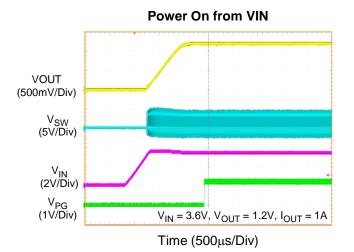

The RT5760A/B/C/D provides an internal soft-start feature for inrush control. At power up, the internal capacitor is charged by an internal current source to generate a soft-start ramp voltage as a reference voltage to the PWM comparator. The device will initiate switching and the output voltage will smoothly ramp up to its targeted regulation voltage only after this ramp voltage is greater than the feedback voltage V<sub>FB</sub> to ensure the converters have a smooth start-up from pre-biased output. The output voltage starts to rise in 0.1ms from EN rising, and the soft-start ramp-up time (10%V<sub>OUT</sub> to 90%V<sub>OUT</sub>) is 0.6ms.

Figure 1. Start-Up Sequence

# **Maximum Duty Cycle Operation**

The RT5760A/B/C/D is designed to operate in dropout at the high duty cycle approaching 100%. If the operational duty cycle is large and the required off time

becomes smaller than minimum off time, the RT5760A/B/C/D starts to enable skip off time function and keeps high-side MOSFET switch on continuously. The RT5760A/B/C/D implements skip off time function to achieve high duty approaching 100%. Therefore, the maximum output voltage is near the minimum input supply voltage of the application. The input voltage at which the devices enter dropout changes depending on the input voltage, output voltage, switching frequency, load current, and the efficiency of the design.

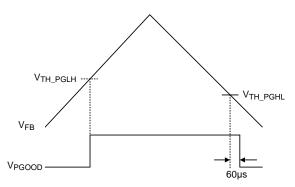

### Power Good Indication (RT5760A/B)

The RT5760A/B features an open-drain power-good output (PGOOD) to monitor the output voltage status. The output delay of comparator prevents false flag operation for short excursions in the output voltage, such as during line and load transients. Pull-up PGOOD with a resistor to VOUT or an external voltage below 6V. When VIN voltage rises above V<sub>UVLO</sub>, the power-good function is activated. After soft start is finished, the PGOOD pin is controlled by a comparator connected to the feedback signal VFB. If VFB rises above a power-good high threshold (V<sub>TH PGLH</sub>) (typically 90% of the reference voltage), the PGOOD pin will be in high impedance and V<sub>PG</sub> will be held high. When VFB falls short of power-good low threshold (V<sub>TH PGHL</sub>) (typically 85% of the reference voltage), the PGOOD pin will be pulled low after a certain delay (60µs, typically) elapsed. Once being started-up, if any internal protection is triggered, PGOOD will be pulled low to GND. The internal open-drain pull-down device  $(10\Omega, \text{ typically})$  will pull the PGOOD pin low. The power good indication profile is shown below.

Figure 2. The Logic of PGOOD

### Table 1. PG Pin Status

| C                                    | onditions                                                                       | PG Pin         |

|--------------------------------------|---------------------------------------------------------------------------------|----------------|

| Enable                               | V <sub>EN</sub> > V <sub>EN_H</sub> ,<br>V <sub>FB</sub> > V <sub>TH_PGLH</sub> | High Impedance |

|                                      | V <sub>EN</sub> > V <sub>EN_H</sub> ,<br>V <sub>FB</sub> < V <sub>TH_PGHL</sub> | Low            |

| Shutdown                             | V <sub>EN</sub> < V <sub>EN_L</sub>                                             | Low            |

| OTP T <sub>J</sub> > T <sub>SD</sub> |                                                                                 | Low            |

# **Input Under-Voltage Lockout**

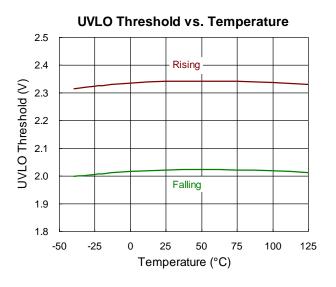

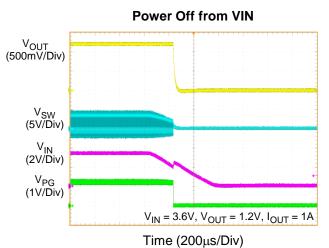

In addition to the EN pin, the RT5760A/B/C/D also provides enable control through the VIN pin. If V<sub>EN</sub> rises above V<sub>EN\_H</sub> first, switching will still be inhibited until the VIN voltage rises above V<sub>UVLO</sub>. It is to ensure that the internal regulator is ready so that operation with not-fully-enhanced internal MOSFET switches can be prevented. After the device is powered up, if the input voltage VIN goes below the UVLO falling threshold voltage (V<sub>UVLO</sub> –  $\Delta$ V<sub>UVLO</sub>), this switching will be inhibited; if VIN rises above the UVLO rising threshold (V<sub>UVLO</sub>), the device will resume normal operation with a complete soft-start.

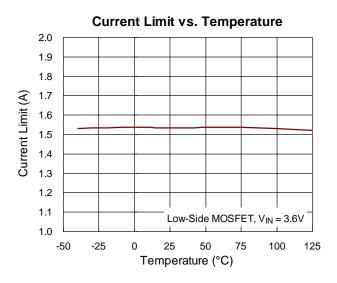

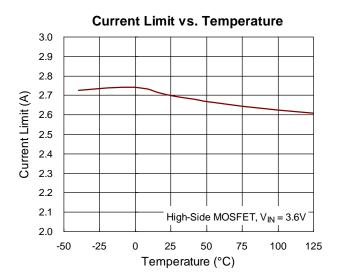

### The Over-Current Protection

The RT5760A/B/C/D features cycle-by-cycle current-limit protection on both the high-side and low-side MOSFETs and prevents the device from the catastrophic damage in output short circuit, over current or inductor saturation.

The high-side MOSFET over-current protection is achieved by an internal current comparator that monitors the current in the high-side MOSFET during each on-time. The switch current is compared with the high-side switch peak-current limit (I<sub>LIM\_H</sub>) after a certain amount of delay when the high-side switch being turned on each cycle. If an over-current condition occurs, the converter will immediately turns off the high-side switch and turns on the low-side switch to prevent the inductor current exceeding the high-side current limit.

The low-side MOSFET over-current protection is achieved by measuring the inductor current through the synchronous rectifier (low-side switch) during the low-side on-time. Once the current rises above the low-side switch valley current limit (I<sub>LIM\_L</sub>), the on-time one-shot will be inhibited until the inductor current

ramps down to the current limit level (I<sub>LIM\_L</sub>), that is, another on-time can only be triggered when the inductor current goes below the low-side current limit. If the output load current exceeds the available inductor current (clamped by the low-side current limit), the output capacitor needs to supply the extra current such that the output voltage will begin to drop. If it drops below the output under-voltage protection trip threshold, the IC will stop switching to avoid excessive heat.

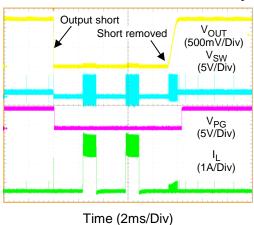

# Over-Current Protection VOUT (500mV/Div) VSW (5V/Div) VPG (5V/Div) IL (1A/Div)

Figure 3. Over-Current Protection

Time (50µs/Div)

# **Output Active Discharge**

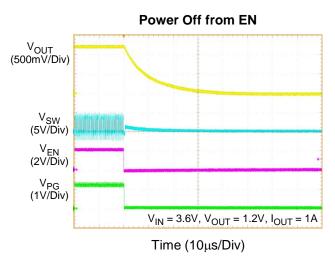

When the RT5760A/B/C/D is disabled by EN pin, UVLO or OTP, the device discharges the output capacitors (via SW pins) through an internal discharge resistor (150 $\Omega$ ) connected to ground. This function prevents the reverse current flow from the output capacitors to the input capacitors once the input voltage collapses. It doesn't need to rely on another active discharge circuit for discharging output capacitors. This function will be turned off when the fault condition is removed.

# **Hiccup-Mode Output Under-Voltage Protection**

The RT5760A/B/C/D includes output under-voltage protection (UVP) against over-load or short-circuited condition by constantly monitoring the feedback voltage VFB. If VFB drops below the under-voltage protection trip threshold (typically 50% of the internal feedback reference voltage), the UV comparator will go high to turn off both the internal high-side and low-side MOSFET switches. The RT5760A/B/C/D will enter

output under-voltage protection with hiccup mode. During hiccup mode, the IC will shut down for thiccup\_off (2.4ms), and then attempt to recover automatically for thiccup\_on (1.2ms). Upon completion of the soft-start sequence, if the fault condition is removed, the converter will resume normal operation; otherwise, such cycle for auto-recovery will be repeated until the fault condition is cleared. Hiccup mode allows the circuit to operate safely with low input current and power dissipation, and then resume normal operation as soon as the over-load or short-circuit condition is removed. A short circuit protection and recovery profile is shown below.

# **Short Circuit Protection and Recovery**

Figure 4. Short Circuit Protection and Recovery

### **Thermal Shutdown**

The RT5760A/B/C/D includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. The OTP will shut down switching operation when junction temperature exceeds a thermal shutdown threshold (TsD). Once the junction temperature cools down by a thermal shutdown hysteresis ( $\Delta T_{SD}$ ), the IC will resume normal operation with a complete soft-start.

Note that the over temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified operating absolute maximum junction temperature may impair device reliability

permanently damage the device.

# **Negative Over-Current Limit (RT5760B/D)**

The RT5760B/D is the part which is forced to PWM and allows negative current operation. In case of PWM operation, high negative current may be generated as an external power source which is tied to output terminal unexpectedly. As the risk described above, the internal circuit monitors negative current in each on-time interval of low-side MOSFET and compares it with NOC threshold. Once the negative current exceeds the NOC threshold, the low-side MOSFET is turned off immediately, and then the high-side MOSFET will be turned on to discharge the energy of output inductor. This behavior can keep the valley of negative current at NOC threshold to protect low-side MOSFET. However, the negative current can't be limited at NOC threshold anymore since minimum off-time is reached.

# **Absolute Maximum Ratings** (Note 1)

| Supply Input Voltage, VIN                                                   | 0.3V to 6.5V |

|-----------------------------------------------------------------------------|--------------|

| Switch Voltage, SW                                                          | 0.3V to 6.5V |

| < 50ns                                                                      | 2.5V to 9V   |

| • Other Pins                                                                | 0.3V to 6.5V |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |              |

| SOT-563 (FC)                                                                | 1W           |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C        |

| • Junction Temperature                                                      | 150°C        |

# **ESD Ratings**

ESD Susceptibility (Note 2)

HBM (Human Body Model) ------ 2kV

# **Recommended Operating Conditions** (Note 3)

| • | Supply Input Voltage | - 2.5V to 6V |

|---|----------------------|--------------|

|   | Output Voltage       | 0.01/40.1/   |

# **Thermal Information** (Note 4 and Note 5)

|                     | Thermal Parameter                                       | SOT-563 (FC) | Unit |

|---------------------|---------------------------------------------------------|--------------|------|

| θја                 | Junction-to-ambient thermal resistance (JEDEC standard) | 109.4        | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 7.3          | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 18.1         | °C/W |

| θJA(EVB)            | Junction-to-ambient thermal resistance (specific EVB)   | 100          | °C/W |

| ΨJC(Top)            | Junction-to-top characterization parameter              | 13           | °C/W |

# **Electrical Characteristics**

$(V_{IN} = 3.6V. T_J = T_A = -40^{\circ}C$  to 125°C. Typical value is tested at  $T_A = 25^{\circ}C$ . The limit over temperature is guaranteed by characterization, unless otherwise noted.)

| Parameter                                     | Symbol                 | Test Conditions                                                         | Min  | Тур  | Max      | Unit |

|-----------------------------------------------|------------------------|-------------------------------------------------------------------------|------|------|----------|------|

| Supply Voltage                                |                        | •                                                                       |      |      |          |      |

| VIN Supply Input Operating Voltage            | VIN                    |                                                                         | 2.5  |      | 6        | V    |

| Under-Voltage Lockout Threshold               | Vuvlo                  | V <sub>IN</sub> rising                                                  | 2.15 | 2.3  | 2.47     | V    |

| Under-Voltage Lockout Threshold<br>Hysteresis | ΔVυνιο                 |                                                                         |      | 300  |          | mV   |

| Shutdown Current                              | ISHDN                  | V <sub>EN</sub> = 0V, T <sub>A</sub> = 25°C                             |      | 0.3  | 1        | μΑ   |

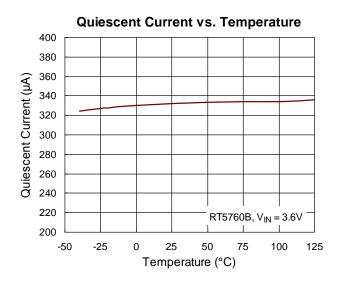

| Quiescent Current (RT5760A/C)                 | 1                      | V 0V V 0 00V                                                            |      | 25   | 35       | ۸    |

| Quiescent Current (RT5760B/D)                 | IQ                     | $V_{EN} = 2V, V_{FB} = 0.63V$                                           |      | 300  |          | μΑ   |

| Soft-Start                                    |                        | 1                                                                       |      | l    |          |      |

| Soft-Start Time                               | tss                    | 10%Vout to 90%Vout                                                      |      | 0.6  |          | ms   |

| Enable Voltage                                |                        | •                                                                       |      |      |          |      |

| Enable Voltage Threshold                      | V <sub>EN_H</sub>      | EN high-level input voltage                                             | 0.6  | 0.82 | 0.95     | V    |

| Enable voltage Threshold                      | V <sub>EN_L</sub>      | EN low-level input voltage                                              | 0.5  | 0.76 | 0.9      |      |

| Feedback Voltage and Discharge                | Resistance             | !                                                                       |      |      |          |      |

| Feedback Threshold Voltage                    | V <sub>FB</sub>        |                                                                         | 594  | 600  | 606      | mV   |

| Feedback Input Current                        | I <sub>FB</sub>        | VFB = 0.6V, TA = 25°C                                                   | -0.1 | 0    | 0.1      | μΑ   |

| Internal MOSFET                               |                        | •                                                                       |      |      |          |      |

| High-Side On-Resistance                       | R <sub>DS(ON)</sub> _H |                                                                         |      | 120  |          | 0    |

| Low-Side On-Resistance                        | R <sub>DS(ON)_L</sub>  |                                                                         |      | 80   |          | mΩ   |

| Current Limit                                 |                        |                                                                         | •    | •    |          |      |

| High-Side Switch Current Limit                | ILIM_H                 |                                                                         | 1.85 | 2.65 |          |      |

| Low-Side Switch Valley Current<br>Limit       | I <sub>LIM_L</sub>     | $V_{IN} = 3.6V, V_{OUT} = 1.2V$<br>L = 1 $\mu$ H, T <sub>A</sub> = 25°C | 1.05 | 1.55 | 2.05     | A    |

| Low-Side Switch Negative Valley Current Limit | I <sub>LIM_NL</sub>    |                                                                         |      | 1.5  |          |      |

| Switching Frequency                           |                        | 1                                                                       |      | l .  | I        |      |

| Switching Frequency                           | f <sub>SW</sub>        |                                                                         | 1.76 | 2.2  | 2.64     | MHz  |

| On-Time Timer Control                         |                        | 1                                                                       |      | I    |          |      |

| Minimum Off-Time                              | toff_MIN               |                                                                         |      | 80   |          | ns   |

| Hiccup-Mode Output Under-Volta                |                        | on                                                                      |      | l    |          |      |

| UVP Trip Threshold                            | V <sub>UVP</sub>       | Hiccup detect                                                           |      | 50   |          | %    |

| Thermal Shutdown                              | 1                      | '                                                                       |      | I    | <u> </u> | 1    |

| Thermal Shutdown Threshold                    | T <sub>SD</sub>        |                                                                         |      | 150  |          |      |

| Thermal Shutdown Hysteresis                   | $\Delta T_{SD}$        |                                                                         |      | 30   |          | °C   |

# RT5760A/B/C/D

| Parameter                     | Symbol    | Test Conditions                         | Min | Тур | Max | Unit |

|-------------------------------|-----------|-----------------------------------------|-----|-----|-----|------|

| Power Good                    |           |                                         |     |     |     |      |

| Power Good High Threshold     | VTH_PGLH  | VFB rising, PGOOD goes high             |     | 90  |     | %    |

| Power Good High Hysteresis    | ΔVTH_PGLH | V <sub>FB</sub> falling, PGOOD goes low |     | 5   |     | %    |

| Power Good Falling Delay Time |           |                                         |     | 60  |     | μS   |

| Output Discharge Resistor     |           |                                         |     |     |     |      |

| Output Discharge Resistor     |           |                                         |     | 150 |     | Ω    |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution is recommended.

- **Note 3.** The device is not guaranteed to function outside its operating conditions.

- Note 4. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

- Note 5.  $\theta_{JA(EVB)}$  and  $\Psi_{JC(TOP)}$  are measured on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

# **Typical Application Circuit**

\*PG: RT5760A/B only.

**Table 2. Suggested Component Values**

| V <sub>OUT</sub> (V) | R <sub>FB1</sub> ( <b>k</b> Ω) | $R_{FB2}$ ( $k\Omega$ ) | <b>L (</b> μ <b>H)</b> | C <sub>FF</sub> (pF) |

|----------------------|--------------------------------|-------------------------|------------------------|----------------------|

| 3.3                  | 45                             | 10                      | 1                      |                      |

| 1.8                  | 20                             | 10                      | 1                      |                      |

| 1.5                  | 15                             | 10                      | 1                      |                      |

| 1.2                  | 10                             | 10                      | 1                      |                      |

| 1.05                 | 7.5                            | 10                      | 1                      |                      |

| 1                    | 6.65                           | 10                      | 1                      |                      |

**Table 3. Recommended External Components**

| Component       | Description           | Vendor P/N                                             |  |  |  |

|-----------------|-----------------------|--------------------------------------------------------|--|--|--|

| C <sub>IN</sub> | 10μF, 6.3V, X5R, 0603 | 0603X106M6R3 (WALSIN)<br>GRM188R60J106ME84 (MURATA)    |  |  |  |

|                 |                       | 0603X106M6R3 (WALSIN)<br>GRM188R60J106ME84 (MURATA)    |  |  |  |

| L               | 1μΗ                   | DFE252010F-1R0M (MURATA)<br>HMLQ25201T-1R0MSR (CYNTEC) |  |  |  |

\*Cout : Considering the effective capacitance de-rated with biased voltage level and size, the Cout component needs satisfy the effective capacitance at least  $4\mu F$  for  $V_{OUT} = 3.3V$  and  $7\mu F$  for  $V_{OUT} < 3.3V$  for stable and normal operation.

# **Typical Operating Characteristic**

DS5760A/B/C/D-04 November 2020 www.richtek.com

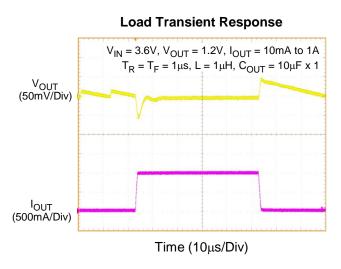

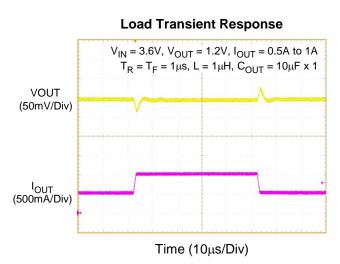

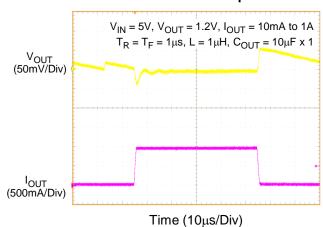

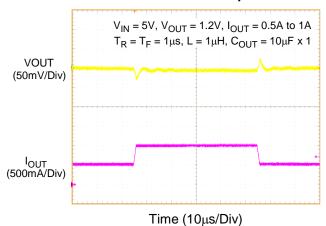

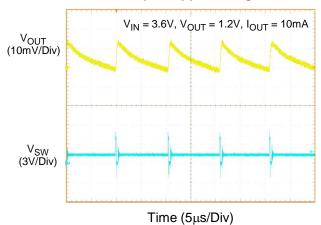

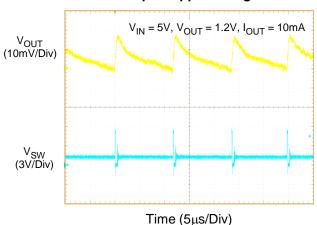

# **Load Transient Response**

### Load Transient Response

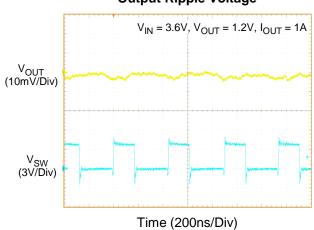

### **Output Ripple Voltage**

# **Output Ripple Voltage**

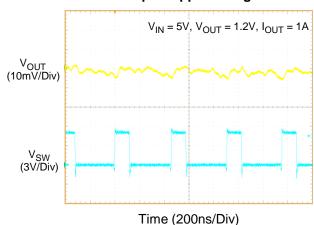

# **Output Ripple Voltage**

# **Output Ripple Voltage**

DS5760A/B/C/D-04 November 2020 www.richtek.com

# **Application Information**

The output stage of a synchronous buck converter is composed of an inductor and capacitor, which stores and delivers energy to the load, and forms a second-order low-pass filter to smooth out the switch node voltage to maintain a regulated output voltage.

### **Inductor Selection**

The inductor selection trade-offs among size, cost, efficiency, and transient response requirements. Generally, three key inductor parameters are specified for operation with the device: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (DCR).

A good compromise between size and loss is to choose the peak-to-peak ripple current equals to 20% to 50% of the IC rated current. The switching frequency, input voltage, output voltage, and selected inductor ripple current determines the inductor value as follows:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_{L}}$$

Once an inductor value is chosen, the ripple current  $(\Delta I_{\text{L}})$  is calculated to determine the required peak inductor current.

$$\Delta I_L = \frac{V_{OUT} \times \left(V_{IN} - V_{OUT}\right)}{V_{IN} \times f_{SW} \times L} \text{ and } I_{L(PEAK)} = I_{OUT(MAX)} + \frac{\Delta I_L}{2}$$

IL(PEAK) should not exceed the minimum value of IC's upper current limit level. Besides, the current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults or transient load conditions, the inductor current can increase above the calculated peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

Considering the Typical Application Circuit for 1.2V output at 1A and an input voltage of 5V, using an inductor ripple of 0.4A (40% of the IC rated current), the

calculated inductance value is:

$$L = \frac{1.2 \times (5 - 1.2)}{5 \times 2.2 MHz \times 0.4A} = 1 \mu H$$

For the typical application, a standard inductance value of  $1\mu H$  can be selected.

$$\Delta I_L = \frac{1.2 \times \left(5-1.2\right)}{5 \times 2.2 MHz \times 1 \mu H} = 0.41 \text{A (41\% of the IC rated current)}$$

and

$$I_{L(PEAK)} = 1A + \frac{0.41A}{2} = 1.205A$$

For the  $1\mu H$  value, the inductor's saturation and thermal rating should exceed at least 1.205A. For more conservative, the rating for inductor saturation current must be equal to or greater than switch current limit of the device rather than the inductor peak current.

For EMI sensitive application, choosing shielding type inductor is preferred.

# **Input Capacitor Selection**

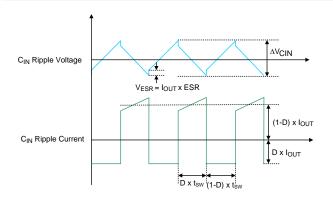

Input capacitance,  $C_{IN}$ , is needed to filter the pulsating current at the drain of the high-side power MOSFET.  $C_{IN}$  should be sized to do this without causing a large variation in input voltage. The waveform of  $C_{IN}$  ripple voltage and ripple current are shown in Figure 5. The peak-to-peak voltage ripple on input capacitor can be estimated as equation below:

$$\Delta V_{CIN} = D \times I_{OUT} \times \left(\frac{1 - D}{C_{IN} \times f_{SW}}\right) + I_{OUT} \times ESR$$

Where

$$D = \frac{V_{OUT}}{V_{IN} \times \eta}$$

For ceramic capacitors, the equivalent series resistance (ESR) is very low, the ripple which is caused by ESR can be ignored, and the minimum input capacitance can be estimated as equation below:

$$C_{\text{IN\_MIN}} = I_{\text{OUT\_MAX}} \times \frac{D(1-D)}{\Delta V_{\text{CIN\_MAX}} \times f_{\text{SW}}}$$

Where  $\Delta V_{CIN\ MAX} \leq 100 \text{mV}$

Figure 5.  $C_{\text{IN}}$  Ripple Voltage and Ripple Current In addition, the input capacitor needs to have a very low ESR and must be rated to handle the worst-case RMS input current of :

$$I_{RMS} \cong \ I_{OUT\_MAX} \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

It is commonly to use the worse  $I_{RMS} \cong I_{OUT}/2$  at  $V_{IN} = 2V_{OUT}$  for design. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to further de-rate the capacitor, or choose a capacitor rated at a higher temperature than required.

Several capacitors may also be paralleled to meet size, height and thermal requirements in the design. For low input voltage applications, sufficient bulk input capacitance is needed to minimize transient effects during output load changes.

Ceramic capacitors are ideal for switching regulator applications due to its small, robust and very low ESR. However, care must be taken when these capacitors are used at the input. A ceramic input capacitor combined with trace or cable inductance forms a high quality (under damped) tank circuit. If the RT5760A/B/C/D circuit is plugged into a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the device's rating. This situation is easily avoided by placing the low ESR ceramic input capacitor in parallel with a bulk capacitor with higher ESR to damp the voltage ringing.

The input capacitor should be placed as close as possible to the VIN pins, with a low inductance connection to the GND of the IC. In addition to a larger bulk capacitor, a small ceramic capacitors of  $0.1 \mu F$  should be placed close to the VIN and GND pin. This

capacitor should be 0402 or 0603 in size.

# **Output Capacitor Selection**

The RT5760A/B/C/D are optimized for ceramic output capacitors and best performance will be obtained using them. The total output capacitance value is usually determined by the desired output voltage ripple level and transient response requirements for sag (undershoot on load apply) and soar (overshoot on load release).

# **Output Ripple**

The output voltage ripple at the switching frequency is a function of the inductor current ripple going through the output capacitor's impedance. To derive the output voltage ripple, the output capacitor with capacitance,  $C_{OUT}$ , and its equivalent series resistance,  $R_{ESR}$ , must be taken into consideration. The output peak-to-peak ripple voltage  $V_{RIPPLE}$ , caused by the inductor current ripple  $\Delta I_L$ , is characterized by two components, which are ESR ripple  $V_{RIPPLE(ESR)}$  and capacitive ripple  $V_{RIPPLE(C)}$ , can be expressed as below:

$$\begin{split} &V_{RIPPLE} = V_{RIPPLE(ESR)} + V_{RIPPLE(C)} \\ &V_{RIPPLE(ESR)} = \Delta I_L \times R_{ESR} \\ &V_{RIPPLE(C)} = \frac{\Delta I_L}{8 \times C_{OUT} \times f_{SW}} \end{split}$$

If ceramic capacitors are used as the output capacitors, both the components need to be considered due to the extremely low ESR and relatively small capacitance.

For the RT5760A/B/C/D's Typical Application Circuit for output voltage of 1.2V, and actual inductor current ripple ( $\Delta I_L$ ) of 0.41A, taking a 10 $\mu$ F ceramic capacitors of GRM188R60J106ME84 from Murata as example, the output ripple of the output capacitor is as below :

The ripple caused by the ESR of about  $5m\Omega$  can be calculated as

$$V_{RIPPLE(ESR)} = 0.41A \times 5m\Omega = 2.05mV$$

Due to DC bias capacitance degrading, the effective capacitance at output voltage of 1.2V is about  $8\mu F$

$$V_{RIPPLE(C)} = \frac{0.41A}{8 \times 8 \mu F \times 2.2 MHz} = 2.91 mV$$

$V_{RIPPLE} = 2.05 mV + 2.91 mV = 4.96 mV$

# **Output Transient Undershoot and Overshoot**

In addition to voltage ripple at the switching frequency, the output capacitor and its ESR also affect the voltage sag (undershoot) and soar (overshoot) when the load steps up and down abruptly. The ACOT<sup>®</sup> transient response is very quick and output transients are usually small. The following section shows how to calculate the worst-case voltage swings in response to very fast load steps.

The output voltage transient undershoot and overshoot each have two components: the voltage steps caused by the output capacitor's ESR, and the voltage sag and soar due to the finite output capacitance and the inductor current slew rate. Use the following formulas to check if the ESR is low enough (typically not a problem with ceramic capacitors) and the output capacitance is large enough to prevent excessive sag and soar on very fast load step edges, with the chosen inductor value.

The amplitude of the ESR step up or down is a function of the load step and the ESR of the output capacitor :

VESR STEP =

$$\Delta I_{OUT} \times R_{ESR}$$

The amplitude of the capacitive sag is a function of the load step, the output capacitor value, the inductor value, the input-to-output voltage differential, and the maximum duty cycle. The maximum duty cycle during a fast transient is a function of the on-time and the minimum off-time since the ACOT® control scheme will ramp the current using on-times spaced apart with minimum off-times, which is as fast as allowed. Calculate the approximate on-time (neglecting parasites) and maximum duty cycle for a given input and output voltage as:

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \times f_{SW}} \text{ and } D_{MAX} = \frac{t_{ON}}{t_{ON} + t_{OFF\_MIN}}$$

The actual on-time will be slightly longer as the IC compensates for voltage drops in the circuit, but we can neglect both of these since the on-time increase compensates for the voltage losses. Calculate the output voltage sag as:

$$V_{SAG} = \frac{L \times (\Delta I_{OUT})^2}{2 \times C_{OUT} \times (V_{IN(MIN)} \times D_{MAX} - V_{OUT})}$$

The amplitude of the capacitive soar is a function of the

load step, the output capacitor value, the inductor value and the output voltage:

$$V_{SOAR} = \frac{L \times (\Delta I_{OUT})^2}{2 \times C_{OUT} \times V_{OUT}}$$

Due to some modern digital loads can exhibit nearly instantaneous load changes, the amplitude of the ESR step up or down should be taken into consideration.

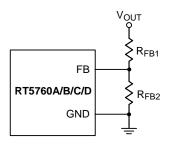

# **Output Voltage Setting**

Set the desired output voltage using a resistive divider from the output to ground with the midpoint connected to FB, as shown in Figure 6. The output voltage is set according to the following equation:

$$V_{OUT} = 0.6V \times (1 + R_{FB1} / R_{FB2})$$

Figure 6. Output Voltage Setting

Place the FB resistors within 5mm of the FB pin. For output voltage accuracy, use divider resistors with 1% or better tolerance.

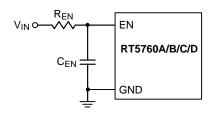

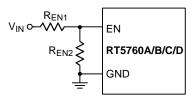

### **EN Pin for Start-Up and Shutdown Operation**

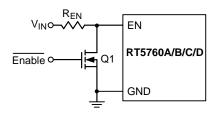

For automatic start-up, the EN pin can be connected to the input supply  $V_{IN}$  directly. The large built-in hysteresis band makes the EN pin useful for simple delay and timing circuits. The EN pin can be externally connected to  $V_{IN}$  by adding a resistor  $R_{EN}$  and a capacitor  $C_{EN}$ , as shown in Figure 7, to have an additional delay. The time delay can be calculated with the EN's internal threshold, at which switching operation begins (typically 0.82V).

An external MOSFET can be added for the EN pin to be logic-controlled, as shown in Figure 8. In this case, a pull-up resistor,  $R_{EN}$ , is connected between VIN and the EN pin. The MOSFET Q1 will be under logic control to pull down the EN pin. To prevent the device being enabled when VIN is smaller than the VOUT target level or some other desired voltage level, a resistive divider ( $R_{EN1}$  and  $R_{EN2}$ ) can be used to externally set

the input under-voltage lockout threshold, as shown in Figure 9.

Figure 7. Enable Timing Control

Figure 8. Logic Control for the EN Pin

Figure 9. Resistive Divider for Under-Voltage Lockout

Threshold Setting

# **Power-Good Output**

The PGOOD pin is an open-drain power-good indication output and is to be connected to an external voltage source through a pull-up resistor.

The external voltage source can be an external voltage supply below 6V, V<sub>CC</sub> or the output of the RT5760A/B/C/D if the output voltage is regulated under 6V. It is recommended to connect a  $100k\Omega$  between external voltage source to PGOOD pin.

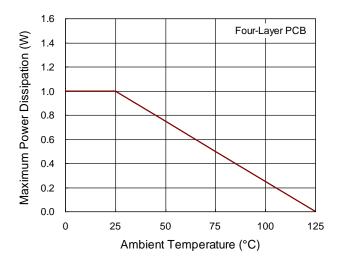

### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a SOT-563 (FC) package, the thermal resistance,  $\theta_{JA}$ , is 100°C/W on a high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A=25^\circ\text{C}$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (100^{\circ}CW) = 1W$  for a SOT-563 (FC) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 10 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 10. Derating Curve of Maximum Power

Dissipation

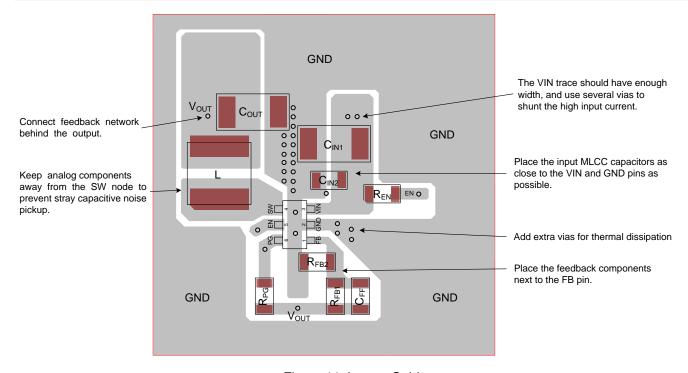

# **Layout Considerations**

Follow the PCB layout guidelines for optimal performance of the device.

► Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable, jitter-free operation. The high current path comprising of input capacitor, high-side FET, inductor, and the output capacitor should be as short

# RT5760A/B/C/D

as possible. This practice is essential for high efficiency.

- ▶ Place the input MLCC capacitors as close to the VIN and GND pins as possible. The major MLCC capacitors should be placed on the same layer as the RT5760A/B/C/D.

- ▶ SW node is with high frequency voltage swing and should be kept at small area. Keep analog components away from the SW node to prevent stray capacitive noise pickup.

- ► Connect feedback network behind the output capacitors. Place the feedback components next to the FB pin.

- ► For better thermal performance, to design a wide and thick plane for GND pin or to add a lot of vias to GND plane.

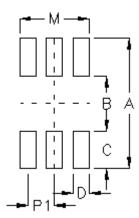

An example of PCB layout guide is shown from Figure 11.

Figure 11. Layout Guide

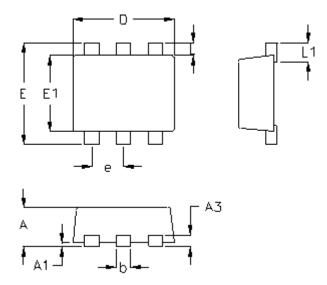

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| Α      | 0.500        | 0.600         | 0.020                | 0.024 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| А3     | 0.080        | 0.180         | 0.003                | 0.007 |  |

| b      | 0.150        | 0.300         | 0.006                | 0.012 |  |

| D      | 1.500        | 1.700         | 0.059                | 0.067 |  |

| E      | 1.500        | 1.700         | 0.059                | 0.067 |  |

| E1     | 1.100        | 1.300         | 0.043                | 0.051 |  |

| е      | 0.5          | 500           | 0.0                  | )20   |  |

| L      | 0.100        | 0.300         | 0.004                | 0.012 |  |

| L1     | 0.200        | 0.400         | 0.008                | 0.016 |  |

SOT-563 (FC) Surface Mount Package

# **Footprint Information**

| Dookogo     | Number of | Footprint Dimension (mm) |      |      |      |      | Toloropoo |           |

|-------------|-----------|--------------------------|------|------|------|------|-----------|-----------|

| Package     | Pin       | P1                       | Α    | В    | С    | D    | М         | Tolerance |

| SOT-563(FC) | 6         | 0.50                     | 2.42 | 1.02 | 0.70 | 0.30 | 1.30      | ±0.10     |

# Richtek Technology Corporation

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2020 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS5760A/B/C/D-04 November 2020 www.richtek.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Richtek manufacturer:

Other Similar products are found below:

NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG

NCP81205MNTXG SJE6600 AZ7500BMTR-E1 IR35215MTRPBF SG3845DM NCP4204MNTXG NCP6132AMNR2G

NCP81102MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C IR35201MTRPBF FSL4110LRLX

NCP1015ST65T3G NCP1240AD065R2G NCP1240FD065R2G NCP1336BDR2G NCP1361BABAYSNT1G NCP1230P100G

NX2124CSTR SG2845M NCP1366BABAYDR2G NCP81101MNTXG TEA19362T/IJ NCP81174NMNTXG NCP4308DMTTWG

NCP4308DMNTWG NCP4308AMTTWG NCP1366AABAYDR2G NCP1256ASN65T1G NCP1251FSN65T1G NCP1246BLD065R2G

MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G

IR35204MTRPBF MCP1633T-E/MG MCP1633-E/MG NCV1397ADR2G NCP81599MNTXG NCP1246ALD065R2G