# High Voltage Synchronous Rectified Buck MOSFET Driver for Notebook Computer

### **General Description**

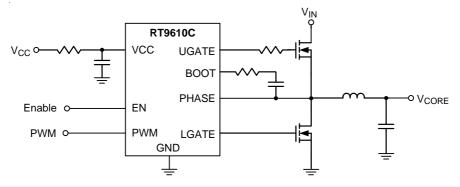

The RT9610C is a high frequency, dual MOSFET driver specifically designed to drive two power N-MOSFETS in a synchronous-rectified buck converter topology. It is especially suited for mobile computing applications that require high efficiency and excellent thermal performance. This driver, combined with Richtek's series of multi-phase Buck PWM controllers, provides a complete core voltage regulator solution for advanced microprocessors.

The drivers are capable of driving a 3nF load with fast rising/falling time and fast propagation delay. This device implements bootstrapping on the upper gates with only a single external capacitor. This reduces implementation complexity and allows the use of higher performance, cost effective, N-MOSFETs. Adaptive shoot through protection is integrated to prevent both MOSFETs from conducting simultaneously.

The RT9610C is available in WDFN-8L 2x2 Package.

# **Marking Information**

2Q : Product Code W : Date Code

### **Features**

- Drives Two N-MOSFETs

- Adaptive Shoot-Through Protection

- 0.5Ω On-Resistance, 4A Sink Current Capability

- Supports High Switching Frequency

- Tri-State PWM Input for Power Stage Shutdown

- Output Disable Function

- Integrated Boost Switch

- Low Bias Supply Current

- VCC POR Feature Integrated

### **Applications**

- Core Voltage Supplies for Intel<sup>®</sup> / AMD<sup>®</sup> Mobile Microprocessors

- High Frequency Low Profile DC/DC Converters

- High Current Low Output Voltage DC/DC Converters

- High Input Voltage DC/DC Converters

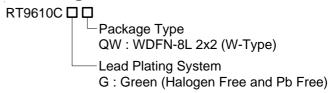

# **Ordering Information**

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- → Suitable for use in SnPb or Pb-free soldering processes.

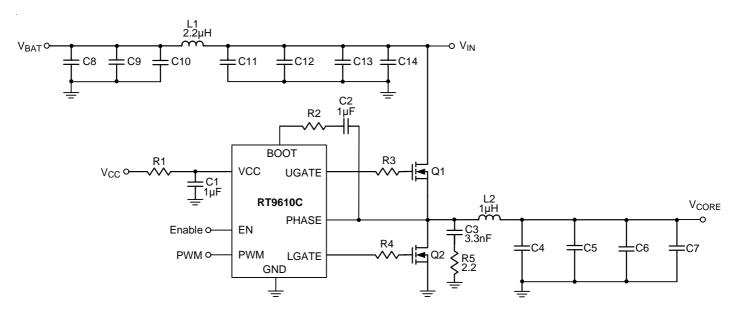

# **Simplified Application Circuit**

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

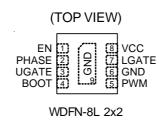

# **Pin Configurations**

# **Functional Pin Description**

| Pin No.               | Pin Name | Pin Function                                                                                                                                                                                     |

|-----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | EN       | Enable Pin. When low, both UGATE and LGATE are driven low and the normal operation is disabled.                                                                                                  |

| 2                     | PHASE    | Switch Node. Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin provides a return path for the upper gate driver.                                    |

| 3                     | UGATE    | Upper Gate Drive Output. Connect to the gate of high side power N-MOSFET.                                                                                                                        |

| 4                     | воот     | Floating Bootstrap Supply Pin for Upper Gate Drive. Connect the bootstrap capacitor between this pin and the PHASE pin. The bootstrap capacitor provides the charge to turn on the upper MOSFET. |

| 5                     | PWM      | Control Input for Driver. The PWM signal can enter three distinct states during operation. Connect this pin to the PWM output of the controller.                                                 |

| 6,<br>9 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                      |

| 7                     | LGATE    | Lower Gate Drive Output. Connect to the gate of the low side power N-MOSFET.                                                                                                                     |

| 8                     | VCC      | Input Supply Pin. Connect this pin to a 5V bias supply. Place a high quality bypass capacitor from this pin to GND.                                                                              |

www.richtek.com

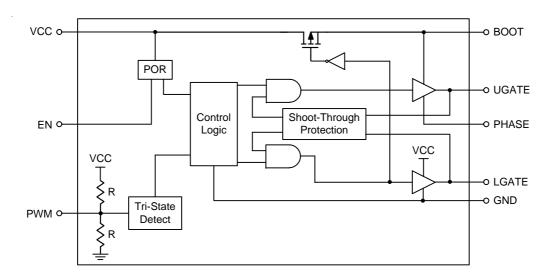

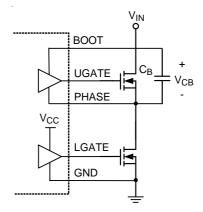

# **Functional Block Diagram**

### **Operation**

### POR (Power On Reset)

POR block detects the voltage at the VCC pin. When the VCC pin voltage is higher than POR rising threshold, the POR pin output voltage (POR output) is high. POR output is low when VCC is not higher than POR rising threshold. When the POR pin voltage is high, UGATE and LGATE can be controlled by PWM input voltage. If the POR pin voltage is low, both UGATE and LGATE will be pulled to low.

#### **Tri-State Detect**

When both POR output and EN pin voltages are high, UGATE and LGATE can be controlled by PWM input. There are three PWM input modes which are high, low, and shutdown state. If PWM input is within the shutdown window, both UGATE and LGATE outputs are low. When PWM input is higher than its rising threshold, UGATE is high and LGATE is low. When PWM input is lower than its falling threshold, UGATE is low and LGATE is high.

### **Control Logic**

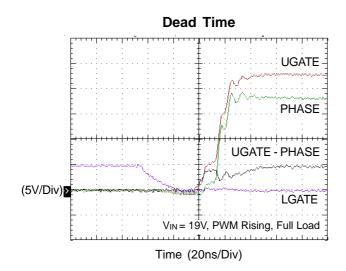

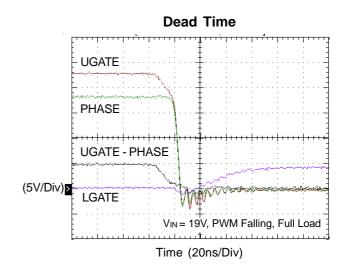

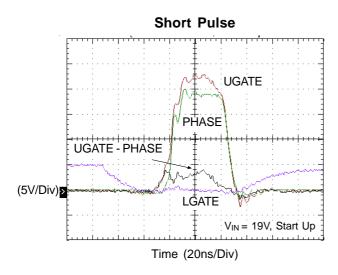

Control logic block detects whether high side MOSFET is turned off by monitoring (UGATE - PHASE) voltages below 1.1V or PHASE voltage below 2V. To prevent the overlap of the gate drives during the UGATE pulls low and the LGATE pulls high, low side MOSFET can be turned on only after high side MOSFET is effectively turned off.

### **Shoot-Through Protection**

Shoot-through protection block implements the dead-time when both high side and low side MOSFETs are turned off. With shoot-through protection block, high side and low side MOSFETs are never turned on simultaneously. Thus, shoot-through between high side and low side MOSFETs is prevented.

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| <b>Absolute Maximum</b> | Ratings | (Note 1) |

|-------------------------|---------|----------|

|-------------------------|---------|----------|

| Supply Voltage, VCC                                                         |          |

|-----------------------------------------------------------------------------|----------|

| BOOT to PHASE                                                               |          |

| PHASE to GND                                                                |          |

| DC                                                                          |          |

| < 20ns                                                                      |          |

| UGATE to PHASE                                                              |          |

| DC                                                                          |          |

| < 20ns                                                                      |          |

| LGATE to GND                                                                |          |

| DC                                                                          |          |

| < 20ns                                                                      |          |

| • PWM, EN to GND                                                            |          |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |          |

| WDFN-8L 2x2                                                                 | 2.19W    |

| Package Thermal Resistance (Note 2)                                         |          |

| WDFN-8L 2x2, $\theta_{JA}$                                                  | 45.5°C/W |

| WDFN-8L 2x2, $\theta_{\text{JC}}$                                           | 11.5°C/W |

| • Junction Temperature                                                      | 150°C    |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C    |

| Storage Temperature Range                                                   |          |

| ESD Susceptibility (Note 3)                                                 |          |

| HBM (Human Body Model)                                                      | 2kV      |

|                                                                             |          |

| Recommended Operating Conditions (Note 4)                                   |          |

# Recommended Operating Conditions (Note 4)

| • Input Voltage, VIN       | 4.5V to 26V    |

|----------------------------|----------------|

| Control Voltage, VCC       | 4.5V to 5.5V   |

| Ambient Temperature Range  |                |

| Junction Temperature Range | –40°C to 125°C |

# **Electrical Characteristics**

( $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                           | Symbol              | Test Conditions                            | Min | Тур  | Max | Unit |  |  |

|-------------------------------------|---------------------|--------------------------------------------|-----|------|-----|------|--|--|

| VCC Supply Current                  |                     |                                            |     |      |     |      |  |  |

| Quiescent Current                   | IQ                  | PWM Pin Floating, V <sub>EN</sub> = 3.3V   |     | 80   |     | μΑ   |  |  |

| Shutdown Current                    | I <sub>SHDN</sub>   | $V_{EN} = 0V$ , $PWM = 0V$ , $V_{CC} = 5V$ |     | 0    | 5   | μΑ   |  |  |

|                                     | $V_{PORH}$          | VCC POR Rising                             |     | 4.2  | 4.5 | V    |  |  |

| VCC Power On Reset (POR)            | V <sub>PORL</sub>   | VCC POR Falling                            | 3.5 | 3.84 |     | V    |  |  |

|                                     | V <sub>PORHYS</sub> | Hysteresis                                 |     | 360  |     | mV   |  |  |

| Internal BOOT Switch                |                     |                                            |     |      |     |      |  |  |

| Internal Boost Switch On Resistance | R <sub>BOOT</sub>   | VCC to BOOT, 10mA                          |     |      | 80  | Ω    |  |  |

| Parameter                                  |                | Symbol               | Test Conditions                        | Min | Тур  | Max  | Unit |  |

|--------------------------------------------|----------------|----------------------|----------------------------------------|-----|------|------|------|--|

| PWM Input                                  |                |                      |                                        |     |      |      |      |  |

| land Comment                               |                |                      | $V_{PWM} = 5V$                         |     | 174  |      |      |  |

| Input Current                              |                | IPWM                 | V <sub>PWM</sub> = 0V                  | -   | -174 | 1    | μΑ   |  |

| PWM Tri-State Rising Threshold             |                | V <sub>PWMH</sub>    | V <sub>CC</sub> = 5V                   | 3.5 | 3.8  | 4.1  | ٧    |  |

| PWM Tri-State Falling                      | g Threshold    | V <sub>PWML</sub>    | V <sub>CC</sub> = 5V                   | 0.7 | 1    | 1.3  | V    |  |

| EN Input                                   |                | •                    |                                        |     |      |      |      |  |

| EN hans it Voltage                         | Logic-High     | V <sub>ENH</sub>     | V <sub>CC</sub> = 5V                   | 1.4 |      |      | ,,   |  |

| EN Input Voltage                           | Logic-Low      | V <sub>ENL</sub>     | V <sub>CC</sub> = 5V                   |     |      | 0.48 | V    |  |

| Switching Time                             |                | •                    |                                        |     | ļ.   |      |      |  |

| UGATE Rise Time                            |                | tugater              | V <sub>CC</sub> = 5V, 3nF Load         |     | 8    |      | ns   |  |

| UGATE Fall Time                            |                | tugatef              | Vcc = 5V, 3nF Load                     | -   | 8    | 1    | ns   |  |

| LGATE Rise Time                            |                | tLGATEr              | Vcc = 5V, 3nF Load                     | -   | 8    | 1    | ns   |  |

| LGATE Fall Time                            |                | tLGATEf              | Vcc = 5V, 3nF Load                     |     | 4    |      | ns   |  |

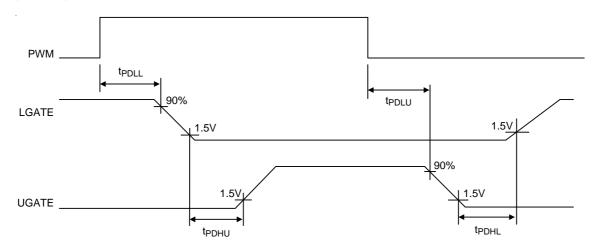

| UGATE Turn-Off Pro                         | pagation Delay | t <sub>PDLU</sub>    | V <sub>CC</sub> = 5V, Outputs Unloaded |     | 35   | -    | ns   |  |

| LGATE Turn-Off Prop                        | pagation Delay | t <sub>PDLL</sub>    | V <sub>CC</sub> = 5V, Outputs Unloaded |     | 35   |      | ns   |  |

| UGATE Turn-On Pro                          | pagation Delay | tPDHU                | V <sub>CC</sub> = 5V, Outputs Unloaded |     | 20   | -    | ns   |  |

| LGATE Turn-On Prop                         | pagation Delay | tPDHL                | V <sub>CC</sub> = 5V, Outputs Unloaded |     | 20   |      | ns   |  |

| UGATE/LGATE Tri-State<br>Propagation Delay |                | tpts                 | Vcc = 5V, Outputs Unloaded             |     | 35   | 1    | ns   |  |

| Output                                     |                |                      |                                        |     |      |      |      |  |

| UGATE Driver Source Resistance             |                | RUGATEsr             | 100mA Source Current                   | -   | 1    | I    | Ω    |  |

| UGATE Driver Source Current                |                | lugatesr             | VUGATE - VPHASE = 2.5V                 |     | 2    | 1    | Α    |  |

| UGATE Driver Sink Resistance               |                | RUGATEsk             | Esk 100mA Sink Current                 |     | 1    | 1    | Ω    |  |

| UGATE Driver Sink Current                  |                | lugatesk             | Vugate – Vphase = 2.5V                 |     | 2    |      | Α    |  |

| LGATE Driver Source Resistance             |                | RLGATEsr             | 100mA Source Current                   | -   | 1    | 1    | Ω    |  |

| LGATE Driver Source Current                |                | ILGATEsr             | VLGATE = 2.5V                          | 1   | 2    | ı    | Α    |  |

| LGATE Driver Sink Resistance               |                | RLGATEsk             | 100mA Sink Current                     |     | 0.5  |      | Ω    |  |

| LGATE Driver Sink Current                  |                | I <sub>LGATEsk</sub> | V <sub>LGATE</sub> = 2.5V              |     | 4    |      | Α    |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- **Note 3.** Devices are ESD sensitive. Handling precaution recommended. The human body mode is a 100pF capacitor is charged through a  $1.5k\Omega$  resistor into each pin.

- Note 4. The device is not guaranteed to function outside its operating conditions.

Copyright © 2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

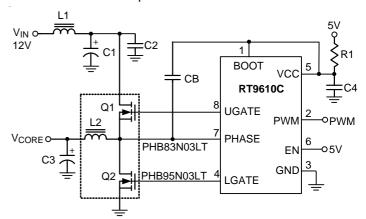

# **Typical Application Circuit**

# **Timing Diagram**

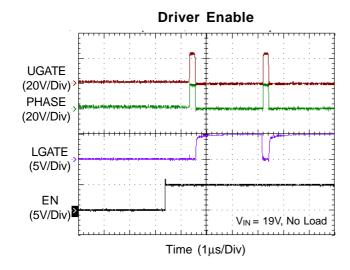

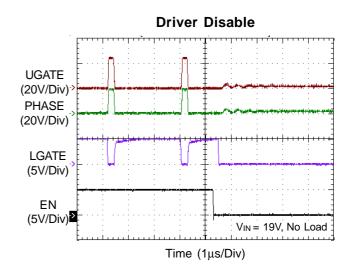

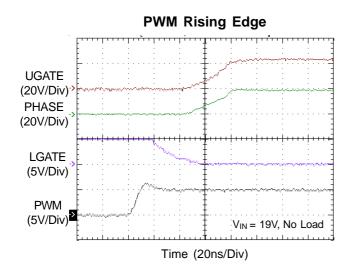

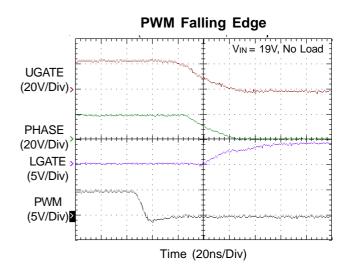

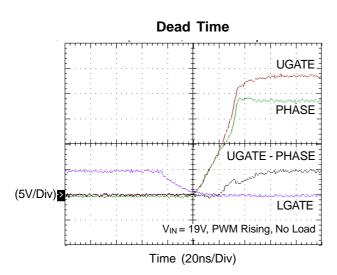

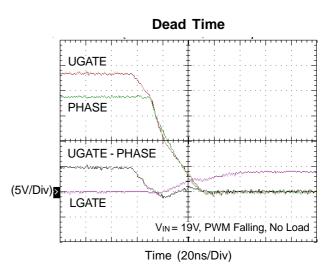

# **Typical Operating Characteristics**

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Application Information**

### Supply Voltage and Power On Reset

The RT9610C is designed to drive both high side and low side N-MOSFETs through an externally input PWM control signal. Connect 5V to VCC to power on the RT9610C. A minimum  $1\mu F$  ceramic capacitor is recommended to bypass the supply voltage. Place the bypassing capacitor physically near the IC. The power on reset (POR) circuit monitors the supply voltage at the VCC pin. If VCC exceeds the POR rising threshold voltage, the controller resets and prepares for operation. UGATE and LGATE are held low before VCC is above the POR rising threshold.

#### **Enable and Disable**

The RT9610C includes an EN pin for sequence control. When the EN pin rises above the  $V_{\text{ENH}}$  trip point, the RT9610C begins a new initialization and follows the PWM command to control the UGATE and LGATE. When the EN pin falls below the  $V_{\text{ENL}}$  trip point, the RT9610C shuts down and keeps UGATE and LGATE low.

### **Three State PWM Input**

After initialization, the PWM signal takes over the control. The rising PWM signal first forces the LGATE signal low and then allows the UGATE signal to go high right after a non-overlapping time to avoid shoot through current. In contrast, the falling PWM signal first forces UGATE to go low. When the UGATE or PHASE signal reach a predetermined low level, LGATE signal is then allowed to go high.

### **Non-overlap Control**

To prevent the overlap of the gate drives during the UGATE pull low and the LGATE pull high, the non-overlap circuit monitors the voltages at the PHASE node and high side gate drive (UGATE-PHASE). When the PWM input signal goes low, UGATE begins to pull low (after propagation delay). Before LGATE can pull high, the non-overlap protection circuit ensures that the monitored (UGATE-PHASE) voltages have gone below 1.1V or phase voltage is below 2V. Once the monitored voltages fall below the threshold, LGATE begins to turn high. By waiting for the voltages of the PHASE pin and high side gate drive to fall

below their threshold, the non-overlap protection circuit ensures that UGATE is low before LGATE pulls high.

Also to prevent the overlap of the gate drives during LGATE pull low and UGATE pull high, the non-overlap circuit monitors the LGATE voltage. When LGATE go below 1.1V, UGATE is allowed to go high.

### **Driving Power MOSFETs**

The DC input impedance of the power MOSFET is extremely high. The gate draws the current only for few nano-amperes. Thus once the gate has been driven up to "ON" level, the current could be negligible.

However, the capacitance at the gate to source terminal should be considered. It requires relatively large currents to drive the gate up and down rapidly. It is also required to switch drain current on and off with the required speed. The required gate drive currents are calculated as follows.

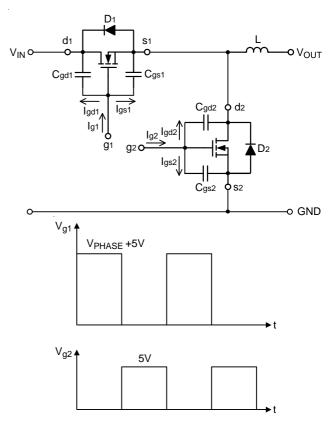

Figure 1. Equivalent Circuit and Associated Waveforms

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

In Figure 1, the current Iq1 and Iq2 are required to move the gate up to 5V. The operation consists of charging C<sub>qd1</sub>,  $C_{gd2}$  ,  $C_{gs1}$  and  $C_{gs2}$ .  $C_{gs1}$  and  $C_{gs2}$  are the capacitors from gate to source of the high side and the low side power MOSFETs, respectively. In general data sheets, the C<sub>qs1</sub> and Cgs2 are referred as "Ciss" which are the input capacitors. C<sub>qd1</sub> and C<sub>qd2</sub> are the capacitors from gate to drain of the high side and the low side power MOSFETs, respectively and referred to the data sheets as "Crss" the reverse transfer capacitance. For example, t<sub>r1</sub> and t<sub>r2</sub> are the rising time of the high side and the low side power MOSFETs respectively, the required current I<sub>gs1</sub> and I<sub>gs2</sub>, are shown as below:

$$I_{gs1} = C_{gs1} \frac{dV_{g1}}{dt} = \frac{C_{gs1} \times 5}{t_{r1}}$$

(1)

$$I_{gs2} = C_{gs1} \frac{dV_{g2}}{dt} = \frac{C_{gs1} x 5}{t_{r2}}$$

(2)

Before driving the gate of the high side MOSFET up to 5V, the low side MOSFET has to be off; and the high side MOSFET is turned off before the low side is turned on. From Figure 1, the body diode "D2" had been turned on before high side MOSFETs turned on.

$$I_{gd1} = C_{gd1} \frac{dV}{dt} = C_{gd1} \frac{5}{t_{r1}}$$

(3)

Before the low side MOSFET is turned on, the C<sub>ad2</sub> have been charged to V<sub>IN</sub>. Thus, as C<sub>gd2</sub> reverses its polarity and g2 is charged up to 5V, the required current is:

$$I_{gd2} = C_{gd2} \frac{dV}{dt} = C_{gd2} \frac{Vi + 5}{t_{r2}}$$

(4)

It is helpful to calculate these currents in a typical case. Assume a synchronous rectified buck converter, input voltage  $V_{IN} = 12V$ ,  $V_{g1} = V_{g2} = 5V$ . The high side MOSFET is PHB83N03LT whose  $C_{iss} = 1660pF$ ,  $C_{rss} = 380pF$ , and  $t_r$  = 14ns. The low side MOSFET is PHB95N03LT whose  $C_{iss}$  = 2200pF,  $C_{rss}$  = 500pF and  $t_r$  = 30ns, from the equation (1) and (2) we can obtain:

$$I_{gs1} = \frac{1660 \times 10^{-12} \times 5}{14 \times 10^{-9}} = 0.593 \quad (A)$$

(5)

$$I_{gs2} = \frac{2200 \times 10^{-12} \times 5}{30 \times 10^{-9}} = 0.367 \quad (A)$$

(6)

from equation. (3) and (4)

$$I_{gd1} = \frac{380 \times 10^{-12} \times 5}{14 \times 10^{-9}} = 0.136 \text{ (A)}$$

$$I_{gd2} = \frac{500 \times 10^{-12} \times (12+5)}{30 \times 10^{-9}} = 0.283$$

(A) (8)

the total current required from the gate driving source can be calculated as following equations:

$$I_{a1} = I_{as1} + I_{ad1} = (0.593 + 0.136) = 0.729$$

(A) (9)

$$I_{q2} = I_{qs2} + I_{qd2} = (0.367 + 0.283) = 0.65$$

(A) (10)

By a similar calculation, we can also get the sink current required from the turned off MOSFET.

### Select the Bootstrap Capacitor

Figure 2 shows part of the bootstrap circuit of the RT9610C. The V<sub>CB</sub> (the voltage difference between BOOT and PHASE on RT9610C) provides a voltage to the gate of the high side power MOSFET. This supply needs to be ensured that the MOSFET can be driven. For this, the capacitance C<sub>B</sub> has to be selected properly. It is determined by following constraints.

Figure 2. Part of Bootstrap Circuit of RT9610C

In practice, a low value capacitor C<sub>B</sub> will lead to the over charging that could damage the IC. Therefore, to minimize the risk of overcharging and to reduce the ripple on V<sub>CB</sub>, the bootstrap capacitor should not be smaller than 0.1 µF, and the larger the better. In general design, using 1µF can provide better performance. At least one low ESR capacitor should be used to provide good local de-coupling. It is recommended to adopt a ceramic or tantalum capacitor.

www.richtek.com

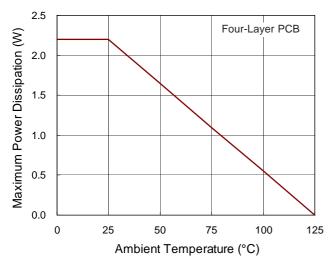

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-8L 2x2 packages, the thermal resistance,  $\theta_{JA}$ , is 45.5°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (45.5^{\circ}C/W) = 2.19W$$

for WDFN-8L 2x2 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 3 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 3. Derating Curve of Maximum Power Dissipation

### **Layout Considerations**

Figure 4 shows the schematic circuit of a synchronous buck converter to implement the RT9610C.

Figure 4. Synchronous Buck Converter Circuit

When layout the PCB, it should be very careful. The power circuit section is the most critical one. If not configured properly, it will generate a large amount of EMI. The junction of Q1, Q2, L2 should be very close.

Next, the trace from UGATE, and LGATE should also be short to decrease the noise of the driver output signals. PHASE signals from the junction of the power MOSFET, carrying the large gate drive current pulses, should be as heavy as the gate drive trace. The bypass capacitor C4 should be connected to GND directly. Furthermore, the bootstrap capacitors (C<sub>B</sub>) should always be placed as close to the pins of the IC as possible.

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9610C-01 April 2016

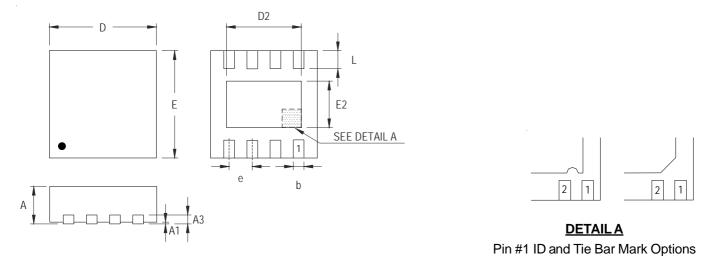

# **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Comple of | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|-----------|--------------|---------------|----------------------|-------|--|

| Symbol    | Min          | Max           | Min                  | Max   |  |

| А         | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1        | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3        | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b         | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D         | 1.950        | 2.050         | 0.077                | 0.081 |  |

| D2        | 1.000        | 1.250         | 0.039                | 0.049 |  |

| Е         | 1.950        | 2.050         | 0.077                | 0.081 |  |

| E2        | 0.400        | 0.650         | 0.016                | 0.026 |  |

| е         | 0.500        |               | 0.0                  | )20   |  |

| L         | 0.300        | 0.400         | 0.012                | 0.016 |  |

W-Type 8L DFN 2x2 Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Isolated DC/DC Converters category:

Click to view products by Richtek manufacturer:

Other Similar products are found below:

ESM6D044440C05AAQ FMD15.24G PSL486-7LR PSR152.5-7IR Q48T30020-NBB0 AVO240-48S12B-6L AVO250-48S28B-6L NAN-0505 HW-L16D JAHW100Y1 217-1617-001 22827 SPB05C-12 SQ24S15033-PS0S 18952 19-130041 CE-1003 CE-1004 GQ2541-7R PSE1000DCDC-12V RDS180245 MAU228 419-2065-201 449-2075-101 J80-0041NL V300C24C150BG 419-2062-200 419-2063-401 419-2067-101 419-2067-501 419-2068-001 DCG40-5G DFC15U48D15 449-2067-000 XGS-0512 XGS-1205 XGS-1212 XGS-2412 XGS-2415 XKS-1215 033456 NCT1000N040R050B SPB05B-15 SPB05C-15 SSQE48T25025-NAA0G L-DA20 HP3040-9RG HP1001-9RTG XKS-2415 XKS-2412 XKS-2415 XKS-2412