# Wireless Power Consortium / Qi Compliant series

# **Wireless Power Transmitter IC**

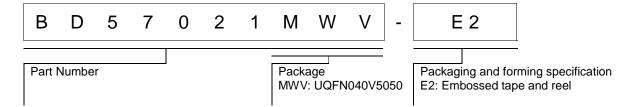

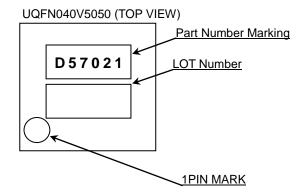

### **BD57021MWV**

#### **General Description**

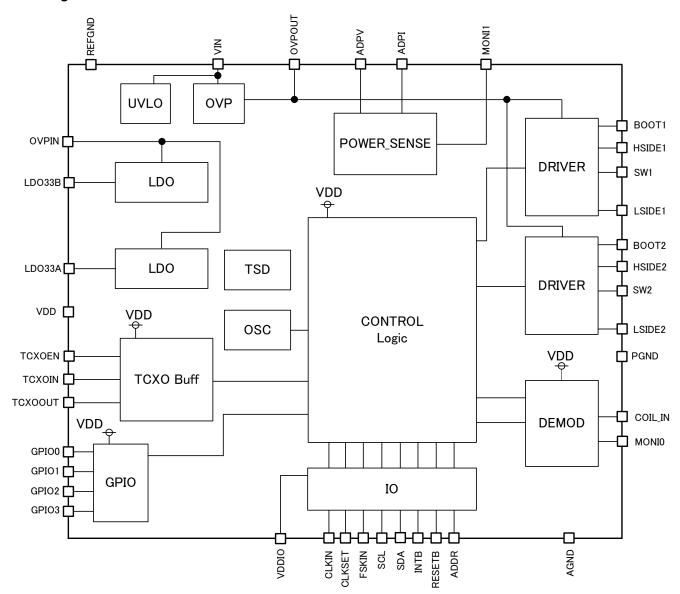

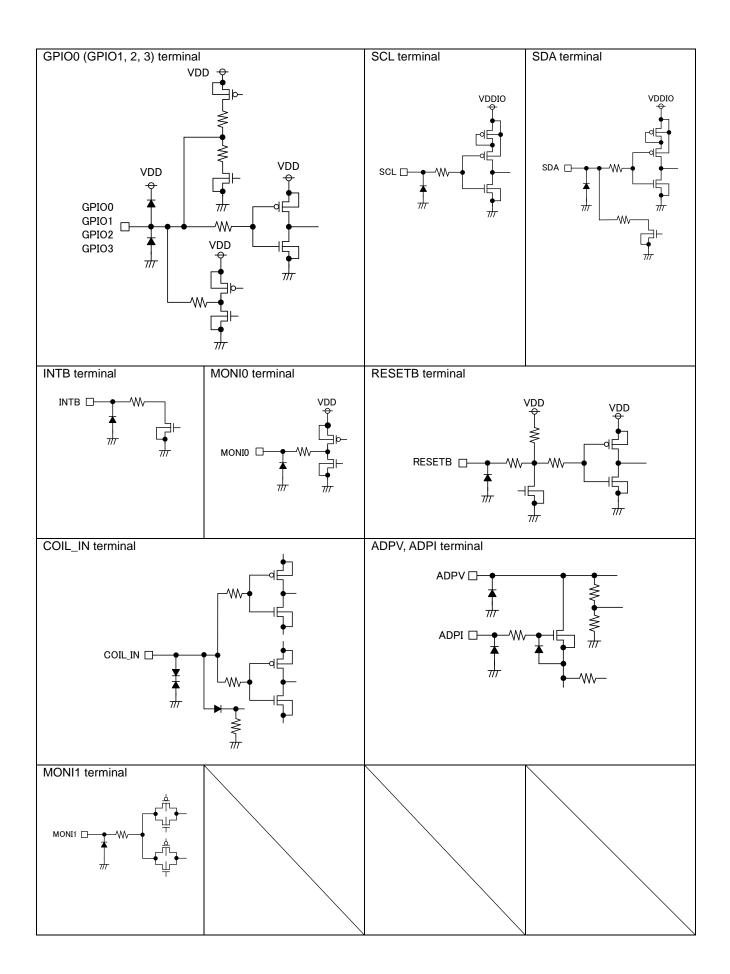

BD57021MWV is an integrated IC for the wireless power transmitter. This device is composed of inverters for the coil drive, controller for the communication of the Qi compliant and demodulating circuit, GPIO, TCXO buffer, and I2C interface.

BD57021MWV works as a controller in the wireless power transmitter based on the Qi compliant by using it with a general-purpose microcomputer.

BD57021MWV is applied to Qi ver.1.2 BPP (Baseline Power Profile).

#### **Features**

- WPC / Qi ver.1.2 BPP (Baseline Power Profile) support.

- Half Bridge / Full Bridge inverter

- Foreign object detection

- GPIO 4CH

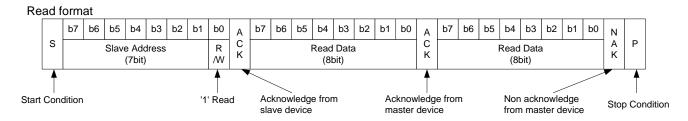

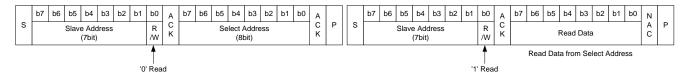

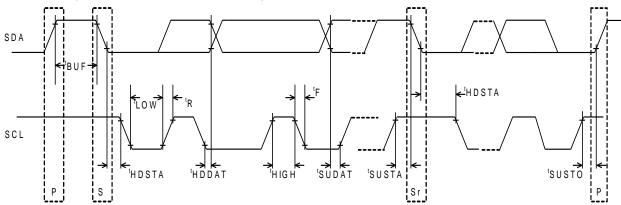

- I2C bus interface

- 5.0mm x 5.0mm UQFN package 40 pin

# **Key Specifications**

Input Voltage Range:

Drive Frequency Range:

Operating Temperature Range:

4.2 V to 5.3 V

110kHz to 205kHz

-20°C to +85°C

Package UQFN040V5050 **W(Typ) x D(Typ) x H(Max)** 5.00mm x 5.00mm x 1.00mm

# **Applications**

WPC compliant devices

- P(

- Cradle for charge stand

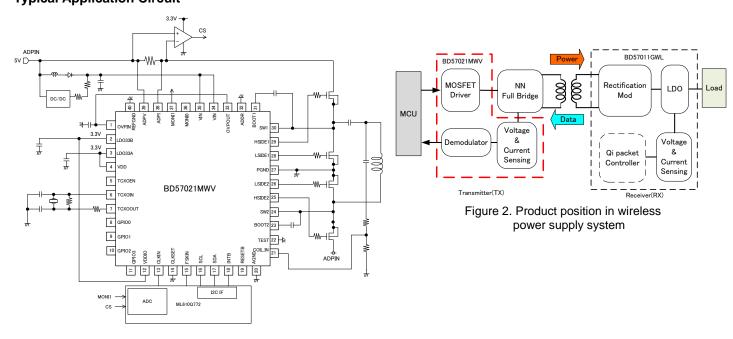

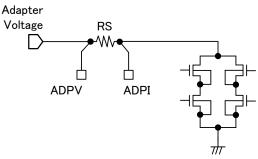

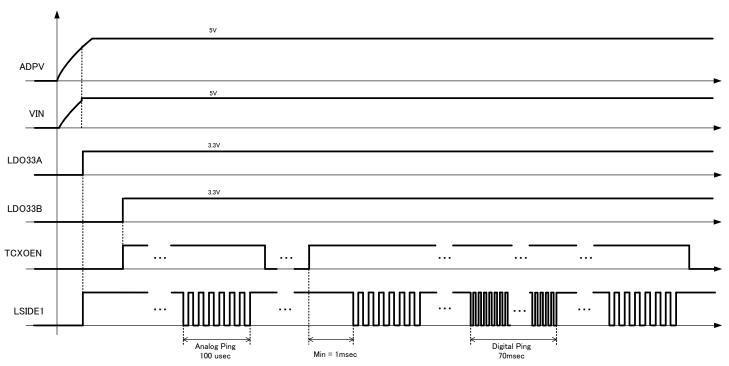

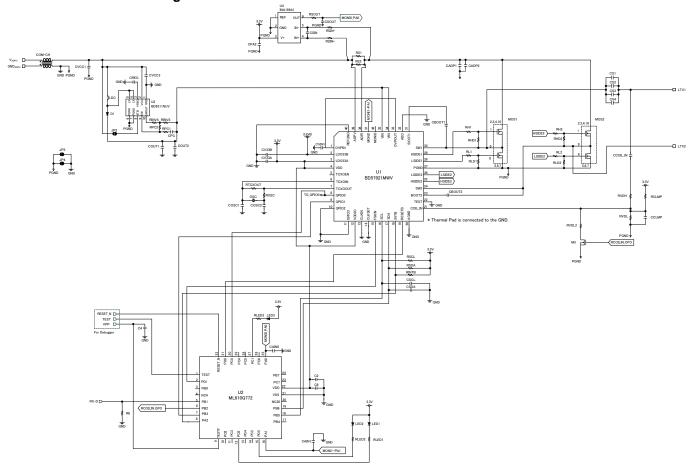

# **Typical Application Circuit**

Figure 1. Typical application circuit

# **Absolute Maximum Ratings**

| Parameter                                                           | Symbol    | Rating                     | Unit |

|---------------------------------------------------------------------|-----------|----------------------------|------|

| VIN, ADPV, ADPI, SW1, SW2 voltage                                   | VIN_H1    | -0.3 to 7.0                | V    |

| BOOT1, BOOT2 voltage                                                | VIN_H2    | -0.3 to 15.5               | V    |

| HSIDE1, HSIDE2 voltage                                              | VOUT_H    | -0.3 to 15.5               | V    |

| OVPIN, VDDIO, SCL, CLKIN, CLKSET, FSKIN, ADDR, TEST, RESETB voltage | VIN_L1    | -0.3 to 7.0                | V    |

| VDD, TCXOIN voltage                                                 | VIN_L2    | -0.3 to 4.5                | V    |

| COIL_IN voltage                                                     | VIN_L3    | -4.5 to 7.0                | V    |

| LSIDE1, LSIDE2, LDO33A, LDO33B, OVPOUT, INTB, MONI0, MONI1 voltage  | VOUT_L1   | -0.3 to 7.0                | V    |

| TCXOEN, TCXOOUT voltage                                             | VOUT_L2   | -0.3 to 4.5                | V    |

| SDA voltage                                                         | VINOUT_L1 | -0.3 to7.0                 | V    |

| GPIO0, GPIO1, GPIO2, GPIO3 voltage                                  | VINOUT_L2 | -0.3 to 4.5                | V    |

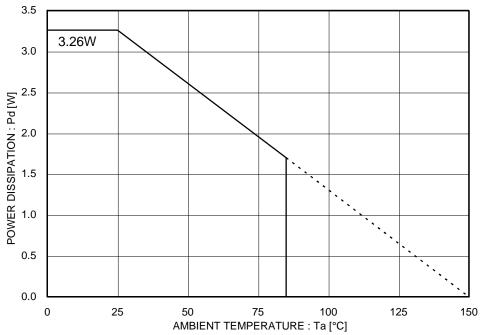

| Power dissipation                                                   | Pd        | 3.26 ( <sup>Note 1</sup> ) | W    |

| Operating ambient temperature range                                 | Та        | -20 to +85                 | °C   |

| Storage temperature range                                           | Tstg      | -55 to +150                | °C   |

<sup>(</sup>Note 1) Derate by 26 mW/°C when operating above Ta=25°C (Mount on 4-layer 74.2mm x 74.2mm x 1.6mm board with front and back layer heat radiation copper foil 4.5 mm x 4.5 mm, second and third layer heat radiation copper foil 74.2 mm x 74.2 mm).

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

# Recommended Operating Conditions (Ta= -20°C to +85°C)

|                                     | 1:     | <del> </del> | <u> </u> |     |      |

|-------------------------------------|--------|--------------|----------|-----|------|

| Parameter                           | Symbol | Min          | Тур      | Max | Unit |

| VIN terminal input voltage range    | VIN    | 4.2          | 5.0      | 5.3 | V    |

| VDD terminal input voltage range    | VDD    | 3.1          | 3.3      | 3.5 | V    |

| VDDIO terminal voltage range        | VDDIO  | 3.1          | 3.3      | 3.5 | V    |

| Adapter input voltage range         | VADPV  | 4.2          | 5.0      | 5.3 | V    |

| TCXO terminal input frequency range | FTCXO  | 32           | -        | 45  | MHz  |

Electrical Characteristics (Unless otherwise specified VIN=5V VDD=3.3V Ta=25°C)

| Operating circuit current 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Parameter                          | Symbol                   | Min  | Limit<br>Typ | Max  | Unit | Conditions                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------|------|--------------|------|------|----------------------------|

| Operating circuit current 2         Icc2         -         15.0         23.0         mA         TCXOIN=32MHz           Protection block (the IC outside)         External OCP operating voltage         Vocp         125         160         195         mV         R₂=100mΩ           Protective circuit (the IC inside)         Vivious March 10 (see Fig. 1)         6.1         6.4         6.7         V         VIN: 5.0 → 8.0V           VIN Over voltage lockout Hysteresis on OVLO         Vovious 140         200         260         mV         VIN: 5.0 → 8.0V           VIN Under voltage lockout Hysteresis on UVLO         Vovious 140         200         260         mV         VIN: 5.0 → 60V           VID UVLO detection voltage Voltous 2         Vovious 2.55         2.50         2.75         V         VDD: 3.3 → 60V           VDDIO UVLO detection voltage Voltous 2         Vovious 2.55         2.80         3.05         V         VDD: 0 → 3.3V           VDDIO UVLO release voltage Voltous 2         Vovious 2.55         2.80         3.05         V         VDD: 0 → 3.3V           VDDIO UVLO release voltage Voltous 2         Vovious 2.55         2.80         3.05         V         VDD: 0 → 3.3V           VDDIO release voltage Voltous 2         Voltous 3         3.2         3.3         3.4         V<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Whole Chip                         |                          |      | .,,,,,       | Max  |      |                            |

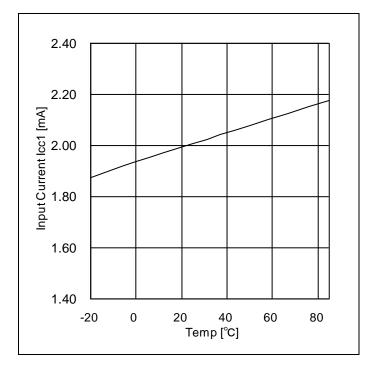

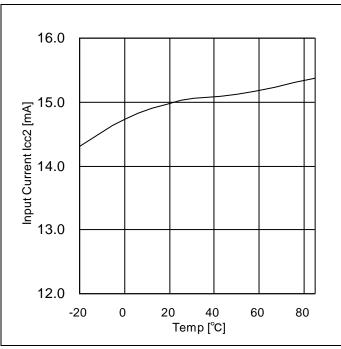

| Protection block (the IC outside) External OCP operating voltage Protective circuit (the IC inside)  VocP  125 160 195 mV Rs=100mΩ  Protective circuit (the IC inside)  VIN Over voltage lockout VoxLo_VNN  140 200 280 mV VIN: 5.0 → 8.0V  Hysteresis on OVLO VoxLo_VNN  140 200 280 mV VIN: 5.0 → 5.0V  VIN Under voltage lockout VoxLo_VNN  140 200 280 mV VIN: 5.0 → 5.0V  VIN Under voltage lockout VoxLo_VNN  140 200 280 mV VIN: 5.0 → 5.0V  VIN Under voltage lockout VoxLo_VNN  140 200 280 mV VIN: 5.0 → 5.0V  VID UVLO detection voltage VoxLo_VND  VDD UVLO detection voltage VoxLo_VND  VDD UVLO detection voltage VoxLo_VND  VDD UVLO release voxLo_VND  VDD UVLO                                                                                                                                                                                                                 | Operating circuit current 1        | I <sub>CC1</sub>         | -    | 2.0          | 3.0  | mA   | TCXOIN=0kHz                |

| External OCP operating voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operating circuit current 2        | I <sub>CC2</sub>         | -    | 15.0         | 23.0 | mA   | TCXOIN=32MHz               |

| Protective circuit (the IC inside)   Vinco_vin   6.1   6.4   6.7   V   VIN: 5.0 → 8.0V   VIN over voltage lockout   Vov.o.vin   140   200   260   mV   VIN: 8.0 → 5.0V   VIN: 5.0 → 8.0V   VIN: 5.0 → 6.0V   VID: 0 → 5.0V                                                                                                                                                                                                                  | Protection block (the IC outside)  |                          |      |              |      |      | 1                          |

| VIN Over voltage lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External OCP operating voltage     | V <sub>OCP</sub>         | 125  | 160          | 195  | mV   | $R_S=100m\Omega$           |

| Hysteresis on OVLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protective circuit (the IC inside) |                          |      | I            | I.   |      | 1                          |

| Vivi                                                                                                                                                                                                                   | VIN Over voltage lockout           | V <sub>OVLO_VIN</sub>    | 6.1  | 6.4          | 6.7  | V    | VIN: 5.0 → 8.0V            |

| Hysteresis on UVLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Hysteresis on OVLO                 | V <sub>OVLO_HYS</sub>    | 140  | 200          | 260  | mV   | VIN: 8.0 → 5.0V            |

| VDD UVLO detection voltage         V <sub>UVLOD_VDD</sub> 2.25         2.50         2.75         V         VDD: 3.3 → 0V           VDD UVLO release voltage         V <sub>UVLOD_VDDIO</sub> 2.55         2.80         3.05         V         VDDIO: 0 → 3.3V           VDDIO UVLO release voltage         V <sub>UVLOD_VDDIO</sub> 2.25         2.50         2.75         V         VDDIO: 3.3 → 0V           VDDIO UVLO release voltage         V <sub>UVLOD_VDDIO</sub> 2.55         2.80         3.05         V         VDDIO: 0 → 3.3V           Internal OCP operating current         Ioce         -         0.48         0.65         A           LDO33A block         LDO33A         3.2         3.3         3.4         V         I <sub>source</sub> =10mA           LDO33B maximum output current         I <sub>LDO33B</sub> 3.2         3.3         3.4         mV         I <sub>source</sub> =10mA           LDO33B maximum output current         I <sub>LDO33B</sub> -         -         30         mA           Demodulating circuit block         -         -         50         µA         VCOIL_IN=3.3V           COIL_IN leak current 1         ILEAKcollini         -         -         50         µA         VCOIL_IN=3.3V           COIL_IN leak current 2         ILEAKcollini <t< td=""><td>VIN Under voltage lockout</td><td>V<sub>UVLO_VIN</sub></td><td>3.3</td><td>3.6</td><td>3.9</td><td>V</td><td>VIN: 5.0 → 0V</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VIN Under voltage lockout          | V <sub>UVLO_VIN</sub>    | 3.3  | 3.6          | 3.9  | V    | VIN: 5.0 → 0V              |

| VDD UVLO release voltage         V <sub>UVLOR_VDD</sub> 2.55         2.80         3.05         V         VDD: 0 → 3.3V           VDDIO UVLO detection voltage         V <sub>UVLOD_VDDIO</sub> 2.25         2.50         2.75         V         VDDIO: 0 → 3.3V           VDDIO UVLO release voltage         V <sub>UVLOD_VDDIO</sub> 2.55         2.80         3.05         V         VDDIO: 0 → 3.3V           Internal OCP operating current         Iocp         - 0.48         0.65         A           LDO33A block         LDO33A maximum output current         I <sub>LD033A</sub> - 30         mA           LDO33B block         LDO33B block         LDO33B subput voltage         V <sub>LD033B</sub> 3.2         3.3         3.4         mV         I <sub>source</sub> =10mA           LDO33B block         LDO33B subput voltage         V <sub>LD033B</sub> 3.2         3.3         3.4         mV         I <sub>source</sub> =10mA           LDO33B maximum output current         I <sub>LD033B</sub> - 30         mA         mA         Maxima=10mA           LDO33B maximum output current         I <sub>LD033B</sub> 50         µA         VCOIL_IN=3.3V           COIL_IN leak current 1         ILEAKcollint         50         µA         VCOIL_IN=3.3V           TCXOEN F block         TCXOEN Level output voltage </td <td>Hysteresis on UVLO</td> <td>V<sub>UVLO_HYS</sub></td> <td>140</td> <td>200</td> <td>260</td> <td>mV</td> <td>VIN: 0 → 5.0V</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Hysteresis on UVLO                 | V <sub>UVLO_HYS</sub>    | 140  | 200          | 260  | mV   | VIN: 0 → 5.0V              |

| VDDIO UVLO detection voltage   Vuv.ob_VDDIO   2.25   2.50   2.75   V   VDDIO: 3.3 → 0V   VDDIO UVLO release voltage   Vuv.ob_VDDIO   2.55   2.80   3.05   V   VDDIO: 0 → 3.3V   Internal OCP operating current   Io_CP   - 0.48   0.65   A   UD033A block   UD033A block   UD033A block   UD033A output voltage   VLD033A   - 30   mA   UD033A maximum output current   ILD033A   - 30   mA   UD033B block   UD033B block   UD033B block   UD033B maximum output current   ILD033B   - 30   mA   UD033B   UD033                                                                                                                                                                                                                  | VDD UVLO detection voltage         | V <sub>UVLOD_VDD</sub>   | 2.25 | 2.50         | 2.75 | V    | VDD: 3.3 → 0V              |

| VDDIO UVLO release voltage         V <sub>UVLOD, VDDIO</sub> 2.55         2.80         3.05         V         VDDIO: 0 → 3.3V           Internal OCP operating current         I <sub>OCP</sub> -         0.48         0.65         A           LDO33A block         LDO33A output voltage         V <sub>LD033A</sub> 3.2         3.3         3.4         V         I <sub>source</sub> =10mA           LDO33B block         LDO33B block           LDO33B maximum output current         I <sub>LD033B</sub> 3.2         3.3         3.4         mV         I <sub>source</sub> =10mA           Demodulating circuit block         COIL_IN leak current 1         ILEAKcollint         -         50         µA         VCOIL_IN=3.3V           TCXOI, In leak current 2         ILEAKcollint         -         50         µA         VCOIL_IN=3.3V           TCXO, BUFF block         TCXOIN input current         ITCXOIN         -         0         1.0         µA         VDD=VTCXOIN=4.5V           Input frequency range         FTCXOIN         -         -         52         MHz           TCXOEN L level output voltage         VOHTXCOEN         VDD         x 0.2         V         I <sub>source</sub> =1.0mA           TCXOEN H level output volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VDD UVLO release voltage           | $V_{UVLOR\_VDD}$         | 2.55 | 2.80         | 3.05 | V    | VDD: 0 → 3.3V              |

| Internal OCP operating current   Ioop   -   0.48   0.65   A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDDIO UVLO detection voltage       | V <sub>UVLOD_VDDIO</sub> | 2.25 | 2.50         | 2.75 | V    | VDDIO: 3.3 → 0V            |

| LDO33A block   LDO33A output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VDDIO UVLO release voltage         | V <sub>UVLOD_VDDIO</sub> | 2.55 | 2.80         | 3.05 | V    | VDDIO: 0 → 3.3V            |

| LDO33A output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Internal OCP operating current     | I <sub>OCP</sub>         | -    | 0.48         | 0.65 | Α    |                            |

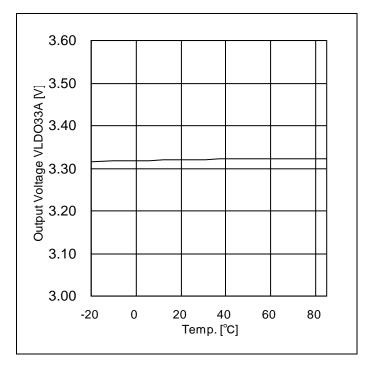

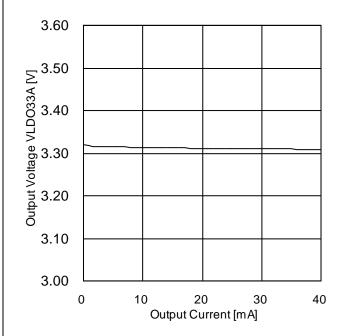

| LDO33A maximum output current   LDO33A   -   -   30   mA     LDO33B block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LDO33A block                       |                          |      |              |      |      |                            |

| LDO33B block   LDO33B output voltage   V <sub>LDO33B</sub>   3.2   3.3   3.4   mV   I <sub>source</sub> =10mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LDO33A output voltage              | V <sub>LDO33A</sub>      | 3.2  | 3.3          | 3.4  | V    | I <sub>source</sub> =10mA  |

| LDO33B output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LDO33A maximum output current      | I <sub>LDO33A</sub>      | -    | -            | 30   | mA   |                            |

| LDO33B maximum output current   ILDO33B   30   mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LDO33B block                       |                          |      |              |      |      |                            |

| Demodulating circuit block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LDO33B output voltage              | $V_{LDO33B}$             | 3.2  | 3.3          | 3.4  | mV   | I <sub>source</sub> =10mA  |

| COIL_IN leak current 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LDO33B maximum output current      | I <sub>LDO33B</sub>      | -    | -            | 30   | mA   |                            |

| COIL_IN leak current 2   ILEAK <sub>COILINZ</sub> -150   -   -   μA   VCOIL_IN=-3.3V     TCXO_BUFF block     TCXOIN input current   ITCXOIN   -   0   1.0   μA   VDD=VTCXOIN=4.5V     Input frequency range   FTCXOIN   -   -   52   MHz     TCXOEN L level output voltage   VOH <sub>TXCOEN</sub>   -   -   VDD   x 0.2   V   I <sub>sink</sub> =1.0mA     TCXOEN H level output voltage   VOL <sub>TXCOEN</sub>   x 0.8   -   -   V   I <sub>source</sub> =1.0mA     TCXOOUT output impedance   ZOTCXOOUT   -   1.0   -   kΩ     Inverter block     Drive frequency   FDRIVE   110   -   205   kHz     Minimum Duty Ratio   Dutymin   -   25   -   %     Dead Time   TDead   -   200   -   ns   TCXOIN=32MHz     Source resistance   RSOURCE   -   1.0   -   Ω     Sink resistance   RSINK   -   0.8   -   Ω     GPIO L level input voltage   VOL <sub>GPIO</sub>   -   -   VDD   x 0.3   V     GPIO pull-down resistor   RPD <sub>GPIO</sub>   -   100   -   kΩ     GPIO pull-up resister   RPU <sub>GPIO</sub>   -   -   VDD   x 0.2   V     GPIO L level output voltage   VIL <sub>GPIO</sub>   -   -   VDD   V   L <sub>sink</sub> =1.0mA     GPIO H level output voltage   VIL <sub>GPIO</sub>   -   -   VDD   V   L <sub>sink</sub> =1.0mA     GPIO H level output voltage   VIL <sub>GPIO</sub>   -   -   VDD   V   L <sub>sink</sub> =1.0mA     GPIO H level output voltage   VIL <sub>GPIO</sub>   -   -   VDD   V   L <sub>sink</sub> =1.0mA     GPIO H level output voltage   VIL <sub>GPIO</sub>   VDD   VDD   V   L <sub>sink</sub> =1.0mA     GPIO H level output voltage   VIL <sub>GPIO</sub>   VDD   VDD   V   L <sub>sink</sub> =1.0mA     TCXOIN=3.3V   TCXOIN=4.5V   TCXOIN=4 | Demodulating circuit block         |                          |      |              |      |      |                            |

| TCXO_BUFF block  TCXOIN input current  ITCXOIN  TCXOIN input current  ITCXOIN  TCXOEN L level output voltage  TCXOEN L level output voltage  VOH <sub>TXCOEN</sub> TCXOEN H level output voltage  VOL <sub>TXCOEN</sub> TCXOEN H level output impedance  ZO <sub>TCXOOUT</sub> TCXOOUT output impedance  ZO <sub>TCXOOUT</sub> TOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUTOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COIL_IN leak current 1             | ILEAK <sub>COILIN1</sub> | -    | -            | 50   | μΑ   | VCOIL_IN=3.3V              |

| TCXOIN input current   ITCXOIN   -   0   1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COIL_IN leak current 2             | ILEAK <sub>COILIN2</sub> | -150 | -            | -    | μΑ   | VCOIL_IN=-3.3V             |

| Input frequency range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TCXO_BUFF block                    |                          |      |              |      |      |                            |

| TCXOEN L level output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TCXOIN input current               | I <sub>TCXOIN</sub>      | -    | 0            | 1.0  | μΑ   | VDD=VTCXOIN=4.5V           |

| TCXOEN Lievel output voltage   VOHTXCOEN   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input frequency range              | F <sub>TCXOIN</sub>      | -    | -            | 52   | MHz  |                            |

| TCXOEN R level dulput Voltage   VOLTXCOEN   x 0.8   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TCXOEN L level output voltage      | VOH <sub>TXCOEN</sub>    | -    | -            |      | V    | I <sub>sink</sub> =1.0mA   |

| TCXOOUT output impedance   ZO <sub>TCXOOUT</sub>   -   1.0   -   kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TCXOEN H level output voltage      | VOLTXCOEN                |      | -            | -    | V    | I <sub>source</sub> =1.0mA |

| Drive frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TCXOOUT output impedance           | ZO <sub>TCXOOUT</sub>    | -    | 1.0          | -    | kΩ   |                            |

| Minimum Duty Ratio       Dutymin       -       25       -       %         Dead Time $T_{Dead}$ -       200       -       ns       TCXOIN=32MHz         Source resistance $R_{SOURCE}$ -       1.0       -       Ω         Sink resistance $R_{SINK}$ -       0.8       -       Ω         GPIO block         GPIO L level input voltage $VOL_{GPIO}$ -       - $VDD$<br>x 0.7       -       -       V         GPIO H level input voltage $VOH_{GPIO}$ -       100       kΩ         GPIO pull-down resistor $RPD_{GPIO}$ -       100       -       kΩ         GPIO pull-up resister $RPU_{GPIO}$ -       - $VDD$ V $V$ $V$ GPIO L level output voltage $VIL_{GPIO}$ -       - $V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Inverter block                     |                          |      | I            | I.   |      | 1                          |

| Dead Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Drive frequency                    | F <sub>DRIVE</sub>       | 110  | -            | 205  | kHz  |                            |