# 1, 2, and 4k bit EEPROMs for direct connection to serial ports BR9010 / BR9010F / BR9010FV / BR9020 / BR9020F / BR9040 / BR9040F

### Features

- •BR9010 / F / FV (1k bit): 64 words × 16 bits BR9020 / F (2k bit): 128 words × 16 bits BR9040 / F (4k bit): 256 words × 16 bits

- Single power supply operation

- Serial data input and output

- Automatic erase-before-write

- Low current consumption

- -1.5mA (max.) active current: 3V

- -2μA (max.) standby current: 3V

- •Noise filter built into SK pin

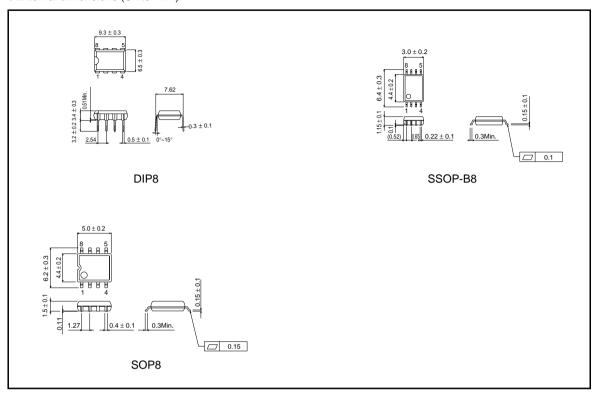

- •Compact DIP8, SOP8, SSOP-B8 packages (SSOP-B8 is available only with BR9010).

- •100,000 ERASE / WRITE cycles

- •10 years Data Retention

- · Easily connects to serial port

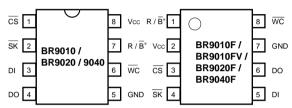

# Pin assignments

\* This pin is N.C. (non connection) on BR9010.

### Pin description

| Pin<br>name | Function                                       |

|-------------|------------------------------------------------|

| CS          | Chip select input                              |

| SK          | Serial data clock input                        |

| DI          | Operating code, address, and serial data input |

| DO          | Serial data output                             |

| GND         | Reference voltage for all I / O, 0V            |

| WC          | Write control input                            |

| R/B         | READY, BUSY status signal output               |

| Vcc         | Power supply connection                        |

### Overview

The BR90 series are serial EEPROMs that can be connected directly to a serial port and can be erased and written electrically. Writing and reading is performed in word units, using four types of operation commands. Communication occurs through  $\overline{CS}$ ,  $\overline{SK}$ , DI, and DO pins,  $\overline{WC}$  pin control is used to initiate a write disabled state, enabling these EEPROMs to be used as one-time ROMs. During writing, operation is checked via the internal status check.

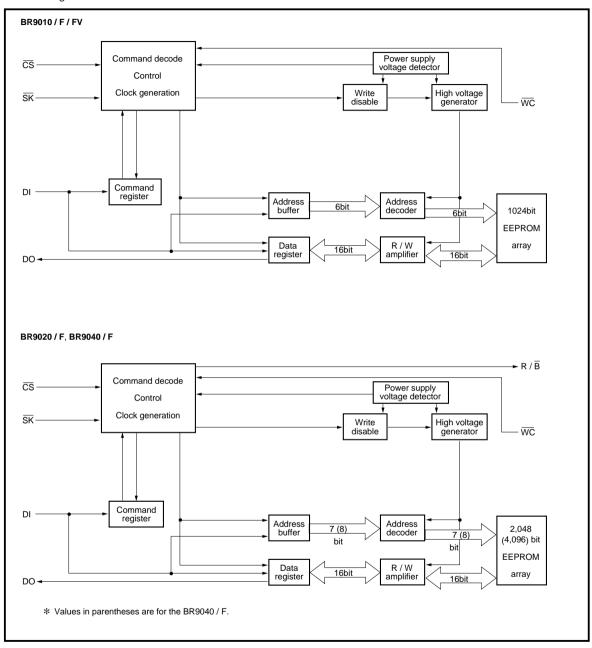

## Block diagram

# ●Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol | Lim                 | nits  | Unit |

|-----------------------|--------|---------------------|-------|------|

| Applied voltage       | Vcc    | - 0.3 ~ + 7.0       |       | V    |

|                       |        | DIP8                | 500*1 |      |

| Power dissipation     | Pd     | SOP8                | 350*2 | mW   |

|                       |        | SSOP-B8             | 300*3 |      |

| Storage temperature   | Tstg   | - 65 ~ <b>+</b> 125 |       | °C   |

| Operation temperature | Topr   | - 40 ~ + 85         |       | °C   |

| Input voltage         | _      | - 0.3 ~ Vcc + 0.3   |       | V    |

<sup>\*</sup> Reduced by 5.0mw\*1 / 3.5mw\*2 / 3.0mw\*3 for each increase in Ta of 1°C over 25°C.

# Recommended operating conditions

| Parameter            | Symbol | Symbol Limits      |   |

|----------------------|--------|--------------------|---|

| Power supply voltage | Vcc    | 2.7 to 5.5 (write) | V |

| rower supply voltage | VCC    | 2.0 to 5.5 (read)  | V |

| Input voltage        | Vin    | 0 ~ Vcc            | V |

### Electrical characteristics

BR9010 / F / FV: At 5V (unless otherwise noted,  $Ta = -40 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 5V \pm 10\%$ )

| Parameter                  | Symbol           | Min.       | Тур. | Max. | Unit | Conditions                                                                                     |

|----------------------------|------------------|------------|------|------|------|------------------------------------------------------------------------------------------------|

| Input low level voltage 1  | VIL1             | _          | _    | 0.3× | V    | DI Pin                                                                                         |

|                            |                  |            |      | Vcc  |      |                                                                                                |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7×       | _    | _    | V    | DI Pin                                                                                         |

|                            |                  | Vcc        |      |      |      |                                                                                                |

| Input low level voltage 2  | VIL2             | _          | _    | 0.2× | V    | CS, SK, WC Pin                                                                                 |

|                            |                  |            |      | Vcc  |      |                                                                                                |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8 ×      | _    | _    | V    | CS, SK, WC Pin                                                                                 |

|                            |                  | Vcc        |      |      |      |                                                                                                |

| Output low level voltage   | Vol              | 0          | _    | 0.4  | V    | lo <sub>L</sub> = 2.1mA                                                                        |

| Output high level voltage  | Vон              | Vcc-       | _    | Vcc  | V    | Iон = - 0.4mA                                                                                  |

|                            |                  | 0.4        |      |      |      |                                                                                                |

| Input leak current         | lu               | <b>– 1</b> | _    | 1    | μΑ   | Vin = 0V ~ Vcc                                                                                 |

| Output leak current        | ILO              | - 1        | _    | 1    | μΑ   | $V_{OUT} = 0V \sim V_{CC} \overline{CS} = V_{CC}$                                              |

| Consumption current        | Icc1             | _          | _    | 2    | mA   | f = 1MHz tE / W = 10ms (WRITE)                                                                 |

| during operation           | Icc2             | _          | _    | 1    | mA   | f = 1MHz (READ)                                                                                |

| Standby current            | Isв              | _          | _    | 3    | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO = OPEN |

| SK frequency               | fsк              | _          | _    | 1    | MHz  | _                                                                                              |

# BR9010 / F / FV: At 3V (unless otherwise noted, $Ta = -40 \text{ to} + 85^{\circ}\text{C}$ , $Vcc = 3V \pm 10\%$ )

| Parameter                  | Symbol           | Min.  | Тур. | Max. | Unit | Conditions                                                                                     |  |  |

|----------------------------|------------------|-------|------|------|------|------------------------------------------------------------------------------------------------|--|--|

| Input low level voltage 1  | VIL1             | _     | _    | 0.3× | V    | DI Pin                                                                                         |  |  |

|                            |                  |       |      | Vcc  |      |                                                                                                |  |  |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7×  | _    | _    | V    | DI Pin                                                                                         |  |  |

|                            |                  | Vcc   |      |      |      |                                                                                                |  |  |

| Input low level voltage 2  | VIL2             | _     | _    | 0.2× | V    | CS, SK, WC Pin                                                                                 |  |  |

|                            |                  |       |      | Vcc  |      |                                                                                                |  |  |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8×  | _    | _    | V    | CS, SK, WC Pin                                                                                 |  |  |

|                            |                  | Vcc   |      |      |      |                                                                                                |  |  |

| Output low level voltage   | Vol              | 0     | _    | 0.4  | V    | IoL = 100μA                                                                                    |  |  |

| Output high level voltage  | Vон              | Vcc - | _    | Vcc  | V    | Іон = − 100μА                                                                                  |  |  |

|                            |                  | 0.4   |      |      |      |                                                                                                |  |  |

| Input leak current         | lu               | -1    | _    | 1    | μΑ   | Vin = 0 ~ Vcc                                                                                  |  |  |

| Output leak current        | ILO              | -1    | _    | 1    | μΑ   | Vout = 0 ~ Vcc $\overline{CS}$ = Vcc                                                           |  |  |

| Consumption current        | Icc1             | _     | _    | 1.5  | mA   | f = 1MHz tE / W = 15ms (WRITE)                                                                 |  |  |

| during operation           | Icc2             | _     | _    | 500  | μΑ   | f = 1MHz (READ)                                                                                |  |  |

| Standby current            | Isa              | _     | _    | 2    | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO = OPEN |  |  |

| SK frequency               | fsк              |       | _    | 1    | MHz  | _                                                                                              |  |  |

O Not designed for radiation resistance

### Electrical characteristics

$\bullet$ BR9020 / F: At 5V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 5V  $\pm$  10%)

| Parameter                  | Symbol           | Min.       | Тур. | Max.      | Unit | Conditions                                                                                                                |

|----------------------------|------------------|------------|------|-----------|------|---------------------------------------------------------------------------------------------------------------------------|

| Input low level voltage 1  | VIL1             | _          | _    | 0.3 × Vcc | V    | DI Pin                                                                                                                    |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7 × Vcc  | _    | _         | V    | DI Pin                                                                                                                    |

| Input low level voltage 2  | VIL2             | _          | _    | 0.2 × Vcc | V    | CS, SK, WC Pin                                                                                                            |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8 × Vcc  | _    | _         | V    | CS, SK, WC Pin                                                                                                            |

| Output low level voltage   | Vol              | 0          | _    | 0.4       | V    | IoL = 2.1mA                                                                                                               |

| Output high level voltage  | Vон              | Vcc - 0.4  | _    | Vcc       | V    | Іон = — 0.4mA                                                                                                             |

| Input leak current         | lu               | <b>– 1</b> | _    | 1         | μΑ   | Vin = 0V ~ Vcc                                                                                                            |

| Output leak current        | ILO              | <b>– 1</b> | _    | 1         | μΑ   | Vout = 0V ~ Vcc $\overline{CS}$ = Vcc                                                                                     |

| Consumption current        | Icc1             | _          | _    | 2         | mA   | fsk = 1MHz tE / W = 10ms (WRITE)                                                                                          |

| during operation           | Icc2             | _          | -    | 1         | mA   | fsk = 1MHz (READ)                                                                                                         |

| Standby current            | IsB              | _          | _    | 3         | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO, R / $\overline{\text{B}}$ = OPEN |

| SK frequency               | fsк              | _          |      | 1         | MHz  | _                                                                                                                         |

# $\bullet$ BR9020 / F: At 3V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 3V $\pm$ 10%)

| Parameter                  | Symbol           | Min.       | Тур. | Max.      | Unit | Conditions                                                                                                                |

|----------------------------|------------------|------------|------|-----------|------|---------------------------------------------------------------------------------------------------------------------------|

| Input low level voltage 1  | VIL1             | _          | _    | 0.3 × Vcc | V    | DI Pin                                                                                                                    |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7 × Vcc  | _    | _         | V    | DI Pin                                                                                                                    |

| Input low level voltage 2  | V <sub>IL2</sub> | _          | _    | 0.2 × Vcc | V    | CS, SK, WC Pin                                                                                                            |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8 × Vcc  | _    | _         | V    | CS, SK, WC Pin                                                                                                            |

| Output low level voltage   | Vol              | 0          | _    | 0.4       | V    | IoL = 100μA                                                                                                               |

| Output high level voltage  | Vон              | Vcc - 0.4  | _    | Vcc       | V    | Іон = − 100μА                                                                                                             |

| Input leak current         | lu               | <b>– 1</b> | _    | 1         | μΑ   | Vin = 0V ~ Vcc                                                                                                            |

| Output leak current        | ILO              | <b>-1</b>  | _    | 1         | μΑ   | Vout = 0V ~ Vcc $\overline{CS}$ = Vcc                                                                                     |

| Consumption current        | Icc1             | _          | _    | 1.5       | mA   | fsk = 1MHz tE / W = 15ms (WRITE)                                                                                          |

| during operation           | Icc2             | _          | _    | 500       | μΑ   | fsk = 1MHz (READ)                                                                                                         |

| Standby current            | Isa              | _          | _    | 2         | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO, R / $\overline{\text{B}}$ = OPEN |

| SK frequency               | fsк              | _          | _    | 1         | MHz  | _                                                                                                                         |

### Electrical characteristics

$\bullet$ BR9040 / F: At 5V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 5V  $\pm 10$ %)

| Parameter                  | Symbol           | Min.      | Тур. | Max.      | Unit | Conditions                                                                                                                |

|----------------------------|------------------|-----------|------|-----------|------|---------------------------------------------------------------------------------------------------------------------------|

| Input low level voltage 1  | VIL1             | _         | _    | 0.3 × Vcc | ٧    | DI Pin                                                                                                                    |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7 × Vcc | _    | _         | V    | DI Pin                                                                                                                    |

| Input low level voltage 2  | VIL2             | _         | _    | 0.2 × Vcc | V    | CS, SK, WC Pin                                                                                                            |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8 × Vcc | _    | _         | V    | CS, SK, WC Pin                                                                                                            |

| Output low level voltage   | Vol              | 0         | _    | 0.4       | V    | IoL = 2.1mA                                                                                                               |

| Output high level voltage  | Vон              | Vcc - 0.4 | _    | Vcc       | ٧    | Іон = - 0.4mA                                                                                                             |

| Input leak current         | lu               | - 1       | _    | 1         | μΑ   | Vin = 0V ~ Vcc                                                                                                            |

| Output leak current        | ILO              | - 1       | _    | 1         | μΑ   | Vout = 0V ~ Vcc $\overline{CS}$ = Vcc                                                                                     |

| Consumption current        | Icc1             | _         | _    | 2         | mA   | fsk = 1MHz tE / W = 10ms (WRITE)                                                                                          |

| during operation           | Icc2             | _         | _    | 1         | mA   | fsk = 1MHz (READ)                                                                                                         |

| Standby current            | Isв              | _         | _    | 3         | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO, R / $\overline{\text{B}}$ = OPEN |

| SK frequency               | fsк              | _         | _    | 1         | MHz  | _                                                                                                                         |

# $\bullet$ BR9040 / F: At 3V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 3V $\pm$ 10%)

| Parameter                  | Symbol           | Min.       | Тур. | Max.      | Unit | Conditions                                                                                                                |

|----------------------------|------------------|------------|------|-----------|------|---------------------------------------------------------------------------------------------------------------------------|

| Input low level voltage 1  | VIL1             | _          | _    | 0.3 × Vcc | V    | DI Pin                                                                                                                    |

| Input high level voltage 1 | V <sub>IH1</sub> | 0.7 × Vcc  | _    | _         | V    | DI Pin                                                                                                                    |

| Input low level voltage 2  | VIL2             | _          | _    | 0.2 × Vcc | V    | CS, SK, WC Pin                                                                                                            |

| Input high level voltage 2 | V <sub>IH2</sub> | 0.8 × Vcc  | _    | _         | V    | CS, SK, WC Pin                                                                                                            |

| Output low level voltage   | Vol              | 0          | _    | 0.4       | V    | IoL = 100μA                                                                                                               |

| Output high level voltage  | Vон              | Vcc - 0.4  | _    | Vcc       | V    | Іон = − 100μА                                                                                                             |

| Input leak current         | lu               | <b>- 1</b> | _    | 1         | μΑ   | Vin = 0V ~ Vcc                                                                                                            |

| Output leak current        | ILO              | <b>– 1</b> | _    | 1         | μΑ   | Vout = 0V ~ Vcc $\overline{CS}$ = Vcc                                                                                     |

| Consumption current        | Icc1             | _          | _    | 1.5       | mA   | fsk = 1MHz tE / W = 15ms (WRITE)                                                                                          |

| during operation           | Icc2             | _          | _    | 500       | μΑ   | fsk = 1MHz (READ)                                                                                                         |

| Standby current            | Isв              | _          | _    | 2         | μΑ   | $\overline{\text{CS}}$ , $\overline{\text{SK}}$ , DI, $\overline{\text{WC}}$ , = Vcc DO, R / $\overline{\text{B}}$ = OPEN |

| CK fraguency               |                  | _          | _    | 1         | MHz  | Vcc = 3.0 ~ 3.3V                                                                                                          |

| SK frequency               | <b>f</b> sk      | _          | _    | 750       | kHz  | Vcc = 2.7 ~ 3.0V                                                                                                          |

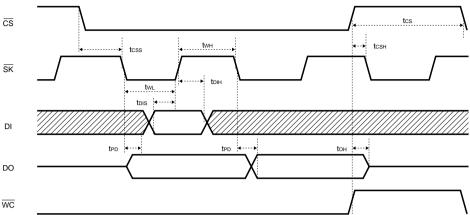

# Operation timing characteristics

BR9010 / F / FV: At 5V (unless otherwise noted,  $Ta = -40 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 5V \pm 10\%$ )

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|------------------|------|------|------|------|

| CS setup time                                          | tcss             | 200  | _    | _    | ns   |

| CS hold time                                           | <b>t</b> csH     | 0    | _    | _    | ns   |

| Data setup time                                        | tois             | 150  | _    | _    | ns   |

| Data hold time                                         | <b>t</b> DIH     | 150  | _    | _    | ns   |

| DO rise delay time                                     | t <sub>PD1</sub> | _    | _    | 350  | ns   |

| DO fall delay time                                     | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| Self-timing programming cycle                          | te/w             | _    | _    | 10   | ms   |

| CS minimum high level time                             | tcs              | 1    | _    | _    | μs   |

| Time when DO goes High-Z (via $\overline{\text{CS}}$ ) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time                             | twн              | 450  | _    | _    | ns   |

| Data clock low level time                              | tw∟              | 450  | _    | _    | ns   |

| Write control setup time                               | twcs             | 0    | _    |      | ns   |

| Write control hold time                                | twcн             | 0    | _    | _    | ns   |

# $\bullet$ BR9010 / F / FV: At 3V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 3V $\pm$ 10%)

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|------------------|------|------|------|------|

| CS setup time                                          | tcss             | 200  | _    | _    | ns   |

| CS hold time                                           | tсsн             | 0    | _    | _    | ns   |

| Data setup time                                        | tois             | 150  | _    | _    | ns   |

| Data hold time                                         | tын              | 150  | _    | _    | ns   |

| DO rise delay time                                     | t <sub>PD1</sub> | _    | _    | 350  | ns   |

| DO fall delay time                                     | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| Self-timing programming cycle                          | te/w             | _    | _    | 15   | ms   |

| CS minimum high level time                             | tcs              | 1    | _    | _    | μs   |

| Time when DO goes High-Z (via $\overline{\text{CS}}$ ) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time                             | twн              | 450  | _    | _    | ns   |

| Data clock low level time                              | tw∟              | 450  | _    | _    | ns   |

| Write control setup time                               | twcs             | 0    | _    | _    | ns   |

| Write control hold time                                | twcн             | 0    | _    | _    | ns   |

# Operation timing characteristics

BR9020 / F / FV: At 5V (unless otherwise noted,  $Ta = -40 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 5V \pm 10\%$ )

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|------------------|------|------|------|------|

| CS setup time                                          | tcss             | 200  | _    | _    | ns   |

| CS hold time                                           | tсsн             | 0    | _    | _    | ns   |

| Data setup time                                        | tois             | 150  | _    | _    | ns   |

| Data hold time                                         | <b>t</b> DIH     | 150  | _    | _    | ns   |

| DO rise delay time                                     | t <sub>PD1</sub> | _    | _    | 350  | ns   |

| DO fall delay time                                     | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| Self-timing programming cycle                          | te/w             | _    | _    | 10   | ms   |

| CS minimum high level time                             | tcs              | 1    | _    | _    | μs   |

| READY / BUSY display valid time                        | tsv              | _    | _    | 1    | μs   |

| Time when DO goes High-Z (via $\overline{\text{CS}}$ ) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time                             | twн              | 450  | _    | _    | ns   |

| Data clock low level time                              | twL              | 450  | _    | _    | ns   |

| Write control setup time                               | twcs             | 0    | _    | _    | ns   |

| Write control hold time                                | twcн             | 0    | _    | _    | ns   |

# $\bullet$ BR9020 / F / FV: At 3V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 3V $\pm$ 10%)

| Parameter                         | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------|------|------|------|------|

| CS setup time                     | tcss             | 200  | _    | _    | ns   |

| CS hold time                      | tсsн             | 0    | _    | _    | ns   |

| Data setup time                   | tois             | 150  | _    | _    | ns   |

| Data hold time                    | tын              | 150  | _    | _    | ns   |

| DO rise delay time                | t <sub>PD1</sub> | _    | _    | 350  | ns   |

| DO fall delay time                | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| Self-timing programming cycle     | te/w             | _    | _    | 15   | ms   |

| CS minimum high level time        | tcs              | 1    | _    | _    | μs   |

| READY / BUSY display valid time   | tsv              | _    | _    | 1    | μs   |

| Time when DO goes High-Z (via CS) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time        | twн              | 450  | _    | _    | ns   |

| Data clock low level time         | twL              | 450  | _    | _    | ns   |

| Write control setup time          | twcs             | 0    | _    | _    | ns   |

| Write control hold time           | twcн             | 0    | _    | _    | ns   |

# Operation timing characteristics

BR9040 / F: At 5V (unless otherwise noted,  $Ta = -40 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 5V \pm 10\%$ )

| Parameter                         | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------|------|------|------|------|

| CS setup time                     | tcss             | 200  | _    | _    | ns   |

| CS hold time                      | tсsн             | 0    | _    | _    | ns   |

| Data setup time                   | tois             | 150  | _    | _    | ns   |

| Data hold time                    | tын              | 150  | _    | _    | ns   |

| DO rise delay time                | t <sub>PD1</sub> | _    | _    | 350  | ns   |

| DO fall delay time                | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| Self-timing programming cycle     | te/w             | _    | _    | 10   | ms   |

| CS minimum high level time        | tcs              | 1    | _    | _    | μs   |

| READY / BUSY display valid time   | tsv              | _    | _    | 1    | μs   |

| Time when DO goes High-Z (via CS) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time        | twн              | 500  | _    | _    | ns   |

| Data clock low level time         | tw∟              | 500  | _    | _    | ns   |

| Write control setup time          | twcs             | 0    | _    | _    | ns   |

| Write control hold time           | twcн             | 0    | _    | _    | ns   |

# $\bullet$ BR9040 / F: At 3V (unless otherwise noted, Ta = -40 to +85°C, Vcc = 3V $\pm$ 10%)

| Parameter                                              | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|------------------|------|------|------|------|

| CS setup time                                          | tcss             | 200  | _    | _    | ns   |

| CS hold time                                           | tсsн             | 0    | _    | _    | ns   |

| Data setup time                                        | tois             | 150  | _    | _    | ns   |

| Data hold time                                         | <b>t</b> DIH     | 150  | _    | _    | ns   |

| DO rise delay time Vcc = 3.0 ~ 3.3V                    | <b>t</b> PD1     | _    | _    | 350  | ns   |

| DO fall delay time Vcc = 3.0 ~ 3.3V                    | t <sub>PD0</sub> | _    | _    | 350  | ns   |

| DO rise delay time Vcc = 2.7 ~ 3.0V                    | <b>t</b> PD1     | _    | _    | 500  | ns   |

| DO fall delay time Vcc = 2.7 ~ 3.0V                    | t <sub>PD0</sub> | _    | _    | 500  | ns   |

| Self-timing programming cycle                          | te/w             | _    | _    | 15   | ms   |

| CS minimum high level time                             | tcs              | 1    | _    | _    | μs   |

| READY / BUSY display valid time                        | tsv              | _    | _    | 1    | μs   |

| Time when DO goes High-Z (via $\overline{\text{CS}}$ ) | tон              | 0    | _    | 400  | ns   |

| Data clock high level time Vcc = 3.0 ~ 3.3V            | twн              | 500  | _    | _    | ns   |

| Data clock low level time Vcc = 3.0 ~ 3.3V             | twL              | 500  | _    | _    | ns   |

| Data clock high level time Vcc = 2.7 ~ 3.0V            | twн              | 650  | _    | _    | ns   |

| Data clock low level time Vcc = 2.7 ~ 3.0V             | twL              | 650  | _    | _    | ns   |

| Write control setup time                               | twcs             | 0    | _    | _    | ns   |

| Write control hold time                                | twcн             | 0    | _    | _    | ns   |

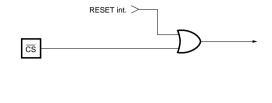

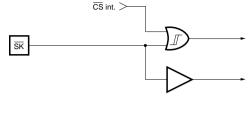

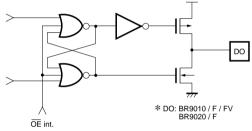

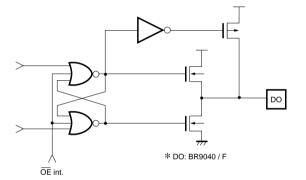

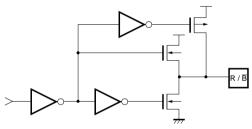

# ●Input / output circuits

# (1) Input circuits

# (2) Output circuits

$R / \overline{B}$ : BR9020 / F, BR9040 / F

# Circuit operation

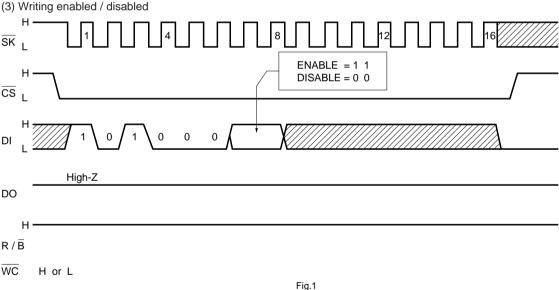

# (1) Command mode

| Command               |         | Start bit | Operating code | Address                                                 | Data          |

|-----------------------|---------|-----------|----------------|---------------------------------------------------------|---------------|

| Read                  | (READ)  | 1010      | 1000           | A0 A1 A2 A3 A4 A5 (A6) <sup>☆2</sup> (A7) <sup>☆1</sup> |               |

| Write                 | (WRITE) | 1010      | 0100           | A0 A1 A2 A3 A4 A5 (A6) <sup>☆2</sup> (A7) <sup>☆1</sup> | D0 D1—D14 D15 |

| Erase / Write enabled | (EWEN)  | 1010      | 0011           | * * * * * * *                                           |               |

| Erase / Write disable | (EWDS)  | 1010      | 0000           | * * * * * * * *                                         |               |

★ Either V<sub>IH</sub> or V<sub>IL</sub>

- Data is read in on the rising edge of  $\overline{SK}$ . Data is output in synchronism with the  $\overline{SK}$  falling edge.

- During a READ operation, data is output from DO in synchronization with the SK rise.

- WC is related to the write command only. Read, erase / write enable, erase / write disable commands can be executed irrespective of the state of WC.

- . .9.

- When the power supply is turned on, the latch used to acknowledge writing is reset in the same way as when the

write disable command is executed. Before entering the write mode, the write enabled mode must first be entered.

Once the write enabled mode has been recognized, it remains valid until the write disabled mode is entered, or

the power supply is turned off.

- 2) The clock is no longer necessary after the first 16 clock pulses have been received. Any subsequent input will be ignored.

- 3) WC does not exist for either the write enabled or write disabled command, so WC may be either HIGH or LOW when the command is being input.

- 4) Commands are received in these modes by means of 8-bit operating codes. Please be aware that, after an operating code has been entered, commands will not be canceled even if  $\overline{CS}$  is set to HIGH. (To cancel a command, either turn off the power supply, or input the command once again.)

### Circuit operation

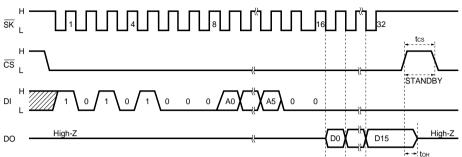

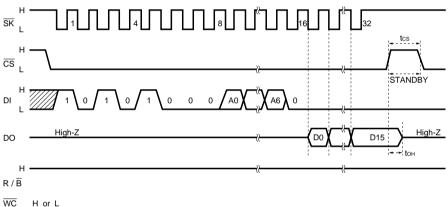

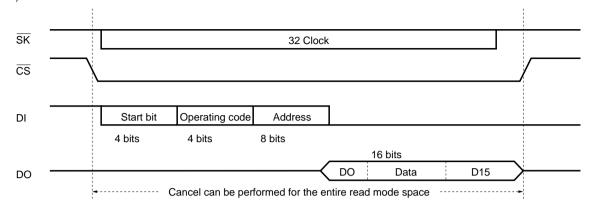

# (4) Read cycle

WC H or L

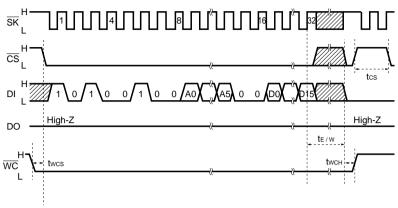

Fig.2 BR9010 / F / FV

H or L

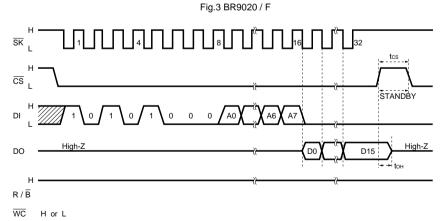

Fig.4 BR9040 / F

1) After the fall of the 16th clock pulse, 16-bit data is output from the DO pin in synchronization with the falling edge of the  $\overline{SK}$  signal. (DO output changes at a time lag of tpdo, tpd1 because of internal circuit delay following the falling edge of the SK signal. During the tepo and tept timing, the tep time should be assured before data is read, to avoid the previous data being lost. See the synchronized data input / output timing chart in Fig. 1.)

# Circuit operation

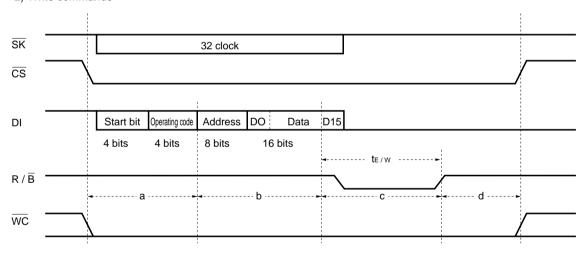

# (5) Writing cycle

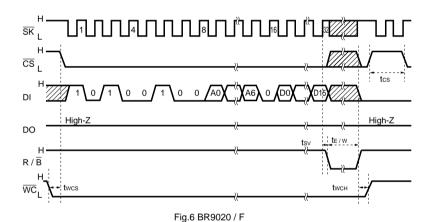

Fig.5 BR9010 / F / FV

Fig.7 BR9040 / F

- 1) During input in the write mode,  $\overline{CS}$  must be LOW, but once writing starts,  $\overline{CS}$  may be either HIGH or LOW. However, if  $\overline{CS}$  and  $\overline{WC}$  share the same connection, both  $\overline{CS}$  and  $\overline{WC}$  should be set to LOW during writing operations.

- (If the WC pin is set to HIGH during a writing operation, writing will be forcibly interrupted at that point. If this happens, the data for that address may be lost, in which case it should be rewritten to that address.)

- 2) Following input of a write command,  $\overline{CS}$  goes HIGH. If  $\overline{CS}$  is then set to LOW, data will be received from  $\overline{SK}$  and DI, because the command reception status has been entered.

- If  $\overline{\text{CS}}$  remains LOW following command input, however, without first going HIGH, command input will be canceled until  $\overline{\text{CS}}$  is set to HIGH.

- 3) Starting from the rising edge of the 32nd clock, the R / B pin goes LOW after RSV has elapsed.

- 4) The R /  $\overline{B}$  pin is LOW during writing operations. (Following the rising edge of  $\overline{SK}$  after the last data D15 has been read, the internal timer circuit is activated, and writing of data in the memory cell is automatically completed during te/w.) At this point,  $\overline{SK}$  input may be either HIGH or LOW during te/w.

- 5) Following input of a write command, if  $\overline{CS}$  falls while  $\overline{SK}$  is LOW, the R /  $\overline{B}$  status can be displayed from the DO pin. (See the section on READY /  $\overline{BUSY}$  states.)

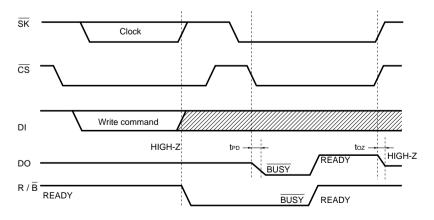

- (6) READY / BUSY display (R / B pin and DO pin)

- 1) This display outputs the internal status signal; the R /  $\overline{B}$  pin outputs the HIGH or LOW status at all times. The display can also be output from the DO pin. Following completion of the writing command, if  $\overline{CS}$  falls while  $\overline{SK}$  is LOW, either HIGH or LOW is output. (The display can also be output without using the R /  $\overline{B}$  pin, leaving it open.)

- 2) When writing data to a memory cell, the READY /  $\overline{BUSY}$  display is output from the rise of the 32nd clock pulse of the  $\overline{SK}$  signal after tsv, from the R /  $\overline{B}$  pin.

$R / \overline{B}$  display = LOW: writing in progress

(The internal timer circuit is activated, and after the te/w timing has been created, the timer circuit stops automatically. Writing of data to the memory cell is done during the te/w timing, during which time other commands cannot be received.)

$R / \overline{B}$  display = HIGH: command standby state

(Writing of data to the memory cell has been completed and the next command can be received.)

Fig.8 R / B status output timing

### Operation notes

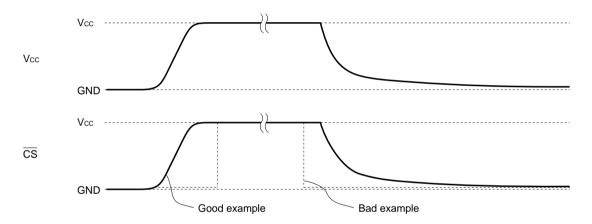

- (1) Turning the power supply on and off

- 1) When the power supply is turned on and off,  $\overline{CS}$  should be set to HIGH (= Vcc).

- 2) When  $\overline{CS}$  is LOW, the command input reception state (active) is entered. If the power supply is turned on in this state, erroneous operations and erroneous writing can occur because of noise and other factors. To avoid this, make sure  $\overline{CS}$  is set to HIGH (= Vcc) before turning on the power supply.

(Good example) Here, the  $\overline{CS}$  pin is pulled up to Vcc.

When turning off the power supply, wait at least 10msec before turning it on again. Failing to observe this condition can result in the internal circuit failing to be reset when the power supply is turned on.

(Bad example)  $\overline{CS}$  is LOW when the power supply is turned on or off

In this case, because  $\overline{\text{CS}}$  remains LOW, the EEPROM may perform erroneous operations or write erroneous data because of noise or other factors.

\* Please be aware that the case shown in this example can also occur if  $\overline{\text{CS}}$  input is HIGH-Z.

### (2) Noise countermeasures

1) SKnoise

If noise occurs at the rise of the  $\overline{SK}$  clock input, the clock is assumed to be excessive, and this can cause malfunction because the bits are out of alignment.

2) WC noise

During a writing operation, noise at the  $\overline{WC}$  pin can be erroneously judged to be data, and this can cause writing to be forcibly interrupted.

3) Vcc noise

Noise and surges on the power supply line can cause malfunction. We recommend installing a bypass capacitor between the power supply and ground to eliminate this problem.

- (3) Canceling modes

- 1) Read commands

WC H or L

Cancellation method: CS HIGH

2) Write commands

### Canceling methods

- a: Canceled by setting CS HIGH. The WC pin is not involved.

- b: If the WC pin goes HIGH for even a second, writing is forcibly interrupted. Cancellation occurs even if the CS pin is HIGH. At this point, data has not been written to the memory, so the data in the designated address has not yet been changed.

- c: The operation is forcibly canceled by setting the  $\overline{WC}$  pin to HIGH or turning off the power supply (although we do not recommend using this method). The data in the designated address is not guaranteed and should be written once again.

- d: If  $\overline{CS}$  is set to HIGH while the R /  $\overline{B}$  signal is HIGH (following the te/w timing), the IC is reset internally, and waits for the next command to be input.

# ●External dimensions (Units: mm)

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for EEPROM category:

Click to view products by ROHM manufacturer:

Other Similar products are found below:

M29F040-70K6 718278CB 718620G 444358RB 444362FB BR93C46-WMN7TP EEROMH CAT25320YIGT-KK LE24C162-R-E 5962-8751409YA BR9016AF-WE2 LE2464DXATBG CAS93C66VP2I-GT3 W60002FT20T CAT24S128C4UTR ZD24C64B-SSGMA0 BL24C04F-RRRC S-25C040A0I-I8T1U AT24C256BY7-YH-T M24C64-DFCT6TPK BR24C21FJ-E2 BR24G02FVJ-3GTE2 BR24L16FJ-WE2 BR24L16FJ-WE2 BR24S16FJ-WE2 BR24S256F-WE2 BR93L56RFV-WE2 BR93L66F-WE2 BR93L76RFV-WE2 CAT24C64C4CTR CHL24C32WEGT3 AT28HC256E-12SU-T AT93C46DY6-YH-T BR24T02FVT-WSGE2 M35B32-WMN6TP M24C64-FMC6TG M24C08-WDW6TP CAT25080VP2IGTQH CAT25020ZIGT-QP CAT24C01VP2I-GT3 CAT93C76BZI-GT3 CAT64LC40WI-T3 CAT25256HU4E-GT3 CAT25128VP2I-GT3 CAT25040VP2I-GT3 CAT25020VP2I-GT3 CAT24C16ZI-G CAT24C05LI-G CAT24C01ZI-G CAT24C05WI-G