Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd.

October 1, 2020

**FEDL22Q62X-02**

Issue date: Jul 17, 2020

## ML22Q623 / ML22Q624 / ML22Q625 / ML22Q626

4-Channel Mixing Speech Synthesis LSI with Built-in Flash Memory

#### Overview

ML22Q623/ML22Q625/ML22Q626 is a 4-channel mixing speech synthesis LSI with a flash memory for sound data. It is equipped with a clock synchronous serial interface.

It adopts a HQ-ADPCM\*1, 16-bit D/A converter, and low-pass filter for high sound quality, and incorporates a 1.0W mono speaker amplifier for driving speakers directly. It is also equipped with a function to detect failure.

The functions necessary for sound output are integrated into a single chip, so that sound functions can be realized simply by adding this LSI.

## • Memory capacity and maximum sound production time (HQ-ADPCM<sup>\*1</sup> algorithm, registered phrase 1024)

| Product Name | Flash memory capacity | Maximum s              | sound production        | time (sec)              |

|--------------|-----------------------|------------------------|-------------------------|-------------------------|

|              |                       | f <sub>s</sub> =8.0kHz | $f_s = 16.0 \text{kHz}$ | $f_s = 32.0 \text{kHz}$ |

| ML22Q623     | 4Mbits                | 161                    | 81                      | 40                      |

| ML22Q624     | 8Mbits                | 325                    | 162                     | 81                      |

| ML22Q625     | 16Mbits               | 652                    | 326                     | 163                     |

| ML22Q626     | 32Mbits               | 1308                   | 654                     | 327                     |

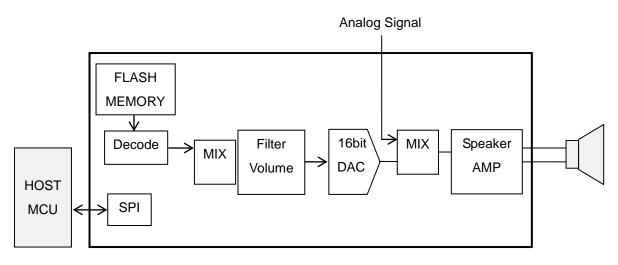

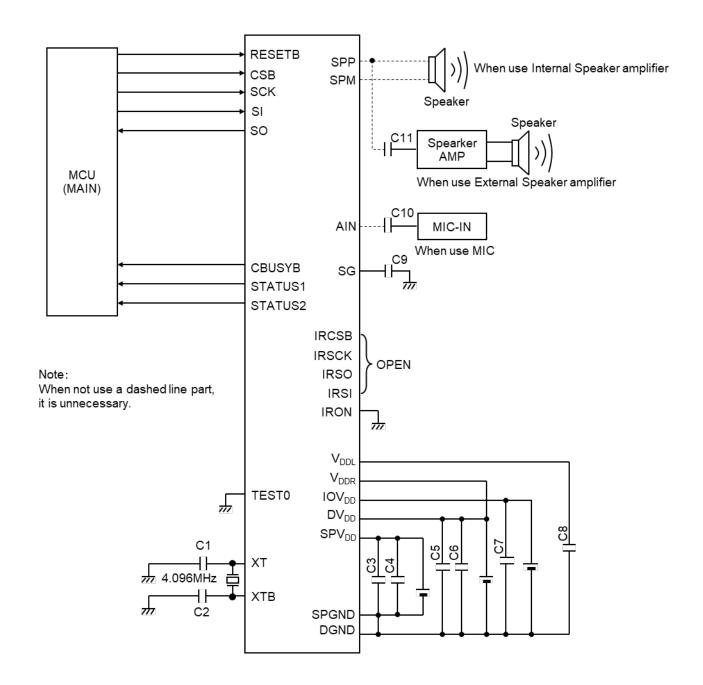

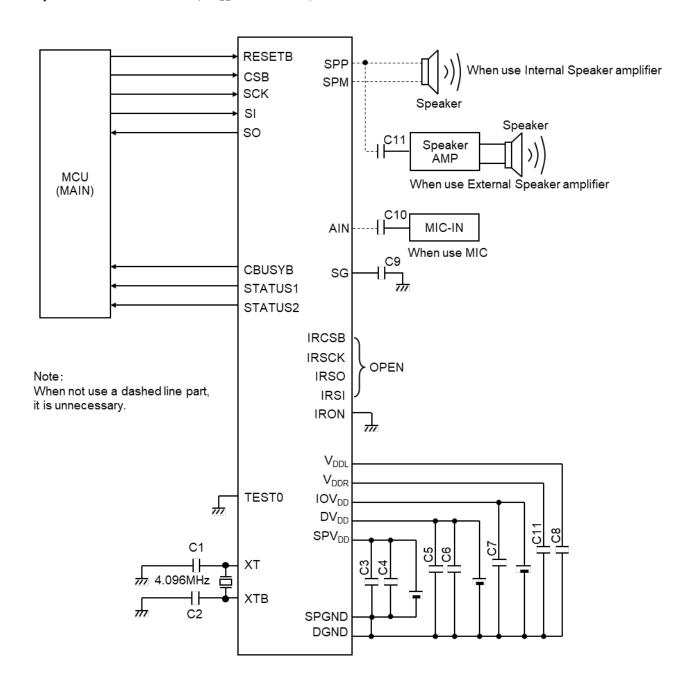

**Application Circuit**

**ML22Q62X**

#### ■ Feature

• Sound data

Speech synthesis algorithm: The algorithm can be specified for each phrase.

HQ-ADPCM/4bit ADPCM2/8bit non-linear PCM /

8bit Straight PCM/16bit Straight PCM

Sampling frequency: The sampling frequency can be specified for each phrase.

10.7/21.3kHz, 6.4/12.8/25.6kHz, 8.0/16.0/32.0kHz, 11.025/22.05/44.1kHz, 12.0/24.0/48.0kHz

Maximum number of phrases: 4096 Phrases

• Edit ROM function

• Playback function

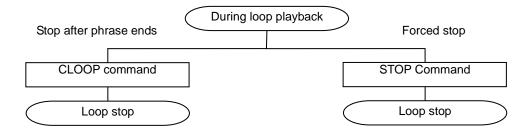

Repeat function: LOOP command Mixing-function: Up to 4-channel

Volume adjustment function: CVOL command 128 levels (including off-state)

AVOL command 16 levels (including off-state)

• Low-pass filter

• 16-bit D/A converter

• Speaker amplifier: Class AB/D 1. 0W  $8\Omega$  (SPV<sub>DD</sub> =5V, Ta=25  $^{\circ}$ C)

Line amplifier output: 10kΩ driving (Exclusive operation from speaker amplifier output)

External analog sound input (at the time Class AB speaker amplifier choice, with analog mixing function)

• MCU command interface: Clock Synchronous Serial Interface

• Failure detection function

Speaker short detection: Speaker pin ground fault detection, speaker pin short detection

Speaker disconnection detection

Thermal detection Clock error detection Flash memory error detection

Clock backup function

• Master clock frequency: 4.096MHz, 4.000MHz

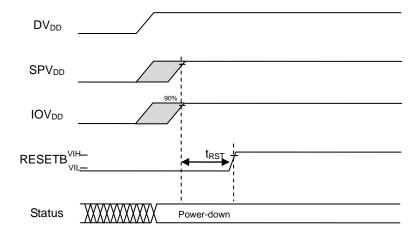

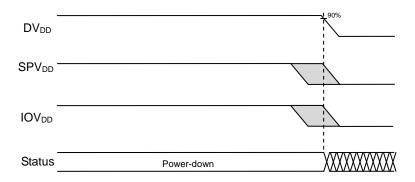

• Power-supply voltage 2.7V to 5.5V \*1

$DV_{DD},~\text{SPV}_{DD}$  and  $IOV_{DD}$  can be set independently. (SPV  $_{DD}\!\!\ge\!\!DV_{DD}\!)$

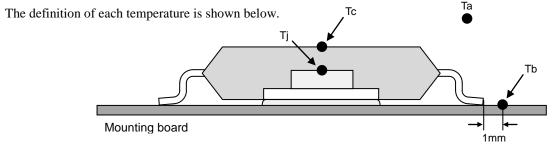

• Operating temperature range:  $-40^{\circ}\text{C to} + 70^{\circ}\text{C}^{*2}$

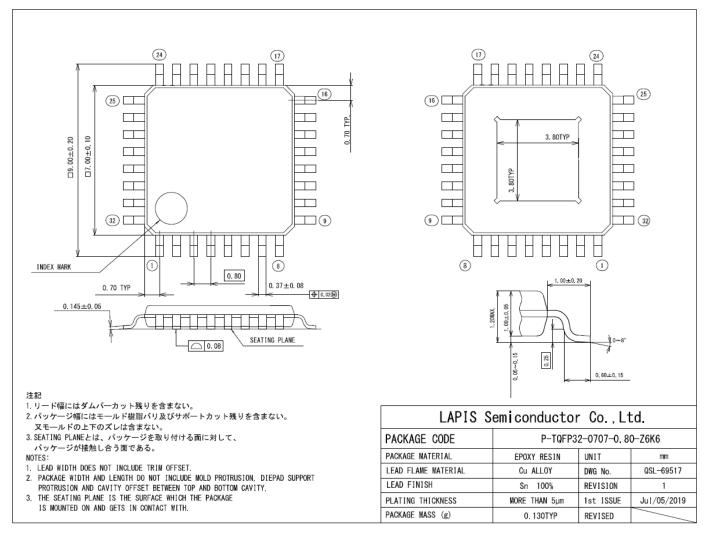

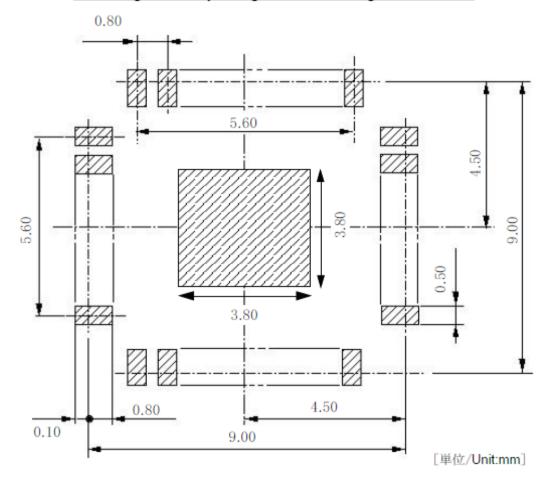

• Package: 32-pin TQFP (7mm x 7mm, 0.8mm pitch)

• Ordered Part Name: ML22Q62X-NNTB, ML22Q62X-xxxTB (32-pin TQFP)\*3

<sup>\*1</sup> Handle  $V_{DDR}$  pin in two different ways depending on the voltage range 2.7-3.6V or 3.3-5.5V. Refer to the "Application Circuit".

<sup>\*2</sup> The operating time of the speaker amplifier may be limited depending on the average ambient temperature (Ta) used.

<sup>\*3</sup> The NNN is blanked. xxx represents ROM code number.

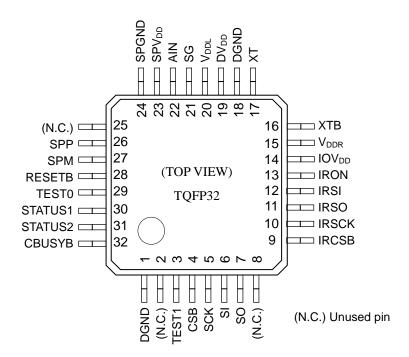

- Pin Configuration (TOP VIEW)

- ML22Q62X-NNNTB/ML22Q62X-xxxTB

ML22Q62X

## ■ Pin Description

| Pin  | Symbol | I/O | Attribute | Description                                                                                                                                                                                                                                                                                                                                                                                 | Initial<br>value *1 |

|------|--------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1,18 | DGND   | G   | -         | Digital ground pin.                                                                                                                                                                                                                                                                                                                                                                         | _                   |

| 3    | TEST1  | 0   | -         | Output pin for testing. Leave open.                                                                                                                                                                                                                                                                                                                                                         | Hi-Z                |

| 4    | CSB    | ı   | Negative  | Synchronous serial interface chip select pin. The SCK and SI inputs are accepted only when this pin is at the "L" level.                                                                                                                                                                                                                                                                    | Н                   |

| 5    | SCK    | I   | -         | Synchronous serial interface clock input pin.                                                                                                                                                                                                                                                                                                                                               | L                   |

| 6    | SI     | ı   | -         | Synchronous serial interface data input pin. Data is fetched in synchronization with SCK.                                                                                                                                                                                                                                                                                                   | L                   |

| 7    | SO     | 0   | -         | Synchronous serial interface data output pin. When the CSB pin is at an "L" level, data is output in synchronization with SCK. When the CSB pin is at an "H" level, this pin enters a high-impedance state.                                                                                                                                                                                 | Hi-Z                |

| 9    | IRCSB  | ı   | Negative  | Flash memory interface chip select input pin. Input the "H" level during non-access and the "L" level during access. Setting the IRON pin to "H" enables input.                                                                                                                                                                                                                             | Н                   |

| 10   | IRSCK  | I   | -         | Flash memory interface serial clock input pin. Setting the IRON pin to "H" enables input.                                                                                                                                                                                                                                                                                                   | Н                   |

| 11   | IRSO   | 0   | -         | Flash memory interface serial data output pin. Setting the IRON pin to "H" enables output.                                                                                                                                                                                                                                                                                                  | Hi-Z <sup>*2</sup>  |

| 12   | IRSI   | I   | -         | Flash memory interface serial data input pin. Setting the IRON pin to "H" enables input.                                                                                                                                                                                                                                                                                                    | L                   |

| 13   | IRON   | I   | Positive  | Pin to enable the flash memory interface.  When this bit is set to "L", the flash memory interface pin is disabled. A pull-down resistor is internally connected to the LSI.  Set this bit to "L" during playback operation using flash memory.  Setting this bit to "H" allows rewriting of the flash memory using the flash memory interface.  Set this bit to "H" for onboard rewriting. | L                   |

<sup>\*1</sup> Initial value at reset input and power-down. The pin whose IO is "I" indicates a fixed level from outside.

\*2 IRON pin "L" setting status

## ML22Q62X

| Pin | Symbol             | I/O | Attribute | Description                                                                                                                                                                                                                                                                                                                                        | Initial<br>value *1 |

|-----|--------------------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 14  | IOV <sub>DD</sub>  | Р   | -         | Flash memory interface power supply pin. Connect to DV <sub>DD</sub> pin even when not using flash memory interface. Connect a bypass capacitor between this pin and the DGND pin.                                                                                                                                                                 | _                   |

| 15  | $V_{\mathrm{DDR}}$ | 0   | -         | 3.0V regulator outputs. Used as a power supply for flash memory. Connect a capacitor between this pin and DGND pin as close as possible. Connect this pin to the $DV_{DD}$ pin when $DV_{DD} = 2.7$ to 3.6V                                                                                                                                        | L                   |

| 16  | XTB                | 0   | Negative  | Crystal or ceramic resonator connection pin. When an external clock is used, leave it open and capacitor is not required when a crystal or ceramic resonator is connected. When using a resonator, connect it as close as possible. Leave it open when not in use.                                                                                 | Н                   |

| 17  | XT                 | I   | Positive  | Crystal or ceramic resonator connection pin. A feedback resistor of about $1M\Omega$ is built in between the XT pin and the XTB pin. To use an external clock, input from this pin. Delete the capacitor when a crystal or ceramic resonator is connected. When using a resonator, connect it as close as possible. Leave it open when not in use. | L                   |

| 19  | $DV_DD$            | Р   | -         | Digital power supply pin. Connect a bypass capacitor between this pin and the DGND pin.                                                                                                                                                                                                                                                            |                     |

| 20  | $V_{DDL}$          | 0   | -         | 2.5V regulator output pin. Used as internal power supply. Connect a capacitor between this pin and DGND pin as close as possible.                                                                                                                                                                                                                  | L                   |

| 21  | SG                 | 0   | -         | Reference voltage output pin for the built-in speaker amplifier. Connect a capacitor between this pin and SPGND pin.                                                                                                                                                                                                                               | L                   |

| 22  | AIN                | I   | -         | Speaker amplifier analog signal input pin. Initially, input is disabled.                                                                                                                                                                                                                                                                           | L                   |

| 23  | SPV <sub>DD</sub>  | Р   | -         | Power supply pin for speaker amplifier. Connect a bypass capacitor between this pin and the SPGND pin.                                                                                                                                                                                                                                             | _                   |

| 24  | SPGND              | G   | -         | Speaker amplifier ground pin.                                                                                                                                                                                                                                                                                                                      | _                   |

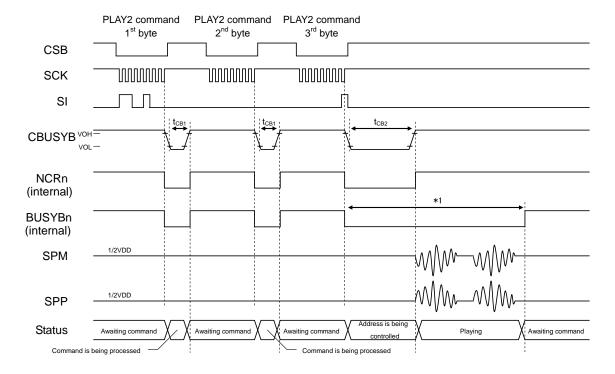

| 26  | SPP                | 0   | -         | Positive output pin of the speaker amplifier. Line amplifier outputs are also available with AMODE command.                                                                                                                                                                                                                                        | L                   |

| 27  | SPM                | 0   | -         | Negative output pin of the speaker amplifier.                                                                                                                                                                                                                                                                                                      | Hi-Z                |

<sup>\*1</sup> Initial value at reset input and power-down. The pin whose IO is "I" indicates a fixed level from outside.

| Pin    | Symbol  | I/O | Attribute | Description                                                                                                                                                                                                                                                                                                               | Initial<br>value *1 |

|--------|---------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

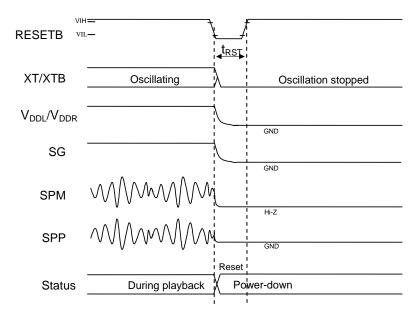

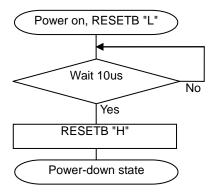

| 28     | RESETB  | I   | Negative  | Reset input pin. The LSI is initialized by the "L" level input. After a reset is input, all the circuits stop operating and enter the power-down state. At power-on, input an "L" level to this pin. After the power supply voltage stabilizes, set this pin to an "H" level. A pull-up resistor is internally connected. | ( <sup>*2</sup> )   |

| 29     | TEST0   | Ι   | Positive  | Input pin for testing. A pull-down resistor is internally connected. Fix to the DGND.                                                                                                                                                                                                                                     | L                   |

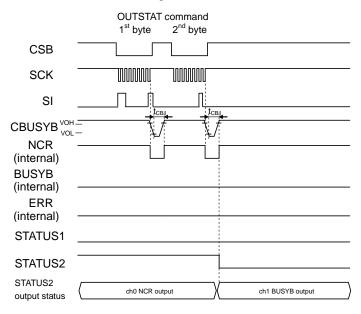

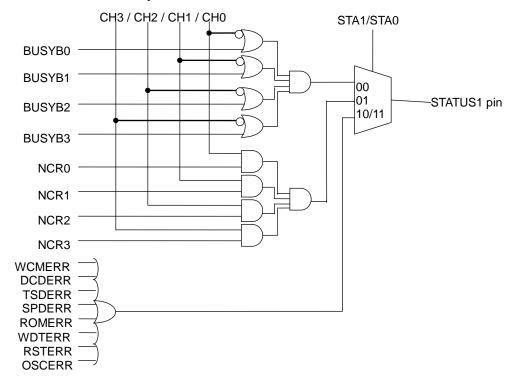

| 30     | STATUS1 | 0   | -         | Status/error output pin 1.  Execute OUTSTAT command to select BUSYB*3 and NCR*3 in each channel, or errors.  The initial value is BUSYB*3 of channel 0, and output data is "H" level.                                                                                                                                     | Н                   |

| 31     | STATUS2 | 0   | -         | Status/error output pin 2. Execute OUTSTAT command to select BUSYB*3 and NCR*3 in each channel, or errors. The initial value is BUSYB*3 of channel 0, and output data is "H" level.                                                                                                                                       | Н                   |

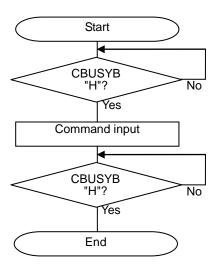

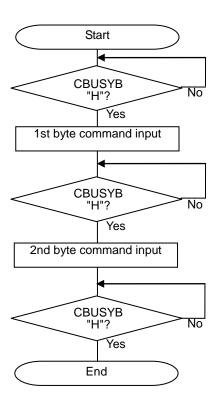

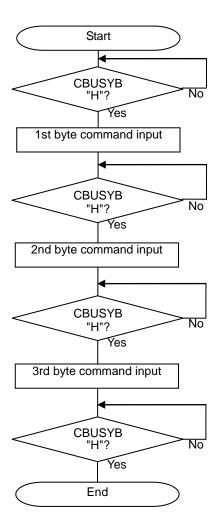

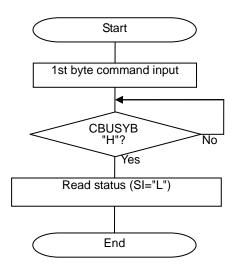

| 32     | CBUSYB  | 0   | Negative  | Command processing status signal output pin. An "L" level is output during command processing. Be sure to input a command with this pin at an "H" level.                                                                                                                                                                  | ( <sup>*2</sup> )   |

| 2,8,25 | N.C.    | -   | -         | Unused pin.<br>Leave open.                                                                                                                                                                                                                                                                                                | Hi-Z                |

<sup>\*1</sup> Initial value at reset input and power-down. The pin whose IO is "I" indicates a fixed level from outside.

\*2 "L" at reset, "H" at power-down

\*3 For NCR, BUSYB, refer to the description of "RDSTAT command".

### ■ Termination of Unused Pins

This section explains how to terminate unused pins.

| Symbol   | Pacammonded ain termination       |

|----------|-----------------------------------|

|          | Recommended pin termination       |

| IRON     | Connect to the DGND.              |

| IRCSB    | Connect to the DV <sub>DD</sub> . |

| IRSCK    | Connect to the DGND.              |

| IRSI     | Connect to the DGND.              |

| XT       | Logvo opon                        |

| XTB      | Leave open.                       |

| AIN      | Connect to the SPGND.             |

| TEST0    | Connect to the DGND.              |

| N.C.     |                                   |

| SO       |                                   |

| SPM      | Leave open.                       |

| STATUS1  |                                   |

| STATUS2  |                                   |

| 01711002 | l .                               |

■ I/O Equivalent Circuit

|                 | Equivalent Circuit | T                                                                                                   |

|-----------------|--------------------|-----------------------------------------------------------------------------------------------------|

| Classifi cation | Circuit            | Overview                                                                                            |

| A               |                    | Attribute: Input Power: DV <sub>DD</sub> Function: CMOS inputs with pull-down Applicable pin: TEST0 |

| В               |                    | Attribute: Input Power: IOV <sub>DD</sub> Function: CMOS inputs with pull-down Applicable pin: IRON |

| С               |                    | Attribute: Input Power: DV <sub>DD</sub> Function: CMOS inputs with pull-up Applicable pin: RESETB  |

| D               |                    | Attribute: Input Power: DV <sub>DD</sub> Function: CMOS inputs Applicable pins: SI, SCK, CSB        |

| Е               |                    | Attribute: Input Power: IOV <sub>DD</sub> Function: CMOS inputs Applicable pins: IRCSB, IRSCK       |

| Classifi | Circuit         | Overview                                                                                                                                  |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| cation   | Circuit         | Overview  Attribute: Input/output                                                                                                         |

| F        |                 | Attribute: Input/output Power: DV <sub>DD</sub> Function: CMOS inputs Function: CMOS outputs Applicable pins: STATUS1, STATUS2, CBUSYB,SO |

| G        |                 | Attribute: Input/output Power: IOV <sub>DD</sub> Function: CMOS inputs Function: CMOS outputs Applicable pin: IRSI                        |

| Н        |                 | Attribute: Input/output Power: IOV <sub>DD</sub> Function: CMOS inputs with pull-down Function: CMOS outputs Applicable pin: IRSO         |

| I        | XTB XTB XTT XTT | Attribute: Oscillator circuit Power: DV <sub>DD</sub> Function: 4.096M, 4.000MHz oscillation Applicable pins: XT, XTB                     |

| Classifi cation | Circuit        | Overview                                                                                    |

|-----------------|----------------|---------------------------------------------------------------------------------------------|

| J               | analog入力<br>SG | Attribute: Analog Power: SPV <sub>DD</sub> Function: Sound output Applicable pins: SPP, SPM |

| L               |                | Attribute: Analog Power: SPV <sub>DD</sub> Function: Sound input Applicable pins: AIN       |

ML22Q62X

### ■ Electrical characteristics

### • Absolute maximum rating

|                              |                           |                                                                           | DGND=SPGND=0V                  | , Ta=25°C |

|------------------------------|---------------------------|---------------------------------------------------------------------------|--------------------------------|-----------|

| Parameter                    | Symbol                    | Condition                                                                 | Rating                         | Unit      |

| Power supply voltage 1       | $DV_DD$ $IOV_DD$ $SPV_DD$ | _                                                                         | -0.3 to +6.0                   | V         |

| Power supply voltage 2       | $V_{DDR}$                 | _                                                                         | -0.3 to +4.6                   | V         |

| Input voltage 1              | V <sub>IN1</sub>          | _                                                                         | -0.3 to DV <sub>DD</sub> +0.3  | V         |

| Input voltage 2              | $V_{IN2}$                 | _                                                                         | -0.3 to IOV <sub>DD</sub> +0.3 | V         |

| Allowable loss               | $P_{D}$                   | When the LSI is mounted on JEDEC 4-layer board.<br>SPV <sub>DD</sub> = 5V | 1000                           | mW        |

| Output short-circuit current | los                       | Applies to pins other than SPM,SPP,VDDL and VDDR pins.                    | 10                             | mA        |

|                              |                           | Applies to SPM and SPP pins.                                              | 500                            | mA        |

|                              |                           | Applies to the $V_{DDL} / V_{DDR}$ pin.                                   | 50                             | mA        |

| Storage temperature          | $T_{STG}$                 | _                                                                         | -55 to +150                    | °C        |

### • Recommended operating conditions

|                                           |                   |           |                         |          | DGND=SI | PGND=0V |  |

|-------------------------------------------|-------------------|-----------|-------------------------|----------|---------|---------|--|

| Parameter                                 | Symbol            | Condition |                         | Range    |         |         |  |

| $DV_{DD},$                                | $DV_DD$           |           |                         | <u>-</u> |         |         |  |

| $IOV_DD,$                                 | $IOV_{DD}$        | _         | 2.7 to 3.6 / 3.3 to 5.5 |          |         | V       |  |

| SPV <sub>DD</sub> *1,Power-supply voltage | SPV <sub>DD</sub> |           |                         |          |         |         |  |

| Operating temperature                     | Тор               | <u> </u>  | -40 to +70              |          |         | °C      |  |

|                                           |                   |           | Min.                    | Тур.     | Max.    | MHz     |  |

| Master clock frequency                    | fosc              | _         | Тур                     | 4.096    | Тур     |         |  |

|                                           |                   |           | -5%                     | 4.000    | +5%     |         |  |

<sup>\*1</sup> SPV<sub>DD</sub> DV<sub>DD</sub>

## • Flash memory condition

| Parameter             | Symbol          | Condition      | Range      | Unit |

|-----------------------|-----------------|----------------|------------|------|

| Operating temperature | т               | At write/erase | 0 to +70   | °C   |

| Operating temperature | IOP             | At read        | -40 to +70 | °C   |

| Number of rewrites    | C <sub>EP</sub> | <del>_</del>   | 100        | Time |

| Data retention period | Y <sub>DR</sub> | <u>—</u>       | 10         | Year |

ML22Q62X

#### DC characteristics

SPV<sub>DD</sub>≥DV<sub>DD</sub>=IOV<sub>DD</sub>=2.7 to 5.5V, DGND=SPGND=0V, Ta=-40 to +70°C, Load capacitance of output pin =15pF(max.)

| -                                         |                   | $OV_{DD}=IOV_{DD}=2.7$ t                                                 | to 5.5V, DGNE           | SPGND=0V, Ta=-40 to                            | +70°C, Load ca         |                    | output pin =15p       | F(max.) |   |                 |        |

|-------------------------------------------|-------------------|--------------------------------------------------------------------------|-------------------------|------------------------------------------------|------------------------|--------------------|-----------------------|---------|---|-----------------|--------|

| Parameter                                 | Symbol            | Condi                                                                    | tion                    | Applicable pin                                 | Min.                   | Typ. <sup>*1</sup> | Max.                  | Unit    |   |                 |        |

| "H" input voltage 1                       | V <sub>IH1</sub>  | _                                                                        |                         | CSB/SCK/SI/<br>XT/RESETB/TEST0                 | 0.8×DV <sub>DD</sub>   | _                  | $DV_DD$               | V       |   |                 |        |

| "H" input voltage 2                       | V <sub>IH2</sub>  | _                                                                        |                         | IRCSB/IRSCK/<br>IRSI/IRON                      | 0.8×IOV <sub>DD</sub>  | _                  | IOV <sub>DD</sub>     | V       |   |                 |        |

| "L" input voltage 1                       | V <sub>IL1</sub>  | _                                                                        |                         | CSB/SCK/SI/<br>XT/RESETB/TEST0                 | 0                      | _                  | 0.2×DV <sub>DD</sub>  | V       |   |                 |        |

| "L" input voltage 2                       | V <sub>IL2</sub>  | _                                                                        |                         | IRCSB/IRSCK/IRSI/<br>IRON                      | 0                      | _                  | 0.2×IOV <sub>DD</sub> | V       |   |                 |        |

| "H" output voltage 1                      | V <sub>OH1</sub>  | I <sub>OH</sub> = -5                                                     | 50μΑ                    | XTB                                            | DV <sub>DD</sub> -0.4  | _                  | _                     | V       |   |                 |        |

| "H" output voltage 2                      | V <sub>OH2</sub>  | I <sub>OH</sub> = -                                                      | 1mA                     | SO/CBUSYB/<br>STATUS1/STATUS2                  | DV <sub>DD</sub> -0.4  | _                  | _                     | V       |   |                 |        |

| "H" output voltage 3                      | V <sub>OH3</sub>  | I <sub>OH</sub> = -1                                                     | 1mA                     | IRSO                                           | IOV <sub>DD</sub> -0.4 | _                  | _                     | V       |   |                 |        |

| "L" output voltage 1                      | $V_{OL1}$         | I <sub>OL</sub> = 5                                                      | 0μΑ                     | XTB                                            | _                      | _                  | 0.4                   | V       |   |                 |        |

| "L" output voltage 2                      | V <sub>OL2</sub>  | I <sub>OL</sub> = 2                                                      | 2mA                     | SO/CBUSYB/<br>STATUS1/STATUS2                  | _                      | _                  | 0.4                   | V       |   |                 |        |

| "L" output voltage 3                      | V <sub>OL3</sub>  | $I_{OL} = 2$                                                             | 2mA                     | IRSO                                           | _                      | _                  | 0.4                   | V       |   |                 |        |

| Output leakage<br>current 1               | I <sub>OOH1</sub> | VOH=[<br>(in high-imped                                                  |                         | SO                                             | _                      | _                  | 10                    | μA      |   |                 |        |

|                                           | I <sub>OOL1</sub> | VOL=D<br>(in high-imped                                                  | _                       |                                                | -10                    | _                  | _                     | μA      |   |                 |        |

| Output leakage current 2                  | I <sub>OOH2</sub> | VOH=IOV <sub>DD</sub> (in high-impedance state)                          |                         | IRSO                                           | _                      | _                  | 10                    | μA      |   |                 |        |

|                                           | I <sub>OOL2</sub> | VOL=D<br>(in high-imped                                                  |                         |                                                | -10                    | _                  | _                     | μA      |   |                 |        |

| "H" input current 1                       | I <sub>IH1</sub>  | V <sub>IH</sub> = D                                                      | )V <sub>DD</sub>        | XT                                             | 0.8                    | 5.0                | 20                    | μA      |   |                 |        |

| "H" input current 2                       | I <sub>IH2</sub>  | V <sub>IH</sub> = D                                                      | $V_{DD}$                | RESETB/CSB/SCK/SI                              | _                      | _                  | 10                    | μA      |   |                 |        |

| "H" input current 3                       | I <sub>IH3</sub>  | V <sub>IH</sub> = D                                                      | $V_{DD}$                | TEST0                                          | 20                     | 500                | 1000                  | μΑ      |   |                 |        |

| "H" input current 4                       | I <sub>IH4</sub>  | $V_{IH} = IC$                                                            |                         | IRCSB/IRSCK/IRSI                               | _                      | _                  | 10                    | μΑ      |   |                 |        |

| "H" input current 5                       | I <sub>IH5</sub>  | $V_{IH} = IC$                                                            |                         | IRON                                           | 20                     | 500                | 1000                  | μΑ      |   |                 |        |

| "L" input current 1                       | I <sub>IL1</sub>  | V <sub>IL</sub> = D                                                      | GND                     | XT                                             | -20                    | -5.0               | -0.8                  | μΑ      |   |                 |        |

| "L" input current 2                       | I <sub>IL2</sub>  | V <sub>IL</sub> = D                                                      | GND                     | CSB/SCK/SI/<br>IRCSB/IRSCK/IRSI/<br>IRON/TEST0 | -10                    | _                  | _                     | μA      |   |                 |        |

| "L" input current 3                       | I <sub>IL3</sub>  | $V_{IL} = De$                                                            |                         | RESETB                                         | -400                   | -100               | -2                    | μΑ      |   |                 |        |

| During playback<br>Current<br>consumption | I <sub>DDO</sub>  | f <sub>OSC</sub> =4.09<br>Fs=48kHz,<br>During HQ<br>playba<br>SPP/SPM No | f=1kHz,<br>ADPCM<br>ack | -                                              | _                      | _                  | 55 <sup>*3</sup>      | mA      |   |                 |        |

|                                           |                   | DV <sub>DD</sub> =IOV <sub>DD</sub> =<br>SPV <sub>DD</sub> =             | Ta=-40 to<br>+55°C      |                                                | _                      | 1 <sup>*3</sup>    | 10.0 <sup>*3</sup>    | μA      |   |                 |        |

| Power-down<br>Current                     |                   | 1                                                                        | la                      |                                                |                        | 3.3~5.5V           | Ta=-40 to<br>+70°C    | _       | _ | 1 <sup>*3</sup> | 30.0*3 |

| consumption                               | I <sub>DDS</sub>  | $DV_{DD}=IO_{DD}=$<br>$SPV_{DD}=V_{DDR}=$                                | Ta=-40 to<br>+55°C      | _                                              | _                      | 6*2*3              | 20.0*3                | μΑ      |   |                 |        |

|                                           |                   | 2.7~3.6V                                                                 | Ta=-40 to<br>+70°C      |                                                |                        | 6*2*3              | 80.0 <sup>*3</sup>    | μA      |   |                 |        |

<sup>\*3</sup> Total values of the  $DV_{DD}$  pin,  $SPV_{DD}$  pin, and  $IOV_{DD}$  pin

ML22Q62X

## • Analog Part Characteristics

$SPV_{DD} \ge DV_{DD} = IOV_{DD} = 2.7$  to 5.5V, DGND=SPGND=0V, Ta=-40 to +70°C, Load capacitance of output pin =15pF(max.)

| Parameter                                       | Symbol             | Condition                                                                              | Min.                          | Тур.                 | Max.                          | Unit |

|-------------------------------------------------|--------------------|----------------------------------------------------------------------------------------|-------------------------------|----------------------|-------------------------------|------|

| RC4MHz clock frequency                          | Frc                | Ta=-40 to +70°C                                                                        | 3.89                          | 4.096                | 4.31                          | MHz  |

| AIN pin input resistance                        | R <sub>AIN</sub>   | Input gain 0dB                                                                         | 10                            | 20                   | 30                            | kΩ   |

| AIN pin input voltage range                     | V <sub>AIN</sub>   | <u> </u>                                                                               | _                             |                      | SPV <sub>DD</sub> ×2/3        | Vp-p |

| Line amplifier output resistance1 <sup>*1</sup> | R <sub>LA1</sub>   | $SPV_{DD} = 3.3 \text{ to } 5.5V$<br>When $1/2SPV_{DD} \pm 1 \text{ mA is}$<br>applied | _                             | _                    | 100                           | Ω    |

| Line amplifier output resistance2 <sup>*1</sup> | R <sub>LA2</sub>   | $SPV_{DD} = 2.7 \text{ to } 3.6V$<br>When $1/2SPV_{DD} \pm 1 \text{ mA is}$<br>applied | _                             | 1                    | 300                           | Ω    |

| Line amplifier output-load-resistance *1        | R <sub>LA</sub>    | For SPGND                                                                              | 10                            |                      | _                             | kΩ   |

| Line amplifier Out put Voltage<br>Range *1      | $V_{AO}$           | No output load                                                                         | SPV <sub>DD</sub> /6          |                      | SPV <sub>DD</sub> ×5/6        | V    |

| SG pin output voltage                           | $V_{SG}$           | ı                                                                                      | 0.95x<br>SPV <sub>DD</sub> /2 | SPV <sub>DD</sub> /2 | 1.05x<br>SPV <sub>DD</sub> /2 | V    |

| SG pin output resistance                        | Rsg                |                                                                                        | 57                            | 96                   | 135                           | kΩ   |

| SPP/SPM pins Output-Load Resistance             | R <sub>LSP1</sub>  | ı                                                                                      | 6                             | 8                    | _                             | Ω    |

| To the SPP and SPM pins                         | R <sub>OCDAB</sub> | Class AB speaker amplifier<br>4.5V≤SP <sub>VDD</sub> ≤5.5V                             | 0.1                           | _                    | 6                             | Ω    |

| Short circuit detection                         | R <sub>OCDD</sub>  | Class D speaker amplifier<br>4.5V≤SP <sub>VDD</sub> ≤5.5V                              | 0.1                           | _                    | 3                             | Ω    |

| Speaker amplifier output power 1                | P <sub>SPO1</sub>  | SPV <sub>DD</sub> =5.0V,<br>f=1kHz R <sub>SPO</sub> =8 $\Omega$ ,<br>THD=10%           | 0.8                           | 1                    | _                             | W    |

| Speaker amplifier output power 2                | P <sub>SPO2</sub>  | $SPV_{DD}$ =3.0V,<br>f=1kHz R <sub>SPO</sub> =8 $\Omega$ ,<br>THD=10%                  | 0.1                           | 0.3                  | _                             | W    |

| During no-signal SPM-SPP Output offset voltage  | V <sub>OF</sub>    | AVOL=0dB<br>8 Ω load                                                                   | -50                           | _                    | 50                            | mV   |

<sup>\*1</sup> Applies to the SPP when outputting LINE.

ML22Q62X

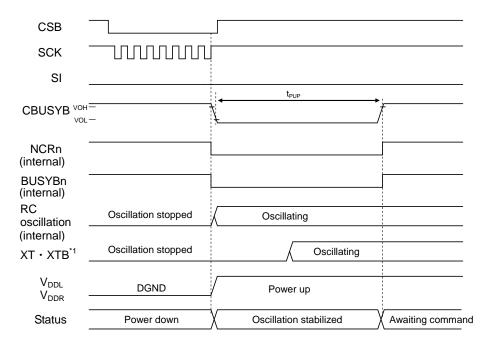

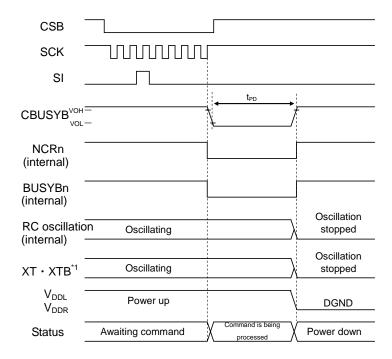

#### • AC characteristic

$SPV_{DD} \ge DV_{DD} = IOV_{DD} = 2.7$  to 5.5V, DGND=SPGND=0V, Ta=-40 to +70°C, Load capacitance of output pin =15pF(max.)

| Parameter                                           | Symbol             | 2.7 to 5.5v, DGND=SPGND=0v, Ta=-40 to +7                                                 | Min.   | Тур.   | Max.      | Unit     |

|-----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------|--------|--------|-----------|----------|

| Master clock duty cycle                             | f <sub>duty</sub>  | _                                                                                        | 40     | 50     | 60        | %        |

| RESETB input pulse width                            | t <sub>RST</sub>   | _                                                                                        | 10     | _      | _         | μs       |

| Reset noise rejection pulse width                   | t <sub>NRST</sub>  | RESETB pin                                                                               | _      | _      | 0.1       | μs       |

| Command input interval time                         | t <sub>INTC</sub>  | fosc = 4.096MHz After input the first command at two-times command input mode            | 0      | _      | _         | μs       |

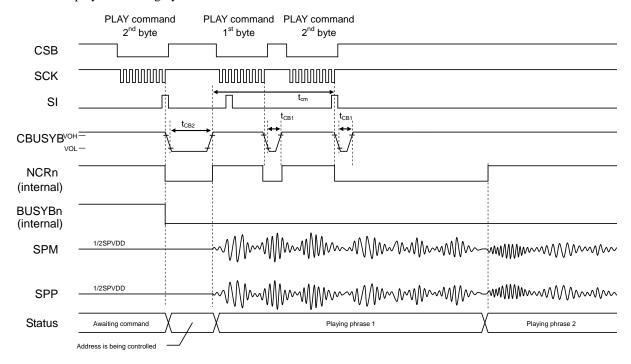

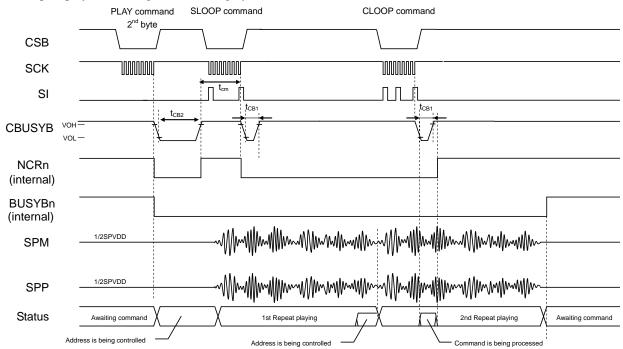

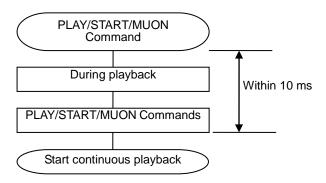

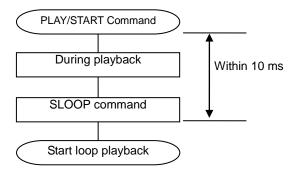

| Command input enable time                           | t <sub>cm</sub>    | f <sub>OSC</sub> = 4.096MHz<br>During continuous playback<br>at SLOOP input              | _      | _      | 10        | ms       |

| At PUP command input CBUSYB "L" level output time   | t <sub>PUP</sub>   | 4.096MHz external clock input                                                            | _      | _      | 8         | ms       |

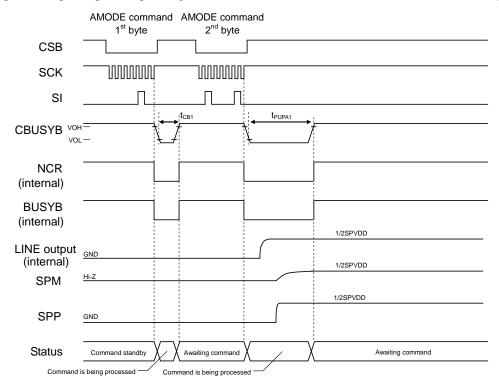

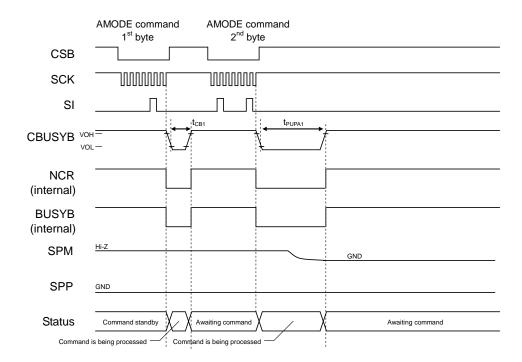

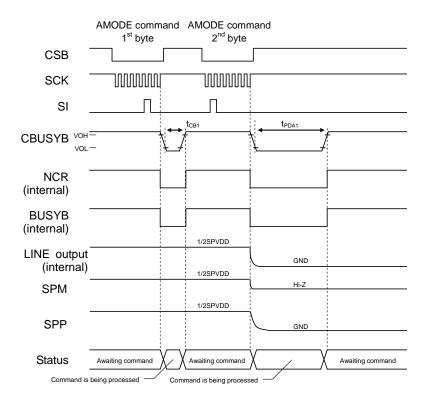

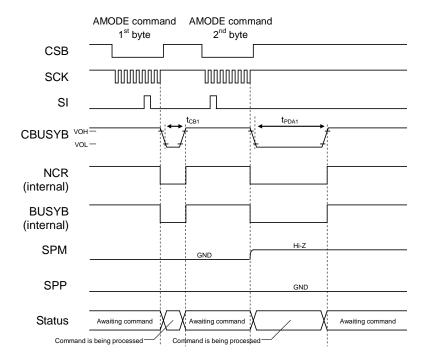

| At AMODE command input CBUSYB "L" level output time | t <sub>PUPA1</sub> | 4.096MHz external clock input POP="L"  AEN0="L"→"H"  AEN1 = "L"  AVOL = -4dB is selected | 35     | 37     | 39        | ms       |

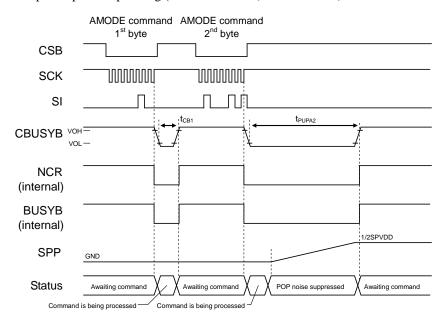

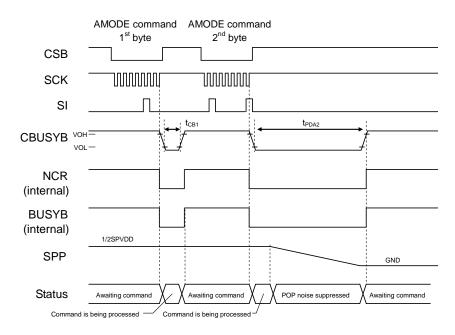

| At AMODE command input CBUSYB "L" level output time | t <sub>PUPA2</sub> | 4.096MHz external clock input<br>DAMP="L",POP="H"<br>AEN1="L"→"H"                        | 72     | 74     | 76        | ms       |

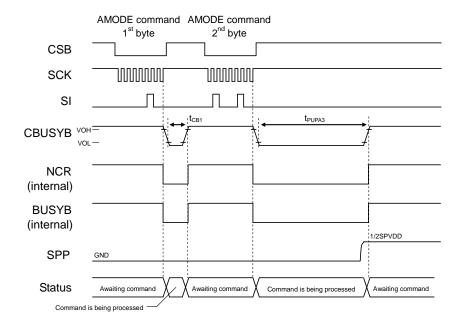

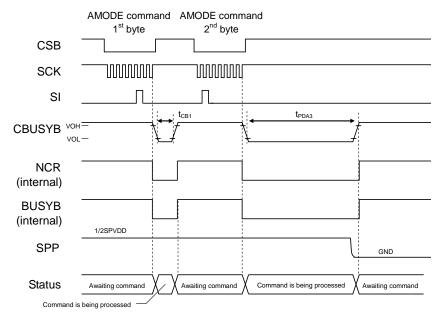

| At AMODE command input CBUSYB "L" level output time | t <sub>PUPA3</sub> | 4.096MHz external clock input<br>DAMP="L",POP="L"<br>AEN1="L"→"H"                        | 32     | 34     | 36        | ms       |

| At PDWN command input CBUSYB "L" level output time  | t <sub>PD</sub>    | f <sub>OSC</sub> = 4.096MHz                                                              | _      | _      | 10        | μs       |

| At AMODE command input CBUSYB "L" level output time | t <sub>PDA1</sub>  | 4.096MHz external clock input<br>POP="L"<br>AEN1="L",AEN0="H"→"L"                        | 106    | 108    | 110       | ms       |

| At AMODE command input CBUSYB "L" level output time | t <sub>PDA2</sub>  | 4.096MHz external clock input<br>DAMP="L",POP="H"<br>AEN1="H"→"L"                        | 143    | 145    | 147       | ms       |

| At AMODE command input CBUSYB "L" level output time | t <sub>PDA3</sub>  | 4.096MHz external clock input<br>DAMP="L",POP= "L"<br>AEN1="H"→"L"                       | 103    | 105    | 107       | ms       |

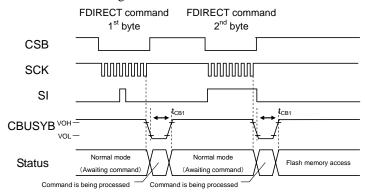

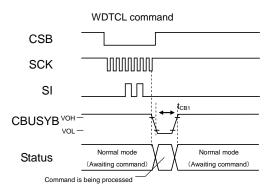

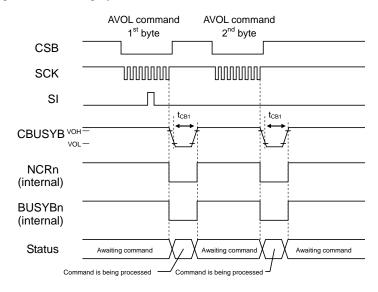

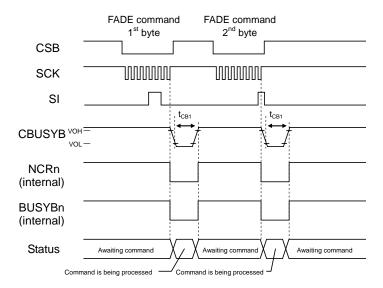

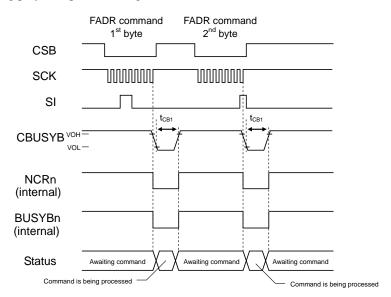

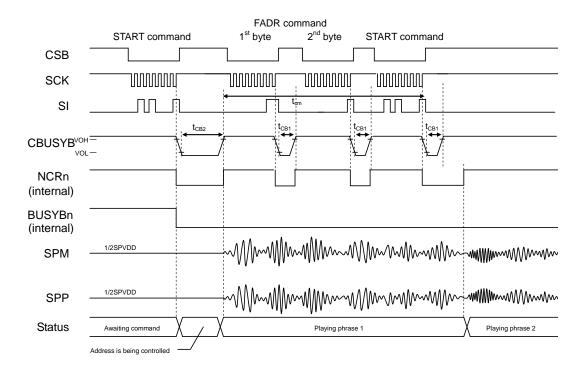

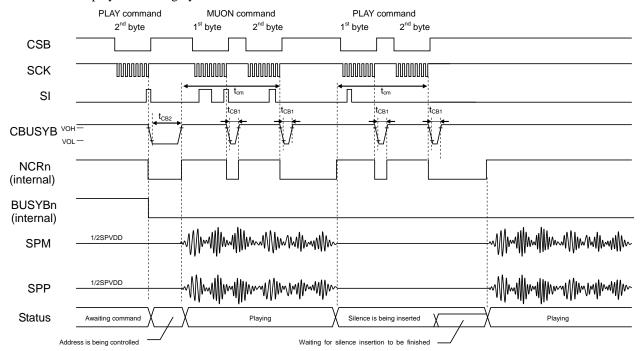

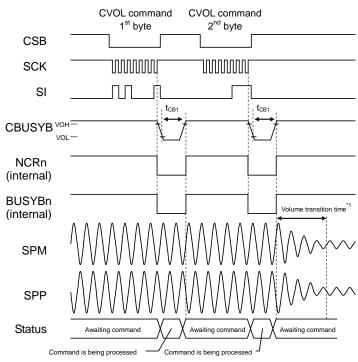

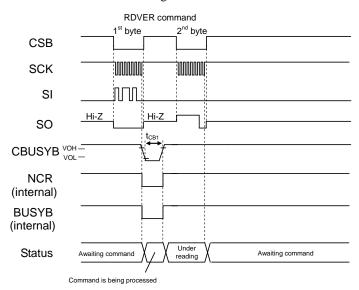

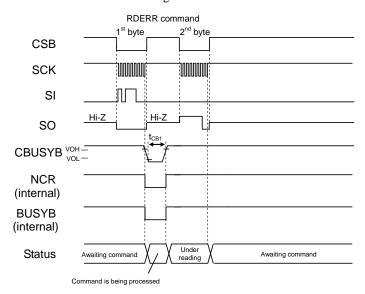

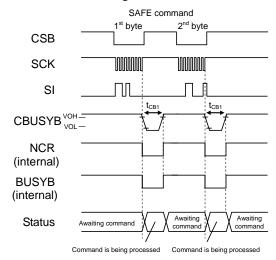

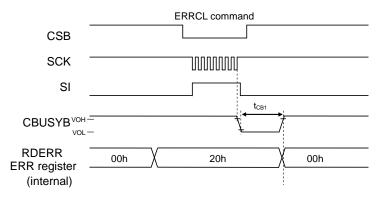

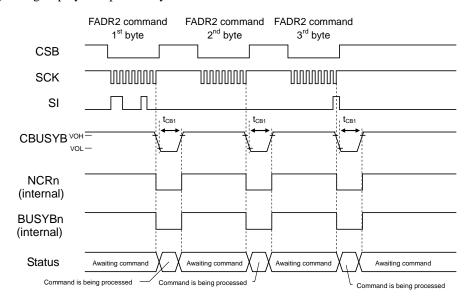

| CBUSYB "L" level output time 1*1                    | t <sub>CB1</sub>   | f <sub>OSC</sub> = 4.096MHz                                                              | _      | _      | 10        | μs       |

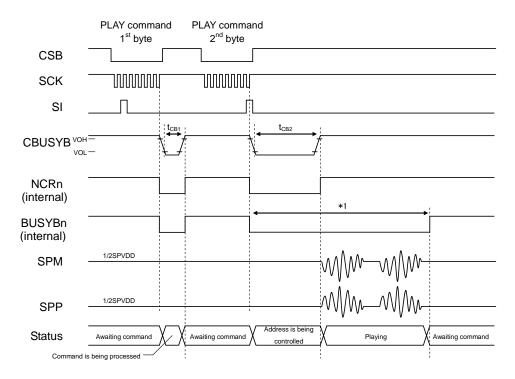

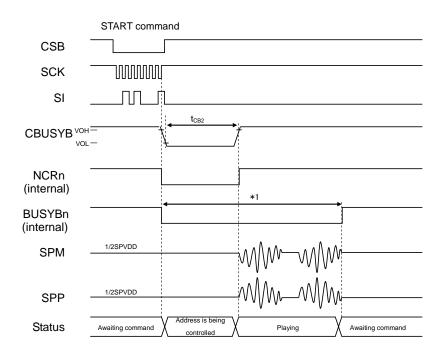

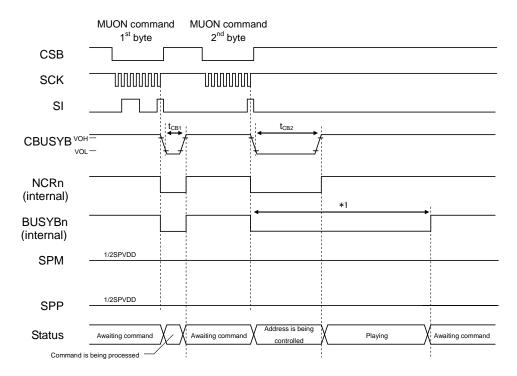

| CBUSYB "L" level output time 2*2                    | t <sub>CB2</sub>   | f <sub>OSC</sub> = 4.096MHz                                                              |        | _      | 3         | ms       |

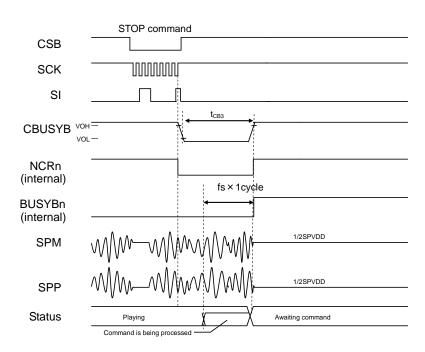

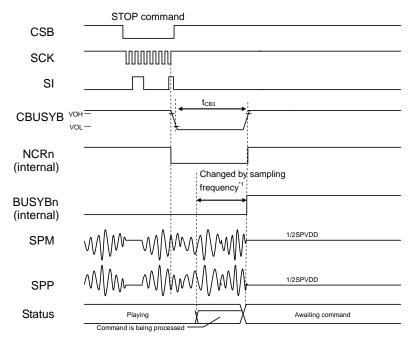

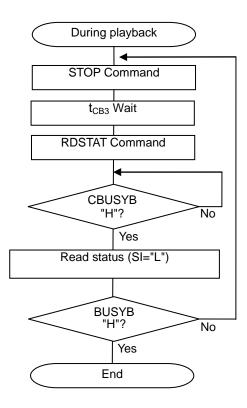

| CBUSYB "L" level output time 3*3                    | t <sub>CB3</sub>   | FAD="L" at $f_{OSC} = 4.096MHz$<br>FAD="H" at $f_{OSC} = 4.096MHz$                       | _<br>_ | _<br>_ | 200<br>10 | μs<br>ms |

<sup>\*1</sup> Applies when inputting commands except the timings after PUP, PDWN, PLAY, or START command is input.

<sup>\*2</sup> Applies when inputting PLAY, START, or MUON command.

<sup>\*3</sup> Applies when inputting STOP command.

ML22Q62X

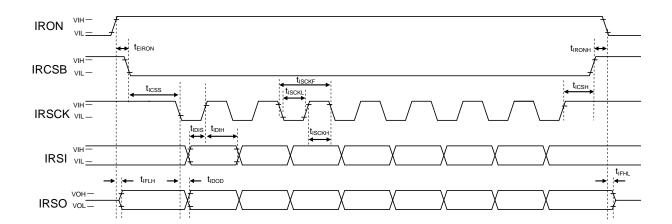

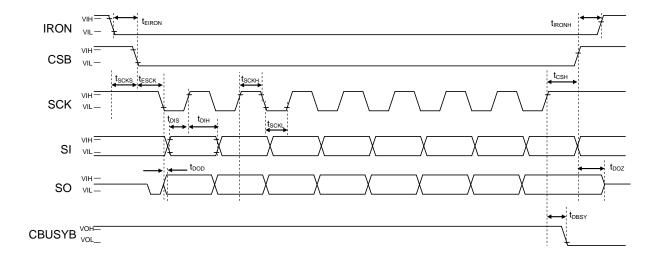

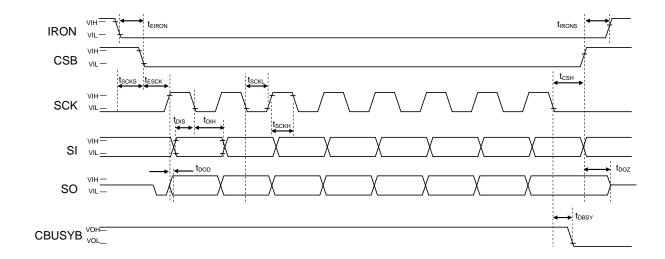

#### • AC Characteristics (Clock Synchronous Serial Interface)

$SPV_{DD} \ge DV_{DD} = IOV_{DD} = 2.7$  to 5.5V, DGND=SPGND=0V, Ta=-40 to +70°C, Load capacitance of output pin =15pF(max.)

| Parameter                                    | Symbol             | Condition | Min. | Тур. | Max. | Unit |

|----------------------------------------------|--------------------|-----------|------|------|------|------|

| CSB input enable time from IRON falling edge | t <sub>EIRON</sub> | _         | 1000 | _    | 1    | ns   |

| CSB hold time from IRON rising edge          | t <sub>IRONH</sub> | _         | 1000 | _    |      | ns   |

| SCK setup time from CSB falling edge         | t <sub>SCKS</sub>  | _         | 100  | _    | 1    | ns   |

| SCK input enable time from CSB falling edge  | tesck              | _         | 100  | _    |      | ns   |

| SCK hold time from CSB rising edge           | t <sub>CSH</sub>   | _         | 100  | _    | 1    | ns   |

| Data floating time from CSB rising edge      | t <sub>DOZ</sub>   | RL=3KΩ    |      | _    | 100  | ns   |

| Data setup time from SCK                     | t <sub>DIS</sub>   | _         | 50   | _    |      | ns   |

| Data hold time from SCK                      | t <sub>DIH</sub>   | _         | 50   | _    | 1    | ns   |

| Data output delay time from SCK              | t <sub>DOD</sub>   | _         |      | _    | 90   | ns   |

| SCK "H" level pulse width                    | tsckh              | _         | 100  | _    |      | ns   |

| SCK "L" level pulse width                    | t <sub>SCKL</sub>  | _         | 100  | _    |      | ns   |

| CBUSYB output delay time from SCK            | t <sub>DBSY</sub>  | _         | _    | _    | 90   | ns   |

<sup>&</sup>lt;When rewriting the flash memory using the clock synchronous serial interface>

$SPV_{DD} \ge DV_{DD} = IOV_{DD} = 2.7$  to 5.5V, DGND=SPGND=0V, Ta=-0 to +70°C, Load capacitance of output pin =15pF(max.)

| Parameter                                    | Symbol             | Condition | Min. | Тур. | Max. | Unit |

|----------------------------------------------|--------------------|-----------|------|------|------|------|

| CSB input enable time from IRON falling edge | t <sub>EIRON</sub> |           | 1000 | _    | _    | ns   |

| CSB hold time from IRON rising edge          | t <sub>IRONH</sub> | _         | 1000 | _    | _    | ns   |

| SCK setup time from CSB falling edge         | t <sub>SCKS</sub>  | _         | 125  | _    | _    | ns   |

| SCK input enable time from CSB falling edge  | tesck              |           | 125  | _    | _    | ns   |

| SCK hold time from CSB rising edge           | t <sub>CSH</sub>   | _         | 125  | _    | _    | ns   |

| Data floating time from CSB rising edge      | t <sub>DOZ</sub>   | RL=3KΩ    | _    | _    | 125  | ns   |

| Data setup time from SCK                     | t <sub>DIS</sub>   | _         | 50   | _    | _    | ns   |

| Data hold time from SCK                      | t <sub>DIH</sub>   | _         | 50   | _    | _    | ns   |

| Data output delay time from SCK              | t <sub>DOD</sub>   | _         | _    | _    | 110  | ns   |

| SCK "H" level pulse width                    | tsckh              | _         | 125  | _    | _    | ns   |

| SCK "L" level pulse width                    | tecki              | _         | 125  | _    | _    | ns   |

ML22Q62X

### • AC Characteristics (Flash Memory Interface)

$SPV_{DD} \ge DV_{DD} = IOV_{DD} = 2.7$  to 5.5V, DGND=SPGND=0V, Ta=-40 to +70°C, Load capacitance of output pin =15pF(max.)

| 0. IDD=2 IDD 10 IDD =11 to 0.01,          | 20.12 0. 0.12      | 01, 14 1010 | 0,0  | apacitaile of | output p | Op. (a) |

|-------------------------------------------|--------------------|-------------|------|---------------|----------|---------|

| Parameter                                 | Symbol             | Condition   | Min. | Тур.          | Max.     | Unit    |

| IRCSB enable time from IRON falling edge  | t <sub>EIRON</sub> | _           | 1000 | _             | _        | ns      |

| IRCSB hold time from IRON rising edge     | t <sub>IRONH</sub> | _           | 1000 | _             | _        | ns      |

| IRSCK enable time from IRCSB falling edge | t <sub>ICSS</sub>  | _           | 100  | _             | _        | ns      |

| IRSCK hold time from IRCSB rising edge    | t <sub>ICSH</sub>  | _           | 100  | _             | _        | ns      |

| Data setup time from IRSCK rising edge    | t <sub>IDIS</sub>  | _           | 50   | _             | _        | ns      |

| Data hold time from IRSCK rising edge     | t <sub>IDIH</sub>  | _           | 50   | _             | _        | ns      |

| Data delay time from IRSCK falling edge   | t <sub>IDOD</sub>  | _           | _    | _             | 80       | ns      |

| IRSCK frequency                           | t <sub>ISCKF</sub> | _           | _    | _             | 5        | MHz     |

| IRSCK "H" level pulse width               | tisckh             | _           | 100  | _             | _        | ns      |

| IRSCK "L" level pulse width               | t <sub>ISCKL</sub> | _           | 100  | _             | _        | ns      |

| IRSO delay time from IRON rising edge     | t <sub>IFLH</sub>  | _           | _    | _             | 1        | ms      |

| IRSO delay time from IRON falling edge    | t <sub>IFHL</sub>  | _           | _    | _             | 1        | ms      |

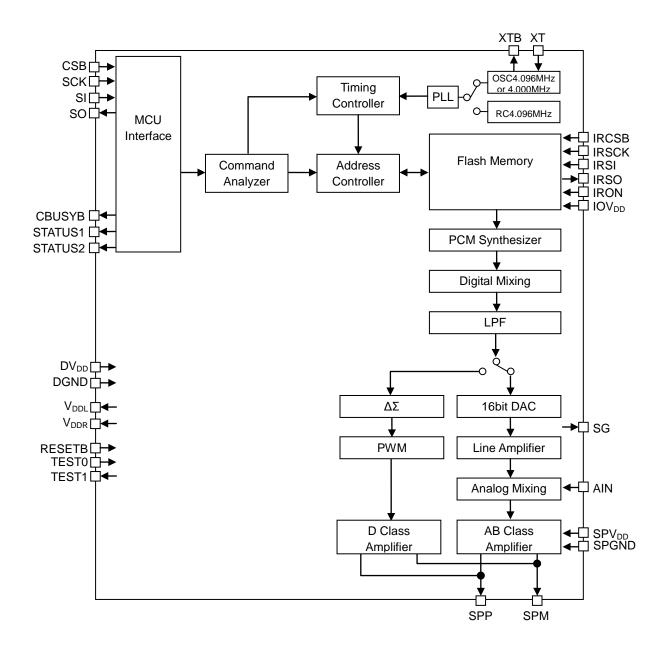

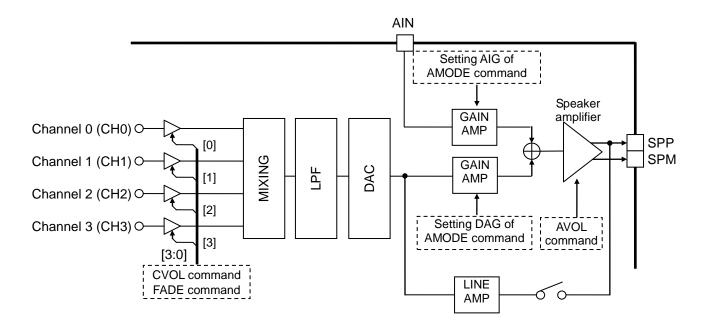

## ■ Block diagram

The block diagram is shown below.

### ■ Function description

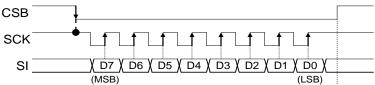

#### Clock Synchronous Serial Interface

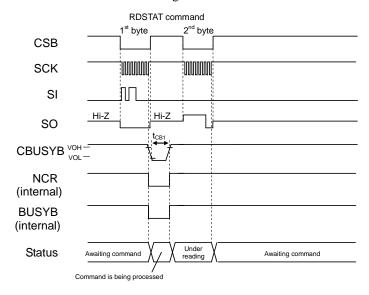

The CSB, SCK, SI, and SO pins are used to input various command data and to read the status.

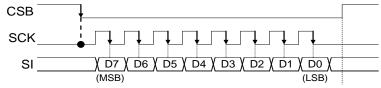

For command and data inputting, after "L" level is input to the CSB pin, data is input to the SI pin in MSB first in synchronization with the input clock signal of the SCK pin. The SI pin data is loaded into the LSI in synchronization with the SCK pin clock, and the command data is determined by the SCK pin clock of the eighth pulse.

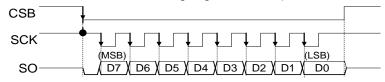

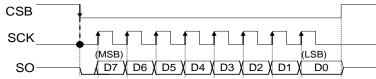

When reading, after "L" level is input to the CSB pin, it is output from the SO pin in synchronization with the input clock signal of the SCK pin.

The selection of the rising or falling edge of the SCK pin clock depends on the state of the SCK pin at the falling edge of the CSB pin.

When the SCK pin is "H" at the falling edge of the CSB pin, the SI pin data is loaded into the LSI on the rising edge of the SCK pin clock, and the status signal is output from the SO pin on the falling edge of the SCK pin clock.

When the SCK pin is "L" at the falling edge of the CSB pin, the SI pin data is loaded into the LSI on the falling edge of the SCK pin clock, and the status signal is output from the SO pin on the rising edge of the SCK pin clock.

When the CSB pin is fixed to "L" level, the SI pin data is loaded into the LSI on the rising edge of the SCK pin clock, and the status signal is output from the SO pin at the falling edge of the SCK pin clock.

However, if unexpected pulses are input to the SCK pin due to noise, etc., the count of the number of SCK pin clocks may be shifted, and normal command input may not be performed.

The serial interface can be returned to the initial state by setting the CSB pin to "H" level.

When the CSB pin is "H" level, the SO pin becomes a high impedance state.

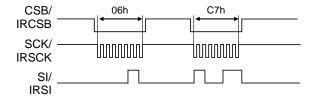

Command data input timing: SCK rising edge operation (When the SCK is "H" at the falling edge of the CSB)

Command data input timing: SCK falling edge operation (When the SCK is "L" at the falling edge of the CSB)

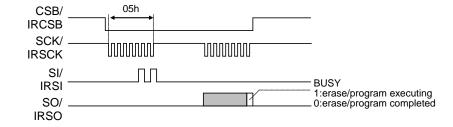

Command data output timing: SCK falling edge operation (When the SCK is "H" at the falling edge of the CSB)

Command data output timing: SCK rising edge operation (When the SCK is "L" at the falling edge of the CSB)

Volume Settings (Differences Between AVOL and CVOL)

The volume can be set with 3 commands CVOL, AVOL and AMODE.

The CVOL can set the volume of each channel, the AVOL can set the volume after channel mixing, and the AMODE can set the input gain to the amplifier. By using the fade function with FADE command, the volume can be adjusted stepwise when the volume is changed with CVOL.

#### • Speech synthesis algorithm

This LSI contains five algorithm types to match the characteristic of playback sound: 4-bit ADPCM2 algorithm, HQ-ADPCM algorithm, 8-bit straight PCM algorithm, and 16-bit straight PCM algorithm. Key feature of each algorithm is described in the table below.

| Speech synthesis algorithm | Compression rate*1 | Feature                                                                                                                                                                                                  |

|----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HQ- ADPCM                  | 1/5                | 4bit ADPCM algorithm is improved. Adopting variable bit length enables high sound quality and high data compression. Suitable for sound effects with sharp changes in waveforms or for pulsed waveforms. |

| 4-bit ADPCM2               | 1/4                | LAPIS original 4bit ADPCM algorithm is improved. Better followability to the waveform improves the sound quality. Suitable for human voices, animal crying, and natural sounds.                          |

| 8-bit non-linear PCM       | 1/2                | This algorithm enables playing back a sound with 10-bit equivalent quality in the center of the waveform. Suitable for low-amplitude sounds that are easily distorted.                                   |

| 8-bit straight PCM         | 1/2                | This algorithm has excellent followability to the waveform in all sound areas. Suitable for sound effects with sharp changes in waveforms or for pulsed waveforms.                                       |

| 16-bit straight PCM        | 1                  | This algorithm has excellent followability to the waveform in all sound areas. Suitable for sound effects with sharp changes in waveforms or for pulsed waveforms.                                       |

<sup>\*1:</sup> When using the same sampling frequency.

Memory Allocation and Creating Sound Data

The flash memory is partitioned into four data areas: sound (i.e., phrase) control area, test area, sound area, and edit ROM area.

The sound control area manages the sound data in the ROM. It contains data for 4,096 phrases.

The sound area contains actual waveform data.

The edit ROM area contains data for effective use of sound data. For the details, refer to the section of "Edit ROM Function".

The edit ROM area is not available if the edit ROM is not used.

The Sound data is created using a dedicated tool (Speech LSI Utility).

#### Configuration of Flash Memory Data (4Mbit)

| 0x00000 |                                                          |

|---------|----------------------------------------------------------|

|         | Test area                                                |

| 0x0007F |                                                          |

| 0x00080 | Sound control area (*) (The number of phrases can be set |

| 0x0207F | with the dedicated tools.)                               |

| 0x02080 |                                                          |

|         |                                                          |

|         | 0                                                        |

|         | Sound area                                               |

|         |                                                          |

|         |                                                          |

|         |                                                          |

|         |                                                          |

|         |                                                          |

|         | Edit ROM area                                            |

|         | Depends on creation of sound                             |

| 0x7FFFF | data                                                     |

<sup>(\*)</sup> When the number of phrases is set to 1024

The number of phrases can be set from 1024 to 4096 in 1024 units using the dedicated tools.

#### Playback time and memory capacity

The playback time depends on the number of phrases, memory capacity, sampling frequency, and playback algorithm. The relationship is shown below. However, this is the playback time when the edit ROM function is not used.

$$Playback \ Time = \frac{-1.024 \times (Memory \ Capacity \ (kbit) - (0.0625 \times Number \ of \ Phrases) - 0.625)}{Sampling \ frequency \ (kHz) \times bit \ length} \qquad (sec)$$

When the number of phrases is 1024, the sampling frequency is 16kHz, and the HQ-ADPCM algorithm is selected, the playback time will be approximately 81 seconds.

ML22Q62X

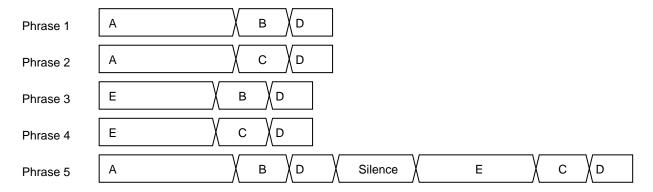

#### • Edit ROM Function

With the edit ROM function, multiple phrases can be played in succession. The following functions can be configured using the edit ROM function:

- Continuous playback: There is no limit to the continuous playback count that can be specified. It depends on the memory capacity only.

- Silence insertion: 20 to 1024 ms

Using the edit ROM function enables an effective use of the flash memory capacity. Below is an example of the ROM configuration in the case of using the edit ROM function.

### Examples of phrases using the edit ROM function

#### Example of sound data where the contents above are stored in ROM

#### Mixing function

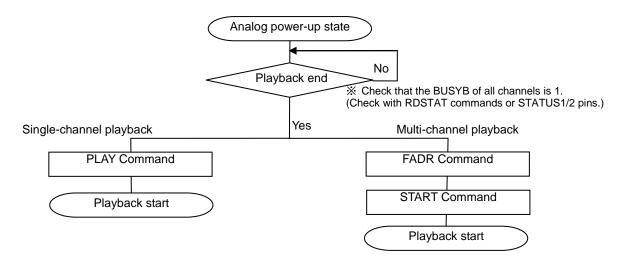

Up to 4 channels mixing playback is possible at the same time. Commands with channel designation can set channels independently.

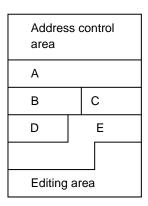

#### Waveform clamp precautions for mixing

When mixing, the clamp may be generated as shown in the figure below due to the calculation of the synthesis. If the clamp is known to be generated in advance, adjust the volume of each channel by CVOL command.

If the result of mixing channels 0 and 1 exceeds from the  $1/6SPV_{DD}$  to 5/6SPVDD level (as indicated by the broken line), the sound quality may be reduced by clamping. Waveforms when AVOL is set to 0.0dB.

#### Class D amplifier precaution on mixing

When mixing with a class d amplifier, use the CVOL command to adjust the volume so that the waveform after mixing does not exceed the full amplitude.

An example of adjusting the volume of the CVOL command during mixing playback is shown below.

#### Example 1)

When performing 2-channels mixing playback of channel 0 and channel 1.

| CVOL command setting value (CV1,CV0,CV6-CV2) |               | Description                                                        |

|----------------------------------------------|---------------|--------------------------------------------------------------------|

| Channel 0                                    | Channel 1     |                                                                    |

| 4Fh(-6.02dB)                                 | 4Fh(-6.02dB)  | Set both channel 0 and channel 1 amplitude to 0.5x.                |

| 67h(-2.50dB)                                 | 37h(-12.04dB) | Set channel 0 amplitude to 0.75x and channel 1 amplitude to 0.25x. |

#### Example2)

When performing 3-channels mixing playback of channel 0, channel 1 and channel 2.

| CVOL command setting value (CV1,CV0,CV6-CV2) |               |               | Description                                                                     |

|----------------------------------------------|---------------|---------------|---------------------------------------------------------------------------------|

| Channel 0                                    | Channel 1     | Channel 2     | _                                                                               |

| 15h(-9.83dB)                                 | 15h(-9.83dB)  | 15h(-9.83dB)  | Set channel 0, channel 1 and channel 2 amplitude to 0.33x.                      |

| 4Fh(-6.02dB)                                 | 37h(-12.04dB) | 37h(-12.04dB) | Set channel 0 amplitude to 0.5x and channel 1 and channel 2 amplitude to 0.25x. |

#### Example3)

When performing all channels mixing playback.

|                                         |               | nd setting value<br>(CV6-CV2) | Description   |                                      |

|-----------------------------------------|---------------|-------------------------------|---------------|--------------------------------------|

| Channel 0 Channel 1 Channel 2 Channel 3 |               | Channel 3                     |               |                                      |

| 37h(-12.04dB)                           | 37h(-12.04dB) | 37h(-12.04dB)                 | 37h(-12.04dB) | Set all channels amplitude to 0.25x. |

Short detection of SPP pin and SPM pin always operates while using the class D amplifier. If the volume of CVOL command is adjusted incorrectly and it it is played back in the clamped state, the short detection circuit is determaine that a short has occurred.

When using class D amplifier, enable short detection of SPP pin and SPM pin by SAFE command and check the short detection error (SPDERR). Refer to SAFE command for setting.

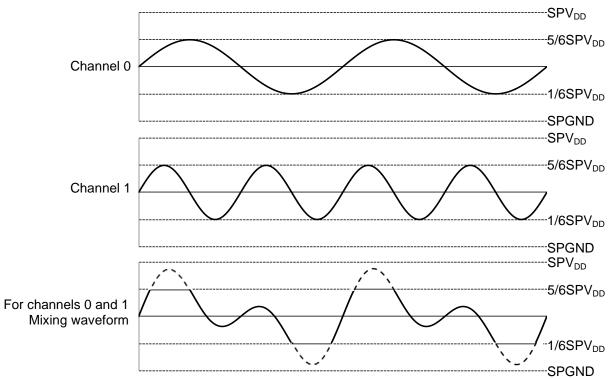

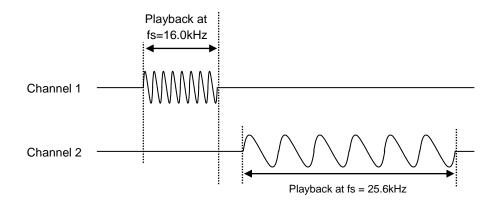

#### Different sampling frequency mixing algorithm

It is not possible to perform channel mixing by a different sampling frequency group.

Note that when channel synthesis is performed on a sampling frequency group other than the selected sampling frequency group, playback will be faster or slower.

The following table lists the frequency group that can be used when mixing different sampling frequency groups.

```

6.4kHz, 12.8kHz, 25.6kHz ... (Group 1)

8.0kHz, 16.0kHz, 32.0kHz ... (Group 2)

11.025kHz, 22.05kHz, 44.1kHz ... (Group 3)

12.0kHz, 24.0kHz, 48.0kHz ... (Group 4)

10.7kHz, 21.3kHz ... (Group 5)

```

The figure below shows the operation image when a sampling frequency group with different sampling frequency group is played back.

Figure 1) Case where a phrase is played at a sampling frequency belonging to a different sampling frequency group during playback on channels 1 and 2

Figure 2) Case where a phrase is played at a sampling frequency belonging to a different sampling frequency group after playback is finished at the other channel

ML22Q62X

• Misoperation detection and failure detection functions

Misoperation detection and failure detection functions can be set with SAFE command. The error detection status can be read by the RDERR command, and the error bit indicating the error detection status can be cleared by the ERRCL command. In addition, OUTSTAT command can be used to send whether an error is detected or not to the STATUS1 pin or STATUS2 pin. For SAFE, RDERR, ERRCL and OUTSTAT commands, refer to the "Command" section. Misoperation detection and failure detection are shown below.

- Command error detection

- Speaker disconnection detection

- LSI temperature error detection

- SPP pin and SPM pin short detection

- Flash memory error detection

- Watchdog timer overflow detection

- RST counter overflow detection

- Detects the stop of clock input from a crystal resonator or ceramic resonator.

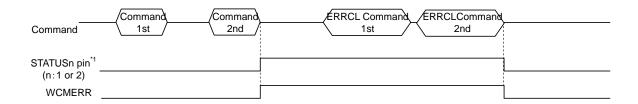

#### ◆ Command error detection

This LSI detects two command errors: phrase number error and command error. Use the WCMEN bit of the SAFE command to set command error detection.

#### ① Phrase number error.

Set the number of phrases (1024, 2048, 3072 or 4096) to use when creating sound data in the Speech LSI Utility. If you specify a phrase that exceeds the number of phrases specified by the Speech LSI Utility with the PLAY2 or FADR2 command, an error in the command is detected and the error bit (WCMERR) is set to "1".

#### ② Command error.

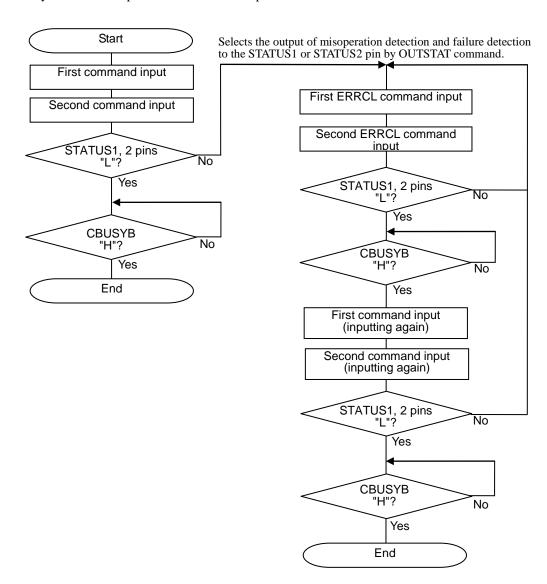

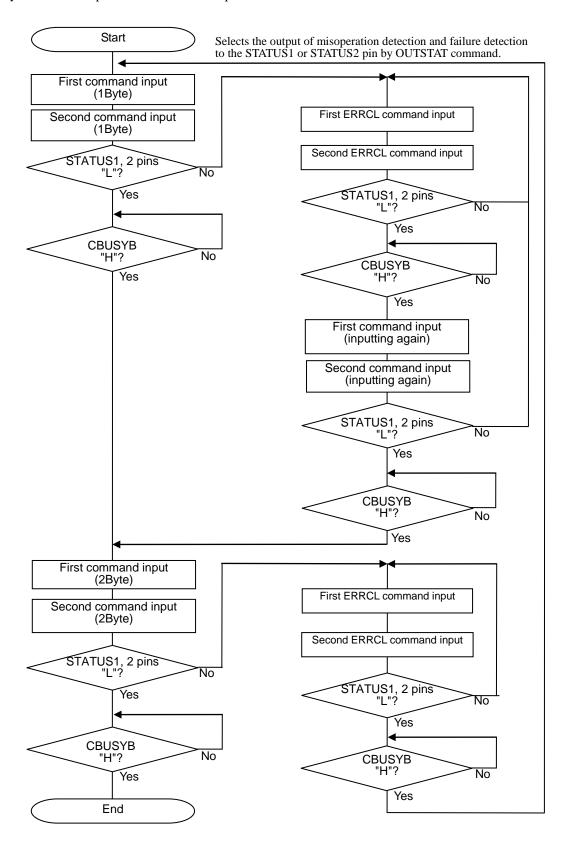

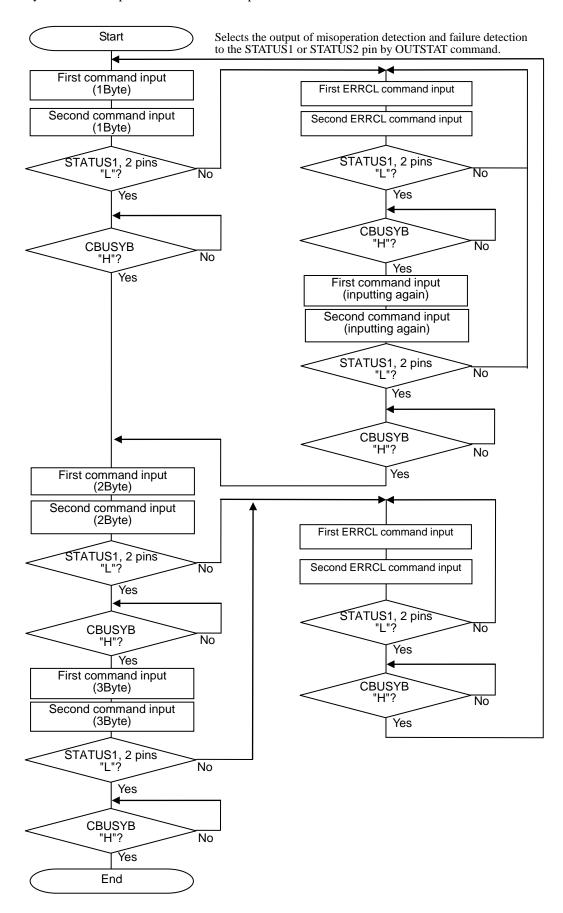

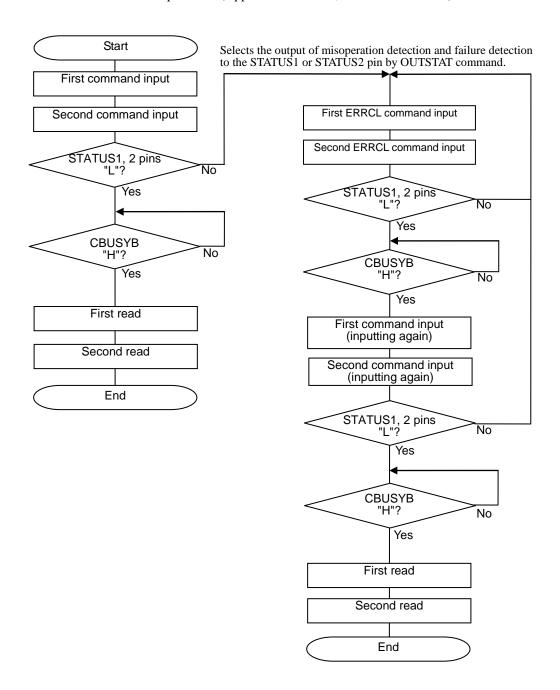

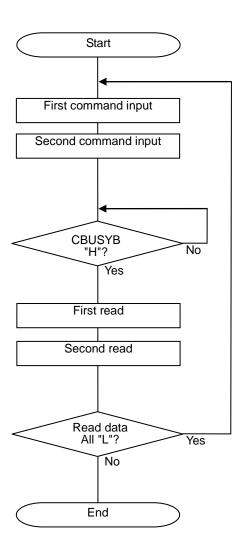

This LSI has a function to input various commands and data two-times to prevent malfunction due to noise at the serial interface pin. The setting of the two-times input mode is made at power-up. Refer to the "PUP command" for the setting method

In the two-times input mode, the command data is input two-times in succession, and it is valid only when the input data matches. If a mismatch occurs during the second data input after the first data input, an error in the command is detected and the error bit (WCMERR) is set to "1", and the command entered is ignored.

Error bit (WCMERR) can be read with RDERR command. Also, error bit (WCMERR) can be cleared by ERRCL command.

<sup>\*1</sup> Misoperation detection and failure detection outputs are selected by OUTSTAT command.

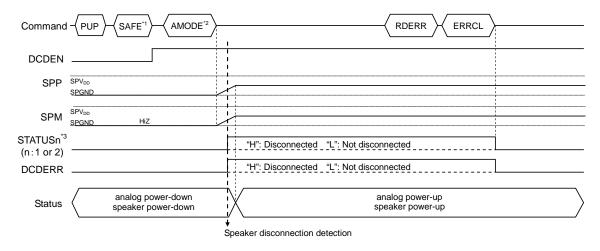

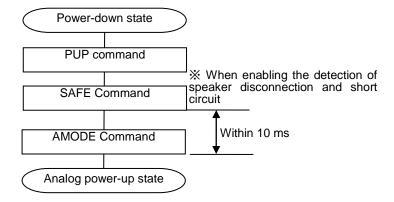

#### Speaker disconnection detection

Set the speaker disconnection detection with the DCDEN bit of the SAFE command.

The speaker connection status of the SPP and SPM pins is checked when the analog power-up is activated in speaker amplifier output mode by AMODE command. When the disconnection of the speaker is detected, the error bit (DCDERR) is set to "1".

Error bit (DCDERR) can be read with RDERR command. Also, error bit (DCDERR) can be cleared by ERRCL command.

- \*1 Set DCDEN = "1"

- \*2 Analog power-up in speaker amplifier output mode

- \*3 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

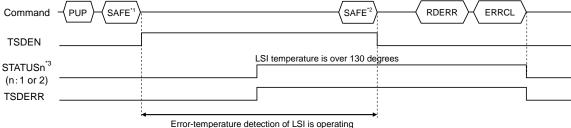

#### ◆ LSI temperature error detection

Set the LSI temperature error detection with the TSDEN bit of the SAFE command.

When the TSDEN bit is set to "1" by the SAFE command, LSI temperature error detection starts. When the TSDEN bit is set to "0", LSI temperature error detection ends.

When the LSI becomes 130°C or more, the error bit (TSDERR) becomes "1".

Error bit (TSDERR) can be read with RDERR command. Also, error bit (TSDERR) can be cleared by ERRCL command.

- \*1 Set TSDEN = "1"

- \*2 Set TSDEN = "0"

- \*3 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

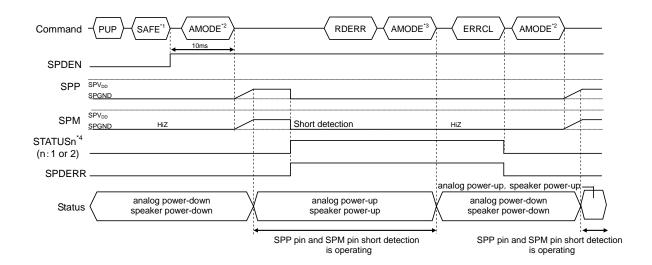

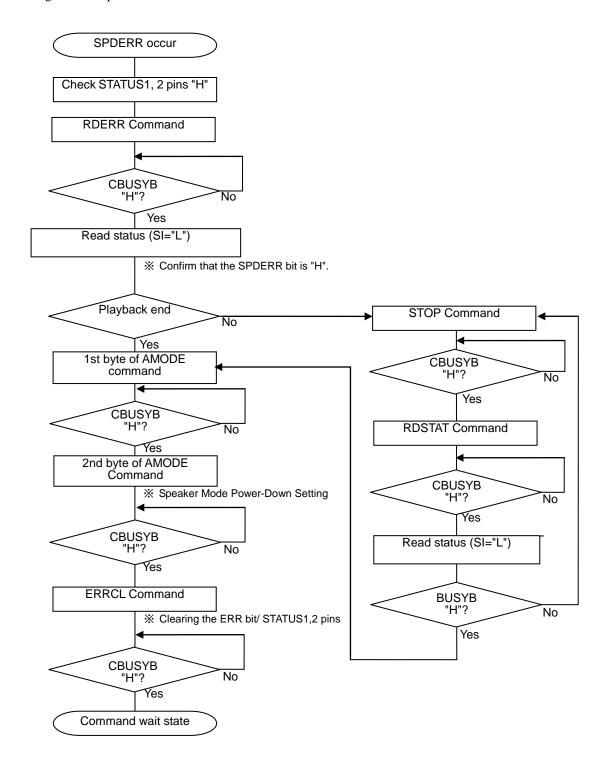

#### ◆ SPP pin and SPM pin short detection

Set the SPP pin and SPM pin short detection with the SPDEN bit of the SAFE command.

Detects short circuit between SPP pin and SPM pin, or SPP pin and GND (ground fault), or SPM pin and GND (ground fault). Can be used when  $SPV_{DD} \ge 4.5V$ . Operation is started by analog power-up in the speaker amplifier output mode by the AMODE command, and operation is terminated by power-down in the speaker amplifier output mode by the AMODE command.

After inputting SAFE command, start the analog power-up operation by AMODE command within 10ms.

When a short-circuit is detected, the error bit (SPDERR) is set to "1". When using a class D amplifier with the DAMP bit of AMODE command set to "1", if the PWM output is fixed to "H" level for 62.5µs or longer, the error bit (SPDERR) is set to "1". At the same time, the speaker amplifier output pin (SPP/SPM) is forcibly turned off. Read the error bit (SPDERR) with the RDERR command, end playback, and perform analog power-down with the AMODE command. Then, use ERRCL command to clear the error bit (SPDERR).

To restart playback, use the AMODE command to analog power-up the speaker amplifier output mode and enter the PLAY command. However, if shorting to ground continues, the error bit (SPDERR) is set to "1" and the speaker amplifier output pin (SPP/SPM) is forcibly turned off simultaneously.

Short detection prevents damage to LSI. However, the detection circuit is effective in preventing damage due to unexpected accidents. It does not support continuous short operation or transient use.

- \*1 Set 1 SPDEN = "1"

- \*2 Analog power-up in speaker amplifier output mode

- \*3 Analog power-down in speaker amplifier output mode

- \*4 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

#### ◆ Flash memory error detection

Set the Flash memory error detection with the ROMEN bit of the SAFE command. It is possible to detect two kinds of errors.

#### ① Flash memory read data error

When an error is detected in the read data from the flash memory, the error bit (ROMERR) is set to "1". At the same time, playback of the corresponding channel is stopped.

If the error bit (ROMERR) is set to "1" after the PUP command and before the PLAY command or START command starts playback, this LSI may have error at the time of start. In such cases, initialize this LSI by moving the LSI to the power-down mode by resetting the LSI by the RESETB pin or by using PDWN command.

#### ② Access outside the flash memory address range

If the flash memory is accessed outside the flash memory address range, an error is detected and the error bit (ROMERR) is set to "1".

At the same time, playback of the corresponding channel is stopped.

Error bit (ROMERR) can be read with RDERR command. Error bit (ROMERR) can be cleared by ERRCL command.

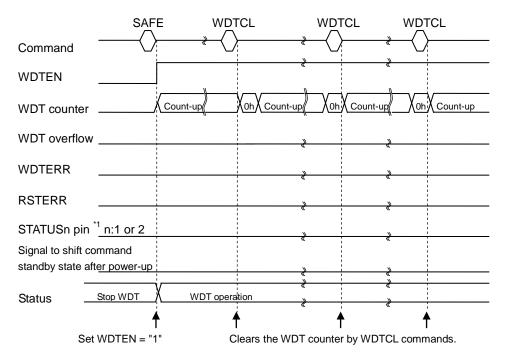

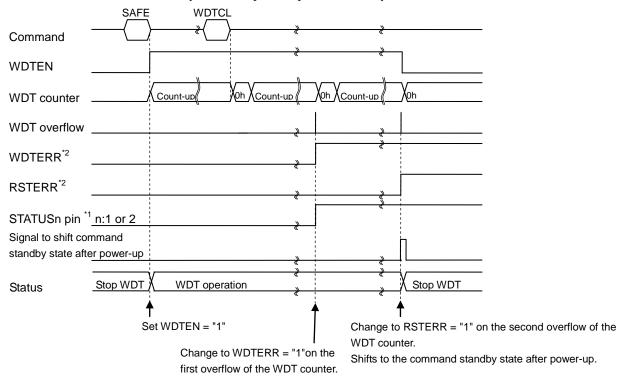

#### Watchdog timer overflow detection

A communication error between the HOST MCU and this LSI (disconnection or short-circuit of the MCU command interface, etc.) can be detected.

Set the watchdog timer overflow detection with WDTEN bit of the SAFE command.

When the detection operation is started, the detection does not stop even if the WDTEN bit is set to "0".

After the detection operation starts, clear the WDT counter with the WDTCL command before the WDT counter overflows.

When the WDT counter overflows (for the first time), the error bit (WDTERR) is set to "1".

Error bit (WDTERR) can be read with RDERR command. In addition, the error bit (WDTERR) can be cleared by the ERRCL command after the WDTCL command.

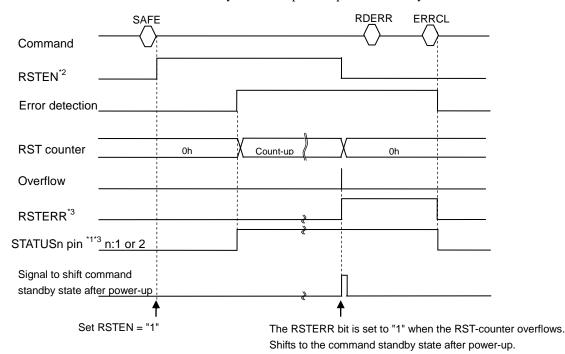

The count time of the WDT counter is 2s the initial value. The counting time can be set to 125ms, 500ms, 2s, 4s. In addition, it is possible to shift to the command wait state after power-up by the second overflow of the WDT counter.

The count time and the second overflow operation can be set with the dedicated tools (Speech LSI Utility).

<sup>\*1</sup> Misoperation detection and failure detection outputs are selected by OUTSTAT command.

Recommended Operation Flow of Watchdog Timer

The operation when no WDTCL command is entered is as follows.

<When "Transition to the command standby state after power-up" is selected by the second overflow of the WDT counter>

- \*1 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

- \*2 Even if transferring to the command standby state after power-up by the second overflow of the the WDT counter, the state of WDTERR bit and RSTERR bit remain. The state configured by OUTSTAT command also remains.

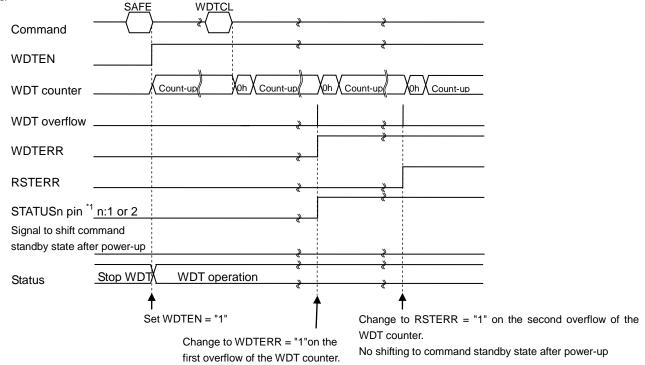

<When "Transition to the command standby state after power-up" is not selected by the second overflow of the WDT counter>

\*1 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

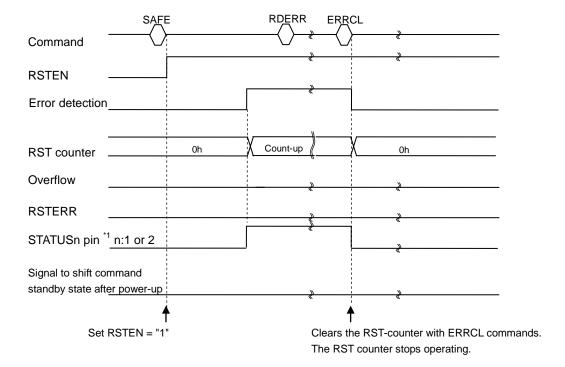

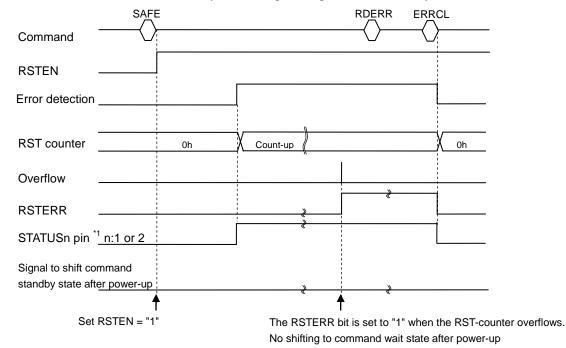

#### ◆ RST counter overflow detection

By using the RST counter overflow detection, it is possible to shift the LSI to the command standby state after power-up after misoperation detection and failure detection occurs.

When the overflow detection of RST counter is set by RSTEN bit of SAFE command, the detection operation will start.

When the detection operation is started, the detection does not stop even if the RSTEN bit is set to "0".

The RST counter starts counting up after misoperation detection and failure detection occurs.

If the RST counter is cleared with the ERRCL command before it overflows, it stops until the next error occurs.

When the RST counter overflows, the error bit (RSTERR) is set to "1".

Error bit (RSTERR) can be read with RDERR command. Also, error bit (RSTERR) can be cleared by ERRCL command.

The count time of the RST-counter is 2s, the initial-value. The counting time can be set to 125ms, 500ms, 2s, or 4s.

Set the counting time and overflow operation (shift to the command standby state after power-up) with the dedicated tools (Speech LSI Utility).

The operation when RSTEN is set to "1" is as follows.

<sup>\*1</sup> Misoperation detection and failure detection outputs are selected by OUTSTAT command.

The operation when no ERRCL command is entered is as follows.

<When "Transition to the command standby state after power-up" is selected by the overflow of the RST counter>

- \*1 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

- \*2 If transferring to the command standby state after power-up is executed by the overflow of the RST counter, each bit of SAFE command is cleared. Also, error bits readable by RDERR command are cleared by ERRCL command.

- \*3 Even if transferring to the command standby state after power-up is executed by the overflow of the RST counter, error bits readable by RDERR command and the state configured by OUTSTAT command remain.

- < When "Transition to command standby state after power-up" is not selected by the overflow of the RST counter >

\*1 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

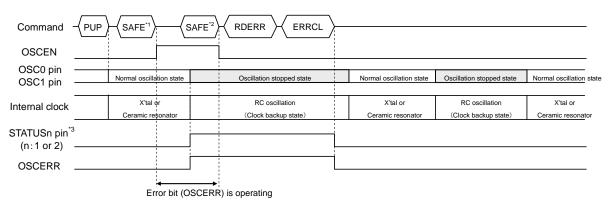

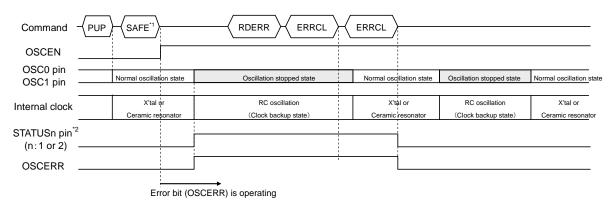

◆ Detects the stop of clock input from a crystal resonator or ceramic resonator

Set the "Detects the stop of clock input from a crystal resonator or ceramic resonator" with the OSCEN bit of the SAFE command.

When the clock input from the crystal resonator or the ceramic resonator is stopped, the error bit (OSCERR) is set to "1". At the same time, the clock backup function is activated and the clock is automatically switched to the RC oscillator circuit (4.096MHz).

Error bit (OSCERR) can be read with RDERR command. However, if the RDERR command (first byte) is inputted before the crystal or ceramic resonator stops and switches to RC oscillation (about 500µs), the CBUSYB pin will remain "L". Therefore, read the command after the CBUSYB pin becomes "H". Also, error bit (OSCERR) can be cleared by ERRCL command. However, if the clock input from the crystal resonator or the ceramic resonator continues to be stopped while the OSCEN bit of the SAFE command is "1", the error bit (OSCERR) is set to "1".

When the crystal resonator or the ceramic resonator stops and switches to RC oscillation, playback may become abnormal. Therefore, after confirming that the error bit (OSCERR) is "1", enter STOP command to stop playback.

If the clock input from the crystal resonator or the ceramic resonator is stopped while the OSCEN bit is "0", the error bit (OSCERR) does not change to "1", but the clock backup function is activated and the clock backup circuit is automatically switched to the RC oscillator circuit (4.096MHz).

- \*1 Set OSCEN = "1"

- \*2 Set OSCEN = "0"

- \*3 Misoperation detection and failure detection outputs are selected by OUTSTAT command.

#### <When the OSCEN bit of SAFE command continue to be "1">

<sup>\*1</sup> Set OSCEN = "1"

<sup>\*2</sup> Misoperation detection and failure detection outputs are selected by OUTSTAT command.

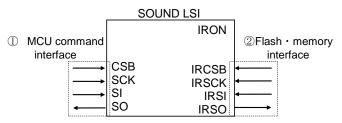

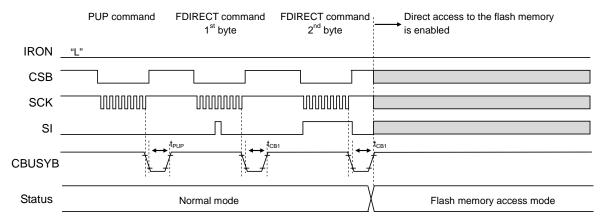

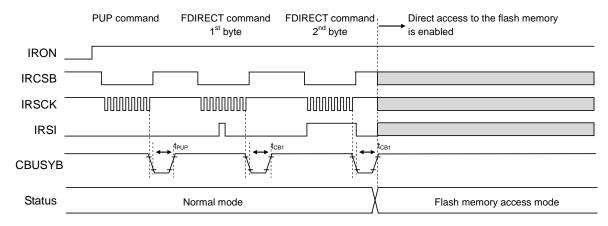

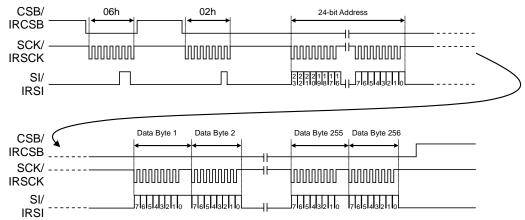

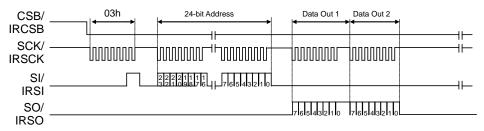

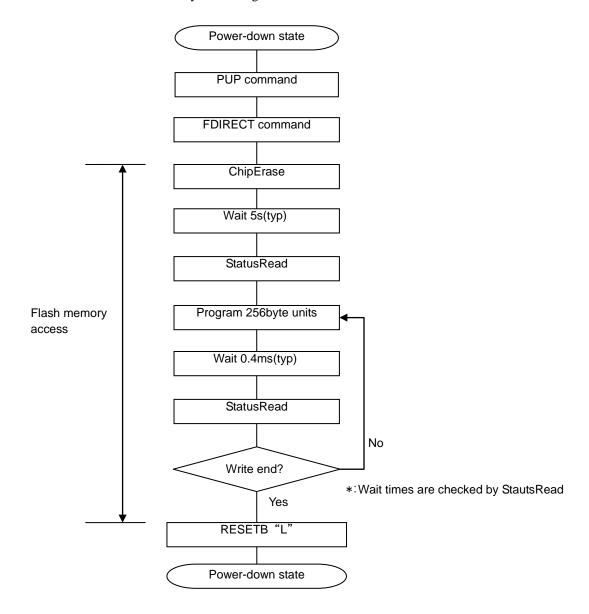

#### • Flash memory rewrite function

The flash memory can be rewritten in the following two ways.

Rewrite using the clock synchronous serial interface of the MCU command interface