PEDL5238-7

LAPIS

ML5238

Issue date: April. 3, 2013

Preliminary Ver.7

16 series Li-ion secondary battery protection, Analog Front End IC

#### ■ GENERAL DESCRIPTION

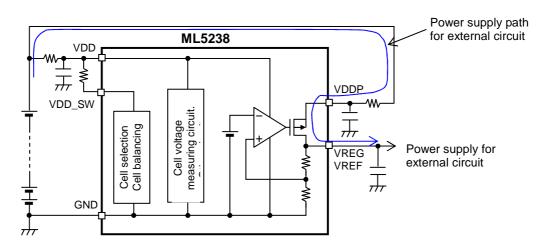

The ML5238 is analog front end IC for 16 series Lithium Ion secondary battery pack protection system. The ML5238 provides the function of cell voltage monitoring, charge/discharge current monitoring function, and it can detect over-charge/over-discharge of each battery cell charge/discharge over-current.

The ML5238 has short current detecting function which can turn off the external charge/discharge MOS-FET without external MCU.

#### ■ FEATURES

- 16 cell highly accurate voltage monitoring function: output cell voltage by half from VMON pin

- built-in cell balancing switches for each cell

- charge/discharge current monitoring function :

Select voltage gain of ISP-ISM and output from IMON pin.

Voltage gain selection: x10 / x50

• short current detecting function: detecting threshold voltage is selectable,

ISP-ISM voltage = 0.1V/0.2V/0.3V/0.4V (typ),

the detecting delay time is set by external capacitor

- external charge/discharge FET control: NMOS-FET driver built-in

- MCU interface: SPI serial interface (mode 0)

- 3.3V regulator for external MCU built-in: output current is 10mA (max)

- Reference voltage regulator for external ADC: 3.3V(typ), 3.28V(min), 3.34V(max) @Ta=-10°C to +60°C

- Small power consumption

| Normal state            | : 50µA (typ), 100µA (max)                  |

|-------------------------|--------------------------------------------|

| Power save state        | : 25µA (typ), 50µA (max)                   |

| Power down state        | : 0.1µA (typ), 1µA (max)                   |

| • power supply voltage  | : +7V to +80V                              |

| • operating temperature | : $-40^{\circ}$ C to $+85^{\circ}$ C       |

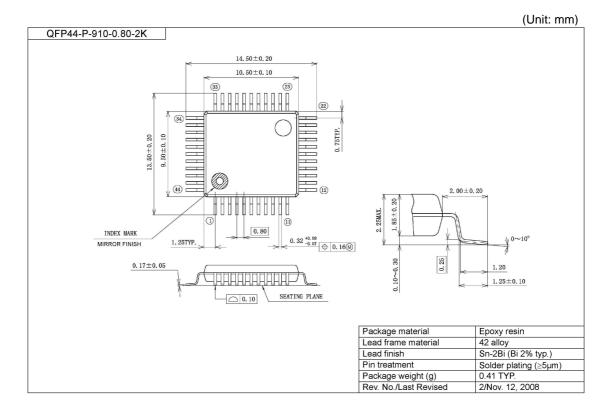

| • package               | : 44 pin plastic QFP (QFP44-P-910-0.80-2K) |

Note: The ML5238 is forbidden to be used for automotive or any equipment, device or system which requires an extremely high level of reliability.

#### **BLOCK DIAGRAM** VDD VDDP VREF VREG VDD\_SW /CS V16 SCK Voltage V15 SDI MCU I/F Regulator V14 SDO Control V13 Cell Selection & Cell Balance Switches /RES Logic V12 /INTO V11 ]/PUPIN V10 TEST V9 Cell Voltage V8 Monitor V7 Charger PSENSE Load V6 **RSENSE** Detector V5 V4 Reference C\_FET V3 Generator FET Driver V2 ]D\_FET V1 V0 Short Current IMON Detector Monitor ŧ GND $\rightarrow$ CDLY VMON ISM ISP

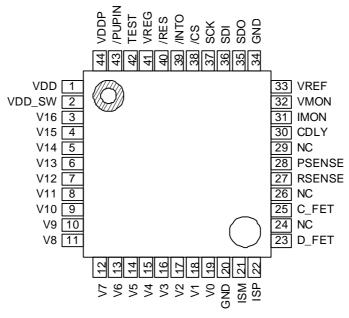

#### ■ PIN CONFIGURATION (TOP VIEW)

|         | Din nome | I/O  | Description                                                                                                                                                                                 |

|---------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin name | 1/0  | Description                                                                                                                                                                                 |

| 1       | VDD      | -    | Power supply input pin.<br>Connect CR filters for noise rejection.                                                                                                                          |

|         |          |      | Power supply input pin for battery selection switches and cell balancing                                                                                                                    |

| 2       | VDD_SW   | -    | switched. Connect this pin to VDD via resistor.                                                                                                                                             |

|         |          |      |                                                                                                                                                                                             |

| 3       | V16      | I    | Battery cell 16 high voltage input pin                                                                                                                                                      |

|         |          |      | If number of connected cell is 5 to 16, connect this pin to VDD_SW pin.                                                                                                                     |

| 4       | V15      | <br> | Battery cell 16 low voltage input and Battery cell 15 high voltage input pin                                                                                                                |

| 5       | V14      |      | Battery cell 15 low voltage input and Battery cell 14 high voltage input pin                                                                                                                |

| 6       | V13      | I    | Battery cell 14 low voltage input and Battery cell 13 high voltage input pin                                                                                                                |

| 7       | V12      | I    | Battery cell 13 low voltage input and Battery cell 12 high voltage input pin                                                                                                                |

| 8       | V11      | I    | Battery cell 12 low voltage input and Battery cell 11 high voltage input pin                                                                                                                |

| 9       | V10      | I    | Battery cell 11 low voltage input and Battery cell 10 high voltage input pin                                                                                                                |

| 10      | V9       | I    | Battery cell 10 low voltage input and Battery cell 9 high voltage input pin<br>For the 5 cell series connected battery pack application, connect this pin to<br>GND                         |

| 11      | V8       | I    | Battery cell 9 low voltage input and Battery cell 8 high voltage input pin<br>For the 5 to 6 cell series connected battery pack application, connect this pin<br>to GND                     |

| 12      | V7       | I    | Battery cell 8 low voltage input and Battery cell 7 high voltage input pin<br>For the 5 to 7 cell series connected battery pack application, connect this pin<br>to GND                     |

| 13      | V6       | I    | Battery cell 7 low voltage input and Battery cell 6 high voltage input pin<br>For the 5 to 8 cell series connected battery pack application, connect this pin<br>to GND                     |

| 14      | V5       | I    | Battery cell 6 low voltage input and Battery cell 5 high voltage input pin<br>For the 5 to 9 cell series connected battery pack application, connect this pin<br>to GND                     |

| 15      | V4       | I    | Battery cell 5 low voltage input and Battery cell 4 high voltage input pin<br>For the 5 to 10 cell series connected battery pack application, connect this<br>pin to GND                    |

| 16      | V3       | I    | Battery cell 4 low voltage input and Battery cell 3 high voltage input pin<br>For the 5 to 11 cell series connected battery pack application, connect this<br>pin to GND                    |

| 17      | V2       | I    | Battery cell 3 low voltage input and Battery cell 2 high voltage input pin<br>For the 5 to 12 cell series connected battery pack application, connect this<br>pin to GND                    |

| 18      | V1       | I    | Battery cell 2 low voltage input and Battery cell 1 high voltage input pin<br>For the 5 to 13 cell series connected battery pack application, connect this<br>pin to GND                    |

| 19      | V0       | I    | Battery cell 1 low voltage input pin<br>For the 5 to 14 cell series connected battery pack application, connect this<br>pin to GND                                                          |

| 20, 34  | GND      | _    | Ground pin.                                                                                                                                                                                 |

| 21      | ISM      | I    | Current sensing resistor connecting pin. Connect this pin to the low voltage terminal of the lowest level battery cell.                                                                     |

| 22      | ISP      | I    | Current sensing resistor connecting pin. The voltage of this pin should be higher than the ISM pin in discharging state.                                                                    |

| 23      | D_FET    | ο    | Discharging NMOS-FET control signal pin. Connect this pin to the gate pin of<br>the external NMOS FET. Output voltage is 14V (typ) for setting ON, output<br>voltage is 0V for setting OFF. |

#### ■ PIN DESCRIPTION

# LAPIS Semiconductor

#### PEDL5238-7 ML5238 (Preliminary Ver.7)

| Pin No.    | Pin name | I/O | Description                                                                                                                                                                                                                                                                                                                     |

|------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25         | C_FET    | ο   | Charging NMOS-FET control signal output pin. Connect this pin to the gate<br>pin of the external NMOS FET. Output voltage is 14V (typ) for setting ON,<br>output is Hi-Z for setting OFF.                                                                                                                                       |

| 27         | RSENSE   | I   | Input pin for detecting the load disconnection. Connect this pin to the negative side of the load.                                                                                                                                                                                                                              |

| 28         | PSENSE   | I   | Input pin for detecting the charger disconnection. Connect this pin to the negative side of the charger. If charger is connected to the same node as the load, connect this pin to the RSENSE pin.                                                                                                                              |

| 30         | CDLY     | Ю   | Short current detection delay time setting pin. Connect a capacitor between GND and this pin.                                                                                                                                                                                                                                   |

| 31         | IMON     | о   | Current monitor output pin. The voltage amplified the voltage between ISP-ISM by 10 or 50 is outputted. When current is not flowing, 1V (typ) is outputted.                                                                                                                                                                     |

| 32         | VMON     | 0   | Cell voltage monitor output pin. The voltage amplified a cell voltage by 0.5 is outputted.                                                                                                                                                                                                                                      |

| 33         | VREF     | О   | Reference voltage output (3.3V) for external ADC. Connect a $4.7\mu$ F capacitor between this pin and the GND pin.                                                                                                                                                                                                              |

| 35         | SDO      | ο   | Serial interface data output pin. If /CS input is "H", output of this pin is Hi-Z state.                                                                                                                                                                                                                                        |

| 36         | SDI      | I   | Serial interface data input pin.                                                                                                                                                                                                                                                                                                |

| 37         | SCK      | I   | Serial interface clock input pin. Capture the SDI input at the rising edge of the SCK clock. Output the data from the SDO pin at the falling edge of the SCK.                                                                                                                                                                   |

| 38         | /CS      | I   | Serial interface chip select pin. The serial interface is active if the input is "L".                                                                                                                                                                                                                                           |

| 39         | /INTO    | 0   | Interrupt signal output to external MCU. This pin is a NMOS open drain output pin and output is "L" level if interrupted.                                                                                                                                                                                                       |

| 40         | /RES     | Ю   | Reset signal input and a reset signal output to external MCU. Since this pin is a NMOS open drain output pin, connect a $0.1\mu$ F capacitor between this pin and GND pin and pull-up resisitor. When recovered power-down state, "L" level reset pulse will be outputted and both ML5238 and external MCU will be initialized. |

| 41         | VREG     | Ю   | Built-in 3.3V regulator output pin. Connect a $4.7\mu$ F capacitor between this pin and GND pin. It can be used as a power supply to the external MCU. And it is also used as a power supply to the MCU interface circuit in this IC.                                                                                           |

| 42         | TEST     | I   | Test input pin. Fix to GND level.                                                                                                                                                                                                                                                                                               |

| 43         | /PUPIN   | Ю   | Power-up trigger input pin. If input is "L" level, the state of the ML5238 changes from power-down state to Initial state. A $100k\Omega$ pull-up resistor is built-in between this pin and the VDD pin.                                                                                                                        |

| 44         | VDDP     | -   | Power supply input pin for internal regulator.<br>Connect CR filters for noise rejection.                                                                                                                                                                                                                                       |

| 24, 26, 29 | NC       | -   | No connection pin. Open this pin.                                                                                                                                                                                                                                                                                               |

#### ■ ABSOLUTE MAXIMUM RATINGS

|                                | T                 | 1                                                     |                                                | ND=0 V, Ta=25℃ |

|--------------------------------|-------------------|-------------------------------------------------------|------------------------------------------------|----------------|

| Parametor                      | Symbol            | Condition                                             | Rating                                         | Unit           |

| Power supply voltage           | V <sub>DD</sub>   | VDD, VDDP , VDD_SW                                    | -0.3 to +86.5                                  | V              |

|                                | V <sub>IN1</sub>  | V16 ~ V0, Voltage difference<br>between Vn+1 – Vn pin | -0.3 to +6.5                                   | V              |

| Input voltage                  | V <sub>IN2</sub>  | RSENSE, PSENSE                                        | V <sub>DD</sub> - 86.5 to V <sub>DD</sub> +0.3 | V              |

|                                | V <sub>IN3</sub>  | /PUPIN                                                | -0.3 to V <sub>DD</sub> + 0.3                  | V              |

| roltage                        | V <sub>IN4</sub>  | /CS, SCK, SDI, ISM, ISP                               | -0.3 to V <sub>REG</sub> + 0.3                 | V              |

|                                | V <sub>OUT1</sub> | D_FET                                                 | -0.3 to V <sub>DD</sub> + 0.3                  | V              |

| Output voltage                 | V <sub>OUT2</sub> | C_FET                                                 | $V_{DD}$ - 86.5 to $V_{DD}$ + 0.3              | V              |

| · · ·                          | V <sub>OUT3</sub> | /RES, /INTO                                           | -0.3 to + 6.5                                  | V              |

| Output short<br>current        | los               | VDD=50V,<br>VREG, SDO, /RES, /INTO,<br>C_FET, D_FET   | 20                                             | mA             |

| Cell balancing<br>curren       | I <sub>CB</sub>   | Per a cell balancing switch                           | 200                                            | mA             |

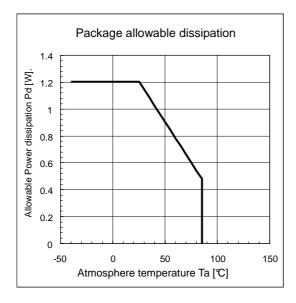

| Allowable power<br>Dissipation | P <sub>D</sub>    | Ta = 25℃                                              | 1.2                                            | W              |

| Junction<br>temperature        | Тј <sub>МАХ</sub> | _                                                     | 125                                            | C              |

| Package thermal resistance     | θja               | JEDEC 2 layer board                                   | 83                                             | cw             |

| Storage<br>tempetrature        | T <sub>STG</sub>  | -                                                     | -55 to +150                                    | Ĵ              |

Package loss tolerant decreases as the atmosphere temperature (Ta) increase. If VREG pin output load current is large, make the power loss smaller than the value shown in this figure.

#### RECOMMENDED OPERATING CONDITIONS

(GND= 0 V)

| Parameter              | Symbol          | Condition         | Range      | unit |

|------------------------|-----------------|-------------------|------------|------|

| Power supply voltage   | V <sub>DD</sub> | VDD, VDDP, VDD_SW | 7 to 80    | V    |

| Opereating temperature | Та              | VREG no-loaded    | -40 to +85 | °C   |

#### ELECTRICAL CHARACTERISTICS

#### • DC CHARACTERISTICS

| Parameter                                         | Symbol            | Condition                                                                  | Min.                   | Тур. | Max.                 | unit |

|---------------------------------------------------|-------------------|----------------------------------------------------------------------------|------------------------|------|----------------------|------|

| Digital "H" input voltage<br>(note1)              | VIH               | -                                                                          | $0.8 \times V_{REG}$   | _    | $V_{REG}$            | V    |

| Digital "L" input voltage<br>(note1)              | VIL               | _                                                                          | 0                      | _    | $0.2 \times V_{REG}$ | V    |

| /PUPIN-pin "H" input voltage                      | VIHP              | -                                                                          | $0.8 \times V_{DD}$    | _    | V <sub>DD</sub>      | V    |

| /PUPIN-pin "L" input voltage                      | $V_{ILP}$         | —                                                                          | 0                      | _    | $0.2 \times V_{DD}$  | V    |

| Digital "H" input current(note1)                  | I <sub>IH</sub>   | $V_{IH} = V_{REG}$                                                         | _                      | _    | 2                    | μA   |

| Digital "L" input current (note1)                 | IIL               | $V_{IL} = GND$                                                             | -2                     | -    | _                    | μA   |

| /PUPIN-pin "H" input current                      | I <sub>IHP</sub>  | $V_{IH} = V_{DD}$                                                          | —                      | -    | 2                    | μA   |

| /PUPIN-pin "L" input current                      | I <sub>ILP</sub>  | $V_{DD}$ = 64V, $V_{IL}$ = GND                                             | -128                   | -64  | -32                  | μA   |

| Digital "H" output voltage<br>(note2)             | V <sub>OH</sub>   | I <sub>OH</sub> = -100μA                                                   | V <sub>REG</sub> - 0.2 | _    | $V_{REG}$            | V    |

| Digital "L" output voltage<br>(note3)             | V <sub>OL</sub>   | I <sub>OL</sub> = 1mA                                                      | 0                      | _    | 0.2                  | V    |

| Digital output Leak current<br>(note3)            | I <sub>OLK</sub>  | V <sub>OH</sub> =3V<br>V <sub>OL</sub> =0V                                 | -2                     | _    | 2                    | μA   |

| Cell monitoring pin<br>Input current (note 4)     | I <sub>INVC</sub> | If measuring battery cell voltage                                          | -5                     | _    | 15                   | μA   |

| Cell monitoring pin<br>Input leak current (note4) | I <sub>ILVC</sub> | If not measuring battery cell voltage                                      | -5                     | _    | 5                    | μA   |

| FET "H" output voltage (note5)                    | V <sub>OH</sub>   | I <sub>OH</sub> =-10μA<br>V <sub>DD</sub> =18V to 72V                      | 10                     | 14   | 18                   | V    |

| FET "L" output voltage (note6)                    | V <sub>OL</sub>   | I <sub>OL</sub> = 100μA                                                    | 0                      | _    | 0.3                  | V    |

| C_FET output leak current                         | ILVC              | V <sub>CFET</sub> =0V to V <sub>DD</sub>                                   | -5                     | _    | 5                    | μA   |

|                                                   | $V_{REG}$         | Output No-loaded                                                           | 3.1                    | 3.3  | 3.6                  | V    |

|                                                   | V <sub>REG1</sub> | 10V <v<sub>DD&lt;64V<br/>Ta=-10 to 60°C<br/>Load current &lt; 10mA</v<sub> | 3.1                    | 3.3  | 3.5                  | V    |

| VREG output voltage                               | V <sub>REG2</sub> | 10V <v<sub>DD&lt;64V<br/>Ta=-40 to 70°C<br/>Load current &lt; 10mA</v<sub> | 3.0                    | 3.3  | 3.6                  | V    |

|                                                   | V <sub>REG3</sub> | 7V <v<sub>DD&lt;10V<br/>Ta = -10 to 60℃<br/>Load current &lt; 5mA</v<sub>  | 3.1                    | 3.3  | 3.5                  | V    |

|                                                   | $V_{REG4}$        | 7V <v<sub>DD&lt;10V<br/>Ta = -40 to 85℃<br/>Load current &lt; 5mA</v<sub>  | 3.0                    | 3.3  | 3.6                  | V    |

| VREF output voltage                               | $V_{REF1}$        | Ta = -10 to 60℃<br>Load current < 1mA                                      | 3.28                   | 3.30 | 3.34                 | V    |

|                                                   | $V_{REF2}$        | Ta = -40 to 85℃<br>Load current < 1mA                                      | 3.25                   | 3.30 | 3.35                 | V    |

| Cell balancing switch ON resistance               | R <sub>BL</sub>   | Internal balancing FET<br>$V_{DS} = 0.6V$<br>$V_{DD} = 18V$ to $64V$       | 3                      | 6    | 12                   | Ω    |

Note 1: Applied to pins: /CS, SCK, SDI

Note2: Applied to SDO pin

Note3: Applied to pins: SDO, /RES, /INTO

Note4: Applied to pins V16 to V0

Note5: Applied to pins C\_FET, D\_FET

Note6: Applied to D\_FET pin

|                          | V <sub>DD</sub> =7 | to 64V, GND=0 V, Ia= | -40 to +85℃ | , VREG, VRE | =⊢ output no | noaded |

|--------------------------|--------------------|----------------------|-------------|-------------|--------------|--------|

| Parameter                | Symbol             | Condition            | Min.        | Тур.        | Max.         | Unit   |

| Normal operating Current | I <sub>DD1</sub>   | No-loaded            | -           | 50          | 100          | μA     |

| Power save Current       | I <sub>DD2</sub>   | No-loaded            | _           | 25          | 50           | μA     |

| Power down Current       | I <sub>DDS</sub>   | No-loaded            | -           | 0.1         | 1.0          | μA     |

#### • SUPPLY CURRENT CHARACTERISTICS

(note) These power supply current is defined as the total current of VDD-pin and the VDDP-pin.

(note) The load current is added to these power supply current, using the load with VREG connector.

#### • DETECTING VOLTAGE CHARACTERISTICS (TA=25°C)

|                                       |                    | V <sub>DD</sub> =48      | BV, GND=0 V, | . Ta=25℃ , VF | REG output no | o-loaded |

|---------------------------------------|--------------------|--------------------------|--------------|---------------|---------------|----------|

| Parameter                             | Symbol             | Condition                | Min.         | Тур.          | Max.          | Unit     |

|                                       | V <sub>SHRT0</sub> | SC1,SC0 bit = (0,0)      | 0.05         | 0.1           | 0.15          | V        |

| Short current detecting               | V <sub>SHRT1</sub> | SC1,SC0 bit = (0,1)      | 0.1          | 0.2           | 0.3           | V        |

| voltage                               | V <sub>SHRT2</sub> | SC1,SC0 bit = (1,0)      | 0.2          | 0.3           | 0.4           | V        |

|                                       | V <sub>SHRT3</sub> | SC1,SC0 bit = (1,1)      | 0.3          | 0.4           | 0.5           | V        |

| Short current detecting<br>delay time | t <sub>SHRT</sub>  | $C_{\text{DLY}} = 1 n F$ | 50           | 100           | 200           | μs       |

| VREG low detecting<br>voltage         | $V_{RD}$           | -                        | 2.3          | 2.45          | 2.6           | V        |

| VREG recovery detecting<br>voltage    | V <sub>RR</sub>    | -                        | 2.5          | 2.75          | 2.9           | V        |

(note) Short detecting delay time tSC [µs]=CDLY[nF] x 100.

#### • DETECTING VOLTAGE CHARACTERISTICS (TA= -10 ~ 60°C)

| • DETECTING VOL                       | INGLU              | IIANACIENISIIC           | $(1A - 10)^{-1}$ | 00 C)       |               |          |

|---------------------------------------|--------------------|--------------------------|------------------|-------------|---------------|----------|

|                                       |                    | V <sub>DD</sub> =48V, GN | ND=0 V, Ta=-     | 10~+60℃, VF | REG output no | o-loaded |

| Parameter                             | Symbol             | Condition                | Min.             | Тур.        | Max.          | Unit     |

|                                       | V <sub>SHRT0</sub> | SC1,SC0 bit = (0,0)      | 0.04             | 0.1         | 0.16          | V        |

| Short current detecting               | V <sub>SHRT1</sub> | SC1,SC0 bit = (0,1)      | 0.09             | 0.2         | 0.31          | V        |

| voltage                               | V <sub>SHRT2</sub> | SC1,SC0 bit = (1,0)      | 0.19             | 0.3         | 0.41          | V        |

|                                       | V <sub>SHRT3</sub> | SC1,SC0 bit = (1,1)      | 0.29             | 0.4         | 0.51          | V        |

| Short current detecting<br>delay time | t <sub>SHRT</sub>  | $C_{DLY} = 1nF$          | 40               | 100         | 220           | μs       |

| VREG low detecting voltage            | V <sub>RD</sub>    | -                        | 2.20             | 2.45        | 2.70          | V        |

| VREG recovery detecting<br>voltage    | V <sub>RR</sub>    | _                        | 2.40             | 2.75        | 3.00          | V        |

(note) Short detecting delay time tSC  $[\mu s]$ =CDLY[nF] x 100.

|                          |                    | V <sub>DD</sub> =4  | 8V, GND=0V, | Ta=25℃,VF | REG output no              | o-loaded |

|--------------------------|--------------------|---------------------|-------------|-----------|----------------------------|----------|

| Parameter                | Symbol             | Condition           | Min.        | Тур.      | Max.                       | Unit     |

|                          | V                  | Cell voltage = 3.6V | 1.79        | 1.8       | 1 01                       | V        |

|                          | V <sub>VMC1</sub>  | Output no-loaded    | 1.79        | 1.0       | 1.01                       | V        |

| VMON output voltage      | V                  | Cell voltage = 1V   | 0.48        | 0.50      | 0.52                       | V        |

|                          | V <sub>VMC2</sub>  | Output no-loaded    | 0.40        | 0.50      | 0.52                       | v        |

|                          | V <sub>IMON0</sub> | ISP-ISM voltage     | 0.9         | 1.0       | 1.1                        |          |

|                          |                    | difference = 0V     |             |           |                            | V        |

| IMON output voltage      |                    | GIM bit = "0"       |             |           |                            |          |

| INON output voltage      |                    | ISP-ISM voltage     |             |           |                            |          |

|                          | VIMON1             | difference = 0V     | 0.5         | 1.0       | 1.5                        | V        |

|                          |                    | GIM bit = "1"       |             |           |                            |          |

| IMON output voltage gain | GIMO               | GIM bit = "0"       | 9           | 10        | 11                         | V/V      |

|                          | G <sub>IM1</sub>   | GIM bit = "1"       | 45          | 50        | 1.81<br>0.52<br>1.1<br>1.5 | V/V      |

#### • VOLTAGE AND CURRENT MONITORING CHARACTERISTICS (TA=25°C)

# • VOLTAGE AND CURRENT MONITORING CHARACTERISTICS (TA=-10 ~60°C)

|                          |                    | V <sub>DD</sub> =48V, G | ind=0v, la=- | 10~+60℃,VF | REG output no | o-loaded |

|--------------------------|--------------------|-------------------------|--------------|------------|---------------|----------|

| Parameter                | Symbol             | Condition               | Min.         | Тур.       | Max.          | Unit     |

|                          | V                  | Cell voltage = 3.6V     | 1.78         | 1.8        | 1.82          | V        |

| VMON output voltage      | V <sub>VMC1</sub>  | Output no-loaded        | 1.70         | 1.0        | 1.02          | v        |

| vinion output voltage    | V                  | Cell voltage = 1V       | 0.47         | 0.50       | 0.52          | V        |

|                          | V <sub>VMC2</sub>  | Output no-loaded        | 0.47         | 0.50       | 0.53          | v        |

|                          | V <sub>IMON0</sub> | ISP-ISM voltage         | 0.85         | 1.0        | 1.15          |          |

|                          |                    | difference = 0V         |              |            |               | V        |

| IMON output voltage      |                    | GIM bit = "0"           |              |            |               |          |

| INON output voltage      |                    | ISP-ISM voltage         |              |            |               |          |

|                          | V <sub>IMON1</sub> | difference = 0V         | 0.4          | 1.0        | 1.6           | V        |

|                          |                    | GIM bit = "1"           |              |            |               |          |

|                          | GIMO               | GIM bit = "0"           | 8.5          | 10.0       | 11.5          | V/V      |

| IMON output voltage gain | GIM1               | GIM bit = "1"           | 44           | 50         | 56            | V/V      |

# • LOAD DISCONNECTION, CHARGER CONNECTION AND DISCONNECTION DETECTING VOLTAGE CHARACTERISTIC (TA=25°C)

| DETECTING VOLTAGE CHARACTERISTIC (TA-25 C)            |                      |                                        |                       |                       |                      |      |  |

|-------------------------------------------------------|----------------------|----------------------------------------|-----------------------|-----------------------|----------------------|------|--|

|                                                       | V <sub>DD</sub> =48V | , GND=0V, 1                            | Гa=25℃                |                       |                      |      |  |

| Parameter                                             | Symbol               | Condition                              | Min.                  | Тур.                  | Max.                 | Unit |  |

| Detecting Charger<br>connection PSENSE pin<br>voltage | V <sub>PC</sub>      | At power up from power down state      | V <sub>DD</sub> × 0.2 | $V_{DD}$ ×0.5         | V <sub>DD</sub> ×0.8 | V    |  |

| Detecting charger<br>disconnection PSENSE             | V <sub>PLU</sub>     | PSENSE register<br>PSL bit threshold   | 0.1                   | 0.2                   | 0.3                  | V    |  |

| pin voltage                                           | V <sub>PLD</sub>     | PSENSE register<br>PSH bit threshold   | $V_{DD} \times 0.7$   | V <sub>DD</sub> ×0.75 | V <sub>DD</sub> ×0.8 | V    |  |

| Detecting load<br>disconnection RSENSE<br>pin voltage | V <sub>RL</sub>      | RSENSE register<br>RRS bit threshold   | 2.2                   | 2.4                   | 2.6                  | V    |  |

| PSENSE pull-up resistor                               | R <sub>PU</sub>      | PSENSE register<br>EPSL、EPSH = "1"     | 300                   | 500                   | 850                  | kΩ   |  |

| RSENSE pull-down<br>resistor                          | $R_{PD}$             | RSENSE register<br>ERS = "1"           | 1                     | 2                     | 3                    | MΩ   |  |

| PSENSE input leakage<br>current                       | I <sub>LPS</sub>     | pull-up resistor is not<br>connected   | -2                    | -                     | 2                    | μA   |  |

| RSENSE input leakage<br>current                       | I <sub>LRS</sub>     | Pull-down resistor is not<br>connected | -2                    | -                     | 2                    | μA   |  |

#### • LOAD DISCONNECTION, CHARGER CONNECTION AND DISCONNECTION DETECTING VOLTAGE CHARACTERISTIC (TA=-10 ~60°C) Von=48V. GND=0V. Ta=-10~60°C

| V <sub>DD</sub> =48V, GND=0V, Ta=-10~60               |                  |                                        |                        |                       |                       |      |  |  |

|-------------------------------------------------------|------------------|----------------------------------------|------------------------|-----------------------|-----------------------|------|--|--|

| Parameter                                             | Symbol           | Condition                              | Min.                   | Тур.                  | Max.                  | Unit |  |  |

| Detecting Charger<br>connection PSENSE pin<br>voltage | V <sub>PC</sub>  | At power up from power down state      | V <sub>DD</sub> × 0.2  | $V_{DD}$ ×0.5         | V <sub>DD</sub> ×0.8  | V    |  |  |

| Detecting charger<br>disconnection PSENSE             | V <sub>PLU</sub> | PSENSE register<br>PSL bit threshold   | 0                      | 0.2                   | 0.4                   | V    |  |  |

| pin voltage                                           | $V_{PLD}$        | PSENSE register<br>PSH bit threshold   | V <sub>DD</sub> × 0.65 | V <sub>DD</sub> ×0.75 | V <sub>DD</sub> ×0.85 | V    |  |  |

| Detecting load<br>disconnection RSENSE<br>pin voltage | V <sub>RL</sub>  | RSENSE register<br>RRS bit threshold   | 2.0                    | 2.4                   | 2.8                   | V    |  |  |

| PSENSE pull-up resistor                               | R <sub>PU</sub>  | PSENSE register<br>EPSL、EPSH = "1"     | 200                    | 500                   | 1000                  | kΩ   |  |  |

| RSENSE pull-down<br>resistor                          | R <sub>PD</sub>  | RSENSE register<br>ERS = "1"           | 0.5                    | 2                     | 4                     | MΩ   |  |  |

| PSENSE input leakage<br>current                       | I <sub>LPS</sub> | pull-up resistor is not<br>connected   | -2                     | -                     | 2                     | μΑ   |  |  |

| RSENSE input leakage<br>current                       | I <sub>LRS</sub> | Pull-down resistor is not<br>connected | -2                     | -                     | 2                     | μΑ   |  |  |

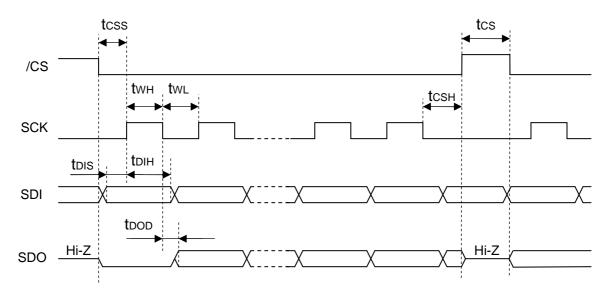

#### • AC CHARACTERISTICS

| $V_{DD}$ =7 to 80V, GND=0V, Ta=-40 to +85 $^\circ$ C, VREG output no-load |                  |           |      |      |      |      |  |  |

|---------------------------------------------------------------------------|------------------|-----------|------|------|------|------|--|--|

| Parameter                                                                 | Symbol           | Condition | Min. | Тур. | Max. | Unit |  |  |

| /CS-SCK setup time                                                        | t <sub>CSS</sub> | _         | 100  | —    | —    | ns   |  |  |

| SCK-/CS hold time                                                         | t <sub>CSH</sub> | _         | 100  | _    | —    | ns   |  |  |

| SCK "H" pulse width                                                       | t <sub>WH</sub>  | _         | 500  | _    | —    | ns   |  |  |

| SCK "L" pulse width                                                       | t <sub>WL</sub>  | _         | 500  | _    | —    | ns   |  |  |

| SCK-SDI setup time                                                        | t <sub>DIS</sub> | _         | 50   | _    | —    | ns   |  |  |

| SCK-SDI hold time                                                         | t <sub>DIH</sub> | -         | 50   | _    | -    | ns   |  |  |

| SCK-SDO output delay time                                                 | t <sub>DOD</sub> | _         | _    | _    | 400  | ns   |  |  |

| /CS "H" pulse width                                                       | t <sub>cs</sub>  | _         | 500  | _    | _    | ns   |  |  |

#### FUNCTIONAL DESCRIPTION

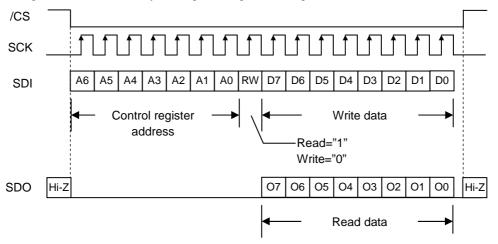

#### • MCU INTERFACE

SPI interface is built in the ML5238.

Setting and control is held by writing /reading control registers.

Set the RW bit "0" to write data, and set the RW bit "1" to read data.

#### • CONTROL REGISTER

Control register map is shown below.

| Address | Register | R/W | Initial<br>value | Register setting                                                 |

|---------|----------|-----|------------------|------------------------------------------------------------------|

| 00H     | NOOP     | R/W | 00H              | No function assigned                                             |

| 01H     | VMON     | R/W | 00H              | Battery cell voltage Measurement                                 |

| 02H     | IMON     | R/W | 00H              | Current measurement setting                                      |

| 03H     | FET      | R/W | 00H              | FET setting                                                      |

| 04H     | PSENSE   | R/W | 00H              | PSENSE pin comparator setting                                    |

| 05H     | RSENSE   | R/W | 00H              | Short current detection setting<br>RSENSE pin comparator setting |

| 06H     | POWER    | R/W | 00H              | Power save, Power down control                                   |

| 07H     | STATUS   | R/W | 00H              | Internal Status                                                  |

| 08H     | CBALH    | R/W | 00H              | Upper 8 cell balancing switch ON/OFF<br>setting                  |

| 09H     | CBALL    | R/W | 00H              | Lower 8 cell balancing switch ON/OFF<br>setting                  |

| 0AH     | SETSC    | R/W | 00H              | Short current detecting voltage setting                          |

| others  | TEST     | R/W | 00H              | TEST (Don't use)                                                 |

#### 1. NOOP register (Adrs = 00H)

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit name      | NO7 | NO6 | NO5 | NO4 | NO3 | NO2 | NO1 | NO0 |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

No function is assigned to NOOP register, there is no status changes in the LSI even if this register is written or read. In the read operation written data is read

#### 2. VMON register (Adrs = 01H)

|               | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|---------------|---|---|---|-----|-----|-----|-----|-----|

| Bit name      | - | _ | _ | OUT | CN3 | CN2 | CN1 | CN0 |

| R/W           | R | R | R | R/W | R/W | R/W | R/W | R/W |

| Initial value | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   |

VMON register sets the battery cell outputted to the VMON pin.

Select the battery cell by CN0, CN1, CN2, CN3 bits, and OUT bit enable the output from VMON

pin.

|     | 1   | 1   | 1   | 1   | 1                             |

|-----|-----|-----|-----|-----|-------------------------------|

| OUT | CN3 | CN2 | CN1 | CN0 | Battery cell selection        |

| 0   | _   | -   | -   | -   | VMON pin = 0V (initial value) |

| 1   | 0   | 0   | 0   | 0   | V1 cell (lower most)          |

| 1   | 0   | 0   | 0   | 1   | V2 cell                       |

| 1   | 0   | 0   | 1   | 0   | V3 cell                       |

| 1   | 0   | 0   | 1   | 1   | V4 cell                       |

| 1   | 0   | 1   | 0   | 0   | V5 cell                       |

| 1   | 0   | 1   | 0   | 1   | V6 cell                       |

| 1   | 0   | 1   | 1   | 0   | V7 cell                       |

| 1   | 0   | 1   | 1   | 1   | V8 cell                       |

| 1   | 1   | 0   | 0   | 0   | V9 cell                       |

| 1   | 1   | 0   | 0   | 1   | V10 cell                      |

| 1   | 1   | 0   | 1   | 0   | V11 cell                      |

| 1   | 1   | 0   | 1   | 1   | V12 cell                      |

| 1   | 1   | 1   | 0   | 0   | V13 cell                      |

| 1   | 1   | 1   | 0   | 1   | V14 cell                      |

| 1   | 1   | 1   | 1   | 0   | V15 cell                      |

| 1   | 1   | 1   | 1   | 1   | V16 cell (upper most)         |

3. IMON register (Adrs = 02H)

|               | 7 | 6 | 5 | 4   | 3     | 2     | 1    | 0   |

|---------------|---|---|---|-----|-------|-------|------|-----|

| Bit name      | Ι | _ | _ | OUT | GCAL1 | GCAL0 | ZERO | GIM |

| R/W           | R | R | R | R/W | R/W   | R/W   | R/W  | R/W |

| Initial value | 0 | 0 | 0 | 0   | 0     | 0     | 0    | 0   |

IMON register set the current measuring.

GIM bit set the voltage gain of current measuring amplifier.

| GIM | Voltage gain G <sub>IM</sub> |

|-----|------------------------------|

| 0   | 10 times (initial value)     |

| 1   | 50 times                     |

ZERO bit set the zero-correction of current measuring amplifier.

| ZERC | ) | ISP input | ISM input |

|------|---|-----------|-----------|

| 0    |   | Pin input | Pin input |

| 1    |   | GND level | GND level |

Voltage gain of current measuring amplifier is corrected by GCAL0, GCAL1 bits. GCAL0 bit changes the ISP and ISM pin input to GND or internal reference voltage (20mV/100mV).

GCAL1 bit changes the IMON pin output to internal reference voltage output.

| GCAL1 | GCAL0   | ISP input |         | ISM input | IMON output                             |

|-------|---------|-----------|---------|-----------|-----------------------------------------|

| 0     | 0       | Pi        | n input | Pin input | Amplified output                        |

| 0     | 1       | GIM=0     | 100mV   | GND level | 2V (typ)                                |

| 0     | I       | GIM=1     | 20mV    | GND level | 2V (typ)                                |

| 1     | 0       | Pi        | n input | Pin input | Amplified output                        |

| 1     | GIM=0 1 |           | 100mV   | GND level | Reference voltage<br>output 100mV (typ) |

|       | I       | GIM=1     | 20mV    | GND level | Reference voltage<br>output 20mV (typ)  |

If the ZERO bit is set "1", setting GCAL1 and GCAL0 bits are neglected.

OUT bit enables to output the current measuring amplifier from IMON pin. If zero correction and gain correction is held, OUT bit is set "1" too.

| OUT | IMON pin output                    |

|-----|------------------------------------|

| 0   | 0V (initial value)                 |

| 1   | Current measuring amplifier output |

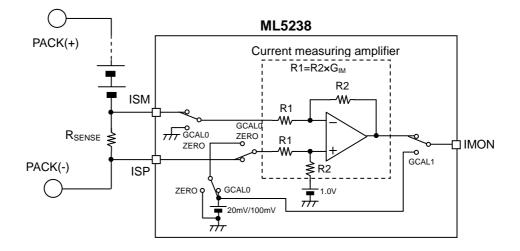

Current measurement is executed with current sensin resistor ( $R_{SENSE}$ ) connected between ISP pin and ISM pin and by measuring input voltage difference between these pins.

Voltage difference between ISP and ISM is converted to voltage, its center is 1.0V (typ), and outputted from IMON pin. IMON pin output voltage  $V_{IMON}$  is given by the following equation with the current sensing resistor  $R_{SENSE}$  and its current  $I_{SENSE}$ .

$V_{IMON} \hspace{0.1 in} = \hspace{0.1 in} (I_{SENSE} \times R_{SENSE}) \times G_{IM} + 1.0$

The circuit of current measuring amplifier is shown below.

If the current is zero,  $V_{IMON} = 1.0V$ , in the discharging state,  $V_{IMON} > 1.0V$ , in the charging state,  $V_{IMON} < 1.0V$ .

When the ZERO bit is set "1", the input of ISM pin and ISM pin is switched to GND level in the LSI and set the input difference voltage of the current measuring amplifier to zero. The IMON pin output voltage in this state is set as the reference voltage of zero current, and internal 1.0V reference voltage and offset voltage of amplifier is corrected.

If the GCAL0 bit is set "1"; the ISM pin input is switched to GND level in the LSI; the ISP pin input is switched to 100mV (internal reference voltage) if the GIM bit is "0", and else if GIM bit is "1" the ISP pin input is switched to 20mV (internal reference voltage). The gain error is corrected with the difference between the IMON output voltage at this state and it at current zero, and internal reference voltage.

Internal reference voltage is outputted from IMON pin by setting the GCAL1 bit "1".

Short current detection characteristic is not depended on the IMON pin output setting.

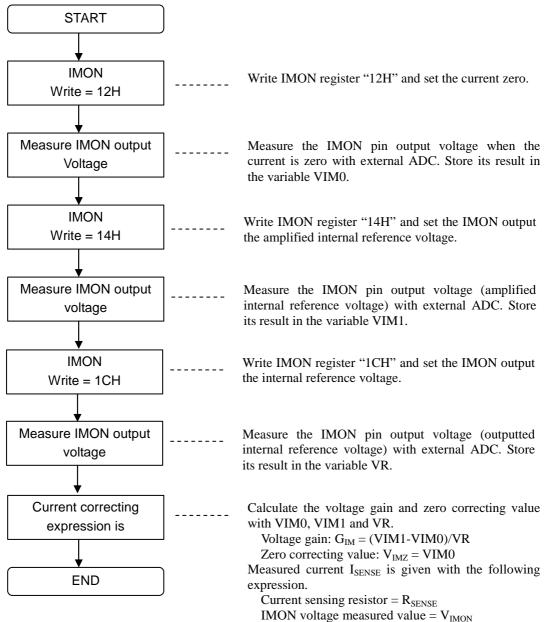

The example flowchart of calibration for current measuring amplifier is shown below. (Voltage gain is 10)

$I_{\text{SENSE}} = (V_{\text{IMON}} - V_{\text{IMZ}}) / G_{\text{IM}} / R_{\text{SENSE}}$

4. FET register (Adrs = 03H)

|               | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|---------------|---|---|---|-----|---|---|-----|-----|

| Bit name      | - | - | - | DRV | _ | _ | CF  | DF  |

| R/W           | R | R | R | R/W | R | R | R/W | R/W |

| Initial value | 0 | 0 | 0 | 0   | 0 | 0 | 0   | 0   |

FET register control the turn ON/OFF of the C\_FET and D\_FET pin, and read the state of its output.

DF bit sets the D\_FET pin output state. If the short current is detected, the DF bit is automatically cleared to "0". Because the DF bit is not automatically set "1" even if the state is changed from short detection to normal state, external MCU must set this bit "1".

| DF | Discharge FET       | D_FET pin output |

|----|---------------------|------------------|

| 0  | OFF (initial value) | 0V               |

| 1  | ON                  | 14V (typ)        |

CF bit set the C\_FET pin output state. If the short current is detected, the CF bit is automatically cleared tot "0". Because the CF bit is not automatically set "1" even if the state is changed from short detection to normal state, external MCU must set this bit "1".

| CF | Charge FET          | C_FET pin output |

|----|---------------------|------------------|

| 0  | OFF (initial value) | Hi-Z             |

| 1  | ON                  | 14V (typ)        |

DRV bit set the output current drive capacity of internal FET driver. If the DRV bit is set "1", the rising time of D\_FET, C\_FET pins is short.

The duration to set the DRV bit "1" should be set depend on the capacitance load of the D\_FET, C\_FET pins. DRV bit should be cleared to "0", after the D\_FET, C\_FET pin output level is fully risen to "H".

If the DRV bit is left "1", power consumption or the "H" output voltage of D\_FET, C\_FET might be higher than the level specified in the electrical characteristics.

| DRV | FET driver output capacity |

|-----|----------------------------|

| 0   | Normal (initial value)     |

| 1   | enhanced                   |

5. PSENSE register (Adrs = 04H)

|               | 7    | 6    | 5    | 4   | 3    | 2    | 1    | 0   |

|---------------|------|------|------|-----|------|------|------|-----|

| Bit name      | EPSH | IPSH | RPSH | PSH | EPSL | IPSL | RPSL | PSL |

| R/W           | R/W  | R/W  | R/W  | R   | R/W  | R/W  | R/W  | R   |

| Initial value | 0    | 0    | 0    | 0   | 0    | 0    | 0    | 0   |

PSENSE register set the parameters of comparators which detect charger connection/disconnection with PSENSE pin input.

Two comparators with difference threshold are connected to PSENSE pin to manage ON and OFF states of discharge FET.

For detecting charger disconnection in the state of discharge FET ON, low level threshold (0.2V (typ)) type comparator is selected, because PSENSE pin voltage is clamped by the body-diode of charge FET.

Low level threshold type comparator is selected mainly for detecting charger open in the state of charge over-current detected,

Parameters of the low level threshold type comparator for detecting the charger open is set in EPSL, IPSL, and RPSL bits. Comparator output is assigned to PSL bit.

EPSL bit set the run/stop of the comparator for detecting charger open. If EPSL bit is set running,  $500k\Omega$  pull-up resistor is connected to PSENSE pin in the LSI.

| EPSL | State of comparator for<br>detecting charger open | PSENSE pin status    |

|------|---------------------------------------------------|----------------------|

| 0    | Stop (initial value)                              | Hi-Z (initial value) |

| 1    | Run                                               | 500kΩ pull-up        |

IPSL bit enables asserting the interrupt from /INTO pin, if the output of comparator detecting charger open (PSL bit) is changed from "0" to "1". IPSL bit should be set "1" more than 1 msec later from setting the EPSL bit "1".

| IPSL | Interrupt enable        |  |

|------|-------------------------|--|

| 0    | Disable (initial value) |  |

| 1    | enable                  |  |

RPSL bit indicates the interrupt assertion if the output of comparator detecting charger open (PSL bit) is changed from "0" to "1". To clear this interrupt, write "0" in the RPSL bit. Writing "1" in the RPSL bit is neglected. If IPSL bit is "0", RPSL bit is fixed to "0".

| RPSL | Interrupt occurred           |

|------|------------------------------|

| 0    | No interrupt (initial value) |

| 1    | Interrupted                  |

PSL bit indicates the state of charger connected. If the EPSL bit is "0", PSL bit is fixed to "0". Writing "1" in the PSL bit is neglected.

| PSL | Charger connection                   | PSENSE pin voltage |

|-----|--------------------------------------|--------------------|

| 0   | Charger connected<br>(initial value) | 0.2V or less       |

| 1   | Charger disconnected                 | Larger than 0.2V   |

For detecting charger disconnection in the state of discharge FET OFF, high level threshold  $(V_{DD} \times 0.75)$  type comparator is selected, because PSENSE pin voltage rise up to power supply voltage  $(V_{DD})$ .

High level threshold comparator is selected mainly for detecting charger open if the status changes to power down state.

Parameters of the high level threshold type comparator for detecting the charger open is set in EPSH, IPSH, and RPSH bits. Comparator output is assigned to PSH bit.

EPSH bit set the run/stop of the comparator for detecting charger open. If EPSH bit is set running,  $500k\Omega$  pull-up resistor is connected to PSENSE pin in the LSI.

| EPSH | State of comparator for detecting charger open | PSENSE pin status    |

|------|------------------------------------------------|----------------------|

| 0    | Stop (initial value)                           | Hi-Z (initial value) |

| 1    | Running                                        | 500kΩ pull-up        |

IPSH bit enables asserting the interrupt from /INTO pin, if the output of comparator detecting charger open (PSH bit) is changed from "0" to "1". IPSH bit should be set "1" more than 1 msec later from setting the EPSH bit "1".

| IPSH | Interrupt enable        |

|------|-------------------------|

| 0    | Disable (initial value) |

| 1    | enabled                 |

RPSH bit indicates the interrupt assertion if the output of comparator detecting charger open (PSH bit) is changed from "0" to "1". To clear this interrupt, write "0" in the RPSH bit. Writing "1" in the RPSH bit is neglected. If IPSH bit is "0", RPSH bit is fixed to "0".

| RPSH | Interrupt occurred           |

|------|------------------------------|

| 0    | No interrupt (initial value) |

| 1    | interrupted                  |

PSH bit indicates the state of charger connected. If the EPSH bit is "0", PSH bit is fixed to "0". Writing "1" in the PSH bit is neglected.

| PSH | Charger connection                   | PSENSE pin voltage                |

|-----|--------------------------------------|-----------------------------------|

| 0   | Charger connected<br>(initial value) | $V_{DD}$ ×0.75 or less            |

| 1   | Charger disconnected                 | Larger than V <sub>DD</sub> ×0.75 |

6. RSENSE register (Adrs = 05H)

|               | 7   | 6   | 5   | 4  | 3   | 2   | 1   | 0  |

|---------------|-----|-----|-----|----|-----|-----|-----|----|

| Bit name      | ESC | ISC | RSC | SC | ERS | IRS | RRS | RS |

| R/W           | R/W | R/W | R/W | R  | R/W | R/W | R/W | R  |

| Initial value | 0   | 0   | 0   | 0  | 0   | 0   | 0   | 0  |

RSENSE register set the parameters of detecting short current and the parameters of comparator which detect load connection/disconnection with RSENSE pin input.

ESC bit set the run/stop of the circuit detecting short current.

| ESC | Status of the circuit detecting |  |  |  |

|-----|---------------------------------|--|--|--|

| L30 | short current                   |  |  |  |

| 0   | Stop (initial value)            |  |  |  |

| 1   | Run                             |  |  |  |

ISC bit enables asserting the interrupt from /INTO pin, if the short current is detected.

| ISC | Interrupt enable        |

|-----|-------------------------|

| 0   | Disable (initial value) |

| 1   | enable                  |

RSC bit indicates the interrupt assertion if the short current is detected. To clear the interrupt, write "0" in the RSC bit. Writing "1" in the RSC bit is neglected. If ISC bit is "0", RSC bit is fiexed to "0".

| RSC | Interrupt occurred           |

|-----|------------------------------|

| 0   | No interrupt (initial value) |

| 1   | interrupted                  |

SC bit indicates the output from the comparator detecting short current.

If the SC bit is changed from "0" to "1", charging the capacitor connected to CDLY pin is started. If this charging is finished, the RSC bit is automatically changed to "1" and the DF bit and the CF bit in the FET register is automatically cleared to "0". If the short current status is cleared before charging the capacitor connected to CDLY pin is finished, charging the CDLY pin is stopped and the CDLY pin is fixed to GND level.

| 1 | se on is o, se on is ince to o. Writing T in the se on is neglected. |                                                            |                                             |  |  |  |

|---|----------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|--|--|--|

|   | SC                                                                   | Status of the comparator<br>output detecting short current | ISP-ISM voltage                             |  |  |  |

|   | 0                                                                    | Short current is not detected (initial value)              | Short current detecting<br>voltage or lower |  |  |  |

|   | 1                                                                    | Short current is detected                                  | Higher than short current detecting voltage |  |  |  |

Short current detecting delay time is set with the charging time of capacitor  $C_{DLY}$  which is connected to CDLY pin ; calculated with following formula.

Short current detecting delay time  $t_{sc} [\mu s] = C_{DLY}[nF] \times 100$

ERS bit set the run/stop of the comparator for detecting load open. If ERS bit is set running,  $2M\Omega$  pull-down resistor is connected to RSENSE pin in the LSI.

| ERS | State of comparator for<br>detecting load open | RSENSE pin status    |

|-----|------------------------------------------------|----------------------|

| 0   | Stop (initial value)                           | Hi-Z (initial value) |

| 1   | Running                                        | 2MΩ pull-down        |

IRS bit enables asserting the interrupt from /INTO pin, if the output of comparator detecting load open (RS bit) is changed from "0" to "1". IRS bit should be set "1" more than 1 msec later from setting the ERP bit "1".

| IRS | Interrupt enable        |

|-----|-------------------------|

| 0   | Disable (initial value) |

| 1   | enabled                 |

RRS bit indicates the interrupt assertion if he output of comparator detecting load open(RS bit) is changed from "0" to "1". To clear this interrupt, write "0" in the RRS bit. Writing "1" in the RRS bit is neglected. If IRS bit is "0", RRS bit is fixed to "0".

| in mas one h |                              |

|--------------|------------------------------|

| RRS          | Interrupt occurred           |

| 0            | No interrupt (initial value) |

| 1            | interrupted                  |

RS bit indicates the state of load connected. If the ERS bit is "0", RS bit is fixed to "0". Writing "1" in the RS bit is neglected.

| RS | Load connection                | RSENSE pin voltage |

|----|--------------------------------|--------------------|

| 0  | Load connected (initial value) | 2.4V or higher     |

| 1  | Load disconnected              | Lower than 2.4V    |

7. POWER register (Adrs = 06H)

|               | 7     | 6 | 5 | 4    | 3 | 2 | 1 | 0   |

|---------------|-------|---|---|------|---|---|---|-----|

| Bit name      | PUPIN | - | - | PDWN | — | - | - | PSV |

| R/W           | R     | R | R | R/W  | R | R | R | R/W |

| Initial value | 0     | 0 | 0 | 0    | 0 | 0 | 0 | 0   |

Power register control the power save and the power down.

PSV bit set the state transition to power save.

| PSV | Power save                   |  |  |  |

|-----|------------------------------|--|--|--|

| 0   | Normal state (initial value) |  |  |  |

| 1   | Power save state             |  |  |  |

In the power save state, circuits for VREG output and VREF output is operating, cell voltage measuring and current measuring is stopped, and the power consumption is reduced. FET driving and short detecting circuit works in the power save state. Comparators in the PSENSE pin and the RSENSE pin are stopped.

Clearing the PSV bit to "0" and the status is recovered from power save state to normal state. To set the comparators in the PSENSE pin and the RSENSE pin running, set these comparators to run after recovering from the power save state.

PDWN bit set the state transition to power down

| PDWN | Power down                   |  |  |  |  |

|------|------------------------------|--|--|--|--|

| 0    | Normal state (initial value) |  |  |  |  |

| 1    | Power down state             |  |  |  |  |

If the PDWN bit is set "1", 500k $\Omega$  pull-up resistor is automatically connected to PSENSE pin in the LSI and all the circuit is stopped, and the /RES pin output is "L".

Before setting the PDWN bit "1", C\_FET and D\_FET should be set OFF and charger disconnection should be confirmed with the PSENSE register. When the /PUPIN pin input is "L", even if PDOWN bit is set to "1", the state doesn't get changed to power-down until the /PUPIN pin input rises to "H". Before setting the PDWN bit "1", it should be confirmed that /PUPIN pin is not "L" by reading the PUPIN bit.

| PUPIN | /PUPIN pin state |

|-------|------------------|

| 0     | "H" level        |

| 1     | "L" level        |

If charger connection is detected with PSENSE pin or if /PUPIN pin is asserter "L" input, the LSI is recovered from power down state to normal state.

In the power down state, VREG output which is power supply for external micro-computer is set GND level. In recovering from power down state, every initial setting should be held after VREG is fully risen and after /RES pin output is fully changed from "L" level to "H" level.

8. STATUS register (Adrs = 07H)

|               | 7   | 6   | 5    | 4    | 3   | 2   | 1  | 0  |

|---------------|-----|-----|------|------|-----|-----|----|----|

| Bit name      | RSC | RRS | RPSH | RPSL | INT | PSV | CF | DF |

| R/W           | R   | R   | R    | R    | R   | R   | R  | R  |

| Initial value | 0   | 0   | 0    | 0    | 0   | 0   | 0  | 0  |

STATUS register indicates each status.

DF bit indicates the D\_FET pin output status.

| ſ | DF | D_FET pin status    |  |  |  |  |

|---|----|---------------------|--|--|--|--|

| Ī | 0  | OFF (initial value) |  |  |  |  |

| Ī | 1  | ON                  |  |  |  |  |

CF bit indicates the C\_FET pin output status.

| CF | C_FET pin status    |

|----|---------------------|

| 0  | OFF (initial value) |

| 1  | ON                  |

PSVbit indicates the power save state.

| PSV | Power save state             |  |  |  |  |

|-----|------------------------------|--|--|--|--|

| 0   | Normal state (initial value) |  |  |  |  |

| 1   | Power save state             |  |  |  |  |

INT bit indicates the /INTO pin output status.

| INT | /INTO pin output status      |

|-----|------------------------------|

| 0   | No interrupt (initial value) |

| 1   | Interrupted                  |

RPSL bit indicates interrupt status of charger disconnecting interrupt if charge over-current detected.

| RPSL | Status of charger disconnecting interrupt if charge over-current detected. |

|------|----------------------------------------------------------------------------|

| 0    | No interrupt (initial value)                                               |

| 1    | Charger disconnecting interrupt                                            |

RPSH bit indicates interrupt status of charger disconnecting interrupt if the status is power down.

| RPSH | Status of charger disconnecting interrupt if the status is power down |

|------|-----------------------------------------------------------------------|

| 0    | No interrupt (initial value)                                          |

| 1    | Charger disconnecting interrupt                                       |

RRS bit indicates interrupt status of load disconnecting interrupt

| RRS | Status of load disconnecting interrupt |

|-----|----------------------------------------|

| 0   | No interrupt (initial value)           |

| 1   | Load disconnecting interrupt           |

RSC bit indicates interrupt status of short current detecting interrupt.

|   | RSC | Status of short current detecting interrupt |

|---|-----|---------------------------------------------|

| ĺ | 0   | No interrupt (initial value)                |

|   | 1   | Short current detecting interrupt.          |

#### 9. CBALH register (Adrs = 08H)

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0   |

|---------------|------|------|------|------|------|------|------|-----|

| Bit name      | SW16 | SW15 | SW14 | SW13 | SW12 | SW11 | SW10 | SW9 |

| R/W           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   |

CBALH register set the cell balancing switches turning ON/OFF of upper 8 cells. SW16~SW9 bit sets switches turning ON/OFF of each cell.

| SW16 | SW15 | SW14 | SW13 | SW12 | SW11 | SW10 | SW9 | Switch ON/OFF                        |

|------|------|------|------|------|------|------|-----|--------------------------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | Upper 8 cells OFF<br>(initial value) |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1   | V9-V8 pin switch ON                  |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0   | V10-V9 pin switch ON                 |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0   | V11-V10 pin switch ON                |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0   | V12-V11 pin switch ON                |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0   | V13-V12 pin switch ON                |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0   | V14-V13 pin switch ON                |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0   | V15-V14 pin switch ON                |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | V16-V15 pin switch ON                |

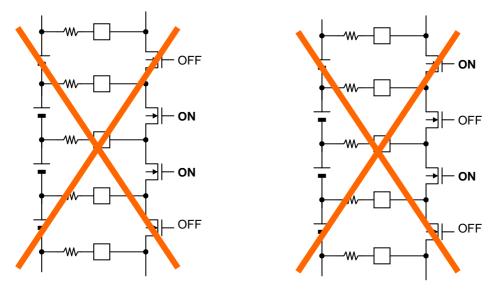

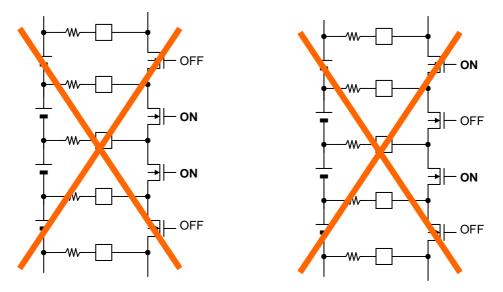

More than one switch can be turned on in the same time, but following settings are inhibited because internal cell balancing switch might be broken.

(1) Side-by-side cell balancing switches are inhibited to be turned on in the same time.

(2) the cell balancing switches of both side of a cell balancing switch which is turned off is inhibited to be turned on in the same time.

IC heats by cell balancing current and cell balancing switch resistor, restrict the number of switches of ON and time of ON, in order to keep the power consumption of cell balancing switch less than allowable power dissipation,

If cell voltage is outputted from VMON pin, the voltage of a cell whose cell balancing switch is turned on is measured as the voltage difference between two ports of cell balancing switch.

10. CBALL register (Adrs = 09H)

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit name      | SW8 | SW7 | SW6 | SW5 | SW4 | SW3 | SW2 | SW1 |

| R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

CBALL register set the cell balancing switches turning ON/OFF of lower 8 cells. SW8~SW1 bit sets switches turning ON/OFF of each cell.

| SW8 | SW7 | SW6 | SW5 | SW4 | SW3 | SW2 | SW1 | Switch ON/OFF                        |

|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | lower 8 cells OFF<br>(initial value) |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | V1-V0 pin switch ON                  |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | V2-V1 pin switch ON                  |

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | V3-V2 pin switch ON                  |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | V4-V3 pin switch ON                  |

| 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | V5-V4 pin switch ON                  |

| 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | V6-V5 pin switch ON                  |

| 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | V7-V6 pin switch ON                  |

| 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | V8-V7 pin switch ON                  |

More than one switch can be turned on in the same time, but following settings are inhibited because internal cell balancing switch might be broken.

(1) Side-by-side cell balancing switches are inhibited to be turned on in the same time.

(2) the cell balancing switches of both side of a cell balancing switch which is turned off is inhibited to be turned on in the same time.

IC heats by cell balancing current and cell balancing switch resistor, restrict the number of switches of ON and time of ON, in order to keep the power consumption of cell balancing switch less than allowable power dissipation,

If cell voltage is outputted from VMON pin, the voltage of a cell whose cell balancing switch is turned on is measured as the voltage difference between two ports of cell balancing switch.

11. SETSC register (Adrs = 0AH)

|               | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|---------------|---|---|---|---|---|---|-----|-----|

| Bit name      | — | - | - | - | - | _ | SC1 | SC0 |

| R/W           | R | R | R | R | R | R | R/W | R/W |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0   |

SETSC register sets the short current detecting voltage. Short current detecting voltage is selected with SC0 and SC1 bit depend on current sensing resistor value.

|   | SC1 | SC0 | Short current detecting voltage | Short current detecting current if Current sensing resistor value = $3m\Omega$ |  |  |

|---|-----|-----|---------------------------------|--------------------------------------------------------------------------------|--|--|

| Ī | 0   | 0   | 0.1V (initial value)            | 33.3A                                                                          |  |  |

| Ī | 0   | 1   | 0.2V                            | 66.6A                                                                          |  |  |

|   | 1   | 0   | 0.3V                            | 100A                                                                           |  |  |

|   | 1   | 1   | 0.4V                            | 133.3A                                                                         |  |  |

#### • CONNECTING POWER SUPPLY (VDDP, VDD, VDD\_SW)

VDDP pin is the power supply pin only for internal 3.3V regulator (VREG pin, VREF pin). If the output current of 3.3V regulator is large, it is recommended to make the voltage drop of RC filter resistor (for removing noise at the VDDP pin) smaller than 1V.

VDD\_SW pin is the power supply pin only for cell selection switches and cell balancing switches. Connect this pin to VDD via  $51\Omega$  resistor.

VDD pin is the power supply pin for all the circuit other than internal 3.3V regulator and cell selection switches and cell balancing switches.

#### • POWER-ON / POWER-OFF SEQUENCE

Recommended connecting order is; connect the GND first, after that connect the VDD, VDDP, VDD\_SW, and after that connect each cells from lower level. Power supply voltage rising time of power-on, power off order, power supply voltage falling time of power-off is not defined.

Following the power-on, the ML5238 normally enter into normal state. ML5238 may rarely enter into the Power down state by the chattering or another reason during the connection of the battery cells. In this case, input the voltage lower than or equal to the Detecting charger connection PSENSE pin voltage ( $V_{PC}$ ) to PSENSE pins, or input the "L" level to the /PUPIN pin, in order to power-up.

Else after the power-on or after the power-up, cell voltage measurement and current measurement should be done after the internal analog circuit is settled. To get the settling time of analog circuit, confirm the output settling time of VREF pin, VMON pin, and IMON pin in the application system.

#### If the number of connected cells is less than 16, connecting order in following table is recommended. Number of V15 to Connected V16 V10 V9 V8 V7 V6 V5 V4 V3 V2 V1 V0 cells 15 VDD\_SW cell 14 VDD\_SW cell GND cell cell cell cell cell cell cell cell cell 13 VDD SW GND GND cell cell cell cell cell cell cell cell cell 12 VDD\_SW cell cell cell cell cell cell GND GND GND cell cell 11 VDD\_SW cell cell cell cell cell cell cell GND GND GND GND 10 VDD\_SW cell cell cell cell cell cell GND GND GND GND GND 9 VDD\_SW cell cell cell GND GND GND GND GND GND cell cell 8 VDD\_SW cell cell cell cell GND GND GND GND GND GND GND 7 VDD\_SW cell cell cell GND GND GND GND GND GND GND GND GND cell cell 6 VDD\_SW GND GND GND GND GND GND GND GND 5 GND GND GND GND GND GND GND GND GND VDD\_SW cell GND

#### • CELL CONNECTING

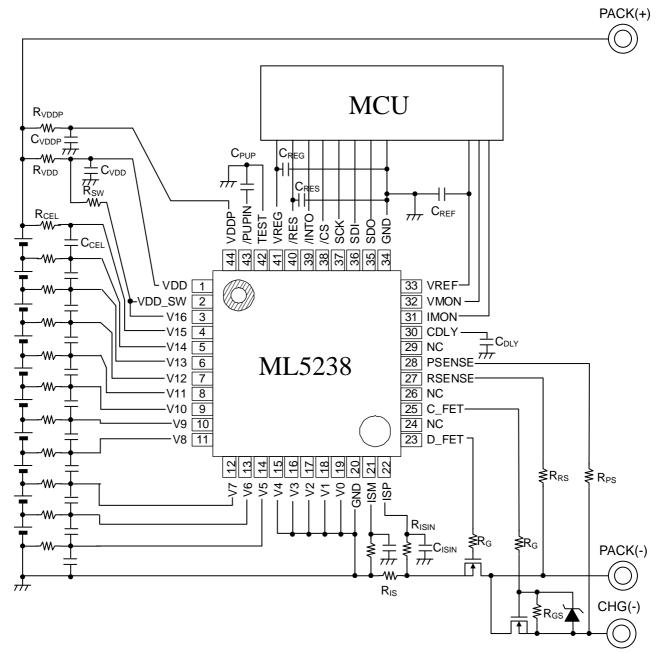

#### EXAMPLE OF APPLICATION CIRCUIT

(10 cells, charge/discharge path is isolated)

#### PARTS LIST

| Symbol            | Value         | Symbol                            | Value       |

|-------------------|---------------|-----------------------------------|-------------|

| R <sub>VDD</sub>  | 510Ω          | R <sub>ISIN</sub>                 | 1kΩ         |

| C <sub>VDD</sub>  | 10µF or more  | $C_{\text{ISIN}}, C_{\text{RES}}$ | 0.1µF       |

| R <sub>VDDP</sub> | 100Ω          | $C_{REG}, C_{REF}$                | 4.7μF       |

| C <sub>VDDP</sub> | 10µF or more  | C <sub>DLY</sub>                  | 1nF to 10nF |

| R <sub>SW</sub>   | 51Ω           | C <sub>PUP</sub>                  | 1μF         |

| R <sub>CEL</sub>  | 18Ω or more   | R <sub>G</sub>                    | 10kΩ        |

| C <sub>CEL</sub>  | 0.1µF or more | R <sub>GS</sub>                   | 1MΩ         |

| R <sub>IS</sub>   | 3mΩ           | R <sub>RS</sub>                   | 10kΩ        |

|                   |               | R <sub>PS</sub>                   | 1kΩ         |

|                   | ·             | R <sub>PS</sub>                   | 1kΩ         |

#### PACKAGE DIMENSIONS

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### **REVISION HISTORY**