# **ML610Q482P**

8-bit Microcontroller

#### GENERAL DESCRIPTION

This LSI is a high-performance 8-bit CMOS microcontroller into which rich peripheral circuits, such as synchronous serial port, UART, I<sup>2</sup>C bus interface (master), buzzer driver, battery level detect circuit, and RC oscillation type A/D converter, are incorporated around 8-bit CPU nX-U8/100.

The CPU nX-U8/100 is capable of efficient instruction execution in 1-intruction 1-clock mode by 3-stage pipe line architecture parallel processing. The Flash ROM that is installed as program memory achieves low-voltage low-power consumption operation (read operation) equivalent to mask ROM and is most suitable for battery-driven applications.

The on-chip debug function that is installed enables program debugging and programming.

#### **FEATURES**

- CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit

manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic

- shift, and so on

- On-Chip debug function

- Minimum instruction execution time

30.5 μs (@32.768 kHz system clock)

0.244μs (@4.096 MHz system clock)

- Internal memory

- Internal 64KByte Flash ROM (32K×16 bits) (including unusable 1KByte TEST area)

- Internal 4KByte Data RAM (4096×8 bits)

- Interrupt controller

- 2 non-maskable interrupt sources (Internal source: 1, External source: 1)

- 18 maskable interrupt sources (Internal sources: 14, External sources: 4)

- Time base counter

- Low-speed time base counter ×1 channel

- Frequency compensation (Compensation range: Approx. –488ppm to +488ppm. Compensation accuracy: Approx. 0.48ppm)

- High-speed time base counter ×1 channel

- · Watchdog timer

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s @32.768 kHz)

- Timers

- 8 bits × 4 channels (Timer0-3: 16-bit x 2 configuration available by using Timer0-1 or Timer2-3)

- Clock frequency measurement mode (in one channel of 16-bit configuration using Timer2-3)

#### PWM

- Resolution 16 bits × 1 channel

- Synchronous serial port

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- UART

- TXD/RXD × 1 channel

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

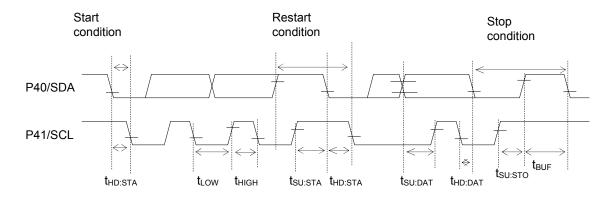

- I<sup>2</sup>C bus interface

- Master function only

- Fast mode (400 kbps@4MHz), standard mode (100 kbps@1MHz, 50kbps@500kHz)

- Buzzer driver

- 4 output modes, 8 frequencies, 16 duty levels

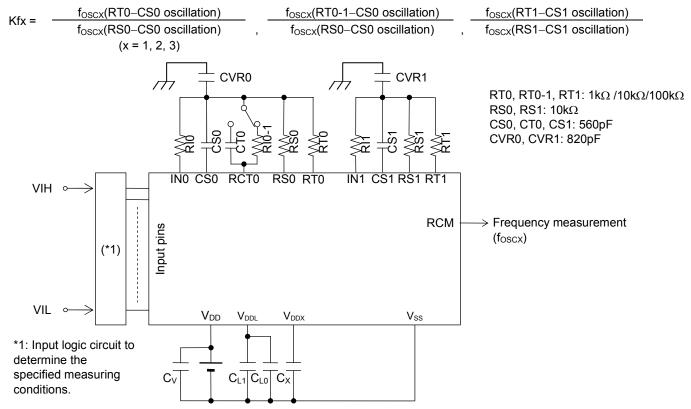

- RC oscillation type A/D converter

- 24-bit counter

- Time division × 2 channels

- Analog Comparator

$\begin{array}{ll} - \mbox{ Operating voltage: } & V_{DD} = 1.8 \mbox{V} \sim 3.6 \mbox{V} \\ - \mbox{ Common mode input voltage: } & 0.2 \mbox{V} \sim \mbox{VDD} - 1.0 \mbox{V} \\ - \mbox{ Input offset voltage: } & 50 \mbox{mV} \mbox{(max)} \end{array}$

- Interrupt allow edge selection and sampling selection

- General-purpose ports

- Non-maskable interrupt input port × 1 channel

- Input-only port × 6 channels (including secondary functions)

- Output-only port × 4 channels (including secondary functions)

- Input/output port × 22 channels (including secondary functions)

- Reset

- Reset through the RESET N pin

- Power-on reset generation when powered on

- Reset when oscillation stop of the low-speed clock is detected

- Reset by the watchdog timer (WDT) overflow

- Power supply voltage detect function

Judgment voltages: One of 16 levels

Judgment accuracy: ±2% (Typ.)

- Clock

- Low-speed clock: (This LSI can not guarantee the operation without low-speed clock)

Crystal oscillation (32.768 kHz/38.4KHz)

- High-speed clock:

Built-in RC oscillation (500 kHz)

Built-in PLL oscillation (8.192 MHz ±2.5%), crystal/ceramic oscillation (4.096 MHz), external clock

- Selection of high-speed clock mode by software:

Built-in RC oscillation, built-in PLL oscillation, crystal/ceramic oscillation, external clock

## • Power management

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or 1/8 of the oscillation clock)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

## • Shipment

- Chip

ML610Q482P-xxxWA (Blank product: ML610Q482P-NNNWA)

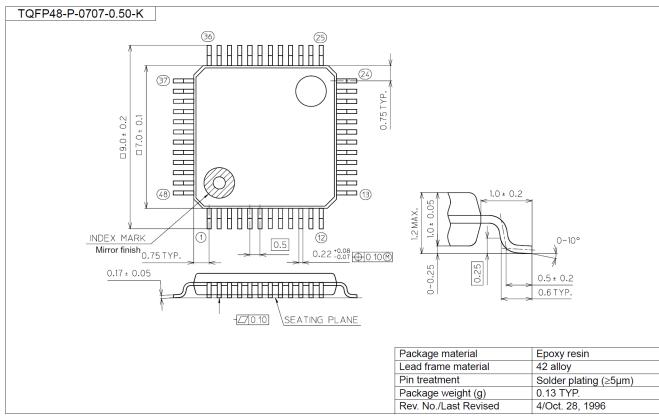

- 48-pin plastic TQFP

ML610Q482P-xxxTBZ03A (Blank product: ML610Q482P-NNNTBZ03A)

xxx: ROM code number

## • Guaranteed operating range

Operating temperature: −40°C to +85°C

- Operating voltage:  $V_{DD} = 1.1 \text{V}$  to 3.6V

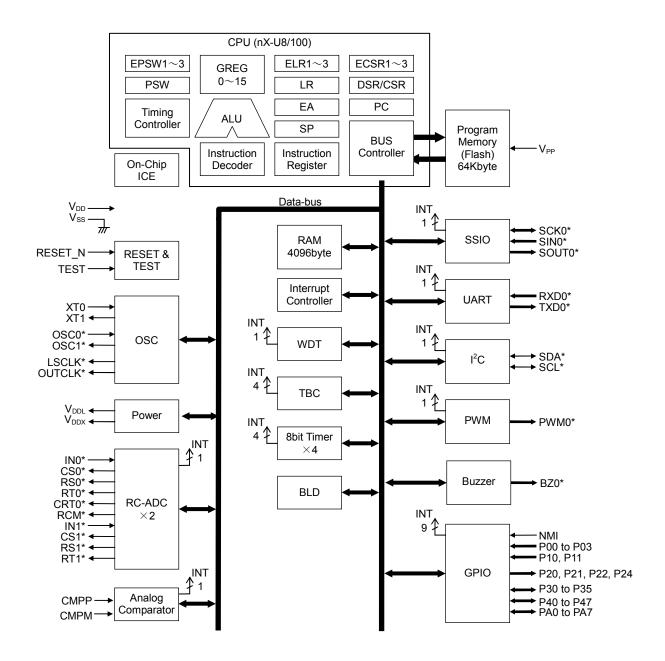

## BLOCK DIAGRAM ML610Q482P Block Diagram

Figure 1 show the block diagram of the ML610Q482P. "\*" indicates the secondary function of each port.

Figure 1 ML610Q482P Block Diagram

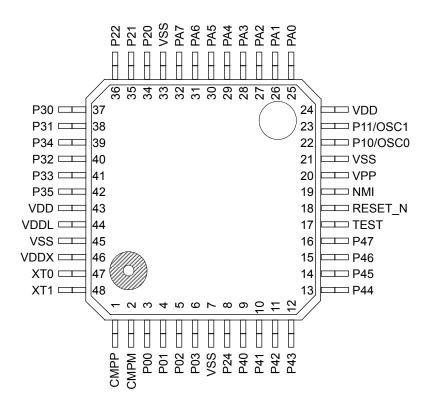

## PIN CONFIGURATION ML610Q482P TQFP48 Pin Layout

Note:

The assignment of the pads P30 to P35 are not in order.

Figure 2 ML610Q482P TQFP48 Pin Configuration

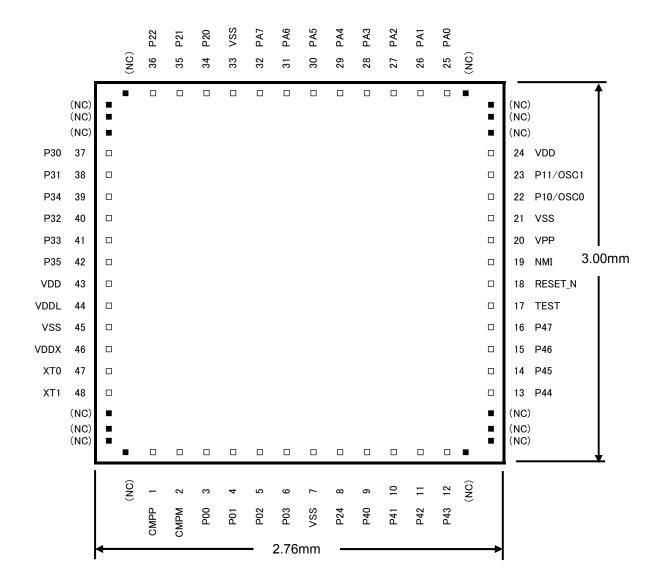

## ML610Q482P Chip Pin Layout & Dimension

(NC): No Connection

Note:

The assignment of the pads P30 to P35 are not in order.

Chip size:  $2.76 \text{ mm} \times 3.00 \text{ mm}$

PAD count: 48 pins Minimum PAD pitch:  $100 \mu m$  PAD aperture:  $80 \mu m \times 80 \mu m$  Chip thickness:  $350 \mu m$  Voltage of the rear side of chip:  $V_{SS}$  level

Figure 3 ML610Q482P Chip Layout & Dimension

## ML610Q482P Pad Coordinates

Table 1 ML610Q482P Pad Coordinates

|  | Chip | Center: | X=0, | Y=0 |

|--|------|---------|------|-----|

|--|------|---------|------|-----|

|     |         |         |         | Chip Center: X=0,Y=0 |     |      |         |         |  |

|-----|---------|---------|---------|----------------------|-----|------|---------|---------|--|

| PAD | Pad     | Х       | Υ       |                      | PAD | Pad  | Х       | Υ       |  |

| No. | Name    | (µm)    | (µm)    |                      | No. | Name | (µm)    | (µm)    |  |

| 1   | CMPP    | -1036.0 | -1380.0 | _                    | 25  | PA0  | 1023.0  | 1380.0  |  |

| 2   | CMPM    | -830.0  | -1380.0 | _                    | 26  | PA1  | 775.0   | 1380.0  |  |

| 3   | P00     | -730.0  | -1380.0 | _                    | 27  | PA2  | 651.0   | 1380.0  |  |

| 4   | P01     | -482.0  | -1380.0 | _                    | 28  | PA3  | 403.0   | 1380.0  |  |

| 5   | P02     | -382.0  | -1380.0 |                      | 29  | PA4  | 279.0   | 1380.0  |  |

| 6   | P03     | -134.0  | -1380.0 | _                    | 30  | PA5  | 31.0    | 1380.0  |  |

| 7   | VSS     | -34.0   | -1380.0 | _                    | 31  | PA6  | -93.0   | 1380.0  |  |

| 8   | P24     | 219.0   | -1380.0 | _                    | 32  | PA7  | -341.0  | 1380.0  |  |

| 9   | P40     | 327.0   | -1380.0 | _                    | 33  | VSS  | -458.0  | 1380.0  |  |

| 10  | P41     | 655.0   | -1380.0 | _                    | 34  | P20  | -666.0  | 1380.0  |  |

| 11  | P42     | 775.0   | -1380.0 | _                    | 35  | P21  | -766.0  | 1380.0  |  |

| 12  | P43     | 1023.0  | -1380.0 | _                    | 36  | P22  | -1032.0 | 1380.0  |  |

| 13  | P44     | 1260.0  | -912.0  | _                    | 37  | P30  | -1260.0 | 922.0   |  |

| 14  | P45     | 1260.0  | -778.0  | _                    | 38  | P31  | -1260.0 | 769.0   |  |

| 15  | P46     | 1260.0  | -530.0  | _                    | 39  | P34  | -1260.0 | 521.0   |  |

| 16  | P47     | 1260.0  | -426.0  |                      | 40  | P32  | -1260.0 | 417.0   |  |

| 17  | TEST    | 1260.0  | -167.0  | _                    | 41  | P33  | -1260.0 | 169.0   |  |

| 18  | RESET_N | 1260.0  | -67.0   | _                    | 42  | P35  | -1260.0 | 67.0    |  |

| 19  | NMI     | 1260.0  | 181.0   | _                    | 43  | VDD  | -1260.0 | -122.0  |  |

| 20  | VPP     | 1260.0  | 281.0   | _                    | 44  | VDDL | -1260.0 | -333.0  |  |

| 21  | VSS     | 1260.0  | 411.0   | _                    | 45  | VSS  | -1260.0 | -503.0  |  |

| 22  | P10     | 1261.3  | 610.0   | _                    | 46  | VDDX | -1260.0 | -673.0  |  |

| 23  | P11     | 1261.3  | 858.0   | _                    | 47  | XT0  | -1260.0 | -773.0  |  |

| 24  | VDD     | 1260.0  | 1010.0  | _                    | 48  | XT1  | -1260.0 | -1021.0 |  |

## PIN LIST

| PAD            | I                 | Prima | ary function                                                      | S        | Secon | dary function                                                  |          | Terti | ary function |

|----------------|-------------------|-------|-------------------------------------------------------------------|----------|-------|----------------------------------------------------------------|----------|-------|--------------|

| No.            | Pin name          | I/O   | Function                                                          | Pin name | I/O   | Function                                                       | Pin name | I/O   | Function     |

| 7,21,<br>33,45 | Vss               | _     | Negative power supply pin                                         |          | _     | _                                                              |          | _     | _            |

| 24,43          | $V_{DD}$          | _     | Positive power supply pin                                         | _        |       | _                                                              | _        | _     | _            |

| 44             | $V_{DDL}$         | _     | Power supply pin for internal logic (internally generated)        | _        | _     | _                                                              | _        | _     | _            |

| 46             | $V_{DDX}$         | _     | Power supply pin for low-speed oscillation (internally generated) | _        | _     | _                                                              | _        | _     | _            |

| 20             | $V_{PP}$          | —     | Power supply pin for Flash ROM                                    | _        |       | _                                                              | _        | _     | _            |

| 17             | TEST              | I/O   | Input/output pin for testing                                      | _        |       | _                                                              | _        | —     | _            |

| 18             | RESET_<br>N       | I     | Reset input pin                                                   |          | _     | _                                                              |          | _     | _            |

| 47             | XT0               | ı     | Low-speed clock oscillation pin                                   | _        | _     | _                                                              | _        | _     | _            |

| 48             | XT1               | 0     | Low-speed clock oscillation pin                                   |          | _     | _                                                              | _        | _     | _            |

| 19             | NMI               | I     | Non-maskable interrupt pin                                        | _        | _     | _                                                              | _        | _     | _            |

| 3              | P00/EXI<br>0      | I     | Input port, External interrupt 0, Capture 0 input                 | _        | _     | _                                                              | _        | _     | _            |

| 4              | P01/EXI<br>1      | I     | Input port, External interrupt 1, Capture 1 input                 | _        | _     | _                                                              | _        | _     | _            |

| 5              | P02/EXI<br>2/RXD0 | I     | Input port, External interrupt 2, UART0 receive                   | _        | _     | _                                                              | _        | _     | _            |

| 6              | P03/EXI           | ı     | Input port, External interrupt 3                                  | _        | _     | _                                                              | _        | _     | _            |

| 1              | CMPP              | I     | Analog comparator non-inverted input                              | _        | _     | _                                                              | _        | _     | _            |

| 2              | СМРМ              | I     | Analog comparator inverted input                                  | _        | _     | _                                                              | _        | _     | _            |

| 22             | P10               | I     | Input port                                                        | OSC0     | I     | High-speed oscillation                                         | _        |       | _            |

| 23             | P11<br>P20/LE     | 1     | Input port                                                        | OSC1     | 0     | High-speed oscillation                                         | _        | _     | <del></del>  |

| 34             | D0<br>P21LED      | 0     | Output port                                                       | LSCLK    | 0     | Low-speed clock output High-speed clock                        | _        | _     | _            |

| 35             | 1                 | 0     | Output port                                                       | OUTCLK   | 0     | output                                                         | _        | _     | _            |

| 36             | P22/LE<br>D2      | 0     | Output port                                                       | BZ0      | 0     | BZ0 output                                                     | _        | _     | _            |

| 8              | P24/LE<br>D4      | 0     | Output port                                                       | PWM0     | 0     | PWM0 output                                                    | _        | _     | _            |

| 37             | P30               | I/O   | Input/output port                                                 | IN0      | I     | RC type ADC0 oscillation input pin                             |          | _     | _            |

| 38             | P31               | I/O   | Input/output port                                                 | CS0      | 0     | RC type ADC0 reference capacitor connection pin                | _        | _     | _            |

| 40             | P32               | I/O   | Input/output port                                                 | RS0      | 0     | RC type ADC0<br>reference resistor<br>connection pin           | _        | _     | _            |

| 41             | P33               | I/O   | Input/output port                                                 | RT0      | 0     | RC type ADC0 resistor<br>sensor connection pin<br>RC type ADC0 | _        | _     | _            |

| 39             | P34               | I/O   | Input/output port                                                 | RCT0     | 0     | resistor/capacitor<br>sensor connection pin                    | PWM0     | 0     | PWM0 output  |

| PAD | ı               | Prima | ary function                                                          | S        | Secondary function |                                                      | Tertiary function |     |                         |

|-----|-----------------|-------|-----------------------------------------------------------------------|----------|--------------------|------------------------------------------------------|-------------------|-----|-------------------------|

| No. | Pin name        | I/O   | Function                                                              | Pin name | I/O                | Function                                             | Pin name          | I/O | Function                |

| 42  | P35             | I/O   | Input/output port                                                     | RCM      | 0                  | RC type ADC oscillation monitor                      |                   |     | _                       |

| 9   | P40             | I/O   | Input/output port                                                     | SDA      | I/O                | I <sup>2</sup> C data input/output                   | SIN0              | _   | SSIO data input         |

| 10  | P41             | I/O   | Input/output port                                                     | SCL      | I/O                | I <sup>2</sup> C clock input/output                  | SCK0              | I/O | SSIO synchronous clock  |

| 11  | P42             | I/O   | Input/output port                                                     | RXD0     | ı                  | UART data input                                      | SOUT0             | 1   | SSIO data output        |

| 12  | P43             | I/O   | Input/output port                                                     | TXD0     | 0                  | UART data output                                     | PWM0              | 0   | PWM output              |

| 13  | P44/T02<br>P0CK | I/O   | Input/output port,<br>Timer 0/Timer<br>2/PWM0 external<br>clock input | IN1      | I                  | RC type ADC1 oscillation input pin                   | SIN0              | I   | SSIO0 data input        |

| 14  | P45/T13<br>P1CK | I/O   | Input/output port,<br>Timer 1/Timer 3<br>external clock input         | CS1      | О                  | RC type ADC1 reference capacitor connection pin      | SCK0              | I/O | SSIO0 synchronous clock |

| 15  | P46             | I/O   | Input/output port                                                     | RS1      | 0                  | RC type ADC1<br>reference resistor<br>connection pin | SOUT0             | 0   | SSIO0 data output       |

| 16  | P47             | I/O   | Input/output port                                                     | RT1      | О                  | RC type ADC1 resistor sensor connection pin          | _                 | -   | _                       |

| 25  | PA0             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 | _   | _                       |

| 26  | PA1             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 |     | _                       |

| 27  | PA2             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 | _   | _                       |

| 28  | PA3             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 | _   | _                       |

| 29  | PA4             | I/O   | Input/output port                                                     | _        | _                  | _                                                    |                   | _   |                         |

| 30  | PA5             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 | _   | _                       |

| 31  | PA6             | I/O   | Input/output port                                                     | _        | _                  | _                                                    | _                 | _   | _                       |

| 32  | PA7             | I/O   | Input/output port                                                     | _        | _                  | _                                                    |                   |     | _                       |

## PIN DESCRIPTION

| Pin name            | I/O    | Description                                                                                                                                                                                                                                        | Primary/<br>Secondary/<br>Tertiary | Logic    |

|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|

| System              |        |                                                                                                                                                                                                                                                    |                                    |          |

| RESET_N             | I      | Reset input pin. When this pin is set to a "L" level, system reset mode is set and the internal section is initialized. When this pin is set to a "H" level subsequently, program execution starts. A pull-up resistor is internally connected.    | _                                  | Negative |

| XT0                 | ı      | Crystal connection pin for low-speed clock.                                                                                                                                                                                                        | _                                  |          |

| XT1                 | 0      | A 32.768 kHz crystal oscillator (see measuring circuit 1) is connected to this pin. Capacitors CDL and CGL are connected across this pin and $V_{\rm SS}$ as required.                                                                             | _                                  |          |

| OSC0                | ı      | Crystal/ceramic connection pin for high-speed clock.                                                                                                                                                                                               | Secondary                          | 1        |

| OSC1                | 0      | A crystal or ceramic is connected to this pin (4.1 MHz max.). Capacitors CDH and CGH (see measuring circuit 1) are connected across this pin and $V_{\rm SS}$ . This pin is used as the secondary function of the P10 pin(OSC0) and P11 pin(OSC1). | Secondary                          | _        |

| LSCLK               | 0      | Low-speed clock output pin. This pin is used as the secondary function of the P20 pin.                                                                                                                                                             | Secondary                          |          |

| OUTCLK              | 0      | High-speed clock output pin. This pin is used as the secondary function of the P21 pin.                                                                                                                                                            | Secondary                          |          |

| General-purp        | ose in | put port                                                                                                                                                                                                                                           |                                    |          |

| P00-P03             | I      | General-purpose input port.  Since these pins have secondary functions, the pins cannot be used as a port when the secondary functions are used.                                                                                                   | Primary                            | Positive |

| P10,P11             | I      | General-purpose input port. Since these pins have secondary functions, the pins cannot be used as a port when the secondary functions are used.                                                                                                    | Primary                            | Positive |

| General-purp        | ose ou |                                                                                                                                                                                                                                                    |                                    |          |

| P20,P21,<br>P22,P24 | 0      | General-purpose output port. Since these pins have secondary functions, the pins cannot be used as a port when the secondary functions are used.                                                                                                   | Primary                            | Positive |

| General-purp        | ose in | put/output port                                                                                                                                                                                                                                    |                                    |          |

| P30-P35             | I/O    | General-purpose input/output port. Since these pins have secondary functions, the pins cannot be used as a port when the secondary functions are used.                                                                                             | Primary                            | Positive |

| P40-P47             | I/O    | General-purpose input/output port. Since these pins have secondary functions, the pins cannot be used as a port when the secondary functions are used.                                                                                             | Primary                            | Positive |

| PA0-PA7             | I/O    | General-purpose input/output port.                                                                                                                                                                                                                 | Primary                            | Positive |

|                              | 1        |                                                                                                                                                    | Drime o m / |            |

|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|

| D                            |          | D toff                                                                                                                                             | Primary/    |            |

| Pin name                     | I/O      | Description                                                                                                                                        | Secondary/  | Logic      |

|                              |          |                                                                                                                                                    | Tertiary    |            |

| UART                         | 1        |                                                                                                                                                    | 1           |            |

| TXD0                         | 0        | UART data output pin. This pin is used as the secondary function of the P43 pin.                                                                   | Secondary   | Positive   |

| RXD0                         | ı        | UART data input pin. This pin is used as the secondary function of the                                                                             | Primary/Se  | Positive   |

|                              |          | P42 or the primary function of the P02 pin.                                                                                                        | condary     |            |

| I <sup>2</sup> C bus interfa | ace      |                                                                                                                                                    |             |            |

| SDA                          | 1/0      | I <sup>2</sup> C data input/output pin. This pin is used as the secondary function of the                                                          | Secondary   | Positive   |

|                              |          | P40 pin. This pin has an NMOS open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor. |             |            |

| SCL                          | 0        | I <sup>2</sup> C clock output pin. This pin is used as the secondary function of the P41                                                           | Secondary   | Positive   |

| SCL                          |          | pin. This pin has an NMOS open drain output. When using this pin as a                                                                              | Secondary   | FUSITIVE   |

|                              |          | function of the I <sup>2</sup> C, externally connect a pull-up resistor.                                                                           |             |            |

| Synchronous                  | serial   |                                                                                                                                                    |             |            |

|                              | Scriai   |                                                                                                                                                    | 1           |            |

| SCK0                         | I/O      | Synchronous serial clock input/output pin. This pin is used as the tertiary function of the P41 or P45 pin.                                        | Tertiary    | _          |

| SIN0                         | ı        | Synchronous serial data input pin. This pin is used as the tertiary function                                                                       | Tertiary    | Positive   |

|                              |          | of the P40 or P44 pin.                                                                                                                             | -           |            |

| SOUT0                        | 0        | Synchronous serial data output pin. This pin is used as the tertiary                                                                               | Tertiary    | Positive   |

|                              |          | function of the P42 or P46 pin.                                                                                                                    |             |            |

| PWM                          |          |                                                                                                                                                    |             |            |

| PWM0                         | 0        | PWM0 output pin. This pin is used as the tertiary function of the P24 or P43 or P34 pin.                                                           | Tertiary    | Positive   |

| T02P0CK                      | 0        | PWM0 external clock input pin. This pin is used as the primary function of                                                                         | Primary     |            |

| 1021 0010                    |          | the P44 pin.                                                                                                                                       | 1 minary    |            |

| External inter               | runt     |                                                                                                                                                    | l .         |            |

| NMI                          | ı        | External non-maskable interrupt input pin. An interrupt is generated on                                                                            | Primary     | Positive/  |

| INIVII                       |          | both edges.                                                                                                                                        | Filliary    | negative   |

| EXI0-3                       | 1        | External maskable interrupt input pins. Interrupt enable and edge                                                                                  | Primary     | Positive/  |

| EX10-3                       |          | selection can be performed for each bit by software. These pins are used                                                                           | Filliary    | negative   |

|                              |          | as the primary functions of the P00-P03 pins.                                                                                                      |             | negative   |

| Timer                        |          | at the primary randitions of the Foot Foot pine.                                                                                                   |             |            |

|                              |          | External clock input pin used for both Timer 0 and Timer 2. The clocks for                                                                         | Drimon      |            |

| T02P0CK                      | 1        | these timers are selected by software. This pin is used as the primary                                                                             | Primary     |            |

|                              |          | function of the P44 pin.                                                                                                                           |             |            |

| T13P1CK                      | -        | External clock input pin used for both Timer 1 and Timer 3. The clocks for                                                                         | Drimon      |            |

| TISPICK                      | I        | these timers are selected by software. This pin is used as the primary                                                                             | Primary     |            |

|                              |          | function of the P45 pin.                                                                                                                           |             | _          |

| Du                           |          | Tuniouon or the F to pin.                                                                                                                          | 1           |            |

| Buzzer                       |          |                                                                                                                                                    |             |            |

| BZ0                          | 0        | Buzzer signal output pin. This pin is used as the secondary function of the                                                                        | Secondary   | Positive/  |

|                              |          | P22 pin.                                                                                                                                           | Jeeniaary   | negative   |

| LED drive                    |          | <u> </u>                                                                                                                                           | I           | . logalive |

|                              |          | NIMOS apan drain autout ping to drive LED. Those ping are used as the                                                                              | Deine       | Positive/  |

| LED0,1,2,4                   | 0        | NMOS open drain output pins to drive LED. These pins are used as the primary function of the P20,P21,P22,P24 pins.                                 | Primary     | negative   |

|                              | <u> </u> | primary runouon or the F20,F21,F22,F24 pins.                                                                                                       | j           | negative   |

| Pin name         |        |                                                                                                                                                                         |           |   |  |  |  |

|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|--|--|--|

| RC oscillation   | type   | A/D converter                                                                                                                                                           |           |   |  |  |  |

| IN0              | I      | Channel 0 oscillation input pin. This pin is used as the secondary function of the P30 pin.                                                                             | Secondary | _ |  |  |  |

| CS0              | 0      | Channel 0 reference capacitor connection pin. This pin is used as the secondary function of the P31 pin.                                                                | Secondary | _ |  |  |  |

| RS0              | 0      | This pin is used as the secondary function of the P32 pin which is the reference resistor connection pin of Channel 0.                                                  | Secondary | _ |  |  |  |

| RT0              | 0      | Resistor sensor connection pin of Channel 0 for measurement. This pin is used as the secondary function of the P34 pin.                                                 | Secondary | _ |  |  |  |

| CRT0             | 0      | Resistor/capacitor sensor connection pin of Channel 0 for measurement.  This pin is used as the secondary function of the P33 pin.                                      | Secondary | _ |  |  |  |

| RCM              | 0      | RC oscillation monitor pin. This pin is used as the secondary function of the P35 pin.                                                                                  | Secondary | _ |  |  |  |

| IN1              | I      | Oscillation input pin of Channel 1. This pin is used as the secondary function of the P44 pin.                                                                          | Secondary | _ |  |  |  |

| CS1              | 0      | Reference capacitor connection pin of Channel 1. This pin is used as the secondary function of the P45 pin.                                                             | Secondary | _ |  |  |  |

| RS1              | 0      | Reference resistor connection pin of Channel 1. This pin is used as the secondary function of the P46 pin.                                                              | Secondary | _ |  |  |  |

| RT1              | 0      | Resistor sensor connection pin for measurement of Channel 1. This pin is used as the secondary function of the P47 pin.                                                 | Secondary | _ |  |  |  |

| Analog compa     | arator |                                                                                                                                                                         |           |   |  |  |  |

| CMPP             | I      | Non-inverted input pin.                                                                                                                                                 | _         | _ |  |  |  |

| CMPM             | I      | Inverted input pin.                                                                                                                                                     | _         | _ |  |  |  |

| For testing      |        |                                                                                                                                                                         |           |   |  |  |  |

| TEST             | I/O    | Input/output pin for testing. A pull-down resistor is internally connected.                                                                                             | _         | _ |  |  |  |

| Power supply     | ,      |                                                                                                                                                                         |           |   |  |  |  |

| V <sub>SS</sub>  | _      | Negative power supply pin.                                                                                                                                              | _         | _ |  |  |  |

| $V_{DD}$         | _      | Positive power supply pin.                                                                                                                                              | _         | _ |  |  |  |

| V <sub>DDL</sub> | _      | Positive power supply pin (internally generated) for internal logic. Capacitors CL0 and CL1 (see measuring circuit 1) are connected between this pin and $V_{\rm SS}$ . | _         |   |  |  |  |

| V <sub>DDX</sub> |        | Plus-side power supply pin (internally generated) for low-speed oscillation. Capacitor Cx (see measuring circuit 1) is connected between this pin and $V_{\rm SS}$ .    | _         | _ |  |  |  |

| V <sub>PP</sub>  | _      | Power supply pin for programming Flash ROM. A pull-up resistor is internally connected.                                                                                 | _         | _ |  |  |  |

## TERMINATION OF UNUSED PINS

Table 2 shows methods of terminating the unused pins.

Table 2 Termination of Unused Pins

| Pin                | Recommended pin termination        |

|--------------------|------------------------------------|

| V <sub>PP</sub>    | Open                               |

| RESET_N            | Open                               |

| TEST               | Open                               |

| NMI                | Open                               |

| P00 to P03         | V <sub>DD</sub> or V <sub>SS</sub> |

| P10, P11           | $V_{DD}$                           |

| P20, P21, P22, P24 | Open                               |

| P30 to P35         | Open                               |

| P40 to P47         | Open                               |

| PA0 to PA7         | Open                               |

| CMPP,CMPM          | $V_{DD}$                           |

#### Note:

It is recommended to set the unused input ports and input/output ports to the inputs with pull-down resistors/pull-up resistors or the output mode since the supply current may become excessively large if the pins are left open in the high impedance input setting.

## **ELECTRICAL CHARACTERISTICS**

## **ABSOLUTE MAXIMUM RATINGS**

$(V_{SS} = 0V)$

| Parameter              | Symbol            | Condition          | Rating                       | Unit |

|------------------------|-------------------|--------------------|------------------------------|------|

| Power supply voltage 1 | $V_{DD}$          | Ta = 25°C          | -0.3 to +4.6                 | V    |

| Power supply voltage 2 | $V_{PP}$          | Ta = 25°C          | -0.3 to +9.5                 | V    |

| Power supply voltage 3 | $V_{DDL}$         | Ta = 25°C          | -0.3 to +3.6                 | V    |

| Power supply voltage 4 | $V_{DDX}$         | Ta = 25°C          | -0.3 to +3.6                 | V    |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current 1       | I <sub>OUT1</sub> | Port3–A, Ta = 25°C | -12 to +11                   | mA   |

| Output current 2       | I <sub>OUT2</sub> | Port2, Ta = 25°C   | -12 to +20                   | mA   |

| Power dissipation      | PD                | Ta = 25°C          | 1.16                         | W    |

| Storage temperature    | T <sub>STG</sub>  | <u> </u>           | -55 to +150                  | °C   |

## RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V)$

|                                                        |                  |                                         |               | , ,, |

|--------------------------------------------------------|------------------|-----------------------------------------|---------------|------|

| Parameter                                              | Symbol           | Condition                               | Range         | Unit |

| Operating temperature                                  | T <sub>OP</sub>  | _                                       | -40 to +85    | °C   |

| Operating voltage                                      | $V_{DD}$         | _                                       | 1.1 to 3.6    | V    |

|                                                        |                  | V <sub>DD</sub> = 1.1 to 3.6V           | 30k to 36k    |      |

| Operating frequency (CPU)                              | f <sub>OP</sub>  | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$ | 30k to 650k   | Hz   |

|                                                        |                  | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$ | 30k to 4.2M   |      |

| Low-speed crystal oscillation frequency                | f <sub>XTL</sub> | _                                       | 32.768k/38.4k | Hz   |

| Low-speed crystal oscillation                          | $C_DL$           | _                                       | 0 to 12       |      |

| external capacitor                                     | $C_GL$           | _                                       | 0 to 12       | pF   |

| High-speed crystal/ceramic oscillation frequency       | f <sub>XTH</sub> | _                                       | 4.0M / 4.096M | Hz   |

| High-speed crystal oscillation                         | C <sub>DH</sub>  | _                                       | 24            | 25   |

| external capacitor                                     | C <sub>GH</sub>  | _                                       | 24            | pF   |

| Capacitor externally connected to                      | C <sub>L0</sub>  | _                                       | 1.0±30%       |      |

| V <sub>DDL</sub> pin                                   | C <sub>L1</sub>  | _                                       | 0.1±30%       | μF   |

| Capacitor externally connected to V <sub>DDX</sub> pin | C <sub>X</sub>   | _                                       | 0.1±30%       | μF   |

## **OPERATING CONDITIONS OF FLASH ROM**

$(V_{SS} = 0V)$

|                       |                 |                  |             | ( - 00 ) |

|-----------------------|-----------------|------------------|-------------|----------|

| Parameter             | Symbol          | Condition        | Range       | Unit     |

| Operating temperature | T <sub>OP</sub> | At write/erase   | 0 to +40    | °C       |

|                       | $V_{DD}$        | At write/erase*1 | 2.75 to 3.6 |          |

| Operating voltage     | $V_{DDL}$       | At write/erase*1 | 2.5 to 2.75 | V        |

|                       | V <sub>PP</sub> | At write/erase*1 | 7.7 to 8.3  |          |

| Write cycles          | C <sub>EP</sub> | <del>_</del>     | 10          | cycles   |

| Data retention        | Y <sub>DR</sub> | _                | 10          | years    |

Those voltages must be supplied to  $V_{DDL}$  pin and  $V_{PP}$  pin when programming and eraseing Flash ROM.  $V_{PP}$  pin has an internal pulldown resister.

## CONDITIONS OF ANALOG COMPARATOR

$(V_{DD}$  = 1.1 to 3.6V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise specified) (2/4)

| Parameter                          | Symbol Condition  |                                         |      | Rating | Unit       | Measuring |         |

|------------------------------------|-------------------|-----------------------------------------|------|--------|------------|-----------|---------|

| Parameter                          |                   |                                         | Min. | Тур.   | Max.       | Unit      | circuit |

| Common mode Input voltage          | CMV <sub>IN</sub> | $V_{DD}$ = 1.8 to 3.6V                  | 0.2  | _      | $V_{DD}-1$ | V         |         |

| Input offset voltage               | $V_{CMPOF}$       | $V_{DD}$ = 1.8 to 3.6V, Ta = 25°C       |      |        | 50         | mV        |         |

| Response time                      | T <sub>CMP</sub>  | $V_{DD}$ = 1.8 to 3.6V, Ta = 25°C       | _    | _      | 100        | μs        | 1       |

| Wake-up time                       | T <sub>CMPw</sub> | Over drive = 100mV                      |      | _      | 3          | ms        |         |

| Circuit current (during operation) | I <sub>CMP</sub>  | V <sub>DD</sub> = 1.8 to 3.6V,Ta = 25°C |      | 2      | 4          | μА        |         |

## DC CHARACTERISTICS (1/4)

( $V_{DD}$  = 1.1 to 3.6V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise specified) (1/4)

| $(V_{DD} = 1.1 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V},$ |                   |                       | 1a = -40                    | 10 +85°C,    | ierwise s | pecified) (1/4) |       |           |

|----------------------------------------------------------------|-------------------|-----------------------|-----------------------------|--------------|-----------|-----------------|-------|-----------|

| Darameter                                                      | Symbol            |                       | Condition                   |              | Rating    |                 | Unit  | Measuring |

| Parameter                                                      | Symbol            |                       | Ondition                    | Min.         | Тур.      | Max.            | Offic | circuit   |

| 500kHz RC oscillation                                          | f <sub>RC</sub>   | V <sub>DD</sub> = 1.3 | Ta = 25°C                   | Typ.<br>-10% | 500       | Typ.<br>+10%    | kHz   |           |

| frequency                                                      | IRC               | to 3.6V               | Ta = −40 to<br>+85°C        | Typ.<br>-35% | 500       | Typ.<br>+35%    | kHz   |           |

| PLL oscillation frequency*4                                    | f <sub>PLL</sub>  |                       | K = 32.768kHz = 1.8 to 3.6V | -2.5%        | 8.192     | +2.5%           | MHz   |           |

| Low-speed crystal oscillation start time*2                     | T <sub>XTL</sub>  |                       | _                           | _            | 0.3       | 2               | s     |           |

| 500kHz RC oscillation start time                               | T <sub>RC</sub>   | _                     |                             | _            | 50        | 500             | μS    | 1         |

| High-speed crystal oscillation start time*3                    | T <sub>XTH</sub>  | V <sub>DD</sub> =     | = 1.8 to 3.6V               | _            | 2         | 20              |       | •         |

| PLL oscillation start time                                     | T <sub>PLL</sub>  | V <sub>DD</sub> =     | = 1.8 to 3.6V               | _            | 1         | 10              | ms    |           |

| Low-speed oscillation stop detect time <sup>*1</sup>           | T <sub>STOP</sub> |                       | _                           |              | 3         | 20              |       |           |

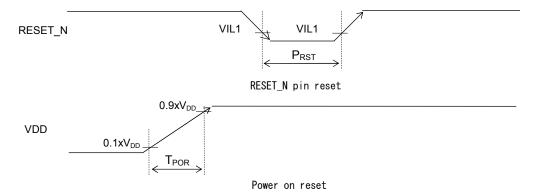

| Reset pulse width                                              | P <sub>RST</sub>  |                       | _                           |              |           | _               |       |           |

| Reset noise elimination pulse width                            | P <sub>NRST</sub> |                       | _                           |              |           | 0.3             | μS    |           |

| Power-on reset activation power rise time                      | T <sub>POR</sub>  |                       | _                           |              | _         | 10              | ms    |           |

<sup>\*1:</sup> When low-speed crystal oscillation stops for a duration more than the low-speed oscillation stop detect time, the system is reset to shift to system reset mode.

## RESET

$<sup>^{\</sup>star 2}$ : Use 32.768KHz Crystal Oscillator C-001R (Epson Toyocom) with capacitance C<sub>GL</sub>/C<sub>DL</sub>=0pF.

<sup>\*3 :</sup> Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

<sup>\*4: 1024</sup> clock average.

## DC CHARACTERISTICS (2/4)

$(V_{DD} = 1.1 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$  (2/4)

|                                             |                  |                                                              | to 3.6V, $V_{SS} = 0V$ , | 1a40 t | Rating | uniess ou |           | Measuring |

|---------------------------------------------|------------------|--------------------------------------------------------------|--------------------------|--------|--------|-----------|-----------|-----------|

| Parameter                                   | Symbol           | Condition                                                    | on                       | Min.   | Typ.   | Max.      | Unit      | circuit   |

|                                             |                  |                                                              | LD2-0 = 0H               |        | 1.35   |           |           |           |

|                                             |                  |                                                              | LD2-0 = 1H               |        | 1.4    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 2H               |        | 1.45   |           |           |           |

|                                             |                  |                                                              | LD2-0 = 3H               |        | 1.5    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 4H               |        | 1.6    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 5H               |        | 1.7    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 6H               |        | 1.8    |           |           |           |

| BLD threshold                               | $V_{BLD}$        | V <sub>DD</sub> = 1.35 to 3.6V                               | LD2-0 = 7H               | Тур.   | 1.9    | Тур.      | V         |           |

| voltage                                     | A BLD            | V UU - 1.33 to 3.0 V                                         | LD2-0 = 8H               | -2%    | 2.0    | +2%       | •         |           |

|                                             |                  |                                                              | LD2-0 = 9H               |        | 2.1    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0AH              |        | 2.2    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0BH              |        | 2.3    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0CH              |        | 2.4    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0DH              |        | 2.5    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0EH              |        | 2.7    |           |           |           |

|                                             |                  |                                                              | LD2-0 = 0FH              |        | 2.9    |           |           |           |

| BLD threshold voltage temperature deviation | $\Delta V_{BLD}$ | V <sub>DD</sub> = 1.35 to                                    | o 3.6V                   | _      | 0      | _         | %/°C      |           |

| Supply current 1                            | IDD1             | CPU: In STOP state.<br>Low-speed/high-speed                  | Ta=25°C                  | _      | 0.2    | 0.5       | 0.5<br>μA | 1         |

| Опррту ситет т                              | 1001             | oscillation: stopped.                                        | Ta=-40 to + 85°C         | _      | _      | 5         | μΑ        |           |

| Supply ourrent 2                            | IDD2             | CPU: In HALT state (LTBC,WDT:Operating*3                     | Ta=25℃                   | _      | 0.5    | 1.3       |           |           |

| Supply current 2                            | IDD2             | ).High-speed oscillation:<br>Stopped.                        | Ta=-40 to + 85℃          | _      | _      | 6         | μА        |           |

| Supply current 3                            | IDD3             | CPU: In 32.768kHz operating state.*1                         | Ta=25℃                   | _      | 5      | 7         | <b>^</b>  |           |

| Supply current 3                            | נטטו             | High-speed oscillation: Stopped.                             | Ta=-40 to + 85℃          | _      |        | 12        | μА        |           |

| Supply current 4                            | IDD4             | CPU: In 500kHz CR                                            | Ta=25°C                  | _      | 70     | 85        | μА        |           |

| Supply current 4                            | 1004             | operating state.                                             | Ta=-40 to + 85℃          | _      |        | 100       | μΑ        |           |

| Supply current 5                            | CPU ope          |                                                              | Ta=25℃                   | _      | 0.83   | 1         | - mA      |           |

| Supply current 5 IDDs                       | 1003             | oscillating state.V <sub>DD</sub> = 1.8 to 3.6V              | Ta=-40 to + 85°C         |        |        | 1.2       | IIIA      |           |

| Complete our month C                        | IDDC             | CPU: In 4.096MHz operating                                   | Ta=25℃                   | _      | 1.3    | 1.4       | ^         |           |

| Supply current 6                            | IDD6             | state.Crystal/ceramic: In oscillating state. *1*2 VDD = 3.0V | Ta=-40 to + 85℃          | _      | _      | 2.0       | mA        |           |

$<sup>^{\</sup>star 1}$ : Use 32.768KHz Crystal Oscillator C-001R (Epson Toyocom) with capacitance C\_GL/C\_DL=0pF.  $^{\star 2}$ : Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).  $^{\star 3}$ : Significant bits of BLKCON0~BLKCON4 registers are all "1".

## DC CHARACTERISTICS (3/4)

$(V_{DD} = 1.1 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V}, \text{ Ta} = -40 \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise specified})$  (3/4)

|                                                                                         |                      | ,                                            | 1.1 to 3.6V, $V_{SS} = 0V$                      | , 1a – <del>-4</del>    | Rating | C, uriless |      | Measuring |  |

|-----------------------------------------------------------------------------------------|----------------------|----------------------------------------------|-------------------------------------------------|-------------------------|--------|------------|------|-----------|--|

| Parameter                                                                               | Symbol               | Cond                                         | ition                                           | Min.                    | Тур.   | Max.       | Unit | circuit   |  |

|                                                                                         |                      | IOH1 = -0.5mA, \                             | V <sub>DD</sub><br>-0.5                         | _                       |        |            |      |           |  |

| Output voltage 1 (P20, P21, P22,                                                        | (P20, P21, P22, VOH1 | IOH1 = -0.1mA, \                             | V <sub>DD</sub><br>-0.3                         |                         |        |            |      |           |  |

| P24/2 <sup>nd</sup> function<br>is selected)<br>(P30–P35)                               |                      | IOH1 = -0.03mA,                              | V <sub>DD</sub> = 1.1 to 3.6V                   | V <sub>DD</sub><br>-0.3 |        |            |      |           |  |

| (P40–P47)                                                                               |                      | IOL1 = +0.5mA, \                             | $I_{DD} = 1.8 \text{ to } 3.6 \text{V}$         |                         |        | 0.5        |      |           |  |

| (PA0-PA7)                                                                               | VOL1                 | IOL1 = +0.1mA, \                             | $I_{DD} = 1.3 \text{ to } 3.6 \text{V}$         |                         | _      | 0.5        | V    | 2         |  |

|                                                                                         | VOLI                 | IOL1 = +0.03mA,                              | $V_{DD}$ = 1.1 to 3.6V                          | _                       |        | 0.3        |      |           |  |

| Output voltage 2<br>(P20, P21, P22,<br>P24/2 <sup>nd</sup> function is<br>Not selected) | VOL2                 | IOL2 = +5mA, V                               | IOL2 = +5mA, V <sub>DD</sub> = 1.8 to 3.6V      |                         |        | 0.5        |      |           |  |

| Output voltage 3 (P40, P41)                                                             | VOL3                 | IOL3 = +3mA, V<br>(when I <sup>2</sup> C mod |                                                 | _                       |        | 0.4        |      |           |  |

| Output leakage<br>(P20, P21, P22,<br>P24)                                               | ЮОН                  | VOH = V <sub>DD</sub> (in high               | VOH = V <sub>DD</sub> (in high-impedance state) |                         |        | 1          |      |           |  |

| (P30–P35)<br>(P40–P47)<br>(PA0–PA7)*1                                                   | IOOL                 | VOL = V <sub>SS</sub> (in high-              | -1                                              | _                       | _      | μА         | 3    |           |  |

|                                                                                         | IIH1                 | VIH1 :                                       | = V <sub>DD</sub>                               | 0                       |        | 1          |      |           |  |

| Input current 1                                                                         |                      |                                              | $V_{DD}$ = 1.8 to 3.6V                          | -600                    | -300   | -20        |      |           |  |

| (RESET_N)                                                                               | IIL1                 | VIL1 = V <sub>SS</sub>                       | $V_{DD}$ = 1.3 to 3.6V                          | -600                    | -300   | -10        |      |           |  |

|                                                                                         |                      |                                              | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$         | -600                    | -300   | -2         |      |           |  |

|                                                                                         |                      |                                              | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$         | 20                      | 300    | 600        |      |           |  |

| Input current 1                                                                         | IIH1                 | VIH1 = V <sub>DD</sub>                       | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$         | 10                      | 300    | 600        |      |           |  |

| (TEST)                                                                                  |                      |                                              | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$         | 2                       | 300    | 600        |      |           |  |

|                                                                                         | IIL1                 | VIL1                                         | = V <sub>ss</sub>                               | -1                      | —      |            |      |           |  |

|                                                                                         |                      | VIH2 = V <sub>DD</sub>                       | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$         | 2                       | 30     | 200        | μΑ   | 4         |  |

| Input current 2                                                                         | IIH2                 | (when pulled-down)                           | $V_{DD}$ = 1.3 to 3.6V                          | 0.2                     | 30     | 200        |      |           |  |

| ·<br>(NMI)                                                                              |                      | (                                            | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$         | 0.01                    | 30     | 200        |      |           |  |

| (P00-P03)                                                                               |                      | VIL2 = V <sub>SS</sub>                       | $V_{DD}$ = 1.8 to 3.6V                          | -200                    | -30    | -2         |      |           |  |

| (P10, P11)                                                                              | IIL2                 | (when pulled-up)                             | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$         | -200                    | -30    | -0.2       |      |           |  |

| (P30–P35)<br>(P40–P47)                                                                  |                      | (                                            | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$         | -200                    | -30    | -0.01      |      |           |  |

| (PA0-PA7)                                                                               | IIH2Z                | VIH2 = V <sub>DD</sub> (in high              | -impedance state)                               | _                       | _      | 1          |      |           |  |

|                                                                                         | IIL2Z                | VIL2 = V <sub>SS</sub> (in high              | -impedance state)                               | -1                      | _      |            |      |           |  |

## DC CHARACTERISTICS (4/4)

$(V_{DD}$  = 1.1 to 3.6V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise specified) (4/4)

| Parameter Symbo                                                                                     |                               | Condition                                         |                         | Rating                  |                         |      | Measuring |  |  |

|-----------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------|-------------------------|-------------------------|-------------------------|------|-----------|--|--|

| Farameter                                                                                           | Symbol                        | Condition                                         | Min.                    | Тур.                    | Max.                    | Unit | circuit   |  |  |

| Input voltage 1<br>(RESET_N)                                                                        | VIH1                          | $V_{DD}$ = 1.3 to 3.6V                            | 0.7<br>×V <sub>DD</sub> | _                       | $V_{DD}$                |      |           |  |  |

| (TEST) VIH1 (NMI) (P00–P03)                                                                         |                               | V <sub>DD</sub> = 1.1 to 3.6V                     | $0.7 \times V_{DD}$     | _                       | $V_{DD}$                |      |           |  |  |

| (P10, P11)<br>(P31–P35)                                                                             |                               | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$           | 0                       |                         | $0.3$ $\times V_{DD}$   | V    | 5         |  |  |

| (P40–P43) VIL1<br>(P45–P47)<br>(PA0–PA7) <sup>*1</sup>                                              | V <sub>DD</sub> = 1.1 to 3.6V | 0                                                 |                         | 0.2<br>×V <sub>DD</sub> | V                       | 3    |           |  |  |

| Input voltage 2                                                                                     | VIH2                          | _                                                 | 0.7<br>×V <sub>DD</sub> | _                       | $V_{DD}$                |      |           |  |  |

| (P30, P44)                                                                                          | VIL2                          | _                                                 | 0                       | _                       | 0.3<br>×V <sub>DD</sub> |      |           |  |  |

| Input pin<br>capacitance<br>(NMI)<br>(P00–P03)<br>(P10, P11)<br>(P30–P35)<br>(P40–P47)<br>(PA0–PA7) | CIN                           | f = 10kHz<br>V <sub>rms</sub> = 50mV<br>Ta = 25°C | _                       | _                       | 5                       | pF   | _         |  |  |

## **MEASURING CIRCUITS**

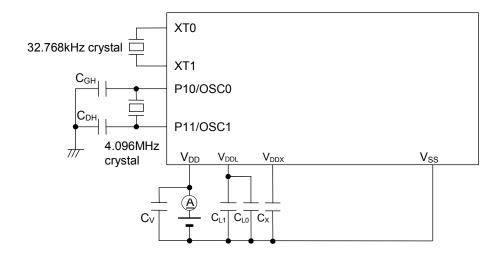

## **MEASURING CIRCUIT 1**

$\begin{array}{lll} \text{C}_{\text{V}:} & 1 \mu \text{F} \\ \text{C}_{\text{L}0:} & 1 \mu \text{F} \\ \text{C}_{\text{L}1:} & 0.1 \mu \text{F} \\ \text{C}_{\text{X}:} & 0.1 \mu \text{F} \\ \text{C}_{\text{GH}:} & 24 \text{pF} \\ \text{C}_{\text{DH}:} & 24 \text{pF} \\ 32.768 \text{kHz crystal:} \\ \text{C-001R (Epson Toyocom)} \\ 4.096 \text{MHz crystal:} \\ \text{HC49SFWB (Kyocera)} \end{array}$

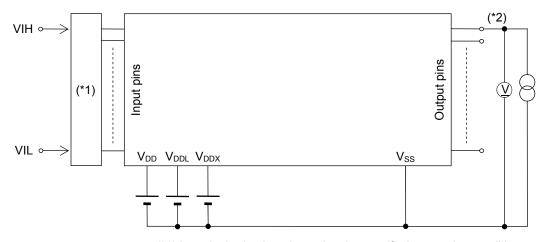

## **MEASURING CIRCUIT 2**

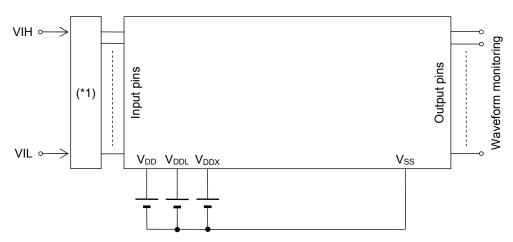

- (\*1) Input logic circuit to determine the specified measuring conditions.

- (\*2) Measured at the specified output pins.

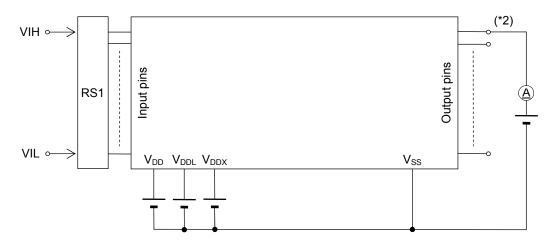

## **MEASURING CIRCUIT 3**

- \*1: Input logic circuit to determine the specified measuring conditions.

- \*2: Measured at the specified output pins.

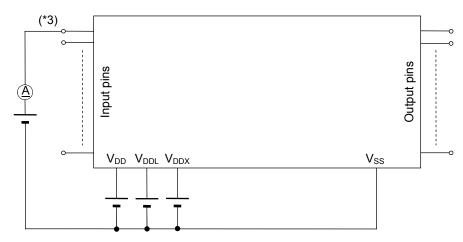

## **MEASURING CIRCUIT 4**

\*3: Measured at the specified output pins.

## **MEASURING CIRCUIT 5**

\*1: Input logic circuit to determine the specified measuring conditions.

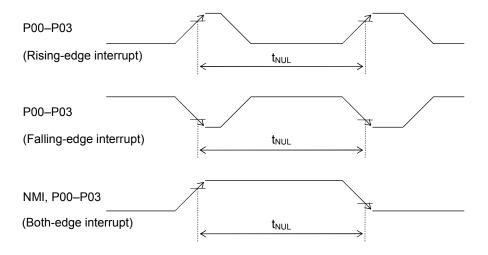

## **AC CHARACTERISTICS (External Interrupt)**

$(\hat{V}_{DD} = 1.1 \text{ to } 3.6\text{V}, \text{V}_{SS} = 0\text{V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

|                                   |                  | 100 111 10 0.01, 133 01, 14 10 10                                        | ,      |      | or moo op |       |  |

|-----------------------------------|------------------|--------------------------------------------------------------------------|--------|------|-----------|-------|--|

| Parameter                         | Symbol           | Condition                                                                | Rating |      |           | Unit  |  |

| r alailletei                      | Symbol           |                                                                          | Min.   | Typ. | Max.      | Offic |  |

| External interrupt disable period | T <sub>NUL</sub> | Interrupt: Enabled (MIE = 1), CPU: NOP operation System clock: 32.768kHz | 76.8   | _    | 106.8     | μS    |  |

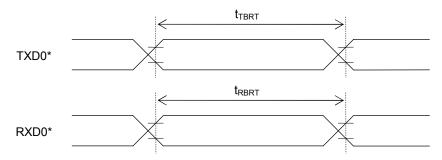

## **AC CHARACTERISTICS (UART)**

( $V_{DD}$  = 1.3 to 3.6V,  $V_{SS}$  = 0V, Ta = -40 to +85°C, unless otherwise specified)

| Parameter          | Symbol            | Symbol Condition Rating |                          |       |                          | Unit  |  |

|--------------------|-------------------|-------------------------|--------------------------|-------|--------------------------|-------|--|

|                    | Syllibol          | Condition               | Min.                     | Тур.  | Max.                     | Offic |  |

| Transmit baud rate | t <sub>TBRT</sub> | _                       | _                        | BRT*1 | _                        | s     |  |

| Receive baud rate  | t <sub>RBRT</sub> | _                       | BRT* <sup>1</sup><br>-3% | BRT*1 | BRT* <sup>1</sup><br>+3% | S     |  |

<sup>\*1:</sup> Baud rate period (including the error of the clock frequency selected) set with the UART0 baud rate register (UA0BRTL,H) and the UART0 mode register 0 (UA0MOD0).

<sup>\*:</sup> Indicates the secondary function of the port.

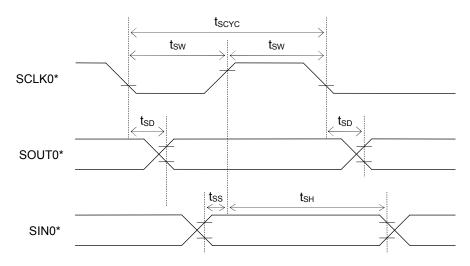

## **AC CHARACTERISTICS (Synchronous Serial Port)**

$(V_{DD} = 1.3 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V}, \text{ Ta} = -40 \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise specified})$

| Darameter                             | Cymhol            | (V <sub>DD</sub> = 1.3 to 3.6V, V <sub>SS</sub> = 0V, 18                   |                            | Rating                     |                            | Unit  |  |

|---------------------------------------|-------------------|----------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|--|

| Parameter                             | Symbol            | Condition                                                                  | Min.                       | Тур.                       | Max.                       | Offic |  |

| SCLK input cycle                      | tscyc             | When RC oscillation is active $*^2$ (V <sub>DD</sub> = 1.3 to 3.6V)        | 10                         | _                          | _                          | μS    |  |

| (slave mode)                          | LSCYC             | When high-speed oscillation is active $*^3(V_{DD} = 1.8 \text{ to } 3.6V)$ | 1                          | _                          |                            | μS    |  |

| SCLK output cycle (master mode)       | t <sub>SCYC</sub> | _                                                                          | _                          | SCLK*1                     | _                          | s     |  |

| SCLK input pulse width                |                   | When RC oscillation is active $*^2$ (V <sub>DD</sub> = 1.3 to 3.6V)        | 4                          | _                          | _                          | μS    |  |

| (slave mode)                          | tsw               | When high-speed oscillation is active $*^3(V_{DD} = 1.8 \text{ to } 3.6V)$ | 0.4                        | _                          |                            | μS    |  |