# 14-Bit, 2 MSPS, Dual-Channel, Differential Analog-to-Digital Converters

#### 1 FEATURES

Sample Rate: 2 MSPS

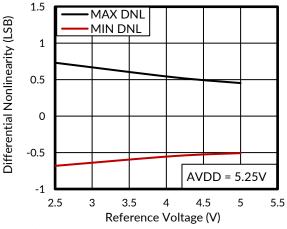

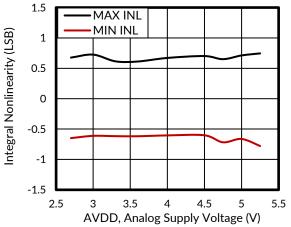

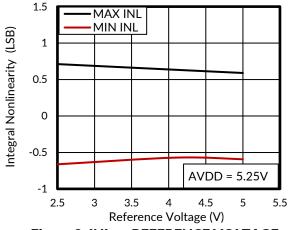

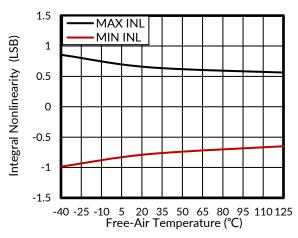

INL 2.5 LSB (max)

• Wide Supply Range:

Analog: 2.7 V to 5.25 V Digital: 1.65 V to AVDD

14-Bit No Missing Code Resolution

Auto Power-Down at Lower Speeds

• Two Differential Inputs

Operating Temperature Range -40 °C to 125 °C

• SPI-Compatible Interface

Package: QFN3x3-16

#### **2 APPLICATIONS**

- Optical networking

- Sensors Measurements

- Portable Instrumentation

- Medical Instrumentation

- Data Acquisition Systems

- Battery-Powered Equipment

#### **3 DESCRIPTIONS**

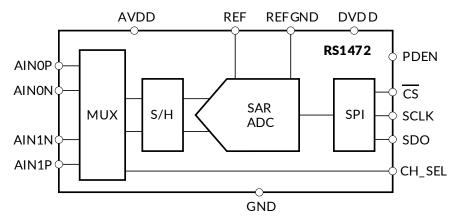

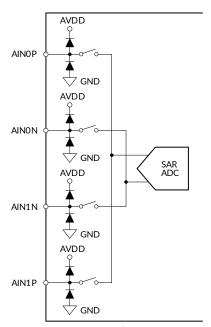

The RS1472 is a 14-bit, 2MSPS analog-to-digital converter (ADC) that offers differential inputs. The device operates at a 2MSPS sample rate with a standard 16 clock data frame. The device includes a two-channel input multiplexer and a low-power successive approximation register (SAR) ADC with an inherent sample-and-hold (S/H) input stage.

The RS1472 supports a wide analog supply range that allows the full-scale input range to extend to ±5Vpp. A simple SPI, with a digital supply that can operate as low as 1.65 V, allows for easy interfacing to a wide variety of digital controllers. Automatic power-down can be enabled when operating at slower speeds to dramatically reduce power consumption.

The RS1472 is offered in a leadless QFN3x3-16 package and is specified over a temperature range of -40°C to +125°C.

#### Device Information (1)

| PART<br>NUMBER | PACKAGE   | BODY<br>SIZE(NOM) |  |  |  |  |  |

|----------------|-----------|-------------------|--|--|--|--|--|

| RS1472         | QFN3x3-16 | 3.00mm x 3.00mm   |  |  |  |  |  |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

Figure 1. Block Diagram

## **Table of Contents**

| 1 FEATURES                                   | 1  |

|----------------------------------------------|----|

| 2 APPLICATIONS                               |    |

| 3 DESCRIPTIONS                               | 1  |

| 4 Revision History                           | 3  |

| 5 PACKAGE/ORDERING INFORMATION (1)           | 4  |

| 6 Pin Configuration and Functions (Top View) | 5  |

| 7 SPECIFICATIONS                             | 6  |

| 7.1 Absolute Maximum Ratings                 | 6  |

| 7.2 ESD Ratings                              | 6  |

| 7.3 Recommended Operating Conditions         | 6  |

| 7.4 ELECTRICAL CHARACTERISTICS               | 7  |

| 7.5 Timing DIAGRAM:RS1472                    | 9  |

| 7.6 TYPICAL CHARACTERISTICS                  | 10 |

| 8 OVERVIEW                                   | 18 |

| 8.1 MULTIPLEXER AND ADC INPUT                | 18 |

| 8.2 REFERENCE                                | 19 |

| 8.3 ADC TRANSFER FUNCTION                    | 20 |

| 9 DEVICE OPERATION                           | 21 |

| 9.1 16-CLOCK FRAME                           | 21 |

| 9.2 32-CLOCK FRAME                           | 21 |

| 9.3 CONVERSION ABORT                         | 22 |

| 9.4 POWER-DOWN                               | 22 |

| 9.5 APPLICATION INFORMATION                  | 23 |

| 9.6 INPUT COMMON-MODE RANGE                  | 24 |

| 9.7 DRIVING AN ADC WITHOUT A DRIVING OP AMP  | 24 |

| 10 PACKAGE OUTLINE DIMENSIONS                | 26 |

| 11 TADE AND DEEL INCODMATION                 | 27 |

## **4 Revision History**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION | Change Date | Change Item                   |

|---------|-------------|-------------------------------|

| A.0     | 2023/02/14  | Preliminary version completed |

| A.1     | 2024/01/31  | Initial version completed     |

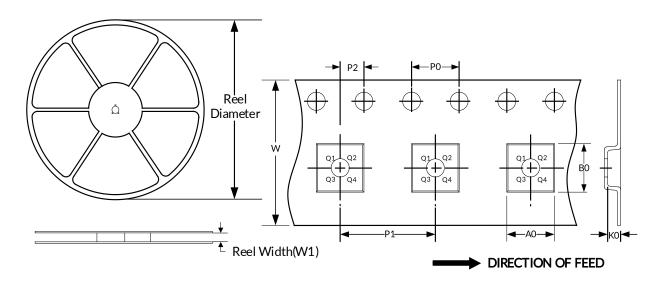

## **5 PACKAGE/ORDERING INFORMATION (1)**

| Orderable<br>Device | Package<br>Type | Pin | Channel            | Op Temp(°C)  | Device<br>Marking <sup>(2)</sup> | MSL <sup>(3)</sup> | Package Qty        |

|---------------------|-----------------|-----|--------------------|--------------|----------------------------------|--------------------|--------------------|

| RS1472XTQC16        | QFN3x3-16       | 16  | 2-<br>Differential | -40°C ~125°C | RS1472                           | MSL3               | Tape and Reel,5000 |

#### NOTE:

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) There may be additional marking, which relates to the lot trace code information(data code and vendor code), the logo or the environmental category on the device.

- (3) MSL, The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications.

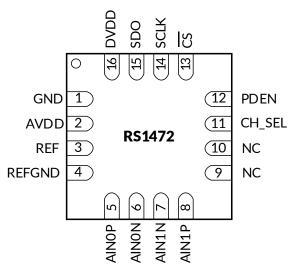

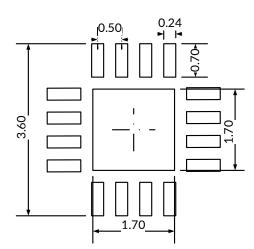

## 6 Pin Configuration and Functions (Top View)

Figure 2. QFN3x3-16

**Table 1. PIN FUNCTIONS**

| PIN | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                             |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND    | Power supply ground                                                                                                                                                                                                                                                                     |

| 2   | AVDD   | ADC power supply                                                                                                                                                                                                                                                                        |

| 3   | REF    | ADC positive reference input, decouple this pin with REFGND                                                                                                                                                                                                                             |

| 4   | REFGND | Reference return; short to analog ground plane                                                                                                                                                                                                                                          |

| 5   | AIN0P  | Positive analog input, channel 0                                                                                                                                                                                                                                                        |

| 6   | AIN0N  | Negative analog input, channel 0                                                                                                                                                                                                                                                        |

| 7   | AIN1N  | Negative analog input, channel1                                                                                                                                                                                                                                                         |

| 8   | AIN1P  | Positive analog input, channel1                                                                                                                                                                                                                                                         |

| 9   | NC     | Not connected internally, recommended to short this pin to GND                                                                                                                                                                                                                          |

| 10  | NC     | Not connected internally, recommended to short this pin to GND                                                                                                                                                                                                                          |

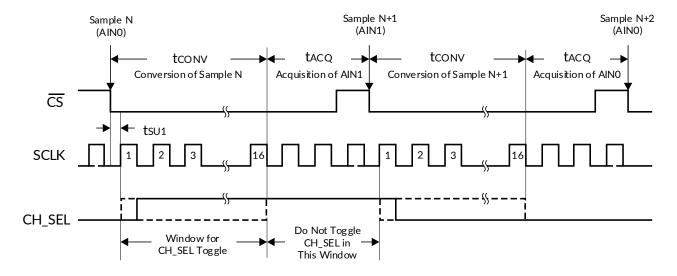

| 11  | CH_SEL | Selects the analog input channel. Low = Channel 0 High = Channel 1 Recommended to change the channel within a window of one clock, from half a clock after the $\overline{\text{CS}}$ falling edge. This change ensures the settling on the multiplexer output before the sample start. |

| 12  | PDEN   | Enables a power down feature if it is high at the $\overline{\text{CS}}$ rising edge                                                                                                                                                                                                    |

| 13  | CS     | Chip select signal, active low                                                                                                                                                                                                                                                          |

| 14  | SCLK   | Serial SPI clock                                                                                                                                                                                                                                                                        |

| 15  | SDO    | Serial data out                                                                                                                                                                                                                                                                         |

| 16  | DVDD   | Digital I/O supply                                                                                                                                                                                                                                                                      |

#### **7 SPECIFICATIONS**

#### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                      | •                                       |           | MIN  | MAX      | UNIT |

|--------------------------------------|-----------------------------------------|-----------|------|----------|------|

|                                      | AVDD to GND, DVDD to GND (2)            | -0.3      | 6    |          |      |

| Voltage Digital input voltage to GND |                                         |           | -0.3 | DVDD+0.3 | V    |

|                                      | Digital output pin (3)                  |           | -0.3 | DVDD+0.3 |      |

| Current                              | Signal input pin                        |           | -10  | 10       | mA   |

| θJA                                  | Package thermal impedance (4)           | QFN3×3-16 |      | 70       | °C/W |

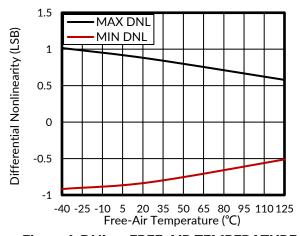

|                                      | Operating range, T <sub>A</sub>         |           | -40  | 125      |      |

| Temperature                          | Junction, T <sub>J</sub> <sup>(5)</sup> | -40       | 150  | °C       |      |

|                                      | Storage, T <sub>stg</sub>               |           | -65  | 150      |      |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

- (3) Include  $\overline{\text{CS}}$ , SCLK, SDO.

- (4) The package thermal impedance is calculated in accordance with JESD-51.

- (5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

#### 7.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | V    |

|                    |                         | Machine model (MM)                                                    | ±200  |      |

- (1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

#### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                               |                                                            | MIN               | NOM | MAX       | UNIT |

|-------------------------------|------------------------------------------------------------|-------------------|-----|-----------|------|

| Supply voltage                | AVDD to GND                                                | 2.7               | 3.3 | 5.25      | V    |

|                               | DVDD to GND                                                | 1.65              | 3.3 | AVDD      | V    |

| Full scale input              | V <sub>IN</sub> =V <sub>(AINP)</sub> - V <sub>(AINN)</sub> | -V <sub>REF</sub> |     | $V_{REF}$ | V    |

| Operating ambient temperature |                                                            | -40               |     | 125       | °C   |

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3V beyond the supply rails should be current-limited to 10mA or less.

### 7.4 ELECTRICAL CHARACTERISTICS

$(T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ AVDD} = 2.7\text{V to } 5.25\text{V}, \text{ DVDD} = 1.65\text{V to AVDD}, input common mode = <math>V_{REF}/2 \pm 0.2$ ,  $f_{SAMPLE} = 2\text{MSPS}$ , Typical specifications at  $T_A = +25^{\circ}\text{C}$ , AVDD = 5V, DVDD=1.8V, unless otherwise noted.)

| PARAMETER                                   | TEST CONDITIONS                    | MIN               | TYP      | MAX       | UNITS              |

|---------------------------------------------|------------------------------------|-------------------|----------|-----------|--------------------|

| ANALOG INPUT                                |                                    |                   |          |           |                    |

| Full-scale input span (1)                   | AINxP - AINxN                      | -V <sub>REF</sub> |          | $V_{REF}$ | V                  |

| Al                                          | AINOP, AIN1P                       | -0.2              | AV       | DD + 0.2  | V                  |

| Absolute input range                        | AINON, AIN1N                       | -0.2              | AV       | DD + 0.2  | V                  |

| Input common-mode range (2)                 | (AINxP + AINxN)/2                  | V                 | /REF/2 ± | 0.2       | V                  |

| Input capacitance (3)                       |                                    |                   | 36       |           | pF                 |

| Input leakage current                       | At +125°C                          |                   | 1        |           | uA                 |

| SYSTEM PERFORMANCE                          |                                    | •                 | •        | •         |                    |

| Resolution                                  |                                    |                   | 14       |           | Bits               |

| No missing codes                            |                                    | 14                |          |           | Bits               |

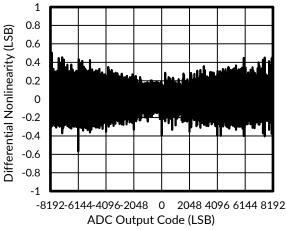

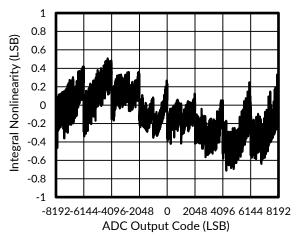

| Integral nonlinearity                       |                                    | -2.5              | ±0.8     | 2.5       | LSB <sup>(4)</sup> |

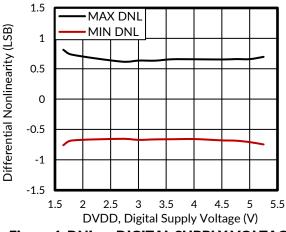

| Differential linearity                      |                                    | -1                | ±0.6     | 1.5       | LSB                |

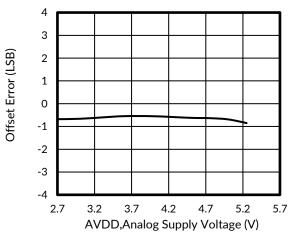

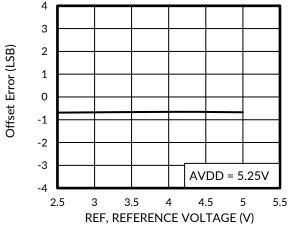

| Offset error (5)                            |                                    | -4                | ±1.5     | 4         | LSB                |

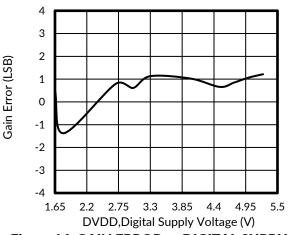

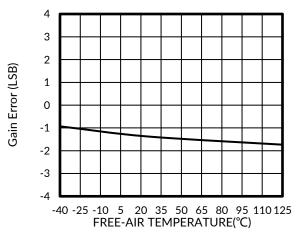

| Gain error                                  |                                    | -4                | ±2       | 4         | LSB                |

| Transition noise                            |                                    |                   | 60       |           | $\mu V_{RMS}$      |

| Power-supply rejection                      | With 500 Hz sine wave on AVDD      |                   | 60       |           | dB                 |

| DYNAMIC CHARACTERISTICS                     |                                    |                   |          |           |                    |

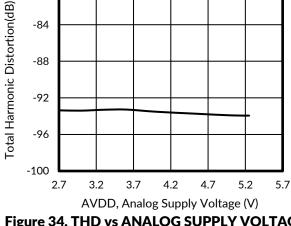

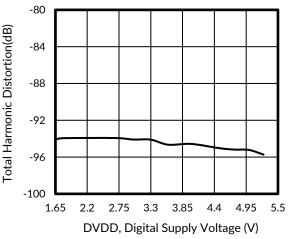

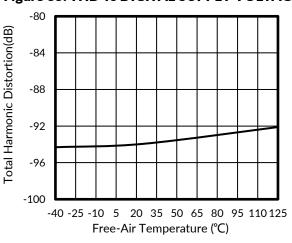

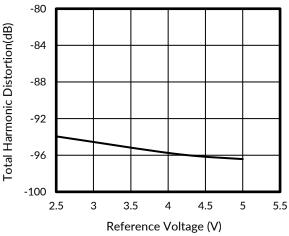

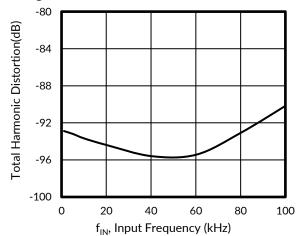

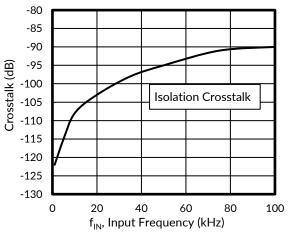

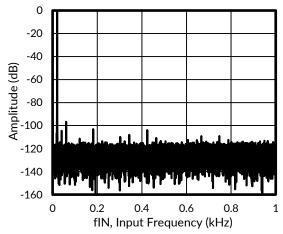

| Total harmonic distortion (THD) (6)         | 20kHz, V <sub>REF</sub> = 4.096V   |                   | -92      |           | dB                 |

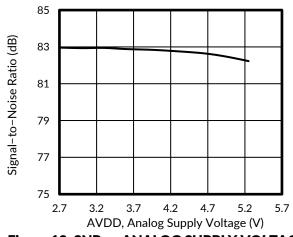

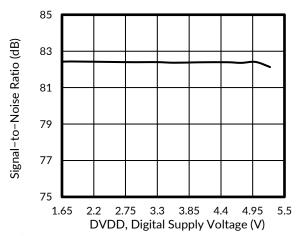

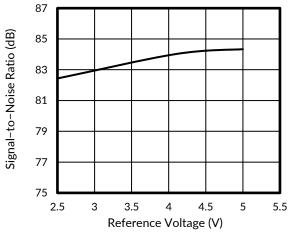

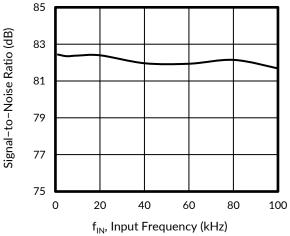

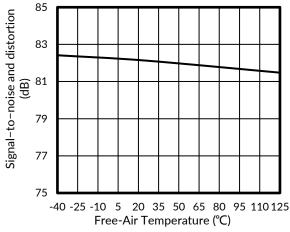

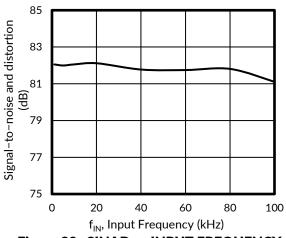

| C: 1: (CVID)                                | 20kHz, V <sub>REF</sub> = 4.096V   | 82                | 84       |           | dB                 |

| Signal to noise ratio (SNR)                 | 100k Hz, V <sub>REF</sub> = 4.096V |                   | 83       |           | dB                 |

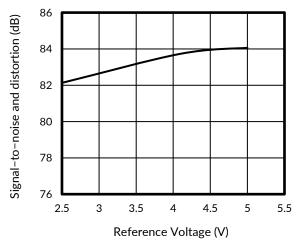

| Signal to noise and distorion ratio (SINAD) | 20kHz, V <sub>REF</sub> = 4.096V   |                   | 84       |           | dB                 |

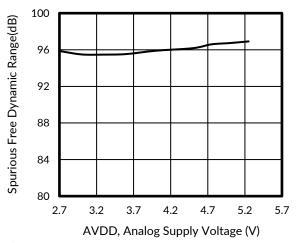

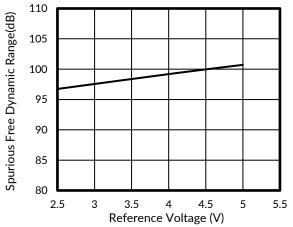

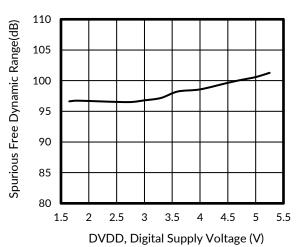

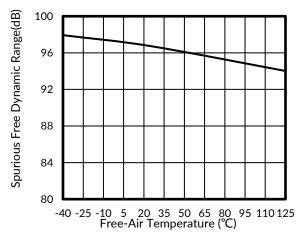

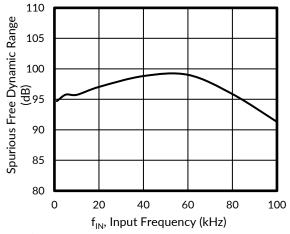

| Spurious-free range (SFDR)                  | 20kHz, V <sub>REF</sub> = 4.096V   |                   | 94       |           | dB                 |

| Full power bandwidth (7)                    | At -1dB                            |                   | 20       |           | MHz                |

| SAMPLING DYNAMICS                           | •                                  |                   |          |           |                    |

| Conversion time                             |                                    |                   |          | 16        | SCLK               |

| Acquisition time                            |                                    | 80                |          |           | ns                 |

| Maximum sample rate (throughput rate)       | 40 MHz SCLK with a 16-clock frame  |                   |          | 2         | MSPS               |

| Aperture delay (8)                          |                                    |                   | 10       |           | ns                 |

#### NOTE:

- (1) Ideal input span; does not include gain or offset error.

- $\begin{tabular}{ll} \end{tabular} \begin{tabular}{ll} \end{tabular} \beg$

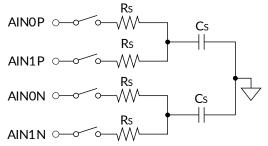

- (3) Refer to Figure 47 for sampling circuit details.

- (4) LSB means least significant bit.

- (5) In the dynamic characteristics test, input signal complies with PIN=-0.5dBFs

- (6) Calculated on the first nine harmonics of the input frequency.

- (7) Indicates signal bandwidth for undersampling applications.

- (8) Ensured by simulation.

### **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ AVDD} = 2.7\text{V to } 5.25\text{V}, \text{ DVDD} = 1.65\text{V to AVDD}, input common mode = <math>V_{REF}/2 \pm 0.2$ ,  $f_{SAMPLE} = 2MSPS$ , Typical specifications at  $T_A = +25^{\circ}\text{C}$ , AVDD = 5V, DVDD=1.8V, unless otherwise noted.)

|                   | DADA44555                             |                                                          |         |        |         |       |

|-------------------|---------------------------------------|----------------------------------------------------------|---------|--------|---------|-------|

|                   | PARAMETER                             | CONDITIONS                                               | MIN     | TYP    | MAX     | UNITS |

| DIGITA            | L INPUTS/OUTPUTS                      |                                                          |         |        | •       | •     |

| VIH               | High level input voltage              |                                                          | 0.7DVDD |        | DVDD    | V     |

| VIL               | Low level input voltage               |                                                          | GND     |        | 0.3DVDD | V     |

| Vон               | High level output voltage             | SDO load 20 pF                                           | 0.8DVDD |        |         | V     |

| V <sub>OL</sub>   | Low level output voltage              | SDO load 20 pF                                           |         |        | 0.2DVDD | ٧     |

| I <sub>LEAK</sub> | Input leakage current                 | 0 < VIN < DVDD                                           |         | ±1     |         | μΑ    |

| External          | l reference                           |                                                          | 2.5     |        | AVDD    | V     |

| POWER             | RSUPPLY                               |                                                          |         |        |         |       |

| AVDD              | Analog Supply Voltage                 |                                                          | 2.7     | 3.3    | 5.25    | V     |

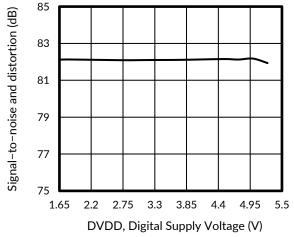

| DVDD              | Digital Supply Voltage                |                                                          | 1.65    | 3.3    | AVDD    | V     |

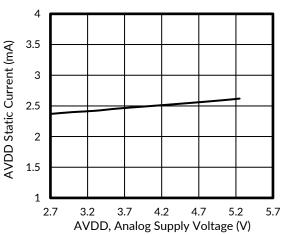

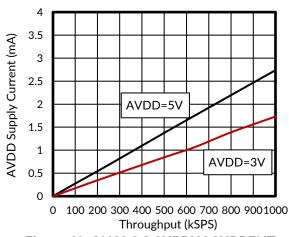

|                   |                                       | AVDD = 3.3V, f <sub>SAMPLE</sub> = 2MSPS                 |         | 3.6    | 4.2     |       |

| ,                 | A                                     | AVDD = 5V, f <sub>SAMPLE</sub> = 2MSPS                   |         | 4.5    | 5.5     |       |

| I <sub>AVDD</sub> | Analog supply current                 | AVDD = 3.3V, SCLK off                                    |         | 2.7    |         | mA    |

|                   |                                       | AVDD = 5V, SCLK off                                      |         | 3      | 3.5     |       |

| I <sub>DVDD</sub> | Digital supply current <sup>(9)</sup> | DVDD =3.3V, f <sub>SAMPLE</sub> = 2MSPS<br>SDO load 20pF |         | 850    |         | μΑ    |

|                   | Power down state                      | SCLK = 40 MHz                                            |         | 500    |         | μΑ    |

| $I_{PD}$          | AVDD supply current                   | SCLK off                                                 |         |        | 2.5     | μΑ    |

| PsT               | Power up time                         | From power down state using PDEN pin                     |         | 0.3(4) | 1       | μs    |

| TA                | Specified performance                 |                                                          | -40     |        | 125     | °C    |

#### NOTE:

<sup>(9)</sup> DVDD consumes only dynamic current. IDVDD = CLOAD × DVDD × number of 0→1 transitions in SDO × fSAMPLE. This is a load-dependent current and there is no DVDD current when the output is not toggling.

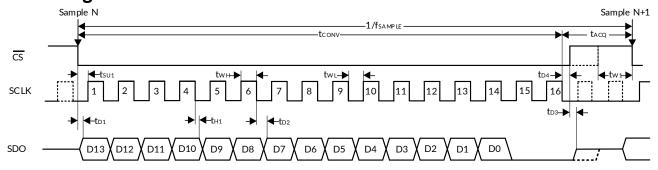

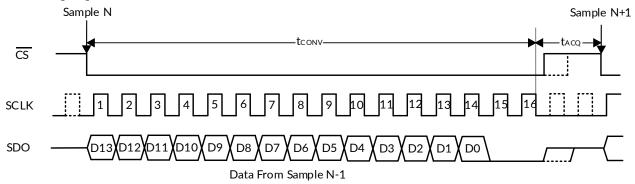

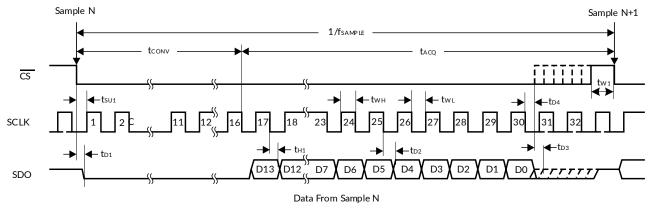

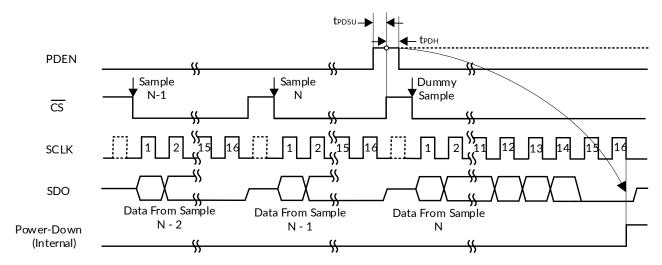

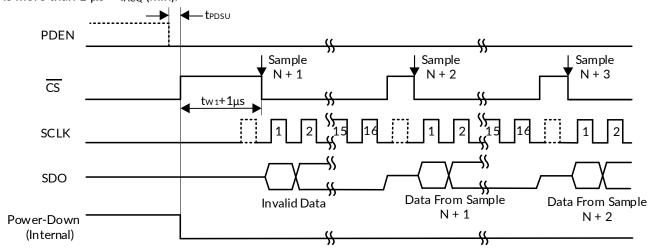

## 7.5 Timing DIAGRAM:RS1472

Data from Sample N - 1

#### Table 2. TIMING REQUIREMENTS: RS1472(1)

|                                | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TEST CONSITIONS(2)           | MIN | TYP | MAX  | UNIT |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|------|------|

| tconv                          | Conversion time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                              |     |     | 16   | SCLK |

| tacq                           | Acquisition time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              | 80  |     |      | ns   |

| tsample                        | Sample rate (throughput rate)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SCLK=40MHz<br>16-clock frame |     |     | 2    | MSPS |

| tw1                            | Pulse width $\overline{\text{CS}}$ high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              | 25  |     |      | ns   |

| t <sub>D1</sub>                | 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 201 1 2 | DVDD = 1.8V                  |     |     | 14.5 | ns   |

|                                | Delay time, $\overline{\text{CS}}$ low to first data (D0~D15) out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DVDD = 3V                    |     |     | 12.5 | ns   |

|                                | out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DVDD = 5V                    |     |     | 8.5  | ns   |

| t <sub>SU1</sub>               | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DVDD = 1.8V                  | 3.5 |     |      | ns   |

|                                | Setup time, $\overline{\text{CS}}$ low to first rising edge of SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DVDD = 3V                    | 3.5 |     |      | ns   |

|                                | SCER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DVDD = 5V                    | 3.5 |     |      | ns   |

| t <sub>D2</sub> <sup>(3)</sup> | Delay time, SCLK falling to SDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 1.8V                  |     |     | 11   |      |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 3V                    |     |     | 9    |      |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 5V                    |     |     | 7.1  |      |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 1.8V                  | 4   |     |      | ns   |

| t <sub>H1</sub>                | Hold time, SCLK falling to data valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DVDD = 3V                    | 3   |     |      | ns   |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 5V                    | 2   |     |      | ns   |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 1.8V                  |     |     | 15   | ns   |

| $t_{\text{D3}}$                | Delay time, $\overline{\text{CS}}$ high to SDO 3-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DVDD = 3V                    |     |     | 12.5 | ns   |

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DVDD = 5V                    |     |     | 8.5  | ns   |

| t <sub>D4</sub>                | Delay time, $\overline{\text{CS}}$ rising edge from conversion end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              | 10  |     |      | ns   |

| twн                            | Pulse duration, SCLK high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              | 8   |     |      | ns   |

| twL                            | Pulse duration, SCLK low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                              | 8   |     |      | ns   |

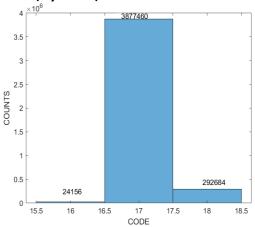

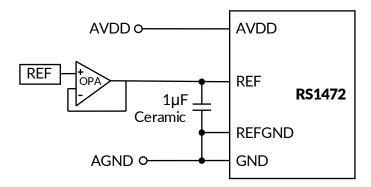

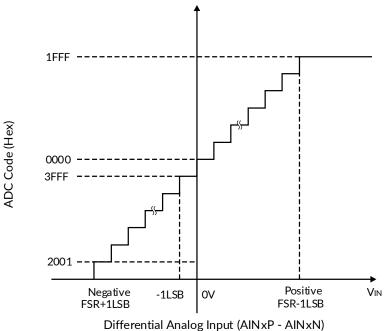

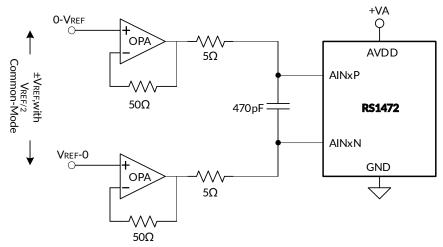

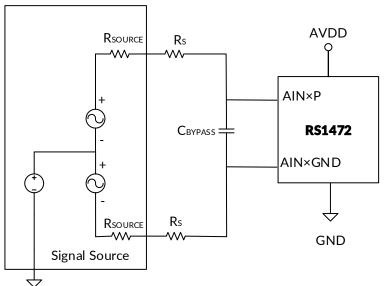

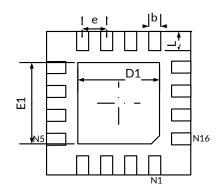

|                                | SCLK frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |     |     | 40   | MHz  |