## **RS4GT08** Quadruple 2-Input Positive-AND Gate

### **1 FEATURES**

- Operating Voltage Range: 2.0V to 5.5V

- Low Power Consumption: 1µA (Max)

- Operating Temperature Range: -40°C to +125°C

- Inputs Are TTL-Voltage Compatible

- High Output Drive: ±32mA at V<sub>CC</sub>=5.0V

- Micro SIZE PACKAGES: SOIC-14(SOP14), TSSOP14

### **2 APPLICATIONS**

- Active Noise Elimination

- Bar Code Scanner

- Blood Pressure Monitor

- CPAP Machine

- Fingerprint identification

- Network attached storage (NAS)

#### **3 DESCRIPTIONS**

The RS4GT08 quadruple 2-input positive-AND gate is designed for 2.0 to 5.5V  $V_{\text{CC}}$  operation.

The RS4GT08 device performs the Boolean function  $Y=A \cdot B$  or  $Y=\overline{A} + \overline{B}$  in positive logic. The device is fully specified for partial-power-down applications using loff. The loff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

The RS4GT08 is available in Green SOIC-14(SOP14) and TSSOP-14 packages. It operates over an ambient temperature range of -40°C to +125°C.

#### **Device Information**<sup>(1)</sup>

| PACKAGE            | BODY SIZE (NOM)    |  |  |  |  |  |

|--------------------|--------------------|--|--|--|--|--|

| SOIC-14<br>(SOP14) | 8.65mm×3.90mm      |  |  |  |  |  |

| TSSOP14            | 5.00mm×4.40mm      |  |  |  |  |  |

|                    | SOIC-14<br>(SOP14) |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### **4 FUNCTION TABLE**

| INP | OUTPUT |   |

|-----|--------|---|

| А   | В      | Y |

| Н   | Н      | Н |

| L   | Н      | L |

| Н   | L      | L |

| L   | L      | L |

Y=A•B H=High Voltage Level L=Low Voltage Level

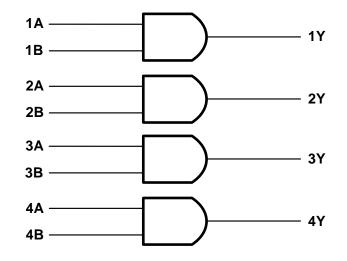

LOGIC SYMBOL 1A 18 17 2A 27 2B 27 3A 37 3A 37 4A 47 4B 47

### **Table of Contents**

| 1 FEATURES                                    | 1                                      |

|-----------------------------------------------|----------------------------------------|

| 2 APPLICATIONS                                | 1                                      |

| 3 DESCRIPTIONS                                | 1                                      |

| 4 FUNCTION TABLE                              | 1                                      |

| 5 Revision History                            | 3                                      |

| 6 PACKAGE/ORDERING INFORMATION <sup>(1)</sup> | 4                                      |

| 7 PIN CONFIGURATIONS                          | 5                                      |

| 8 SPECIFICATIONS                              | 6                                      |

| 8.1 Absolute Maximum Ratings <sup>(1)</sup>   | 6                                      |

| 8.2 ESD Ratings                               | 6                                      |

| 9 ELECTRICAL CHARACTERISTICS                  | 7                                      |

| 9.1 Recommended Operating Conditions          | 7                                      |

| 9.2 DC Characteristics                        | 7                                      |

| 9.3 AC Characteristics                        | 8                                      |

| 10 Parameter Measurement Information          | 9                                      |

| 11 Detailed Description                       | 10                                     |

| 11.1 Overview                                 | 10                                     |

| 11.2 Functional Block Diagram                 | 10                                     |

|                                               |                                        |

| 11.3 Feature Description                      | 10                                     |

| -                                             |                                        |

| 11.3 Feature Description                      | 11                                     |

| 11.3 Feature Description                      | 11<br>11                               |

| 11.3 Feature Description                      | 11<br>11<br>11                         |

| <ul> <li>11.3 Feature Description</li></ul>   | 11<br>11<br>11<br>11                   |

| 11.3 Feature Description                      | 11<br>11<br>11<br>11<br>11             |

| 11.3 Feature Description                      | 11<br>11<br>11<br>11<br>12<br>12       |

| 11.3 Feature Description                      | 11<br>11<br>11<br>11<br>12<br>12<br>12 |

**5 Revision History** <u>Note: Page numbers for previous revisions may different from page numbers in the current version.</u>

| Version | Change Date | Change Item               |

|---------|-------------|---------------------------|

| A.1     | 2023/03/27  | Initial version completed |

### 6 PACKAGE/ORDERING INFORMATION (1)

| PRODUCT | ORDERING<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE LEAD   | PACKAGE<br>MARKING <sup>(2)</sup> | PACKAGE OPTION     |

|---------|--------------------|----------------------|----------------|-----------------------------------|--------------------|

| RS4GT08 | RS4GT08XP -40°C    |                      | SOIC-14(SOP14) | RS4GT08                           | Tape and Reel,4000 |

| K34G100 | RS4GT08XQ          | -40°C ~+125°C        | TSSOP-14       | RS4GT08                           | Tape and Reel,4000 |

NOTE:

(1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

(2) There may be additional marking, which relates to the lot trace code information (data code and vendor code), the logo or the environmental category on the device.

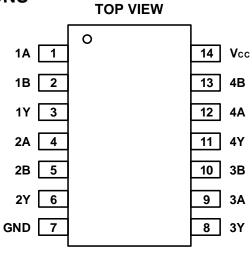

### 7 PIN CONFIGURATIONS

SOIC-14(SOP14)/TSSOP-14

#### **PIN DESCRIPTION**

| PIN                       |      |   | FUNCTION              |

|---------------------------|------|---|-----------------------|

| SOIC-14(SOP14)/TSSOP-14   | NAME |   | FUNCTION              |

| 1                         | 1A   | I | Channel 1 logic input |

| 2                         | 1B   | I | Channel 1 logic input |

| 3                         | 1Y   | 0 | Logic level output1   |

| 4                         | 2A   | I | Channel 2 logic input |

| 5                         | 2B   | I | Channel 2 logic input |

| 6                         | 2Y   | 0 | Logic level output2   |

| 7                         | GND  | - | Ground                |

| 8                         | 3Y   | 0 | Logic level output3   |

| 9                         | ЗA   | I | Channel 3 logic input |

| 10                        | 3B   | I | Channel 3 logic input |

| 11                        | 4Y   | 0 | Logic level output4   |

| 12                        | 4A   | I | Channel 4 logic input |

| 13                        | 4B   | I | Channel 4 logic input |

| 14<br>(1) Linput O output | Vcc  | - | Power Supply          |

(1) I=input, O=output.

### 8 SPECIFICATIONS

#### 8.1 Absolute Maximum Ratings <sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted) (1) (2)

|      |                                                          |                             | MIN  | MAX     | UNIT  |

|------|----------------------------------------------------------|-----------------------------|------|---------|-------|

| Vcc  | Supply voltage range                                     |                             | -0.5 | 6.5     | V     |

| VI   | Input voltage range (2)                                  |                             | -0.5 | 6.5     | V     |

| Vo   | Voltage range applied to any output in the high-impeda   | ince or power-off state (2) | -0.5 | 6.5     | V     |

| Vo   | Voltage range applied to any output in the high or low s | state <sup>(2) (3)</sup>    | -0.5 | Vcc+0.5 | V     |

| Ік   | Input clamp current VI<0                                 |                             |      | -50     | mA    |

| loк  | Output clamp current Vo<0                                |                             |      | -50     | mA    |

| lo   | Continuous output current                                |                             |      | ±50     | mA    |

|      | Continuous current through Vcc or GND                    |                             |      | ±100    | mA    |

| θ.JA | Package thermal impedance (4)                            | SOIC-14(SOP14)              |      | 104.5   | °C/W  |

| UJA  | TSSOP14                                                  |                             |      | 89.21   | C/ VV |

| TJ   | Junction temperature <sup>(5)</sup>                      |                             |      | 150     | °C    |

| Tstg | Storage temperature                                      | -65                         | 150  | °C      |       |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.

(3) The value of  $V_{CC}$  is provided in the Recommended Operating Conditions table.

(4) The package thermal impedance is calculated in accordance with JESD-51.

(5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

#### 8.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                                            |                                                                       | VALUE | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------|-------|------|

|                                            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1000 | V    |

|                                            | Machine model (MM)                                                    | ±200  | V    |

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

### ESD SENSITIVITY CAUTION

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 9 ELECTRICAL CHARACTERISTICS

over recommended operating free-air temperature range (TYP values are at  $T_A = +25$ °C, Full=-40°C to 125°C, unless otherwise noted.) <sup>(1)</sup>

#### 9.1 Recommended Operating Conditions

|                               | - p o . a |                               |     |      |      |

|-------------------------------|-----------|-------------------------------|-----|------|------|

| PARAMETER                     | SYMBOL    | TEST CONDITIONS               | MIN | MAX  | UNIT |

| Supply voltage                | Vcc       | Operating                     | 2.0 | 5.5  | V    |

|                               |           | V <sub>CC</sub> =2.0V         | 1.0 |      |      |

| High-level input voltage      | VIH       | Vcc=3.3V                      | 1.5 |      | V    |

|                               |           | V <sub>CC</sub> =4.5V to 5.5V | 2.0 |      |      |

|                               |           | V <sub>CC</sub> =2.0V         |     | 0.3  |      |

| Low-level input voltage       | VIL       | V <sub>CC</sub> =3.3V         |     | 0.55 | V    |

|                               |           | V <sub>CC</sub> =4.5V to 5.5V |     | 0.8  |      |

| Input voltage                 | VI        |                               | 0   | 5.5  | V    |

| Output voltage                | Vo        |                               | 0   | Vcc  | V    |

| Input transition rise or fall | Δt/Δv     | V <sub>CC</sub> =2.0V to 5.5V |     | 5    | ns/V |

| Operating temperature         | TA        |                               | -40 | +125 | °C   |

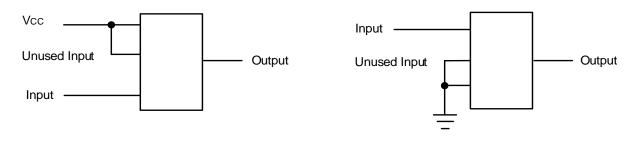

(1) All unused inputs of the device must be held at V<sub>cc</sub> or GND to ensure proper device operation.

#### 9.2 DC Characteristics

| PA               | RAMETER         | TEST CONDITIONS                                    | Vcc              | TEMP  | MIN <sup>(2)</sup> | <b>TYP</b> <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|------------------|-----------------|----------------------------------------------------|------------------|-------|--------------------|---------------------------|--------------------|------|

|                  |                 | Іон = -100μА                                       | 2.0V to 5.5V     |       | Vcc-0.1            |                           |                    |      |

|                  |                 | I <sub>OH</sub> = -8mA                             | 2.0              |       | 1.6                |                           |                    |      |

|                  | Maria           | I <sub>OH</sub> = -24mA                            | 3.3              | Full  | 2.5                |                           |                    |      |

|                  | Vон             |                                                    | 4.5V             | Full  | 3.8                |                           |                    | V    |

|                  |                 | Iон = -32mA                                        | 5V               |       | 4.2                |                           |                    |      |

|                  |                 |                                                    | 5.5V             |       | 4.8                |                           |                    |      |

|                  |                 | I <sub>OL</sub> = 100µA                            | 2.0V to 5.5V     |       |                    |                           | 0.1                |      |

|                  |                 | I <sub>OH</sub> = 8mA                              | 2.0              |       |                    |                           | 0.45               |      |

|                  |                 | I <sub>OH</sub> = 24mA                             | 3.3              | Full  |                    |                           | 0.55               | v    |

|                  | Vol             |                                                    | 4.5V             | Fuii  |                    | 0.55                      | 0.55               | v    |

|                  |                 | I <sub>OL</sub> = 32mA                             | 5V               |       |                    |                           | 0.5                |      |

|                  |                 |                                                    | 5.5V             |       |                    |                           | 0.45               |      |

| h                | A or P inputo   |                                                    | 0V to 5.5V       | +25°C |                    | ±0.1                      | ±1                 |      |

| П                | A or B inputs   | VI=5.5V or GND                                     | 00 10 5.50       | Full  |                    |                           | ±5                 | μA   |

|                  | 1               | $V_1$ or $V_0=5.5V$                                | 0V               | +25°C |                    | ±0.1                      | ±1                 |      |

| l <sub>off</sub> |                 | V 0  V0=5.5V                                       | 00               | Full  |                    |                           | ±10                | μA   |

| lcc              |                 |                                                    | 2.0 / to $5.5$ / | +25°C |                    | 0.1                       | 1                  |      |

|                  |                 | VI=5.5V or GND, Io=0                               | 2.0V to 5.5V     | Full  |                    |                           | 10                 | μA   |

| ICCT             |                 | One input at 3.4V, Other inputs at $V_{CC}$ or GND | 5.5V             | Full  |                    |                           | 500                | μA   |

| Ci (Inp          | ut Capacitance) | Vcc=0V, f=10MHz                                    | 0V               | +25°C |                    | 6                         |                    | pF   |

(1) All unused inputs of the device must be held at  $V_{\text{CC}}$  or GND to ensure proper device operation.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

### 9.3 AC Characteristics

| PARAMETER                     | SYMBOL          | TEST CONDITIONS      |                           | MIN <sup>(2)</sup> | <b>TYP</b> <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|-------------------------------|-----------------|----------------------|---------------------------|--------------------|---------------------------|--------------------|------|

| -                             |                 | $V_{CC}=2.0V\pm0.2V$ | $C_L=30pF, R_L=500\Omega$ |                    | 15.4                      |                    |      |

| Propagation<br>Delay          | t <sub>pd</sub> | Vcc=3.3V±0.3V        | C∟=50pF, R∟=500Ω          |                    | 13.3                      |                    | ns   |

| Dolay                         |                 | Vcc=5V±0.5 V         | CL=50pF, RL=500Ω          |                    | 4.4                       |                    |      |

| Power dissipation capacitance | $C_{pd}$        | Vcc=5V               | f=10MHz                   |                    | 22                        |                    | pF   |

(1) All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation.

(2) This parameter is ensured by design and/or characterization and is not tested in production.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

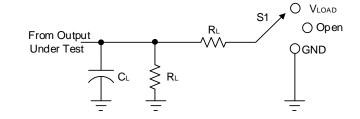

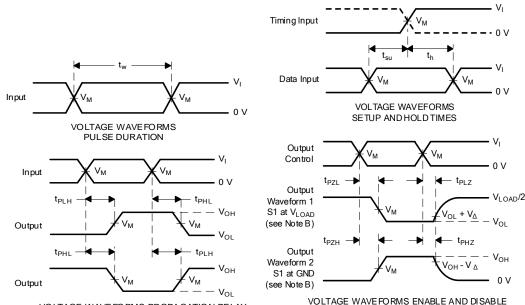

### **10 Parameter Measurement Information**

| TEST                               | S1    |  |  |

|------------------------------------|-------|--|--|

| t <sub>PLH</sub> /t <sub>PHL</sub> | Open  |  |  |

| tplz/tpzl                          | VLOAD |  |  |

| tрнz/tрzн                          | GND   |  |  |

| Ver        | INPUTS |                                | VM                 | View                 | C    |      | D.  |      | V.    |

|------------|--------|--------------------------------|--------------------|----------------------|------|------|-----|------|-------|

| Vcc        | Vı     | t <sub>r</sub> /t <sub>f</sub> | VМ                 | VLOAD                | C∟   |      | R∟  |      | V۵    |

| 1.8V±0.15V | Vcc    | ≤2ns                           | V <sub>CC</sub> /2 | 2 x V <sub>cc</sub>  | 15pF | 30pF | 1MΩ | 1kΩ  | 0.15V |

| 2.5V±0.2V  | Vcc    | ≤2ns                           | V <sub>CC</sub> /2 | $2 \text{ x V}_{CC}$ | 15pF | 30pF | 1MΩ | 500Ω | 0.15V |

| 3.3V±0.3V  | 3V     | ≤2.5ns                         | 1.5V               | 6V                   | 15pF | 50pF | 1MΩ | 500Ω | 0.3V  |

| 5V±0.5V    | Vcc    | ≤2.5ns                         | V <sub>cc</sub> /2 | 2 x Vcc              | 15pF | 50pF | 1MΩ | 500Ω | 0.3V  |

VOLTAGE WAVE FORMS PROPAGATION DE LAY TIMES INVERTION AND NONINVERTING OUTPUTS

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω.

- D. The outputs are measured one at a time, with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{PZL}$  and  $t_{PZH}$  are the same as  $t_{en}$ .

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

- H. All parameters and waveforms are not applicable to all devices.

#### Figure 1. Load Circuit and Voltage Waveforms

### **11 Detailed Description**

#### 11.1 Overview

The RS4GT08 device is a quadruple 2-input positive-AND gate. The device performs the Boolean AND function (Y=A • B or Y= $\overline{A} + \overline{B}$ ) in positive logic. Low I<sub>CC</sub> current allows this device to be used in power sensitive or battery-powered applications. Robust inputs allow the device to up-translate with a propagation delay of 4.4 ns.

#### **11.2 Functional Block Diagram**

#### **11.3 Feature Description**

- The V<sub>cc</sub> for the device is optimized at 5 V.

- The inputs accept VIH levels of 2 V.

- Output ringing is minimized by slow edge rates.

- Inputs are TTL-Voltage compatible.

### 12 Application and Implementation

Information in the following applications sections is not part of the RUNIC component specification, and RUNIC does not warrant its accuracy or completeness. RUNIC's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **12.1 Application Information**

The RS4GT08 device is quadruple AND gate, which is often used for many common functions like power sequencing or an on LED indicator. Because the device is configured to output LOW unless all inputs are HIGH, an LED tied to the output of the device will only turn HIGH when all systems connected are sending a HIGH, or ready signal.

#### **12.2 Design Requirements**

This device uses CMOS technology and has balanced output drive. Take care to avoid bus contention because it can drive currents that would exceed maximum limits. The high drive also creates fast edges into light loads, so routing and load conditions must be considered to prevent ringing.

### **13 Power Supply Recommendations**

The power supply pin should have a good bypass capacitor to prevent power disturbance. For devices with a single supply, a 0.1uF capacitor is recommended and if there are multiple V<sub>CC</sub> terminals then 0.01uF or 0.022uF capacitors are recommended for each power terminal. It is acceptable to parallel multiple bypass caps to reject different frequencies of noise. The 0.1µF and 1µF capacitors are commonly used in parallel. The bypass capacitor should be installed as close to the power terminal as possible.

### 14 Layout

#### 14.1 Layout Guidelines

When using multiple bit logic devices inputs should not ever float. In many cases, functions or parts of functions of digital logic devices are unused; for example, when only two inputs of a triple-input AND gate are used or only 3 of the 4 buffer gates are used. Such input pins should not be left unconnected because the undefined voltages at the outside connections result in undefined operational states. Specified below are the rules that must be observed under all circumstances. All unused inputs of digital logic devices must be connected to a high or low bias to prevent them from floating. The logic level that should be applied to any particular unused input depends on the function of the device. Generally, they will be tied to GND or V<sub>CC</sub> whichever make more sense or is more convenient.

#### 14.2 Layout Example

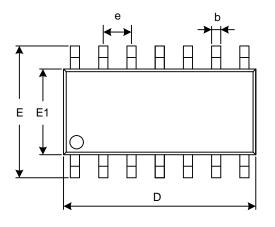

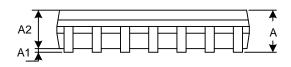

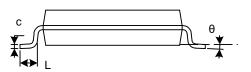

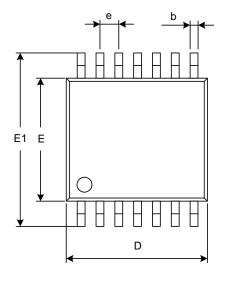

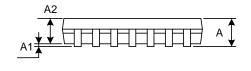

# 15 PACKAGE OUTLINE DIMENSIONS SOIC-14(SOP14)

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions I | In Millimeters | Dimensions In Inches |       |  |  |

|--------|--------------|----------------|----------------------|-------|--|--|

|        | Min          | Мах            | Min                  | Max   |  |  |

| А      | 1.350        | 1.750          | 0.053                | 0.069 |  |  |

| A1     | 0.100        | 0.250          | 0.004                | 0.010 |  |  |

| A2     | 1.350        | 1.550          | 0.053                | 0.061 |  |  |

| b      | 0.310        | 0.510          | 0.012                | 0.020 |  |  |

| с      | 0.100        | 0.250          | 0.004                | 0.010 |  |  |

| D      | 8.450        | 8.850          | 0.333                | 0.348 |  |  |

| е      | 1.270        | (BSC)          | 0.050(BSC)           |       |  |  |

| E      | 5.800        | 6.200          | 0.228                | 0.244 |  |  |

| E1     | 3.800        | 4.000          | 0.150                | 0.157 |  |  |

| L      | 0.400        | 1.270          | 0.016                | 0.050 |  |  |

| θ      | 0°           | 8°             | 0 °                  | 8°    |  |  |

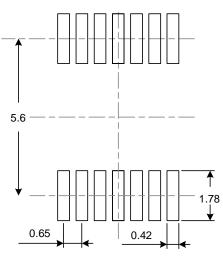

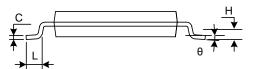

#### **TSSOP-14**

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |

|--------|------------|----------------|----------------------|-------|--|--|

|        | Min Max    |                | Min                  | Max   |  |  |

| A      |            | 1.200          |                      | 0.047 |  |  |

| A1     | 0.050      | 0.150          | 0.002                | 0.006 |  |  |

| A2     | 0.800      | 1.050          | 0.031                | 0.041 |  |  |

| b      | 0.190      | 0.300          | 0.007                | 0.012 |  |  |

| с      | 0.090      | 0.200          | 0.004                | 0.008 |  |  |

| D      | 4.860      | 5.100          | 0.191                | 0.201 |  |  |

| E      | 4.300      | 4.500 0.169    |                      | 0.177 |  |  |

| E1     | 6.250      | 6.550          | 0.246                | 0.258 |  |  |

| е      | 0.650      | (BSC)          | (BSC)                |       |  |  |

| L      | 0.500      | 0.700          | 0.020                | 0.028 |  |  |

| Н      | 0.25(      | (TYP)          | 0.01(TYP)            |       |  |  |

| θ      | 1°         | 7°             | 1°                   | 7°    |  |  |

NOTE:

A. All linear dimension is in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

D. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

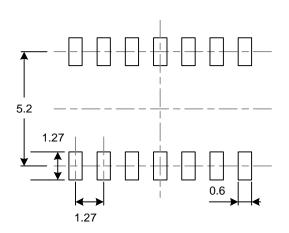

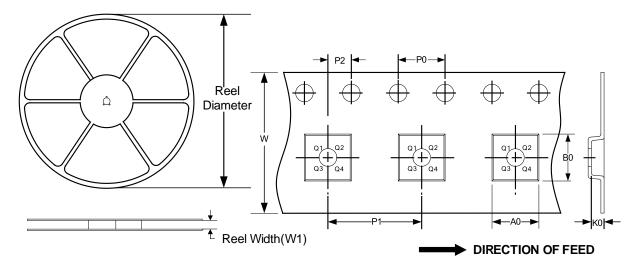

#### 16 TAPE AND REEL INFORMATION REEL DIMENSIONS

#### TAPE DIMENSION

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type   | Reel<br>Diameter | Reel<br>Width(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|------------------|-------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOIC-14(SOP14) | 13"              | 16.4              | 6.60       | 9.30       | 2.10       | 4.0        | 8.0        | 2.0        | 16.0      | Q1               |

| TSSOP-14       | 13"              | 12.4              | 6.95       | 5.60       | 1.20       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

NOTE:

1. All dimensions are nominal.

2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

### IMPORTANT NOTICE AND DISCLAIMER

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Logic Gates category:

Click to view products by RUNIC manufacturer:

Other Similar products are found below :

NL17SG32DFT2G CD4068BE NL17SG86DFT2G NLX1G11AMUTCG NLX1G97MUTCG 74LS38 74LVC1G08Z-7 CD4025BE NLV17SZ00DFT2G NLV17SZ126DFT2G NLV27WZ17DFT2G NLV74HC02ADR2G 74HC32S14-13 74LS133 74LVC1G32Z-7 74LVC1G86Z-7 NLV74HC14ADR2G NLV74HC20ADR2G NLVVHC1G09DFT1G NLX2G86MUTCG 74LVC2G32RA3-7 74LVC2G00HD4-7 NL17SG02P5T5G 74LVC2G86HK3-7 NLVVHC1G14DFT2G NLX1G99DMUTWG NLVVHC1G00DFT2G NLV7SZ57DFT2G NLV74VHC04DTR2G NLV27WZ00USG NLU1G86CMUTCG NLU1G08CMUTCG NL17SZ32P5T5G NL17SZ00P5T5G NL17SH02P5T5G 74AUP2G00RA3-7 NLVVHC1GT00DFT2G NLV74HC02ADTR2G NLX1G332CMUTCG NLV1CT132ADTR2G NL17SG86P5T5G NL17SZ05P5T5G NLV74VHC00DTR2G NLVVHC1G02DFT1G NLV74HC86ADR2G 74LVC2G86RA3-7 NL17SZ38DBVT1G NLV18SZ00DFT2G NLVVHC1G07DFT1G NLVVHC1G02DFT2G