# 12G UHD-SDI Retiming Adaptive Cable Equalizer

### **Key Features**

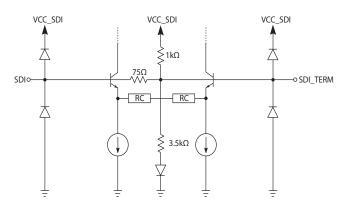

- $75\Omega$  cable input interface with on-chip termination

- SMPTE ST 2082-1, ST 2081-1, ST 424, ST 292-1 and ST 259 compliant input/output

- Multi-standard operation from 1Mb/s to 11.88Gb/s

- In addition to standard SMPTE rates, the device also supports re-timing of DVB-ASI at 270Mb/s, and MADI at 125Mb/s

- Automatic cable equalization. Typical equalized cable lengths of Belden 1694A cable:

- 70m at 11.88Gb/s

- 90m at 5.94Gb/s

- 180m at 2.97Gb/s

- 240m at 1.485Gb/s

- 400m at 270Mb/s

- Cable equalizer mode features:

- Programmable carrier detect with squelch threshold adjustment

- Manual and automatic cable equalizer bypass

- Trace driver features:

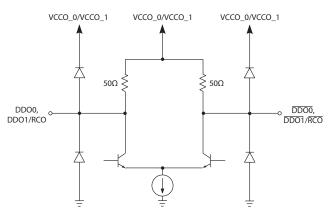

- Integrated 100Ω, differential output termination

- DC-coupling from 1.2V to 2.5V CML logic

- Trace driver data output pre-emphasis to compensate for up to 20" FR4 at 11.88Gb/s

- Manual or automatic re-timer bypass

- Manual or automatic Mute or disable on LOS

- CDR features:

- Manual or automatic rate modes

- Wide Loop bandwidth control

- Re-timing at the following data rates: 125Mb/s, 270Mb/s, 1.485Gb/s, 2.97Gb/s, 5.94Gb/s, 11.88Gb/s. This includes the f/1.001 rates.

- Single 1.8V power supply for analog and digital core

- 1.2V, 1.8V, or 2.5V for trace driver output supply

- GSPI serial control and monitoring interface

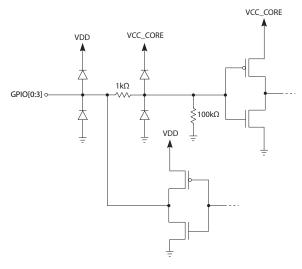

- Four configurable GPIO pins for control or status monitoring

- Wide operating temperature range: -40°C to +85°C

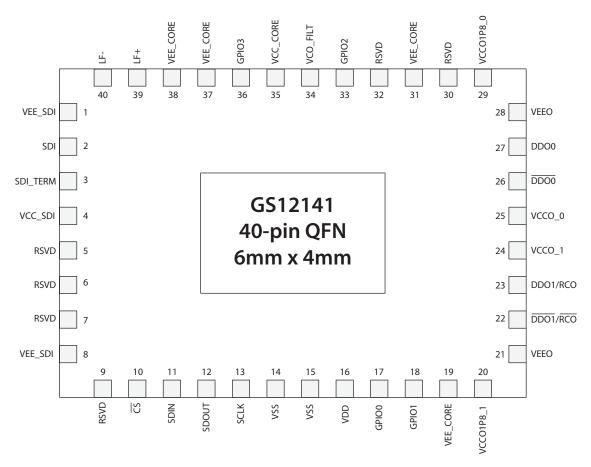

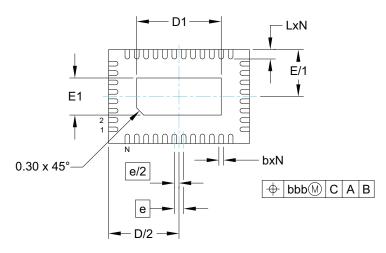

- Small 6mm x 4mm 40-pin QFN

- Pb-free/Halogen-free/RoHS and WEEE compliant package

## **Applications**

Next Generation 3D / 2D HFR HDTV and 2K D-Cinema, UHDTV1 and 4K D-Cinema end-equipment: Cameras, Monitors, Switchers, etc.

Next Generation 3G, 6G, and 12G UHD-SDI infrastructures designed in support of UHDTV1, UHDTV2, 4K D-Cinema and 3D HFR and HDR production image formats.

## **Description**

The GS12141 is a low-power, multi-rate re-timing Cable Equalizer supporting rates up to 12G UHD-SDI. It is designed to equalize and restore signals received over 70m coaxial cable at 12G, compensate for DC content of SMPTE pathological signals, and re-time the incoming data. The device supports SMPTE ST 2082-1 (12G UHD-SDI), ST 2081-1 (6G UHD-SDI), ST 424 (3G SDI), ST 292-1 (HD-SDI), and ST 259 (SD-SDI) signals and is optimized for performance at 11.88Gb/s. In addition to standard SMPTE rates, the device also supports re-timing of DVB-ASI at 270Mb/s, and MADI at 125Mb/s.

The two trace drivers have highly configurable pre-emphasis and swing controls to compensate for long trace and connector losses.

Since the GS12141 is a re-timing equalizer, extremely low output jitter is achievable even at extended cable lengths. Typical jitter performance versus cable length is as follows:

- 70m at 11.88Gb/s: <0.2Ul output jitter

- 90m at 5.94Gb/s: <0.15Ul output jitter

- 180m at 2.97Gb/s: <0.1Ul output jitter

- 240m at 1.485Gb/s: <0.1Ul output jitter

- 400m at 270Mb/s: <0.1Ul output jitter

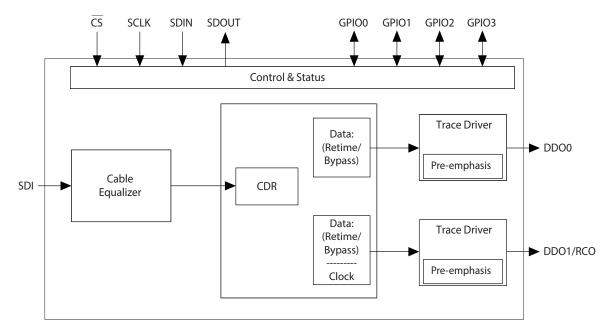

**GS12141 Functional Block Diagram**

# **Revision History**

| Version | ECO    | PCN | Date           | Changes and/or Modifications                                                                                 |

|---------|--------|-----|----------------|--------------------------------------------------------------------------------------------------------------|

| 8       | 041683 | _   | June 2018      | Updated environmental declaration and Table 7-2: Ordering Information.                                       |

| 7       | 033520 | _   | October 2016   | PLL_LOOP_ BANDWIDTH_ SD_MADI had CFG_PLL_LBW_SD parameter's reset value updated from "8" to "1C".            |

| 6       | 033432 | _   | September 2016 | Removed External Reference Clock section. Updated schematic and block diagrams.                              |

| 5       | 032340 | _   | July 2016      | Minor formatting updates performed throughout document.                                                      |

| 4       | 030855 | _   | June 2016      | Updated from Draft to Preliminary Data Sheet.                                                                |

| 3       | 028156 | _   | October 2015   | Correction to document referenced in Section 5. Updated Figure 4-6 and Figure 4-7. Minor updates throughout. |

| 2       | 026806 | _   | July 2015      | Removed all references to Eye Monitor and PRBS Generator/Checker throughout document.                        |

| 1       | 025089 | _   | May 2015       | Many changes throughout document.                                                                            |

| 0       | 022342 | _   | February 2015  | New Document.                                                                                                |

## **Contents**

| 1. Pin Out                                                | 5  |

|-----------------------------------------------------------|----|

| 1.1 GS12141 Pin Assignment                                | 5  |

| 1.2 GS12141 Pin Descriptions                              | 5  |

| 2. Electrical Characteristics                             | 8  |

| 2.1 Absolute Maximum Ratings                              | 8  |

| 2.2 DC Electrical Characteristics                         | 9  |

| 2.3 AC Electrical Characteristics                         | 12 |

| 3. Input/Output Circuits                                  | 14 |

| 4. Detailed Description                                   | 15 |

| 4.1 Cable Equalizer                                       | 15 |

| 4.1.1 Cable Equalizer Bypass                              | 15 |

| 4.1.2 Upstream Launch Swing Compensation                  | 15 |

| 4.1.3 Carrier Detect, Squelch Control, and Loss of Signal | 16 |

| 4.1.4 Equalizer Control and Status Parameters Summary     | 17 |

| 4.2 Serial Digital Re-timer (CDR)                         | 18 |

| 4.2.1 PLL Loop Bandwidth Control                          | 18 |

| 4.2.2 Automatic and Manual Rate Detection                 | 18 |

| 4.2.3 Lock Time                                           |    |

| 4.3 Output Trace Drivers                                  |    |

| 4.3.1 Bypassed Re-timer Signal Output Control             | 21 |

|                                                           |    |

| 4.3.2 Clock Out on DDO1                  | 21 |

|------------------------------------------|----|

| 4.3.3 Amplitude and Pre-emphasis Control | 21 |

| 4.3.4 Output Waveform Specifications     | 26 |

| 4.3.5 Output State Control Modes         | 27 |

| 4.4 GPIO Controls                        | 30 |

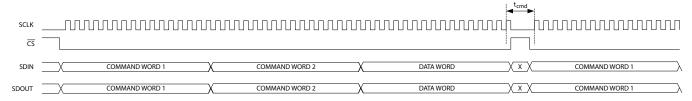

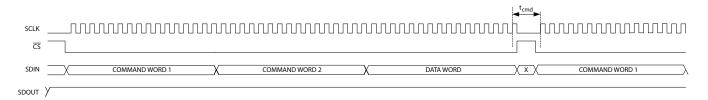

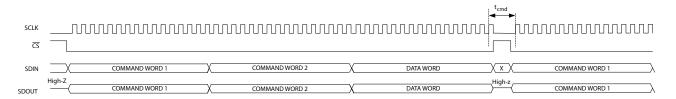

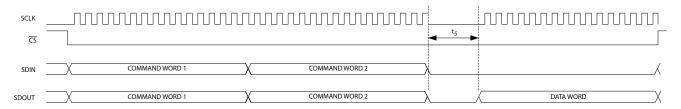

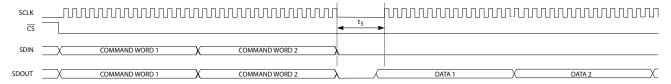

| 4.5 GSPI Host Interface                  | 30 |

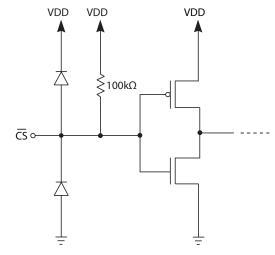

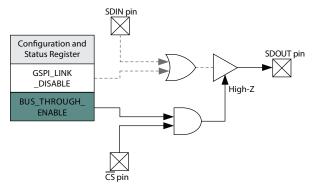

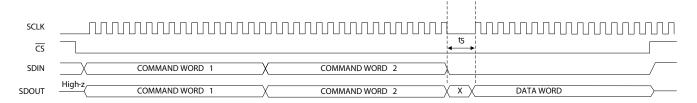

| 4.5.1 CS Pin                             | 31 |

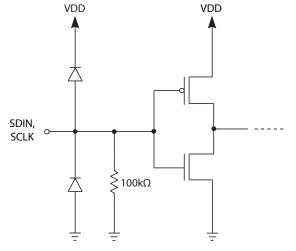

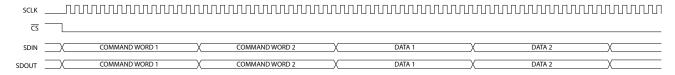

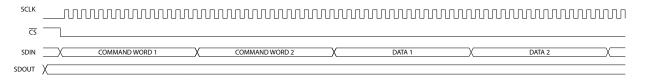

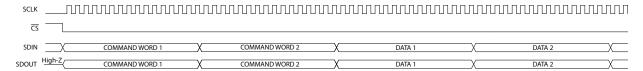

| 4.5.2 SDIN Pin                           | 31 |

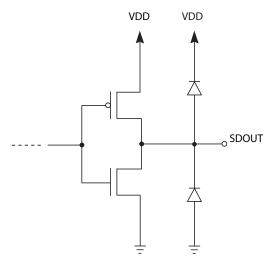

| 4.5.3 SDOUT Pin                          | 31 |

| 4.5.4 SCLK Pin                           | 33 |

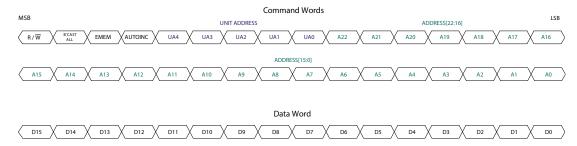

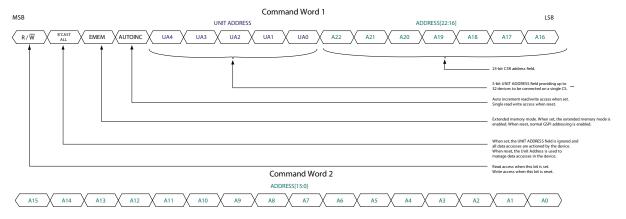

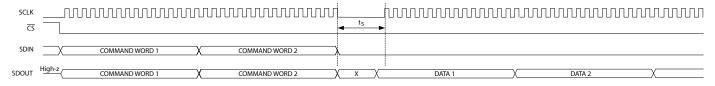

| 4.5.5 Command Word 1 Description         | 33 |

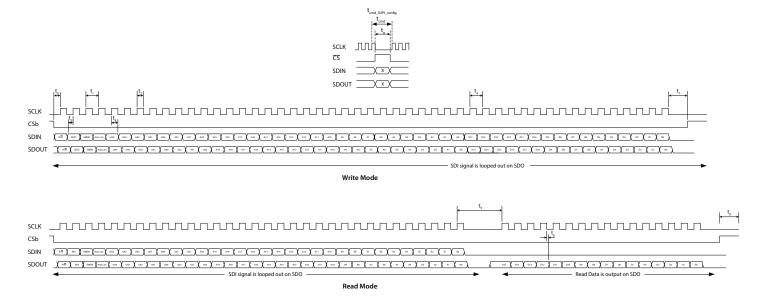

| 4.5.6 GSPI Transaction Timing            | 35 |

| 4.5.7 Single Read/Write Access           | 37 |

| 4.5.8 Auto-increment Read/Write Access   | 38 |

| 4.5.9 Setting a Device Unit Address      | 39 |

| 4.5.10 Default GSPI Operation            | 40 |

| 5. Register Map                          | 42 |

| 5.1 Control Registers                    | 42 |

| 5.2 Status Registers                     | 44 |

| 5.3 Register Descriptions                | 44 |

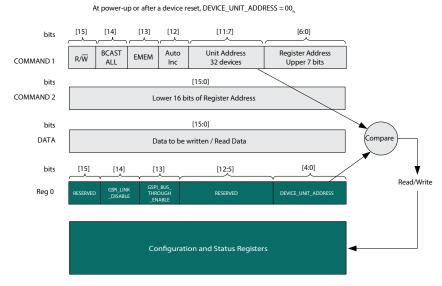

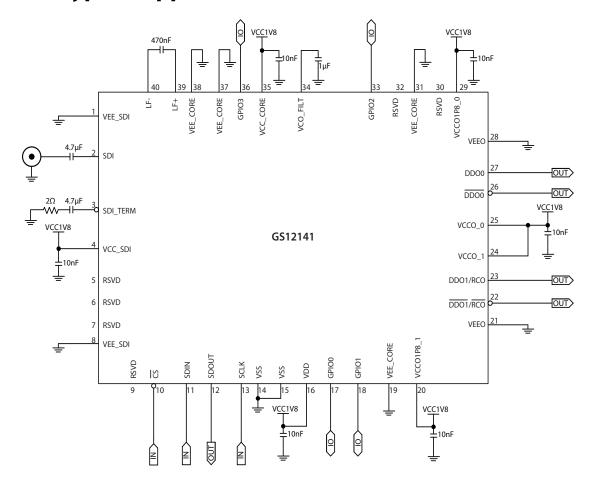

| 6. Application Information               | 61 |

| 6.1 Typical Application Circuit          | 61 |

| 7. Package & Ordering Information        | 62 |

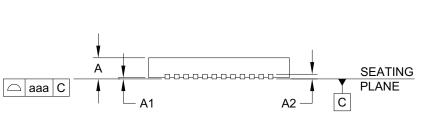

| 7.1 Package Dimensions                   | 62 |

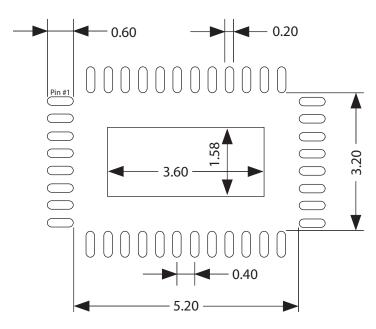

| 7.2 Recommended PCB Footprint            | 63 |

| 7.3 Packaging Data                       | 63 |

| 7.4 Marking Diagram                      | 64 |

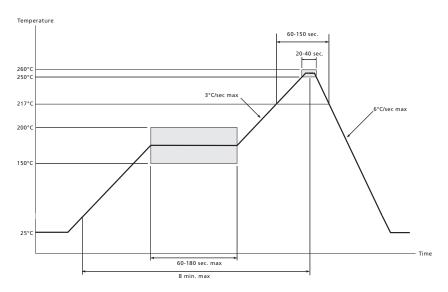

| 7.5 Solder Reflow Profiles               | 64 |

| 7.6 Ordering Information                 | 64 |

# 1. Pin Out

# 1.1 GS12141 Pin Assignment

Figure 1-1: GS12141 Pin Assignment

# 1.2 GS12141 Pin Descriptions

**Table 1-1: GS12141 Pin Descriptions**

| Pin Number | Name     | Туре  | Description                                                                                    |

|------------|----------|-------|------------------------------------------------------------------------------------------------|

| 1, 8       | VEE_SDI  | Power | Most negative power supply connection for the Cable Equalizer.  Connect to GND.                |

| 2          | SDI      | Input | Single-ended CML input with internal 75 $\Omega$ termination on SDI.                           |

| 3          | SDI_TERM | _     | Input Common Mode termination. Decouple to GND through $2\Omega$ resistor and 4.7uF capacitor. |

| 4          | VCC_SDI  | Power | Most positive power supply connection for the Cable Equalizer.  Connect to 1.8V.               |

**Table 1-1: GS12141 Pin Descriptions (Continued)**

| Pin Number         | Name                                 | Туре                    | Description                                                                                                                                        |

|--------------------|--------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 6, 7, 9, 30, 32 | RSVD                                 | _                       | These pins may be left floating or connected to GND. Contact FAE for additional information on circuit compatibility with the GS12241 and GS12242. |

|                    |                                      |                         | Chip Select input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                                      |

| 10                 | <u>CS</u>                            | Digital Input           | 1.8V CMOS input with 100kΩ pull-up.                                                                                                                |

|                    |                                      |                         | Active-LOW input.  Refer to Section 4.5.1 for more details.                                                                                        |

|                    |                                      |                         |                                                                                                                                                    |

|                    |                                      |                         | Serial digital data input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                              |

| 11                 | SDIN                                 | Digital Input           | 1.8V CMOS input with 100kΩ pull-down.                                                                                                              |

|                    |                                      |                         | Refer to Section 4.5.2 for more details.                                                                                                           |

|                    |                                      |                         | Serial digital data output for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                             |

| 12                 | SDOUT                                | Digital Output          | 1.8V CMOS output.                                                                                                                                  |

|                    |                                      |                         | Active-HIGH output.                                                                                                                                |

|                    |                                      |                         | Refer to Section 4.5.3 for more details.                                                                                                           |

|                    | 55114                                | Digital Input           | Burst-mode clock input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                                 |

| 13                 | 13 SCLK                              |                         | 1.8V CMOS input with $100k\Omega$ pull-down.                                                                                                       |

|                    |                                      |                         | Refer to Section 4.5.4 for more details.                                                                                                           |

| 14, 15             | VSS                                  | Power                   | Most negative power supply for digital core logic.                                                                                                 |

| 11,13              | V 33                                 | rower                   | Connect to GND.                                                                                                                                    |

| 16                 | VDD                                  | Power                   | Most positive power supply connection for digital core logic.  Connect to 1.8V.                                                                    |

|                    |                                      |                         | Multi-function Control/Status Input/Output 0.                                                                                                      |

| 17                 | GPIO0                                | Digital<br>Input/Output | Default function: Direction = Output<br>Signal = High indicates LOS (Loss of Signal, inverse of Carrier Detect)                                    |

|                    |                                      | pas, caspas             | Pin is 1.8V CMOS I/O, please refer to GPIOO_CFG for more information on how to configure GPIOO.                                                    |

|                    |                                      |                         | Multi-function Control/Status Input/Output 1.                                                                                                      |

| 18                 | GPIO1                                | Digital<br>Input/Output | Default function: Direction = Output<br>Signal = High indicates PLL is locked                                                                      |

|                    |                                      | mpad output             | Pin is 1.8V CMOS I/O, please refer to GPIO1_CFG for more information on how to configure GPIO1.                                                    |

| 19, 31, 37, 38     | VEE_CORE                             | Power                   | Most negative power supply connection for the analog core. Connect to GND.                                                                         |

| 20, 29, 35         | VCC_CORE,<br>VCCO1P8_0,<br>VCCO1P8_1 | Power                   | Most positive power supply connection for the analog core. Connect to 1.8V.                                                                        |

**Table 1-1: GS12141 Pin Descriptions (Continued)**

| Pin Number | Name                  | Туре                    | Description                                                                                                                                                                                                                                                               |

|------------|-----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21, 28     | VEEO                  | Power                   | Most negative power supply connection for the output drivers.  Connect to GND.                                                                                                                                                                                            |

| 22, 23     | DDO1/RCO,<br>DDO1/RCO | Output                  | Second differential output or differential clock output divided by 2. Differential CML output with two internal $50\Omega$ pull-ups. If both outputs are unused, they can be left floating and disabled through the host interface.                                       |

| 24         | VCCO_1                | Power                   | Most positive power supply connection for the DDO1/RCO/DDO1/RCO output driver.  Connect to 1.2V – 2.5V.                                                                                                                                                                   |

| 25         | VCCO_0                | Power                   | Most positive power supply connection for the DDO0/ $\overline{DDO0}$ output driver.  Connect to 1.2V – 2.5V.                                                                                                                                                             |

| 26, 27     | DDO0, DDO0            | Output                  | Differential serial digital outputs. Differential CML output with two internal $50\Omega$ pull-ups. If both outputs are unused, they can be left floating and disabled through the host interface.                                                                        |

| 33         | GPIO2                 | Digital<br>Input/Output | Multi-function Control/Status Input/Output 2.  Note: The default signal option is not active on this version of the device, but will be Sleep control on future devices.  Pin is 1.8V CMOS I/O, please refer to GPIO2_CFG for more information on how to configure GPIO2. |

| 34         | VCO_FILT              | Passive                 | VCO filter capacitor connection. Decouple to ground through 1uF capacitor.                                                                                                                                                                                                |

| 36         | GPIO3                 | Digital<br>Input/Output | Multi-function Control/Status Input/Output 3.  Default function: Direction = Input Signal = Set high to disable DDO1  Pin is 1.8V CMOS I/O, please refer to GPIO3_CFG for more information on how to configure GPIO3.                                                     |

| 39         | LF+                   | Passive                 | Loop filter capacitor connection. Connect to pin 40 through 470nF capacitor.                                                                                                                                                                                              |

| 40         | LF-                   | Passive                 | Loop filter capacitor connection. Connect to pin 39 through 470nF capacitor.                                                                                                                                                                                              |

| Tab        | _                     | _                       | Central paddle can be connected to ground or left unconnected. Its purpose is to provide increased mechanical stability. It is not required for thermal dissipation.                                                                                                      |

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                                    | Value                    |

|--------------------------------------------------------------|--------------------------|

| Supply Voltage - Core (VCC_SDI, VCC_CORE, VDD)               | -0.5V to +2.2V           |

| Supply Voltage - Output Driver (VCCO_0, VCCO_1)              | -0.5V to +2.8V           |

| Input ESD Voltage (any pin)                                  | 2kV HBM                  |

| Storage Temperature Range (T <sub>S</sub> )                  | -50°C to +125°C          |

| Input Voltage Range (SDI, SDI)                               | -0.3 to (VCC_SDI +0.3)V  |

| Input Voltage Range (GPIO2, GPIO3)                           | -0.3 to (VCC_CORE +0.3)V |

| Input Voltage Range (CS, SDIN, SCLK, VSS, VDD, GPIO0, GPIO1) | -0.3 to (VDD +0.3)V      |

| Solder Reflow Temperature                                    | 260°C                    |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC/DC electrical characteristics tables is not guaranteed.

# 2.2 DC Electrical Characteristics

**Table 2-2: DC Electrical Characteristics**

$VCC\_SDI, VCC\_CORE, VDD, VCCO\_0, VCCO\_1, VCCO\_1 = +1.8V \pm 5\%, T_A = -40^{\circ}C \ to \ +85^{\circ}C, \ unless \ otherwise \ shown.$

| Parameter                         | Symbol                       | Conditions                                                                                                               | Min                                                                                                                                                               | Тур | Max  | Units    | Notes |

|-----------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|-------|

| Supply Voltage                    | VCC_SDI,<br>VCC_CORE,<br>VDD |                                                                                                                          | 1.71                                                                                                                                                              | 1.8 | 1.89 | V        | _     |

|                                   |                              |                                                                                                                          | 1.14                                                                                                                                                              | 1.2 | 1.26 | V        | _     |

| Supply Voltage - Output<br>Driver | VCCO_0,<br>VCCO_1            |                                                                                                                          | 1.71                                                                                                                                                              | 1.8 | 1.89 | V        | _     |

|                                   | _                            |                                                                                                                          | 1.71 1.8 1.89 V  1.14 1.2 1.26 V  1.71 1.8 1.89 V  2.38 2.5 2.63 V  2.9pdr — 348 — mW  2.ppdr — 373 — mW  2.ppdr — 362 — mW  2.ppdr — 387 — mW  2.ppdr — 398 — mW | _   |      |          |       |

|                                   |                              | VCCO = 1.2V, Output Swing = 400mV <sub>ppd</sub> , DDO0/DDO0 enabled, DDO1/DDO1 disabled                                 | _                                                                                                                                                                 | 348 | _    | mW       | 1     |

|                                   |                              | VCCO = 1.8V, Output Swing = 400mV <sub>ppd</sub> , DDO0/DDO0 enabled, DDO1/DDO1 disabled                                 | _                                                                                                                                                                 | 355 | _    | mW       | 1     |

|                                   |                              | VCCO = 1.8V, Output Swing = 800mV <sub>ppd</sub> , DDO0/DDO0 enabled, DDO1/DDO1 disabled                                 | _                                                                                                                                                                 | 373 | _    | mW       | 1     |

| D.                                |                              | VCCO = 2.5V, Output Swing = 400mV <sub>ppd</sub> , DDO0/DDO0 enabled, DDO1/DDO1 disabled                                 | _                                                                                                                                                                 | 362 | _    | mW       | 1     |

| Power                             | P <sub>D</sub>               | VCCO = 2.5V, Output Swing = 800mV <sub>ppd</sub> , DDO0/DDO0 enabled, DDO1/DDO1 disabled                                 | _                                                                                                                                                                 | 387 | _    | mW<br>mW | 1     |

|                                   |                              | VCCO = 1.2V, Output Swing = 400mV <sub>ppd</sub> , DDO0/DDO0 and DDO1/DDO1 enabled                                       | _                                                                                                                                                                 | 398 | _    | mW       | 1     |

|                                   |                              | VCCO = 1.8V, Output Swing = 400mV <sub>ppd</sub> , DDO0/DDO0 and DDO1/DDO1 enabled                                       | _                                                                                                                                                                 | 410 | _    | mW       | 1     |

|                                   |                              | VCCO = 1.8V,<br>Output Swing = $800 \text{mV}_{ppd}$ ,<br>DD00/ $\overline{DD00}$ and<br>DD01/ $\overline{DD01}$ enabled | _                                                                                                                                                                 | 446 | _    | mW       | 1     |

## **Table 2-2: DC Electrical Characteristics (Continued)**

$VCC\_SDI, VCC\_CORE, VDD, VCCO\_0, VCCO\_1, VCCO\_1 = +1.8V \pm 5\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise shown.}$

| Parameter                            | Symbol                                  | Conditions                                                                                                               | Min          | Тур                                      | Max          | Units                                           | Notes |

|--------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------|--------------|-------------------------------------------------|-------|

|                                      |                                         | VCCO = 2.5V,<br>Output Swing = $400 \text{mV}_{ppd}$ ,<br>DDO0/ $\overline{DDO0}$ and<br>DDO1/ $\overline{DDO1}$ enabled | _            | 424                                      | _            | mW                                              | 1     |

| Power                                | P <sub>D</sub>                          | VCCO = 2.5V,<br>Output Swing = $800 \text{mV}_{ppd}$ ,<br>DDO0/ $\overline{DDO0}$ and<br>DDO1/ $\overline{DDO1}$ enabled | _            | 474                                      | _            | mW                                              | 1     |

|                                      |                                         | DDO0/DDO0 and<br>DDO1/DDO1 disabled                                                                                      | _            | 214                                      | _            | mW                                              | _     |

|                                      |                                         | VCCO = 1.2V,<br>Output Swing = 400mV <sub>ppd</sub> ,                                                                    | _            | 10                                       | 16           | mA                                              | 1     |

|                                      |                                         | VCCO = 1.8V,<br>Output Swing = 400mV <sub>ppd</sub> ,                                                                    | _            | 10                                       | 16           | mA                                              | 1     |

| Supply Current - Trace Driver        | I <sub>CCO_0</sub> , I <sub>CCO_1</sub> | VCCO = 1.8V,<br>Output Swing = 800mV <sub>ppd</sub> ,                                                                    | _            | 20                                       | 30           | mW mW mM mA | 1     |

|                                      |                                         | VCCO = 2.5V,<br>Output Swing = 400mV <sub>ppd</sub> ,                                                                    | _            | 10                                       | 16           |                                                 | 1     |

|                                      |                                         | VCCO = 2.5V,<br>Output Swing = 800mV <sub>ppd</sub> ,                                                                    | _            | 20                                       | 30           |                                                 | 1     |

|                                      | I <sub>CC_CORE</sub>                    | DDO0/DDO0 and<br>DDO1/DDO1 disabled                                                                                      | _            | 106                                      | 123          | mA                                              | _     |

| Supply Current – Analog<br>Core      |                                         | DDO0/DDO0 enabled and DDO1/DDO1 disabled                                                                                 | _            | 127                                      | 151          | mA                                              | _     |

|                                      |                                         | DDO0/DDO0 and<br>DDO1/DDO1 enabled                                                                                       | _            | 148                                      | 173          | mA                                              | _     |

| Supply Current - Cable<br>Equalizer  | I <sub>CC_SDI</sub>                     |                                                                                                                          | _            | 45                                       | 58           | mA                                              | _     |

| Supply Current - Digital Logic       | I <sub>DD</sub>                         |                                                                                                                          | _            | 15                                       | 17           | mA                                              | _     |

| Serial Input Common<br>Mode Voltage  | V <sub>CMIN</sub>                       |                                                                                                                          | 1.4          | _                                        | 1.6          | V                                               | _     |

| Serial Output Common<br>Mode Voltage | V <sub>CMOUT</sub>                      |                                                                                                                          | _            | $V_{CMOUT} = V_{CCO} - \Delta V_{DDO}/2$ | _            | _                                               | _     |

| Serial Output Termination            |                                         | Differential                                                                                                             | _            | 100                                      | _            | Ω                                               | _     |

| Serial Input Termination             |                                         | Between SDI and SDI pins                                                                                                 | _            | 75                                       | _            | Ω                                               | _     |

| Input Voltage - Digital Pins         | V <sub>IH</sub>                         |                                                                                                                          | 0.65*<br>VDD | _                                        | VDD          | V                                               |       |

| (CS, SDIN, SCLK, GPIO[0:3])          | V <sub>IL</sub>                         |                                                                                                                          | 0            | _                                        | 0.35*<br>VDD | V                                               | _     |

## **Table 2-2: DC Electrical Characteristics (Continued)**

$VCC\_SDI, VCC\_CORE, VDD, VCCO\_0, VCCO\_1, VCCO\_1 = +1.8V \pm 5\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise shown.}$

| Parameter                                           | Symbol   | Conditions      | Min           | Тур | Max  | Units | Notes |

|-----------------------------------------------------|----------|-----------------|---------------|-----|------|-------|-------|

| Output Voltage - Digital Pins<br>(SDOUT, GPIO[0:3]) | $V_{OH}$ | $I_{OH} = -5mA$ | VDD -<br>0.45 | _   | _    | V     | _     |

|                                                     | $V_{OL}$ | $I_{OL} = +5mA$ | _             | _   | 0.45 | V     | _     |

#### Notes:

<sup>1.</sup> Pre-emphasis is disabled.

# 2.3 AC Electrical Characteristics

**Table 2-3: AC Electrical Characteristics**

$VCC\_SDI, VCC\_CORE, VDD, VCCO\_0, VCCO\_1, VCCO\_1, VCCO\_1 = +1.8V \pm 5\%, T_A = -40^{\circ}C \ to \ +85^{\circ}C, unless \ otherwise \ shown.$

| Parameter                                                                                                                                                                                                                                                                                                                                                                        | Symbol             | Conditions                                            | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Тур  | Max   | Units                                                                                                                                                                                     | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Serial Input Data Rate                                                                                                                                                                                                                                                                                                                                                           | DR <sub>SDI</sub>  | _                                                     | 0.001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _    | 11.88 | Gb/s                                                                                                                                                                                      | _     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 1.485Gb/s                                             | 720                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 800  | 960   | mV <sub>ppd</sub>                                                                                                                                                                         | _     |

| Upstream Launch Swing                                                                                                                                                                                                                                                                                                                                                            | $\Delta V_{SDI}$   | 270Mb/s, 270Mb/s,<br>2.97Gb/s, 5.94Gb/s,<br>11.88Gb/s | 720                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 800  | 880   | mV <sub>ppd</sub>                                                                                                                                                                         | 4     |

| Output Voltage Swing                                                                                                                                                                                                                                                                                                                                                             | $\Delta V_{DDO}$   |                                                       | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _    | 800   | $mV_{ppd}$                                                                                                                                                                                | _     |

| Tutput Voltage Swing $\Delta V_{DDO}$ Intrinsic Input Jitter Tolerance IIJT  LL Lock Time – Asynchronous $t_{ALOCK}$ LL Lock Time – Synchronous $t_{SLOCK}$ DO0, $\overline{DD00}$ , DD01/RCO, $\overline{D001/RCO}$ Rise/Fall Time $t_{fallDD01/RCO}$ Dismatch in Rise/Fall Time $t_{fallDD01/RCO}$ DO00, $\overline{DD00}$ , DD01/RCO, DD01/RCO, $\overline{DD00}$ , DD01/RCO, | 12G                | 0.7                                                   | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _    | UI    | 5                                                                                                                                                                                         |       |

| intrinsic input sitter folerance                                                                                                                                                                                                                                                                                                                                                 | 11011              | MADI/SD/HS/3G/6G                                      | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.95 | _     | UI                                                                                                                                                                                        | 5     |

| PLL Lock Time – Asynchronous                                                                                                                                                                                                                                                                                                                                                     | t <sub>ALOCK</sub> |                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75   | _     | ms                                                                                                                                                                                        | 1     |

| DLL Lock Time Synchronous                                                                                                                                                                                                                                                                                                                                                        | t                  | SD                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 10    | μs                                                                                                                                                                                        | _     |

| PLL LOCK Time – Synchronous                                                                                                                                                                                                                                                                                                                                                      | SLOCK              | HD/3G/UHD                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 2     | μs                                                                                                                                                                                        | _     |

| DDO0, DDO0, DDO1/RCO,                                                                                                                                                                                                                                                                                                                                                            | _                  | 20% – 80% rising edge into 50Ω load                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 40    | ps                                                                                                                                                                                        | _     |

| DDO1/RCO Rise/Fall Time                                                                                                                                                                                                                                                                                                                                                          |                    | 20% – 80% falling edge into 50 $\Omega$ load          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 40    | Gb/s  mV <sub>ppd</sub> mV <sub>ppd</sub> mV <sub>ppd</sub> UI  UI  ms  μs  μs                                                                                                            | _     |

| Mismatch in Rise/Fall Time                                                                                                                                                                                                                                                                                                                                                       |                    |                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 5     | ps                                                                                                                                                                                        | _     |

| Duty Cycle Distortion (DDO0, DDO1/RCO, DDO1/RCO)                                                                                                                                                                                                                                                                                                                                 |                    |                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 8     | ps                                                                                                                                                                                        | _     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 5MHz to 1.485GHz                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | -15   | dB                                                                                                                                                                                        | 2     |

| Innut Datum Lace                                                                                                                                                                                                                                                                                                                                                                 |                    | 1.485GHz to 2.97GHz                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | -10   | dB                                                                                                                                                                                        | 2     |

| Input Return Loss                                                                                                                                                                                                                                                                                                                                                                |                    | 2.97GHz to 5.94GHz                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | -7    | dB                                                                                                                                                                                        | 2     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 5.94GHz to 11.88GHz                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | -4    | dB                                                                                                                                                                                        | 2     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 270Mb/s<br>Belden 1694A: 400m                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.04 | 0.2   | mV <sub>ppd</sub> mV <sub>ppd</sub> UI  UI  ms  µs  µs  ps  ps  ps  dB  dB  dB  dB  UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> | 6     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 1.485Gb/s<br>Belden 1694A: 240m                       | Mb/s, 270Mb/s, Gb/s, 5.94Gb/s, 8Gb/s  200 — 800 mV <sub>ppd</sub> 0.7 0.85 — UI  0//SD/HS/3G/6G 0.8 0.95 — UI  — 75 — ms  — — 10 µs  3G/UHD — 2 µs  0-80% rising edge 50Ω load  - — 40 ps  - 80% falling edge 50Ω load  - — 5 ps  — — 8 ps  Hz to 1.485GHz — — -15 dB  GHz to 5.94GHz — — -7 dB  GHz to 11.88GHz — — 4 dB  Mb/s  len 1694A: 400m  Gb/s  Gb/s  len 1694A: 90m  GGb/s  len 1694A: 90m | 3    |       |                                                                                                                                                                                           |       |

| Serial Data Output Jitter                                                                                                                                                                                                                                                                                                                                                        | <b>t</b>           | 2.97Gb/s<br>Belden 1694A: 180m                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.07 | 0.2   | mV <sub>ppd</sub> mV <sub>ppd</sub> UI  UI  ms  µs  µs  ps  ps  ps  dB  dB  dB  dB  UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub> UI <sub>pp</sub>                  | 3     |

| Schar Bata Gatpat Sitter                                                                                                                                                                                                                                                                                                                                                         | t <sub>OJ</sub>    | 5.94Gb/s<br>Belden 1694A: 80m                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.07 | 0.15  | Ul <sub>pp</sub>                                                                                                                                                                          | 3     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    | 5.94Gb/s<br>Belden 1694A: 90m                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.15 | _     | Ul <sub>pp</sub>                                                                                                                                                                          | 3     |

|                                                                                                                                                                                                                                                                                                                                                                                  |                    |                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.2   | Ul <sub>pp</sub>                                                                                                                                                                          | 3     |

## **Table 2-3: AC Electrical Characteristics (Continued)**

$VCC\_SDI, VCC\_CORE, VDD, VCCO\_0, VCCO\_1\_VCCO\_1 = +1.8V \pm 5\%, T_A = -40^{\circ}C \ to \ +85^{\circ}C, \ unless \ otherwise \ shown.$

| Parameter          | Symbol                        | Conditions             | Min | Тур  | Max | Units                                                                                                                                                                                                                                                             | Notes |

|--------------------|-------------------------------|------------------------|-----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                    |                               | Setting 0.0625x        | _   | 5    | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.125x         | _   | 10   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    | BW <sub>LOOP(125Mb/s)</sub>   | Setting 0.25x          | _   | 19   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.5x (Default) | _   | 38   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 1.0x           | _   | 75   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    | <del></del>                   | Setting 0.0625x        | _   | 10   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.125x         | _   | 20   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    | BW <sub>LOOP(270Mb/s)</sub>   | Setting 0.25x          | _   | 40   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.5x           | _   | 80   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 1.0x (Default) | _   | 158  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.0625x        | _   | 55   | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.125x         | _   | 110  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    | BW <sub>LOOP(1.485Gb/s)</sub> | Setting 0.25x          | _   | 220  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.5x (Default) | _   | 438  | _   | kHz                                                                                                                                                                                                                                                               | _     |

| LL Loop Bandwidth  |                               | Setting 1.0x           | _   | 875  | _   | kHz                                                                                                                                                                                                                                                               | _     |

| PLL LOOP Bandwidth |                               | Setting 0.0625x        | _   | 110  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.125x         | _   | 220  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    | BW <sub>LOOP(2.97Gb/s)</sub>  | Setting 0.25x          | _   | 440  | _   | kHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 0.5x (Default) | _   | 0.88 | _   | MHz                                                                                                                                                                                                                                                               | _     |

|                    |                               | Setting 1.0x           | _   | 1.75 | _   | <ul> <li>KHz</li> <li>MHz</li> </ul> | _     |

|                    | ·                             | Setting 0.0625x        | _   | 220  | _   | kHz                                                                                                                                                                                                                                                               | _     |

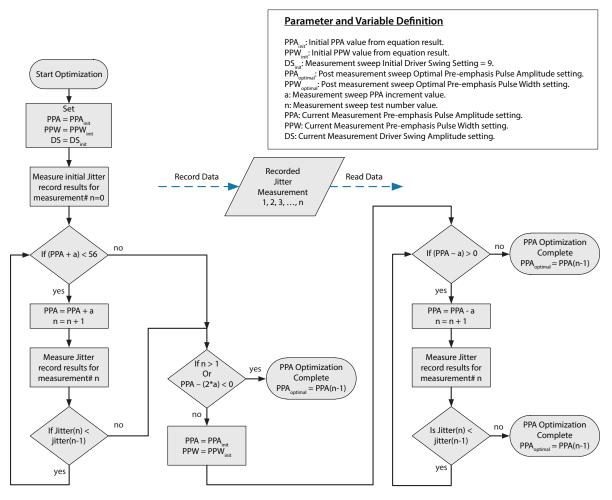

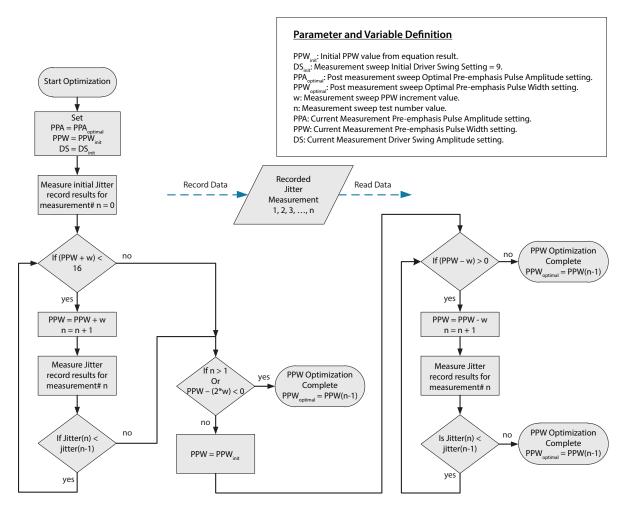

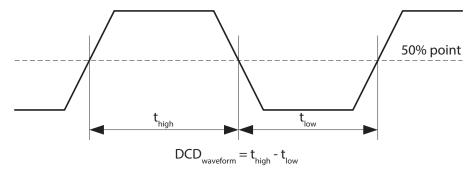

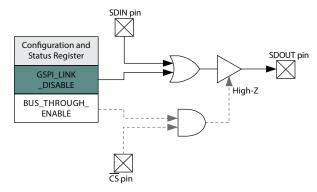

|                    |                               | Setting 0.125x         | _   | 440  | _   | kHz                                                                                                                                                                                                                                                               | _     |