## GX4002 2x2 14.025Gb/s Crosspoint Switch with Trace Equalization and Output De-Emphasis

## **Key Features**

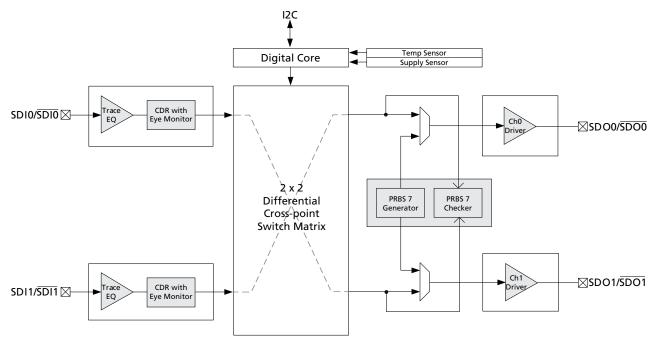

- 2 x 2 crosspoint switch architecture

- Integrated CDR with 9.95 to 11.3Gb/s and 14.025Gb/s reference-free operation

- Automatic rate detect

- Dynamic on-chip power management control

- Multiple user-programmable power-down saving modes

- Independent programmable input trace equalization to reduce deterministic jitter (ISI)

- Independent programmable output pre-emphasis for driving long board traces

- Digital control through I<sup>2</sup>C interface

- Integrated analog-to-digital converter, which provides access to digital diagnostic information on supply voltage and die temperature

- Integrated eye monitor and PRBS7 generator/checker

- Polarity invert, output mute functions available

- Single 3.3V supply (±5%)

- On-chip I/O termination

- Low power consumption: 600mW typical

- Low power option for 4.25 & 8.5Gb/s operation: 415mW typical

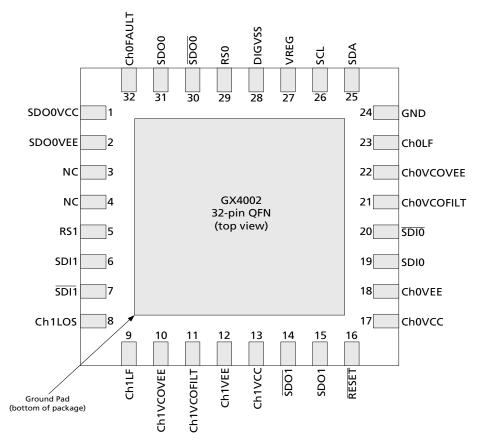

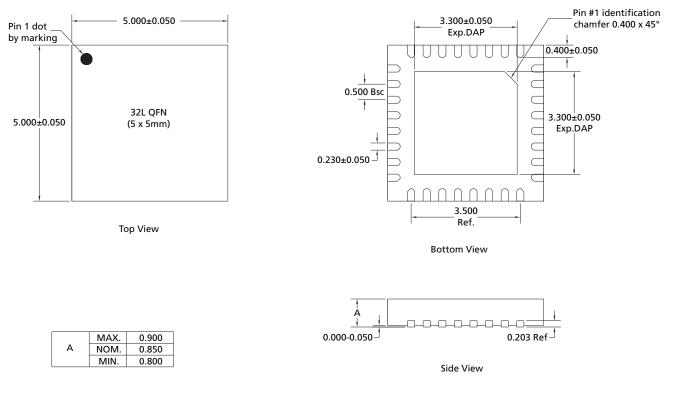

- 5mm x 5mm 32-pin QFN package

- -40°C to +100°C case operation

- RoHS-compliant

## **Applications**

- Enterprise and carrier applications

- 10GbE, Fibre Channel and InfiniBand networks

- Redundancy switching

- Retimer for 10Gb/s and 14Gb/s backplane and linecards

## Description

The GX4002 is a low-power, high-speed 2 x 2 crosspoint switch, with robust signal conditioning circuits for driving and receiving high-speed signals through backplanes.

The device consumes as low as 600mW of power (typical) with all channels operational. Unused portions of the chip can be turned off in order to further reduce power consumption.

The signal conditioning features of the GX4002 include per-input clock and data recovery (CDR), programmable equalization and per-output programmable de-emphasis. The input equalizer removes ISI jitter—typically caused by PCB trace losses—by opening the input data eye in applications where long PCB traces are used. The integrated CDR "resets" the jitter budget, effectively erasing the signal distortion that can occur during transmission.

Output pre-emphasis capability provides a boost of the high-frequency content of the output signal, such that the data eye remains open after passing through a long interconnect of PCB traces and connectors.

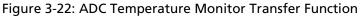

The GX4002 features an integrated analog-to-digital converter, which, through the serial interface, provides digital diagnostic information about supply voltage and die temperature.

The GX4002 device is packaged in a small-outline 5mm × 5mm 32-pin, high-frequency QFN package with exposed pad.

The GX4002 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant. This component and all homogeneous sub components are RoHS-compliant.

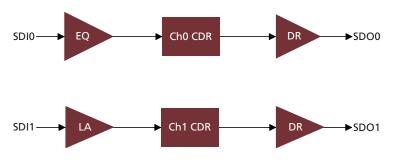

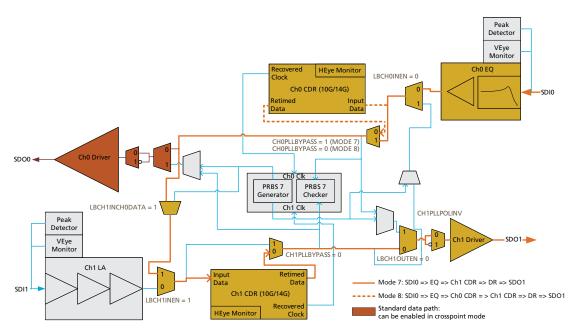

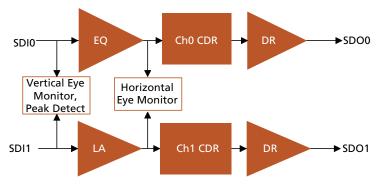

Figure A: GX4002 Functional Block Diagram

# **Revision History**

| Version | ECR    | Date             | Changes and / or Modifications                                                                                                                                                                                                                                                                     |

|---------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 157889 | March 2012       | Ability to propagate loss of lock to Ch0FAULT pin was added.                                                                                                                                                                                                                                       |

| с       | 157185 | November<br>2011 | Converted document to a Data Sheet. Updates<br>throughout. Removed typical temperature<br>monitor accuracy. Removed typical voltage<br>monitor accuracy. Added AC common-mode<br>channel characteristics. Added register 101 bits<br>[5:3] to Table 7-1: Configuration and Status<br>Register Map. |

| В       | 155955 | March 2011       | Correction to pin 21 and 23 in Table 1-1: Pin Descriptions.                                                                                                                                                                                                                                        |

| А       | 155765 | February 2011    | New document.                                                                                                                                                                                                                                                                                      |

## Contents

| Key Features                            | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| 1. Pin Out                              | 5  |

| 1.1 Pin Assignment                      | 5  |

| 1.2 Pin Descriptions                    | 6  |

| 2. Electrical Characteristics           | 8  |

| 2.1 Absolute Maximum Ratings            | 8  |

| 2.2 DC Electrical Characteristics       | 8  |

| 2.2.1 Power Features                    | 9  |

| 2.3 AC Electrical Characteristics       | 10 |

| 2.4 Required Initialization Settings    | 12 |

| 3. Detailed Description                 | 13 |

| 3.1 Multirate CDR Functionality         | 13 |

| 3.1.1 Rate Selection and Rate Detection | 13 |

| 3.1.2 Auto Retimer Bypass               | 16 |

| 3.2 Channel 0 Path (Ch0)                | 17 |

| 3.2.1 Ch0 Equalization                  | 17 |

| 3.2.2 Ch0 PLL Variable Loop Bandwidth   | 18 |

| 3.2.3 Channel 0 Output Polarity Invert  | 18 |

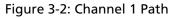

| 3.3 Channel 1 Path (Ch1)                | 19 |

| 3.3.1 Integrated Limiting Amplifier     | 19 |

| 3.3.2 Ch1 Equalization                  | 19 |

| 3.3.3 Ch1 PLL Variable Loop Bandwidth   | 20 |

GX4002 2x2 14.025Gb/s Crosspoint Switch with Trace Equalization and Output De-Emphasis Data Sheet 55972 - 0 March 2012

| 3.3.4 Pre-Emphasis Driver with Auto-Mute             | 21 |

|------------------------------------------------------|----|

| 3.3.5 Channel 1 Output Polarity Invert               | 22 |

| 3.4 Crosspoint                                       | 23 |

| 3.5 Status Indicators                                | 27 |

| 3.5.1 Ch0 Loss Of Signal (LOS)                       | 27 |

| 3.5.2 Ch1 Loss Of Signal                             | 29 |

| 3.5.3 Loss Of Lock (LOL)                             | 32 |

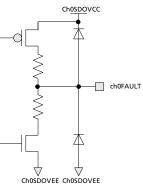

| 3.5.4 Ch0FAULT - Channel 0 Fault                     | 33 |

| 3.6 Test Features                                    | 33 |

| 3.6.1 PRBS Generator and Checker                     | 34 |

| 3.6.2 Eye Monitor & Peak Detector                    | 36 |

| 3.7 Digital Diagnostics                              | 38 |

| 3.7.1 Analog to Digital Converter (ADC)              | 38 |

| 3.8 Power Control Options                            | 48 |

| 3.9 Device Reset                                     | 49 |

| 3.9.1 Reset State During Power-up                    | 49 |

| 3.9.2 RESET Timing                                   | 50 |

| 3.9.3 I/O and Register States During and After Reset | 51 |

| 3.10 Digital Control Interface                       | 51 |

| 3.10.1 I <sup>2</sup> C Host Interface Mode          | 51 |

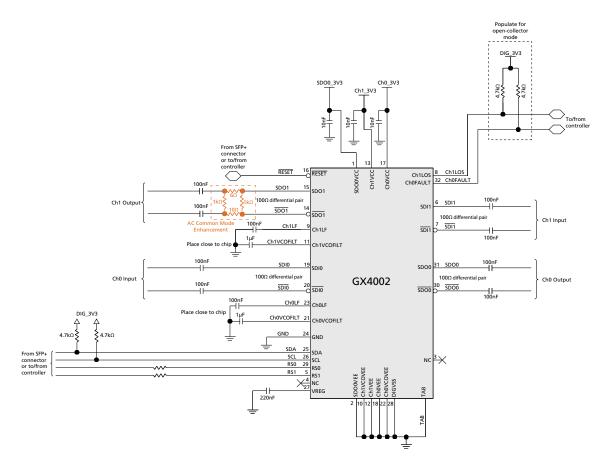

| 4. Typical Application Circuit                       | 53 |

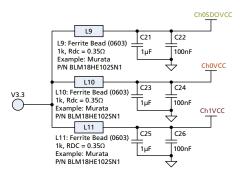

| 4.1 Power Supply Filter Recommendations              | 53 |

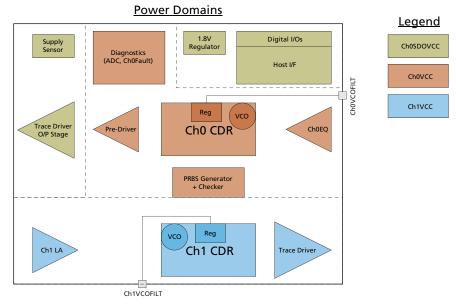

| 4.2 Power Supply Domains                             | 54 |

| 5. Layout Considerations                             | 55 |

| 6. Input/Output Equivalent Circuits                  | 56 |

| 7. Package and Ordering Information                  | 59 |

| 7.1 Package Dimensions                               | 59 |

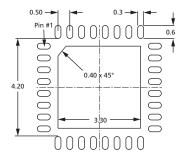

| 7.2 Recommended PCB Footprint                        | 59 |

| 7.3 Packaging Data                                   | 60 |

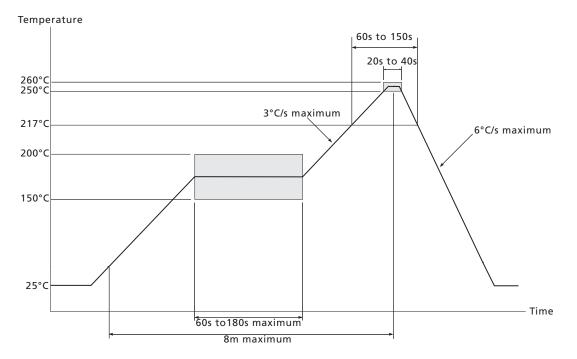

| 7.4 Solder Reflow Profile                            | 60 |

| 7.5 Marking Diagram                                  | 61 |

| 7.6 Ordering Information                             | 61 |

# 1. Pin Out

# **1.1 Pin Assignment**

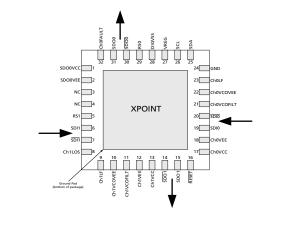

Figure 1-1: GX4002 Pin Assignment

# **1.2 Pin Descriptions**

#### Table 1-1: Pin Descriptions

| Pin #  | Name              | Туре                        | Description                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SDO0VCC           | Power                       | Power supply for channel 0 path output.                                                                                                                                                                                                                                                                                                                                       |

| 2      | <b>SDO0VEE</b>    | Ground                      | Ground for channel 0 path output.                                                                                                                                                                                                                                                                                                                                             |

| 3, 4   | NC                | _                           | No connect.                                                                                                                                                                                                                                                                                                                                                                   |

| 5      | RS1               | Digital<br>Input            | Input Digital LVTTL/LVCMOS-compliant input.<br>Rate Select Input for the Ch1 Signal Path.<br>See Section 3.1 Multirate CDR Functionality for more details.                                                                                                                                                                                                                    |

| 6, 7   | SDI1, SDI1        | Input                       | High-speed input for the channel 1 signal path.                                                                                                                                                                                                                                                                                                                               |

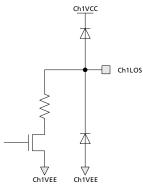

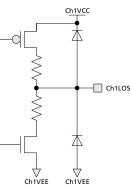

| 8      | Ch1LO5            | Digital<br>Output           | SFP+-compliant active-high digital output. Open-collector Loss-Of-Signal indicator for<br>the channel 1 signal path. Requires an external pull-up resistor.<br>When Ch1LOS is LOW, a valid channel 1 input signal has been detected.<br>When Ch1LOS is high-impedance, a valid channel 1 input signal has not been detected<br>Configurable as LVTTL/LVCMOS-compliant output. |

| 9      | Ch1LF             | Passive                     | Loop filter capacitor connection for the channel 1 signal path.                                                                                                                                                                                                                                                                                                               |

| 10     | Ch1VCOVEE         | Ground                      | Ground for the channel 1 signal path VCO.                                                                                                                                                                                                                                                                                                                                     |

| 11     | Ch1VCOFILT        | Passive                     | Filter for the channel 1 signal path VCO supply.                                                                                                                                                                                                                                                                                                                              |

| 12     | Ch1VEE            | Ground                      | Ground for the channel 1 signal path and output.                                                                                                                                                                                                                                                                                                                              |

| 13     | Ch1VCC            | Power                       | Power supply for the channel 1 signal path and output.                                                                                                                                                                                                                                                                                                                        |

| 14, 15 | SDO1,<br>SDO1     | Output                      | High-speed differential output for the channel 1 signal path.                                                                                                                                                                                                                                                                                                                 |

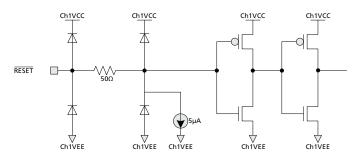

| 16     | RESET             | Digital<br>Input            | Digital active-low LVTTL/LVCMOS-compliant Schmitt-trigger input.<br>Device reset control pin.<br>Includes an internal pull-down resistor to hold the device in a reset state during<br>power-up, should this pin be externally disconnected.                                                                                                                                  |

| 17     | Ch0VCC            | Power                       | Power supply for the channel 0 signal path.                                                                                                                                                                                                                                                                                                                                   |

| 18     | Ch0VEE            | Ground                      | Ground for the channel 0 signal path.                                                                                                                                                                                                                                                                                                                                         |

| 19, 20 | SDIO, <u>SDIO</u> | Input                       | High-speed input for the channel 0 signal path.                                                                                                                                                                                                                                                                                                                               |

| 21     | Ch0VCOFILT        | Passive                     | Filter for the channel 0 signal path VCO supply.                                                                                                                                                                                                                                                                                                                              |

| 22     | Ch0VCOVEE         | Ground                      | Ground for the channel 0 signal path VCO.                                                                                                                                                                                                                                                                                                                                     |

| 23     | Ch0LF             | Passive                     | Loop filter capacitor connection for the Ch0 signal path.                                                                                                                                                                                                                                                                                                                     |

| 24     | GND               | Ground                      | Connect to GND.                                                                                                                                                                                                                                                                                                                                                               |

| 25     | SDA               | Digital<br>Input/<br>Output | Digital active-high serial data signal for the host interface.<br>Bi-directional, I <sup>2</sup> C-compliant, open-drain driver/receiver.                                                                                                                                                                                                                                     |

| 26     | SCL               | Digital<br>Input            | Digital active-high clock input signal for the serial host interface.                                                                                                                                                                                                                                                                                                         |

GX4002 2x2 14.025Gb/s Crosspoint Switch with Trace Equalization and Output De-Emphasis Data Sheet 55972 - 0 March 2012

## Table 1-1: Pin Descriptions (Continued)

| Pin #  | Name                 | Туре    | Description                                                                                                          |

|--------|----------------------|---------|----------------------------------------------------------------------------------------------------------------------|

| 27     | VREG                 | Passive | LDO regulator capacitor connection. (1.8V)                                                                           |

| 28     | DIGVSS               | Ground  | Ground for low-speed digital I/O and internal logic.                                                                 |

|        |                      | Digital | Input Digital LVTTL/LVCMOS-compliant input.                                                                          |

| 29     | 29 RS0               | Input   | Rate Select Input for the Ch0 Signal Path.                                                                           |

|        | ···P                 |         | See Section 3.1 Multirate CDR Functionality for more details.                                                        |

| 30, 31 | <u>SDO0,</u><br>SDO0 | Output  | High-speed differential output for the channel 0 signal path.                                                        |

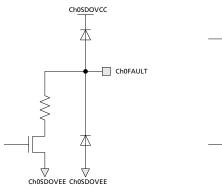

|        |                      |         | SFP+-compliant active-high digital output. Open-collector Ch0FAULT indicator. Requires an external pull-up resistor. |

|        |                      |         | When Ch0FAULT is LOW, the channel 0 path output is operating properly.                                               |

| 32     | Ch0FAULT             | Digital | When Ch0FAULT is high-impedance, the device has detected a fault condition.                                          |

|        |                      | Output  | The Ch0FAULT is latched, and may be cleared via the host interface or by strobing the Ch0DSBL pin.                   |

|        |                      |         | Can be configured as a LVTTL/LVCMOS compatible output.                                                               |

# **2. Electrical Characteristics**

## 2.1 Absolute Maximum Ratings

| Parameter                           | Value                          |

|-------------------------------------|--------------------------------|

| Supply Voltage                      | -0.5 to +3.8V <sub>DC</sub>    |

| Input ESD Voltage                   | 2kV                            |

| Storage Temperature Range           | -50°C < T <sub>A</sub> < 125°C |

| Input Voltage Range (any input pin) | -0.3 to 3.8V <sub>DC</sub> *   |

| Solder Reflow Temperature           | 260°C                          |

**\*NOTE:** Stress above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not applied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 2.2 DC Electrical Characteristics

#### **Table 2-1: DC Electrical Characteristics**

$V_{CC}$  = +2.8V to +3.47V,  $T_C$  = -40°C to 100°C. Typical values are  $V_{CC}$  = +3.3V and  $T_A$  = 25°C, unless otherwise specified. Specifications assume default setting to end-terminated 50 $\Omega$  transmission lines, unless otherwise stated. Typical Data Rate = 14.025Gb/s Note: mApp refers to mA peak-to-peak value.

| Parameter                              | Conditions                                        | Symbol          | Min | Тур  | Max             | Units | Notes |  |

|----------------------------------------|---------------------------------------------------|-----------------|-----|------|-----------------|-------|-------|--|

| Supply Voltage                         |                                                   | V <sub>CC</sub> | 2.8 | 3.3  | 3.47            | V     | _     |  |

| Power                                  |                                                   |                 | _   | 600  | 800             | mW    | 1, 2  |  |

| Control Logic Input Specifications     |                                                   |                 |     |      |                 |       |       |  |

| Input Low Voltage                      |                                                   | V <sub>IL</sub> | 0   |      | 0.4             | V     | _     |  |

| Input High Voltage                     |                                                   | V <sub>IH</sub> | 2.0 | _    | V <sub>CC</sub> | V     | _     |  |

| Input Low Current                      | V <sub>IL</sub> = 0V                              | I <sub>IL</sub> | _   | -100 | _               | μΑ    | —     |  |

| Input High Current                     | V <sub>IH</sub> = 3.3V,<br>V <sub>CC</sub> = 3.3V | I <sub>IH</sub> | _   | 100  | _               | μΑ    | _     |  |

| Status Indicator Output Specifications |                                                   |                 |     |      |                 |       |       |  |

| Indicator Output Logic<br>LOW          | I <sub>SINK</sub> (max) = 3mA                     | V <sub>OL</sub> |     | 0.2  | 0.4             | V     |       |  |

#### Table 2-1: DC Electrical Characteristics (Continued)

$V_{CC}$  = +2.8V to +3.47V,  $T_C$  = -40°C to 100°C. Typical values are  $V_{CC}$  = +3.3V and  $T_A$  = 25°C, unless otherwise specified. Specifications assume default setting to end-terminated 50 $\Omega$  transmission lines, unless otherwise stated. Typical Data Rate = 14.025Gb/s Note: mApp refers to mA peak-to-peak value.

| Parameter                         | Conditions   | Symbol | Min | Тур | Max | Units | Notes |

|-----------------------------------|--------------|--------|-----|-----|-----|-------|-------|

| Channel 0 Specifications          |              |        |     |     |     |       |       |

| Input Termination (SDI0)          | Differential |        | 80  | 100 | 120 | Ω     | _     |

| Output Termination (SDO0)         |              |        | _   | 50  | _   | Ω     | —     |

| Channel 1 Specifications          |              |        |     |     |     |       |       |

| Input Termination<br>(Ch1SDIP/N)  | Differential |        | 80  | 100 | 120 | Ω     | _     |

| Output Termination<br>(Ch1SDOP/N) | Differential |        | 80  | 100 | 120 | Ω     | _     |

#### NOTES:

1. Typical Conditions: T = 25°C, V = 3.3V. Maximum Conditions: T = 100°C, V = 3.467V.

2. Each output terminated.

## 2.2.1 Power Features

#### Table 2-2: Power Features

| Configuration                                       | Typical<br>Baseline<br>Power<br>(mW) | Typical<br>Incremental<br>Power<br>(mW) | Description                                                   | Feature<br>Section |

|-----------------------------------------------------|--------------------------------------|-----------------------------------------|---------------------------------------------------------------|--------------------|

| GX4002 Base                                         | 600                                  |                                         |                                                               |                    |

| SDO1 Pre-emphasis = 3dB @ 600mVppd                  | _                                    | 20                                      | _                                                             | 3.3.4              |

| PRBS7 Generator                                     | —                                    | 115                                     | Path for PRBS7 generator to Ch1SDO is on.                     | 3.6.1              |

| PRBS7 Checker                                       | _                                    | 125                                     | PRBS7 checker is on.                                          | 3.6.1              |

| Diag + ADC                                          | _                                    | 14                                      | Temperature, Supply Sensor, ADC.                              | 3.7                |

| Eye Monitor + ADC                                   | _                                    | 50                                      | All, Ch0 and Ch1 horizontal and vertical eye monitors are on. | 3.6.2              |

| Ch0 EQ Boost                                        | _                                    | 0                                       | _                                                             | 3.2.1              |

| GX4002 with Ch0 CDR bypassed and powered-down       | _                                    | -90mW                                   | _                                                             | _                  |

| GX4002 with Ch1 & Ch0 CDR bypassed and powered-down | —                                    | -185mW                                  | _                                                             | _                  |

## 2.3 AC Electrical Characteristics

#### **Table 2-3: AC Electrical Characteristics**

$V_{CC}$  = +2.8V to +3.47V,  $T_{C}$  = -40°C to 100°C. Typical values are  $V_{CC}$  = +3.3V and  $T_{A}$  = 25°C, unless otherwise specified. Specifications assume default setting to end-terminated 50 transmission lines, unless otherwise stated. Typical Data Rate = 14.025Gb/s

| Parameter                                  | Conditions                              | Symbol                          | Min  | Тур    | Max  | Units | Notes |

|--------------------------------------------|-----------------------------------------|---------------------------------|------|--------|------|-------|-------|

| Data Bata                                  | 10G configuration                       |                                 | 9.95 | —      | 11.3 | Gb/s  | 1     |

| Data Rate                                  | 16GFC configuration                     |                                 | _    | 14.025 | _    | Gb/s  | 1     |

| Channel 0 Specifications                   |                                         |                                 |      |        |      |       |       |

| Input Amplitude Range                      | differential                            |                                 | 120  | _      | 850  | mVppd | _     |

| LOS Threshold Level Setting<br>Range       |                                         |                                 | 20   | _      | 100  | mVppd | _     |

| Equalization Gain                          |                                         |                                 | _    | 6      | _    | dB    | 6     |

| Jitter Transfer Bandwidth<br>Setting Range | PRBS31 data                             |                                 | 1    | _      | 23   | MHz   | _     |

| Total Output Jitter                        |                                         |                                 | _    | 0.1    | 0.25 | Ulpp  | —     |

| Ch0 CDR Lock Time                          | 16G FC mode: loop<br>filter cap = 100nF |                                 | _    | _      | 0.5  | ms    | _     |

| Ch0SDO Output Rise/Fall<br>Time (minimum)  | 20% - 80%                               | t <sub>r</sub> , t <sub>f</sub> | _    | _      | 20   | ps    | 7     |

| Ch0SDO Output Rise/Fall<br>Time (maximum)  | 20% - 80%                               | t <sub>r</sub> , t <sub>f</sub> | 40   | _      | _    | ps    | 8     |

| Channel 1 Specifications                   |                                         |                                 |      |        |      |       |       |

| Input Sensitivity                          |                                         |                                 | _    | _      | 10   | mVppd | _     |

| Input Overload                             |                                         |                                 | 1200 | _      | _    | mVppd | _     |

| Limiting Amplifier<br>Equalization         | maximum EQ setting                      |                                 | 14   | _      | —    | dB    | 2     |

| Jitter Transfer Bandwidth<br>Setting Range |                                         |                                 | 1    |        | 23   | MHz   | _     |

| Ch1SDO Output Total Jitter                 | PRBS31 data                             | τJ                              | _    | 0.1    | 0.25 | Ulpp  | —     |

| Ch1SDO Output Rise/Fall<br>time            | 20% - 80%                               | t <sub>r</sub> , t <sub>f</sub> | 20   | _      | _    | ps    | _     |

| Ch1SDO Output AC<br>Common Mode Voltage    |                                         |                                 | _    | _      | 7.5  | mVrms | 3     |

| Ch1LOS De-assert                           | minimum<br>programmable<br>setting      |                                 | _    | 5      | _    | mVppd | _     |

| Threshold Level Setting<br>Range           | maximum<br>programmable<br>setting      |                                 | _    | 400    | _    | mVppd |       |

GX4002 2x2 14.025Gb/s Crosspoint Switch with Trace **Equalization and Output De-Emphasis** Data Sheet 55972 - 0 March 2012

### Table 2-3: AC Electrical Characteristics (Continued)

$V_{CC}$  = +2.8V to +3.47V,  $T_C$  = -40°C to 100°C. Typical values are  $V_{CC}$  = +3.3V and  $T_A$  = 25°C, unless otherwise specified. Specifications assume default setting to end-terminated 50 $\Omega$  transmission lines, unless otherwise stated. Typical Data Rate = 14.025Gb/s

| Parameter                                          | Conditions                                   | Symbol | Min | Тур          | Max | Units | Notes |

|----------------------------------------------------|----------------------------------------------|--------|-----|--------------|-----|-------|-------|

|                                                    | 1 sigma, IC to IC                            |        | —   | 1.50         | —   | mVrms | _     |

| Ch1LOS Threshold Level                             | over V <sub>CC</sub> Range                   |        | _   | <u>+</u> 0.5 | _   | dB    | _     |

| Variation                                          | over temperature<br>range -40°C to<br>+100°C |        | _   | <u>+</u> 0.5 | _   | dB    | _     |

| Ch1LOS Threshold Level<br>Hysteresis Setting Range | electrical                                   |        | 0   | _            | 6   | dB    | _     |

| Ch1LOS Response Time                               |                                              |        | 3   | 5            | 20  | μs    | _     |

| Ch1 CDR Lock Time                                  | 16G FC mode: loop<br>filter cap = 100nF      |        | _   | _            | 0.5 | ms    | 4     |

| Differential Output Voltage                        | minimum swing<br>setting                     |        | _   | 100          | _   | mVppd | _     |

| Setting Range                                      | maximum swing<br>setting                     |        | _   | 850          | _   | mVppd | _     |

| Output Pre-emphasis<br>Setting Range               | maximum setting                              |        | 3   |              | _   | dB    | 5     |

#### NOTES:

- 1. See Table 3-1 for details.

- 2. At 7GHz.

- 3. 600mVppd swing.

- 4. For loop bandwidth = 13MHz (as detailed in Table 3-4).

- 5. 600mVppd swing.

- 6. At 7GHz (dielectric loss).

- 7. Reg89[7:0] = "11001000" = Reg110[7:0]. Reg90[1:0] = "00" = Reg111[7:0]. Reg102[1:0] = "00". Reg118[4:3] = "11" = Reg119[4:3]. Reg80[7:0] = "11101110". Reg81[4:0] = "11100" = Reg103[4:0]. Reg82[4:0] = "11010" = Reg104[4:0].

- 8. Reg89[7:0] = "111111111" = Reg110[7:0]. Reg90[1:0] = "11" = Reg111[7:0]. Reg102[1:0] = "00". Reg118[4:3] = "00" = Reg119[4:3]. Reg80[7:0] = "01000100". Reg81[4:0] = "01000" = Reg103[4:0]. Reg82[4:0] = "10000" = Reg104[4:0].

# **2.4 Required Initialization Settings**

The GX4002 configuration registers must be set as described in Table 2-4 below to meet the power specification listed in Table 2-1. The AC parametric specifications in Table 2-3 are also based on these settings:

| Register<br>Name | Register<br>Address<br>(decimal) | Parameter Name | Bit<br>Position | New<br>Value<br>(binary) | Valid<br>Range<br>(decimal) | Function                |

|------------------|----------------------------------|----------------|-----------------|--------------------------|-----------------------------|-------------------------|

| CH1_REG17        | 64                               | CH1PWR1        | 4:0             | 10101                    | 0-31                        | Channel 1 power control |

| CH1_REG18        | 65                               | CH1PWR2        | 6:5             | 10                       | 0-3                         | Channel 1 power control |

| CH0_REG15        | 45                               | CH0PWR1        | 4:0             | 10101                    | 0-31                        | Channel 0 power control |

| CH0_REG16        | 46                               | CH0PWR2        | 4:3             | 10                       | 0-3                         | Channel 0 power control |

#### **Table 2-4: Required Initialization Settings**

# 3. Detailed Description

# 3.1 Multirate CDR Functionality

There are two data rate ranges available for selection, so that a single part can be used for multiple applications. The GX4002 does not require a reference clock. Some example applications are as follows:

- 10Gb/s Ethernet (10.3Gb/s)

- 10Gb/s Ethernet with FEC (11.1Gb/s)

- 10G Fibre Channel (10.5Gb/s)

- 10G Fibre Channel with FEC (11.3Gb/s)

- Fibre Channel over Ethernet (10.3Gb/s)

- 16G Fibre Channel (14.025Gb/s)

#### Table 3-1: Mode Details

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10G  | The part will retime in a continuous range from 9.95Gb/s to 11.3Gb/s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14G  | Through the serial interface, the part can be placed in 14G mode. In this<br>mode, the CDRs will retime at 14.025Gb/s, and is intended for use in 16G Fibre<br>Channel applications. An automatic rate detect circuit can be used that will<br>determine if the incoming data rate is a legacy Fibre Channel rate, and will<br>automatically bypass the CDRs. By using the automatic rate detect feature,<br>RS0 and RS1 pins are not required. The automatic rate detect feature is not<br>enabled by default when the device is configured in 14G mode. |

## **3.1.1 Rate Selection and Rate Detection**

The GX4002 has three different methods to select the data rate. The rate can be selected through the use of the RS0/RS1 pins, through the use of registers, or through automatic detection. The rate selection methods are described in more detail below.

The GX4002 also contains a set of data-dependent registers. This enables parameters such as rise and fall times to be automatically configured based on the data rate. There are two profiles, one for low data rates such as 4G or 8G Fibre Channel, and one for high data rates such as 10GbE or 16G Fibre Channel. The register map (Appendix: Configuration and Status Register Map) shows which registers contain both low data rate and high data rate options.

A configuration profile is invoked by one of three methods:

- Using input pins RS0 and RS1 to invoke a "hard" rate select for either the Ch0 path or Ch1 path respectively (CH0PLLRATESELVAL is HIGH and/or CH1PLLRATESELVAL is HIGH).

- Using host interface commands to invoke a "soft" rate select for either the Ch1 or Ch0 path, or for both Ch1 and Ch0 paths together using the CH1PLLRATESEL and CH0PLLRATESEL bits (CH1PLLRATESELVAL is HIGH and/or CH0PLLRATESELVAL is HIGH).

3. Using on-chip automatic rate detection circuitry to detect the new data rate, and to invoke an internal rate select in either the Ch1 or Ch0 path independently. The application is defined using the RATEDETFCGBEN bits (CH1PLLRATESELVAL is LOW and/or CH0PLLRATESELVAL is LOW).

| Rate<br>Selection<br>Method | Rate<br>Select<br>Valid<br>Register | RSO/RS1<br>Pins | Rate<br>Select<br>Registers | Fibre<br>Channel/<br>Ethernet<br>Register                                            | Operation                                                                             | Data Rate<br>Dependent<br>Register Set Used                       |

|-----------------------------|-------------------------------------|-----------------|-----------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|                             |                                     | LOW             | LOW                         | Not<br>Applicable                                                                    | The CDRs are placed in bypass<br>mode. Intended for 2G/4G/8G Fibre<br>Channel or 1GbE | Low Data Rate<br>Profile                                          |

| Hard Rate<br>Select         | HIGH                                | ЫСН             | Not                         | Fibre<br>Channel                                                                     | The CDR will lock to 14.025Gb/s<br>data                                               | High Data Rate<br>Profile                                         |

|                             |                                     | HIGH            | Applicable                  | Ethernet                                                                             | The CDR will lock to 9.95G to<br>11.3Gb/s data                                        | High Data Rate<br>Profile                                         |

|                             | Low or LOW<br>High Z                |                 | Not<br>Applicable           | The CDRs are place in bypass mode.<br>Intended for 2G/4G/8G Fibre<br>Channel or 1GbE | Low Data Rate<br>Profile                                                              |                                                                   |

| Soft Rate<br>Select         | HIGH                                | Not             | High                        | Fibre<br>Channel                                                                     | The CDR will lock to 14.025Gb/s<br>data                                               | High Data Rate<br>Profile                                         |

|                             |                                     | Applicable      | nign                        | Ethernet                                                                             | The CDR will lock to 9.95G to<br>11.3Gb/s data                                        | High Data Rate<br>Profile                                         |

|                             |                                     |                 |                             | Fibre                                                                                | If the input data is 14.025Gb/s, the<br>CDR will lock to it. Otherwise, the           | lf 14.025Gb/s is<br>detected: High Data<br>Rate Profile           |

| Automatic                   | LOW                                 | Not             | Not                         | Channel                                                                              | CDRs are automatically bypassed                                                       | If 14.025Gb/s is not<br>detected: Low Data<br>Rate Profile        |

| Rate<br>Detect              | LOVV                                | Applicable      | Applicable                  |                                                                                      | If the input data is 9.95G to 11.3G,<br>the CDR will lock to it. Otherwise,           | lf 9.95G to 11.3Gb/s<br>is detected: High<br>Data Rate Profile    |

|                             |                                     |                 |                             | Ethernet                                                                             | the CDRs are automatically<br>bypassed                                                | If 9.95G to 11.3Gb/s<br>is not detected: Low<br>Data Rate Profile |

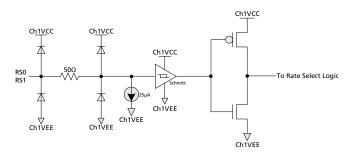

### 3.1.1.1 Hard Rate Select (Rate Select Pins)

The RS0 pin controls the rate-dependent profile of the Ch0 path, and the RS1 pin controls the rate-dependent profile of the Ch1 path. The rate select valid bit, CH0PLLRATESELVAL (or CH1PLLRATESELVAL), must be HIGH for RS0 (or RS1) to control the rate.

When the RS0 (or RS1) pin is held LOW, the low-speed rate-dependent registers of the channel 0 (or channel 1) path are active. When the RS0 (or RS1) pin is held HIGH, the high-speed rate-dependent profile of the channel 0 (or channel 1) path is active. RS0 is logically OR'ed with CH0PLLRATESEL, while RS1 is logically OR'ed with CH1PLLRATESEL. Due to the OR'ing operation, when RS0 and RS1 are used for rate control, CH0PLLRATESEL and CH1PLLRATESEL must be set LOW.

#### 3.1.1.2 Soft Rate Select

The CH1PLLRATESEL and CH0PLLRATESEL bits can be programmed to select a rate profile using the host interface. Setting these parameters and their associated valid parameters (CH1PLLRATESELVAL and CH0PLLRATESELVAL) override the on-chip automatic rate detection circuitry. CH0PLLRATESEL is logically OR'd with the RS0 pin, while CH1PLLRATESEL is logically OR'd with RS1, so RS0 and RS1 must be LOW or hi-impedance for the PLLRATESEL bits to function properly.

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name   | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                               |

|---------------|----------------------------------|------------------|-----------------|--------|--------------------------|-----------------------------|------------------------------------------------------------------------|

| CH0PLL REG5   | 14                               | CH0PLLRATESEL    | 3:3             | RW     | 1                        | 0-1                         | Selects data rates:<br>0 = 1.25 - 8.5G, 1= 10.3G or 14.025G.           |

| CHUPLE_KEG5   | 14                               | CHOPLLRATESELVAL | 4:4             | RW     | 1                        | 0-1                         | When HIGH, CH0PLLRATESEL or RS0 are valid, otherwise they are ignored. |

|               | 24                               | CH1PLLRATESEL    | 3:3             | RW     | 1                        | 0-1                         | Selects data rates:<br>0 = 1.25 - 8.5G, 1= 10.3G or 14.025G.           |

| CH1PLL_REG5   | 24                               | CH1PLLRATESELVAL | 4:4             | RW     | 1                        | 0-1                         | When HIGH, CH1PLLRATESEL or RS1 are valid, otherwise they are ignored. |

The default setting is the high (10Gb/s or 14.025Gb/s) data-rate profile, with the on-chip automatic rate detection circuitry overridden.

#### 3.1.1.3 Automatic Rate Detection

In addition to the controls outlined in the preceding tables, the auto rate detection circuitry has the following controls. To enable operation of the auto rate detection function, CHORATEDETEN (or CH1RATEDETEN) can be set HIGH.

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name    | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                     |

|---------------|----------------------------------|-------------------|-----------------|--------|--------------------------|-----------------------------|--------------------------------------------------------------|

| CH0RDET_REG1  | 67                               | CHORATEDETRESET   | 0               | RW     | 0                        | 0-1                         | When HIGH, the Ch0 path rate detector is reset.              |

|               | -                                | CHORATEDETEN      | 1               | RW     | 1                        | 0-1                         | When HIGH, enables the rate detector.                        |

| CH0RDET_REG2  | 68                               | CHORATEDETRATEPER | 3:0             | RW     | 1000                     | 0-15                        | Rate detector rate period (0.3µs to 13ms,<br>100µs default). |

| CH1RDET_REG1  | 72                               | CH1RATEDETRESET   | 0               | RW     | 0                        | 0-1                         | When HIGH, the Ch1 path rate detector is reset.              |

|               | -                                | CH1RATEDETEN      | 1               | RW     | 1                        | 0-1                         | When HIGH, enables the rate detector                         |

| CH1RDET_REG2  | 73                               | CH1RATEDETRATEPER | 3:0             | RW     | 1000                     | 0-15                        | Rate detector rate period (0.3µs to 13ms,<br>100µs default). |

If CH1RATEDETEN (or CH0RATEDETEN) is LOW, the CH1PLLRATESELVAL (or CH0PLLRATESELVAL) bit must be HIGH, otherwise the device will be in an undefined state.

CHORATEDETPERIOD (address 68) and CH1RATEDETPERIOD (address 73) control the frequency at which the automatic rate detection block checks the lock state of the PLL. The recommended setting for shortest lock time is 1001b.

### 3.1.1.4 Application-Dependent Rate Select Profiles

The **RATEDETFCGBEN** and **RATEDETFCGBENVAL** bits indicate whether the application traffic is running Fibre Channel, Ethernet or unspecified (for example: the transceiver may be required to handle either Fibre Channel or Ethernet traffic in mission mode). The default setting is Fibre Channel traffic.

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name   | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                                                  |

|---------------|----------------------------------|------------------|-----------------|--------|--------------------------|-----------------------------|-------------------------------------------------------------------------------------------|

| CH0RDET REG1  | 67                               | RATEDETFCGBEN    | 2:2             | RW     | 1                        | 0-1                         | When HIGH, the application is Fibre<br>Channel. When LOW, the application is<br>Ethernet. |

|               |                                  | RATEDETFCGBENVAL | 3:3             | RW     | 1                        | 0-1                         | When HIGH, indicates that RATEDETFCGBEN is valid. When LOW, it is ignored.                |

#### Table 3-2: Summary of Rate Selection and Rate Detection Control

| CH1PLLRATESELVAL<br>CH0PLLRATESELVAL | RATEDETFCGBENVAL | Data Rate                                                                                         | Configuration Profile                        |

|--------------------------------------|------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------|

| 0                                    | 0                | Undefined                                                                                         | Undefined                                    |

| 0                                    | 1                | Auto Rate Detect                                                                                  | Profile selected based on detected rate      |

| 1                                    | 0                | Auto Rate Detect                                                                                  | Profile selected by hard or soft rate select |

| 1                                    | 1                | Fixed rate determined by the<br>combination of<br>RATEDETFCGBEN and rate<br>select (hard or soft) | Profile selected by hard or soft rate select |

## 3.1.2 Auto Retimer Bypass

The GX4002 supports an automatic rate detect feature for legacy Fibre Channel data rates when configured in 16G mode. Upon enabling the automatic rate detect feature, the device constantly monitors incoming data for a valid 14.025Gb/s data rate. If the input data rate is a legacy Fibre Channel rate, the CDR is automatically bypassed.

While the automatic rate detect feature is enabled, and the CDR is in bypass mode, the device continues monitoring the incoming data rate. If the data rate changes to 14.025Gb/s, the CDR goes back into retimed mode.

The auto retimer bypass feature also applies to Ethernet mode.

The following registers enable and configure the automatic rate detect feature:

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name      | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                  |

|---------------|----------------------------------|---------------------|-----------------|--------|--------------------------|-----------------------------|-----------------------------------------------------------|

|               |                                  | CHOPLLBYPASS        | 1:1             | RW     | 0                        | 0-1                         | When HIGH, forces CDR into bypass mode.                   |

| CH0PLL_REG5   | 14                               | CHOPLLAUTOBYPASSEN  | 2:2             | RW     | 1                        | 0-1                         | When HIGH, enables automatic bypass mode for the Ch0 CDR. |

|               | (7                               | CHORATEDETRESET     | 0:0             | RW     | 0                        | 0-1                         | When HIGH, resets the Ch0 path rate detector.             |

| CHORDET_REG1  | 67                               | CHORATEDETEN        | 1:1             | RW     | 1                        | 0-1                         | When HIGH, enables the Ch0 path automatic rate detector.  |

|               | 72                               | CH1RATEDETRESET     | 0:0             | RW     | 0                        | 0-1                         | When HIGH, resets the Ch1 path rate detector.             |

| CH1RDET_REG1  | 72                               | <b>CH1RATEDETEN</b> | 1:1             | RW     | 1                        | 0-1                         | When HIGH, enables the Ch1 path automatic rate detector.  |

The device can be configured to manually bypass each of the Ch1 and Ch0 CDRs through the CH0PLLBYPASS and CH1PLLBYPASS controls when the automatic bypass is disabled.

# 3.2 Channel 0 Path (Ch0)

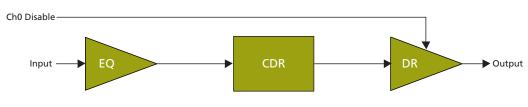

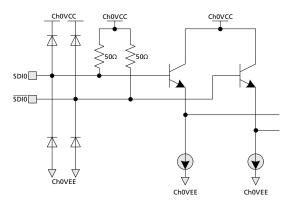

The channel 0 path is comprised of a trace equalizer, a multi-rate CDR and an output driver.

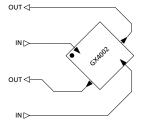

Figure 3-1: Channel 0 Path

## 3.2.1 Ch0 Equalization

The channel 0 path input has an equalizer with 6dB gain at 7GHz. The equalizer can be bypassed through the following register:

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                    |

|---------------|----------------------------------|----------------|-----------------|--------|--------------------------|-----------------------------|-------------------------------------------------------------|

| CH0_REG3      | 33                               | CH0EQBOOST     | 0:0             | RW     | 1                        | 0-1                         | When HIGH, applies a fixed CH0 EQ boost of 6dB. 0dB if LOW. |

## 3.2.2 Ch0 PLL Variable Loop Bandwidth

The loop bandwidth of the channel 0 Phase Locked Loop (PLL) can be varied through the digital control interface. The loop bandwidths are individually controlled, and can cover the range of 1MHz to 23MHz through following five-bit registers (recommended settings are shown):

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name  | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                   |

|---------------|----------------------------------|-----------------|-----------------|--------|--------------------------|-----------------------------|------------------------------------------------------------|

| CH0PLL_REG1   | 10                               | CHOPLLLBWCURVT  | 4:0             | RW     | 10011                    | 0-31                        | Adjusts LBW positive temperature coefficient control.      |

| CH0PLL_REG2   | 11                               | CHOPLLLBWCURVBE | 4:0             | RW     | 01110                    | 0-31                        | Adjusts LBW negative temperature coefficient control.      |

| CH0PLL_REG9   | 18                               | CHOPLLLBWMULT   | 1:0             | RW     | 10                       | 0-3                         | LBW multiplier;<br>00 = 0.67, 10 = 1, 01 = 1.33, 11 = 1.67 |

The temperature coefficient of the loop bandwidth can be adjusted by weighted summation of CHOPLLLBWCURVT, which has a positive temperature coefficient and CHOPLLLBWCURVBE, which has a negative temperature coefficient. The default reset values of the registers above produce an approximate loop bandwidth of 7MHz.

| CHOPLLLBWMULT | CHOPLLLBWCURVT | CHOPLLLBWCURVBE | Loop<br>Bandwidth |

|---------------|----------------|-----------------|-------------------|

| 00            | 10011          | 01110           | 4.6MHz            |

| 10 (default)  | 10011          | 01110           | 7.3MHz            |

| 01            | 10011          | 01110           | 9.9MHz            |

| 10            | 11111          | 10110           | 13MHz             |

| 11            | 11000          | 11000           | 22.7MHz           |

#### Table 3-3: Typical Loop Bandwidths for Various Register Settings

## 3.2.3 Channel 0 Output Polarity Invert

The channel 0 output polarity can be inverted through the following register:

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                       |

|---------------|----------------------------------|----------------|-----------------|--------|--------------------------|-----------------------------|------------------------------------------------|

| CH0PLL_REG5   | 14                               | CH0PLLPOLINV   | 0:0             | RW     | 0                        | 0-1                         | When HIGH, inverts the Ch0 data path polarity. |

# 3.3 Channel 1 Path (Ch1)

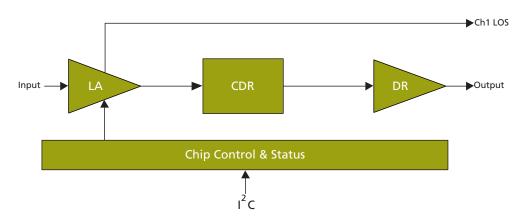

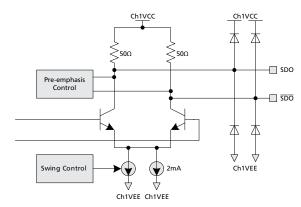

The GX4002 channel 1 path contains a high-sensitivity limiting amplifier with optional equalization, a multi-rate CDR, and a pre-emphasis driver.

## 3.3.1 Integrated Limiting Amplifier

The GX4002 has an integrated Limiting Amplifier (LA), with better than 10mV sensitivity. Optional equalization is available on the limiting amplifier input.

## 3.3.2 Ch1 Equalization

The channel 1 input implements an equalizer that provides peaking at 7GHz. This feature allows for optimal performance with extended reach connections.

The equalizer implements 0dB to 14dB of high-frequency boost in fifteen steps, while achieving optimal receive sensitivity at any given equalization setting. The equalization setting is set through the CH1LABOOST control.

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name    | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function            |

|---------------|----------------------------------|-------------------|-----------------|--------|--------------------------|-----------------------------|---------------------|

| CH1_REG1      | 48                               | <b>CH1LABOOST</b> | 3:0             | RW     | 0000                     | 0-15                        | 0: 0dB to 15: 14dB. |

When the equalization setting is 0dB, the equalization function is bypassed and the receive sensitivity performance is the same as that of a limiting amplifier.

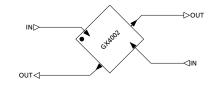

Figure 3-3: Channel 1 Equalization

## 3.3.3 Ch1 PLL Variable Loop Bandwidth

The loop bandwidth of the channel 1 Phase Locked Loops (PLLs) can be varied through the digital control interface. The loop bandwidths are individually controlled, and can cover a range of 1MHz to 23MHz through the following 5-bit registers:

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name  | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                   |

|---------------|----------------------------------|-----------------|-----------------|--------|--------------------------|-----------------------------|------------------------------------------------------------|

| CH1PLL_REG1   | 20                               | CH1PLLLBWCURVT  | 4:0             | RW     | 10011                    | 0-31                        | Adjusts LBW positive temperature coefficient control.      |

| CH1PLL_REG2   | 21                               | CH1PLLLBWCURVBE | 4:0             | RW     | 01110                    | 0-31                        | Adjusts LBW negative temperature coefficient control.      |

| CH1PLL_REG9   | 28                               | CH1PLLLBWMULT   | 7:6             | RW     | 10                       | 0-3                         | LBW multiplier;<br>00 = 0.67, 10 = 1, 01 = 1.33, 11 = 1.67 |

The temperature coefficient of the loop bandwidth can be adjusted by a weighted summation of CH1PLLLBWCURVT, which has a positive temperature coefficient, and CH1PLLLBWCURVBE, which has a negative temperature coefficient. The default reset values of the above registers produce an approximate loop bandwidth of 7MHz.

| Table 3-4: Typical Loop Ba | andwidths for Various Register Settings |

|----------------------------|-----------------------------------------|

|----------------------------|-----------------------------------------|

| CH1PLLLBWMULT | CH1PLLLBWCURVT | CH1PLLLBWCURVBE | Loop<br>Bandwidth |

|---------------|----------------|-----------------|-------------------|

| 00            | 10011          | 01110           | 4.6MHz            |

| 10 (default)  | 10011          | 01110           | 7.3MHz            |

| 01            | 10011          | 01110           | 9.9MHz            |

| CH1PLLLBWMULT | CH1PLLLBWCURVT | CH1PLLLBWCURVBE | Loop<br>Bandwidth |

|---------------|----------------|-----------------|-------------------|

| 10            | 11111          | 10110           | 13MHz             |

| 11            | 11000          | 11000           | 22.7MHz           |

### Table 3-4: Typical Loop Bandwidths for Various Register Settings (Continued)

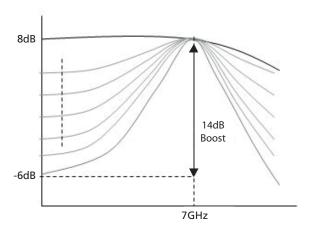

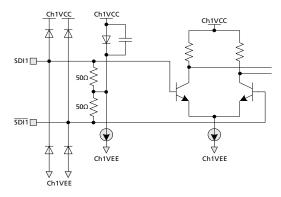

## 3.3.4 Pre-Emphasis Driver with Auto-Mute

The channel 1 driver is a pre-emphasis driver that can be used to compensate for losses in the connector and trace between the module and ASIC. The pre-emphasis can compensate for up to 6dB of loss. The output swing can be set from 100mV to 800mV in steps of 50mV through the CH1SDOSWING[3:0] register. The pre-emphasis amplitude can be varied from 0dB to 6dB in eight non-linear steps through CH1SDOPECTRL[4:2].

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                                      |

|---------------|----------------------------------|----------------|-----------------|--------|--------------------------|-----------------------------|---------------------------------------------------------------|

| CH1SDO_REG1   | 77                               | CH1SDOSWING    | 3:0             | RW     | 1010                     | 0-15                        | Driver swing.<br>0-15: 100-850mVppd, Default = 10: 600mV      |

| CH1SDO_REG2   | 78                               | CH1SDOPECTRL   | 4:2             | RW     | 000                      | 0-7                         | Pre-emphasis amplitude.<br>0: 0dB, 7: 6dB for 200mVppd swing. |

Figure 3-4 above shows the pre-emphasis waveform. Amplitudes V1, V2 and pre-emphasis in dB are defined as follows:

#### V1, V2 and Pre-emphasis are defined as follows:

V1 which represents the "peak" V2 which represents DC or Steady State Pre-emphasis [dB] = 20 x log(V1/V2)

The amount of pre-emphasis varies with CH1SDOSWING as shown in Table 3-5:

| <b>CH1SDOSWING</b> | CH1SDOPECTRL | Pre-emphasis |

|--------------------|--------------|--------------|

| 0010 (200mV)       | 001          | 2.3dB        |

| 0101 (350mV)       | 001          | 1.8dB        |

| 1010 (600mV)       | 001          | 1.0dB        |

| 0010 (200mV)       | 011          | 4.7dB        |

| 0101 (350mV)       | 011          | 3.8dB        |

| 1010 (600mV)       | 011          | 3.1dB        |

| 0010 (200mV)       | 111          | 6.2dB        |

| 0101 (350mV)       | 111          | 5.5dB        |

| 1010 (600mV)       | 111          | 3.4dB        |

| Table 3-5: | Pre-Em | phasis v | s. Ch1 | SDO | Swina |

|------------|--------|----------|--------|-----|-------|

|            |        |          |        |     |       |

The output can be configured to automatically mute if Ch1 LOS is detected through the following registers. When muted, the output driver remains powered-up, and the output common mode is maintained. The output driver can be configured to power-down when muted by setting the CH1SDOPWRDNONMUTE bit:

| Register Name | Register<br>Address <sup>d</sup> |                   |     | Valid<br>Range <sup>d</sup> | Function |     |                                                                                            |

|---------------|----------------------------------|-------------------|-----|-----------------------------|----------|-----|--------------------------------------------------------------------------------------------|

|               |                                  | CH1SDOMUTE        | 5:5 | RW                          | 0        | 0-1 | When HIGH, mutes driver and maintains<br>output common mode when not in auto<br>mute mode. |

| CH1SDO_REG3   | 79                               | CH1SDOAUTOMUTEEN  | 6:6 | RW                          | 1        | 0-1 | When HIGH, enables muting the driver upon LOS. LOW disables muting.                        |

|               |                                  | CH1SDOPWRDNONMUTE | 7:7 | RW                          | 1        | 0-1 | When HIGH, enables power-down on mute<br>for output stage. LOW disables<br>power-down.     |

## 3.3.5 Channel 1 Output Polarity Invert

The channel 1 output polarity can be inverted through the following register:

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name      | Bit<br>Position | Access | Reset Value <sup>b</sup> | Valid<br>Range <sup>d</sup> | Function                                       |

|---------------|----------------------------------|---------------------|-----------------|--------|--------------------------|-----------------------------|------------------------------------------------|

| CH1PLL_REG5   | 24                               | <b>CH1PLLPOLINV</b> | 0:0             | RW     | 0                        | 0-1                         | When HIGH, inverts the Ch1 data path polarity. |

**Proprietary & Confidential**

## **3.4 Crosspoint**

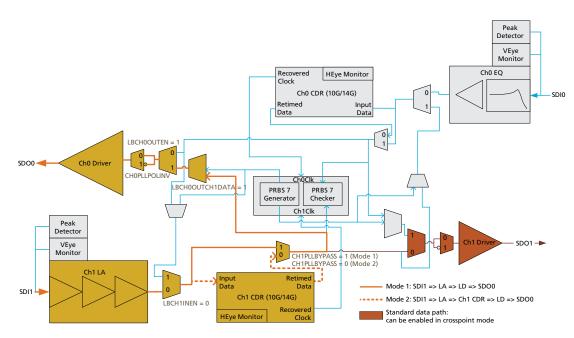

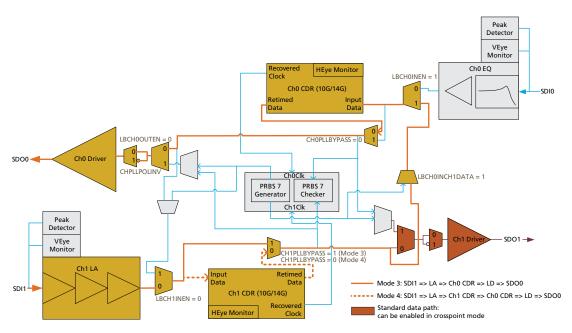

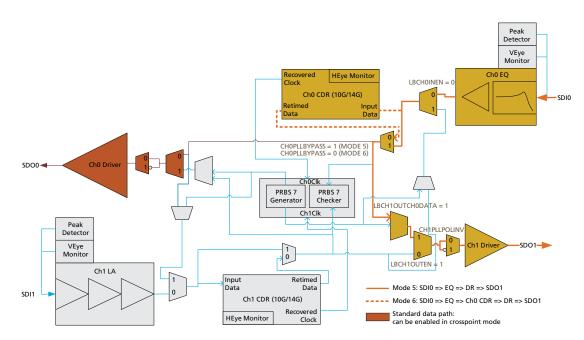

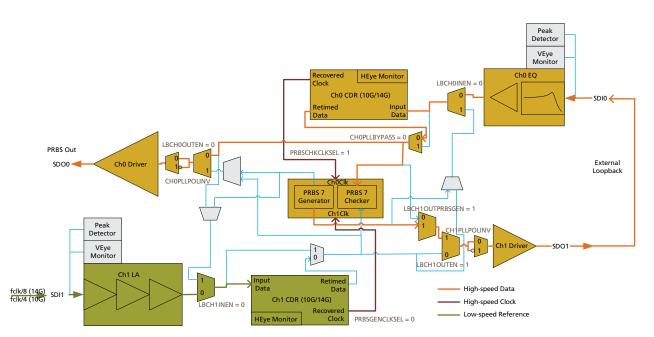

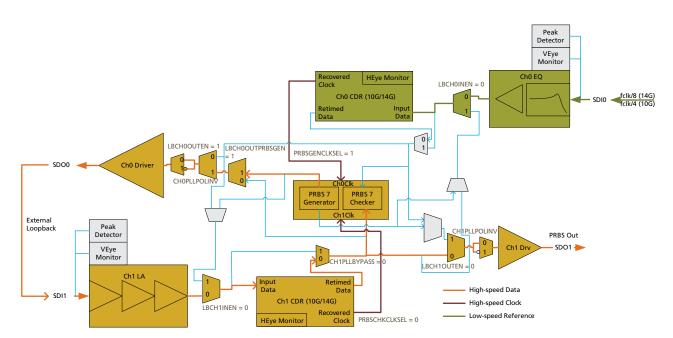

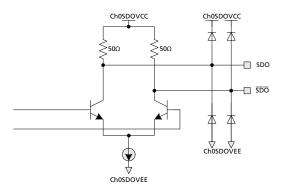

The GX4002 provides eight different crosspoint paths, as shown in Table 3-6. The blocks referenced in the different crosspoint paths are shown in Figure 3-5.

Figure 3-5: Crosspoint Block Diagram

#### Table 3-6: Crosspoint Paths

| Mode | Crosspoint Path                     | Reference  |

|------|-------------------------------------|------------|

| 1    | SDI1 =>LA=>DR=>SDO0                 | Figure 3-6 |

| 2    | SDI1 =>LA=>CH1CDR=>DR=>SDO0         | Figure 3-6 |

| 3    | SDI1 =>LA=>CH0CDR=>DR=>SDO0         | Figure 3-7 |

| 4    | SDI1 =>LA=>CH1CDR=>CH0CDR=>DR=>SDO0 | Figure 3-7 |

| 5    | SDI0=>EQ=>DR=>SDO1                  | Figure 3-8 |

| 6    | SDI0=>EQ=>CH0CDR=>DR=>SDO1          | Figure 3-8 |

| 7    | SDI0=>EQ=>CH1CDR=>DR=>SDO1          | Figure 3-9 |

| 8    | SDI0=>EQ=>CH0CDR=>CH1CDR=>DR=>SDO1  | Figure 3-9 |

When the crosspoint is enabled, the standard data path is not interrupted. For example: in Mode 1, the input to SDI1 will also be accessible at SDO1. When using crosspoint modes, the automute feature for SDO1 or SDO0 may have to be disabled if the corresponding SDI1 or SDI0 inputs are unused.

The relevant parameters in these registers and their values required to enable each of the crosspoint options indicated above, are shown in Table 3-7.

The selection of a crosspoint path impacts the following feature:

• Polarity inversion

Table 3-7 also captures the impact on these features in each crosspoint mode.

## Table 3-7: Crosspoint Options

| Crosspoint Mode<br>(see Table 3-6) | LBCH1INEN | LBCH1INPRBSGEN | LBCH1INCH0DATA | LBCH10UTEN | LBCH1OUTCH0DATA | LBCh1OutPRBSGen | LBCH10UTCH1CLK | CH1PLLBYPASS | LBCHOINEN | LBCHOINPRBSGEN | LBCH0INCH1DATA | LBCH00UTEN | LBCH0OUTCH1DATA | LBCH0OUTPRBSGEN | LBCH0OUTCH0CLK | CHOPLLBYPASS | CH0PLLPOLINV Effective | CH0PLLPOLINV Effective |

|------------------------------------|-----------|----------------|----------------|------------|-----------------|-----------------|----------------|--------------|-----------|----------------|----------------|------------|-----------------|-----------------|----------------|--------------|------------------------|------------------------|

| 1                                  | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 1            | 0         | 0              | 0              | 1          | 1               | 0               | 0              | 0            | Y                      | Ν                      |

| 2                                  | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 0            | 0         | 0              | 0              | 1          | 1               | 0               | 0              | 0            | Y                      | Ν                      |

| 3                                  | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 1            | 1         | 0              | 1              | 0          | 0               | 0               | 0              | 0            | Y                      | Ν                      |

| 4                                  | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 0            | 1         | 0              | 1              | 0          | 0               | 0               | 0              | 0            | Y                      | Ν                      |

| 5                                  | 0         | 0              | 0              | 1          | 1               | 0               | 0              | 0            | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 1            | Ν                      | Y                      |

| 6                                  | 0         | 0              | 0              | 1          | 1               | 0               | 0              | 0            | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 0            | Ν                      | Y                      |

| 7                                  | 1         | 0              | 1              | 0          | 0               | 0               | 0              | 0            | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 1            | Ν                      | Y                      |

| 8                                  | 1         | 0              | 1              | 0          | 0               | 0               | 0              | 0            | 0         | 0              | 0              | 0          | 0               | 0               | 0              | 0            | Ν                      | Y                      |

| Control<br>Register<br>Address     | 7         | 7              | 7              | 7          | 7               | 7               | 7              | 24           | 8         | 8              | 8              | 8          | 8               | 8               | 8              | 14           | _                      | _                      |

| Associated<br>Bit<br>Slice         | 0         | 1              | 2              | 4          | 5               | 6               | 7              | 1            | 0         | 1              | 2              | 4          | 5               | 6               | 7              | 1            | _                      | _                      |

**Proprietary & Confidential**

Figure 3-6: Crosspoint Modes 1 & 2

Figure 3-7: Crosspoint Modes 3 & 4

Figure 3-8: Crosspoint Modes 5 & 6

Figure 3-9: Crosspoint Modes 7 & 8

# **3.5 Status Indicators**

The GX4002 supports three status indicators: Loss of Signal (LOS), Loss of Lock (LOL) and Channel 0 Fault (Ch0FAULT). LOS and LOL indicators are available on both the Ch1 and the Ch0 paths.

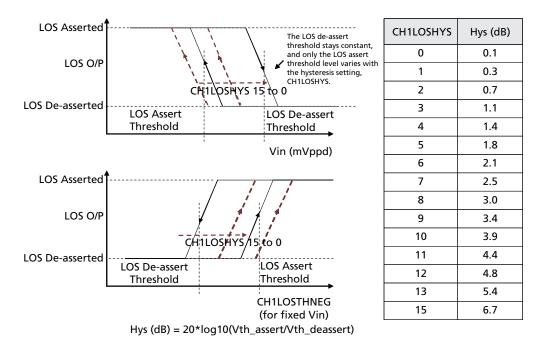

## 3.5.1 Ch0 Loss Of Signal (LOS)

The Ch0 LOS indicator status is available through a register. If desired, its status can be included in the generation of the Ch0FAULT output pin. The LOS assert threshold can be set from 20mV to 100mV in <1mV steps. In addition, the temperature coefficient of the LOS threshold can be adjusted to ensure consistent LOS operation over temperature. The LOS also has hysteresis that is programmable from 0dB to 6dB in steps of 0.5dB.

| Register Name | Register<br>Address <sup>d</sup> | Parameter Name     | Bit<br>Position                  | Access | Reset Value <sup>b</sup>                                | Valid<br>Range <sup>d</sup> | Function                                                                                                                                   |

|---------------|----------------------------------|--------------------|----------------------------------|--------|---------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CH0_REG9      | 39                               | CHOLOSTHNEG        | 7:0                              | RW     | 01010011                                                | 0-255                       | Negative temperature coefficient LOS threshold setting.                                                                                    |

| CH0_REG10     | 40                               | CHOLOSTHPOS        | CH0LOSTHPOS 7:0 RW 0000000 0-255 |        | Positive temperature coefficient LOS threshold setting. |                             |                                                                                                                                            |

| CH0_REG11     | 41                               | CH0LOSHYS          | 3:0                              | RW     | 1001                                                    | 0-15                        | Sets LOS hysteresis from 0dB to 6dB in steps of 0.5dB.                                                                                     |

| CH0_REG12     | 42                               | CHOLOSSOFTASSERT   | 3:3                              | RW     | 0                                                       | 0-1                         | When HIGH, asserts LOS for internal<br>functions, asserts LOS register (CHOPLLLOS)<br>and asserts external indication through<br>ChOFAULT. |

|               | -                                | CHOLOSSOFTASSERTEN | 4:4                              | RW     | 0                                                       | 0-1                         | When HIGH, LOS is controlled by CH0LOSSOFTASSERT.                                                                                          |

The following registers are used to control the Ch0 LOS feature:

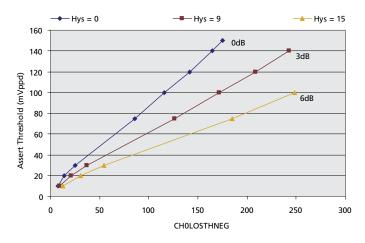

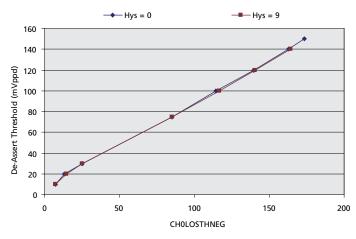

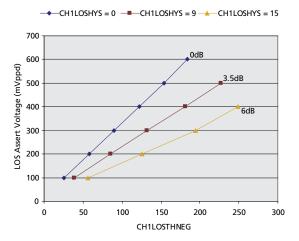

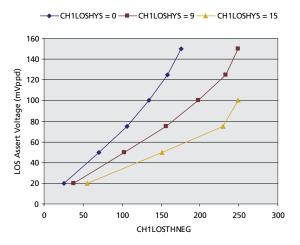

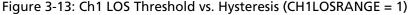

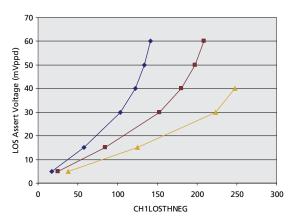

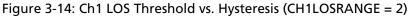

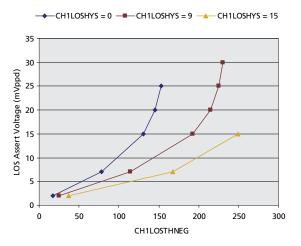

### 3.5.1.1 Ch0 LOS Threshold

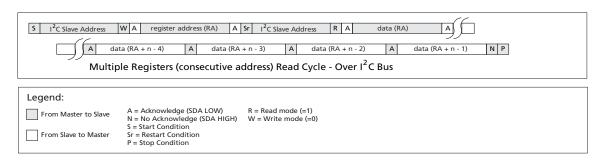

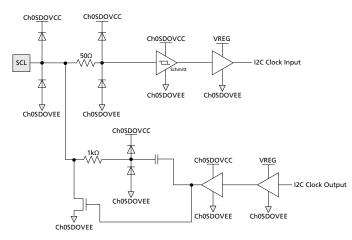

Figure 3-10 and Figure 3-11 show the typical recommended range of Ch0 LOS assert thresholds and corresponding CH0LOSTHNEG[7:0] setting to achieve these thresholds. It is recommended to keep CH0LOSPOS[7:0] = 0 to achieve a flat temperature coefficient for LOS threshold. The Ch0 LOS de-assert thresholds are the same as the Ch0 LOS assert thresholds for a hysteresis setting of 0.