# Low Voltage Synchronous Boost Converter

#### **POWER MANAGEMENT**

### **Features**

- Input voltage 0.7V to 1.6V

- Minimum start-up voltage 0.85V

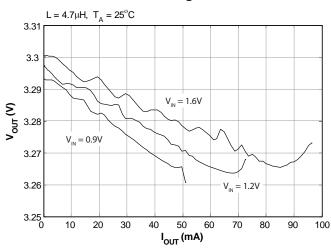

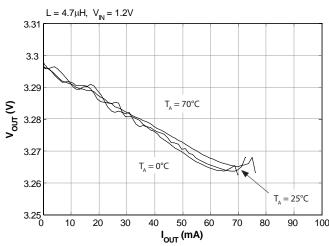

- Output voltage fixed at 3.3V

- Peak input current limit 350mA typically

- Output current 95mA at  $V_{IN} = 1.6V$ , 50mA at  $V_{IN} = 0.9V$

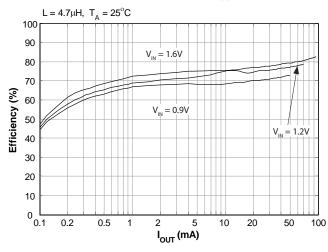

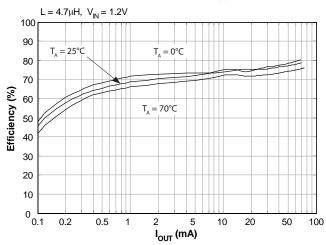

- Efficiency up to 80%

- Internal synchronous rectifier

- Switching frequency 1.2MHz

- Power save (voltage hysteretic) control

- Anti-ringing circuit

- Operating supply current (measured at OUT) 40µA

- No forward conduction path during shutdown

- MLPD-UT-6 1.5  $\times$  2.0  $\times$  0.6 (mm) package

- Lead-free and halogen-free

- WEEE and RoHS compliant

## **Applications**

- Electric toothbrushes

- Personal medical products

- Single-cell alkaline, NiCd, or NiMH applications

## **Description**

The SC122 is a high efficiency, low noise, synchronous step-up DC-DC converter. It produces a fixed 3.3V output from a single cell alkaline or NiMH battery. It features an internal 1.2A switch and synchronous rectifier to achieve high efficiency and to eliminate the need for an external Schottky diode.

The SC122 operates exclusively in voltage-hysteretic power save mode (PSAVE) for high efficiency under light load conditions. It features anti-ringing circuitry for reduced EMI in noise sensitive applications. While disabled, the output remains in a high impedance state to preserve the charge on the output capacitor. This permits ultra-low idle quiescent currents in applications in which the SC122 can be periodically enabled by an external controller to recharge the output capacitor.

Low quiescent current is obtained despite a high 1.2MHz operating frequency. Small external components and the space saving MLPD-UT-6, 1.5×2.0×0.6 (mm) package, make this device an excellent choice for small handheld applications that require the longest possible battery life.

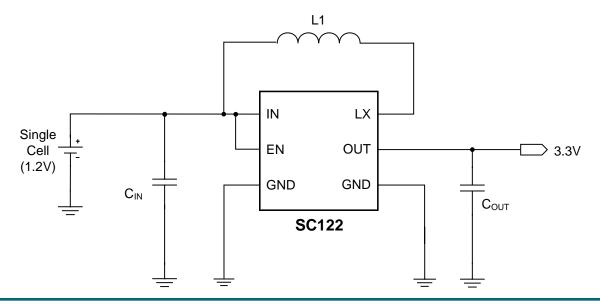

## **Typical Application Circuit**

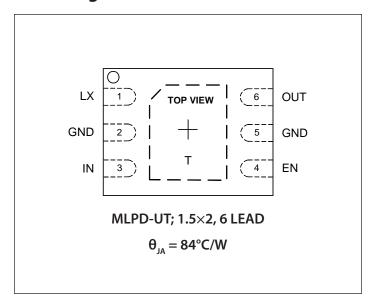

# **Pin Configuration**

# **Ordering Information**

| Device                       | Package          |

|------------------------------|------------------|

| SC122ULTRT <sup>(1)(2)</sup> | MLPD-UT-6 1.5×2  |

| SC122EVB                     | Evaluation Board |

#### Notes:

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Lead-free packaging only. Device is WEEE and compliant and halogen-free.

# **Marking Information**

## **Absolute Maximum Ratings**

## IN, OUT, LX (V) ..... -0.3 to +6.0 EN (V) ..... -0.3 to $(V_{IN} + 0.3)$ ESD Protection Level<sup>(1)</sup> (kV) ..... 3

## **Recommended Operating Conditions**

| Ambient Temperature Range (°C) | 0 to +70   |

|--------------------------------|------------|

| V <sub>IN</sub> (V)            | 0.7 to 1.6 |

| V <sub>OUT</sub> (V)           | 3.3        |

### **Thermal Information**

| Thermal Resistance Junction-Ambient $^{(2)}$ (°C/V | V)84        |

|----------------------------------------------------|-------------|

| Maximum Junction Temperature (°C)                  | 150         |

| Storage Temperature Range (°C) $\dots$             | -65 to +150 |

| Peak IR Reflow Temperature (10s to 30s) (°C)       | +260        |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

- (1) Tested according to JEDEC standard JESD22-A114.

- (2) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

### **Electrical Characteristics** —

Unless otherwise noted  $V_{IN}=1.2V$ ,  $C_{IN}=C_{OUT}=22\mu F$ ,  $L_{1}=4.7\mu H$ ,  $T_{A}=0$  to  $+70^{\circ}C$ . Typical values are at  $T_{A}=25^{\circ}C$ .

| Parameter                                          | Symbol                 | Conditions                                                                                      |     | Тур  | Max | Units |

|----------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Input Voltage Range                                | V <sub>IN</sub>        |                                                                                                 | 0.7 |      | 1.6 | V     |

| Output Voltage                                     | V <sub>out</sub>       |                                                                                                 |     | 3.3  |     | V     |

| Output Accuracy                                    | V <sub>OUT-tol</sub>   | $V_{EN} = V_{IN}$                                                                               | -3  |      | 3   | %     |

| Minimum Startup Voltage                            | V <sub>IN-SU</sub>     | I <sub>OUT</sub> < 1mA                                                                          |     | 0.85 |     | V     |

| Operating Supply Current <sup>(1)</sup>            | I <sub>OUT-Q</sub>     | $V_{EN} = V_{IN'} I_{OUT} = 0 \text{mA}, V_{OUT} = 3.3 \text{V}$                                |     | 40   |     | μΑ    |

| Disabled OUT Leakage Current                       | I <sub>OUT-DIS</sub>   | $V_{EN} = 0$ , $V_{OUT} = 3.3V$ (externally forced)                                             |     | 2    |     | μΑ    |

| Disabled IN Quiescent Current                      | I <sub>IN-DIS</sub>    | $V_{EN} = 0$ , $V_{IN} = 1.6$ , $V_{OUT} = 3.3V$ (externally forced)                            |     | 4    |     | μΑ    |

| Shutdown Current                                   | I <sub>IN-SHDN</sub>   | $V_{EN} = 0V, V_{IN} = 1.6V, V_{OUT} = 0V$                                                      |     | 8.5  |     | μΑ    |

| Internal Oscillator Frequency                      | f <sub>osc</sub>       | while bursting                                                                                  |     | 1.2  |     | MHz   |

| Startup Time                                       | t <sub>su</sub>        | From V <sub>EN</sub> low-to-high transition                                                     |     | 1    |     | ms    |

| Minimum V <sub>IN</sub> for Restart <sup>(2)</sup> | V<br>IN-Restart        | Lowest $V_{IN}$ to ensure re-enable within 300 $\mu$ s,<br>$V_{OUT} = 3.1V$ (externally forced) |     |      | 1.0 | V     |

| P-Channel ON Resistance                            | R <sub>DS(ON)P</sub>   | I <sub>LX</sub> = 50mA                                                                          |     | 0.6  |     | Ω     |

| N-Channel ON Resistance                            | R <sub>DS(ON)N</sub>   | $I_{LX} = 50 \text{mA}, V_{IN} = 1.6 \text{V}$                                                  |     | 0.5  |     | Ω     |

| P-Channel Startup Current Limit                    | I <sub>LIM(P)-SU</sub> | $V_{IN} = 1.2V, V_{EN} > V_{IH}$                                                                |     | 100  |     | mA    |

## **Electrical Characteristics (continued)**

| Parameter                | Symbol              | Conditions                                         |      | Тур | Max | Units |

|--------------------------|---------------------|----------------------------------------------------|------|-----|-----|-------|

| N-Channel Current Limit  | I <sub>LIM(N)</sub> | V <sub>IN</sub> = 1.2V                             |      | 350 |     | mA    |

| LX Leakage Current PMOS  | I <sub>LXPLK</sub>  | $T_A = 25^{\circ}C, V_{LX} = 0V, V_{OUT} = 3.3V$   |      |     | 1   | μΑ    |

| LX Leakage Current NMOS  | I <sub>LXNLK</sub>  | $T_A = 25$ °C, $V_{LX} = 3.3$ V, $V_{OUT} = 3.3$ V |      |     | 1   | μΑ    |

| Logic Input High         | V <sub>IH</sub>     | V <sub>IN</sub> = 1.2V                             | 0.4  |     |     | V     |

| Logic Input Low          | V <sub>IL</sub>     | V <sub>IN</sub> = 1.2V                             |      |     | 0.1 | V     |

| Logic Input Current High | I <sub>IH</sub>     | V <sub>EN</sub> = V <sub>IN</sub> = 1.2V           |      |     | 1   | μΑ    |

| Logic Input Current Low  | I <sub>IL</sub>     | V <sub>EN</sub> = 0V                               | -0.2 |     |     | μΑ    |

#### NOTES:

- (1) Quiescent operating current is drawn from the OUT pin while in regulation. The quiescent operating current projected to the IN pin is approximately  $I_Q \times (V_{OUT}/V_{IN})$ .

- (2) Restart occurs when the EN pin transitions from low to high while the output voltage is at or near the regulation value (3.3V). See the application section "The Enable Pin" for details.

# Typical Characteristics — $V_{OUT} = 3.3V$

# Efficiency vs. I<sub>OUT</sub>

## **Load Regulation**

## **Load Regulation**

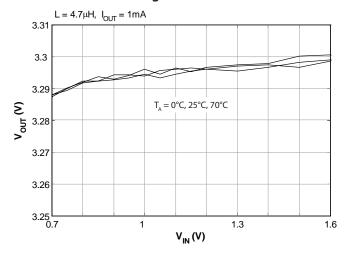

### Line Regulation — Low Load

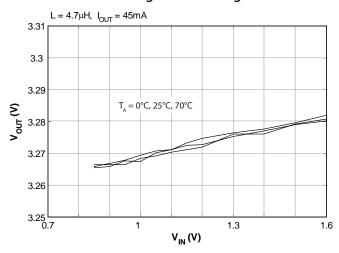

### Line Regulation — High Load

# Typical Characteristics — $V_{OUT} = 3.3V$ (continued)

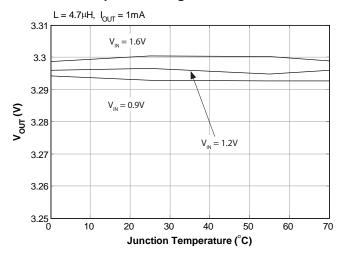

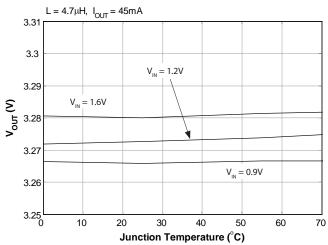

### **Temperature Regulation** — Low Load

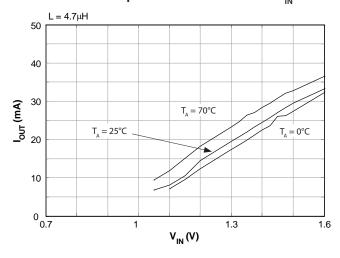

## Startup Max. Load Current vs. $V_{IN}$

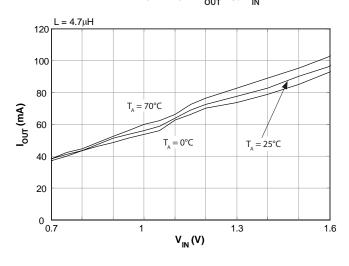

# $\mathbf{Maximum}\ \mathbf{I}_{\mathrm{OUT}}\ \mathbf{vs.}\ \mathbf{V}_{\mathrm{IN}}$

## **Temperature Regulation** — **High Load**

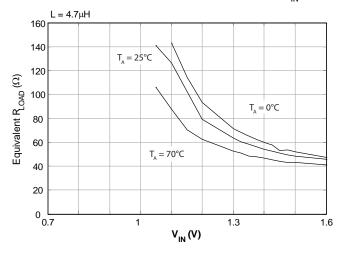

## Startup Min. Load Resistance vs. V<sub>IN</sub>

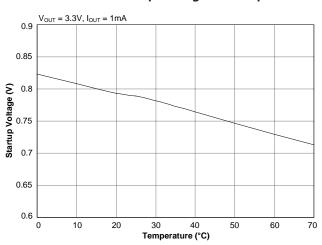

### Minimum Start-up Voltage vs. Temperature

# **Pin Descriptions**

| MLPD Pin # | Pin Name       | Pin Function                                                                                                                                |  |

|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | LX             | Switching node — connect an inductor from the input supply to this pin.                                                                     |  |

| 2, 5       | GND            | nal and power ground connections.                                                                                                           |  |

| 3          | IN             | Battery input and damping switch connection.                                                                                                |  |

| 4          | EN             | Enable digital control input — active high.                                                                                                 |  |

| 6          | OUT            | Output voltage supply pin — requires an external $10\mu F$ bypass capacitance (effective under $V_{\text{OUT}}$ bias) for normal operation. |  |

| Т          | Thermal<br>Pad | Thermal Pad is for heat sinking purposes — connect to ground using multiple vias, not connected internally.                                 |  |

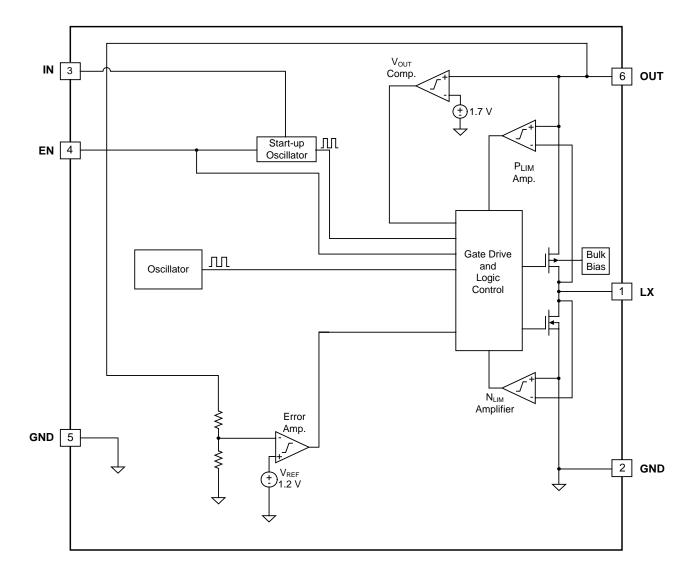

# **Block Diagram**

### **Applications Information**

### **Detailed Description**

The SC122 is a synchronous step-up hysteretic DC-DC converter utilizing a 1.2MHz fixed frequency switching architecture. It provides a fixed 3.3V output from an input voltage as low as 0.7V, with an unloaded startup input voltage of 0.85V.

The SC122 operates exclusively in PSAVE regulation mode (bursts of switching boost cycles, alternating with periods of an output-high-impedance state). It has quiescent current consumption as little as 40µA into the OUT pin. It features anti-ringing circuitry for reduced EMI in noise sensitive applications. The boost cycles can be disabled with an active-high enable input. While disabled, the output remains in a high impedance state to preserve the charge on the output capacitor. This permits ultra-low idle quiescent currents in applications in which the SC122 can be periodically enabled by an external controller to recharge the output capacitor.

The regulator control circuitry is shown in the Block Diagram. It is comprised of a feedback controller, an internal 1.2MHz oscillator, an n-channel Field Effect Transistor (FET) between the LX and GND pins, and a p-channel FET between the LX and OUT pins. The current flowing through both FETs is monitored and limited as required for startup and PSAVE regulator operation. An external inductor must be connected between the IN pin and the LX pin.

During the burst phase of PSAVE operation, the controller alternates between the on-state and the off-state. During the on-state the n-channel FET is turned on, grounding the inductor at the LX pin. This causes the current flowing from the input supply through the inductor to ground to ramp up. The on-state continues until the first of two limits is reached, either the n-channel current limit  $I_{\text{LIM(N)'}}$  or the ontime limit  $T_{\text{ON-MAX}} = 0.9 \times 1/f_{\text{OSC}}$ . Then during the off-state, the n-channel FET is turned off and the p-channel FET is turned on, connecting the inductor between IN and OUT. The (now decreasing) inductor current flows from the input to the output, transferring the inductor energy to the output and boosting the output voltage above the input voltage for the remainder of the cycle period  $T = 1/f_{\text{OSC}}$ . The cycle then repeats to re-energize the inductor.

The burst phase continues until  $V_{\rm OUT}$  reaches an upper voltage threshold, at which point both FETs are turned off.

This begins the high-impedance phase. The output capacitor then discharges into the load until  $V_{\text{OUT}}$  reaches a lower voltage threshold, which initiates a new burst phase. The upper and lower voltage thresholds differ by approximately 50mV, and were chosen to provide an average output voltage of 3.3V. The time between bursts is determined by the discharge rate of the output capacitor, which depends on the value of output capacitance and the magnitude of the applied load. Figure 1 illustrates PSAVE regulation.

Figure 1 — PSAVE Regulation Waveforms

### **The Enable Pin**

The EN pin is a high impedance logical input that can be used to enable or disable the SC122 under processor control.  $V_{EN} > 0.4V$  will enable the output. The startup sequence from the EN pin is identical to the startup sequence from the application of input power.

$V_{EN} < 0.1V$  will disable regulation and set the LX pin in a high-impedance state (turn off both FET switches). The OUT pin is also left in a high-impedance state when disabled. The SC122 can be disabled while maintaining the output voltage on the output capacitor, for the lowest possible quiescent current, while supporting a low application idle state load. The SC122 can then be periodically re-enabled for a brief time to refresh the charge held on the output capacitor, then disabled for an extended time as determined by the discharge rate of the output capacitor while supplying the idle-state load current. For  $V_{IN} > V_{IN-Restart'}$  and over the full specified temperature range, regulation will be fully enabled within 300µs of a high voltage on the EN pin with  $V_{OUT}$  discharged to as low as 2.5V.

### **Applications Information (continued)**

A suggested very low duty cycle refresh oscillator circuit is included on the SC122 EVB-RM, the SC122 Evaluation Board with Refresh Modulation.

# Regulator Startup, Short Circuit Protection, and Current Limits

The SC122 permits power up at input voltages from 0.85V to 1.6V. Startup current limiting of the internal switching n-channel and p-channel FET power devices protects them from damage in the event of a short between OUT and GND. This protection prevents startup into an excessive load.

At the beginning of the cycle, the p-channel FET between the LX and OUT pins turns on with its current limited to approximately 100mA, the short-circuit output current. When  $V_{\text{OUT}}$  approaches  $V_{\text{IN}}$  (still below 1.7V), the n-channel current limit is set to 350mA (the p-channel limit is disabled), an internal oscillator turns on (approximately 200kHz), and a fixed 75% duty cycle PWM-type operation begins. When the output voltage exceeds 1.7V, fixed frequency PSAVE operation begins, with the duty cycle determined by an n-channel FET peak current limit of 350mA.

Note that startup with a regulated active load is not the same as startup with a resistive load. The resistive load output current increases proportionately as the output voltage rises until it reaches  $V_{\text{OUT}}/R_{\text{LOAD'}}$  while a regulated active load presents a constant load as the output voltage rises from 0V to  $V_{\text{OUT'}}$ . Note also that if the load applied to the output exceeds the startup current limit, the criterion to advance to the next startup stage may not be achieved. In this situation startup may pause at a reduced output voltage until the load is reduced further.

### **Output Overload and Recovery**

As the output load increases, the duration of each burst increases, and the time between bursts decreases. The output load reaches its maximum when the burst duration becomes indefinite (and the time between bursts becomes zero). At this time, all the energy stored in the inductor during the on-time portion of each burst cycle is discharged into the output during off-time. The inductor current reduces to zero just as the next on-time begins.

Above this critical maximum load, the output voltage will decrease rapidly, and the startup current and switching

limits will be invoked in reverse order as the output voltage falls through its various startup voltage thresholds. How far the output voltage drops depends on the load voltage vs. current characteristic.

A reduction in input voltage, such as a discharging battery, will lower the load current at which overload occurs. At the overload threshold, the energy stored in the inductor at the end of each on-time is the same for all  $V_{IN}$ . But since the voltage increase above the input voltage is greater, the available output current,  $I_{OUT} = P/(V_{OUT} - V_{IN})$ , must decrease.

When an overload has occurred, the load must be decreased to permit recovery. The conditions required for overload recovery are identical to those required for successful initial startup.

### **Anti-ringing Circuitry**

When both FET switches are simultaneously turned off, an internal switch between the IN and LX pins is closed. This provides a moderate resistance path across the inductor to dampen the oscillations at the LX pin. This effectively reduces EMI that can develop from the resonant circuit formed by the inductor and the drain capacitance at LX. The anti-ringing circuitry is disabled between PSAVE bursts.

#### **Inductor Selection**

The inductance value primarily affects the amplitude of inductor current ripple ( $\Delta I_L$ ). The inductor peak current  $I_{L-max} = I_{L-avg} + \Delta I_L/2$ , where  $I_{L-avg}$  is the inductor current averaged over a full on/off cycle, is subject to the n-channel FET peak current limit  $I_{LIM(N)}$ . The inductor average current is equal to the output load current. Increasing inductance reduces  $\Delta I_L$  and therefore increases the maximum supportable output current.

The performance plots of this datasheet were obtained with  $L=4.7\mu H$ . Larger values of inductance can provide higher maximum output currents.

Any chosen inductor should have low DCR, compared to the  $R_{DS-ON}$  of the FET switches, to maintain efficiency. For DCR <<  $R_{DS-ON}$ , further reduction in DCR will provide diminishing benefit. The inductor  $I_{SAT}$  value must exceed  $I_{LIM(N)}$ . The inductor self-resonant frequency should exceed

## **Applications Information (continued)**

$5 \times f_{osc}$ . Any inductor with these properties should provide satisfactory performance.

The following table lists the manufacturers of recommended inductor options.

| Manufacturer/<br>Part #  | Value<br>(μΗ) | DCR<br>(mΩ) | Rated<br>Current<br>(mA) | Tolerance<br>(%) | Dimensions<br>L×W×H<br>(mm) |

|--------------------------|---------------|-------------|--------------------------|------------------|-----------------------------|

| Sumida 5508472xxxx       | 4.7           | 3800        | 90                       | 2/5/10/20        | 2.2 × 1.4 × 1.6             |

| Murata<br>LQM31PN4R7M00L | 4.7           | 300         | 700                      | 20               | 3.2 × 1.6 × 0.85            |

#### **Capacitor Selection**

Low ESR capacitors such as X5R or X7R type ceramic capacitors are recommended for input bypassing and output filtering. Low-ESR tantalum capacitors are not recommended due to possible reduction in capacitance seen at the switching frequency of the SC122. Ceramic capacitors of type Y5V are not recommended as their temperature coefficients make them unsuitable for this application.

The input and output each require a minimum capacitance value of  $10\mu F$  at the programmed output voltage. This must be considered when choosing small package size capacitors as the DC bias must be included in their derating to ensure this required value. For example, a  $10\mu F$  0805 capacitor may provide sufficient capacitance at low output voltages but may be too low at higher output voltages. Therefore, a higher nominal capacitance value may be required to provide the minimum of  $10\mu F$  at these higher output voltages. Additional output capacitance can be used extend the time between bursts, or to improve load transient response. The following table lists recommended capacitors.

| Manufacturer/<br>Part Number | Value<br>(μF) | Rated Voltage<br>(VDC) | Туре | Case<br>Size |

|------------------------------|---------------|------------------------|------|--------------|

| Murata<br>GRM21BR60J226ME39B | 22            | 6.3                    | X5R  | 0805         |

| Murata<br>GRM31CR71A226KE15L | 22            | 10                     | X7R  | 1206         |

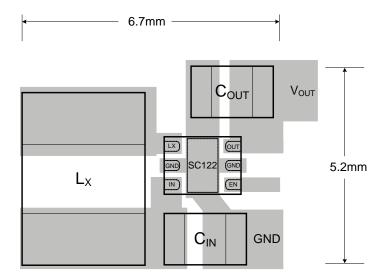

### **PCB Layout Considerations**

Good layout can enhance the performance of the DC-DC converter and can avoid EMI problems, ground bounce, and resistive voltage losses. The recommended layout is shown in Figure 2.

The following simple design rules can be implemented to ensure good layout:

- Place the inductor and filter capacitors as close to the device as possible and use short wide traces between the power components.

- Maximize ground metal on the component side to improve the return connection and thermal dissipation. Separation between the LX node and GND should be maintained to avoid coupling capacitance between the LX node and the ground plane.

- Use a ground plane with several vias connecting to the component side ground to further reduce noise interference on sensitive circuit nodes.

Figure 2 — Recommended Layout

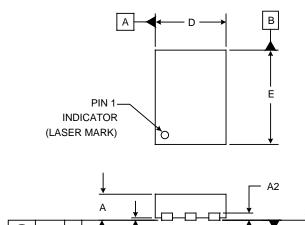

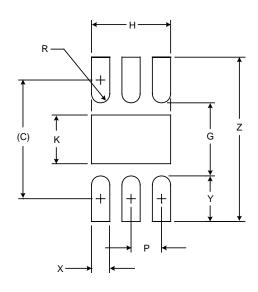

# Outline Drawing — MLPD-UT-6 1.5x2

| DIMENSIONS |      |          |      |             |         |      |

|------------|------|----------|------|-------------|---------|------|

| DIM        |      | INCHES   |      | MILLIMETERS |         |      |

| DIM        | MIN  | NOM      | MAX  | MIN         | NOM     | MAX  |

| Α          | .020 | -        | .024 | 0.50        | -       | 0.60 |

| A1         | .000 | -        | .002 | 0.00        | ı       | 0.05 |

| A2         |      | (.006)   |      |             | (.152)  |      |

| b          | .007 | .010     | .012 | 0.18        | 0.25    | 0.30 |

| D          | .055 | .059     | .063 | 1.40        | 1.50    | 1.60 |

| D1         | .035 | -        | .055 | 0.90        | 1       | 1.40 |

| Е          | .075 | .079     | .083 | 1.90        | 2.00    | 2.10 |

| E1         | .026 | .031     | .035 | 0.65        | 0.80    | 0.90 |

| е          |      | .020 BSC |      |             | 0.50 BS | С    |

| L          | .012 | .014     | .016 | 0.30        | 0.35    | 0.40 |

| N          |      | 6        |      |             | 6       |      |

| aaa        |      | .003     |      |             | 0.08    |      |

| bbb        |      | .004     |      |             | 0.10    |      |

#### NOTES:

1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

bxN

bbb M C A B

2. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS TERMINALS.

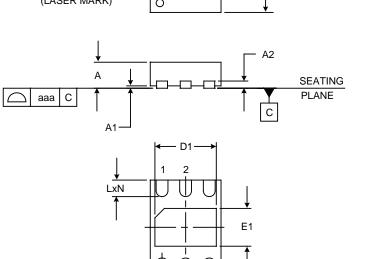

### Land Pattern — MLPD-UT-6 1.5x2

|     | DIMENSIONS |             |  |  |  |  |

|-----|------------|-------------|--|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |  |

| С   | (.077)     | (1.95)      |  |  |  |  |

| G   | .047       | 1.20        |  |  |  |  |

| Н   | .051       | 1.30        |  |  |  |  |

| K   | .031       | 0.80        |  |  |  |  |

| Р   | .020       | 0.50        |  |  |  |  |

| R   | .006       | 0.15        |  |  |  |  |

| Х   | .012       | 0.30        |  |  |  |  |

| Υ   | .030       | 0.75        |  |  |  |  |

| Z   | .106       | 2.70        |  |  |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

## **Contact Information**

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Semtech manufacturer:

Other Similar products are found below:

FAN53610AUC33X FAN53611AUC123X FAN48610BUC33X FAN48610BUC45X FAN48617UC50X R3 430464BB KE177614

FAN53611AUC12X MAX809TTR NCV891234MW50R2G NCP81103MNTXG NCP81203PMNTXG NCP81208MNTXG

NCP81109GMNTXG SCY1751FCCT1G NCP81109JMNTXG AP3409ADNTR-G1 NCP81241MNTXG LTM8064IY LT8315EFE#TRPBF

LTM4664EY#PBF LTM4668AIY#PBF NCV1077CSTBT3G XCL207A123CR-G MPM54304GMN-0002 MPM54304GMN-0004

MPM54304GMN-0003 AP62300Z6-7 MP8757GL-P MIC23356YFT-TR LD8116CGL HG2269M/TR OB2269 XD3526 U6215A U6215B

U6620S LTC3412IFE LT1425IS MAX25203BATJA/VY+ MAX77874CEWM+ XC9236D08CER-G MP3416GJ-P BD9S201NUX-CE2

MP5461GC-Z MPQ4415AGQB-Z MPQ4590GS-Z MAX38640BENT18+T MAX77511AEWB+