# SC2602/SC2602A

# Synchronous Voltage Mode Controller for Distributed Power Supply Applications

## **POWER MANAGEMENT**

#### Description

The SC2602 and SC2602A are low-cost, full featured, synchronous voltage-mode controllers designed for use in single ended power supply applications where efficiency is of primary concern. Synchronous operation allows for the elimination of heat sinks in many applications. The SC2602s are ideal for implementing DC/DC converters needed to power advanced microprocessors in low cost systems, or in distributed power applications where efficiency is important. Internal level-shift, high-side drive circuitry, and preset shoot-thru control, allows the use of inexpensive N-channel power switches.

SC2602s features include temperature compensated voltage reference, triangle wave oscillator and current sense comparator circuitry. Power good signaling, shutdown, and over voltage protection are also provided.

The SC2602 operates at a fixed 200kHz and the SC2602A at 500kHz, providing a choice for optimum compromise between efficiency, external component size, and cost.

Two SC2602s can be used together to sequence power up of telecom systems. The power good of the first SC2602 connected to the enable of the second SC2602 makes this possible.

#### **Features**

- Synchronous operation for high efficiency (95%)

- ◆ R<sub>DS(ON)</sub> current sensing

- On-chip power good and OVP functions

- ◆ Small size with minimum external components

- Soft Start

- Enable function

#### **Applications**

- Microprocessor core supply

- ◆ Low cost synchronous applications

- ◆ Voltage Regulator Modules (VRM)

- DDR termination supplies

- Networking power supplies

- ◆ Sequenced power supplies

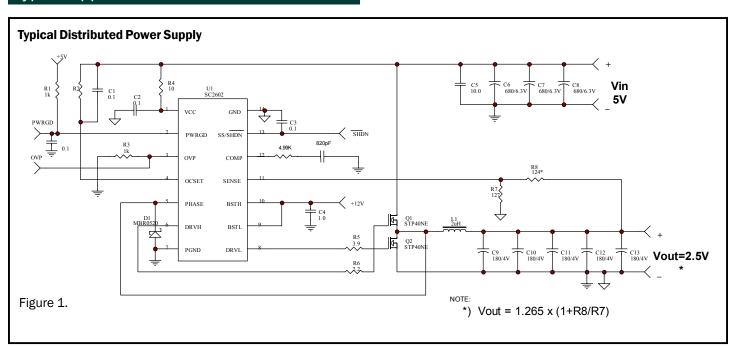

#### **Typical Application Circuit**

# Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. Exposure to Absolute Maximum rated conditions for extended periods of time may affect device reliability.

| Parameter                              | Symbol            | Maximum                | Units |

|----------------------------------------|-------------------|------------------------|-------|

| VCC, BSTL to GND                       | V <sub>IN</sub>   | -1.0 to 16 (20V Surge) | V     |

| PGND to GND                            |                   | ± 0.5                  | V     |

| PHASE to GND <sup>(1)</sup>            |                   | -0.5 to 18 (20V Surge) | V     |

| BSTH to PHASE                          |                   | 16 (20V Surge)         | V     |

| Thermal Resistance Junction to Case    | $\theta_{JC}$     | 45                     | °C/W  |

| Thermal Resistance Junction to Ambient | $\theta_{JA}$     | 115                    | °C/W  |

| Operating Temperature Range            | T <sub>A</sub>    | -40 to +85             | °C    |

| Maximum Junction Temperature           | T <sub>J</sub>    | 125                    | °C    |

| Storage Temperature Range              | T <sub>STG</sub>  | -65 to +150            | °C    |

| Lead Temperature (Soldering) 10 Sec.   | T <sub>LEAD</sub> | 300                    | °C    |

| ESD Rating (Human Body Model)          | ESD               | 2                      | kV    |

Note: (1) -1.5V to 20V for 25ns repetitive every cycle.

#### **Electrical Characteristics**

Unless specified:  $V_{CC} = 4.75V$  to 12.6V; GND = PGND = 0V; FB =  $V_{O}$ ;  $V_{BSTL} = 12V$ ;  $V_{BSTH-PHASE} = 12V$ ;  $V_{DSTH-PHASE} = 12V$

| Parameter                  | Conditions                           | Min | Тур | Max  | Units |

|----------------------------|--------------------------------------|-----|-----|------|-------|

| Power Supply               | 1                                    |     |     |      |       |

| Supply Voltage             | VCC                                  | 4.2 |     | 12.6 | V     |

| Supply Current             | EN = VCC                             |     | 6   | 10   | mA    |

| Line Regulation            | VO = 2.5V                            |     | 0.5 |      | %     |

| Error Amplifier            |                                      |     |     |      |       |

| Transconductance           | Gm                                   |     | 1.8 |      | mS    |

| Gain (AOL)                 |                                      |     | 50  |      | dB    |

| Input Bias                 |                                      |     | 5   | 8    | μΑ    |

| Oscillator                 |                                      |     |     |      |       |

| Oscillator Frequency       | SC2602                               | 180 | 200 | 220  | kHz   |

|                            | SC2602A                              | 450 | 500 | 550  |       |

| Oscillator Max Duty Cycle  |                                      | 90  | 95  |      | %     |

| Internal Ramp Peak to Peak |                                      |     | 1   |      | V     |

| MOSFET Drivers             |                                      |     |     |      |       |

| DH Source/Sink             | BSTH - DH = 4.5V,<br>DH- PHASE = 2V  | 1   |     |      | А     |

| DL Source/Sink             | BSTL - DL = 4.5V.<br>DL - PGND. = 2V | 1   |     |      | А     |

## Electrical Characteristics (Cont.)

Unless specified:  $V_{CC}$  = 4.75V to 12.6V; GND = PGND = 0V; FB =  $V_{O}$ ;  $V_{BSTL}$  = 12V;  $V_{BSTH-PHASE}$  = 12V;  $V_{DSTH-PHASE}$  = 12V;  $V_{DST$

| Parameter              | Conditions                      | Min   | Тур   | Max   | Units |

|------------------------|---------------------------------|-------|-------|-------|-------|

| PROTECTION             | PROTECTION                      |       |       |       |       |

| OVP Threshold Voltage  |                                 |       | 20    |       | %     |

| OVP Source Current     | V <sub>OVP</sub> = 3V           | 10    |       |       | mA    |

| Power Good Threshold   |                                 | 88    |       | 112   | %     |

| Dead Time              |                                 | 45    |       | 100   | ns    |

| Over current Set Isink | 2.0V ≤ V <sub>OCSET</sub> ≤ 12V | 180   | 200   | 220   | μΑ    |

| Reference              |                                 |       |       |       |       |

| Reference Voltage      | 0°C to 70°C                     | 1.252 | 1.265 | 1.278 | V     |

| Accuracy               |                                 | -1    |       | +1    | %     |

| Soft Start             |                                 |       |       |       |       |

| Charge Current         | V <sub>SS</sub> = 1.5V          | 8.0   | 10    | 12    | μA    |

| Discharge Current      | V <sub>ss</sub> = 1.5V          |       | 1.5   |       | μA    |

#### Note:

(1) Specification refers to application circuit (Figure 1).

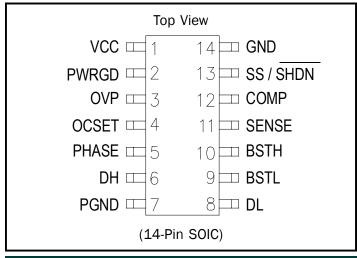

# Pin Configuration

# Ordering Information

| Device <sup>(2)</sup> | Frequency        | Package <sup>(1)</sup> |

|-----------------------|------------------|------------------------|

| SC2602STRT            | 200kHz           | SO-14                  |

| SC2602ASTRT           | 500kHz           |                        |

| SC2602EVB             | Evaluation Board |                        |

#### Notes:

- (1) Only available in tape and reel packaging. A reel contains 2500 devices.

- (2) Lead free product. This product is fully WEEE and RoHS compliant.

## Pin Descriptions

| Pin # | Pin Name | Pin Function                                                |

|-------|----------|-------------------------------------------------------------|

| 1     | VCC      | Chip supply voltage.                                        |

| 2     | PWRGD    | Logic high indicates correct output voltage.                |

| 3     | OVP      | Over voltage protection.                                    |

| 4     | OCSET    | Sets the converter overcurrent trip point.                  |

| 5     | PHASE    | Input from the phase node between the MOSFETs.              |

| 6     | DH       | High side driver output.                                    |

| 7     | PGND     | Power ground.                                               |

| 8     | DL       | Low side driver output.                                     |

| 9     | BSTL     | Bootstrap, low side driver.                                 |

| 10    | BSTH     | Bootstrap, high side driver.                                |

| 11    | SENSE    | Voltage sense input.                                        |

| 12    | COMP     | Compensation pin.                                           |

| 13    | SS/SHDN  | Soft start. A capacitor to ground sets the slow start time. |

| 14    | GND      | Signal ground.                                              |

#### Note:

(1) All logic level inputs and outputs are open collector TTL compatible.

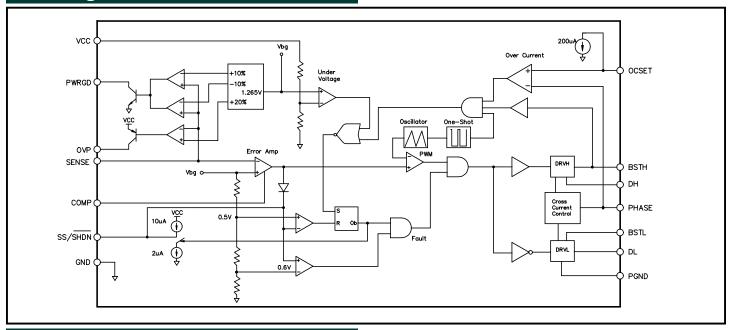

## **Block Diagram**

# Theory of Operation

#### **Synchronous Buck Converter**

Primary  $V_{\text{CORE}}$  power is provided by a synchronous, voltage-mode pulse width modulated (PWM) controller. This section has all the features required to build a high efficiency synchronous buck converter, including "Power Good" flag, shut-down, and cycle-by-cycle current limit.

The output voltage of the synchronous converter is set and controlled by the output of the error amplifier. The external resistive divider reference voltage is derived from an internal trimmed-bandgap voltage reference (See Fig. 1). The inverting input of the error amplifier receives its voltage from the SENSE pin.

The internal oscillator uses an on-chip capacitor and trimmed precision current sources to set the oscillation frequency to 200kHz/500kHz. The triangular output of the oscillator sets the reference voltage at the inverting input of the comparator. The non-inverting input of the comparator receives it's input voltage from the error amplifier. When the oscillator output voltage drops below the error amplifier output voltage, the comparator output goes high. This pulls DL low, turning off the low-side FET, and DH is pulled high, turning on the high-side FET (once the cross-current control allows it). When the oscillator voltage rises back above the error amplifier output voltage, the comparator output goes low. This pulls DH low, turning off the high-side FET, and DL is pulled high, turning on the low-side FET (once the cross-current control allows it).

As SENSE increases, the output voltage of the error amplifier decreases. This causes a reduction in the ontime of the high-side MOSFET connected to DH, hence lowering the output voltage.

#### **Under Voltage Lockout**

The under voltage lockout circuit of the SC2602 assures that the high-side MOSFET driver outputs remain in the off state whenever the supply voltage drops below set parameters. Lockout occurs if  $V_{\rm cc}$  falls below 4.1V. Normal operation resumes once  $V_{\rm cc}$  rises above 4.2V.

#### **Over-Voltage Protection**

The over-voltage protection pin (OVP) is high only when the voltage at SENSE is 20% higher than the target value programmed by the external resistor divider. The OVP pin is internally connected to a PNP's collector.

#### **Power Good**

The power good function is to confirm that the regulator outputs are within  $\pm 10\%$  of the programmed level. PWRGD remains high as long as this condition is met. PWRGD is connected to an internal open collector NPN transistor.

## Applications Information (Cont.)

#### **Soft Start**

Initially, SS/ $\overline{\text{SHDN}}$  sources 10µA of current to charge an external capacitor. The outputs of the error amplifiers are clamped to a voltage proportional to the voltage on SS/ $\overline{\text{SHDN}}$ . This limits the on-time of the high-side MOSFETs, thus leading to a controlled ramp-up of the output voltages.

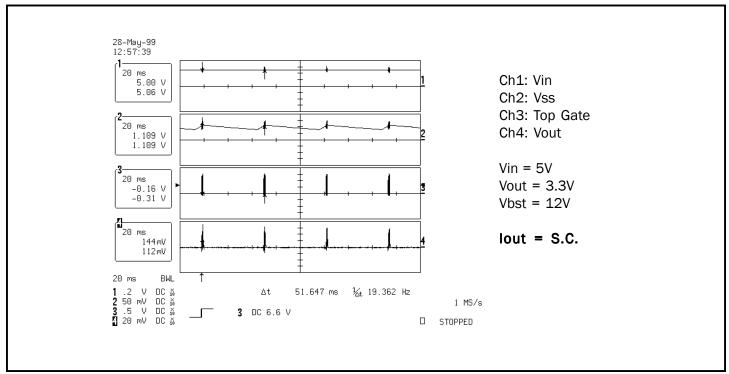

## $R_{DS(ON)}$ Current Limiting

The current limit threshold is set by connecting an external resistor from the  $V_{\rm cc}$  supply to OCSET. The voltage drop across this resistor is due to the 200µA internal sink sets the voltage at the pin. This voltage is compared to the voltage at the PHASE node. This comparison is made only when the high-side drive is high to avoid false current limit triggering due to uncontributing measurements from the MOSFETs off-voltage. When the voltage at PHASE is less than the voltage at OCSET, an overcurrent condition occurs and the soft start cycle is initiated. The synchronous switch turns off and SS/SHDN starts to sink 2µA. When SS/SHDN reaches 0.8V, it then starts to source 10µA and a new cycle begins.

#### **Hiccup Mode**

During power up, the SS/SHDN pin is internally pulled low until VCC reaches the undervoltage lockout level of 4.2V. Once  $V_{\rm CC}$  has reached 4.2V, the SS/SHDN pin is released and begins to source 10µA of current to the external soft-start capacitor. As the soft-start voltage rises, the output of the internal error amplifier is clamped to this voltage. When the error signal reaches the level of the internal triangular oscillator, which swings from 1V to 2V at a fixed frequency of 200kHz/500kHz, switching occurs. As the error signal crosses over the oscillator signal, the duty cycle of the PWM signal continues to increase until the output comes into regulation. If an over-current condition has not occurred the soft-start voltage will continue to rise and level off at about 2.2V.

An over-current condition occurs when the high-side drive is turned on, but the PHASE node does not reach the voltage level set at the OCSET pin. The PHASE node is sampled only once per cycle during the valley of the triangular oscillator. Once an over-current occurs, the high-side drive is turned off and the low-side drive turns on and the SS/SHDN pin begins to sink 2µA. The soft-start voltage will begin to decrease as the 2µA of current discharges the external capacitor. When the soft-start voltage reaches 0.8V, the SS/SHDN pin will begin to source 10µA and begin to charge the external capacitor causing the soft-start voltage to rise again. Again, when the soft-start voltage reaches the level of the internal oscillator, switching will occur.

If the over-current condition is no longer present, normal operation will continue. If the over-current condition is still present, the SS/SHDN pin will again begin to sink 2µA. This cycle will continue indefinitely until the over-current condition is removed.

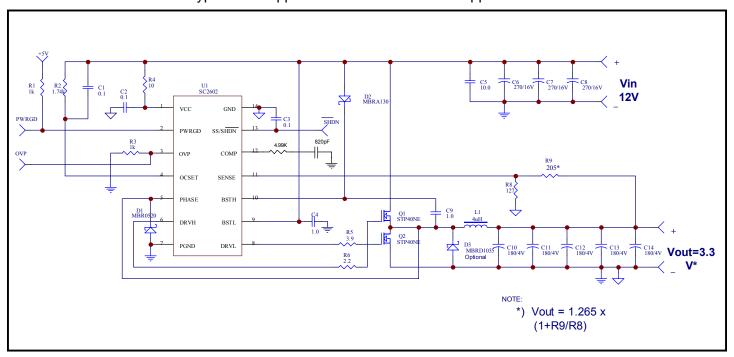

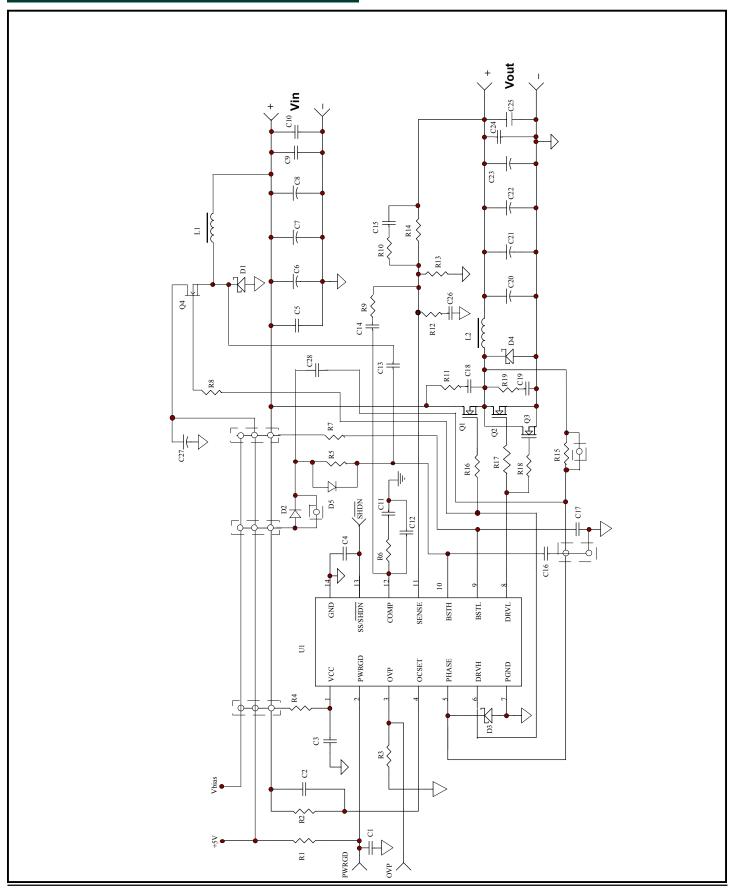

In conclusion, below is shown a typical "12V Application Circuit" which has a BSTH voltage derived by bootstrapping input voltage to the PHASE node through diode D1. This circuit is very useful in cases where only input power of 12V is available.

In order to prevent substrate glitching, a small-signal diode should be placed in close proximity to the chip with cathode connected to PHASE and anode connected to PGND.

# **Application Circuit**

Typical 12V Application Circuit with Bootstrapped BSTH

## Typical Characteristics

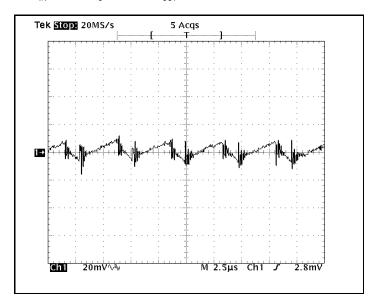

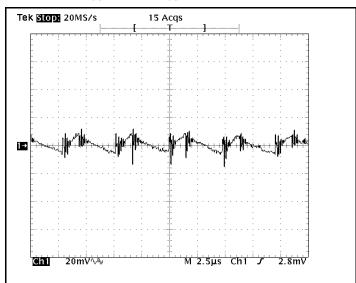

#### **Output Ripple Voltage**

Ch1: Vo\_rpl

1.

$$V_{IN} = 5V$$

;  $V_{O} = 3.3V$ ;  $I_{OUT} = 12A$

Wave forms are shown for SC2602 and are similar for SC2602A but at higher frequency.

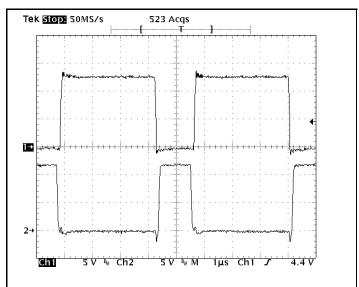

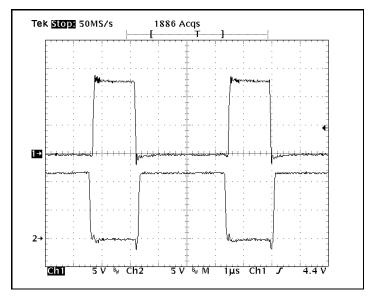

#### **Gate Drive Waveforms**

Ch1: Top FET Ch2: Bottom FET

Ch1: Top FET Ch2: Bottom FET

# Typical Characteristics (Cont.)

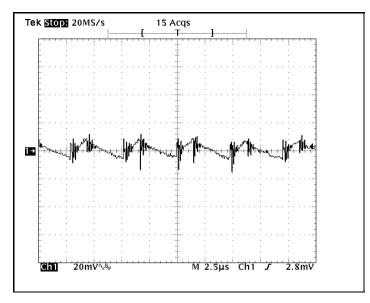

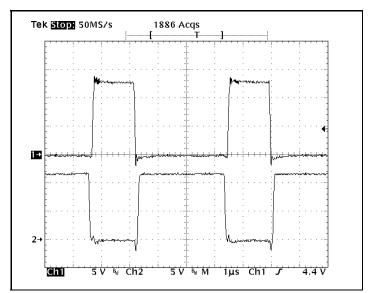

Ch1: Vo\_rpl

2.

$$V_{IN} = 5V$$

;  $V_{OUT} = 1.3V$ ;  $I_{OUT} = 12A$

Ch1: Top FET Ch2: Bottom FET

# Typical Characteristics (Cont.)

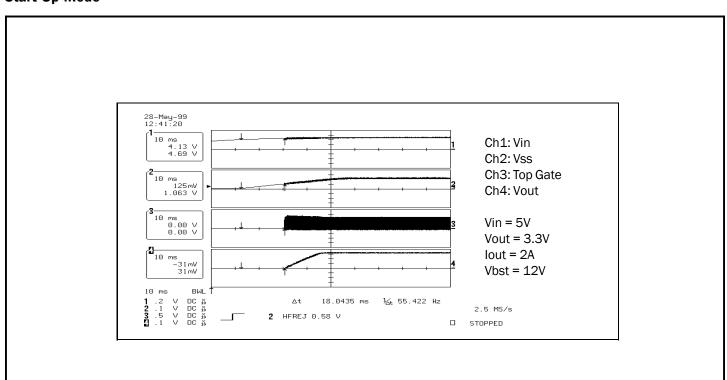

#### **Hiccup Mode**

#### **Start Up Mode**

# Typical Characteristics (Cont.)

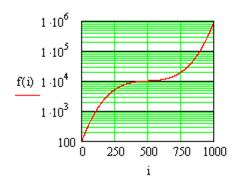

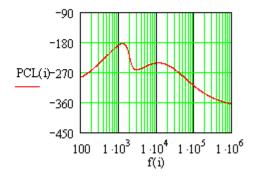

#### **Math Cad Close Loop Stability Analysis**

General Equational Sample Frequencies Calculations

$$i := 1, 2.. 10^3$$

$$Fc := 10 \cdot 10^3$$

$$\mathbf{f}(i) := Fc \cdot 1.0005^{i - 500 + 10^{-4.16} \cdot (i - 500)^3}$$

g(i) := if

$$\left(i - 900 \ge 0, \frac{i - 900}{100}, 0\right)$$

j :=  $(-1)^{.5}$

$$W(i) := 2\!\cdot\!\pi\!\cdot\! j\!\cdot\! f(i)$$

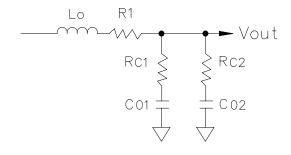

#### Output Filter Schematic:

#### Typical Characteristics (Cont.)

Output filter calculation

$$Lo := 4.3 \cdot 10^{-6} \qquad R1 := 5 \cdot 10^{-3} \qquad Co1 := 1500 \cdot 10^{-6} \qquad Rc1 := 20 \cdot 10^{-3} \qquad Co2 := 100 \cdot 10^{-6} \qquad Rc2 := 1 \cdot 10^{-3}$$

$$Zc1(i) := Rc1 + \frac{1}{Co1 \cdot W(i)} \qquad \qquad Zc2(i) := Rc2 + \frac{1}{Co2 \cdot W(i)} \qquad Zc(i) := \frac{Zc1(i) \cdot Zc2(i)}{Zc1(i) + Zc2(i)}$$

$$\mathsf{OF}(\mathfrak{j}) \coloneqq \frac{\mathsf{Zc}(\mathfrak{j})}{\mathsf{Ri} + \mathsf{Lo} \cdot \mathsf{W}(\mathfrak{j}) + \mathsf{Zc}(\mathfrak{j})} \\ \mathsf{Gof}(\mathfrak{j}) \coloneqq \left( \mathsf{Re}(\mathsf{OF}(\mathfrak{j}))^2 + \mathsf{Im}(\mathsf{OF}(\mathfrak{j}))^2 \right)^5$$

$GOF(i) := 20 \cdot log(Gof(i))$

$$C(i) := \frac{\text{Re}\Big(\text{OF}(i) \cdot j^{g(i)}\Big)}{\text{Gof}(i)} \qquad \qquad \text{S(i)} := \frac{\text{Im}\Big(\text{OF}(i) \cdot j^{g(i)}\Big)}{\text{Gof}(i)}$$

$$POF(i) := \frac{360}{2 \cdot \pi} \cdot acos(C(i)) \cdot if(S(i) \ge 0, 1, -1) + 180 \cdot if(S(i) \ge 0, -2, 0) - 90 \cdot g(i)$$

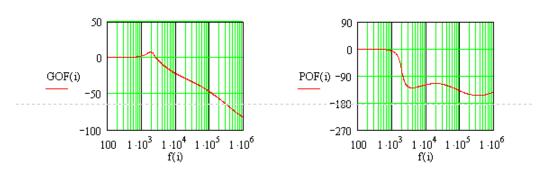

#### Output Filter Plots

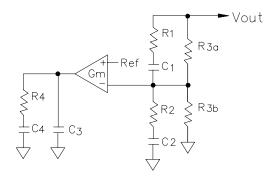

#### **Error Amplifier Schematic**

#### Typical Characteristics (Cont.)

Error Amplifier calculation

$$R1 := .1 \cdot 10^3$$

$$R2 := .1 \cdot 10^3$$

$$R4 := 15 \cdot 10^3$$

$$C3 := .01 \cdot 10^{-9}$$

$$C1 := 30 \cdot 10^{-9}$$

$$\begin{aligned} \text{R3a} &:= 10 \cdot 10^3 & \text{R1} &:= .1 \cdot 10^3 & \text{R2} &:= .1 \cdot 10^3 & \text{R4} &:= 15 \cdot 10^3 & \text{C3} &:= .01 \cdot 10^{-9} \\ \text{R3b} &:= 10 \cdot 10^3 & \text{C1} &:= 30 \cdot 10^{-9} & \text{C2} &:= 1000 \cdot 10^{-9} & \text{C4} &:= 100 \cdot 10^{-9} & \text{Gm} &:= 1.5 \cdot 10^{-3} \end{aligned}$$

$$Z1(i) := \frac{R3a \left(R1 + \frac{1}{C1 \cdot W(i)}\right)}{R3a + R1 + \frac{1}{C1 \cdot W(i)}}$$

$$Z2(i) := \frac{R3b \cdot \left(R2 + \frac{1}{C2 \cdot W(i)}\right)}{R3b + R2 + \frac{1}{C2 \cdot W(i)}}$$

$$Z1(\mathbf{i}) := \frac{R3a \cdot \left(R1 + \frac{1}{C1 \cdot W(\mathbf{i})}\right)}{R3a + R1 + \frac{1}{C1 \cdot W(\mathbf{i})}} \qquad Z2(\mathbf{i}) := \frac{R3b \cdot \left(R2 + \frac{1}{C2 \cdot W(\mathbf{i})}\right)}{R3b + R2 + \frac{1}{C2 \cdot W(\mathbf{i})}} \qquad Z3(\mathbf{i}) := \frac{\left(R4 + \frac{1}{C4 \cdot W(\mathbf{i})}\right) \cdot \frac{1}{C3 \cdot W(\mathbf{i})}}{R4 + \frac{1}{C4 \cdot W(\mathbf{i})} + \frac{1}{C3 \cdot W(\mathbf{i})}}$$

$$EA(i) := -\frac{Z2(i)}{Z1(i) + Z2(i)} \cdot Z3(i) \cdot Gn$$

$$EA(i) := -\frac{Z2(i)}{Z1(i) + Z2(i)} \cdot Z3(i) \cdot Gm \qquad \qquad Gea(i) := \left\{ Re(EA(i))^2 + Im(EA(i))^2 \right\}^{5}$$

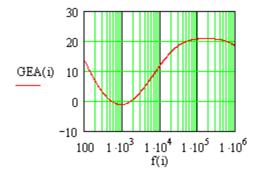

$$GEA(i) := 20 \cdot log(Gea(i))$$

$$C(i) := \frac{Re\left(EA(i) \cdot j^{g(i)}\right)}{Gea(i)}$$

$$C(i) := \frac{\text{Re}\Big(\text{EA}(i) \cdot j^{g(i)}\Big)}{\text{Gea}(i)} \qquad \qquad S(i) := \frac{\text{Im}\Big(\text{EA}(i) \cdot j^{g(i)}\Big)}{\text{Gea}(i)}$$

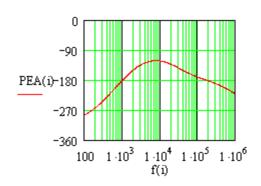

$$PEA(i) := \frac{360}{2 \cdot \pi} \cdot acos(C(i)) \cdot if(S(i) \ge 0, 1, -1) + 180 \cdot if(S(i) \ge 0, -2, 0) - 90 \cdot g(i)$$

Error Amplifier plots

# Typical Characteristics (Cont.)

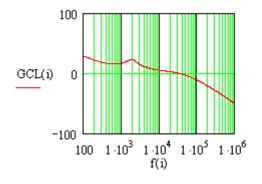

Close Loop Calculation

$$\begin{split} & \forall pp := \frac{1}{1.7} \\ & \text{CL}(i) := \text{OF}(i) \cdot \text{EA}(i) \cdot \frac{\forall m}{\forall pp} \\ & \text{Gcl}(i) := \left( \text{Re}(\text{CL}(i))^2 + \text{Im}(\text{CL}(i))^2 \right)^5 \\ & \text{GCL}(i) := 20 \cdot \log(\text{Gcl}(i)) \\ & \text{C}(i) := \frac{\text{Re}\left( \text{CL}(i) \cdot j^{g(i)} \right)}{\text{Gcl}(i)} \\ & \text{S}(i) := \frac{\text{Im}\left( \text{CL}(i) \cdot j^{g(i)} \right)}{\text{Gcl}(i)} \\ & \text{PCL}(i) := \frac{360}{2 \cdot \pi} \cdot \text{acos}(\text{C}(i)) \cdot \text{if}(\text{S}(i) \geq 0, 1, -1) + 180 \cdot \text{if}(\text{S}(i) \geq 0, -2, 0) - 90 \cdot g(i) \end{split}$$

#### Close Loop plots

# **Evaluation Board Schematic**

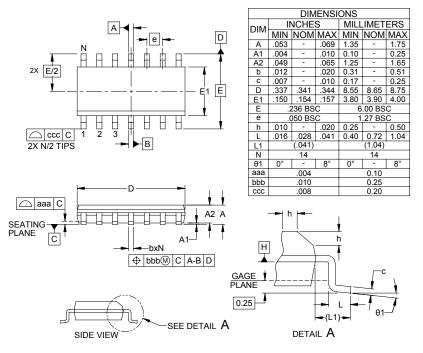

# Outline Drawing - S0-14

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

- 3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MS-012, VARIATION AB

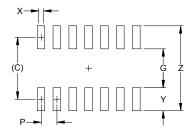

## Land Pattern - S0-14

| DIMENSIONS |        |             |

|------------|--------|-------------|

| DIM        | INCHES | MILLIMETERS |

| С          | (.205) | (5.20)      |

| G          | .118   | 3.00        |

| Р          | .050   | 1.27        |

| Χ          | .024   | 0.60        |

| Υ          | .087   | 2.20        |

| Z          | .291   | 7.40        |

#### NOTES:

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 2. REFERENCE IPC-SM-782A, RLP NO. 302A

## **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Semtech manufacturer:

Other Similar products are found below:

SC202AEVB SLVU2.8-4.T SX1243SKA433 SX8651EVKA SC3BH6 EBK-GS6080-00 SC183CULTRT SX9513EWLTRT

SX1276DVK1KAS SX1243SKA915 SX1211-11SKA868 JANTXV1N5811US JANTX1N4986 JANTXV1N5552 SM1231E868 GRP-DATA

JANTXV1N5806US GRP-DATA-JANS1N5811US 1N6147 SCHJ22.5K SX9310MINIEVKA EBK-GS3471-00 GRPA-DATA

JANTXV1N6463US GRP-A-DATA-JANTX1N4465 SX1302CSS868GW1 1N4469 SC3BA6 SM1211E868 SX1508BEVK SX1509BEVK

SX8674EVK GS1524-CKDE3 IOT434STK1-8 IOT915STK1-8 IOT922STK1-8 TS13102-QFNR SX1211-11SKA915 SM1212E433

1N6138US TS13102\_TS13103\_Combo\_PTO\_EVM RDK-12GCONV-01 IOT9USATREF-1 SX1232-32SKA868 SX1272DVK1BAS

SX1276DVK1IAS SX9500EVKA SA4684 SX9300EVKA JANTX1N5806T/R JANTX1N5806/TR GS3471-IBE3