# Neo-Iso™ TS13101M Galvanic Isolated Latching 60V Solid State Relay

#### **HIGH-RELIABILITY PRODUCTS**

#### **Features**

- Low Quiescent Operating Currents 2μΑ/4μA in OFF/ON state

- Scalable galvanic isolation from primary to secondary sides of the device

- Single control signal for on/off input (CLK)

Operation from 2.7V to 5.5V

Compatible with standard microcontrollers

- Switch Characteristics High voltage switch with bi-directional blocking in OFF state  $60V\ switch\ and\ 110m\Omega\ R_{DS(on)}$  Up to 4A operating current

- Transient protection for SW1 and SW2 to:

IEC 61000-4-2 (ESD) ±30kV (air), ±30kV (contact)

IEC 61000-4-4 (EFT) 40A (5/50ns) level 4

IEC 61000-4-5 (Surge/Lightning) 160V with 2Ω internal impedance (1.2/50µs)

## **Specification**

- Junction operating temperature -55°C to 125°C

- Packaged in a 20 pin QFN (4x4)

- Product is lead-free, Halogen Free, RoHS / WEEE compliant

### **Description**

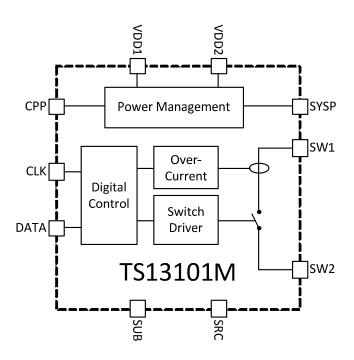

The TS13101M is a galvanically isolated 60V solid state relay with bi-directional blocking. The device includes a single integrated 110m $\Omega$  high voltage switch allowing high efficiency switching of power loads or other high current applications. The input pin, CLK, controls the turn on/off of the switch. When the correct CLK sequence is provided the switch will latch on and stay on until the turn off sequence is given or a fault is detected.

The TS13101M includes several protection features. Each switch has an integrated over-current shut-down to prevent device damage during short-circuit or other unusually high load conditions. If an over-current event is detected for a time, the FET is latched off until the CLK turn on sequence is given. While the CLK pin is active after an over-current event or in the event of an incorrect turn-on sequence, the DATA pin is toggled at ¼ the CLK frequency.

## **Applications**

- Power load/rail switching

- Input supply multiplexing

- Isolated power supplies

- Solid state relays

- HVAC control

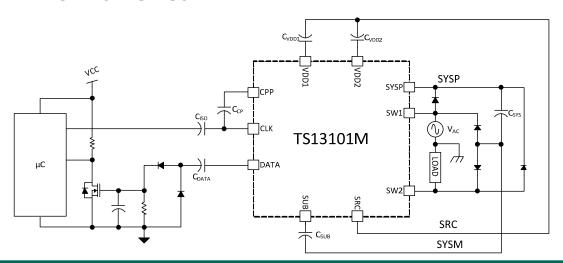

### TYPICAL APPLICATION CIRCUIT

**Rev 2.0**

TS13101M Final Datasheet Aug 3 2017

www.semtech.com

# **PIN DESCRIPTION**

| Pin# | Pin Name | Pin Function                | Description                                       |

|------|----------|-----------------------------|---------------------------------------------------|

| 1    | SRC      | Switch Driver Supply Return | Local common supply return                        |

| 2    | SW2      | Switch Output Node 2        |                                                   |

| 3    | SW1      | Switch Output Node 1        |                                                   |

| 4    | SW1      | Switch Output Node 1        |                                                   |

| 5    | SW2      | Switch Output Node 2        |                                                   |

| 6    | SW1      | Switch Output Node 1        |                                                   |

| 7    | SW2      | Switch Output Node 2        |                                                   |

| 8    | SW2      | Switch Output Node 2        |                                                   |

| 9    | DATA     | Data Output                 | AC Coupled Data Output                            |

| 10   | CLK      | Clock Input                 | AC Coupled Clock and Power Input                  |

| 11   | SYSP     | Positive System Voltage     |                                                   |

| 12   | СРР      | Charge Pump Cap             | Additional Cap used for lower voltage Clock drive |

| 13   | VDD1     | Internal Supply 1           | Bypass Capacitor for Internal Supply              |

| 14   | VDD2     | Internal Supply 2           | Bypass Capacitor for Internal Supply              |

| 15   | NC       | No Connect                  |                                                   |

| 16   | SUB      | IC Substrate Bias           | Connect C <sub>SUB</sub> Capacitor to SYSM        |

| 17   | NC       | No Connect                  |                                                   |

| 18   | SW1      | Switch Output Node 1        |                                                   |

| 19   | SW1      | Switch Output Node 1        |                                                   |

| 20   | SW2      | Switch Output Node 2        |                                                   |

| PAD  | PAD      | Power PAD                   | Must be floating or connected to SUB              |

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: TS13101M Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range unless otherwise noted. (1,2,3)

| Parameter                                                         | Range       | Unit |

|-------------------------------------------------------------------|-------------|------|

| SW1, SW2, SYSP (Peak Voltage, with respect to SUB, SRC)           | -0.5 to 60  | V    |

| SW1, SW2 (with respect to each other)                             | -60 to 60   | V    |

| CLK, DATA, VDD1, VDD2, CPP (with respect to SUB, SRC)             | -0.3 to 5.5 | V    |

| SUB                                                               | -60 to 0.3  | V    |

| Maximum Junction Temperature, T <sub>J MAX</sub>                  | 150         | °C   |

| Storage Temperature Range, T <sub>STG</sub>                       | -65 to 150  | °C   |

| Electrostatic Discharge – Human Body Model                        | ±2          | kV   |

| Electrostatic Discharge – IEC Contact (SW1 and SW2 Pins)(4)       | ±30         | kV   |

| Electrostatic Discharge – IEC Air Discharge (SW1 and SW2 Pins)(4) | ±30         | kV   |

| Peak IR Reflow Temperature (10s to 30s)                           | 260         | °C   |

#### Notes:

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to SRC terminal.

- (3) ESD testing is performed according to the respective JESD22 JEDEC standard

- (4) IEC ESD testing is performed on Semtech Product Evaluation Board TS13101-EVMX3.

# THERMAL CHARACTERISTICS

| Symbol | Parameter                                    | Value      | Unit |

|--------|----------------------------------------------|------------|------|

| ΘЈА    | Thermal Resistance Junction to Air (Note 1)  | 25         | °C/W |

| Өлс    | Thermal Resistance Junction to Case (Note 1) | 2.5        | °C/W |

| Tı     | Operating Junction Temperature Range         | -55 to 125 | °C   |

Note 1: Assumes 20LD 4x4 QFN with hi-K JEDEC board and 13.5 inch2 of 1 oz. Cu and 4 thermal vias connected to PAD

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                   | Parameter                                                                                             | Min | Тур | Max  | Unit   |

|--------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|------|--------|

| V <sub>sw</sub>          | AC Switch Voltage (RMS Voltage)                                                                       | -36 |     | 36   | V      |

| V <sub>sw</sub>          | DC or AC Peak Switch Voltage                                                                          | -51 |     | 51   | V      |

| C <sub>DATA</sub>        | Data Isolation Capacitor                                                                              |     | 100 |      | pF     |

| C <sub>ISO</sub>         | Clock Isolation Capacitor                                                                             |     | 680 |      | pF     |

| C <sub>CP</sub>          | Charge Pump Capacitor                                                                                 |     | 100 |      | pF     |

| C <sub>VDD1</sub>        | VDD1 Bypass Capacitor                                                                                 |     | 10  |      | nF     |

| C <sub>VDD2</sub>        | VDD2 Bypass Capacitor                                                                                 |     | 1   |      | μF     |

| C <sub>SUB</sub>         | Sub Capacitor                                                                                         |     | 100 |      | nF     |

| C <sub>SYS</sub>         | System Bypass Capacitor                                                                               |     | 100 |      | nF     |

| CLK Drive                |                                                                                                       |     |     |      |        |

| $V_{CLK}$                | Clock Drive Voltage; Amplitude of driven CLK signal, Drive Impedance $< 100\Omega$                    | 2.7 |     | 5.5  | V      |

| F <sub>CLK</sub>         | Clock Frequency to Turn on Switch                                                                     | 500 |     | 2000 | kHz    |

| N <sub>CLKON-INIT</sub>  | Number of CLK pulses to initialize Turn On                                                            | 3   |     | 8    | pulses |

| T <sub>LOW-ON</sub>      | CLK Low time during Turn On Sequence                                                                  | 10  |     | 20   | μs     |

| N <sub>CLKON</sub>       | CLK Pulses to Turn on SW After T <sub>LOW-ON</sub>                                                    | 15  |     |      | pulses |

| T <sub>CLKOFF-INIT</sub> | CLK Low time to Initialize Turn-Off                                                                   | 10  |     | 20   | μs     |

| N <sub>CLKOFF</sub>      | CLK Pulses to Enable Turn-Off After T <sub>CLKOFF-INIT</sub>                                          | 6   |     | 13   | pulses |

| N <sub>CLK-OFFDET</sub>  | CLK Pulses to Detect Incorrect Turn-On Sequence                                                       | 19  |     |      | pulses |

| T <sub>PRE-CHG</sub>     | Pre-Charge Time for VDD1, VDD2 when $ V_{SW2}-V_{SW1}  < 5.0V$<br>$V_{CLK} = 3.0V$ , $F_{CLK} = 1MHz$ | 50  |     |      | ms     |

## **ELECTRICAL CHARACTERISTICS**

Electrical Characteristics, T<sub>J</sub> = -55°C to 125°C (unless otherwise noted)

| Symbol                | Parameter                                 | Condition                                        | Min | Тур                 | Max | Unit |

|-----------------------|-------------------------------------------|--------------------------------------------------|-----|---------------------|-----|------|

| Supply Voltage        |                                           |                                                  |     |                     |     |      |

| I <sub>CLK-NORM</sub> | Normal Mode, CLK running                  | $V_{CLK} = 5.0V, F_{CLK} = 500kHz$               |     | 15                  |     | μΑ   |

| I <sub>CLK-NORM</sub> | Normal Mode, CLK running                  | $V_{CLK} = 3.0V, F_{CLK} = 1000kHz$              |     | 50                  |     | μΑ   |

| I <sub>CLK-STBY</sub> | Quiescent current                         | $V_{CLK} = 0V, C_{ISO} = 680pF$                  |     | 3                   |     | μΑ   |

| I <sub>SYSP</sub>     | Quiescent current                         | T」 < 125°C, Latch Mode                           |     | 3                   | 20  | μΑ   |

| DATA Output           |                                           |                                                  | ·   |                     |     |      |

| F <sub>DATA</sub>     | Data Frequency during<br>Current Shutdown |                                                  |     | F <sub>CLK</sub> /4 |     | kHz  |

| Output Switch         |                                           |                                                  |     |                     |     |      |

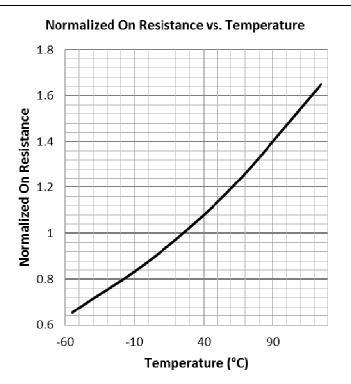

| R <sub>DS(on)</sub>   | On Resistance                             | T <sub>J</sub> = 25°C                            | 85  | 110                 | 135 | mΩ   |

| l <sub>OFF</sub>      | Off State Leakage                         | $V_{SYS} = V_{SW}, T_J < 125^{\circ}C$           |     | 0.1                 | 3   | μΑ   |

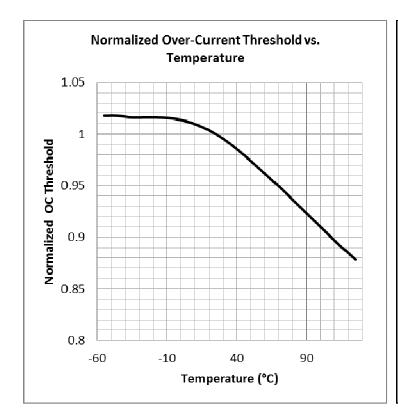

| I <sub>оитос</sub>    | Over Current Shutdown                     | T = 25°C                                         |     | 5.5                 |     | Α    |

| $OC_{FILT}$           | Output Over Current Deglitch              |                                                  |     | 25                  |     | μs   |

| $V_{CLAMP}$           | Differential SW1/2 Clamping<br>Voltage    | (SW1-SW2) or (SW2-SW1)<br>I <sub>SW</sub> = 50mA | 58  | 63                  | 68  | V    |

| $T_{CLKOFF}$          | Time for Turn Off                         |                                                  | 4   |                     | 10  | μs   |

## **PRODUCT CHARACTERISTICS**

## **APPLICATION WAVEFORMS**

### **SWITCH CONTROL**

The TS13101M CLK pin performs a dual function:

- 1. It provides the command sequences in level and timing that determine the state of the switch.

- 2. It provides a source of power by which the switch can operate.

The microcontroller provides the CLK signal to the switch by a coupling capacitor,  $C_{ISO}$ , that provides galvanic isolation between the microcontroller supply domain and that of the switch, the latter of which has a different reference voltage with respect to ground dependent on its state. Because of the requirement to source power, it is required that the microcontroller has a maximum source impedance of  $100\Omega$ .

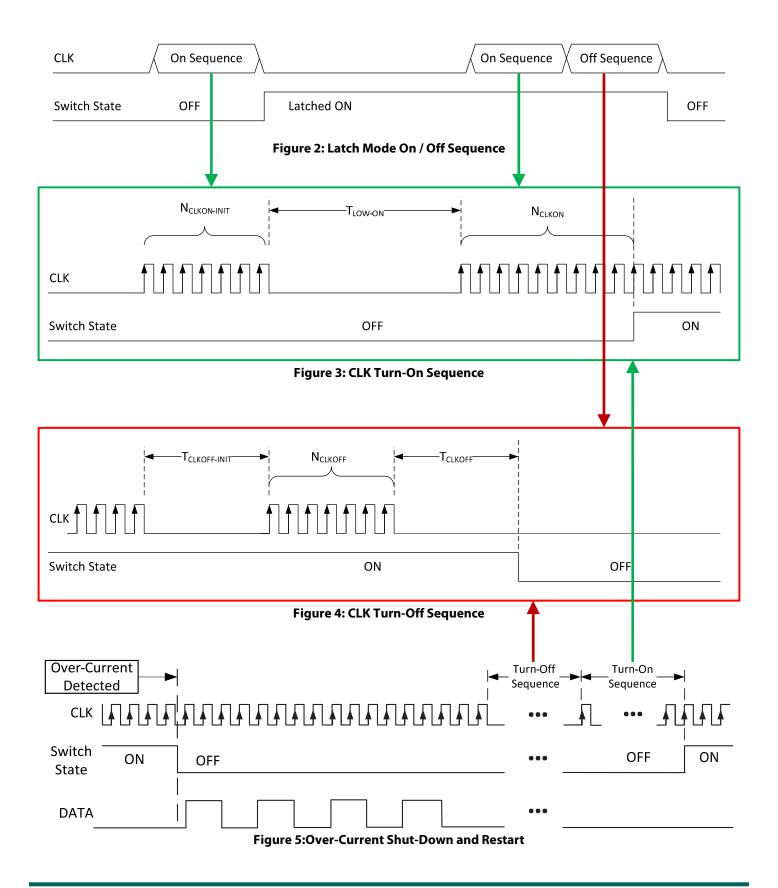

The CLK pin is used as a means to command the state of the switch by the ON and OFF sequences shown in Figure 2 through Figure 5. Figure 2 shows the state of the switch being changed by sending ON and OFF Sequences. On initial power up, the switch state will default to the OFF condition.

It is necessary to send a device ON Sequence to transition the device to the ON state, as shown in Figure 3. First a series of clocks,  $N_{\text{CLKON-INIT}}$ , of frequency  $F_{\text{CLK}}$  is transmitted, followed by a CLK low time of  $T_{\text{LOW-ON}}$ . Then another series of clocks of number  $N_{\text{CLKON}}$  is transmitted. On the final CLK edge the switch will be closed. Note that the CLK continues to cycle and the state of the DATA pin continues to be low. This indicates that the device is ON.

When it is desired to transition the device to the OFF state, the OFF Sequence must be transmitted via the microcontroller. This sequence is shown in Figure 4. Here the CLK is stopped for a period of  $T_{CLKOFF-INIT}$ , followed by a series of clocks of number  $N_{CLKOFF}$ . Then the CLK must be asserted low for a period  $T_{CLKOFF}$ , after which the switch will be opened. If the CLK resumes switching, the DATA pin will return a signal  $F_{CLK}$  / 4, indicating that the state of the switch is OFF.

Figure 5 shows the operation when an over-current event is detected, and the device autonomously transitions to the OFF state in order to protect itself and the load in the system. During the ON time, the CLK was being switched and the DATA pin was static, being held by the device in the low state. After the over-current event opens the switch, the DATA pin will start switching at F<sub>CLK</sub> / 4 to signal the microcontroller that the switch is no longer in the ON state. The microcontroller may infer from this that there has been a fault in the system. If diagnostics (performed elsewhere in the system) determine that the fault condition has been removed, the device may be returned to the ON state through the restart sequence shown. After an over-current event opens the switch, an OFF Sequence must be registered in the part before an ON Sequence can successfully transition the device back to the ON state. The DATA pin will assert low and stay low after the ON Sequence as long as load current remains below l<sub>OUTOC</sub>. If the switch transitions to the closed state and an over-current condition is detected, the process of Figure 5 will repeat.

#### **Failed Communication**

In the event of a failed ON command sequence (due to external interference, system transients, etc.) the DATA pin will begin sending a signal at frequency  $F_{CLK}$  / 4. Thus the microcontroller is alerted to a communication failure. Similarly, when an OFF command sequence has been sent, resuming CLK pulses after the  $T_{CLKOFF}$  time will result in the DATA pin sending a signal of frequency  $F_{CLK}$  / 4. If the DATA pulses do not commence after 23 CLK cycles, the microcontroller can discern that the OFF sequence was not received correctly and the switch is still in the closed state. It is up to the microcontroller to do this fault handling and rectify the situation.

TS13101M Final Datasheet Aug 3 2017 www.semtech.com 8 of 12

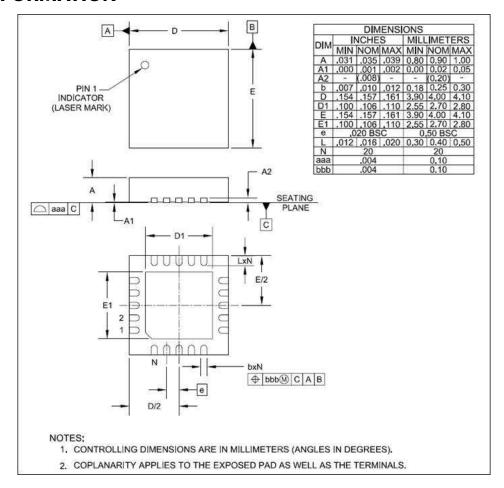

## **PACKAGE INFORMATION**

**Figure 6: Package Outline Drawing**

Figure 7: Device Symbolization

Notes:

YYWW = Year Calendar Week XXXXX = Semtech Lot Number

XXXXX = Lot Number (Continued)

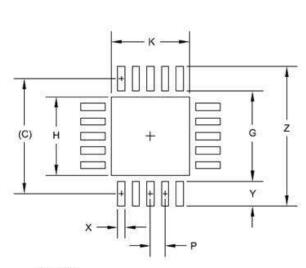

| DIMENSIONS |        |             |  |  |

|------------|--------|-------------|--|--|

| DIM        | INCHES | MILLIMETERS |  |  |

| С          | (.156) | (3,95)      |  |  |

| G          | .122   | 3.10        |  |  |

| Н          | .106   | 2.70        |  |  |

| K          | .106   | 2.70        |  |  |

| Р          | .020   | 0.50        |  |  |

| X          | .010   | 0.25        |  |  |

| Y          | .033   | 0.85        |  |  |

| Z          | .189   | 4.80        |  |  |

#### NOTES;

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE, FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

Figure 8: Recommended Board Layout Land Pattern

# **ORDERING INFORMATION**

| Part Number   | Description                       | Package                      |

|---------------|-----------------------------------|------------------------------|

| TS13101M-QFNR | Latching Galvanic Isolated Switch | 20-pin PQFN Reel (3,300 pcs) |

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2017

### **CONTACT INFORMATION**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com

**Rev 2.0**

www.semtech.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Semtech manufacturer:

Other Similar products are found below:

TCK111G,LF(S FPF1018 DS1222 TCK2065G,LF SZNCP3712ASNT3G MIC2033-05BYMT-T5 MIC2033-12AYMT-T5 MIC2033-05BYM6-T5 SLG5NT1437VTR SZNCP3712ASNT1G NCV330MUTBG DML1008LDS-7 KTS1670EDA-TR KTS1640QGDV-TR KTS1641QGDV-TR NCV459MNWTBG FPF2260ATMX U6513A U6119S NCP45780IMN24RTWG MAX14919ATP+ MC33882PEP TPS2021IDRQ1 TPS2104DBVR MIC2098-1YMT-TR MIC94062YMT TR MP6231DN-LF MIC2075-2YM MIC2095-2YMT-TR MIC94068YML-TR SIP32461DB-T2-GE1 NCP335FCT2G FPF2701MX TCK105G,LF(S AP2151DSG-13 MIC94094YC6-TR MIC94064YC6-TR MIC2505-1YM MIC294042YFL-TR MIC94041YFL-TR MIC2005-1.2YM6-TR TPS2032QDRQ1 SIP32510DT-T1-GE3 NCP333FCT2G NCP331SNT1G TPS2092DR TPS2063DR TPS2042P MIC2008YML-TR MIC2040-1YMM