# Neo-Iso<sup>™</sup> TS13102 Solid State Relay with Enhanced Diagnostics

## **TRIUNE PRODUCTS**

### Features

- Low Quiescent Operating Currents 2μA in OFF state 5μA in ON state

- Supports scalable galvanically-isolated I/O

- Addressable for minimum GPIO usage Supports eight physical address configurations

- Single control signal for on/off input (CLK) Microcontroller-compatible 1.7V to 5.5V input levels Configurable switching options

- Switch Characteristics: Bi-directional blocking in OFF state Single switch device 60V switch and 290mΩ on-resistance Up to 2.5A operating current

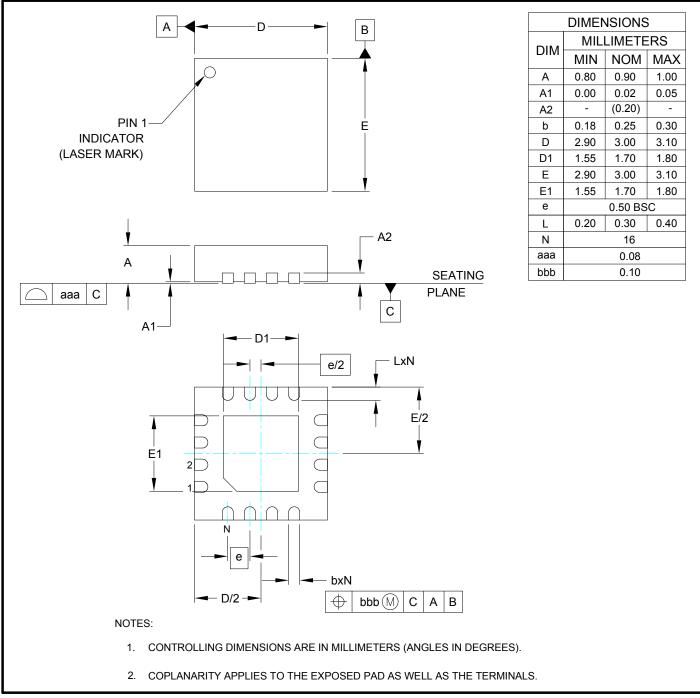

- Package Options

16 lead QFN package 3x3mm, 1.0mm max height

- Operating Modes Zero-cross ON / OFF Immediate ON / OFF Dithering Mode for system power sharing Switch state polling

## **Summary Specification**

- Junction operating temperature -40°C to 125°C

- Packaged in a 16 pin QFN (3x3)

- Product is lead-free, Halogen Free, RoHS / WEEE compliant

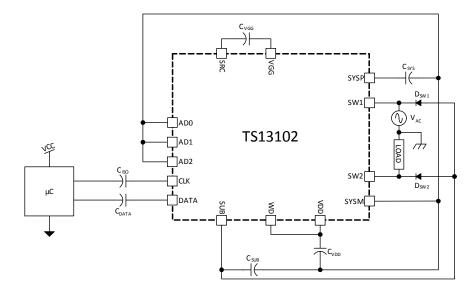

## **Typical Application Circuit**

## Description

The TS13102 is a galvanically isolated 60V power switch device with bi-directional blocking. The device includes a single integrated 290m $\Omega$  high voltage switch allowing high efficiency switching of power loads or other high current applications. The single-pin CLK input pin controls the state of the switch through sequence options which control the way the device switches, including immediate on/off, zero-volt switch-on, zero-current switch-off, dither modes, as well as latching and non-latching behavior.

The TS13102 includes several protection features. Each switch has an integrated over-current shutdown to prevent device damage during short-circuit or other unusually high load conditions. If an overcurrent event is detected for a time, the switch is latched off until the CLK turn on sequence is given.

## **Applications**

- Power load / rail switching

- Input supply multiplexing

- Isolated power supplies

- Solid state relays

- HVAC control

- Sprinkler control

- Internet of Things (IoT)

## **Pin Description**

| Pin Symbol | Pin # | Function                      | Description                                                                         |

|------------|-------|-------------------------------|-------------------------------------------------------------------------------------|

| SYSP       | 1     | Positive System Voltage       | Connect C <sub>SYS</sub> to SYSM                                                    |

| SYSM       | 2     | Negative System Voltage       |                                                                                     |

| SUB        | 3     | IC Substrate Bias             | Connect C <sub>SUB</sub> Capacitor to SYSM                                          |

| SRC        | 4     | Switch Driver Supply Return   | Local common supply return                                                          |

| VGG        | 5     | Internal Switch Driver Supply | Connect Bypass Capacitor C <sub>VGG</sub> to SRC                                    |

| SW2        | 6     | Switch Output Node 2          |                                                                                     |

| SW2        | 7     | Switch Output Node 2          |                                                                                     |

| DATA       | 8     | Data Output                   | AC Coupled Data Output                                                              |

| CLK        | 9     | Clock Input                   | AC Coupled Clock Input                                                              |

| WD         | 10    | Watch Dog                     | Control input for latching vs non-latching Switch                                   |

| VDD        | 11    | Internal Supply 1             | Connect Bypass Capacitor C <sub>VDD</sub> to SYSM                                   |

| AD0        | 12    | Address Select 0              |                                                                                     |

| AD1        | 13    | Address Select 1              | For logic 0, must be tied to SYSM on PCB<br>For logic 1, must be tied to VDD on PCB |

| AD2        | 14    | Address Select 2              |                                                                                     |

| SW1        | 15    | Switch Output Node 1          |                                                                                     |

| SW1        | 16    | Switch Output Node 1          |                                                                                     |

| PAD        | PAD   | Power PAD                     | Must be floating or connected to SUB                                                |

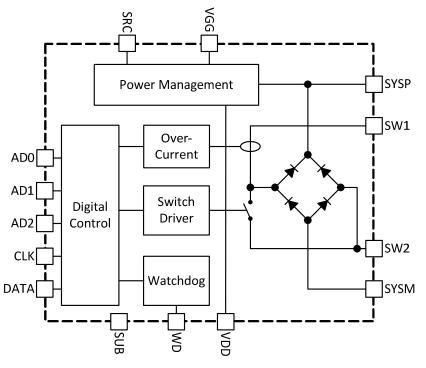

## **Functional Block Diagram**

Figure 1: TS13102 Block Diagram

www.semtech.com

## **Absolute Maximum Ratings**

Over operating free-air temperature range unless otherwise noted<sup>(1, 4)</sup>

| Parameter                                         | Range       | Unit |

|---------------------------------------------------|-------------|------|

| SW1, SW2 <sup>(2)</sup>                           | -1 to 60    | V    |

| SYSP <sup>(3)</sup>                               | -1 to 60    | V    |

| CLK , DATA, VDD, AD2, AD1, AD0, WD <sup>(3)</sup> | -0.3 to 5.5 | V    |

| VGG <sup>(2)</sup>                                | -0.3 to 5.5 | V    |

| SUB <sup>(2)</sup>                                | -55 to 0.3  | V    |

| Maximum Junction Temperature, T <sub>J MAX</sub>  | 150         | °C   |

| Storage Temperature Range, T <sub>STG</sub>       | -65 to 150  | °C   |

| Electrostatic Discharge – Human Body Model        | ±2k         | V    |

| Electrostatic Discharge – Charged Device Model    | ±1.5k       | V    |

| Lead Temperature (soldering, 10 seconds)          | 260         | °C   |

Notes:

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Voltage values are with respect to SRC terminal.

(3) Voltage values are with respect to SYSM terminal.

(4) ESD testing is performed according to the respective JESD22 JEDEC standard.

## **Thermal Characteristics**

| Symbol        | Parameter                              | Value      | Unit |

|---------------|----------------------------------------|------------|------|

| $\theta_{JA}$ | Thermal Resistance Junction to Air (1) | 50         | °C/W |

| Τj            | Operating Junction Temperature Range   | -40 to 125 | °C   |

Notes:

(1) Assumes 16 LD 3x3 QFN with hi-K JEDEC board and 13.5 inch<sup>2</sup> of 1 oz Cu and 4 thermal vias connected to PAD

# **Recommended Operating Conditions**

| Symbol             | Parameter                              | Min | Тур | Мах | Unit             |

|--------------------|----------------------------------------|-----|-----|-----|------------------|

| V <sub>sw</sub>    | AC Switch Voltage                      | 18  | 24  | 36  | V <sub>RMS</sub> |

| F <sub>sys</sub>   | System Supply Voltage Frequency        | DC  |     | 60  | Hz               |

| C <sub>DATA</sub>  | Data Isolation Capacitor               |     | 100 |     | рF               |

| C <sub>ISO</sub>   | Clock Isolation Capacitor              |     | 220 |     | pF               |

| C <sub>VDD</sub>   | VDD Bypass Capacitor                   |     | 470 |     | nF               |

| C <sub>VGG</sub>   | VGG Bypass Capacitor                   |     | 470 |     | nF               |

| C <sub>SUB</sub>   | Sub Capacitor                          |     | 100 |     | nF               |

| C <sub>WD</sub>    | Watch Dog Capacitor                    |     | 22  |     | nF               |

| C <sub>SYS</sub>   | VSYS Capacitor                         |     | 10  |     | nF               |

| R <sub>WD</sub>    | Watch Dog Resistor                     |     | 1   |     | MΩ               |

| D <sub>SW1/2</sub> | SW1/2 Schottky Diode (Forward Voltage) |     | 0.3 |     | V                |

| CLK Drive          |                                        |     |     |     |                  |

| V <sub>CLK</sub>   | Clock Drive Voltage                    | 1.7 |     | 5.5 | V                |

| Т <sub>ськ</sub>   | Clock Period                           | 0.9 | 1   | 1.2 | μs               |

| Т <sub>віт</sub>   | Bit Period                             | 7   | 8   | 10  | μs               |

| T <sub>reset</sub> | Reset Time                             | 25  |     |     | μs               |

## **Electrical Characteristics**

Electrical Characteristics,  $T_J = -40^{\circ}$ C to 125°C (unless otherwise noted)

| Symbol                | Parameter                                       | Parameter Condition                                               |          |         |         |    |

|-----------------------|-------------------------------------------------|-------------------------------------------------------------------|----------|---------|---------|----|

| Supply and            | Power Management                                |                                                                   | <u>.</u> | -       |         |    |

| I <sub>CLK-STBY</sub> | Quiescent current<br>Disable Mode or Latch Mode | $V_{CLK} = 0V, C_{ISO} = 220pF, F_{SYS} = 60Hz$<br>$V_{SW} = 24V$ |          | 3       |         | μA |

| I <sub>SYSP</sub>     | System Supply Current                           | Latch Mode                                                        |          | 8       | 15      | μΑ |

| VDD                   | VDD Supply Voltage                              | With respect to SYSM                                              | 4        | 5.0     | 5.5     | V  |

| VGG                   | VGG Supply Voltage                              | With respect to SRC                                               | 4        | 5.0     | 5.5     | V  |

|                       | Dither Off Period                               |                                                                   |          | 25      |         | μs |

| T <sub>DRTY</sub>     | Dither Retry Interval                           |                                                                   |          | 4       |         | ms |

| V <sub>DON</sub>      | Dither Voltage ON Threshold                     |                                                                   |          | 12      |         | V  |

| $V_{DOFF}$            | Dither Voltage OFF Threshold                    |                                                                   |          | 13      |         | V  |

| Communica             | tion Parameters                                 |                                                                   |          |         |         |    |

| T <sub>HB</sub>       | Heartbeat Pulse-width                           |                                                                   |          | 20      |         | μs |

| <b>Output Swit</b>    | ch                                              | ·                                                                 |          |         |         |    |

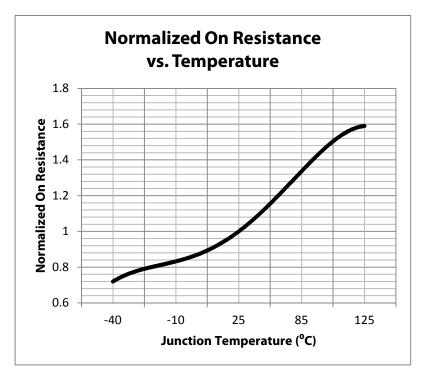

| R <sub>ON</sub>       | Switch On Resistance                            | Т_=25°С                                                           | 230      | 290     | 350     | mΩ |

| I <sub>OFF</sub>      | Off State Leakage                               | Т <sub>Ј</sub> <85°С                                              |          |         | 3       | μA |

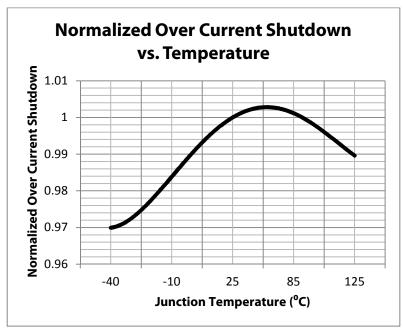

| IOUT <sub>oc</sub>    | Output Over Current<br>Shutdown                 | Tj=25°C                                                           |          | 2.5     |         | А  |

| OC <sub>FILT</sub>    | Output Over Current Deglitch                    |                                                                   |          | 25      |         | μs |

| I <sub>TURN-OFF</sub> | Switch Current for Zero Cross<br>Turn-Off       |                                                                   | -150     |         | 150     | mA |

| Watch Dog             |                                                 |                                                                   |          |         |         |    |

| WD <sub>TO</sub>      | Turn-Off Threshold                              |                                                                   | 500      | 700     | 900     | mV |

| WD <sub>RC</sub>      | WD Recharge Voltage                             |                                                                   | VDD-1.1  | VDD-0.8 | VDD-0.5 | V  |

## **Product Characteristics**

www.semtech.com

## **Detailed Description**

### **Communication Protocol**

The TS13102 device supports a proprietary single-wire interface that is compact and allows support of systems where galvanic isolation is required with a minimum number of external components. If the status sent on the DATA is not required for your application, this pin can remain floating.

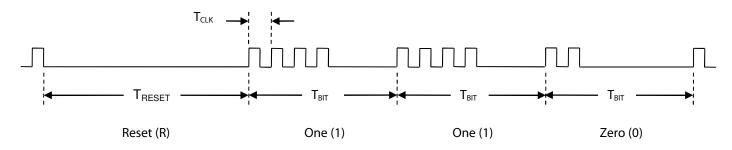

### **Bit Signaling**

The MCU can generate three signals on the CLK pin: Reset, Zero, and One. The Zero and One signals are digital bits and form a command word. Each command word is preceded by a Reset signal.

#### Reset Signal (R)

The Reset signal is a zero logic level that is kept low for longer than  $T_{RESET}$ .

#### Zero Signal (0)

The Zero signal is two pulses of period  $T_{\text{CLK}}$  during a bit period  $T_{\text{BIT}}$

#### One Signal (1)

The One signal is four pulses of period  $T_{CLK}$  during a bit period  $T_{BIT}$ .

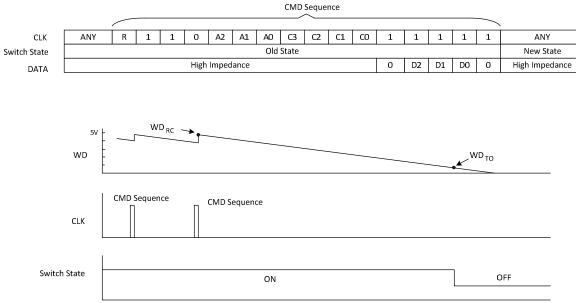

#### **Figure 2: Communication Protocol**

|               |     |                        | Prea      | mble |   | 4  | ddres، | s  |                   | Com | mand      |    |   |   |   |   |   |     |

|---------------|-----|------------------------|-----------|------|---|----|--------|----|-------------------|-----|-----------|----|---|---|---|---|---|-----|

| CLK:          | ANY | R                      | 1         | 1    | 0 | A2 | A1     | A0 | C3                | C2  | C1        | C0 | 1 | 1 | 1 | 1 | 1 | ANY |

| Switch State: |     |                        | Old State |      |   |    |        |    |                   |     | New State |    |   |   |   |   |   |     |

| DATA:         |     | High Impedance0S2S1S00 |           |      |   |    |        |    | High<br>Impedance |     |           |    |   |   |   |   |   |     |

|               |     |                        |           |      |   |    |        |    |                   |     |           |    |   |   |   |   |   |     |

#### Table 1: Communication Sequence

Status

#### **Device Addressing**

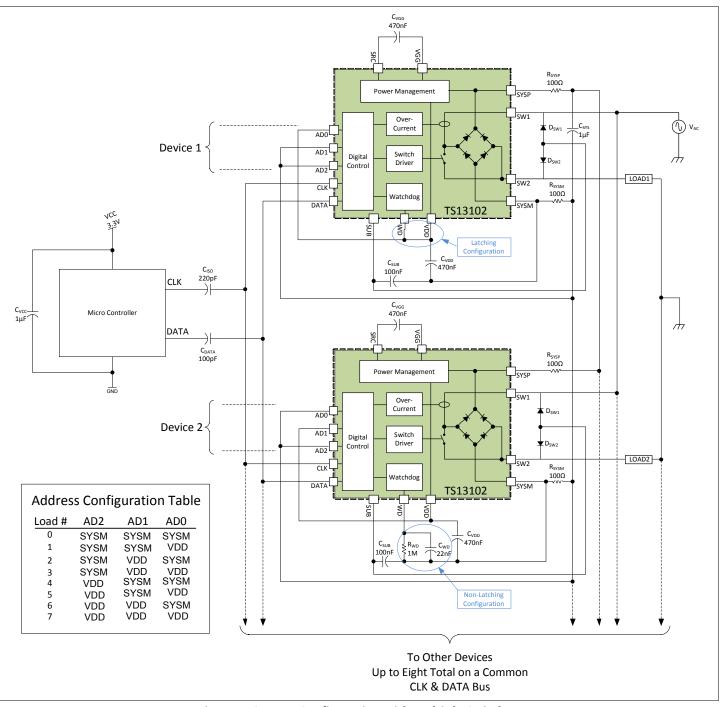

Figure 2 shows the beginning of a command sequence. This pattern appears at the CLK input and forms the Preamble, as shown in Table 1, a sequence of a low period for duration of  $T_{RESET}$  or greater, followed by a bit sequence of (1 1 0). The following three bits designate the address of the device being selected. These three bits (A2 A1 A0) correspond to the device with AD2, AD1, and AD0 pins connected as in the Address Configuration Table shown in Figure 5. See the Multi-channel Application section for more information.

### Switch Commands

The (C3 C2 C1 C0) field sent using the CLK pin determines the command sent to the switch. The following commands are defined:

| C3 | C2 | C1 | <b>C0</b> | Command                           |  |  |  |

|----|----|----|-----------|-----------------------------------|--|--|--|

| 0  | 0  | 0  | 0         | Not allowed (No Operation)        |  |  |  |

| 0  | 0  | 0  | 1         | OFF, Immediate                    |  |  |  |

| 0  | 0  | 1  | 0         | OFF, Zero Crossing                |  |  |  |

| 0  | 0  | 1  | 1         | ON, Immediate                     |  |  |  |

| 0  | 1  | 0  | 0         | ON, Zero Crossing                 |  |  |  |

| 0  | 1  | 0  | 1         | ON, Immediate, with Dithering     |  |  |  |

| 0  | 1  | 1  | 0         | ON, Zero Crossing, with Dithering |  |  |  |

| 0  | 1  | 1  | 1         | Heartbeat                         |  |  |  |

| 1  | 0  | 0  | 0         | Not allowed (No Operation)        |  |  |  |

| 1  | 0  | 0  | 1         | Not allowed (No Operation)        |  |  |  |

| 1  | 0  | 1  | 0         | Not allowed (No Operation)        |  |  |  |

| 1  | 0  | 1  | 1         | Not allowed (No Operation)        |  |  |  |

| 1  | 1  | 0  | 0         | Not allowed (No Operation)        |  |  |  |

| 1  | 1  | 0  | 1         | Not allowed (No Operation)        |  |  |  |

| 1  | 1  | 1  | 0         | Not allowed (No Operation)        |  |  |  |

| 1  | 1  | 1  | 1         | Poll State (No Operation)         |  |  |  |

**Table 2: Valid Commands**

Each switch monitors the CLK line regardless of the address; however only the device with the (AD2 AD1 AD0) pins configured to match the (A2 A1 A0) field sent via the CLK pin will respond to the Command bits (C3 C2 C1 C0). If two or more devices on the CLK bus have address pins wired alike, those devices will all respond to the same command. However, doing this may lead to DATA bus conflicts when the device Status Values are reported.

The command is executed after the status values are shifted out to avoid interference on the status values caused by transients in the system.

### **ON Commands**

Four modes of closing the switch are available:

- 1. ON, Immediate: When this command sequence is sent, the switch will be closed after the status values are shifted out. The system must comprehend the time it takes to complete the sequence in order to place the switch in the closed state at the desired time.

- 2. ON, Zero Crossing: When this command sequence is sent, the switch will close on the first occurrence of a polarity change in the voltage across the switch (V<sub>SW1</sub>-V<sub>SW2</sub> changes sign to indicate a voltage zero-crossing) after the switch receives the command and the status values are shifted out. This should not be used for DC applications.

- 3. ON, Immediate with Dithering: This command closes the switch as in ON, Immediate, above, but puts the device into Dither mode as well. Dithering opens the switch after an interval of  $T_{DRTY}$  for a period of time,  $T_{DOFF}$  when the system voltage drops below  $V_{DON}$ . This allows the  $C_{SYS}$  capacitor to be re-charged. See the Dither Functionality section for more details.

- 4. ON, Zero Crossing with Dithering: This command closes the switch as in ON, Zero Crossing, but enables the Dither mode as described above.

### **OFF Commands**

Two modes of opening the switch are available:

- 1. OFF, Immediate: When the OFF, Immediate sequence is sent, the switch will transition to the open state after the status values are shifted out.

- 2. OFF, Zero Crossing: When the OFF, Zero-Crossing sequence is received, the switch will open on the first occurrence of the load-current dropping within I<sub>TURN\_OFF</sub> after the status values are shifted out.

### **Poll Command**

A Poll State command may be sent to the device when no change of operation is desired, but the state of the Status Values is needed by the microcontroller. In non-latched operation, this command will also serve to recharge the Watchdog Timer. See the Latching Configuration section for details.

#### **Status Values**

The (S2 S1 S0) field received using the DATA pin provides the status of the switch before the command has been executed. Each of the S2, S1 or the S0 bits is generated by the switch in the following way:

- For zero: the DATA pin is pulsed for first 2 clock pulses matching the protocol (the pulses corresponding to the Zero signal).

- For one: the DATA pin duplicates the signal available at the CLK pin (the pulses corresponding to the One signal).

The following status values are defined:

| S2 | S1 | <b>S0</b> | Status                 |

|----|----|-----------|------------------------|

| 0  | 0  | 0         | Reserved               |

| 0  | 0  | 1         | OFF                    |

| 0  | 1  | 0         | Reserved               |

| 0  | 1  | 1         | Reserved               |

| 1  | 0  | 0         | ON, Dithering disabled |

| 1  | 0  | 1         | ON, Dithering enabled  |

| 1  | 1  | 0         | Reserved               |

| 1  | 1  | 1         | Over Current           |

#### Table 3: Valid Status Values

### **DATA Bus Contention**

Note that if more than one device is wired to the same address, the devices will all report their status values at the same time. Since the status of each device may be different (for example, an over-current event was recorded on one device and it has disabled itself), the status values (S2 S1 S0) can possibly be different, leading to the DATA pins of two (or more) devices to transmit different data. This will lead to high supply current draw which may damage the device, reset the system (due to voltage drop), or other undesirable events. If sharing addresses is desired, the DATA pins of those devices must have a separate  $C_{DATA}$  capacitor wired to a dedicated GPIO on the microcontroller.

#### **Latching Configuration**

The Switch can be configured for latching or non-latching functionality via external interconnect. When the WD pin is tied to VDD, the Switch state is latched after each command (CMD) sequence. When the WD pin is tied to an RC circuit, the device is configured for non-latching behavior. If a CMD sequence is not received before the WD pin voltage decays to  $WD_{TO}$ , the Switch will be turned off. A CMD sequence received by the device before the WD pin voltage decays to  $WD_{TO}$  will cause the WD pin to recharge to  $WD_{RC}$ , and the switch will remain closed. In order to recharge, the CMD address must be for the corresponding device address configuration. Typical waveforms for non-latching behavior are shown below.

The time between the last CMD sequence and the switch opening (in a non-latching configuration) can be computed by the following equation:

$$t_{OFF} = -R_{WD}C_{WD}\ln\left(\frac{WD_{TO}}{WD_{RC}}\right)$$

Where:

$t_{OFF}$  is the time from the last CMD sequence until the switch opens  $R_{WD}$  is the WD pin resistor  $C_{WD}$  is the WD pin capacitor  $WD_{TO}$  is the WD pin turn-off voltage threshold  $WD_{RC}$  is the WD pin re-charge voltage

It should be noted that the WD capacitor,  $C_{WD}$ , is recommended to be 22nF. The reason for this is that charge proportional to  $C_{WD}$  is drawn from the  $C_{SYS}$  capacitor in every re-charge cycle, thereby elevating the average current, and forcing the device to switch off more frequently in order to re-charge  $C_{SYS}$  (see Dither Functionality, below).  $C_{WD}$  can be made smaller, but this will necessitate a larger value of  $R_{WD}$  to be used to define a given  $t_{OFF}$  time.  $R_{WD}$  has its practical limits due to leakage within the components attached to the WD pin and possible leakage on the circuit board due to contamination. The system designer should consider all these issues when selecting  $R_{WD}$  and  $C_{WD}$ . Device 2 in Figure 5 shows  $R_{WD}$  and  $C_{WD}$  being used to create a non-latching channel. Device 1 is shown in latching mode.

### **Dither Functionality**

Dithering is provided as a mode of operation for applications where a single device per system is used. It enables powering the TS13102 from the AC waveform. The device monitors the system voltage,  $(V_{SYSP}-V_{SYSM})$ , and if it falls below  $V_{DON}$ , the Switch is shut off for approximately  $T_{DOFF}$ . This causes energy stored in the load to be transferred into the  $C_{SYS}$  capacitor. When the device is in dither mode, this event occurs at  $T_{DRTY}$  intervals until the system voltage reaches  $V_{DOFF}$ .

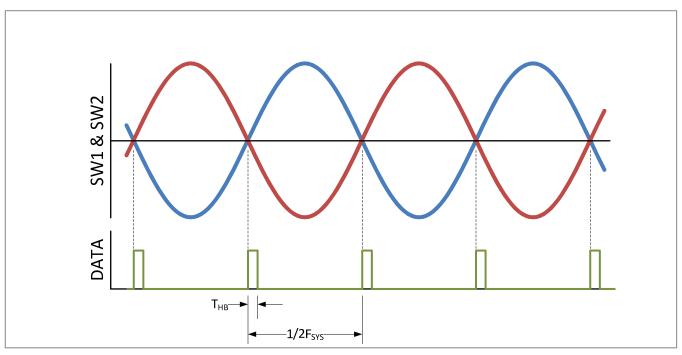

#### **Heartbeat Functionality**

When the Switch is off and the Heartbeat Command Sequence has been transmitted, the DATA pin provides a pulse synchronous with the zero crossings of the AC waveform. A single pulse or "Heartbeat" for each crossing will be present with a pulse-width of  $T_{HB}$  as shown in the figure below. This is useful for monitoring load presence and for evaluating the phase of the AC waveform.

Figure 4: Heartbeat Functionality

#### **Multi-channel Application**

In a multi-channel application, dithering is unnecessary as long as one device is switched off. As long as the device address pins are wired uniquely for each channel, a single pair of GPIO pins on the microcontroller can control each device by matching the address in the CMD sequence with the hardwired address. If all devices must be on simultaneously, one device can be configured for dithering mode to maintain system supply.

The SYSP net should be tied to the SYSM net through the  $C_{SYS}$  capacitor as shown in the Figure 5 below. For a single transformer system, only one is necessary. If additional transformers are used in a given system, then the SYSP and SYSM pins for those TS13102 devices will need an additional  $C_{SYS}$  capacitor for each additional transformer.

Current limit resistors are needed for each SYSP pin and each SYSM pin as shown below ( $R_{SYSP}$  and  $R_{SYSM}$  respectively). These are typically 100  $\Omega$ , 1/4 W.

A pair of GPIO pins can manage the command and control for up to 8 loads as long as each TS13102 has a unique address. The address pins are set using hard wired connections according to the Address Configuration Table shown in Figure 5.

Also note that some devices can be wired in non-latching mode and others in latching mode.

Figure 5: System Configuration with Multiple Switches

## **Package Information**

### **Product Marking**

#### Figure 6: Device Symbolization

Notes: YYWW = Year Calendar Week XXXXX = Semtech Lot Number XXXXX = Lot Number (Continued)

### **Package Outline Drawing**

Figure 7: Package Outline Drawing

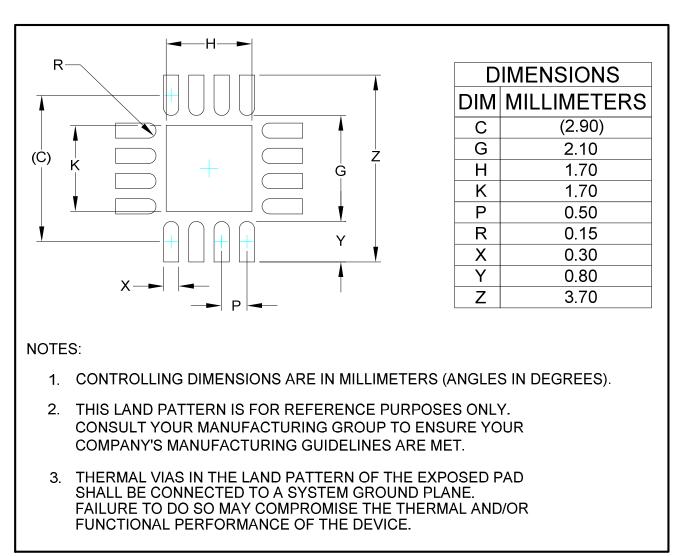

#### **Board Land Pattern**

#### Figure 8: Recommended Board Layout Land Pattern

## **Ordering Information**

| Device Part Number | Description           | Package                                            |  |  |  |  |

|--------------------|-----------------------|----------------------------------------------------|--|--|--|--|

| TS13102-QFNR       | 60V Power Load Switch | MLPQ-16 3.0 x 3.0<br>Tape & Reel (3300 parts/reel) |  |  |  |  |

| TS13102EVB         | Evaluation Board      |                                                    |  |  |  |  |

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2016

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Semtech manufacturer:

Other Similar products are found below :

TCK111G,LF(SFPF1018DS1222TCK2065G,LFSZNCP3712ASNT3GMIC2033-05BYMT-T5MIC2033-12AYMT-T5MIC2033-05BYM6-T5SLG5NT1437VTRSZNCP3712ASNT1GNCV330MUTBGDML1008LDS-7KTS1670EDA-TRKTS1640QGDV-TRKTS1641QGDV-TRNCV459MNWTBGFPF2260ATMXU6513AU6119SNCP45780IMN24RTWGMAX14919ATP+MC33882PEPTPS2021IDRQ1TPS2104DBVRMIC2098-1YMT-TRMIC94062YMT TRMP6231DN-LFMIC2075-2YMMIC2095-2YMT-TRMIC94068YML-TRSIP32461DB-T2-GE1NCP335FCT2GFPF2701MXTCK105G,LF(SAP2151DSG-13MIC94094YC6-TRMIC94064YC6-TRMIC2505-1YMMIC94042YFL-TRMIC94041YFL-TRMIC2005-1.2YM6-TRTPS2032QDRQ1SIP32510DT-T1-GE3NCP333FCT2GNCP331SNT1GTPS2092DRTPS2063DRTPS2042PMIC2008YML-TRMIC2040-1YMM