## POWER MANAGEMENT

### **Features**

Dual N-Channel MOSFET Driver with Programmable Dead Time Control Wide Power Stage Input Voltage: Up to 36V Integrated Low Input Voltage 3.3V LDO Smart Gate Drive to Reduce EMI Integrated Bootstrap Switch Diode Emulation for High Light Load Ef ciency Tri-State PWM Input for Drive Stage Shutdown UVLO, Over Temperature Shutdown 10 Lead MLPD-UT 2.3mm x 2.3mm Package Full Industrial Temperature Range Fully WEEE and RoHS Compliant

## Description

The TS61005 is a high-side and low-side N-channel MOSFET driver with integrated bootstrap switch optimized for wireless charging applications. This driver can be used as a synchronous buck converter MOSFET driver. The SmartDrive<sup>™</sup> function at the

turn-on of the high-side MOSFET is a standout feature of this part to reduce the EMI. The diode emulation mode operation offers the opportunity to achieve high ef ciency at light load. The integrated LDO reduces the cost and the footprint of the system.

## **Applications**

Smart Watches Wearables Consumer Toys Portable Lighting Medical Devices Low power Industrial applications

An Under-Voltage-Lock-Out (UVLO) function is included to ensure the driver outputs are of when the bias voltage falls below 4.02V. An over temperature shutdown feature is also included to prevent the driver from overheating.

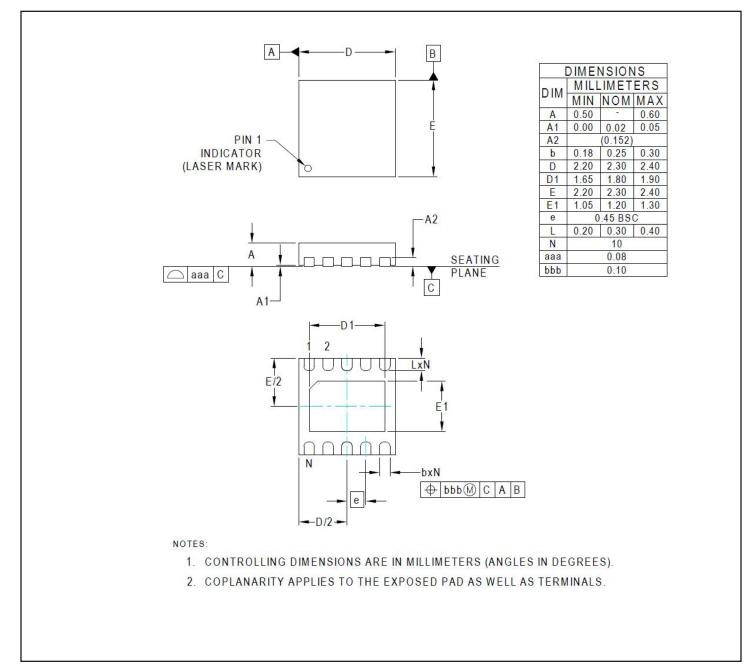

The TS61005 is available in a space-saving 10 lead 2.3mm x 2.3mm MLPD-UT package and operates over the industrial temperature range.

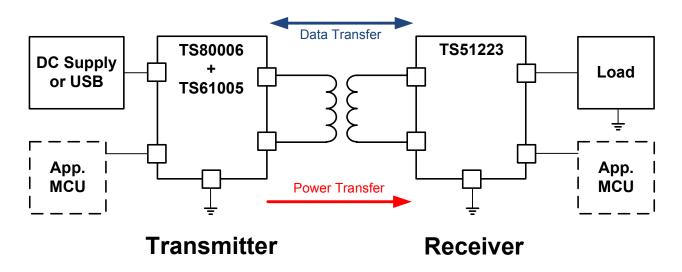

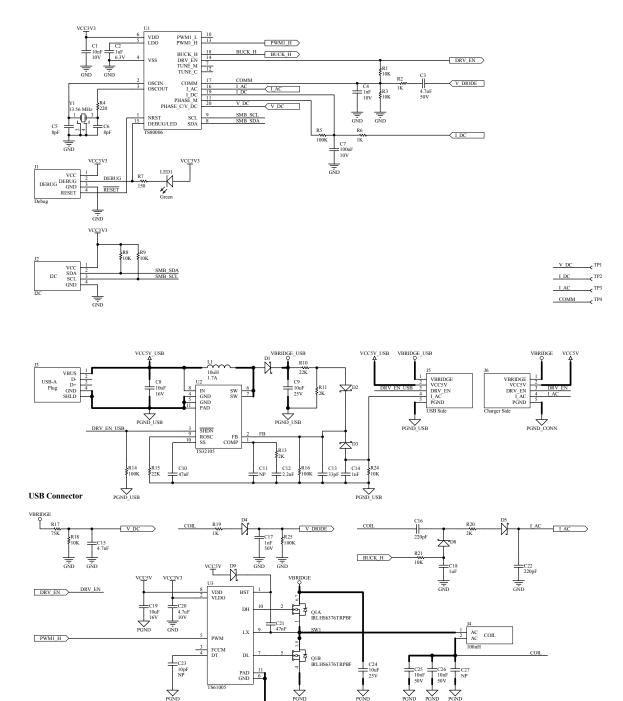

## **Typical Application Circuit**

Figure 1. Typical Application for Wireless Power

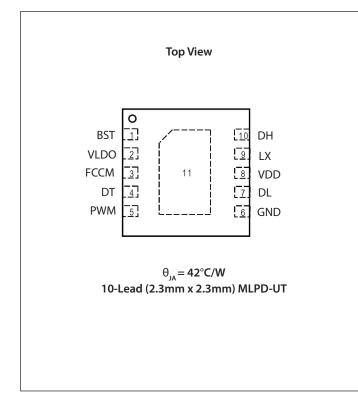

# **Pin Configuration**

## **Ordering Information**

| Device Part # | Description                         | MLPD-UT-10<br>(2.3mm x 2.3mm)    |

|---------------|-------------------------------------|----------------------------------|

| TS61005-QFNR  | Wireless Charging<br>PWM Controller | Tape & Reel<br>(3000 parts/reel) |

Notes:

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Available in lead-free package only. Device is WEEE and RoHS compliant and halogen free.

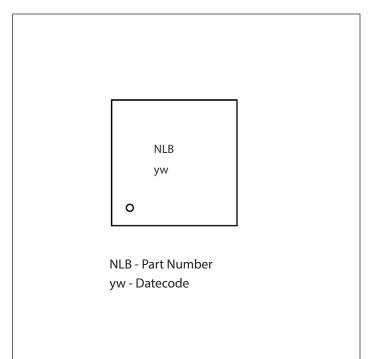

## **Marking Information**

## **Absolute Maximum Ratings**

| VDD to GND (V)0.3 to +6.0                  |

|--------------------------------------------|

| DH, BST to GND (V)0.3 to +44               |

| DH, BST to LX (V)0.3 to +6.0               |

| LX to GND (V) <sup>(1)</sup> 2.0 to $+38$  |

| PWM, FCCM, DT, DL to GND (V)0.3 to VDD+0.3 |

| VLDO to GND (V)0.3 to +6.0                 |

| ESD Protection Level <sup>(2)</sup> (kV)   |

# **Recommended Operating Conditions**

| VDD (V) |

|---------|

|---------|

## **Thermal Information**

| Thermal Resistance, Junction to $Ambient^{\scriptscriptstyle{(3)}}(^{\circ}C/W)\ \dots 42$ |

|--------------------------------------------------------------------------------------------|

| Maximum Junction Temperature (°C)+150                                                      |

| Storage Temperature Range (°C)65 to +150                                                   |

| Peak IR Reflow Temperature (10s to 30s) (°C) +260                                          |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

(1) The transient negative voltage specification for the LX pin is -6V for 100ns.

- (2) Tested according to JEDEC standard JS-001-2012. BST-VDD passed 1.5kV.

- (3) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

### Electrical Characteristics -

Unless noted otherwise  $T_1 = 25^{\circ}$  C for typical,  $-40^{\circ}$  C  $\leq T_1 \leq 125^{\circ}$  C for min and max, VDD = 5.25V.

| Parameter                 | Symbol | Conditions                   | Min  | Тур  | Max  | Units |

|---------------------------|--------|------------------------------|------|------|------|-------|

| VDD                       |        |                              |      |      |      |       |

| Operating range           |        |                              | 4.5  |      | 5.5  | V     |

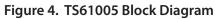

| UVLO threshold            |        | rising edge                  | 3.92 | 4.14 | 4.34 |       |

|                           |        | falling edge                 | 3.88 | 4.02 | 4.13 | V     |

| Quiescent current         |        | PWM = high                   | 249  | 374  | 463  | μΑ    |

|                           |        | PWM = low                    | 392  | 531  | 665  | μΑ    |

|                           |        | PWM pin floating             | 440  | 570  | 709  | μΑ    |

| Internal LDO              | · · ·  |                              | l    |      | 1    |       |

| LDO output accuracy       |        | LDO load = 10mA              | 3.16 | 3.26 | 3.38 | V     |

| Current limit             |        |                              | 127  |      | 372  | mA    |

| Over Temperature Shutdown | I I    |                              | I    |      | 1    | 1     |

| Over temperature shutdown |        | temperature rising threshold |      | 150  |      | °C    |

| Hysteresis                |        |                              |      | 20   |      | °C    |

# **Electrical Characteristics (continued)**

| Parameter                          | Symbol              | Conditions                                      | Min  | Тур  | Max  | Units |

|------------------------------------|---------------------|-------------------------------------------------|------|------|------|-------|

| High-Side Driver                   | · · · · ·           |                                                 | ·    |      |      |       |

| Peak source current                |                     | BST-LX=5.25V                                    |      | 2    |      | A     |

| Source resistance                  |                     |                                                 |      | 1.2  | 1.7  | Ω     |

| Rise time <sup>(1)</sup>           | t <sub>DH_R</sub>   | C <sub>L</sub> = 3.3nF, BST-LX = 5.25V, LX = 5V |      | 12   |      | ns    |

| Peak sink current                  |                     | BST-LX = 5.25V                                  |      | 2    |      | A     |

| Sink resistance                    |                     |                                                 |      | 0.8  | 1.4  | Ω     |

| Fall time <sup>(1)</sup>           | t <sub>DH_F</sub>   | $C_{L} = 3.3 nF, BST-LX = 5.25 V$               |      | 8    |      | ns    |

| Propagation delay time (1)         | t <sub>DH_PD</sub>  | From PWM input falling to DH output falling     |      | 16   |      | ns    |

| Low-Side Driver                    |                     |                                                 |      | -    |      |       |

| Peak source current                |                     | VDD = 5.25V                                     |      | 2    |      | A     |

| Source resistance                  |                     |                                                 |      | 1.1  | 1.7  | Ω     |

| Rise time (1)                      | t <sub>DL_R</sub>   | C <sub>L</sub> = 3.3nF, VDD = 5.25V             |      | 12   |      | ns    |

| Peak sink current                  |                     | VDD = 5.25V                                     |      | 4    |      | A     |

| Sink resistance                    |                     |                                                 |      | 0.4  | 0.8  | Ω     |

| Fall time <sup>(1)</sup>           | t <sub>DL_F</sub>   | C <sub>L</sub> = 3.3nF, VDD = 5.25V             |      | 6    |      | ns    |

| Propagation delay time $^{(1)}$    | t <sub>DL_PD</sub>  | From PWM input rising to DL output falling      |      | 16   |      | ns    |

| PWM Input                          |                     |                                                 |      |      |      |       |

| Tri-state rising threshold         |                     | $V_{PWM_PEAK} = 3.3V$ and 5V, VDD = 5.25V       | 0.75 | 1.0  | 1.3  | V     |

| Tri-state falling threshold        |                     | $V_{PWM_PEAK} = 3.3V$ and 5V, VDD = 5.25V       | 1.7  | 2.1  | 2.5  | V     |

| Tri-state voltage                  |                     | PWM float                                       |      | 1.45 |      | V     |

| Tri-state shutdown entry delay (1) | t <sub>rr_end</sub> | VDD = 5.25V                                     |      | 303  |      | ns    |

| Tri-state shutdown exit delay (1)  | t <sub>TR_EXD</sub> | VDD = 5.25V                                     |      | 62   |      | ns    |

| PWM sink impedance                 |                     |                                                 | 7.5  | 10   | 14   | kΩ    |

| PWM source impedance               |                     |                                                 | 19   | 26   | 34   | kΩ    |

| Operating frequency range          |                     |                                                 | 4    |      | 7000 | kHz   |

| Minimum pulse width at high        |                     |                                                 |      | 30   |      | ns    |

| FCCM                               |                     |                                                 |      |      |      |       |

| Input logic high                   |                     | Rising threshold                                | 2.0  |      |      | V     |

# **Electrical Characteristics (continued)**

| Parameter                     | Symbol          | Conditions                                                 | Min  | Тур  | Мах | Units |  |

|-------------------------------|-----------------|------------------------------------------------------------|------|------|-----|-------|--|

| Input logic low               |                 | Falling threshold                                          |      |      | 0.8 | V     |  |

| Zero cross detector threshold |                 | VDD = 5V                                                   | -1   |      | +1  | mV    |  |

| Zero cross blanking time      |                 | FCCM enabled, VDD = 5V                                     |      | 325  |     | ns    |  |

|                               |                 | FCCM = VDD                                                 |      | 3.5  | 5.6 | μΑ    |  |

| FCCM pin leakage current      |                 | FCCM = GND                                                 | -1.5 |      | 1.5 | μΑ    |  |

| Intenal Bootstrap Switch      |                 |                                                            |      |      |     |       |  |

| On resistance                 |                 |                                                            |      | 10   |     | Ω     |  |

| Leakage current               |                 |                                                            |      | 5    | 15  | μΑ    |  |

| Dead Time                     | Dead Time       |                                                            |      |      |     |       |  |

| Minimum dead time             |                 | DT pin is floated                                          |      | 20   |     | ns    |  |

| Dead Time <sup>(2)</sup>      | t <sub>DT</sub> | A capacitor $C_{DT} = 100$ pF connected from DT pin to GND |      | 100  |     | ns    |  |

| Internal series resistor      |                 |                                                            | 15   | 24.5 | 38  | kΩ    |  |

NOTES:

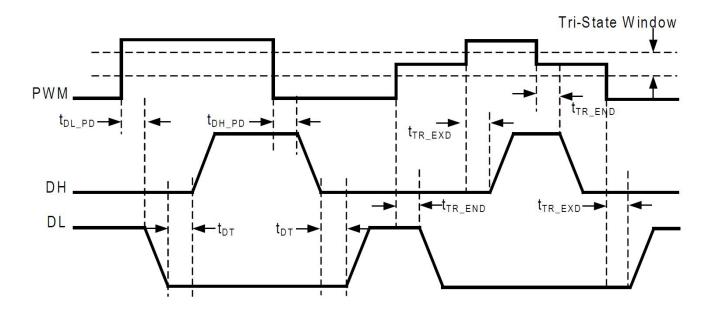

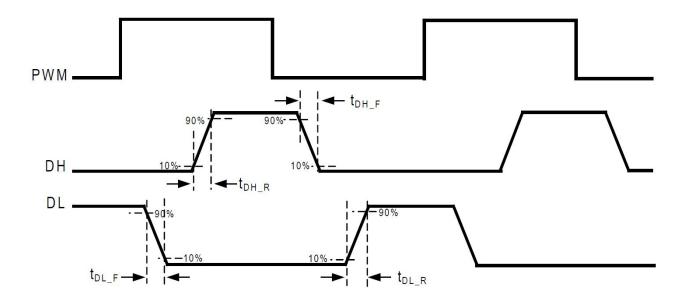

(1) Refer to Figure 2 and Figure 3 for the timing definition.

(2) The dead time is  $C_{DT} x 1ns/pF$ , where  $C_{DT}$  is in pF.

# **Electrical Characteristics (continued)**

## **Timing Diagram**

Figure 2. Timing Diagram 1

Figure 3. Timing Diagram 2

# **Pin Descriptions**

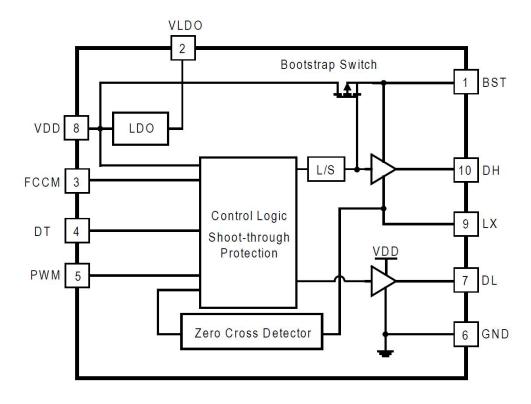

| Pin # | Pin Name    | Pin Function                                                                                                                                                                                                                           |  |  |  |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1     | BST         | Bootstrap pin, supply for the high-side driver.                                                                                                                                                                                        |  |  |  |

| 2     | VLDO        | 3.3V LDO output pin.                                                                                                                                                                                                                   |  |  |  |

| 3     | FCCM        | If FCCM pin is low, the low-side MOSFET is turned off when the inductor current reaches zero (di-<br>ode emulation mode); if FCCM pin is pulled high or floated, the device operates in forced continu-<br>ous conduction mode (FCCM). |  |  |  |

| 4     | DT          | Dead time programming pin. Connect a ceramic capacitor from this pin to GND to set the dead time (1ns/pF) between DH and DL.                                                                                                           |  |  |  |

| 5     | PWM         | PWM input pin.                                                                                                                                                                                                                         |  |  |  |

| 6     | GND         | Ground pin.                                                                                                                                                                                                                            |  |  |  |

| 7     | DL          | Low-side drive output pin.                                                                                                                                                                                                             |  |  |  |

| 8     | VDD         | Power supply pin for the device.                                                                                                                                                                                                       |  |  |  |

| 9     | LX          | Phase node.                                                                                                                                                                                                                            |  |  |  |

| 10    | DH          | High-side drive output pin.                                                                                                                                                                                                            |  |  |  |

|       | THERMAL PAD | The exposed pad enhances thermal performance and is not electrically connected inside the pack-<br>age. It is recommended to connect the exposed pad to the ground plane.                                                              |  |  |  |

# **Block Diagram**

# **Typical Characteristics**

### Under Voltage Lockout Threshold

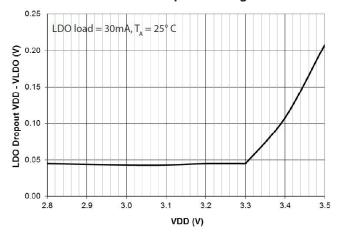

3.3V LDO Dropout Voltage

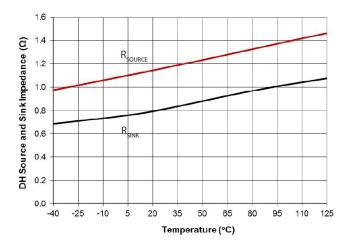

High-Side Driver Source and Sink Impedance

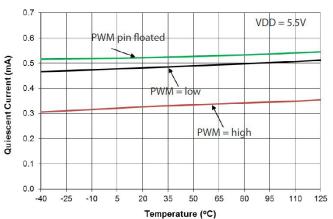

VDD Quiescent Current

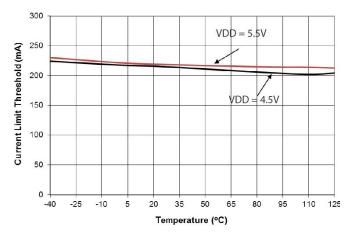

3.3V LDO Current Limit

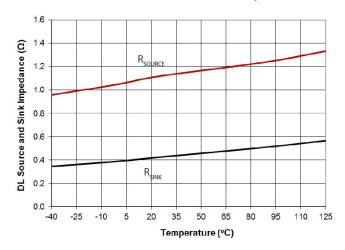

Low-Side Driver Source and Sink Impedance

# **Typical Characteristics (Continued)**

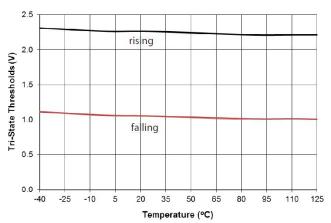

PWM Tri-State Thresholds

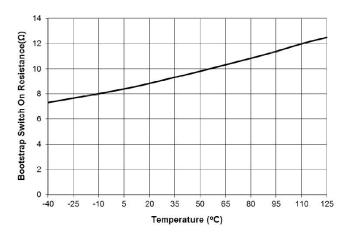

**Bootstrap Switch On Resistance**

1.55 1.50 FCCM Thresholds (V) rising 1.45 1.40 1.35 falling 1.30 1.25 -25 -10 5 -40 20 35 50 65 80 95 110 125 Temperature (°C)

**FCCM Logic Thresholds**

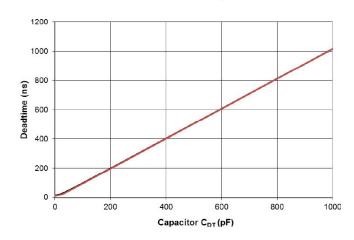

Dead Time vs C<sub>DT</sub>

## **Application Information**

### **Overview**

The TS61005 is a high-side and low-side N-channel MOSFET driver. The driver receives a ground-referenced PWM signal with fast slew rate to drive two N-channel MOSFETs in a synchronous buck converter or any other application with two MOSFETs in a half-bridge configuration. The SmartDrive<sup>™</sup> function at the turn-on of the high-side MOSFET reduces the voltage ringing on the low-side switch and also reduces the EMI. Tying the FCCM pin to ground offers diode emulation mode operation to achieve high efficiency at light load. The Under-Voltage-Lock-Out (UVLO) threshold ensures a reliable drive voltage for the external MOSFETs. The over temperature shutdown feature is also included to prevent the driver from overheating.

**Under Voltage Lockout**

The TS61005 has an under voltage lockout (UVLO) circuit which keeps the driver off when the input voltage is not high enough to drive the external MOSFETs reliably. During power on, the driver outputs (DH and DL) are low until the input voltage reaches the UVLO rising threshold. Once the UVLO threshold is reached, the driver outputs are determined by the signals on the PWM pin and FCCM pin. The UVLO falling threshold is about 0.2V lower which prevents the driver from turning on and off due to a slow input slew rate.

### **Tri-State PWM Input**

The TS61005 features a tri-state PWM input pin. When the PWM signal is less than 1V (typical), it is considered as a logic low while the signal is taken as a logic high when it is higher than 2.1V (typical). 1V to 2.1V is the tri-state window for the PWM signal. These thresholds make it work well for both 3.3V logic and 5V logic PWM signals. If the PWM pin is left floating, the internal resistor divider sets the voltage on the PWM pin to 1.45V which is within the tri-state window. For a synchronous buck converter application, pre-biased output startup is supported if the buck controller features a tri-state PWM output pin.

### **Programmable Dead Time Control**

The dead time control is to prevent shoot-through of the high-side MOSFET and the low-side MOSFET. Shootthrough can cause poor efficiency and even cause the MOSFET to blow up. The dead time control circuitry of a MOSFET driver is thus very important in real applications. An adaptive dead time control function is implemented in the TS61005 by sensing the DH and DL signals. The TS61005 has a DT pin which offers an option to program the dead time with a ceramic capacitor from this pin to the GND pin. A ceramic capacitor with tight tolerance such as Murata COG material capacitor should be used for this purpose. The dead time is 20ns typical with the DT pin floated.

## **Application Information (Continued)**

### FCCM/Diode Emulation Mode Operation

There are two operating modes which can be configured with the FCCM pin of the TS61005. When the FCCM pin is floated or tied to a logic high signal (e.g. VDD), the drive signal DL is always complementary to DH. This is called forced continuous conduction mode (FCCM) operation. If the FCCM pin is grounded, a zero-crossing circuit is activated in the TS61005. The DL output is turned to low when the current in the external low-side MOSFET reaches zero. In other words, the external low-side MOSFET acts like a diode. This operation mode is thus called diode emulation mode. The benefit of this diode emulation mode is to reduce conduction losses at light load for high efficiency.

### SmartdriveTM

For each DH drive pulse, the TS61005 initially turns on the high-side MOSFET with a weak driver, allowing a softer, smooth turnoff of the low-side MOSFET. Once the low-side MOSFET is turned off and the LX pin voltage has risen about 2.5V above ground, the TS61005 switches to a much stronger driver to complete the turn-on of the high-side MOSFET at a more rapid rate. This technique reduces the voltage ringing for the switching node, which relieves the need for a snubber or a gate resistor.

### **Bootstrap Capacitor**

The TS61005 integrates the bootstrap switch. Only an external bootstrap capacitor connected between the BST pin and the LX pin is needed for a complete bootstrap circuit. The bootstrap capacitor, which is charged from VDD during the on time of the low-side MOSFET, provides the energy to turn on the high-side MOSFET. The capacitance for the bootstrap capacitor is mainly determined by the gate charge  $Q_g$  of the high-side MOSFET. The equation below gives a first order estimate:

$C_{b} = Q_{q} / \Delta V_{b}$

Where  $\Delta V_{b}$  is the allowable voltage drop of the drive voltage for the high-side MOSFET. In a real application, considering the capacitance tolerance,  $Q_{g}$  variation, leakage current of the BST pin etc., a capacitor with two times the calculated value is a good starting point. A ceramic capacitor of X5R or X7R, or equivalent material, should be used.

### **VLDO Decoupling Capacitor**

The VLDO pin is the 3.3V LDO output pin. This 3.3V LDO can be used as the bias for a microcontroller or any other digital controller which requires quite, accurate 3.3V bias on the system board. A high frequency decoupling capacitor with low ESR and low ESL should be put from the VLDO pin to the GND pin with minimum trace length. A typical value of  $2.2\mu$ F, 6.3V rating, X5R or X7R ceramic capacitor is recommended.

### **VDD Decoupling Capacitor**

The VDD is the input bias for the low-side driver and the internal control circuitry. This pin is also used for the VDD UVLO check. A high frequency decoupling capacitor with low ESR and low ESL should be put from the VDD pin to the GND pin with minimum trace length. A typical value of  $2.2\mu$ F, 10V rating, X5R or X7R ceramic capacitor is recommended.

### **Power Dissipation**

wer dissipation in this driver consists of two main components: the power loss for turning on and off the external MOSFETs, and the power loss in the internal LDO (if used). The below equation can be used to estimate the total power dissipation in the driver:

$P_d = VDD f_s (Q_{gh} + Q_{gl}) + (VDD - 3.3) I_L$ Where:

f is the switching frequency

$\dot{Q}_{gh}$  is the total gate charge of the high-side MOSFET

$Q_{al}^{g_{al}}$  is the total gate charge of the low-side MOSFET

I, is the external load connected to the VLDO pin

## **Application Information (Continued)**

To ensure proper operation and long-term reliability, the power dissipation should be examined in the real application to make sure the junction temperature will not go beyond 125°C. Multiple vias should be used to connect the thermal pad underneath the driver package to the ground plane on the system board for good thermal management.

$$\begin{split} T_{J} &= T_{A} + P_{d} \ \theta_{JA} \\ Where: \\ T_{J} \ is the junction temperature \\ T_{A} \ is the ambient temperature \\ \theta_{JA} \ is the thermal resistance, 42°C/W \end{split}$$

There is a temperature monitor in the driver which will shut down the driver outputs and the LDO when the junction temperature reaches 150°C. The driver will automatically recover when the junction temperature cools to less than 132°C.

### Layout Recommendations

TS61005 is designed to provide strong source and sink capability for MOSFET drive at high frequency. In order to achieve this objective, the PCB layout is critical. Some guidelines are highlighted below to achieve good performance with TS61005.

A. Locate the driver as close as possible to the MOSFETs.

B. Mount the decoupling capacitors as close as possible between the VIN pin and the GND pin, the VDD pin and the GND pin, the BST pin and the LX pin. C. Minimize the PCB trace length between the DL pin to the low-side MOSFET gate, the GND pin and the source of the low-side MOSFET. Avoid mixing the ground trace of the drive loop with the power stage current path.

D. Apply a similar rule for the high-side drive loop.

E. Use wide PCB trace > 20 mils for the drive loops.

F. Use two or more vias if the PCB trace for the drive loops needs to be routed from one layer to another.

G. The ground of the input signals (PWM, FCCM and DT) should be separated from the power ground plane and directly connected to the GND pin of the driver.

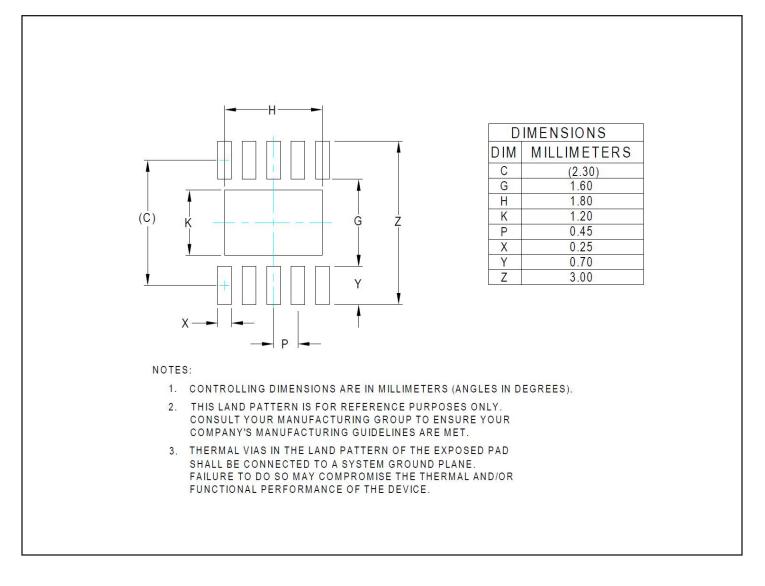

H. Use multiple vias to connect the thermal pad to the ground plane.

# **Typical Application Circuits**

Figure 5. Wearable Wireless Power Transmitter

GND

C TIE1 OTIE2

PGND

TS6100

PGND\_CONN

0.02 1% PGND

## Outline Drawing — 2.3mm x 2.3mm MLPD-UT-10

### Land Pattern — 2.3mm x 2.3mm MLPD-UT-10

### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2016

**Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Wireless Charging ICs category:

Click to view products by Semtech manufacturer:

Other Similar products are found below :

MWCT1111CLH P9028AC-0NBGI8 P9036BNTGI MWCT1012CFM BD57020MWV-E2 P9027LP-RAWGI8 MWCT1012VLF MWCT1013VLH MWCT1000CFM MWCT1003AVLHR NXQ1TXA5/404J TS51111-M22WCSR TS51224-M000WCSR TS51231-QFNR MWCT1001AVLH STWBC STWLC03JR STWLC04JR BQ500410ARGZT BQ51003YFPR BQ51013BRHLR BQ51020YFPR TS80003-QFNR NN32251A-VT STWBCTR STWLC68JRH BQ50002ARHBR BQ50002RHBR BQ50002RHBT BQ500211ARGZT BQ500211RGZT BQ500414QRGZTQ1 BQ51013AYFPT BQ51025YFPT BQ51051BRHLR BQ51051BRHLT BQ51051BYFPR BQ51051BYFPT BQ51052BYFPT BQ51221YFPT BQ51222YFPR