# TS80000

## High Efficiency Transmitter Controller for Wireless Power Systems

#### **POWER PRODUCTS**

#### Features

- Supports Qi<sup>®</sup>, PMA and proprietary charging applications

- Power outputs up to 40W+

- Support for single and multi-coil applications

- Support for half and full-bridge power sections

- Support for variable voltage, variable frequency and variable duty cycle architectures

- Integrated controller and flash for communications and control

- High precision data converters

- Precise control of bridge duty cycle and frequency

- Low external component count

- RISC-based controller core with flash and SRAM memory

- Two 12-bit A/D converters

- DMA controller

- Three 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter

- Dual 16-bit PWM timers with dead-time generation

- 3 AGPIO and 5 GPIO for application customization

- I2C or UART interface

- USB interface

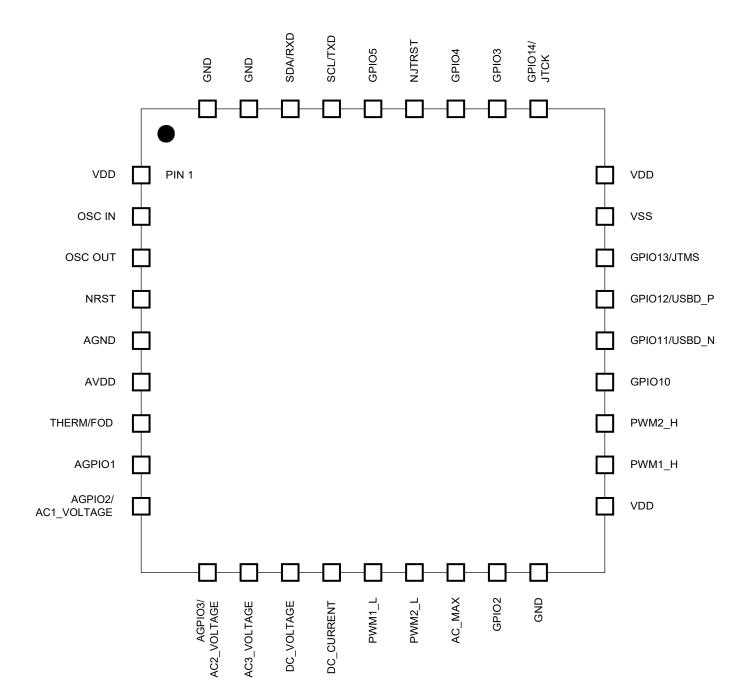

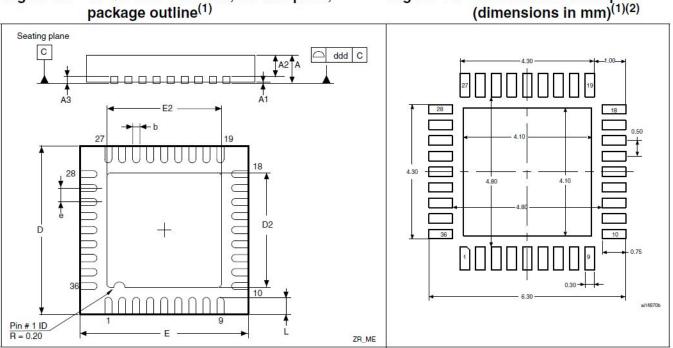

- 36 pin 6x6 QFN

#### Description

The TS80000 is a power transmitter communications and control unit for wireless charging applications. The TS80000 can support power outputs up to 40W+, and supports Qi<sup>®</sup> compliant, PMA compliant and proprietary applications. The TS80000 can be configured to drive single or multi-coil applications, in half and full-bridge systems.

The TS80000 performs the necessary decode of packets from the secondary side device and adjusts the control accordingly. An integrated PID filter provides the necessary compensation for the loop for high-precision control of duty cycle, frequency, and or bridge voltage.

#### **Applications**

- Qi<sup>®</sup> and non-standard wireless chargers for:

- Cell Phones and Smartphones

- GPS Devices

- Digital Cameras

- Tablets and eReaders

- Portable Lighting

- **0** Industrial applications

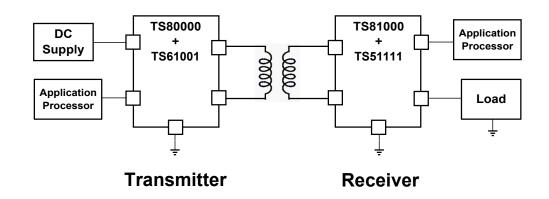

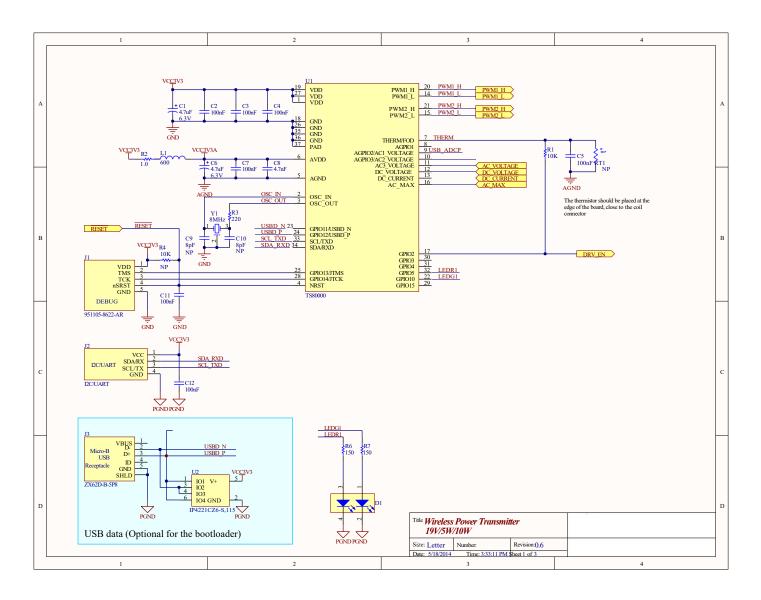

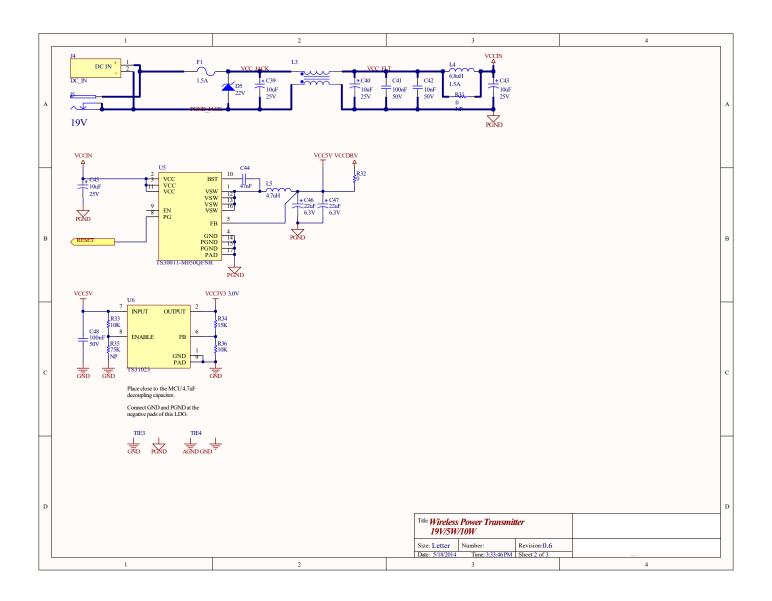

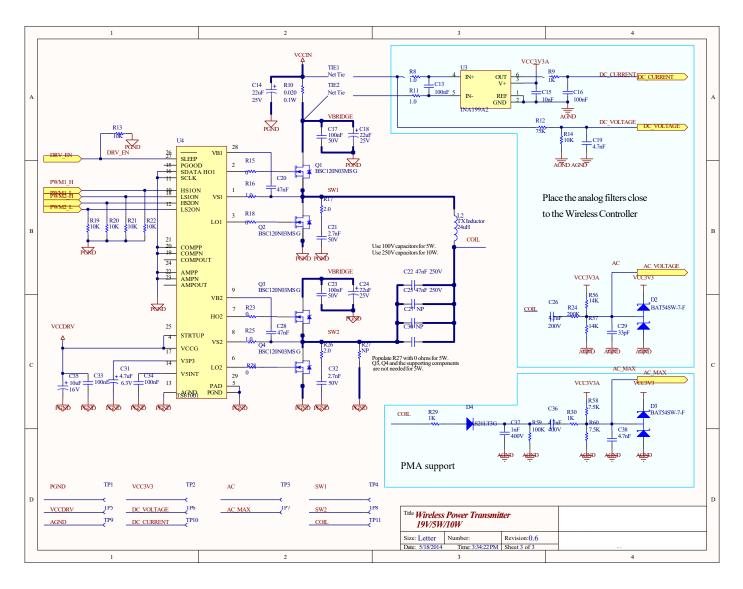

#### Typical Application Circuit

# Pinout(TopView)

# **Pin Description**

| Pin # | Pin Name            | Pin Function      | Description                                                                                    |

|-------|---------------------|-------------------|------------------------------------------------------------------------------------------------|

| 1     | VDD                 | Input power       | Input power supply                                                                             |

| 2     | OSC_IN              | Oscillator input  | Oscillator input                                                                               |

| 3     | OSC_OUT             | Oscillator output | Oscillator output                                                                              |

| 4     | NRST                | Reset             | Reset input                                                                                    |

| 5     | AGND                | Analog GND        | Analog GND                                                                                     |

| 6     | AVDD                | Analog power      | Analog power supply                                                                            |

| 7     | THERM/FOD           | Thermistor/FOD    | Thermistor input or FOD calibration input                                                      |

| 8     | AGPI01              | Analog GPIO       | Analog GPIO1                                                                                   |

| 9     | AGPIO2/ AC1_VOLTAGE | Analog GPIO       | Analog GPIO2 or AC coil voltage for coil #1 in a three-coil system                             |

| 10    | AGPIO3/ AC2_VOLTAGE | Analog GPIO       | Analog GPIO3 or AC coil voltage for coil #2 in a three-coil system                             |

| 11    | AC3_VOLTAGE         | Analog GPIO       | AC coil voltage for a single-coil system or AC coil voltage for coil #3 in a three-coil system |

| 12    | DC_VOLTAGE          | Analog GPIO       | DC input voltage measurement                                                                   |

| 13    | DC_CURRENT          | Analog GPIO       | DC input current measurement                                                                   |

| 14    | PWM1_L              | PWM output        | PWM1 low-side control                                                                          |

| 15    | PWM2_L              | PWM output        | PWM2 low-side control                                                                          |

| 16    | AC_MAX              | Analog GPIO       | Communication demodulator input                                                                |

| 17    | DRV_EN              | Drive enable      | FET driver enable                                                                              |

| 18    | GND                 | Power GND         | Power GND                                                                                      |

| 19    | VDD                 | Input power       | Input power supply                                                                             |

| 20    | PWM1_H              | PWM               | PWM1 high-side control                                                                         |

| 21    | PWM2_H              | PWM               | PWM2 high-side control                                                                         |

| 22    | GPIO10              | GPIO              | GPI010                                                                                         |

| 23    | GPIO11/USBD_N       | GPIO/USB data     | GPIO11 or USB data input (D-)                                                                  |

| 24    | GPIO12/USBD_P       | GPIO/USB data     | GPIO12 or USB data input (D+)                                                                  |

| 25    | GPIO13/JTMS         | GPIO/JTAG         | GPIO13 or JTAG state machine control                                                           |

| 26    | GND                 | Power GND         | Power GND                                                                                      |

| 27    | VDD                 | Input power       | Input power supply                                                                             |

| 28    | GPIO14/JTCK         | GPIO/JTAG         | GPIO14 or JTAG clock                                                                           |

| 29    | GPIO15              | GPIO              | GPI015                                                                                         |

| 30    | GPIO3               | GPIO              | GPIO3                                                                                          |

| 31    | GPIO4               | GPIO              | GPIO4                                                                                          |

| 32    | GPIO5               | GPIO              | GPIO5                                                                                          |

| 33    | SCL/TXD             | I2C/UART          | I2C clock or UART output                                                                       |

| 34    | SDA/RXD             | I2C/UART          | I2C data or UART input                                                                         |

| 35    | GND                 | Power GND         | Power GND                                                                                      |

| 36    | GND                 | Power GND         | Power GND                                                                                      |

# Functional Block Diagram

# Absolute Maximum Rating

Over operating free-air temperature range unless otherwise noted (1,2,3)

| Parameter                                                                                                                                                       | Min       | Max       | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|

| VDD, AVDD, GND, AGND (supply voltage)                                                                                                                           | -0.3      | 4.0       | V    |

| OSC_IN, OSC_OUT, DRV_EN, PWM1_H, PWM2_H, GPIO10, GPIO11/USBD_N, GPIO12/<br>USBD_P, GPIO13/JTMS, GPIO3, GPIO4, SCL/TXD, SDA/RXD                                  | GND - 0.3 | VDD + 4.0 | v    |

| NRST, THERM/FOD, AGPIO1, AGPIO2/AC1_VOLTAGE, AGPIO3/AC2_VOLTAGE, AC3_<br>VOLTAGE, DC_VOLTAGE, DC_CURRENT, PWM1_L, PWM2_L, AC_MAX, GPIO14/JTCK,<br>GPIO15, GPIO5 | GND - 0.3 | 4.0       | v    |

| Operating Junction Temperature Range, TJ                                                                                                                        | -40       | 125       | °C   |

| Storage Temperature Range, TSTG                                                                                                                                 | -65       | 150       | °C   |

| Electrostatic Discharge – Human Body Model                                                                                                                      |           | ±2k       | V    |

| IR Reflow Temperature (soldering, 10 seconds)                                                                                                                   |           | 260       | °C   |

Notes:

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) ESD testing is performed according to the respective JESD22 JEDEC standard.

| Parameter                                  | Symbol           | Min. | Тур.    | Max. | Units |

|--------------------------------------------|------------------|------|---------|------|-------|

| Input Operating Voltage                    | VDD / AVDD       | 2.0  | 3.3     | 3.6  | V     |

| Oscillator Frequency                       | F <sub>osc</sub> |      | 8.0     |      | MHz   |

|                                            |                  |      | 100     |      | nF    |

| Analog Supply decoupling capacitor values  | AVDD             |      | 4.7     |      | nF    |

|                                            |                  |      | 4.7     |      | uF    |

|                                            |                  |      | 3 x 100 |      | - 5   |

| Digital Supply decoupling capacitor values | VDD              |      | 4.7     |      | nF    |

| Operating Free Air Temperature             | T <sub>A</sub>   | -40  |         |      | uF    |

|                                            |                  | 10   |         | 85   | °C    |

| Operating Junction Temperature             | T,               | -40  |         | 105  | °C    |

# **Operating Conditions**

# **Communication Interfaces**

The Applications Processor can interrogate the TS8000x using the I2C or UART interface. The two interfaces share the same pins. Only one interface is active at any time.

# I2C

#### I/O Pins

ALERT pin (optional):

- Driven high when an event is active in the internal STATUS register

- Driven low when all the internal events are cleared

Note: The ALERT pin is provided to help with I2C communication, i.e. to signal events to the App. MCU so the App. MCU can interrogate the TS80000 via I2C to see what changed on the wireless interface. The use of the ALERT pin is not mandatory in the application.

SCL pin:

- Clock pin for the I2C interface.

- Open-drain with weak pull-ups. Needs stronger external pull-ups for full-speed operation.

#### SDA pin:

- Data pin for the I2C interface.

- Open-drain with weak pull-ups. Needs stronger external pull-ups for full-speed operation.

# Write Register Operations

#### I2C Protocol

The TS80000 Wireless Power Transmitter Controller acts as an I2C slave peripheral to allow communication with an application microcontroller. The slave address (7 bit) is 0x50. The Application MCU is an I2C master and initiates every data transfer.

The TS80000 implements a set of registers available from the I2C bus. It also implements a set of API functions that receive parameters and return values using the I2C bus. Four transfer types are possible:

- Write Register

- Read Register

- Run API Function

- Read API Function Return Buffer

#### Description

Description

| START |                             |           |           | Start of the I2C transfer.               |  |  |  |  |

|-------|-----------------------------|-----------|-----------|------------------------------------------|--|--|--|--|

| M→S   | Slave Address (7 bits)      | 0 (1 bit) | Slave ACK | Slave address + R/nW bit (0xA0 as 8-bit) |  |  |  |  |

| M→S   | Register n address (8 bits) |           | Slave ACK | Address of the first register            |  |  |  |  |

| M→S   | Register n Data (8 bits)    |           | Slave ACK | Write the first register                 |  |  |  |  |

| M→S   | Register n+1 Data (8 bits)  |           | Slave ACK | Optionally write the following registers |  |  |  |  |

|       |                             |           |           |                                          |  |  |  |  |

| M→S   | Register n+k Data (8 bits)  |           | Slave ACK |                                          |  |  |  |  |

| STOP  |                             |           |           | Stop of the I2C transfer                 |  |  |  |  |

#### **Read Register Operations**

| START        |                             |                              |            | Start of the I2C transfer.                                           |  |  |  |  |

|--------------|-----------------------------|------------------------------|------------|----------------------------------------------------------------------|--|--|--|--|

| M➔S          | Slave Address (7 bits)      | 0 (1 bit)                    | Slave ACK  | Slave address + 0 as R/nW bit (0xA0 as 8-bit)                        |  |  |  |  |

| M <b>→</b> S | Register n address (8 bits) |                              | Slave ACK  | Address of the first register                                        |  |  |  |  |

| START        |                             |                              |            | Repeated Start                                                       |  |  |  |  |

| M➔S          | Slave Address (7 bits)      | 1 (1 bit)                    | Slave ACK  | Slave address + 1 as R/nW bit (0xA1 as 8-bit)                        |  |  |  |  |

| S➔M          | Register n Data (8 bits)    |                              | Master ACK | Read the first register                                              |  |  |  |  |

| S➔M          | Register n+1 Data (8 bits)  |                              | Master ACK | Optionally read the following registers                              |  |  |  |  |

|              |                             |                              |            |                                                                      |  |  |  |  |

| ѕ➔м          | Register n+k Data (8 bits)  | +k Data (8 bits) Master nACK |            | The master should send a nACK after the last data byte was received. |  |  |  |  |

| STOP         |                             |                              |            | Stop of the I2C transfer                                             |  |  |  |  |

#### **Run API Function**

### Description

| START |                               |           |           | Start of the I2C transfer                                                          |

|-------|-------------------------------|-----------|-----------|------------------------------------------------------------------------------------|

| M➔S   | Slave Address (7 bits)        | 0 (1 bit) | Slave ACK | Slave address + R/nW bit (0xA0 as 8-bit                                            |

| M➔S   | API number (8 bits)           |           | Slave ACK | API number                                                                         |

| M→S   | API input buffer length m (   | 8 bits)   | Slave ACK | API input buffer length. Equal to 0 if no input buffer data is required by the API |

| M➔S   | Input buffer data[0] (8 bits) |           | Slave ACK | First byte of the input buffer (optional)                                          |

| M➔S   | Input buffer data[1] (8 bits) |           | Slave ACK | Second byte of the input buffer (optional)                                         |

|       |                               |           |           |                                                                                    |

| M➔S   | Input buffer data[m-1] (8 bit | s)        | Slave ACK | Last byte of the input buffer (optional)                                           |

| STOP  |                               |           |           | Stop of the I2C transfer and execute the API function                              |

#### Read API Function Return Buffer

#### Description

| START        |                               |           |             | Start of the I2C transfer.                                           |  |  |  |  |  |

|--------------|-------------------------------|-----------|-------------|----------------------------------------------------------------------|--|--|--|--|--|

| M➔S          | Slave Address (7 bits)        | 0 (1 bit) | Slave ACK   | Slave address + 0 as R/nW bit (0xA0 as 8-bit)                        |  |  |  |  |  |

| M➔S          | API number (8 bits)           |           | Slave ACK   | API number.                                                          |  |  |  |  |  |

| START        |                               |           |             | Repeated Start                                                       |  |  |  |  |  |

| M <b>→</b> S | Slave Address (7 bits)        | 1 (1 bit) | Slave ACK   | Slave address + 1 as R/nW bit (0xA1 as 8-bit)                        |  |  |  |  |  |

| S➔M          | API number (8 bits)           |           | Master ACK  | API number for the following return buffer                           |  |  |  |  |  |

| S <b>→</b> M | API return buffer length n (8 | bits)     | Master ACK  | API return buffer length                                             |  |  |  |  |  |

| S→M          | Output buffer data[0] (8 bits | )         | Master ACK  | Read the first byte in the output buffer                             |  |  |  |  |  |

| S→M          | Output buffer data[1] (8 bits | )         | Master ACK  | Optionally read the following bytes                                  |  |  |  |  |  |

|              |                               |           |             |                                                                      |  |  |  |  |  |

| ѕ➔м          | Output buffer data[n-1] (8 bi | its)      | Master nACK | The master should send a nACK after the last data byte was received. |  |  |  |  |  |

| STOP         |                               |           |             | Stop of the I2C transfer                                             |  |  |  |  |  |

# **Internal Registers**

| Addresss        | Name                                   | Туре       | Access Mode (bits) | Description                                        |

|-----------------|----------------------------------------|------------|--------------------|----------------------------------------------------|

| General Regist  | ers                                    |            |                    | <b>•</b>                                           |

| 0x00            | BOOTFW_REV_L                           | R          | 8/16               | Bootloader Firmware Revision (L)                   |

| 0x01            | BOOTFW REV H                           | R          | 8/16               | Bootloader Firmware Revision (H)                   |

|                 |                                        |            |                    |                                                    |

| 0x02            | FW_REV_L                               | R          | 8/16               | Firmware Revision (L)                              |

| 0x03            | FW_REV_H                               | R          | 8/16               | Firmware Revision (H)                              |

| 0x04            | MODE_L                                 | R          | 8/16               | Operating Mode (L)                                 |

| 0x05            | MODE_H                                 | R          | 8/16               | Operating Mode (H)                                 |

| 0x06            | RESET_L                                | R/W        | 8/16               | Reset Register (L)                                 |

| 0x07            | RESET_H                                | R/W        | 8/16               | Reset Register (H)                                 |

| 0x08            | STATUS0                                | R          | 8                  | Status0 Register                                   |

| 0x09<br>0x0A    | STATUS1<br>STATUS2                     | R          | 8                  | Status1 Register<br>Status2 Register               |

| 0x0A<br>0x0B    | STATUS2<br>STATUS3                     | R          | 8                  | Status2 Register                                   |

| 0x0C            | RESERVED                               | N          | 0                  |                                                    |

| Bootloader Mo   |                                        |            |                    |                                                    |

|                 |                                        |            |                    |                                                    |

| 0x0D<br>0x0E    | BLOCK_SIZE                             | R          | 8<br>8 / 16        | Block Size                                         |

| 0x0E<br>0x0F    | FW_SIZE_L<br>FW_SIZE_H                 | R          | 8/16               | Firmware Size (L)                                  |

| 0x0F<br>0x10    | CONFIG SIZE L                          | R          | 8/16               | Firmware Size (H)<br>Configuration Size (L)        |

| 0x10            | CONFIG SIZE H                          | R          | 8/16               | Configuration Size (H)                             |

| 0x11            | CALIBRATION SIZE L                     | R          | 8/16               | Calibration Size (L)                               |

| 0x12            | CALIBRATION SIZE H                     | R          | 8/16               | Calibration Size (H)                               |

| 0x14            | FW FLAGS L                             | R          | 8/16               | Firmware Flags (L)                                 |

| 0x15            | FW FLAGS H                             | R          | 8/16               | Firmware Flags (H)                                 |

| 0x16-0x7F       | RESERVED                               |            |                    |                                                    |

| Transmitter Mod |                                        |            |                    | 1                                                  |

| 0x0D            | CHANNEL COUNT                          | R          | 8                  | Channel Count                                      |

| 0x0E            | CHANNEL_SELECT                         | R/W        | 8                  | Channel Selection Register                         |

| 0x0F            | COIL_COUNT                             | R          | 8                  | Coil Count                                         |

| 0x10            | FREQ_MIN_LIMIT_L                       | R/W        | 16                 | Limit for the Minimum Frequency (L)                |

| 0x11            | FREQ_MIN_LIMIT_H                       | R/W        | 16                 | Limit for the Minimum Frequency (H)                |

| 0x12            | FREQ_MAX_LIMIT_L                       | R/W        | 16                 | Limit for the Maximum Frequency (L)                |

| 0x13            | FREQ_MAX_LIMIT_H                       | R/W        | 16                 | Limit for the Maximum Frequency (H)                |

| 0x14            | DC_CURRENT_LIMIT_L                     | R/W        | 16                 | DC Current Limit (L)                               |

| 0x15            | DC_CURRENT_LIMIT_H                     | R/W        | 16                 | DC Current Limit (H)                               |

| 0x16            |                                        | R/W        | 16                 | AC Voltage Limit (L)                               |

| 0x17            | AC_VOLTAGE_LIMIT_H                     | R/W<br>R/W | 16<br>16           | AC Voltage Limit (H)<br>Coil Temperature Limit (L) |

| 0x18<br>0x19    | TEMP_COIL_LIMIT_L<br>TEMP_COIL_LIMIT_H | R/W        | 16                 | Coil Temperature Limit (L)                         |

| 0x1A            | TEMP DIE LIMIT L                       | R/W        | 16                 | Die Temperature Limit (L)                          |

| 0x1A<br>0x1B    |                                        | R/W        | 16                 | Die Temperature Limit (H)                          |

| 0x1C            | FAN TEMP MIN                           | R/W        | 8                  | Minimum Temperature for Fan Control                |

| 0x1D            | FAN TEMP MAX                           | R/W        | 8                  | Maximum Temperature for Fan Control                |

| 0x1E            | FAN DTC MIN                            | R/W        | 8                  | Minimum Duty Cycle for Fan Control                 |

| 0x1F            | FAN_DTC_MAX                            | R/W        | 8                  | Maximum Duty Cycle for Fan Control                 |

| 0x20            | SUPPORTED_STANDARDS                    | R/W        | 8                  | Supported Standards                                |

| 0x21            | MAX_POWER_WPC                          | R/W        | 8                  | Maximum Power in WPC Mode                          |

| 0x22            | MAX_POWER_PMA                          | R/W        | 8                  | Maximum Power in PMA Mode                          |

| 0x23            | MAX_POWER_A4WP                         | R/W        | 8                  | Maximum Power in A4WP Mode                         |

| 0x24-0x3F       | RESERVED                               |            |                    |                                                    |

| 0x40            | ACTIVE_COIL                            | R          | 8                  | Active Coil                                        |

| 0x41            | POWER_STATE_TX                         | R          | 8                  | Transmitter Power State                            |

| 0x42            | STANDARD                               | R          | 8                  | Wireless Power Standard                            |

| 0x43            | POWER_LEVEL                            | R          | 8                  | Power Level                                        |

| 0x44            | FOD_TYPE                               | R          | 8                  | Foreign Object Detection Type                      |

# **Internal Registers**

| Addresss       | Name                 | Туре | Access Mode (bits) | Description                            |

|----------------|----------------------|------|--------------------|----------------------------------------|

| Transmitter Ma | ode continues        | 1    |                    |                                        |

| 0x45           | POWER STATE RX       | R    | 8                  | Receiver Power State                   |

| 0x46           | PWM FREQUENCY L      | R    | 16                 | PWM Frequency (L)                      |

| 0x47           | PWM FREQUENCY H      | R    | 16                 | PWM Frequency (H)                      |

| 0x48           | PWM DTC L            | R    | 16                 | PWM Duty Cycle (L)                     |

| 0x49           | PWM DTC H            | R    | 16                 | PWM Duty Cycle (H)                     |

| 0x4A           | DC VOLTAGE L         | R    | 16                 | Bridge DC Voltage (L)                  |

| 0x4B           | DC VOLTAGE H         | R    | 16                 | Bridge DC Voltage (H)                  |

| 0x4C           | DC CURRENT L         | R    | 16                 | Bridge DC Current (L)                  |

| 0x4D           | DC CURRENT H         | R    | 16                 | Bridge DC Current (H)                  |

| 0x4E           | AC VOLTAGE L         | R    | 16                 | Coil AC voltage (L)                    |

| 0x4F           | AC VOLTAGE H         | R    | 16                 | Coil AC Voltage (H)                    |

| 0x50           | AC CURRENT L         | R    | 16                 | Coil AC Current (L)                    |

| 0x51           | AC CURRENT H         | R    | 16                 | Coil AC Current (H)                    |

| 0x52           | TEMP_COIL_L          | R    | 16                 | Temperature at the Coil Thermistor (L) |

| 0x53           | TEMP COIL H          | R    | 16                 | Temperature at the Coil Thermistor (H) |

| 0x54           | TEMP DIE L           | R    | 16                 | Die Temperature (L)                    |

| 0x55           | TEMP DIE H           | R    | 16                 | Die Temperature (H)                    |

| 0x56           | POWER DC IN L        | R    | 16                 | DC Power at the Bridge Input (L)       |

| 0x57           | POWER DC IN H        | R    | 16                 | DC Power at the Bridge Input (H)       |

| 0x58           | POWER TX L           | R    | 16                 | TX Power into the Magnetic Field (L)   |

| 0x59           | POWER TX H           | R    | 16                 | TX Power into the Magnetic Field (H)   |

| 0x5A           | POWER RX L           | R    | 8                  | Received Power Reported by the RX (L)  |

| 0x5B           | POWER RX H           | R    | 8                  | Received Power Reported by the RX (H)  |

| 0x5C           | BATT CHARGE LEVEL RX | R    | 8                  | Receiver Battery Charge Level          |

| 0x5D           | LED STATE            | R    | 8                  | LED State                              |

| 0x5E           | ERROR L              | R    | 16                 | Error Code and Parameter (L)           |

| 0x5F           | ERROR H              | R    | 16                 | Error Code and Parameter (H)           |

| 0x60-0x6F      | RESERVED             |      |                    |                                        |

| 0x70           | CONTROL POWER L      | R/W  | 16                 | Power Control Register (L)             |

| 0x71           | CONTROL POWER H      | R/W  | 16                 | Power Control Register (H)             |

| 0x72           | CONTROL DEBUG L      | R/W  | 16                 | Debug Control Register (L)             |

| 0x73           | CONTROL DEBUG H      | R/W  | 16                 | Debug Control Register (H)             |

| 0x74           | DEBUG MASKO          | R/W  | 8                  | Debug Mask Register 0                  |

| 0x75           | DEBUG MASK1          | R/W  | 8                  | Debug Mask Register 1                  |

| 0x76           | DEBUG MASK2          | R/W  | 8                  | Debug Mask Register 2                  |

| 0x77           | <br>DEBUG_MASK3      | R/W  | 8                  | Debug Mask Register 3                  |

| 0x78           | INTERRUPT MASKO      | R/W  | 8                  | Interrupt Mask Register 0              |

| 0x79           | INTERRUPT MASK1      | R/W  | 8                  | Interrupt Mask Register 1              |

| 0x7A           | INTERRUPT MASK2      | R/W  | 8                  | Interrupt Mask Register 2              |

| 0x7B           | INTERRUPT MASK3      | R/W  | 8                  | Interrupt Mask Register 3              |

| 0x7C-0x7F      | RESERVED             |      |                    |                                        |

#### Bootloader Firmware Revision Register (BOOTFW\_REV\_H:BOOTFW\_REV\_L)

Address:

0x00

Reset value: Major and Minor version number of the bootloader firmware

| 15 | 14 | 13 | 12   | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3      | 2 | 1 | 0 |

|----|----|----|------|--------|----|---|---|---|---|---|------|--------|---|---|---|

|    |    |    | REV_ | H[7:0] |    |   |   |   |   |   | REV_ | L[7:0] |   |   |   |

| r  | r  | r  | r    | r      | r  | r | r | r | r | r | r    | r      | r | r | r |

Bits 15:8 REV\_H[7:0]: Major Bootloader Firmware Revision These bits contain the major version number of the bootloader firmware. Bits 7:0 REV\_L[7:0]: Minor Bootloader Firmware Revision

These bits contain the minor version number of the bootloader firmware.

#### Firmware Revision Register (FW\_REV\_H:FW\_REV\_L)

| Address:     | 0x02                                                       |

|--------------|------------------------------------------------------------|

| Reset value: | Major and Minor version number of the transmitter firmware |

| 15 | 14         | 13 | 12 | 11 | 10 | 9 | 8          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|------------|----|----|----|----|---|------------|---|---|---|---|---|---|---|---|

|    | REV_H[7:0] |    |    |    |    |   | REV_L[7:0] |   |   |   |   |   |   |   |   |

| r  | r          | r  | r  | r  | r  | r | r          | r | r | r | r | r | r | r | r |

Bits 15:8 REV\_H[7:0]: Major Firmware Revision These bits contain the major version number of the transmitter firmware. Bits 7:0 REV\_L[7:0]: Minor Firmware Revision These bits contain the minor version number of the transmitter firmware.

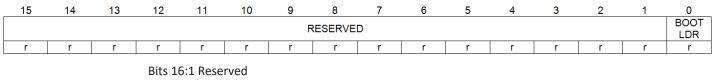

#### Operating Mode Register (MODE\_H:MODE\_L)

Address:0x04Reset value:Depends on the bootloader mode and the firmware type

Bit 0 BOOTLDR: Bootloader mode

0: The transmitter firmware is running

1: The controller is in bootloader mode

#### Reset Register (RESET\_H:RESET\_L)

| Address<br>Reset va |    | 0x06<br>0x00 |    |    |    |    |        |                                                                                              |    |    |    |    |    |    |    |

|---------------------|----|--------------|----|----|----|----|--------|----------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|

| 15                  | 14 | 13           | 12 | 11 | 10 | 9  | 8      | 7                                                                                            | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|                     |    |              |    |    |    |    | RESET_ | <ey[15:0]< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td></ey[15:0]<> |    |    |    |    |    |    |    |

| rw                  | rw | rw           | rw | rw | rw | rw | rw     | rw                                                                                           | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 RESET\_KEY[15:0]: Reset Key

0xAA55: generate a system reset

0xA5A5: generate a system reset and enter bootloader mode

Any other value: a system reset is not generated

The reset sequence takes about 20 milliseconds. During this time the communication interfaces are not available.

After reset the MODE register can be used to check if the system is in bootloader mode or is running the transmitter firmware.

### Status0 Register(STATUS0)

| Address:     | 0x08    |              |                      |                     |                    |                     |                   |

|--------------|---------|--------------|----------------------|---------------------|--------------------|---------------------|-------------------|

| leset value: | 0xC0    |              |                      |                     |                    |                     |                   |

| 7            | 6       | 5            | 4                    | 3                   | 2                  | 1                   | 0                 |

| CTS          | CTS_API | CTS_IF       | CTS_API_IF           | STATUS3             | STATUS2            | STATUS1             | Res               |

| r            | r       | r            | r                    | r                   | r                  | r                   |                   |

|              | Bit 7   | CTS: Clear T | o Send               |                     |                    |                     |                   |

|              |         | This bit     | indicates if a new   | v read/write reg    | ister access can l | be issued to the co | ontroller. This b |

|              |         |              | eset by hardware     |                     |                    |                     |                   |

|              |         |              | -                    |                     | vious register ac  | ccess. New comma    | ands should not   |

|              |         |              | to the controller.   |                     | -                  |                     |                   |

|              |         | 1:The        | controller can acc   | ept a new regist    | er access comm     | and over the com    | munication        |

|              |         | interfa      |                      |                     |                    |                     |                   |

|              | Bit 6   | CTS API: Cle | ar to Send for API   |                     |                    |                     |                   |

|              |         | _            |                      | API call or API     | read request car   | be issued to the    | controller. This  |

|              |         |              | ot reset by hardwa   |                     | ·                  |                     |                   |

|              |         |              | -                    |                     | vious API call. N  | ew API calls shoul  | d not be sent to  |

|              |         | the cor      |                      |                     |                    |                     |                   |

|              |         | 1: The       | controller can ac    | cept a new API      | call over the co   | mmunication inte    | erface.           |

|              | Bit 5   |              | To Send Event In     | -                   |                    |                     |                   |

|              |         | 0: No e      | vent is signaled fo  | or the CTS bit or   | the correspondi    | ng bit in the INTEF | RUPT_MASKO        |

|              |         | registe      | r is cleared.        |                     | -                  | -                   | _                 |

|              |         | 1: The       | CTS bit has been s   | et and the corre    | sponding bit in t  | the INTERRUPT_M     | IASK0 register i  |

|              |         | set. Re      | set to 0 by hardwa   | are when the ST     | ATUS0 register is  | s read.             |                   |

|              | Bit 4   | CTS_API_IF:  | Clear to Send for A  | API Event Interru   | upt Flag           |                     |                   |

|              |         | 0: No e      | vent is signaled fo  | or the CTS_API b    | it.                |                     |                   |

|              |         | 1: The       | CTS_API bit has be   | en set and the o    | corresponding bi   | it in the INTERRUP  | T_MASK0           |

|              |         | registe      | r is set. Reset to 0 | by hardware wi      | nen the STATUS     | O register is read. |                   |

|              | Bit 3   | STATUS3_IF:  | STATUS1 Event Ir     | nterrupt Flag       |                    |                     |                   |

|              |         | 0: No e      | vent is signaled in  | the STATUS3 re      | gister or the cor  | rresponding bit in  | the INTERRUP      |

|              |         | MASK         | ) register is cleare | ed.                 |                    |                     |                   |

|              |         | 1: An e      | vent is signaled in  | the STATUS3 re      | gister and the co  | orresponding bit ir | the               |

|              |         | INTERR       | UPT_MASK3 regist     | er is set. Reset to | o 0 by hardware v  | when the STATUS3    | register is read. |

|              | Bit 2   | STATUS2_IF:  | STATUS2 Event Ir     | nterrupt Flag       |                    |                     |                   |

|              |         | 0: No e      | vent is signaled in  | the STATUS2 re      | gister or the cor  | rresponding bit in  | the INTERRUP      |

|              |         | MASK         | ) register is cleare | ed.                 |                    |                     |                   |

|              |         | 1: An e      | vent is signaled in  | the STATUS2 re      | gister and the co  | prresponding bit ir | the               |

|              |         | INTERR       | UPT_MASK2 regist     | er is set. Reset to | o 0 by hardware v  | when the STATUS2    | register is read. |

|              | Bit 1   | STATUS1_IF:  | STATUS1 Event Ir     | nterrupt Flag       |                    |                     |                   |

|              |         | 0: No e      | vent is signaled in  | the STATUS1 re      | gister or the cor  | rresponding bit in  | the INTERRUP      |

|              |         | MASK         | ) register is cleare | ed.                 |                    |                     |                   |

|              |         | 1: An e      | vent is signaled in  | the STATUS1 re      | gister and the co  | prresponding bit in | the               |

|              |         | INTERR       | UPT_MASK1 regist     | er is set. Reset to | o 0 by hardware v  | when the STATUS1    | register is read. |

|              | Bit 0   | Reserved     |                      |                     |                    |                     |                   |

### Status1 Register(STATUS1)

| Address:<br>Reset value: | 0x09<br>0x00 |          |                |                    |                      |                   |                   |               |

|--------------------------|--------------|----------|----------------|--------------------|----------------------|-------------------|-------------------|---------------|

| 7                        |              | 6        | 5              | 4                  | 3                    | 2                 | 1                 | 0             |

|                          | Res          | _        | RX_EOC         | RX_CHG             | RX_CONFIG            | RX_ID             | RX_RMV            | RX_DET        |

|                          |              |          | ſ              | r                  | r                    | r                 | r                 | r             |

|                          |              | Bits 7:4 | Reserved       |                    |                      |                   |                   |               |

|                          |              | Bit 5    | RX_EOC: RX I   | End of Charge R    | eceived              |                   |                   |               |

|                          |              |          | 0: No RX End   | of Charge comm     | and has been rece    | ived since the    | last read.        |               |

|                          |              |          | 1: The RX End  | of Charge comm     | nand has been reco   | eived. Reset to   | 0 by hardware w   | hen read.     |

|                          |              | Bit 4    | RX_CHG: RX C   | Charge Level Rec   | eived                |                   |                   |               |

|                          |              |          | 0: No RX char  | ge level has beer  | n received since th  | e last read.      |                   |               |

|                          |              |          | 1: The RX cha  | rge level has bee  | en received. Reset   | to 0 by hardwa    | are when read.    |               |

|                          |              | Bit 3    | RX_CONFIG:     | RX Configuratio    | n Received           |                   |                   |               |

|                          |              |          | 0: No RX con   | figuration data    | has been received    | since the last    | read.             |               |

|                          |              |          | 1: The RX con  | figuration phase   | has completed. Re    | eset to 0 by ha   | rdware when read  | d.            |

|                          |              | Bit 2    | RX_ID: RX Ide  | ntification Recei  | ved                  |                   |                   |               |

|                          |              |          | 0: No RX iden  | tification data ha | as been received si  | ince the last rea | ad.               |               |

|                          |              |          | 1: The RX ider | ntification phase  | has completed. Re    | eset to 0 by hai  | rdware when read  | d.            |

|                          |              | Bit 1    | RX RMV: RX I   |                    |                      | -                 |                   |               |

|                          |              |          | 0: No RX remo  | oval event has o   | ccurred since the la | ast read.         |                   |               |

|                          |              |          | 1: The RX dev  | ice has been ren   | noved from the TX    | surface. Reset    | to 0 by hardware  | when read.    |

|                          |              | Bit 0    | RX_DET: RX D   |                    |                      |                   |                   |               |

|                          |              |          | —              |                    | occurred since the   | last read.        |                   |               |

|                          |              |          | 1: A RX device | e has been detec   | ted on the transm    | itter surface. R  | eset to 0 by hard | ware when rea |

### Status2 Register(STATUS2)

| Address:<br>Reset value: | 0x0A<br>0x00 |   |    |   |   |     |       |

|--------------------------|--------------|---|----|---|---|-----|-------|

| 7                        | 6            | 5 | 4  | 3 | 2 | 1   | 0     |

|                          |              | D | es |   |   | LED | ERROR |

|                          |              | N | 53 |   |   | r   | r     |

| TS80000<br>Final Datasheet<br>April 23, 2018 | Rev1.5         |                 | www.sem                               | itech.com         |                 |                | 12 of |

|----------------------------------------------|----------------|-----------------|---------------------------------------|-------------------|-----------------|----------------|-------|

|                                              |                | 1: A debug eve  | ent has occurred                      | . Reset to 0 by h | ardware when re | ead.           |       |

|                                              |                |                 | vent has occurre                      |                   |                 |                |       |

|                                              | Bit 0          | DEBUG: Debug    |                                       |                   |                 |                |       |

|                                              |                | 1: A test event | has occurred. R                       | eset to 0 by hard | dware when read | d.             |       |

|                                              |                | 0: No test eve  | nt has occurred s                     | ince the last rea | ıd.             |                |       |

|                                              | Bit 1          | TEST: Test Eve  | nt                                    |                   |                 |                |       |

|                                              | Bits 7:2       | Reserved        |                                       |                   |                 |                |       |

|                                              |                | Re              | :5                                    |                   |                 | r              | r     |

| 1                                            | 5              | Re              |                                       | 5                 | 2               | LED            | ERROR |

| 7                                            | 6              | 5               | 4                                     | 3                 | 2               | 1              | 0     |

| eset value:                                  | 0x00           |                 |                                       |                   |                 |                |       |

| ddress:                                      | 0x0B           |                 |                                       |                   |                 |                |       |

| status3 Reg                                  | ister(STATUS3) |                 |                                       |                   |                 |                |       |

|                                              |                | 1: An error ha  | s occurred. Reset                     | to 0 by hardwa    | re when read.   |                |       |

|                                              |                | 0: No error ha  | s occurred since                      | the last read.    |                 |                |       |

|                                              | Bit 0          | -               | Condition Detect                      |                   | ,               |                |       |

|                                              |                | -               | n the LED state h<br>the LED state ha |                   |                 | are when read. |       |

|                                              | Bit 1          | LED: LED State  |                                       |                   | a the last read |                |       |

|                                              |                | Reserved        |                                       |                   |                 |                |       |

#### Block Size Register(BLOCK\_SIZE)

| Address:<br>Reset value: | 0x0D<br>0x40 |   |       |           |   |   |   |

|--------------------------|--------------|---|-------|-----------|---|---|---|

| 7                        | 6            | 5 | 4     | 3         | 2 | 1 | 0 |

|                          |              |   | BLOCK | SIZE[7:0] |   |   |   |

| r                        | r            | r | r     | r         | r | r | r |

Bits 7:0 BLOCK\_SIZE[7:0]: FLASH Block Size

This field reports the length of the FLASH block size in bytes.

The following FLASH API functions should use a BLOCK\_DATA field with a size that is equal to BLOCK\_SIZE (or optionally for USB communication, a multiple of BLOCK\_SIZE):

- BOOTLOADER\_WRITE\_BLOCK

- BOOTLOADER\_WRITE\_CONFIGURATION

- BOOTLOADER READ CONFIGURATION

- BOOTLOADER\_WRITE\_CALIBRATION

- BOOTLOADER READ CALIBRATION

- BOOTLOADER TRIM

- BOOTLOADER\_READ\_TRIM

#### Firmware Size Register (FW\_SIZE\_H:FW\_SIZE\_L)

Address: 0x0E

Reset value: Size of the firmware image segment (unit: number of blocks)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8      | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|--------|----------|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   | FW_SI2 | ZE[15:0] |   |   |   |   |   |   |   |

| r  | r  | r  | r  | r  | r  | r | r      | r        | r | r | r | r | r | r | r |

Bits 15:0 FW\_SIZE[15:0]: Size of the firmware image segment (blocks) These bits contain size of the firmware image segment in FLASH measured as a number of BLOCK\_SIZE byte long blocks.

Example: if BLOCK\_SIZE = 64 and the firmware image segment is 51KB (52224 bytes) then FW\_SIZE is 52224 / 64 = 816.

#### Configuration Size Register (CONFIG\_SIZE\_H:CONFIG\_SIZE\_L)

| Address  | 5:    | 0x10    |         |           |          |         |           |            |         |     |   |   |   |   |   |

|----------|-------|---------|---------|-----------|----------|---------|-----------|------------|---------|-----|---|---|---|---|---|

| Reset va | alue: | Size of | the con | figuratio | on image | e segme | nt (unit: | number     | ofblock | (s) |   |   |   |   |   |

| 15       | 14    | 13      | 12      | 11        | 10       | 9       | 8         | 7          | 6       | 5   | 4 | 3 | 2 | 1 | 0 |

|          |       |         |         |           |          |         | CONFIG_   | SIZE[15:0] | ]       |     |   |   |   |   |   |

| r        | r     | r       | r       | r         | r        | r       | r         | r          | r       | r   | r | r | r | r | r |

| r        | r     | r       | r       | r         | r        | r       | r         | r          | r       | r   | r | r | r | r | - |

Bits 15:0 CONFIG\_SIZE[15:0]: Size of the configuration image segment (blocks)

These bits contain size of the configuration image segment in FLASH measured as a number of BLOCK\_SIZE byte long blocks (see the FW\_SIZE for details).

#### Calibration Size Register (CAL\_SIZE\_H:CAL\_SIZE\_L)

| Address | s:    | 0x12    |         |           |          |         |              |          |          |                                                                |   |   |   |   |   |

|---------|-------|---------|---------|-----------|----------|---------|--------------|----------|----------|----------------------------------------------------------------|---|---|---|---|---|

| Reset v | alue: | Size of | the con | figuratio | on image | e segme | nt (unit:    | number   | of block | <s)< td=""><td></td><td></td><td></td><td></td><td></td></s)<> |   |   |   |   |   |

| 15      | 14    | 13      | 12      | 11        | 10       | 9       | 8            | 7        | 6        | 5                                                              | 4 | 3 | 2 | 1 | 0 |

|         |       |         |         |           |          |         | CAL_SI       | ZE[15:0] |          |                                                                |   |   |   |   |   |

| r       | r     | r       | r       | r         | r        | r       | r            | r        | r        | r                                                              | r | r | r | r | r |

|         |       |         |         |           |          |         | <b>C</b> . 1 |          |          |                                                                |   |   |   |   |   |

Bits 15:0 CAL\_SIZE[15:0]: Size of the calibration image segment (blocks)

These bits contain size of the calibration image segment in FLASH measured as a number of BLOCK\_SIZE byte long blocks (see the FW\_SIZE for details).

# Firmware Flags Register (FW\_FLAGS\_H:FW\_FLAGS\_L)

|   | Address<br>Reset va |    | 0x14<br>Firmwa | are flags |        |           |       |   |    |   |   |   |   |   |   |   |

|---|---------------------|----|----------------|-----------|--------|-----------|-------|---|----|---|---|---|---|---|---|---|

|   | 15                  | 14 | 13             | 12        | 11     | 10        | 9     | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| [ |                     |    |                |           |        |           |       | R | es |   |   |   |   |   |   |   |

|   | r                   | r  | r              | r         | r      | r         | r     | r | r  | r | r | r | r | r | r | r |

| _ |                     |    |                |           | Bits 1 | 15:0 Rese | erved |   |    |   |   |   |   |   |   |   |

#### ChannelCountRegister(CHANNEL\_COUNT)

Address: 0x0D Reset value: From the configuration data

| 7 | 6 | 5 | 4       | 3          | 2 | 1 | 0 |

|---|---|---|---------|------------|---|---|---|

|   |   |   | CHANNEL | COUNT[7:0] |   |   |   |

| r | r | r | r       | r          | r | r | r |

|   |   |   |         |            |   |   |   |

Bits 7:0 CHANNEL\_COUNT[7:0]: Number of independent transmitter channels

A transmitter has multiple channels if it can transfer power through multiple coils at the same time.

#### Channel Selection Register (CHANNEL\_SELECT)

| Address:     | 0x0E |

|--------------|------|

| Reset value: | 0x00 |

| _ | 7                   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|---|---------------------|---|---|---|---|---|---|---|--|--|--|--|--|

| [ | CHANNEL SELECT[7:0] |   |   |   |   |   |   |   |  |  |  |  |  |

|   |                     |   |   |   |   |   |   |   |  |  |  |  |  |

Bits 7:0 CHANNEL\_SELECT[7:0]: Number of independent transmitter channels For transmitters with a single channel this register has no effect. For transmitters with more than one channel this field associates all the other registers with one of the channels: 0x00: Channel 0 selected 0x01: Channel 1 selected 0x02: Channel 2 selected

#### CoilCountRegister(COIL\_COUNT)

| Address:     | 0x0F                        |

|--------------|-----------------------------|

| Reset value: | From the configuration data |

| 7             | 6 | 5 | 4       | 3          | 2 | 1 | 0 |  |  |  |

|---------------|---|---|---------|------------|---|---|---|--|--|--|

|               |   |   | CHANNEL | COUNT[7:0] |   |   |   |  |  |  |

| r r r r r r r |   |   |         |            |   |   |   |  |  |  |

Bits 7:0 COIL\_COUNT[7:0]: Number of coils in the transmitter channel:

0x01: 1 coil 0x02: 2 coils ..... 0x07: 7 coils

#### Limitfor the Minimum Frequency Register (FREQ\_MIN\_LIMIT\_H: FREQ\_MIN\_LIMIT\_L)

Address: 0x10 Reset value: From the configuration data

| 15 | 14                   | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | FREQ_MIN_LIMIT[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw | rw                   | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 FREQ\_MIN\_LIMIT[15:0]: Minimum frequency allowed for the transmitter channel (100 Hz) The transmitter doesn't allow its operating frequency to go below this limit. The unit is 100 Hz.

> If a value higher than the transmitter operating frequency is written to this register, the transmitter adjusts its operating frequency so it falls within the correct boundaries. This mechanism can be used for automotive applications to force the transmitter to avoid certain frequency ranges when other wireless devices are used.

Example: To limit the transmitter frequency to 150 kHz or higher, a value of 1500 is written to the FREQ\_MIN\_LIMIT register.

#### Limit for the Maximum Frequency Register (FREQ\_MAX\_LIMIT\_H:FREQ\_MAX\_LIMIT\_L)

| Address:     | 0x12                        |

|--------------|-----------------------------|

| Reset value: | From the configuration data |

| 15                                       | 14                   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|----------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                                          | FREQ MIN LIMIT[15:0] |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| rw r |                      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Bits 15:0 FREQ\_MAX\_LIMIT[15:0]: Maximum frequency allowed for the transmitter channel (100 Hz) The transmitter doesn't allow its operating frequency to go above this limit. The unit is 100 Hz.

If a value lower than the transmitter operating frequency is written to this register, the transmitter adjusts its operating frequency so it falls within the correct boundaries.

Example: To limit the transmitter frequency to 180 kHz or lower, a value of 1800 is written to the FREQ\_MAX\_LIMIT register.

#### DCCurrentLimitRegister(DC\_CURRENT\_LIMIT\_H:DC\_CURRENT\_LIMIT\_L)

| Address  | :     | 0x14  |                           |    |    |    |        |           |       |    |    |    |    |    |    |

|----------|-------|-------|---------------------------|----|----|----|--------|-----------|-------|----|----|----|----|----|----|

| Reset va | alue: | Fromt | om the configuration data |    |    |    |        |           |       |    |    |    |    |    |    |

|          |       |       |                           |    |    |    |        |           |       |    |    |    |    |    |    |

| 15       | 14    | 13    | 12                        | 11 | 10 | 9  | 8      | 7         | 6     | 5  | 4  | 3  | 2  | 1  | 0  |

|          |       |       |                           |    |    | DC | CURREN | IT_LIMIT[ | 15:0] |    |    |    |    |    |    |

| rw       | rw    | rw    | rw                        | rw | rw | rw | rw     | rw        | rw    | rw | rw | rw | rw | rw | rw |

Bits 15:0 DC\_CURRENT\_LIMIT[15:0]: Maximum DC current allowed into the transmitter bridge (mA) The transmitter stops the power transfer and reports an error if the bridge current goes above this limit.

A value of 0x0000 disables the limit checking.

Example: To limit the bridge current to 2A, a value of 2000 is written to the DC\_CURRENT\_LIMIT register.

#### AC Voltage Limit Register (AC\_VOLTAGE\_LIMIT\_H:AC\_VOLTAGE\_LIMIT\_L)

| Address:   |     | 0x16                 |                        |                       |                        |                                                 |                       |            |           |           |    |    |    |    |     |

|------------|-----|----------------------|------------------------|-----------------------|------------------------|-------------------------------------------------|-----------------------|------------|-----------|-----------|----|----|----|----|-----|

| Reset valu | ie: | From th              | ne config              | guration              | data                   |                                                 |                       |            |           |           |    |    |    |    |     |

| 15         | 14  | 13                   | 12                     | 11                    | 10                     | 9                                               | 8                     | 7          | 6         | 5         | 4  | 3  | 2  | 1  | 0   |

|            |     |                      |                        |                       |                        | AC                                              | VOLTAG                | E_LIMIT    | 15:0]     |           |    |    |    |    |     |

| rw         | rw  | rw                   | rw                     | rw                    | rw                     | rw                                              | rw                    | rw         | rw        | rw        | rw | rw | rw | rw | rw  |

| Bits 15:0  |     | The trai<br>point of | nsmitter<br>f the AC r | stops the<br>resonant | e power t<br>circuit g | imum AC<br>transfer a<br>oes above<br>limit che | nd repo<br>e this lim | rts an err | or if the | AC voltag |    |    |    |    | ing |

Example: To limit the AC voltage amplitude to 200V, a value of 20000 is written to the AC\_VOLTAGE\_LIMIT register.

#### CoilTemperatureLimitRegister(TEMP\_COIL\_LIMIT\_H:TEMP\_COIL\_LIMIT\_L)

| Address                                                                                                                                                                                            | :     | 0x18  |          |          |        |    |         |           |      |         |          |          |        |    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----------|----------|--------|----|---------|-----------|------|---------|----------|----------|--------|----|----|

| Reset va                                                                                                                                                                                           | alue: | Fromt | he confi | guratior | n data |    |         |           |      |         |          |          |        |    |    |

| 15                                                                                                                                                                                                 | 14    | 13    | 12       | 11       | 10     | 9  | 8       | 7         | 6    | 5       | 4        | 3        | 2      | 1  | 0  |

|                                                                                                                                                                                                    |       |       |          |          |        | TE | EMP_COI | L_LIMIT[1 | 5:0] |         |          |          |        |    |    |

| rw                                                                                                                                                                                                 | rw    | rw    | rw       | rw       | rw     | rw | rw      | rw        | rw   | rw      | rw       | rw       | rw     | rw | rw |

| Bits 15:0 TEMP_COIL_LIMIT[15:0]: Maximum coil temperature allowed (degree<br>The transmitter stops the power transfer and reports an error if the co<br>external thermistor goes above this limit. |       |       |          |          |        |    |         | •         |      | ture me | asured b | y an opf | tional |    |    |

A value of 0x0000 disables the limit checking.

Example: To limit the coil temperature to 85 degrees C, a value of 85 is written to the TEMP\_ COIL\_LIMIT register.

#### Die Temperature Limit Register (TEMP\_DIE\_LIMIT\_H:TEMP\_DIE\_LIMIT\_L)

| Address                                  | 5: | 0x1A |    |    |    |    |         |          |     |    |    |    |    |    |    |

|------------------------------------------|----|------|----|----|----|----|---------|----------|-----|----|----|----|----|----|----|

| Reset value: From the configuration data |    |      |    |    |    |    |         |          |     |    |    |    |    |    |    |

| 15                                       | 14 | 13   | 12 | 11 | 10 | 9  | 8       | 7        | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

|                                          |    |      |    |    |    | T  | EMP_DIE | LIMIT[15 | :0] |    |    |    |    |    |    |

| rw                                       | rw | rw   | rw | rw | rw | rw | rw      | rw       | rw  | rw | rw | rw | rw | rw | rw |

Bits 15:0 TEMP\_DIE\_LIMIT[15:0]: Maximum die temperature allowed (0.01 degrees C) The transmitter stops the power transfer and reports an error if the TS80000 die temperature measured internally goes above this limit. The unit is 0.01 deg. C. A value of 0x0000 disables the limit checking.

Example: To limit the die temperature to 85 degrees C, a value of 8500 is written to the TEMP\_DIE\_LIMIT register.

#### Minimum Temperature for Fan Control Register (FAN\_TEMP\_MIN)

| Address:<br>Reset value:                     | 0x1C<br>From the configu | uration data |         |           |    |    |       |    |

|----------------------------------------------|--------------------------|--------------|---------|-----------|----|----|-------|----|

| 7                                            | 6                        | 5            | 4       | 3         | 2  | 1  | 0     |    |

|                                              |                          |              | Re      | es        |    |    |       | ]  |

| rw                                           | rw                       | rw           | rw      | rw        | rw | rw | rw    | ]  |

| Bits 7:0                                     | Reserved                 |              |         |           |    |    |       |    |

| TS80000<br>Final Datasheet<br>April 23, 2018 | Rev1.5                   |              | www.sen | ntech.com |    |    | 16 of | 37 |

| Maximum Te       | emperature for  | Fan Control Reg  | gister (FAN_T | EMP_MAX) |    |    |    |

|------------------|-----------------|------------------|---------------|----------|----|----|----|

| Address:         | 0x1D            |                  |               |          |    |    |    |

| Reset value:     | From the confi  | iguration data   |               |          |    |    |    |

|                  |                 |                  |               |          |    |    |    |

| 7                | 6               | 5                | 4<br>Re       | 3        | 2  | 1  | 0  |

| rw               | rw              | rw               | rw            | rw       | rw | rw | rw |

| Rite 7:0 Record  |                 |                  |               |          |    |    |    |

| Bits 7:0 Reserve | 20              |                  |               |          |    |    |    |

|                  |                 |                  |               |          |    |    |    |

|                  |                 |                  |               |          |    |    |    |

| Minimum Du       | ty Cycle for Fa | n Control Regis  | ter (FAN_DTC  | _MIN)    |    |    |    |

| Address:         | 0x1E            |                  |               |          |    |    |    |

| Reset value:     | From the confi  | iguration data   |               |          |    |    |    |

| -                |                 |                  |               | 0        | 0  |    |    |

| 7                | 6               | 5                | 4<br>Re       | 3        | 2  | 1  | 0  |

| rw               | rw              | rw               | rw            | rw       | rw | rw | rw |

|                  |                 |                  |               |          |    |    |    |

| Bits 7:0 Reserve | 2 <b>0</b>      |                  |               |          |    |    |    |

|                  |                 |                  |               |          |    |    |    |

|                  |                 |                  |               |          |    |    |    |

|                  | ut Cuele for Er |                  | ANT CAN DIC   |          |    |    |    |

|                  |                 | an Control Regis | Ter (FAN_DIC  | _MAX)    |    |    |    |

| Address:         | 0x1F            |                  |               |          |    |    |    |

| Reset value:     | From the confi  | iguration data   |               |          |    |    |    |

| 7                | 6               | 5                | 4             | 3        | 2  | 1  | 0  |

|                  |                 |                  | Re            | es       |    |    |    |

Bits 7:0 Reserved

rw

rw

rw

rw

rw

rw

rw

rw

| ddress:      | 0x20    |                                                  |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|--------------|---------|--------------------------------------------------|---------------------|-----------------|-------------------|-------------|-----------|--|--|--|--|--|--|--|--|

| Reset value: | Fromth  | e configuration data                             |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

| 7            | 6       | 5                                                | 4                   | 3               | 2                 | 1           | 0         |  |  |  |  |  |  |  |  |

|              | Re      | S                                                | A4WP                | PMA<br>rw       | WPCRES<br>rw      | WPCMP<br>rw | WPC<br>rw |  |  |  |  |  |  |  |  |

|              | D:1 7 5 |                                                  | 111                 |                 |                   | iw.         |           |  |  |  |  |  |  |  |  |

|              |         | Reserved                                         | ant Taskus alasu    |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              | Bit 4   | A4WP: A4WP Reson<br>Read:                        | iant rechnology     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         |                                                  | ot supported by hai | dware           |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 1: A4WP su                                       |                     | uware.          |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Write:                                           | apporteu.           |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 0: A4WP is not allowed.                          |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 1: A4WP is allowed if supported by the hardware. |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              | Bit 3   |                                                  |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Read:                                            |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 0: PMA not                                       | supported by hard   | lware.          |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 1: PMA sup                                       |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Write:                                           |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Write:<br>0: PMA is not allowed.                 |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | 1: PMA is allowed if supported by the hardware.  |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              | Bit 2   | NPCRES: WPC 1.2 Resonant Technology              |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Read:                                            |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         |                                                  | not supported by h  | nardware.       |                   |             |           |  |  |  |  |  |  |  |  |

|              |         |                                                  | supported.          |                 |                   |             |           |  |  |  |  |  |  |  |  |

|              |         | Write:                                           |                     |                 |                   |             |           |  |  |  |  |  |  |  |  |