### Features

Transient protection for high-speed data lines IEC61000 -4-2 (ESD) ±15kV (Air)

±15kV (Air) ±15kV (Contact) 5.0A (8/20µs)

IEC 61000-4-5 (Lightning)

- Cable Discharge Event (CDE)

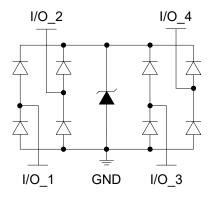

- Array of surge rated diodes with internal TVS diode

- Small package saves board space

- Protects four I/O lines

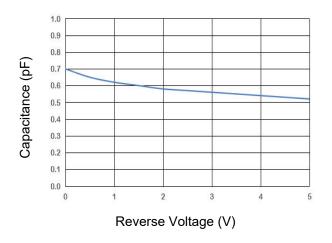

- Low capacitance: 0.70pF@0V(Typical)(I/O-GND) 0.35pF@0V(Typical)(I/O-I/O)

- Low leakage current: 0.1µA@VRWM (Typical)

- Low clamping voltage

- Each I/O pin can withstand over 1000 ESD strikes for ±8kV contact discharge

### Description

TT0314TPX is an ultra-low capacitance Transient Voltage Suppressor (TVS) designed to provide electrostatic discharge (ESD) protection for high-speed data interfaces. With typical capacitance of 0.7pF only, is designed to protect parasitic-sensitive systems against over-voltage and over-current transient events. It complies with IEC61000-4-2 (ESD), Level 4 (±15kV air, ±8kV contact discharge), IEC61000-4-5 (Lightning) (5A, 8/20us), very fast charged device model (CDM) ESD and cable discharge event (CDE),etc.

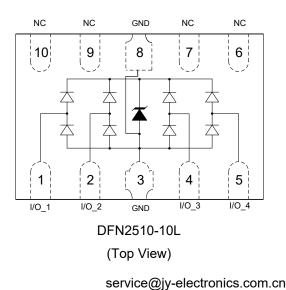

The TT0314TP comes in a RoHS compliant and Halogen Free 2.5mm x 1.0mm x 0.55mm DFN2510-10L package. This device incorporates eight surge rated, ultra-low capacitance steering diodes and a TVS in a single package. During transient conditions, the steering diodes direct the transient to either the positive side of the power supply line or to ground.

DFN2510-10L (Bottom View)

### **Applications**

- HDMI 1.4/2.0, USB 3.0, MDDI, SATA ports

- Monitors and flat panel displays

- Set-top box

- Video graphics cards

- Digital Video Interface (DVI)

- Notebook computers

### **Mechanical Characteristics**

- Package: DFN2510-10L

- Marking: Part number

- Packaging: Tape and Reel

- ROHS compliant

### **Circuit Diagram**

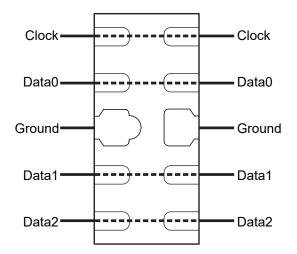

# **Pin Configuration**

1

## **Absolute Maximum Rating**

| Symbol           | Parameter                                                    | Value      | Units |

|------------------|--------------------------------------------------------------|------------|-------|

| I <sub>PP</sub>  | Peak Pulse Current (8/20µs)                                  | 5          | А     |

| P <sub>PK</sub>  | Peak Pulse Power (8/20µs)                                    | 20         | W     |

| V <sub>ESD</sub> | ESD per IEC61000-4-2 (Air)<br>ESD per IEC61000-4-2 (Contact) | ±15<br>±15 | kV    |

| T <sub>OPT</sub> | Operating Temperature                                        | -55/+125   | °C    |

| T <sub>STG</sub> | Storage Temperature                                          | -55/+150   | °C    |

## **Electrical Characteristics (T = 25°C)**

| Symbol           | Parameter                                  | Diagram                                                        |

|------------------|--------------------------------------------|----------------------------------------------------------------|

| V <sub>RWM</sub> | Nominal Reverse Working Voltage            | <b>↑</b> <sup>1</sup>                                          |

| I <sub>R</sub>   | Reverse Leakage Current @ V <sub>RWM</sub> | 1 <sub>PP</sub> Z                                              |

| $V_{BR}$         | Reverse Breakdown Voltage @ $I_T$          |                                                                |

| Ι <sub>Τ</sub>   | Test Current for Reverse Breakdown         |                                                                |

| Vc               | Clamping Voltage @ IPP                     |                                                                |

| I <sub>PP</sub>  | Maximum Peak Pulse Current                 | V <sub>F</sub> V <sub>C</sub> V <sub>RWM</sub> V <sub>BR</sub> |

| $C_{\text{ESD}}$ | Parasitic Capacitance                      |                                                                |

| I <sub>F</sub>   | Forward Current                            |                                                                |

| V <sub>F</sub>   | Forward Voltage @ I <sub>F</sub>           |                                                                |

| Symbol           | Test Condition                                                       | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------------------------------------------|---------|---------|---------|-------|

| V <sub>RWM</sub> |                                                                      |         |         | 3.3     | V     |

| I <sub>R</sub>   | V <sub>RWM</sub> = 3.3V, T = 25°C<br>Between I/O and GND             |         | 0.1     | 1.0     | μA    |

| V <sub>BR</sub>  | I <sub>T</sub> = 1mA<br>Between I/O and GND                          | 5.0     | 7.0     | 9.0     | V     |

| VC               | I <sub>PP</sub> = 5A, t <sub>p</sub> = 8/20µs<br>Between I/O and GND |         | 3.5     |         | V     |

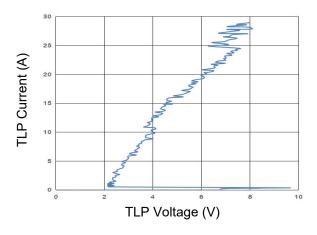

| Vc               | $I_{PP} = 8.0A, t_p = 100ns^{(1)}$                                   |         | 3.50    |         | V     |

| Ŭ                | I <sub>PP</sub> = 16.0A, t <sub>p</sub> =100ns <sup>(1)</sup>        |         | 5.20    |         | V     |

| R <sub>dyn</sub> | I <sub>PP</sub> = 12.0A, t <sub>p</sub> = 100ns <sup>(1)</sup>       |         | 0.22    |         | Ω     |

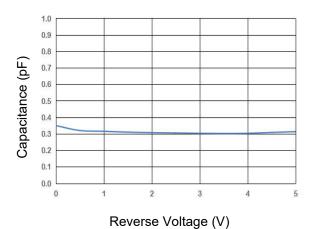

| C <sub>ESD</sub> | V <sub>R</sub> = 0V, f = 1MHz Between<br>I/O and GND                 |         | 0.70    |         | pF    |

| C <sub>ESD</sub> | V <sub>R</sub> = 0V, f = 1MHz<br>Between I/O and I/O                 |         | 0.35    |         | pF    |

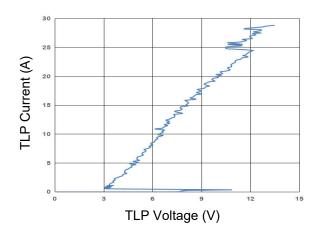

Notes:(1)Measurements performed using a 100ns Transmission Line Pulse(TLP) system, Between I/O and GND.

service@jy-electronics.com.cn

## **Typical Performance Characteristics**

### TLP Measurement of I/O to GND

#### Capacitance vs Reverse Voltage IO to GND

### TLP Measurement of I/O to I/O

#### Capacitance vs Reverse Voltage IO to IO

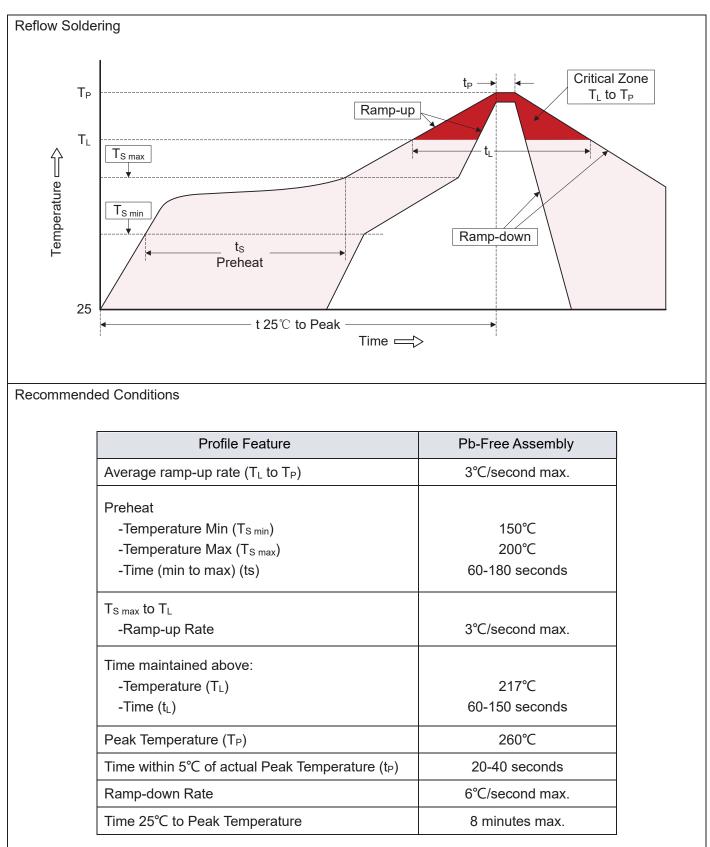

### **Recommended Soldering Conditions**

### **High Speed PCB Layout Guidelines**

Printed circuit board layout is the key to achieving the highest level of surge immunity on power and data lines. The location of the protection devices on the PCB is the simplest and most important design rule to follow. The TT0314TPX devices should be located as close as possible to the noise source. The TT0314TPX devices should be placed on all data and power lines that enter or exit the PCB at the I/O connector. In most system, surge pulses occur on data and power lines that enter the PCB through the I/O connector. Placing the TT0 314TPX devices as close as possible to the noise source ensures that a surge voltage will be clamped before the puls e can be coupled into adjacent PCB traces. In addition, the PCB should use the shortest possible traces. A sh ort tracelength equates to low impedance, which ensures that the surge energy will be dissipated

by the TT0314TPX device. Long signal traces will act as antennas to receive energy from fields that are p roduced bythe ESD pulse. By keeping line lengths as short as possible, the efficiency of the line to act as an ante nna for ESD related fields is reduced. Minimize interconnecting line lengths by placing devices with the most interconn ect as close together as possible. The protection circuits should shunt the surge voltage to either the referenc e or chassis ground. Shunting the surge voltage directly to the IC's signal ground can cause ground bounce. T he clamping performance of TVS diodes on a single ground PCB can be improved by minimizing the impedance with relatively short and wide ground traces. The PCB layout and IC package parasitic inductances can cause signifi cant overshoot to the TVS's clamping voltage. The inductance of the PCB can be reduced by using short trace lengt hs and multiple layers with separate ground and power planes. One effective method to minimize loop problems is t o incorporate a ground plane in the PCB design.

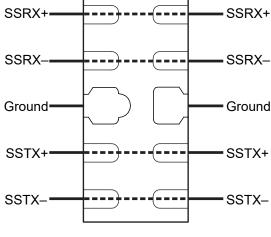

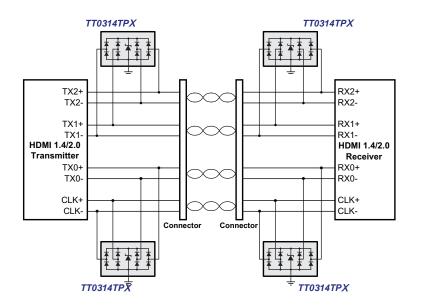

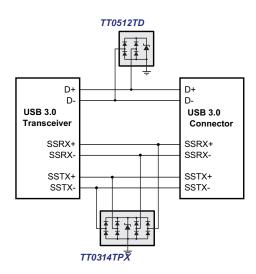

The TT0314TPX ultra-low capacitance TVS is designed to protect four high speed data transmission lines from transient over-voltages by clamping them to a fixed reference. The low inductance and construction minimizes voltage overshoot during high current surges. When the voltage on the protected line exceeds the reference voltage the internal steering diodes are forward biased, conducting the transient current away from the sensitive circuitry. The TT0314TPX is designed for ease of PCB layout by allowing the traces to run underneath the device. The pinout of the TT0314TPX is designed to simply drop onto the IO lines of a High Definition Multimedia Interface (HDMI 1.4/2.0) or USB 3.0 design without having to divert the signal lines that may add more parasitic inductance. Pins 1, 2, 4 and 5 are connected to the internal TVS devices and pins 6, 7, 9 and 10 are no connects. The no connects was done so the package can be securely soldered onto the PCB surface.

Flow Through Layout for HDMI 1.4/2.0

Flow Through Layout for USB 3.0

### **Application Information**

www.jy-electronics.com.cn

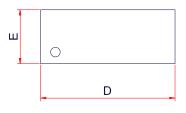

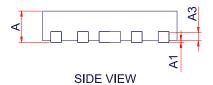

### Package Outline

• DFN2510-10L package

| Symbol | Dimensions in Millimeters |         |      |  |  |  |  |

|--------|---------------------------|---------|------|--|--|--|--|

|        | Min.                      | Тур.    | Max. |  |  |  |  |

| A      | 0.45                      | 0.52    | 0.60 |  |  |  |  |

| A1     | 0.00                      | 0.02    | 0.05 |  |  |  |  |

| A3     |                           | 0.15Ref |      |  |  |  |  |

| D      | 2.40                      | 2.50    | 2.60 |  |  |  |  |

| E      | 0.90                      | 1.00    | 1.10 |  |  |  |  |

| E1     | 0.50Ref                   |         |      |  |  |  |  |

| b      | 0.15                      | 0.20    | 0.25 |  |  |  |  |

| b1     | 0.13                      | 0.18    | 0.23 |  |  |  |  |

| b2     | 0.35                      | 0.40    | 0.45 |  |  |  |  |

| е      | 0.50BSC                   |         |      |  |  |  |  |

| L      | 0.28                      | 0.39    | 0.50 |  |  |  |  |

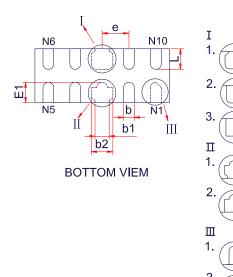

### **Tape and Reel Specification**

| Symbol            | W                  | A0        | B0       | K0       | Е        | F        | Ρ       | P0      | P2       | т         |

|-------------------|--------------------|-----------|----------|----------|----------|----------|---------|---------|----------|-----------|

| Dimension<br>(mm) | s 8.00+0.3<br>-0.1 | 1.23±0.05 | 2.7±0.05 | 0.7±0.05 | 1.75±0.1 | 3.5±0.05 | 4.0±0.1 | 4.0±0.1 | 2.0±0.05 | 0.25±0.02 |

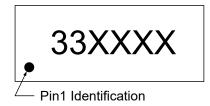

## **Marking Codes**

#### Note:

- (1) "33" is part number, fixed.

- (2) "XXXX" is the identification number.

### **Ordering Information**

| Part Number | Working<br>Voltage | Quantity<br>Per Reel | Reel Size |  |

|-------------|--------------------|----------------------|-----------|--|

| TT0314TP    | 3.3V               | 3,000                | 7 Inch    |  |

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for ESD Suppressors / TVS Diodes category:

Click to view products by Shenzhen JingYang manufacturer:

Other Similar products are found below :

60KS200C D18V0L1B2LP-7B D5V0F4U5P5-7 NTE4902 P4KE27CA P6KE11CA P6KE8.2A SA60CA SA64CA SMBJ12CATR SMBJ33CATR SMBJ6.5A SMBJ8.0A ESD101-B1-02ELS E6327 ESD112-B1-02EL E6327 ESD7451N2T5G 19180-510 CPDT-5V0USP-HF 3.0SMCJ33CA-F 3.0SMCJ36A-F HSPC16701B02TP JANTX1N6126A D3V3Q1B2DLP3-7 D55V0M1B2WS-7 SCM1293A-04SO ESD200-B1-CSP0201 E6327 SM12-7 CEN955 W/DATA VESD12A1A-HD1-GS08 CPDQC5V0-HF D1213A-01LP4-7B ESD101-B1-02EL E6327 AOZ8808DI-03 5KP15A 5KP48A 5KP90A ESD3V3D7-TP 15KPA36A-LF P4KE56CA P4KE68A P4KE91CATR P6KE120A P6KE13CA P6KE43CA P6KE6.8CA P6KE8.2 P6SMBJ20CA JANTX1N6072A SR2835ESKG SA90CA