# **GreenFET<sup>TM</sup> High Voltage Gate Driver**

#### **Features**

- 5V ±5% Power supply

- SLG55021 Drain Voltage Range 1.0V to 20V

- Internal Gate Voltage Charge Pump

- · Controlled Turn on Delay

- · Controlled Load Discharge Rate

- Controlled Turn on Slew Rate

- Stable Slew Rate (±2% typ) over Temperature Range

- TDFN-8 Package

**Applications**

- · Power Rail Switches

- Hot Plugging Applications

- Soft Switching

- Personal computers and Servers

- Data Communications Equipment

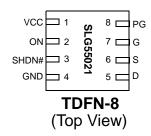

### **Pin Configuration**

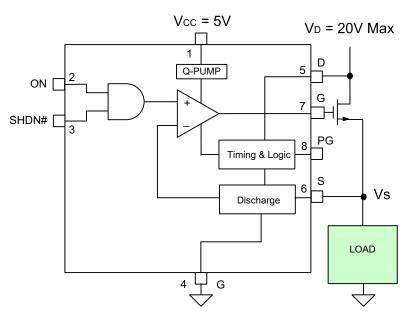

### **Block Diagram**

SLG55021 For N-MOSFETS with  $V_{GS} < 20V$

### **Pin Description**

| Pin Name | Pin Number | Туре   | Pin Description                                                      |  |  |  |

|----------|------------|--------|----------------------------------------------------------------------|--|--|--|

| VCC      | 1          | Power  | Supply Voltage                                                       |  |  |  |

| ON       | 2          | Input  | CMOS Logic Level. High True                                          |  |  |  |

| SHDN#    | 3          | Input  | Shut Down# - Low True Signal which immediately turns FET off         |  |  |  |

| GND      | 4          | GND    | Ground                                                               |  |  |  |

| D        | 5          | Input  | FET Drain Connection                                                 |  |  |  |

| S        | 6          | Input  | Source Connection                                                    |  |  |  |

| G        | 7          | Output | FET Gate Drive                                                       |  |  |  |

| PG       | 8          | Output | Output CMOS Open Drain - Power Good, indicates external FET fully on |  |  |  |

#### Overview

The SLG55021 N-Channel FET Gate Driver is used for controlling a delayed turn on and ramping slew rate of the source voltage on N-Channel FET switches from a CMOS logic level input. Intended as a supporting control element for switched voltage rails in energy efficient, advanced power management systems, the SLG55021 also integrates circuits to discharge opened switched voltage rails. The gate driver is available in a variety of configurations supporting a range of turn-on slew rates from 0.80V/ms up to 4V/ms which, depending on load supplying source voltages in the range of 1.0V to 20V results in ramp times from  $200\mu s$  up to over 20ms (see Application Section). Delays until the ramp begins are source voltage independent and range from  $250\mu s$  to 5ms. A power good condition is output to indicate that the ramp-up slew of the source voltage is finished. Additionally, an internal discharge circuit provides a controlled path to remove charge from open power rails. The SLG55021 gate drive is packaged in an 8 pin DFN package.

When used with external N-Channel FETs, the SLG55021 supports low transient, energy efficient switching of high current loads at source voltages ranging from 1.0V to 20V.

#### **Ordering Information**

| Part Number        | Ramp Slew<br>Rate<br>(Volts/ms) | Delay Time<br>(ms) | Discharge<br>Resistor<br>(ohms) | Package Type                      |

|--------------------|---------------------------------|--------------------|---------------------------------|-----------------------------------|

| SLG55021-200010V   | 2.0                             | 0.15               | 200                             | TDFN-8                            |

| SLG55021-200010VTR | 2.0                             | 0.15               | 200                             | TDFN-8 - Tape and Reel (3k units) |

000-0055021-102 Page 2 of 8

### **Absolute Maximum Conditions**

| Parameter                               | Min. | Max. | Unit |

|-----------------------------------------|------|------|------|

| V <sub>D</sub> or V <sub>S</sub> to GND | -0.3 | 40.0 | V    |

| Voltage at Logic Input pins             | -0.3 | 6.5  | V    |

| Current at input pin                    | -1.0 | 1.0  | mA   |

| Storage temperature range               | -65  | 150  | °C   |

| Operating temperature range             | -55  | 125  | °C   |

| Junction temperature                    |      | 150  | °C   |

| ESD Human Body Model                    |      | 2000 | V    |

| ESD Machine Model                       |      | 200  | V    |

### Electrical Characteristics (-10°C to 75°C)

| Symbol                | Parameter                   | Condition/Note                                       | Min.  | Тур. | Max.  | Unit |

|-----------------------|-----------------------------|------------------------------------------------------|-------|------|-------|------|

| V <sub>CC</sub>       | Supply Voltage              |                                                      | 4.75  | 5.0  | 5.25  | V    |

| 1                     | Quiescent Current           | V <sub>G</sub> not ramping<br>FET = ON               |       | <7   | 10    | μА   |

| I <sub>q</sub>        | Quiescent Current           | V <sub>G</sub> not ramping<br>FET = OFF              |       | 0.1  | 1     | μА   |

| V <sub>D</sub>        | FET Drain Voltage           | SLG55021                                             | 1.0   |      | 20    | V    |

| V <sub>GS</sub>       | Gate-Source Voltage         | SLG55021                                             | 8.0   | 11.5 | 13    | V    |

| C <sub>G</sub>        | FET Gate Capacitance        |                                                      | 500   |      | 8000  | pF   |

| T <sub>DELAY</sub>    | Ramp Delay Range            | 1.5ms Default, 500µs step                            | 0.105 | 0.15 | 0.195 | ms   |

| T <sub>SLEW</sub>     | FET Turn on Slew Rate       |                                                      | 1.4   | 2.0  | 2.6   | V/ms |

| IDISCHARGE            | Internal Discharge Resistor | Nominal discharge<br>time of ~100ms<br>10mA max rate | 100   | 200  | 300   | Ω    |

| V <sub>IH</sub>       | HIGH-level input voltage    | ON, SHDN#<br>(200mV Hysteresis)                      | 2.4   |      | 5.5   | V    |

| V <sub>IL</sub>       | LOW-level Input voltage     | ON, SHDN#<br>(200mV Hysteresis)                      |       |      | 0.4   | V    |

| V <sub>OH</sub>       | HIGH-level output voltage   | PG Open Drain                                        |       |      | 5.5   | V    |

| I <sub>OL_LOGIC</sub> | Logic LOW level output      | PG Sink Current                                      | 1     | 2    | 3     | mA   |

| l <sub>IH</sub> *     | SHDN#                       | V <sub>IH</sub> = 3.3V                               |       |      | <1.0  | μΑ   |

| I <sub>G_OL</sub>     | Gate Drive Sink Current     |                                                      | 400   |      |       | μΑ   |

| I <sub>G_OH</sub>     | Gate Drive Source Current   |                                                      | 32    |      |       | μΑ   |

| I <sub>D_IH</sub>     | Drain Pin Current           | V <sub>D</sub> = 20V in Standby                      |       |      | <1.0  | μΑ   |

| I <sub>S_IH</sub>     | Source Pin Current Quiesent | V <sub>S</sub> = 20V                                 |       |      | <1.0  | μА   |

$<sup>^{\</sup>star}$  If using an open drain to drive SHDN#; pull up with 10k $\!\Omega$  to  $V_{CC}$

000-0055021-102 Page 3 of 8

### **Application Example**

In a typical application, de-asserting ON (low) or asserting the low true Shut Down signal (SHDN#) turns off the external power N-FET. SHDN# is provided as an asynchronous override to the ON signal. When the FET is turned off, the voltage at the load is discharged through a resistor (typically 200 ohms) internal to the SLG55021 with the discharge current limited to a maximum of 10mA. When ON is asserted (high), gate voltage is not applied to the gate of the external power N-FET until after  $T_{DELAY}$  then the gate source (Vgs) voltage is ramped up to 11.5V above the source voltage  $V_S$  at a slew rate determined by the internal slew rate control element internal to the SLG55021. Monotonic rise of Vs is maintained even as ID increases dramatically after the load device turn on threshold voltage is reached. After the source voltage has ramped up to its maximum steady state value, the Open Drain PG (Power Good) signal is asserted. PG may be used as the ON control of a second SLG55021 thereby providing power on sequence control of a number of switched power rails, or used in a 'wired and' with other PG signals to indicate all switched power rails are in a power good condition.

The devices will not operate if Vcc is below 3.5V.

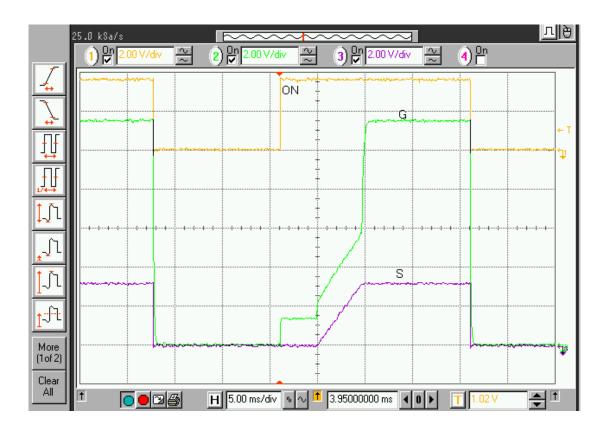

The waveforms shown illustrate the monotonic rise of the source voltage of a FET as gate voltage is controlled to accommodate for variations in load current as the voltage is applied.

000-0055021-102 Page 4 of 8

### **Package Top Marking System Definition**

|          | 8 7 6 5 |               |

|----------|---------|---------------|

| Part ID  | XXA     | Assembly Code |

| Datecode | DD L    | Lot           |

|          | R       | Revision      |

|          | 1 2 3 4 |               |

XX - Part ID Field: identifies the specific device configuration

A – Assembly Code Field: Assembly Location of the device.

DD – Date Code Field: Coded date of manufacture

L – Lot Code: Designates Lot #

R – Revision Code: Device Revision

000-0055021-102 Page 5 of 8

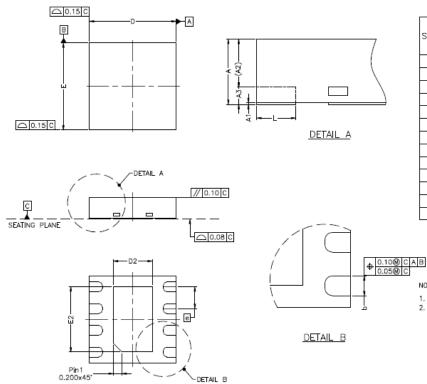

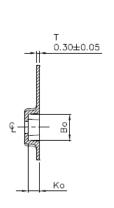

### **Package Drawing and Dimensions**

#### 8 Lead TDFN Package

|        | [        | DIMENSION | ٧    | DIMENSION |        |      |  |

|--------|----------|-----------|------|-----------|--------|------|--|

| SYMBOL |          | (MM)      |      | (MIL)     |        |      |  |

|        | MIN.     | NOM.      | MAX. | MIN.      | NOM.   | MAX. |  |

| Α      | 0.70     | 0.75      | 0.80 | 28        | 30     | 31   |  |

| A1     | 0.00     | 0.02      | 0.05 | 0         | 1      | 2    |  |

| A2     | 0        | 0.55      | 0.80 | 0         | 22     | 31   |  |

| A3     | _        | 0.20      | -    | _         | 8      | _    |  |

| b      | 0.18     | 0.25      | 0.30 | 7         | 10     | 12   |  |

| D      | 1.90     | 2.00      | 2.10 | 74        | 79     | 83   |  |

| D1     |          | _         |      | _         |        |      |  |

| D2     | 0.75     | 0.90      | 1.05 | 30        | 35     | 41   |  |

| Ε      | 1.90     | 2.00      | 2.10 | 75        | 79     | 83   |  |

| E1     |          | -         |      |           | _      |      |  |

| E2     | 1.35     | 1.50      | 1.65 | 53        | 59     | 65   |  |

| е      | 0.50 BSC |           |      |           | 20 BSC |      |  |

| L      | 0.25     | 0.30      | 0.35 | 10        | 12     | 14   |  |

- 1. REFER TO JEDEC STD: MO-229.

2. DIMENSION "6" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

Note: Bottom side metal plate is at ground potential

000-0055021-102 Page 6 of 8

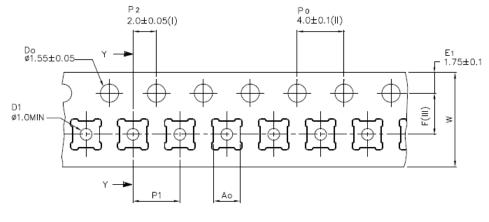

### **Tape and Reel Specifications**

|              | 9 # of |                 | Unitsper | Trailer A |                | Leader B |                | Pocket Tape(mm) |       | Reel             |

|--------------|--------|-----------------|----------|-----------|----------------|----------|----------------|-----------------|-------|------------------|

| Package Type | Pins   | Package<br>Size | Reel     | Pockets   | Length<br>(mm) | Pockets  | Length(<br>mm) | Width           | Pitch | Diameter<br>(mm) |

| 8TDFN        | 8      | 2x2mm           | 3,000    | 42        | 168            | 42       | 168            | 8               | 4     | 178              |

### **Tape and Reel Drawing**

SECTION Y-Y

| Ao | 2.25 +/-0.1 |

|----|-------------|

| Во | 2.25 +/-0.1 |

| Ko | 1.00 +/-0.1 |

| F  | 3.50 +/-0.1 |

| P1 | 4.00 +/-0.1 |

| W  | 8.00 +/-0.3 |

- Measured from centreline of sprocket hole

- to centreline of pocket. Cumulative tolerance of 10 sprocket holes is  $\pm$  0.20 . (II)

- Measured from centreline of sprocket hole to centreline of pocket.

- (IV) Other material available.

- ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED.

000-0055021-102 Page 7 of 8

### **Revision History**

| Date      | Version | Change                            |

|-----------|---------|-----------------------------------|

| 9/26/2016 | 1 (1)2  | Removed TBD values<br>Fixed typos |

000-0055021-102 Page 8 of 8

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by Silego manufacturer:

Other Similar products are found below:

00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP 5951900000 011003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3-UA-DC24

00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP 00-8275RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000 60100564

01312 0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P

6131-220-21149P 6131-260-2358P 6131-265-11149P