## CurrentPAK<sup>TM</sup> Ultra-small 3.8 mΩ, 10 A Power Switch with Current Sense

#### **General Description**

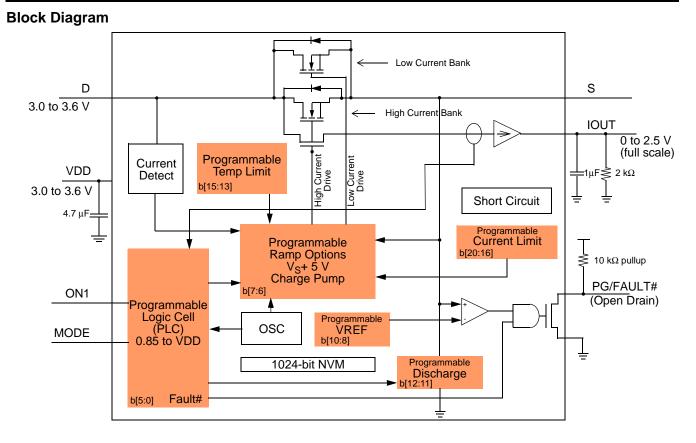

The SLG6M6201V is a 3.8 m $\Omega$  10 A single-channel load switch that is able to switch 3.0 V to 3.6 V power rails. The product is packaged in an ultra-small 2 x 3 mm package.

#### Features

- 2 x 3 mm STQFN 18L FC package (6 fused pins for drain and 6 fused pins for source)

- Logic level ON pins capable of supporting 1.05 V CMOS Logic

- $3.8 \text{ m}\Omega \text{ RDS}_{ON}$  while supporting 10 A

- Discharges load when off

- Two Over Current Protection Modes (Short Circuit/Active)

- Short Circuit Current Limit

- Active Current Limit

- Over Temperature Protection

- High / Low Current Select

- Automatic Switch from Low to High Current

- Current Sense Output:

- Wide IDS current sensing range: 50 mA to 10 A

- High Current Mode Accuracy

- ±3% from 3A to 10A

- ±6% from 1A to 2.9A

- Low Current Mode Accuracy

- ±10% from 0.1A to 1A

- Pb-Free / Halogen-Free / RoHS 6/6 compliant

- Operating Temperature: -10 °C to 70°C

- Operating Voltage

- V<sub>DD</sub>: 3.0 V to 3.6 V

- V<sub>D</sub>: 3.0 V to 3.6 V

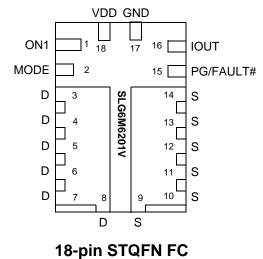

### **Pin Configuration**

(Top View)

### Applications

- Notebook Power Rail Switching

- Tablet Power Rail Switching

- Server Power Rail Switching

- Telecommunications Equipment Power Rail Switching

## **Pin Description**

| Pin # | Pin Name  | Туре                       | Pin Description                                                                                                                                                                                                         |

|-------|-----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ON1       | Input                      | Programmable Logic (4 M $\Omega$ pull down resistor) CMOS input with V <sub>IL</sub> < 0.3 V, V <sub>IH</sub> > 0.85 V                                                                                                  |

| 2     | MODE      | Input                      | ON2 or Current Mode Selection Pin<br>Current Mode<br>L = High Current Mode, 10 A max (Power Up Default)<br>H = Low Current Mode, 750 mA max                                                                             |

| 3     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 4     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 5     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 6     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 7     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 8     | D         | MOSFET                     | Drain of Power MOSFET (fused pin 3 through pin 8)                                                                                                                                                                       |

| 9     | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

| 10    | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

| 11    | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

| 12    | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

| 13    | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

| 14    | S         | MOSFET                     | Source of Power MOSFET (fused pin 9 through pin 14)                                                                                                                                                                     |

|       |           |                            | Pin 15 is a multipurpose status output pin. 10 k $\Omega$ pull up resistor recommended.                                                                                                                                 |

| 15    | PG/FAULT# | Output, Open<br>Drain Only | - When Pin 15 asserts high, it acts as a power good output signal. The device's VS voltage has reached 90% voltage level and the internal N-FET has fully turned on which allows max IDS current at lowest RDSON value. |

|       |           |                            | - When Pin 15 asserts low, it acts as a fault# notification signal. The fault condition is dependent on Pin 2's input level.                                                                                            |

| 16    | IOUT      | Output                     | Current Output. 2 k $\Omega$ external resistor and 1 nF external capacitor recommended.                                                                                                                                 |

| 17    | GND       | GND                        | Ground                                                                                                                                                                                                                  |

| 18    | VDD       | PWR                        | VDD power for load switch control (3.0 V to 3.6 V)                                                                                                                                                                      |

## **PG/FAULT# Status Table**

| Pin 2<br>(MODE)       | Pin 15<br>(Fault#) | Device Status                                                                |

|-----------------------|--------------------|------------------------------------------------------------------------------|

| L (High Current Mode) | Low                | VS dropped below 90% of power rail voltage.                                  |

| H (Low Current Mode)  | Low                | Device failed to enter low current mode. See State diagram for more details. |

#### **Absolute Maximum Ratings**

| Description                       | Conditions                                                                                                         | Min.                                                                                                                                                                                                                         | Тур.                                                                                                                                                                                                                             | Max.                                                                                                                                                                                              | Unit                                                                                                                                                                                                            |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supply                      |                                                                                                                    |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  | 7                                                                                                                                                                                                 | V                                                                                                                                                                                                               |

| Storage Temperature               |                                                                                                                    | -65                                                                                                                                                                                                                          |                                                                                                                                                                                                                                  | 150                                                                                                                                                                                               | °C                                                                                                                                                                                                              |

| ESD Protection                    | Human Body Model                                                                                                   | 2000                                                                                                                                                                                                                         |                                                                                                                                                                                                                                  |                                                                                                                                                                                                   | V                                                                                                                                                                                                               |

| Package Power Dissipation         |                                                                                                                    |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  | 2.5                                                                                                                                                                                               | W                                                                                                                                                                                                               |

| Current from Drain to Source      | Continuous                                                                                                         |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  | 12                                                                                                                                                                                                | А                                                                                                                                                                                                               |

| Peak Current from Drain to Source | For no more than 1 ms with 1% duty cycle                                                                           |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  | 16                                                                                                                                                                                                | А                                                                                                                                                                                                               |

|                                   | Power Supply<br>Storage Temperature<br>ESD Protection<br>Package Power Dissipation<br>Current from Drain to Source | Power Supply  Estimate    Storage Temperature  ESD Protection    Human Body Model  Package Power Dissipation    Current from Drain to Source  Continuous    Peak Current from Drain to Source  For no more than 1 ms with 1% | Power Supply     Storage Temperature 65    ESD Protection  Human Body Model  2000    Package Power Dissipation     Current from Drain to Source  Continuous     Peak Current from Drain to Source  For no more than 1 ms with 1% | Power SupplyStorage Temperature-65ESD ProtectionHuman Body Model2000Package Power DissipationCurrent from Drain to SourceContinuousPeak Current from Drain to SourceFor no more than 1 ms with 1% | Power Supply7Storage Temperature-65150ESD ProtectionHuman Body Model2000Package Power Dissipation2.52.5Current from Drain to SourceContinuous12Peak Current from Drain to SourceFor no more than 1 ms with 1%16 |

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Operating Temperature**

| Parameter      | Description           | Min. | Max. | Unit |

|----------------|-----------------------|------|------|------|

| Т <sub>О</sub> | Operating Temperature | -10  | 70   | °C   |

#### **Electrical Characteristics**

Conditions: -10 °C to 70 °C (unless otherwise noted)

| Parameter       | Description             | Conditions                 | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------|----------------------------|------|------|------|------|

| V <sub>DD</sub> | Power Supply Voltage    | -10 °C to 70 °C            | 3.0  |      | 3.6  | V    |

| I <sub>DD</sub> | Power Supply Current    | when OFF @ 25°C<br>Leakage |      | 1    | 4    | μA   |

|                 |                         | when ON, no load, @ 25°C   |      | 340  | 400  | μA   |

| IDS             | Drain to Source Current | High Current Mode          |      |      | 10   | А    |

| 103             |                         | Low Current Mode           |      |      | 750  | mA   |

#### **MOSFET Characteristics**

Conditions:  $V_{DD}$  = 3.3 V, -10 °C to 70 °C (unless otherwise noted)

| Parameter         | Description                       | Conditions                   | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------|------------------------------|------|------|------|------|

|                   | ON Resistance (High Current Mode) | T <sub>A</sub> 25°C @ 100 mA | 3.5  | 3.6  | 4.0  | mΩ   |

|                   | RDSau                             | T <sub>A</sub> 85°C @ 100 mA | 4.2  | 4.4  | 4.7  | mΩ   |

| KD3 <sub>ON</sub> |                                   | T <sub>A</sub> 25°C @ 100 mA | 24.7 | 25.1 | 27.0 | mΩ   |

|                   |                                   | T <sub>A</sub> 85°C @ 100 mA | 29   | 30   | 32   | mΩ   |

| V <sub>S</sub>    | Source Voltage                    |                              |      | 0    | VD   | V    |

| V <sub>D</sub>    | Drain Voltage                     |                              | 3.0  |      | 3.6  | V    |

### **ON/OFF Characteristics**

Conditions: -10 °C to 70 °C (unless otherwise noted)

| Parameter                  | Description                                                                       | Conditions                                                                              | Min. | Тур. | Max.            | Unit |

|----------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|-----------------|------|

| T <sub>INIT_DELAY</sub>    | Power up initiation delay*                                                        | See Timing Diagram                                                                      |      |      | 1               | ms   |

| T <sub>ON_DELAY</sub>      | ON Logic Delay*                                                                   | See Timing Diagram                                                                      |      |      | 500             | μs   |

| T <sub>PROG_DELAY</sub>    | Programmable Delay                                                                |                                                                                         |      | 0.   |                 | ms   |

| T <sub>SLEW</sub>          | Programmable Slew Rate                                                            | 10% to 90% V <sub>S</sub> , C <sub>L</sub> = 10 $\mu$ F, R <sub>L</sub> = 20 $\Omega$   |      | 1.6  |                 | V/ms |

| T <sub>TOTAL_ON</sub>      | Total on Delay                                                                    | 50% ON1 to V <sub>S</sub> 90%, C <sub>L</sub> = 10 μF, R <sub>L</sub> = 20 Ω            | 1.4  |      | 3               | ms   |

| T <sub>OFF_DELAY</sub>     | Off Delay                                                                         | 50% ON1 to V <sub>S</sub> Fall, No C <sub>L</sub> , R <sub>L</sub> = 20 $\Omega$        | 11   | 16   | 25              | μs   |

| T <sub>PG_DELAY</sub>      | PG/FAULT# Driver Assertion Delay*                                                 | Logic trigger to PG/FAULT# assert-<br>ed                                                |      |      | 100             | μs   |

| T <sub>SWITCH_DLY_LH</sub> | Low Current mode to High Current<br>Mode switch delay                             | 50% Pin 2 to High Current Mode                                                          |      |      | 5               | ms   |

| T <sub>SWITCH_DLY_HL</sub> | High Current mode to Low Current<br>Mode switch delay                             | 50% Pin 2 to Low Current Mode                                                           |      |      | 500             | μs   |

| V <sub>IH</sub>            | High Input Voltage                                                                | Pin 1 & Pin 2                                                                           | 0.85 |      | V <sub>DD</sub> | V    |

| V <sub>IL</sub>            | Low Input Voltage                                                                 | Pin 1 & Pin 2                                                                           | -0.3 |      | 0.3             | V    |

| V <sub>OL_PG</sub>         | PG/FAULT# Low Output Voltage                                                      | $I_{OL} = 1 \text{ mA}$ , Pull Up Resistor = 10 k $\Omega$ ,<br>Pin 15                  |      |      | 0.5             | V    |

| $V_{REF_{PG_{RISE}}}$      | Power Good Rising VREF compara-<br>tor voltage                                    | V <sub>D</sub> = 3.3 V                                                                  |      | 2.97 |                 | V    |

| V <sub>REF_PG_FALL</sub>   | Power Good Falling VREF compar-<br>ator voltage                                   | V <sub>D</sub> = 3.3 V                                                                  |      | 2.80 |                 | V    |

|                            | Active Current Limit (High Mode)                                                  | I <sub>LIMIT</sub> . V <sub>S</sub> > 500 mV, Pin 2 = Assert<br>Low (High Current Mode) | 11.5 | 12.5 | 14.0            | Α    |

| I <sub>LIMIT</sub>         | Active Current Limit (Low Mode)                                                   | I <sub>LIMIT</sub> . V <sub>S</sub> > 500 mV, Pin 2 = Assert<br>High (Low Current Mode) |      | 1.25 |                 | A    |

|                            | Short Circuit Current Limit                                                       | V <sub>S</sub> < 500 mV                                                                 |      | 2.0  |                 | A    |

| I <sub>LIMIT</sub> _ACC    | Current Limit Accuracy*                                                           | Current Limit Accuracy                                                                  |      |      | ±20             | %    |

| THERM <sub>OFF</sub>       | Thermal Protection Shutoff*                                                       | automatic shutoff temperature                                                           |      | 125  |                 | °C   |

| THERM <sub>OFF_ACC</sub>   | Thermal Sensor Accuracy*                                                          |                                                                                         |      |      | ±10             | %    |

| THERMON                    | Thermal Protection turn on*                                                       | automatic Turn on temperature                                                           | 85   |      |                 | °C   |

| THERM <sub>TIME</sub>      | Thermal shutoff reaction time*                                                    |                                                                                         |      |      | 1.0             | ms   |

| I <sub>AS_TRIGGER</sub>    | IDS Current Automatic Low Current to High Current Trigger Level                   |                                                                                         | 0.8  | 1.0  | 1.2             | Α    |

| I <sub>BLK_HL_TRANS</sub>  | IDS Current level to block illegal<br>High current to Low Current transi-<br>tion |                                                                                         |      |      | 750             | mA   |

| R <sub>DIS</sub>           | Equivalent discharge resistance                                                   | V <sub>S</sub> discharge resistor                                                       | 280  | 300  | 350             | Ω    |

| CapSource                  | Source Cap                                                                        | Source to GND                                                                           | 10   | 100  |                 | μf   |

\* Not 100% tested

#### **Current Output Characteristics**

Conditions: -10 °C to 70 °C (unless otherwise noted)

| Parameter  | Description                                                             | Conditions                           | Min. | Тур. | Max. | Unit |

|------------|-------------------------------------------------------------------------|--------------------------------------|------|------|------|------|

|            |                                                                         | IDS = 10 A, Pin 2 (Mode) = L         |      | 1000 |      | μA   |

|            | IOUT (Pin 16) Output Current, FET<br>Array High Current Mode 10 A Max   | IDS = 1 A, Pin 2 (Mode) = L          |      | 100  |      | μA   |

| 1          |                                                                         | IDS = 0.5 A, Pin 2 (Mode) = L        |      | 50   |      | μA   |

| ISENSE     |                                                                         | IDS = 0.75 A, Pin 2 (Mode) = H       |      | 600  |      | μA   |

|            | IOUT (Pin 16) Output Current, FET<br>Array Low Mode 750 mA Max          | IDS = 0.1 A, Pin 2 (Mode) = H        |      | 80   |      | μA   |

|            | .,                                                                      | IDS = 0.05 A, Pin 2 (Mode) = H       |      | 40   |      | μA   |

|            |                                                                         | IDS = 3 A to 10 A, Pin 2 (Mode) = L  |      | ±3   |      | %    |

| L          | racy, FET Array High Current Mode<br>10 A Max                           | IDS = 1 A to 2.9 A, Pin 2 (Mode) = L |      | ±6   |      | %    |

| ISENSE_ACC | IOUT (Pin 16) Output Current Accuracy, FET Array Low Mode 750 mA<br>Max |                                      |      | ±10  |      | %    |

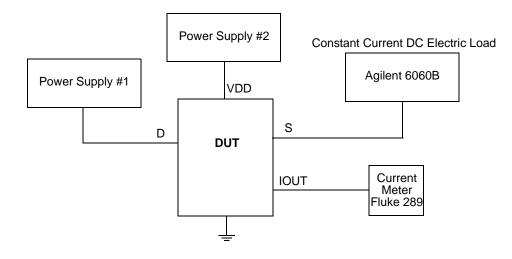

## **IOUT Accuracy Test Setup**

#### SLG6M6201V Turn ON

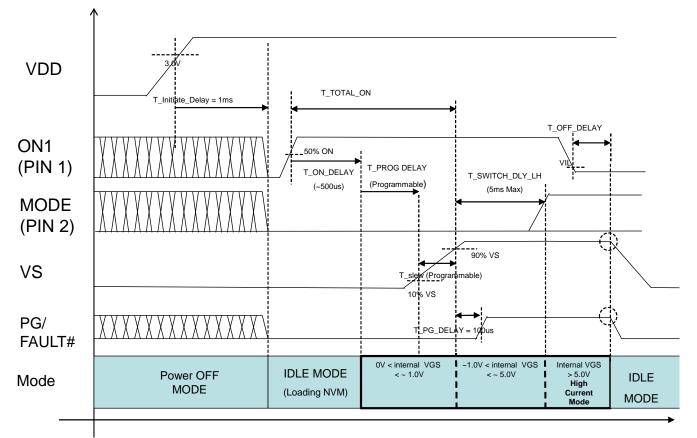

The normal power on sequence is first VDD, with VD only being applied after VDD is > 1 V, and then ON after VD is at least 90% of final value. The normal power off sequence is the power on sequence in reverse.

If VDD and VD are turned on at the same time, then it is possible that a voltage glitch will appear on VS before VDD achieves 1V, which is the VT of the main MOSFET. The size of the glitch is dependent on source and drain capacitance loading and the ramp rate of VDD & VD.

#### SLG6M6201V Turn ON

The VS ramp follows a linear path, not an RC limitation provided the ramp is slow enough to not be current limited by load capacitance.

#### SLG6M6201V Current Limiting

The SLG6M6201V has two forms of current limiting.

#### 12 A Standard Current Limiting Mode (Programmable Level)

Current is measured by mirroring the current through the main MOSFET. This response is a closed loop response and is therefore very fast and current limits in less than a few micro-seconds. There is no difference between peak or constant current limit

#### **Temperature Cutoff**

As the V(g) drops the Rds(ON) of the main MOSFET will increase, thus limiting the current, but also increasing the power dissipation of the IC. The IC is very small and cannot dissipate much power. Therefore, if a current limit condition is sustained the IC will heat up. If the junction temperature exceeds approximately 125°C (Default, Programmable), then V(g) will be brought low completely shutting off the main MOSFET. As the die cools the MOSFET will be turned back on at 100°C (Default, Programmable hysteresis).

If the current limiting condition has not been mitigated then the die will again heat up to 125°C (Default, Programmable) and the process will repeat.

#### Short Circuit Current Limiting Mode

When V(S) < 500 mV, the current is limited to approximately 3 A to 1.5 A. The short circuit current limit is a NVM programmable setting. This current limit is accomplished in the same manner as the Standard Current Limiting Mode with the exception that the current mirror is 15x greater. Because the current mirror is so much larger, a 15x smaller main MOSFET current is required to generate the same V(i). If V(S) rises above approximately 500 mV, then this mode is automatically switched out.

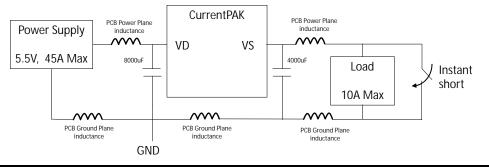

The short circuit current limiting mode does not protect the device from a sudden short after ON. In the event of a sudden short after ON, the VS pin of the CurrentPAK will switch from 10A @ 5V to ground within few nanoseconds. During this transition, the device will incur irreversible damage due to a high voltage spike created on VD or VS pins. To prevent this damage, it is recommended to add decoupling capacitors at the VD and VS pins of the CurrentPAK, as shown below, to suppress the voltage spike on the VS and VD pins. For example, assume the power supply max output feeding into the CurrentPAK is 45A max, it is recommended to use an 8000  $\mu$ F capacitor from VD to GND and a 4000  $\mu$ F capacitor from VS to GND. The decoupling capacitors should be placed as close to the CurrentPAK as possible. In addition to using the large size decoupling capacitors, minimizing the inductance on PCB power and ground plane is also important to minimize the voltage spike.

### Short Circuit Current Limiting Mode

When V(S) < 500 mV, which is the case if there is a solder bridge during the manufacturing process or a hard short on the power rail, then the current is limited to approximately 3 A to 1.5 A. The short circuit current limit is a NVM programmable setting. This current limit is accomplished in the same manner as the Standard. Current Limiting Mode with the exception that the current mirror is 15x greater. Because the current mirror is so much larger, a 15x smaller main MOSFET current is required to generate the same V(i). If V(S) rises above approximately 500 mV, then this mode is automatically switched out.

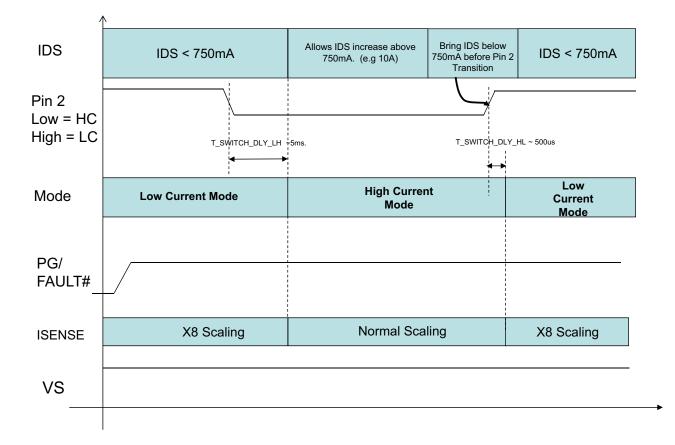

#### High Current Mode vs. Low Current Mode Selection

The device powers up in high current mode as default setting. In high current mode, the max IDS is 10 A. When Pin 2 is driven from low to high, the internal power FET array shuts down 7 out of 8 banks and keeps 1 out 8 banks active.

Best system practice: The purpose of low current mode is to allow the system to get a more precise current sense reading when instantaneous IDS is between 50 mA to 750 mA. In low current mode, the IOUT (pin 16) output scales up by 8 times to produce a higher current level reading. If the system does not need precise current reading at low IDS, it is recommended to stay in high current mode at all times by tying MODE (pin 2) to GND.

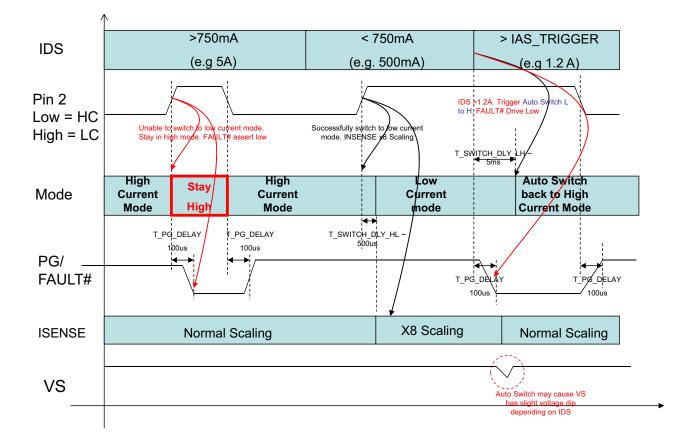

The load switch can only switch to low current mode when instantaneous IDS is less than  $I_{BLK\_HL\_TRANS}$  (750 mA). If the device attempts to switch to low current mode while the instantaneous IDS is higher than  $I_{BLK\_HL\_TRANS}$  (750 mA), the device's internal control logic will block this operation. The device keeps the FET array in high current mode to prevent any system failures. The device also asserts FAULT# (Pin 15) low to notify the system that the attempt to switch to low current mode has failed.

If the IDS current increases above  $I_{AS\_TRIGGER}$  (1.0 A typ), the device automatically switches back to high current mode by turning on all eight banks of the FET array. The auto switch delay time is  $T_{SWITCH}$  DLY LH (5 ms max).

#### **Programmable NVM Settings**

#### **ON1 and ON2 Pin Configuration**

ON1 and ON2 pins are inputs to a small NVM programmable logic cell "PLC".

| Bits [2:0] | ON Logic Functions                        |

|------------|-------------------------------------------|

| 000        | Pin1 = ON1<br>Pin2 = H/L Select, No Delay |

| Bits [5:3] | Turn ON Delay Functions                   |

| 000        | 0 ms Delay ON1                            |

Note: Delay table not applicable to turn device off.

#### **Power On Ramp Options**

The Power On Ramp Options are NVM programmable via the followings bits.

| Dite [7:6] | Pomp Options (V. of 2.2)()                                                                                                               | Toler    | ance     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| Bits [7:6] | Ramp Options (V <sub>D</sub> of 3.3V)                                                                                                    | Тур      | Max      |

| 00         | 2 ms linear ramp from output of programmable logic cell "PLC" to 90% of $V_D$ assuming < 500 $\mu s$ delay from PLC out to start of ramp | 1.6 V/ms | 2.0 V/ms |

#### **Power Good Reference Settings**

The Power Good feature is NVM programmable via the followings bits.

|             |                    | Under Voltage                | e Detect Level                 | Tolerance       |                                |  |

|-------------|--------------------|------------------------------|--------------------------------|-----------------|--------------------------------|--|

| Bits [10:8] | V <sub>D</sub> [V] | PG rising on<br>rising input | PG falling on<br>falling input | Typical @ 25 °C | Max over PVT<br>@ -20 to 70 °C |  |

| 001         | 3.3                | 2.97                         | 2.805                          | ±3%             | ±5%                            |  |

Power Good turns on ~ 100  $\mu s$  after power condition is met.

#### **Discharge Settings**

The discharge options are NVM programmable via the followings bits.

| Pite [12:11] | Resistance [Ω] |     |     |  |  |

|--------------|----------------|-----|-----|--|--|

| Bits [12:11] | Min            | Тур | Мах |  |  |

| 01           | 280            | 300 | 350 |  |  |

#### **Temperature Shutdown Settings**

The temperature shutdown limit is NVM programmable via the followings bits.

| Bits [15:13] | Temperature [°C] | Hysteresis [°C] | Tolerance |  |  |

|--------------|------------------|-----------------|-----------|--|--|

| 000          | 125              | 25              | ±10 °C    |  |  |

#### **Active Current Limit Settings**

The Active Current Limit is NVM programmable via the followings bits.

| Bits [17:16] | Current Limit [A]<br>(High Current Mode) | Current Limit [A]<br>(Low Current Mode) | Voltage Level of $V_S$ | Tolerance |  |

|--------------|------------------------------------------|-----------------------------------------|------------------------|-----------|--|

| 00           | 12 (default)                             | 1.5 (default)                           | > 500 mV               | ±20%      |  |

#### Short Circuit Current Limit Level

| Bits [20:18] | Current Limit [A],<br>VS < 500 mV | Short Circuit Current<br>Limit Tolerance |  |  |

|--------------|-----------------------------------|------------------------------------------|--|--|

| 011          | 2.0                               | ±50%                                     |  |  |

Bits [1023:21] are reserved.

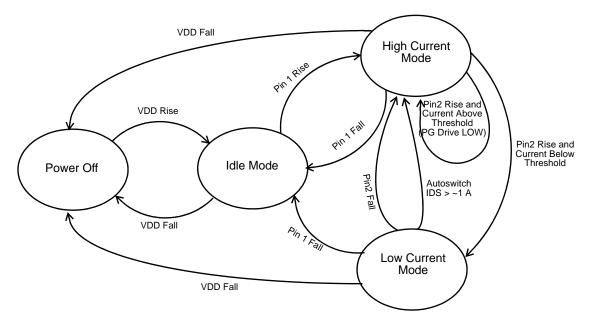

### State Diagram

Note: Pin 2 (MODE) must stay LOW during initial power up. After the device enters High Current Mode, the system can select Low Current Mode by driving Pin 2 to HIGH level

### **Initialization Timing Diagram**

Note: Pin 2 must stay LOW before the rising edge of Pin 1. Pin 2 can go HIGH only after  $V_{S}$  goes above 90%

## H->L & L->H Transition Timing Diagram

## Illegal & Auto Mode Transition Timing Diagram

## **Ordering Information**

| Part Number  | Туре                         | Production Flow             |

|--------------|------------------------------|-----------------------------|

| SLG6M6201V   | STQFN 18L FC                 | Commercial, -10 °C to 70 °C |

| SLG6M6201VTR | STQFN 18L FC (Tape and Reel) | Commercial, -10 °C to 70 °C |

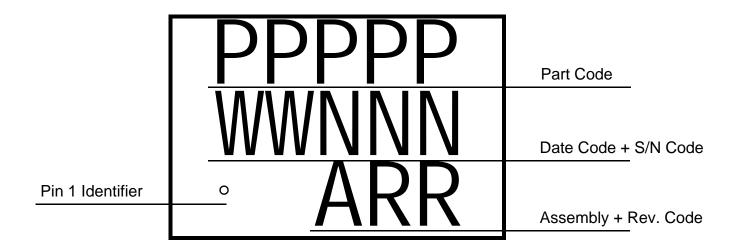

### Package Top Marking System Definition

A2

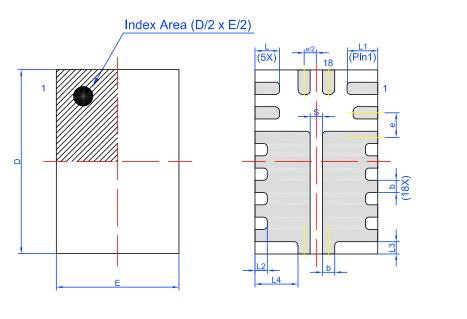

#### **Package Drawing and Dimensions**

#### 18 Lead TQFN Package 2 x 3 mm (Fused Lead) JEDEC MO-220, Variation WCEE

### Unit: mm

| Symbol | Min        | Nom. | Max   | Symbol | Min     | Nom. | Max  |  |

|--------|------------|------|-------|--------|---------|------|------|--|

| Α      | 0.50       | 0.55 | 0.60  | D      | 2.95    | 3.00 | 3.05 |  |

| A1     | 0.005      | -    | 0.060 | E      | 1.95    | 2.00 | 2.05 |  |

| A2     | 0.10       | 0.15 | 0.20  | L      | 0.35    | 0.40 | 0.45 |  |

| b      | 0.15       | 0.20 | 0.25  | L1     | 0.45    | 0.50 | 0.55 |  |

| е      | e 0.40 BSC |      |       |        | 0.2 REF |      |      |  |

| S      | 0.2 REF    |      |       | L3     | 0.2 REF |      |      |  |

|        |            |      |       | L4     | 0.7 REF |      |      |  |

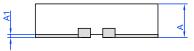

#### **Tape and Reel Specifications**

| Baakaga                  | # of         | Package Size | Max Units |         | Reel &           | Leader (min) |                | Trailer (min) |                | Таре          | Part          |

|--------------------------|--------------|--------------|-----------|---------|------------------|--------------|----------------|---------------|----------------|---------------|---------------|

| Package<br>Type          | # of<br>Pins |              | per Reel  | per Box | Hub Size<br>[mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| STQFN<br>18L FC<br>Green | 18           | 2 x 3 x 0.55 | 3,000     | 3,000   | 178 / 60         | 42           | 168            | 42            | 168            | 8             | 4             |

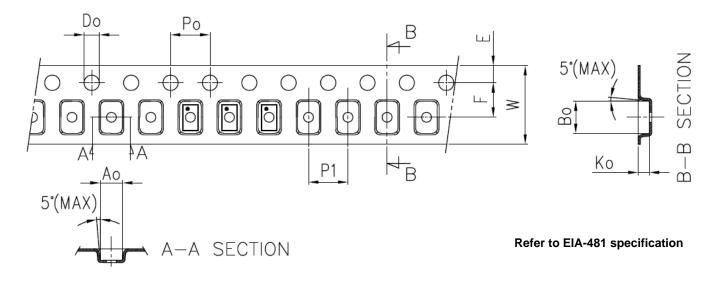

#### **Carrier Tape Drawing and Dimensions**

| Package<br>Type       | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge | le Index Hole<br>to Pocket Tap<br>Center |   |

|-----------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|------------------------------------------|---|

|                       | A0                  | B0                 | К0              | P0                  | P1              | D0                     | Е                             | F                                        | W |

| STQFN 18L<br>FC Green | 2.25                | 3.3                | 1.1             | 4                   | 4               | 1.55                   | 1.75                          | 3.5                                      | 8 |

#### **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.30 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by Silego manufacturer:

Other Similar products are found below :

TCK111G,LF(SFPF1018DS1222TCK2065G,LFSZNCP3712ASNT3GMIC2033-05BYMT-T5MIC2033-12AYMT-T5MIC2033-05BYM6-T5SLG5NT1437VTRSZNCP3712ASNT1GDML1008LDS-7KTS1670EDA-TRKTS1640QGDV-TRKTS1641QGDV-TRNCV459MNWTBGFPF2260ATMXU6513AU6119SMIC2012YM-TRMAX14919ATP+MC33882PEPTPS2021IDRQ1TPS2104DBVRMIC2098-1YMT-TRMIC94062YMTTRMP6231DN-LFMIC2075-2YMMIC2095-2YMT-TRMIC94068YML-TRSIP32461DB-T2-GE1NCP335FCT2GTCK105G,LF(SAP2151DSG-13MIC94094YC6-TRMIC94064YC6-TRMIC2505-1YMMIC94305YMT-TRMIC94081YFT-TRMIC94042YFL-TRMIC94041YFL-TRMIC2005-1.2YM6-TRTPS2032QDRQ1SIP32510DT-T1-GE3NCP333FCT2GNCP331SNT1GTPS2063DRTPS2042PMIC2008YML-TRMIC2040-1YMM