### **PCIE RTD3**

#### **General Description**

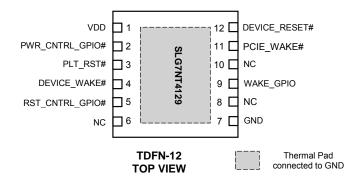

Silego SLG7NT4129 is a low power and small form device. The SoC is housed in a 2.5mm x 2.5mm TDFN package which is optimal for using with small devices.

#### **Features**

- Low Power Consumption

- Dynamic Supply Voltage

- RoHS Compliant / Halogen-Free

- Pb-Free TDFN-12 Package

### **Pin Configuration**

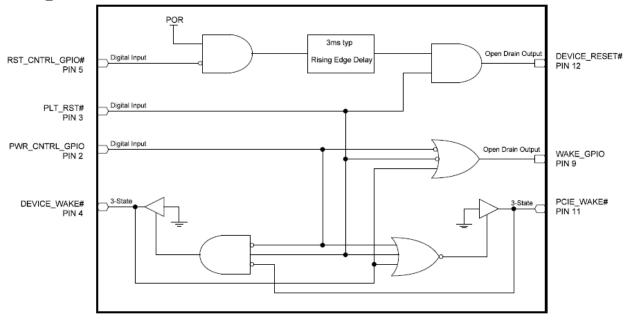

### **Output Summary**

- 2 Outputs Open Drain

- 2 Outputs 3-State

### **Block Diagram**

## Pin Configuration

| Pin#       | Pin Name           | Туре         | Pin Description                 |

|------------|--------------------|--------------|---------------------------------|

| 1          | VDD                | PWR          | Supply Voltage                  |

| 2          | PWR_CNTRL_GPIO#    | Input        | Digital Input                   |

| 3          | PLT_RST#           | Input        | Digital Input                   |

| 4          | DEVICE_WAKE#       | Input/Output | 3-State                         |

| 5          | RST_CNTRL_GPIO#    | Input        | Digital Input                   |

| 6          | NC                 |              | Keep floating or connect to GND |

| 7          | GND                | GND          | Ground                          |

| 8          | NC                 |              | Keep floating or connect to GND |

| 9          | WAKE_GPIO          | Output       | Open Drain                      |

| 10         | NC                 |              | Keep floating or connect to GND |

| 11         | PCIE_WAKE#         | Input/Output | 3-State                         |

| 12         | DEVICE_RESET#      | Output       | Open Drain                      |

| Exposed    | Exposed Bottom Pad | GND          | Ground                          |

| Bottom Pad |                    |              |                                 |

**Ordering Information**

| Part Number   | Package Type                             |

|---------------|------------------------------------------|

| SLG7NT4129V   | V = TDFN-12                              |

| SLG7NT4129VTR | VTR = TDFN-12 - Tape and Reel (3k units) |

### **Absolute Maximum Conditions**

| Parameter                 | Min. | Max. | Unit |

|---------------------------|------|------|------|

| V <sub>HIGH</sub> to GND  | -0.3 | 7    | V    |

| Voltage at input pins     | -0.3 | 7    | V    |

| Current at input pin      | -1.0 | 1.0  | mA   |

| Storage temperature range | -65  | 150  | °C   |

| Junction temperature      |      | 150  | °C   |

### **Electrical Characteristics**

(@ 25°C, unless otherwise stated)

| Symbol            | Parameter                                                  | Condition/Note                                                        | Min.  | Тур. | Max.  | Unit |  |  |  |

|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|-------|------|--|--|--|

| $V_{DD}$          | Supply Voltage                                             |                                                                       | 1.71  |      | 3.6   | V    |  |  |  |

| ΙQ                | Quiescent Current                                          | Static inputs and outputs                                             |       | 1    |       | μΑ   |  |  |  |

| T <sub>A</sub>    | Operating Temperature                                      |                                                                       | -40   | 25   | 85    | °C   |  |  |  |

| ΙL                | Input Leakage Current                                      | Leakage Current for Digital Inputs or outputs in High impedance state | -100  |      | 100   | nA   |  |  |  |

| \/                | LICH Loyal Input Valtage                                   | Logic Input, at VDD=1.8V                                              | 1.1   |      |       | V    |  |  |  |

| $V_{IH}$          | HIGH-Level Input Voltage                                   | Logic Input, at VDD=3.3V                                              | 1.8   |      |       | V    |  |  |  |

| V                 | LOW Lovel Input Voltage                                    | Logic Input, at VDD=1.8V                                              |       |      | 0.65  | V    |  |  |  |

| $V_{IL}$          | LOW-Level Input Voltage                                    | Logic Input, at VDD=3.3V                                              |       |      | 1.1   | V    |  |  |  |

| I <sub>IH</sub>   | HIGH-Level Input Current                                   | Logic Input Pins; V <sub>IN</sub> =VDD                                | -1    |      | 1     | μΑ   |  |  |  |

| I <sub>IL</sub>   | LOW-Level Input Current                                    | Logic Input Pins; V <sub>IN</sub> =0V                                 | -1    |      | 1     | μΑ   |  |  |  |

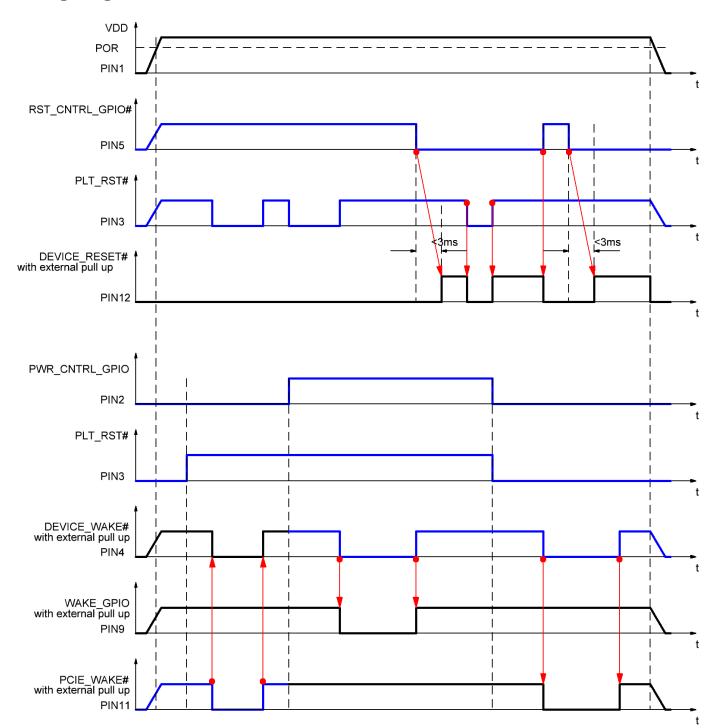

| T <sub>DLY0</sub> | Delay0 Time                                                |                                                                       | 2.1   | 3    | 3.9   | ms   |  |  |  |

| V                 | Output Voltage High                                        | 3-State, OE=1, I <sub>OH</sub> = 100μA at VDD=1.8V                    | 1.66  |      |       | V    |  |  |  |

| $V_{OH}$          | Output voltage riigii                                      | 3-State, OE=1, I <sub>OH</sub> = 3mA at VDD=3.3V                      | 2.1   |      |       | v    |  |  |  |

|                   | 3-State, OE=1, $I_{OL}$ = 100 $\mu$ A at VDD=1.8V          |                                                                       |       |      | 0.04  |      |  |  |  |

|                   |                                                            | 3-State, OE=1, I <sub>OL</sub> = 3mA at VDD=3.3V                      |       |      | 0.81  |      |  |  |  |

| $V_{OL}$          | Output Voltage Low                                         | Open Drain, I <sub>OL</sub> = 5mA, at VDD=1.8V                        |       |      | 0.340 | V    |  |  |  |

|                   |                                                            | Open Drain, I <sub>OL</sub> = 20mA at VDD=3.3V                        |       |      | 0.605 |      |  |  |  |

| $V_{O}$           | Maximal Voltage Applied to any PIN in High-Impedance State |                                                                       |       |      | VDD   | V    |  |  |  |

|                   |                                                            | 3-State, OE=1, V <sub>OL</sub> =0.15V, at VDD=1.8V                    | 0.34  |      |       |      |  |  |  |

|                   | LOW-Level Output Current                                   | 3-State, OE=1, V <sub>OL</sub> = 0.4V, at VDD=3.3V                    | 1.836 |      |       | m ^  |  |  |  |

| I <sub>OL</sub>   |                                                            | Open Drain, V <sub>OL</sub> =0.15V, at VDD=1.8V                       | 2.7   |      |       | mA   |  |  |  |

|                   |                                                            | Open Drain, V <sub>OL</sub> = 0.4V, at VDD=3.3V                       | 14.6  |      |       |      |  |  |  |

| T <sub>SU</sub>   | Start up Time                                              | After VDD reaches 1.6V level                                          |       | 7    |       | ms   |  |  |  |

### **Timing diagram**

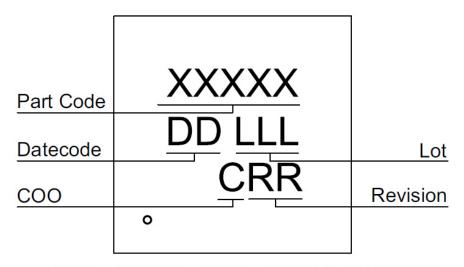

### **Package Top Marking**

XXXXX - Part ID Field: identifies the specific device configuration

DD – Date Code Field: Coded date of manufacture

LLL – Lot Code: Designates Lot #

C – COO: Specifies Country of Origin

RR – Revision Code: Device Revision

| Datasheet<br>Revision | Programming<br>Code Number | Part Code | Revision | Date       |

|-----------------------|----------------------------|-----------|----------|------------|

| 1.0                   | 04                         | 4129V     | AA       | 01/23/2013 |

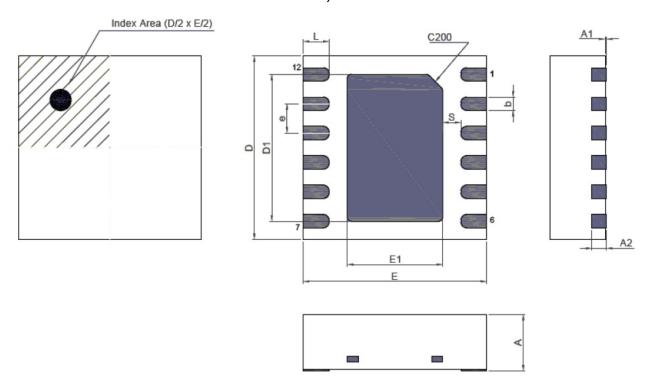

## **Package Drawing and Dimensions**

### 12 Lead TDFN Package JEDEC MO-252, Variation 2525E

#### Unit: mm

| Symbol | Min   | Nom. | Max   | Symbol | Min      | Nom. | Max  |

|--------|-------|------|-------|--------|----------|------|------|

| Α      | 0.70  | 0.75 | 0.80  | D1     | 1.95     | 2.00 | 2.05 |

| A1     | 0.005 | -    | 0.060 | E1     | 1.25     | 1.30 | 1.35 |

| A2     | 0.15  | 0.20 | 0.25  | е      | 0.40 BSC |      |      |

| b      | 0.13  | 0.18 | 0.23  | L      | 0.30     | 0.35 | 0.40 |

| D      | 2.45  | 2.50 | 2.55  | S      | 0.18     | -    | -    |

| E      | 2.45  | 2.50 | 2.55  |        |          |      |      |

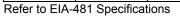

### **Tape and Reel Specification**

|                                     | # of | Nominal              | Max      | Units | Reel &           |         | er A           | Lead    | ler B          | Pocke | t (mm) |

|-------------------------------------|------|----------------------|----------|-------|------------------|---------|----------------|---------|----------------|-------|--------|

| Package Type                        | Pins | Package<br>Size (mm) | per reel |       | Hub Size<br>(mm) | Pockets | Length<br>(mm) | Pockets | Length<br>(mm) | Width | Pitch  |

| TDFN 12L<br>2.5x2.5mm<br>0.4P Green | 12   | 2.5x2.5x0.75         | 3000     | 3000  | 178/60           | 42      | 168            | 42      | 168            | 8     | 4      |

## **Carrier Tape Drawing and Dimensions**

| Package<br>Type                     | Pocket<br>BTM<br>Length<br>(mm) | Pocket<br>BTM Width<br>(mm) | Pocket<br>Depth<br>(mm) | Index Hole<br>Pitch<br>(mm) | Pocket<br>Pitch<br>(mm) | Index Hole<br>Diameter<br>(mm) | Index Hole<br>to Tape<br>Edge<br>(mm) | Index Hole<br>to Pocket<br>Center<br>(mm) | Tape Width (mm) |

|-------------------------------------|---------------------------------|-----------------------------|-------------------------|-----------------------------|-------------------------|--------------------------------|---------------------------------------|-------------------------------------------|-----------------|

|                                     | Α0                              | В0                          | K0                      | P0                          | P1                      | D0                             | E                                     | F                                         | w               |

| TDFN 12L<br>2.5x2.5mm<br>0.4P Green | 2.75                            | 2.75                        | 1.05                    | 4                           | 4                       | 1.55                           | 1.75                                  | 3.5                                       | 8               |

### **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 4.6875 mm<sup>3</sup> (nominal). More information can be found at <a href="https://www.jedec.org">www.jedec.org</a>.

## **Datasheet Revision History**

| Date       | Version | Change                                                              |

|------------|---------|---------------------------------------------------------------------|

| 11/08/2012 | 0.1     | New design                                                          |

| 11/22/2012 | 0.11    | Changed PIN12 type to Open Drain                                    |

| 11/26/2012 | 0.20    | Changed DEVICE_WAKE# and PCIE_WAKE# functionality to bi-directional |

| 01/18/2013 | 0.21    | Some typos in PIN out table are fixed                               |

| 01/23/2013 | 1.0     | Production Release                                                  |

| 06/11/2013 | 1.01    | Housekeeping (fixed block diagram)                                  |

#### Silego Website & Support

#### Silego Technology Website

Silego Technology provides online support via our website at <a href="http://www.silego.com/">http://www.silego.com/</a>. This website is used as a means to make files and information easily available to customers.

For more information regarding Silego Green products, please visit:

http://greenpak.silego.com/ http://greenpak2.silego.com/ http://greenfet.silego.com/ http://greenfet2.silego.com/ http://greenclk.silego.com/

Products are also available for purchase directly from Silego at the Silego Online Store at <a href="http://store.silego.com/">http://store.silego.com/</a>.

#### Silego Technical Support

Datasheets and errata, application notes and example designs, user guides, and hardware support documents and the latest software releases are available at the Silego website or can be requested directly at info@silego.com.

For specific GreenPAK design or applications questions and support please send email requests to GreenPAK@silego.com

Users of Silego products can receive assistance through several channels:

#### **Online Live Support**

Silego Technology has live video technical assistance and sales support available at <a href="http://www.silego.com/">http://www.silego.com/</a>. Please ask our live web receptionist to schedule a 1 on 1 training session with one of our application engineers.

#### **Contact Your Local Sales Representative**

Customers can contact their local sales representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. More information regarding your local representative is available at the Silego website or send a request to info@silego.com

#### **Contact Silego Directly**

Silego can be contacted directly via e-mail at <a href="mailto:info@silego.com">info@silego.com</a> or user submission form, located at the following URL: <a href="http://support.silego.com/">http://support.silego.com/</a>

#### Other Information

The latest Silego Technology press releases, listing of seminars and events, listings of world wide Silego Technology offices and representatives are all available at http://www.silego.com/

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. SILEGO TECHNOLOGY DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. SILEGO TECHNOLOGY RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Delay Lines/Timing Elements category:

Click to view products by Silego manufacturer:

Other Similar products are found below:

MC100EP195BFAG XDL20-3-050S HMC910LC4B HMC877LC3 DS1010-250 DS1023S-50+ DS1100LU-150 DS1100LU-20+ DS1100LU-25+ DS1100LU-30+ DS1100LU-35 DS1100LU-45 DS1100LU-500+ DS1100LU-75+ DS1100U-250 DS1100U-30+ DS1110E-150+ DS1110E-75+ DS1110LE-500+ DS1110S-100+ DS1110S-250+ DS1110S-300+ DS1110S-50+ DS1110S-500+ DS1100U-45+ DS1100U-40+ DS1100U-25+ DS1100LU-50+ DS1100LU-250+ DS1100U-60+ DS1100U-50+ DS1100U-150+ DS1100U-100+ DS1100U-50+ DS1135LU-30+ SY100E196JY DS1813R-10+ DS1010-100 MC100EP196BMNG NB6L295MMNG DS1135Z-6 DS1135Z-25+ DS1135Z-15+ DS1135Z-10+ DS1135LZ-12+ DS1100Z-50+ DS1100Z-200+ DS1100LZ-60+ DS1100LZ-500+ DS1100LZ-50+ DS1100LZ-50+