# **Application Note: SY5033A** CCM+QR SSR Flyback Controller

Advanced Design Specification

# **General Description**

SY5033A is a peak current mode SSR flyback controller targeting at wide output range fast charger application. It features wide VCC operating range (10~90V) which can eliminate external LDO circuit. It features HV start up circuit and low quiescent current which can achieve low no load loss. It adopts pseudo fixed frequency control which can eliminate slope compensation under CCM. It combines CCM and QR mode together to achieve optimized efficiency. It adopts adaptive peak current limit to achieve LPS requirement. It also provides comprehensive and reliable protections including BO, output OVP/UVP, VCC OVP, OLP, external OTP, OTP, Secondary SR MOS SCP, etc.

SY5033A is available with compact SO8 package.

### **Features**

- Wide VCC Operating Range: 10~90V

- HV Start up

- Mixed CCM+QR Control Strategy

- Pseudo Fixed Frequency Control to Eliminate Slope Compensation under CCM

- 65kHz Fixed Switching Frequency under CCM

- 90kHz Switching Frequency Limit under QR Mode

- Frequency Fold Back for High Average Efficiency

- Minimum Switching Frequency Limited to 28kHz

- Burst Control for High Light Load Efficiency

- Adaptive Peak Current Limit for LPS

- Comprehensive Protections Including BO, Output OVP/UVP, VCC OVP, OLP, External OTP, OTP, Secondary SR MOS SCP, etc

- Gate Drive Capability: +75mA/-600mA

- Internal Soft Start ProcessCompact Package: SO8

# **Applications**

Fast Charger AC/DC Adapter

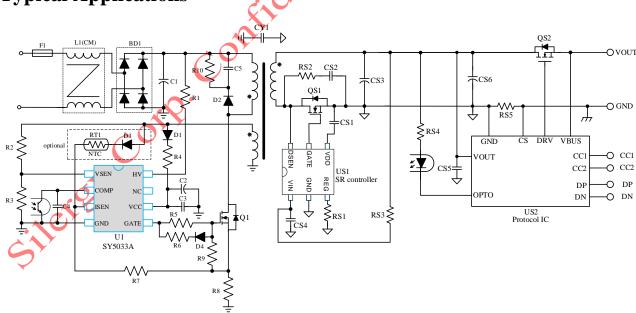

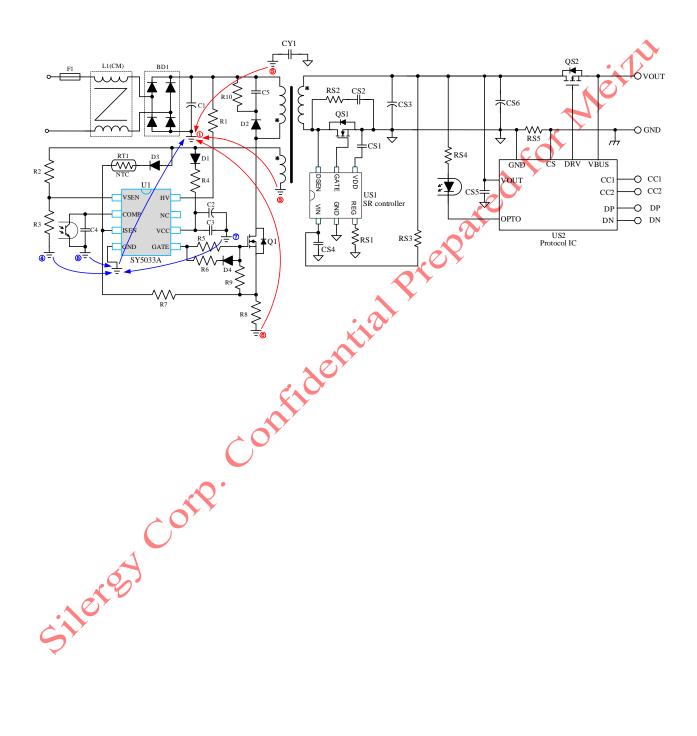

# **Typical Applications**

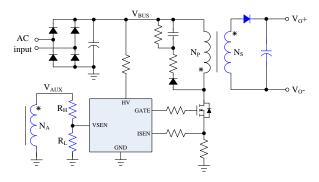

Fig.1 Typical Application Circuit

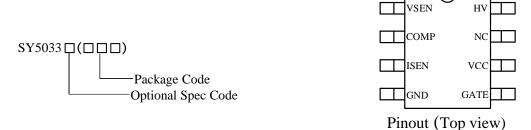

# **Ordering Information**

| Ordering Number | Package | Top Mark |

|-----------------|---------|----------|

| SY5033AFAP      | SO8     | GHQxyz   |

x=year code, y=week code, z= lot number code

## **Pinout**

| Pin Number | Pin Name | Pin Description                                                                             |

|------------|----------|---------------------------------------------------------------------------------------------|

| 1          | VSEN     | Multiple functions including valley detecting, input voltage sense and output voltage sense |

| 2          | COMP     | This pin is connected to an opto-coupler for output voltage feed back                       |

| 3          | ISEN     | Primary peak current sense and programmable external OTP                                    |

| 4          | GND      | Ground                                                                                      |

| 5          | GATE     | Gate drive                                                                                  |

| 6          | VCC      | Power supply                                                                                |

| 7          | NC       |                                                                                             |

| 8          | HV       | HV start up                                                                                 |

# Absolute Maximum Ratings (Note 1)

| HV                                            |            |

|-----------------------------------------------|------------|

| VCC                                           | -0.3V~100V |

| GATE                                          | -0.3V~15V  |

| VSEN, ISEN                                    |            |

| COMP                                          |            |

| Power Dissipation, at $T_A = 25^{\circ}C$ SO8 | 1.1W       |

| Package Thermal Resistance (Note 2)           |            |

| SO8, $\theta_{JA}$                            | 125°C/W    |

| SO8, $\theta_{JC}$                            | 60°C/W     |

| Junction Temperature Range                    |            |

|                                               | 260°C      |

|                                               |            |

# **Recommended Operating Conditions**

| V <sub>CC</sub>            | 10V~90V        |

|----------------------------|----------------|

| Junction Temperature Range | -40°C to 125°C |

| Ambient Temperature Range  | 40°C to 105°C  |

# **Electrical Characteristics**

$(V_{CC} = 12V \text{ (Note 3)}, T_A = 25^{\circ}\text{C unless otherwise specified)}$

| $(V_{CC} = 12V \text{ (Note 3)}, T_A = 25^{\circ}\text{C u})$ |                          |                              |     | Г    |     |      |

|---------------------------------------------------------------|--------------------------|------------------------------|-----|------|-----|------|

| Parameter                                                     | Symbol                   | Test Conditions              | Min | Тур  | Max | Unit |

| HV Pin Section                                                |                          |                              |     |      |     |      |

| Break Down Voltage                                            | $V_{HV\_BR}$             |                              | 900 |      |     | V    |

| Leakage Current                                               | $I_{HV\_LK}$             | $V_{HV}=400V_{DC}$           |     |      | 1   | μA   |

| HV Current to Charge VCC                                      | $I_{HV}$                 | $V_{HV}=100V_{DC}$           |     | 2.3  |     | mΑ   |

| VCC Pin Section                                               | 1                        |                              |     |      |     |      |

| Turn ON Threshold                                             | V <sub>CC_ON</sub>       | V <sub>CC</sub> rising up    |     | 18   | •   | V    |

| HV Current Source Enable                                      |                          |                              |     |      | 40) |      |

| Threshold                                                     | V <sub>CC_MIN</sub>      | V <sub>CC</sub> falling down |     | 9.0  |     | V    |

| Turn OFF Threshold                                            | V <sub>CC_OFF</sub>      | V <sub>CC</sub> falling down |     | 8.0  |     | V    |

| OVP Threshold                                                 | V <sub>CC_OVP</sub>      |                              |     | 94   |     | V    |

| Current Sink under Over                                       |                          | ** **                        |     | 60   |     |      |

| Voltage Condition                                             | $I_{CC\_OVP}$            | $V_{CC}=V_{CC\_OVP}+0.1V$    |     | 3    |     | mA   |

| Start up Current                                              | I <sub>CC_ST</sub>       | $V_{CC}=V_{CC\_ON}-0.5V$     |     |      | 100 | μA   |

| Quiescent Current                                             | I <sub>CC_Q</sub>        |                              |     | 280  |     | μA   |

| Operating Current                                             | I <sub>CC_OPT</sub>      | $C_L=1$ nF, $F_{SW}=65$ kHz  |     | 2.2  |     | mA   |

| Current Sink under Fault                                      |                          | 2 , 511                      | 200 |      |     |      |

| Condition                                                     | $I_{CC\_FAULT}$          |                              | 0)  | 0.65 |     | mA   |

| ISEN Pin Section                                              |                          | 0^                           |     |      |     |      |

| Max Peak Current Limit                                        | V <sub>ISEN_MAX</sub>    |                              | ,   | 500  |     | mV   |

| Min Peak Current Limit                                        | V <sub>ISEN_MIN</sub>    |                              |     | 138  |     | mV   |

| Primary OCP Threshold                                         | V <sub>ISEN_OCP</sub>    |                              |     | 650  |     | mV   |

| Leading Edge Blanking                                         | T <sub>ISEN_LEB</sub>    |                              |     | 450  |     | ns   |

| Blanking time for ISEN                                        | 1 ISEN_LEB               |                              |     |      |     | 113  |

| Short Detecting                                               | T <sub>ISENSCP_BLK</sub> | Low line condition           |     | 3.9  |     | μs   |

| Threshold Voltage for ISEN                                    | C                        |                              |     |      |     |      |

| Short Detecting                                               | V <sub>ISEN_SCP</sub>    | <b>Y</b>                     |     | 50   |     | mV   |

| External OTP Threshold                                        | V <sub>ISEN_EXOTP</sub>  |                              |     | 0.5  |     | V    |

| VSEN Pin Section                                              | I ISEN_ENGIN             |                              |     |      |     |      |

| Blanking Time for Output                                      |                          |                              |     |      |     |      |

| Voltage Sense after MOS is                                    | Tyosen_blk               | I <sub>COMP</sub> =120uA     |     | 1.45 |     | μs   |

| Turned OFF                                                    | O COLIN COLIN            | Com                          |     |      |     |      |

| Output OVP Threshold                                          | V <sub>VSEN_OVP</sub>    |                              |     | 2.0  |     | V    |

| Output UVP Threshold                                          | V <sub>VSEN_UVP</sub>    |                              |     | 150  |     | mV   |

| Output UVP Blanking Time                                      |                          |                              |     |      |     |      |

| during Start up                                               | T <sub>STBLK_UVP</sub>   |                              |     | 17.8 |     | ms   |

| Brown out Threshold                                           | T                        |                              |     | 100  |     |      |

| Current                                                       | $I_{BO}$                 |                              |     | 100  |     | μA   |

| Brown in Hysteresis Current                                   | I <sub>BI_HYS</sub>      |                              |     | 12   |     | μA   |

| Brown out Debounce Time                                       | T <sub>BO_DBC</sub>      |                              |     | 64   |     | ms   |

| High line condition (Force                                    |                          |                              |     |      |     |      |

| QR) Threshold Current                                         | $I_{LINE\_H}$            |                              |     | 300  |     | μA   |

| Back to Low Line                                              |                          |                              |     |      |     |      |

| Condition Hysteresis                                          | I <sub>LINE_L_HYS</sub>  |                              |     | 54   |     | μΑ   |

| Current                                                       |                          |                              |     |      |     |      |

| COMP Pin Section                                              |                          |                              |     |      |     |      |

| OLP Debounce Time                                             | T <sub>OLP_DBC</sub>     |                              |     | 64   |     | ms   |

| Switching Frequency Section                                   |                          |                              |     |      |     |      |

|                                                               |                          |                              |     |      |     |      |

| Frequency under CCM               | F <sub>SW_CCM</sub>      |                      |                | 65                 |  | kHz |

|-----------------------------------|--------------------------|----------------------|----------------|--------------------|--|-----|

| Frequency Limit under QR Mode     | F <sub>SW_MAX_QR</sub>   |                      |                | 90                 |  | kHz |

| Minimum Switching<br>Frequency    | F <sub>SW_MIN</sub>      |                      |                | 28                 |  | kHz |

| Frequency Modulation<br>Amplitude | A <sub>FSW_MOD_AMP</sub> | Under CCM            |                | ±6%                |  |     |

| Frequency Modulation<br>Period    | $T_{FSW\_MOD}$           |                      |                | 500                |  | μs  |

| Maximum ON Time                   | T <sub>ON_MAX</sub>      |                      |                | 18                 |  | μs  |

| Maximum OFF Time                  | T <sub>OFF_MAX</sub>     |                      |                | 240                |  | μs  |

| <b>GATE Pin Section</b>           |                          |                      |                |                    |  |     |

| High Level Clamp                  | V <sub>GATE_CLAMP</sub>  | V <sub>CC</sub> =20V |                | 13.5               |  | V   |

| Max Source Current                | I <sub>SOURCE_MAX</sub>  |                      |                | 75                 |  | mA  |

| Max Sink Current                  | I <sub>SINK_MAX</sub>    |                      |                | 600                |  | mA  |

| Internal OTP Section              |                          |                      |                | <b>\(\lambda\)</b> |  |     |

| OTP threshold                     | T <sub>OTP</sub>         |                      |                | 150                |  | °C  |

| Hysteresis to Recovery            | T <sub>OTP_HYS</sub>     |                      |                | 23                 |  | °C  |

| Soft Start Section                |                          |                      |                |                    |  |     |

| Soft start time                   | $T_{SS}$                 |                      |                | 3.5                |  | ms  |

| <b>Auto-recovery Control</b>      | ·                        |                      | χ <sup>0</sup> |                    |  |     |

| Re-start timer                    | $T_{RST}$                |                      |                | 2                  |  | S   |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note2:**  $\Theta_{JA}$  is tested on Silergy EVB, the EVB is two layer and loz copper is used.

Note 3: Increase VCC pin voltage gradually higher than VCC on voltage then turn down to 12V.

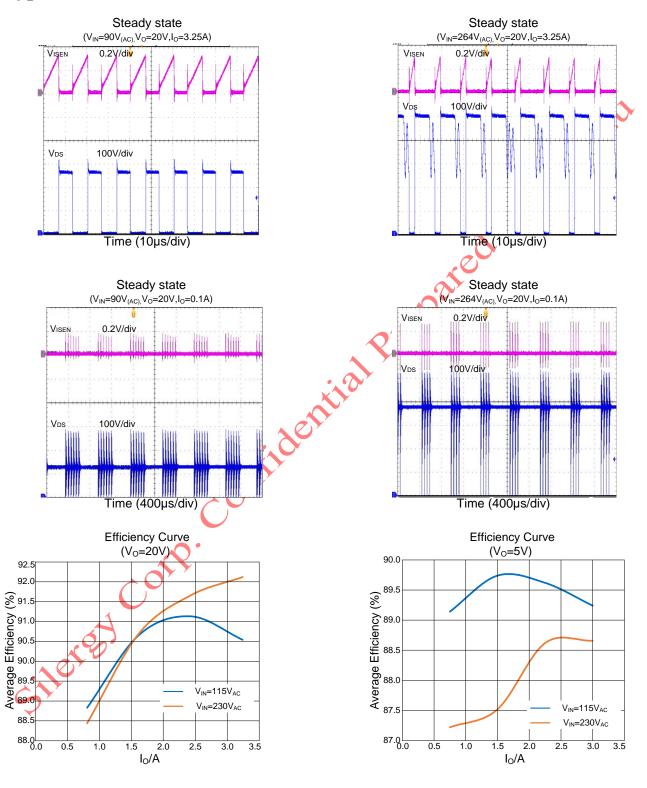

# **Typical Performance Characteristics**

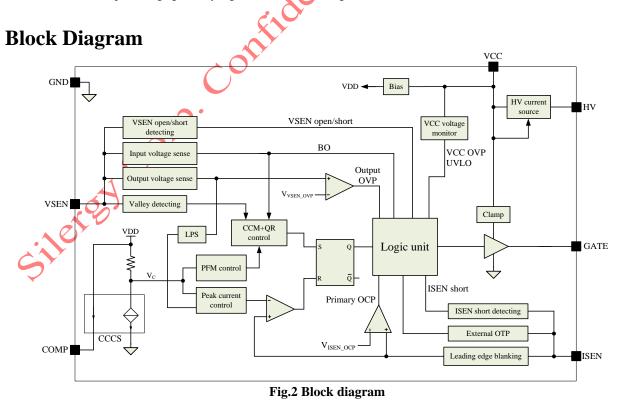

# **Operation Principles**

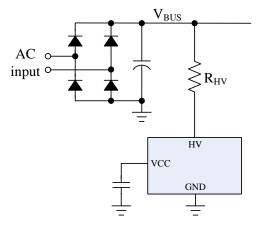

#### HV start up

SY5033A features HV start up to simplify start up circuit and achieve low no load loss. HV pin is recommended to connected to BUS+ through a resistor  $R_{HV}$ .  $R_{HV}$  is used to improve the reliability of HV pin and the recommended resistance is  $10k\Omega\sim20k\Omega$ .

Fig.1 HV start up circuit

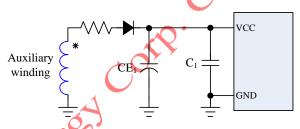

#### Wide VCC operating range

SY5033A features wide VCC operating range from 10V to 90V, which is dedicated for fast charger applications. The traditional external LDO circuit for IC power supply can be eliminated to achieve simple peripheral circuit. A ceramic capacitor C<sub>1</sub> is recommended to be mounted as close as possible to IC's VCC and GND pin on PCB layout.

Fig.2 Simple IC power supply circuit

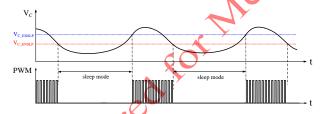

#### CCM+QR mixed operating principle

SY5033A adopts mixed control method that combine CCM and QR mode together. CCM frequency is fixed to 65kHz, while QR mode frequency is limited to 90kHz. Transformer is designed that under low line input and heavy load condition, IC operates under CCM. While under other conditions, IC will operate under QR mode (valley switching). Due to this mixed control method, optimized efficiency and transformer size can be achieved.

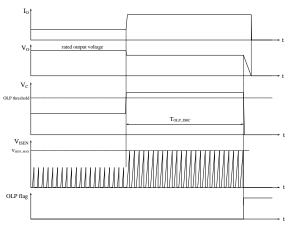

Under light load condition, IC operates under burst mode to further improve light load efficiency. Burst mode is controlled by COMP pin internal control voltage  $V_C$ . When  $V_C$  is lower than sleep mode threshold, IC will stop switching and enter sleep mode. Under sleep mode, the current consumed by IC is maintained to very low level (typical=280uA). When  $V_C$  is higher than another exit sleep threshold, IC will exit sleep mode and resume normal operating. The lighter the load is, the longer IC will stay in sleep mode.

Fig.3 Timing diagram of burst mode control

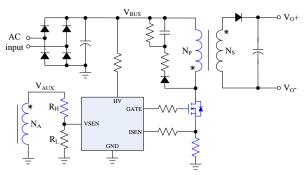

### Force QR at high line input condition

CCM under high line input condition is generally not allowed due to lower converter efficiency and higher voltage spike if secondary SR switcher is used. SY5033A adopts force QR mode control to guarantee QR mode (valley turn on) under high line input condition and steady state.

SY5033A senses input voltage by VSEN pin negative current I<sub>VSEN</sub> (flowing out of VSEN pin) when primary power MOS is turned on. When primary power MOS is turned on, VSEN pin will be internally clamped to 0V, since the negative voltage on auxiliary winding is proportional to BUS voltage, the current flowing out of VSEN pin will be proportional to BUS voltage. SY5033A will compare the current flowing out of VSEN pin with high line threshold current I<sub>LINE H</sub> (typical=300uA), if the current flowing out of VSEN pin is larger than I<sub>LINE H</sub>, input high line condition is recognized by IC and force QR mode is enabled. When VSEN pin negative current is lower than another threshold current I<sub>LINE H</sub>-I<sub>LINE L HYS</sub>, low line input condition will be recognized by IC and force QR will be disabled, CCM operating will be allowed. The upper resistor of VSEN pin resistor divider connected between auxiliary winding will set input high line condition threshold voltage. Input high line condition threshold  $V_{IN\_H}$  (RMS) is calculated as below equation:

$$V_{\mathrm{IN}_{-}\mathrm{H}} = \frac{I_{\mathrm{LINE}_{-}\mathrm{H}}}{\sqrt{2}} \times \frac{N_{\mathrm{P}}}{N_{\mathrm{A}}} \times R_{\mathrm{H}}$$

Fig.4 Illustration of input voltage detecting

#### **BO** (brown out) protection

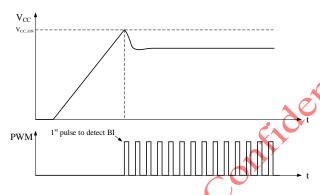

During Vin start up, when  $V_{CC}$  rises to  $V_{CC\_ON}$  threshold, IC will check if input voltage is higher than BI(brown in) threshold firstly. The  $1^{st}$  switching pulse is aimed to detect input voltage condition. If VSEN pin negative current  $I_{VSEN}$  is larger than BI threshold, IC will continue normal switching. Otherwise, IC will stop switching and enter auto-recovery mode.

Fig.5 1st detecting pulse when Vin start up

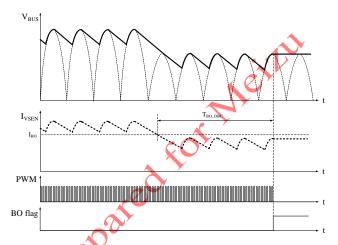

Under abnormal conditions, if AC input voltage becomes lower and lower, input current will become larger and larger, there is high risk of AC components such as NTC resistor, EMI choke and bridge rectifier which may be over heated and finally break down. SY5033A adopts BO protection (input under voltage protection) to avoid over heating of AC input components. It detects BUS voltage by VSEN pin negative current I<sub>VSEN</sub> when primary power MOS is turned on. IC will compare I<sub>VSEN</sub> with internal BO threshold current I<sub>BO</sub>, if I<sub>VSEN</sub> is lower than I<sub>BO</sub>, and sustained longer than BO debounce time T<sub>BO\_DBC</sub>, IC will stop switching and enter auto-recovery mode. The input BO threshold can be calculated according to below equation:

$$V_{\text{IN\_BO}} = \frac{I_{\text{BO}}}{\sqrt{2}} \times \frac{N_{\text{P}}}{N_{\text{A}}} \times R_{\text{H}}$$

Generally, input BO threshold voltage is defined between 60Vac and 70Vac.

Fig.6, Timing diagram of BO protection

### Programmable output OVP/UVP

SY5033A will sense output voltage by VSEN pin cycle by cycle, and programmable output OVP/UVP can be achieved. When primary power MOS is turned off, voltage on auxiliary winding  $V_{AUX}$  will be proportional to output voltage  $V_O$ . VSEN pin will sense the output voltage by a resistor divider ( $R_H$  and  $R_L$ ) connected between auxiliary winding.

Fig.7 Circuit diagram of output voltage sense

The relationship between VSEN pin voltage and output voltage is shown as below equation:

$$V_{\text{VSEN}} = V_{\text{O}} \cdot \frac{N_{\text{A}}}{N_{\text{S}}} \cdot \frac{R_{\text{L}}}{R_{\text{H}} + R_{\text{L}}}$$

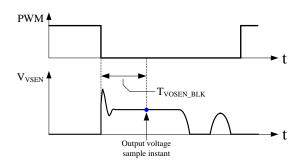

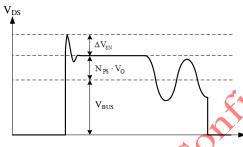

Since voltage spike will present on VSEN pin when primary side power MOS is turned off as shown in below figure, to avoid false trigger of output OVP by the voltage

spike, a blanking time  $T_{VOSEN\_BLK}$  is adopted. Output voltage will only be sampled after  $T_{VOSEN\_BLK}$  elapse. Primary side RCD snubber should be carefully tuned to make sure that voltage spike sustained time will not exceed  $T_{VOSEN\_BLK}$ .

Fig.8 Illustration of blanking time for output voltage sense

When VSEN pin voltage rises above OVP threshold  $V_{VSEN\_OVP}$ , IC will stop switching and enter auto-recovery mode. Output OVP threshold is calculated as below equation.

$$V_{\text{O\_OVP}} = V_{\text{VSEN\_OVP}} \cdot \frac{N_{\text{S}}}{N_{\text{A}}} \cdot \frac{R_{\text{H}} + R_{\text{L}}}{R_{\text{L}}}$$

For fast charger applications, output voltage varies according to protocol controller, so output OVP level should be determined by the maximum output voltage. For example, a fast charger claims output voltage range from 3.3V to 20V, then output OVP level is equal to 20V multiplied by 120% ( $V_{O_OVP}$ =24V).

Note: VSEN pin upper resistor  $R_{\rm H}$  should be determined firstly according to input BO threshold voltage (customer predefined), and then lower resistor  $R_{\rm L}$  of VSEN pin resistor divider is calculated according to below equation.

$$R_{L} = R_{H} \cdot \frac{1}{\frac{N_{A}}{N_{S}} \cdot \frac{V_{O_{L}OVP}}{V_{VSEN_{L}OVP}} - 1}$$

### Programmable external OTP

SY5033A features programmable external OTP on ISEN pin. The circuit diagram is shown as fig.9. A fast-switching signal diode  $D_1$ , a NTC resistor  $RT_1$  and a fine tune resistor  $R_{TUNE}$  are used to achieve external OTP. When primary power MOS is turned off, the volage on auxiliary winding will be proportional to output voltage. The relationship between ISEN pin voltage and output voltage is shown as below equation:

$$V_{\text{ISEN}} = (\frac{N_{\text{A}}}{N_{\text{S}}} \cdot V_{\text{O}} - V_{\text{D1}}) \cdot \frac{R_{\text{OCP}} + R_{\text{ISEN}}}{R_{\text{RT1}} + R_{\text{TUNE}} + R_{\text{OCP}} + R_{\text{ISEN}}}$$

The voltage on ISEN pin will be sensed and compared with external OTP threshold V<sub>ISEN\_EXOTP</sub> (typical=0.5V), if ISEN pin voltage is higher than the OTP threshold for 4 consecutive switching cycles, external OTP will be triggered. When external OTP is triggered, IC will enter auto-recovery mode. The resistance of NTC resistor to trigger external OTP is calculated by below equation:

$$R_{\text{NTC(OTP)}} = (R_{\text{OCP}} + R_{\text{ISEN}}) \cdot (\underbrace{\frac{N_{\text{A}}}{N_{\text{S}}} \cdot V_{\text{O}} - V_{\text{DI}}}_{\text{VISEN_EXOTP}} - 1) - R_{\text{TUNE}}$$

$$AC \underset{\text{input}}{\longrightarrow} V_{\text{NS}} \underset{\text{ISEN}}{\longrightarrow} V_{\text{O}} \underset{\text{NS}}{\longrightarrow} V_{\text{O}} \underset{\text{NS}} \underset{\text{NS}}{\longrightarrow} V_{\text{O}} \underset{$$

Fig.9 Circuit diagram of external OTP

#### **OLP (Over Load Protection)**

When output over load happens, COMP pin internal voltage  $V_{\rm C}$  will be pulled up to high level, and primary peak current will reach the maximum value. SY5033A will compare  $V_{\rm C}$  with internal OLP threshold, when  $V_{\rm C}$  is higher than the OLP threshold, a timer will begin to count, and if  $V_{\rm C}$  is continuously higher than OLP threshold which result in OLP timer elapse, SY5033A will stop switching and enter auto-recovery mode.

Fig.10 Timing diagram of OLP

#### Secondary SR MOS short circuit protection

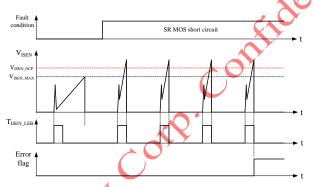

Under secondary SR MOS short circuit condition, when primary power MOS is turned on, primary current of flyback converter will increase with very high di/dt rate, during ISEN pin leading edge blanking time, primary peak current sense voltage V<sub>ISEN</sub> will rise to very high level without limit. SY5033A adopts a primary OCP threshold V<sub>ISEN\_OCP</sub>, when V<sub>ISEN</sub> is larger than V<sub>ISEN\_OCP</sub>, and last for 4 consecutive switching cycles, secondary SR MOS short circuit protection will be triggered, IC will stop switching and enter auto-recovery mode.

Fig.11 Timing diagram of primary OCP

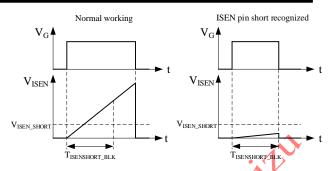

### ISEN pin short circuit protection

SY5033A will check if ISEN pin is shorted to GND during each switching cycle. When primary side power MOS is turned on, a blanking time T<sub>ISENSHORT\_BLK</sub> is adopted, after this blanking time elapse, IC will compare ISEN pin voltage with internal threshold voltage V<sub>ISEN\_SHORT</sub> (typical=50mV), if ISEN pin voltage is lower than this threshold voltage and last for 2 switching cycles, ISEN pin shorted to GND fault is detected, IC will stop switching and then enter auto-recovery mode.

Fig.12 Illustration of ISEN short circuit detecting

#### **Internal OTP**

SY5033A monitors die temperature under normal operating mode. Once die temperature rises above internal OTP threshold, IC will stop switching and enter autorecovery mode. Once die temperature drops below recovery threshold (Tore Totp\_Hys), IC will resume normal operating.

# Power Supply Design Guard

### **BUS** capacitor calculation

Generally, bulk capacitor C<sub>BUS</sub> is selected according to below rules:

1~2uF per watt of input power

$$C_{BUS.MIN} = (1.0 \cdot P_{IN}) uF$$

$$C_{\text{BUS MAX}} = (2.0 \cdot P_{\text{IN}}) uF$$

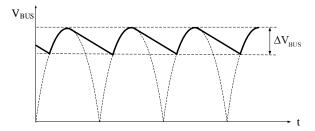

To be more accurate, BUS capacitor can be selected according to predefined voltage ripple  $\triangle V_{BUS}$  on BUS capacitor under minimum AC input voltage and full load condition as shown in below figure.

Fig.13 Illustration of voltage ripple on BUS capacitor When voltage ripple  $\triangle$  V<sub>BUS</sub> is selected, then BUS capacitor can be calculated as below equation:

$$C_{_{BUS}} = \frac{P_{_{O}}}{\eta \cdot \pi \cdot f_{_{AC}} \cdot \Delta V_{_{BUS}}} \cdot \frac{\arcsin(1 - \frac{\Delta V_{_{BUS}}}{\sqrt{2} \cdot V_{_{IN,MIN}}}) + \frac{\pi}{2}}{2\sqrt{2} \cdot V_{_{IN,MIN}} - \Delta V_{_{BUS}}}$$

Where  $P_O$  is rated output power,  $\triangle V_{BUS}$  is predefined voltage ripple on BUS capacitor,  $\eta$  is converter efficiency,  $f_{AC}$  is frequency of AC input voltage and  $V_{IN,MIN}$  is the minimum AC input voltage.

### Transformer parameter calculation

### 1) Primary/secondary turns ratio: NPS

Maximum allowed  $N_{PS}$  is limited by the voltage stress of primary power MOSFET:

$$N_{PS} \leq \frac{V_{MOS,BR} \cdot K_{DR} - \sqrt{2} \cdot V_{IN,MAX} - \Delta V_{SN}}{V_{O,MAX}}$$

Where  $V_{MOS,BR}$  is the breakdown voltage of primary MOSFET,  $K_{DR}$  is  $V_{DS}$  de-rating factor of MOSFET,  $\Delta V_{SN}$  is voltage spike generated when primary MOS is turned off, and  $V_{O,MAX}$  is the maximum output voltage.

Fig.14 Illustration of voltage spike on primary MOS

# 2) Primary inductance: L<sub>M</sub>

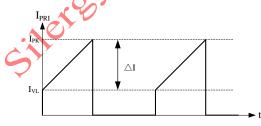

Primary inductance of transformer is related with primary current ripple. Generally, primary side current ripple is defined as shown in below figure. And current ripple factor is defined as below equation:

Fig.15 Illustration of primary current ripple

$$K_{RP} = \frac{0.5 \cdot \Delta I}{I_{PK} - 0.5 \cdot \Delta I}$$

K<sub>RP</sub><1: CCM

K<sub>RP</sub>=1: DCM (QR mode)

Generally, to get optimized transformer size and efficiency for universal input application, under low input and full load condition, CCM operating is selected, and under high input and full load condition, QR mode is selected.

Based on design experience, under lowest input voltage and full load condition, it is recommended to choose  $K_{RP}$  between 0.3~0.5 for optimized performance. And for an initial start,  $K_{RP}$ =0.4 is selected. Once  $K_{RP}$  is selected, primary inductance of transformer is calculated as below equation:

$$L_{M} = \frac{V_{BUS,MIN}^{2} \cdot D_{MAX}^{2} \cdot \eta}{2 \cdot P_{O} \cdot f_{SW} \cdot K_{RP}}$$

Where  $f_{SW}$  is rated CCM switching frequency,  $P_O$  is rated output power, is converter efficiency.  $D_{MAX}$  is maximum duty cycle at  $V_{BUS,MIN}$  and rated output power, and  $D_{MAX}$  is calculated as below equation:

$$D_{\text{MAX}} = \frac{N_{\text{PS}} \cdot V_{\text{O}}}{V_{\text{BUS MIN}} + N_{\text{PS}} \cdot V_{\text{O}}}$$

### 3) Turns of primary winding

(a)Select the magnetic core type, identify the effective cross-sectional area A<sub>E</sub>

**(b)**Preset the maximum magnetic flux density  $B_{MAX}$  at minimum BUS voltage and full load condition:

$$B_{MAX} = 0.2T \sim 0.3T$$

(c)Calculate maximum primary peak current I<sub>PK</sub> at rated output power:

$$I_{PK} = \frac{V_{O} \cdot I_{O} \cdot (1 + K_{RP})}{V_{BUS,MIN} \cdot D_{MAX} \cdot \eta}$$

(d)Calculate primary turns: N<sub>P</sub>

$$N_{_{P}} = \frac{L_{_{M}} \cdot I_{_{PK}}}{B_{_{MAX}} \cdot A_{_{E}}}$$

Where A<sub>E</sub> is effective cross-sectional area of core

#### 4) Turns of secondary winding: N<sub>S</sub>

$$N_{S} = \frac{N_{P}}{N_{PS}}$$

#### 5) Turns of auxiliary winding: NA

Turns of auxiliary winding is decided by minimum VCC pin voltage under normal operating. Minimum VCC pin voltage occurs under minimum output voltage. Generally,

minimum VCC pin voltage should be guaranteed to be above 10V. Turns of auxiliary winding can be initially calculated as below equation:

$$N_{A} = \frac{10 \cdot N_{S}}{V_{O,MIN}}$$

VCC pin voltage should be checked under minimum output voltage and null load condition, and turns of auxiliary winding should be fine-tuned according to actual test results.

### Peak current sense resistor calculation

Under minimum AC input voltage condition, when BUS voltage is maximum value and primary peak current reaches ISEN pin maximum setpoint, maximum output current is reached (OCP point). Under OCP point, primary peak current is calculated as below equations:

$$D_{\text{OCP}} = \frac{N_{\text{PS}} \cdot V_{\text{O}}}{\sqrt{2} \cdot V_{\text{IN,MIN}} + N_{\text{PS}} \cdot V_{\text{O}}}$$

$$I_{\text{PK},\text{MAX}} = \frac{P_{\text{O}} \cdot K_{\text{OCP}}}{\sqrt{2} \cdot V_{\text{IN},\text{MIN}} \cdot D_{\text{OCP}} \cdot \eta} + \frac{\sqrt{2} \cdot V_{\text{IN},\text{MIN}} \cdot D_{\text{OCP}}}{2 \cdot L_{\text{M}} \cdot f_{\text{SW}}}$$

Where  $K_{OCP}$  is OCP proportion,  $K_{OCP}$  is generally set to  $120\% \sim 130\%$ .

$$K_{OCP} = \frac{I_{O,OCP}}{I_{O}}$$

After maximum primary peak current has been calculated, the peak current sense resistor R<sub>ISEN</sub> can be easily derived by below equation:

$$R_{ISEN} = \frac{V_{ISEN,MAX}}{I_{PK,MAX}}$$

Where V<sub>ISEN,MAX</sub> is ISEN pin current sense limit voltage (typical=0.5V).

Customer needs to fine tune the current sense resistor according to the converter actual OCP point. If OCP point is larger than target level,  $R_{\rm ISEN}$  should be tuned a little larger, If OCP point is smaller than target level,  $R_{\rm ISEN}$  should be tuned a little smaller.

### **Secondary SR MOS Selection**

Under the conditions of the maximum BUS voltage and maximum output voltage, the reverse voltage of secondary rectification diode will reach the maximum level. The maximum value of SR MOS reverse voltage is calculated as below equation:

$$V_{DS(SR),MAX} = \frac{\sqrt{2} \cdot V_{IN,MAX}}{N_{PS}} + V_{O,MAX} + V_{SPIKE}$$

Where  $V_{\rm IN,MAX}$  is maximum AC input voltage,  $N_{PS}$  is the primary/secondary turns ratio of transformer,  $V_{\rm O,MAX}$  is maximum output voltage and  $V_{\rm SPIKE}$  is the voltage spike generated when primary MOS is turned on.

Maximum peak current of SR MOS is calculated as equation below:

$$I_{\text{D(SR),MAX}} = I_{\text{PK,MAX}} \cdot N_{\text{PS}}$$

Where  $I_{PK,MAX}$  is the maximum primary peak current at  $V_{BUS,MIN}$  and OCP point.

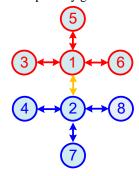

# **Layout Considerations**

A proper PCB design must follow below guidelines:

(a) To achieve good EMI performance and to reduce the line frequency voltage ripples, the output of the bridge rectifier should be connected to the BUS capacitor first, then to the switching circuit.

(b) The loop of all switching circuit should be kept as small as possible: primary power loop, secondary power loop and auxiliary power loop.

(c) The connection of primary ground is recommended as:

Ground (1): Ground of BUS capacitor

Ground ②: Ground of primary IC (SY5033A)

Ground ③: Ground node of auxiliary winding

Ground 4: Ground node of VSEN pin resistor divider

Ground ⑤: Ground of primary side Y capacitor

Ground 6: Ground of current sense resistor

Ground ⑦: Ground of VCC pin capacitor

Ground **③**: Ground of receiver of opto-coupler.

- (d) Bias supply trace should be connected to the bias supply capacitor first and then to the GND pin. The bias supply capacitor should be put right beside the IC.

- (e) The ceramic capacitor C3 should be mounted as close as possible to IC's VCC and GND pin.

- (f) The resistor divider connected to VSEN pin is recommended to be put close to the IC.

# Design Example of 65W Quick Charger

A design example of typical application is shown below step by step.

### Input/output specification

| Parameter            | Symbol           | Value                           |

|----------------------|------------------|---------------------------------|

| Input voltage range  | $V_{ m IN}$      | 90~264Vac                       |

| AC input frequency   | $f_{AC}$         | 50Hz                            |

| Rated output power   | Po               | 65W                             |

| PDO output           | Vo               | 5V/3A, 9V/3A, 15V/3A, 20V/3.25A |

| Output OVP threshold | $V_{O,OVP}$      | 24V                             |

| OCP proportion       | K <sub>OCP</sub> | 130%                            |

### Preset parameter

| Parameter                                          | Symbol                  | Value                       |

|----------------------------------------------------|-------------------------|-----------------------------|

| Break down voltage of power MOS                    | V <sub>MOS,BR</sub>     | 650V                        |

| V <sub>DS</sub> de-rating factor of power MOS      | K <sub>DR</sub>         | 90%                         |

| Spike on V <sub>DS</sub> during power MOS turn off | $\Delta { m V}_{ m SN}$ | 80V                         |

| Converter efficiency                               | η                       | 88%                         |

| Primary current ripple factor                      | $K_{RP}$                | 0.4                         |

| Voltage ripple on BUS capacitor                    | $\Delta V_{ m BUS}$     | 63V                         |

| Input high line condition threshold                | V <sub>IN,H</sub>       | 180Vac                      |

| Transformer effective cross-sectional area         | AE                      | 96.6 mm <sup>2</sup> (RM10) |

| Voltage spike on SR MOS                            | VSPIKE                  | 7V                          |

## 1) BUS capacitor selection

Voltage ripple on BUS capacitor is set to: AV\_BUS=63V

$$C_{BUS} = \frac{P_{O}}{\eta \cdot \pi \cdot f_{AC} \cdot \Delta V_{BUS}} \cdot \frac{\arcsin(1 - \frac{\Delta V_{BUS}}{\sqrt{2} \cdot V_{IN,MIN}}) + \frac{\pi}{2}}{2\sqrt{2} \cdot V_{IN,MIN} - \Delta V_{BUS}} = \frac{65}{88\% \times 3.14 \times 50 \times 63} \cdot \frac{\arcsin(1 - \frac{63}{\sqrt{2} \times 90}) + \frac{\pi}{2}}{2\sqrt{2} \times 90 - 63} = 81.8 \text{uF}$$

Select BUS capacitor:  $C_{BO} = 82uF$ Minimum BUS voltage:

$$V_{\text{BUS,MIN}} = \sqrt{2} \cdot V_{\text{IN,MIN}} - \Delta V_{\text{BUS}} = \sqrt{2} \times 90 - 63 = 64V$$

# 2) Transformer design

(a) Calculate primary/secondary turns ratio: N<sub>PS</sub>

Maximum output voltage: V<sub>O,MAX</sub>=20V

$$N_{PS} \le \frac{V_{MOS,BR} \cdot K_{DR} - \sqrt{2}V_{IN,MAX} - \Delta V_{SN}}{V_{O,MAX}} = \frac{650 \times 0.9 - \sqrt{2} \cdot 264 - 80}{20} = 6.58$$

$N_{PS}$  is selected to:  $N_{PS} = 6$

(b) Calculate maximum duty cycle D<sub>MAX</sub> at minimum BUS voltage and rated output power condition

$$D_{MAX} = \frac{N_{PS} \cdot V_{O,MAX}}{V_{BUS,MIN} + N_{PS} \cdot V_{O,MAX}} = \frac{6 \times 20}{64 + 6 \times 20} = 65.2\%$$

(c) Calculate primary inductance: L<sub>M</sub>

$$L_{M} = \frac{V_{BUS,MIN}^{2} \cdot D_{MAX}^{2} \cdot \eta}{2 \cdot P_{O} \cdot f_{SW} \cdot K_{RP}} = \frac{64^{2} \times 65.2\%^{2} \times 88\%}{2 \times 65 \times 65k \times 0.4} = 453.3uH$$

(d)Calculate primary peak current at minimum BUS voltage and rated output power condition:

$$\begin{aligned} & L_{\text{M}} = \frac{1}{2 \cdot P_{\text{O}} \cdot f_{\text{SW}} \cdot K_{\text{RP}}} = \frac{1}{2 \times 65 \times 65 \text{k} \times 0.4} = 453.5 \text{ur} \\ & \text{Select } L_{\text{M}} = 450 \text{uH} \\ & \text{Iculate primary peak current at minimum BUS voltage and rated output power condition:} \\ & I_{\text{PK}} = \frac{P_{\text{O}}}{V_{\text{BUS,MIN}} \cdot D_{\text{MAX}} \cdot \eta} + \frac{V_{\text{BUS,MIN}} \cdot D_{\text{MAX}}}{2 \cdot L_{\text{M}} \cdot f_{\text{SW}}} = \frac{65}{64 \times 65.2\% \times 88\%} + \frac{64 \times 0.652}{2 \times 450 \text{u} \times 65 \text{k}} = 2.48 \text{A} \\ & \text{Iculate primary winding turns: } N_{\text{P}} \\ & \text{Transformer core effective cross-sectional area: } A_{\text{E}} = 96.6 \cdot 10^{-6} \, \text{m}^2 \\ & \text{Maximum allowed flux density at rated output power: } B_{\text{MAX}} = 0.27 \text{T} \end{aligned}$$

(e)Calculate primary winding turns: N<sub>P</sub>

$$V_{\text{BUS,MIN}} \cdot D_{\text{MAX}} \cdot \eta \qquad 2 \cdot L_{\text{M}} \cdot f_{\text{SW}} \qquad 64 \times 65.2\% \times 88\% \qquad 2 \times 450\text{u} \times 65\text{k}$$

leulate primary winding turns:  $N_{\text{P}}$  Transformer core effective cross-sectional area:  $A_{\text{E}} = 96.6 \cdot 10^{-6} \, \text{m}^2$  Maximum allowed flux density at rated output power:  $B_{\text{MAX}} = 0.27\text{T}$

$$N_{\text{P}} = \frac{L_{\text{M}} \cdot I_{\text{PK}}}{B_{\text{MAX}} \cdot A_{\text{E}}} = \frac{450\text{u} \times 2.48}{0.27 \times 96.6 \times 10^{-6}} = 42.8$$

Select primary winding turns:  $N_{\text{P}} = 42$  alculate secondary winding turns:  $N_{\text{S}} = \frac{N_{\text{P}}}{N_{\text{PS}}} = \frac{42}{6} = 7$  Select secondary turns:  $N_{\text{S}} = 7$  falculate auxiliary winding turns:  $N_{\text{A}} = 7$

(f) Calculate secondary winding turns: N<sub>S</sub>

$$N_S = \frac{N_P}{N_{PS}} = \frac{42}{6} = 7$$

(g) Calculate auxiliary winding turns: NA

Minimum VCC pin voltage is set to: V<sub>CC(AUX)</sub>=10V

$$N_A = \frac{V_{CC(AUX)} \cdot N_S}{V_{O,MIN}} = \frac{10 \times 7}{3.3} = 21.2$$

Select auxiliary winding turns: N<sub>A</sub>=21

Note: Auxiliary winding turns should be fine-tuned according to actual VCC pin voltage under minimum output voltage and no-load condition

(h) If other transformer core type is selected, then re-calculate (e) $\sim$ (g).

### 3) Current sense resistor calculation:

(a)Calculate duty cycle under minimum input voltage (maximum BUS voltage): Docp

$$D_{OCP} = \frac{N_{PS} \cdot V_{O,MAX}}{\sqrt{2} \cdot V_{IN,MIN} + N_{PS} \cdot V_{O,MAX}} = \frac{6 \times 20}{\sqrt{2} \times 90 + 6 \times 20} = 48.5\%$$

(b)Calculate primary side peak current at OCP point: IPK,MAX

$$I_{PK,MAX} = \frac{P_{O} \cdot K_{OCP}}{\sqrt{2} \cdot V_{IN,MIN} \cdot D_{OCP} \cdot \eta} + \frac{\sqrt{2} \cdot V_{IN,MIN} \cdot D_{OCP}}{2 \cdot L_{M} \cdot f_{SW}} = \frac{65 \times 130\%}{\sqrt{2} \times 90 \times 48.5\% \times 88\%} + \frac{\sqrt{2} \times 90 \times 48.5\%}{2 \times 450u \times 65k} = 2.61A$$

(c)Calculate current sense resistor: R<sub>ISEN</sub>

$$R_{ISEN} = \frac{V_{ISEN,MAX}}{I_{PK\ MAX}} = \frac{0.5}{2.61} = 0.192\Omega$$

repated for Meilli Note: ISEN pin current sense resistor R<sub>ISEN</sub> should be fine-tuned according to the actual OCP point.

### 4) Secondary SR MOS selection

(a) Maximum reverse voltage calculation:

$$V_{DS(SR),MAX} = \frac{\sqrt{2} \cdot V_{IN,MAX}}{N_{ps}} + V_{O,MAX} + V_{SPIKE} = \frac{\sqrt{2} \times 264}{6} + 20 + 7 = 89.2V$$

Considering voltage derating, SR MOS with 100V rating is recommended.

(b)Maximum instantaneous SR MOS current:

$$I_{D(SR),MAX} = N_{PS} \cdot I_{PK,MAX} = 6 \times 2.61 = 15.7A$$

### 5) Calculate VSEN pin resistor divider

(a) Firstly, calculate VSEN pin upper resistor: R<sub>H</sub>

Predefined input voltage high line condition threshold: V<sub>IN.H</sub>=180Vac

$$R_{H} = \frac{\sqrt{2} \cdot V_{IN,H}}{I_{IN,H}} \cdot \frac{N_{A}}{N_{P}} = \frac{\sqrt{2} \cdot 180}{300u} \cdot \frac{21}{42} = 424.3k\Omega$$

Select  $R_H=420k\Omega$

(b) After R<sub>H</sub> is determined, then calculate lower resistor R<sub>L</sub>:

$$R_{L} = \frac{1}{\frac{V_{O,OVP}}{V_{VSEN,OVP}} \cdot \frac{N_{A}}{N_{S}} - 1} \cdot R_{H} = \frac{1}{\frac{24}{2} \cdot \frac{21}{7} - 1} \cdot 420k = 19.4k\Omega$$

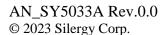

# SO8 Package outline & PCB layout design

Notes: All dimension in millimeter and exclude mold flash & metal burr.

# **Taping & Reel Specification**

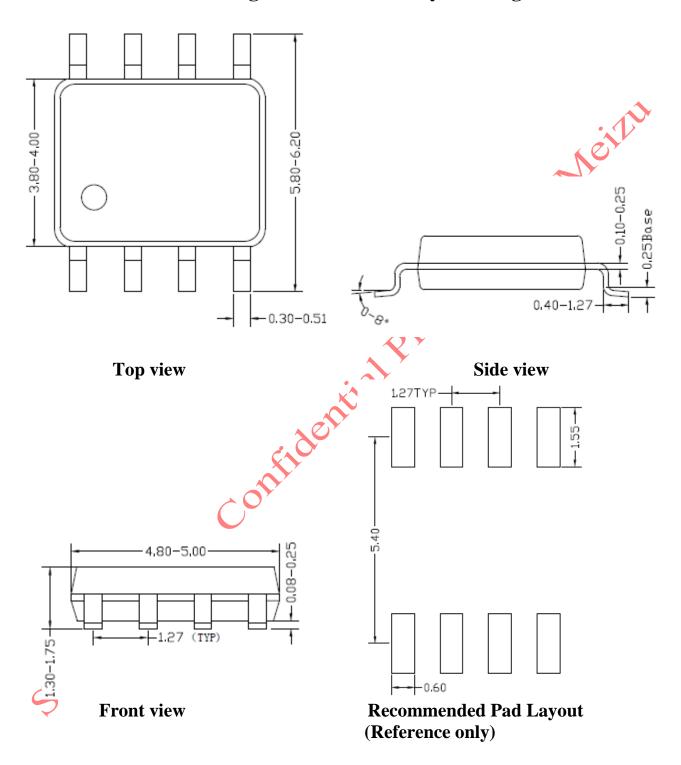

# 1. Taping orientation for packages (SO8)

Feeding direction ——

# 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|-----------------|-----------------|---------------------|---------------------|-----------------------|--------------------|-----------------|

| SOS             | 12              | 8                   | 13"                 | 400                   | 400                | 2500            |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Silergy manufacturer:

Other Similar products are found below:

FAN53610AUC33X FAN53611AUC123X EN6310QA 160215 R3 KE177614 FAN53611AUC12X MAX809TTR NCV891234MW50R2G

AST1S31PUR NCP81203PMNTXG NCP81208MNTXG PCA9412AUKZ NCP81109GMNTXG NCP3235MNTXG NCP81109JMNTXG

NCP81241MNTXG NTE7223 NTE7222 NTE7224 L6986FTR MPQ4481GU-AEC1-P MP8756GD-P MPQ2171GJ-P MPQ2171GJ-AEC1-P

NJW4153U2-A-TE2 MP2171GJ-P MP28160GC-Z MPM3509GQVE-AEC1-P XDPE132G5CG000XUMA1 LM60440AQRPKRQ1

MP5461GC-P IW673-20 NCV896530MWATXG MPQ4409GQBE-AEC1-P S-19903DA-A8T1U7 S-19903CA-A6T8U7 S-19903CA

S8T1U7 S-19902BA-A6T8U7 S-19902CA-A6T8U7 S-19902AA-A6T8U7 S-19903AA-A6T8U7 S-19902AA-S8T1U7 S-19902BA-A8T1U7

AU8310 LMR23615QDRRRQ1 LMR33630APAQRNXRQ1 LMR33630APCQRNXRQ1 LMR36503R5RPER LMR36503RFRPER