# **Application Note: SY5238**

ZVS Flyback SR Controller Advanced Design Specification

### **General Description**

SY5238 is a Flyback SR controller compatible with QR IC to achieve ZVS operation. The primary side PWM IC must work in quasi resonant mode. SY5238 adopts proprietary operation mode to achieve flyback ZVS turn on, which greatly improves Flyback efficiency and power density. SY5238 also adopts adaptive gate voltage control for safe operation.

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY5238DGD       | DFN2*3-8     |      |

### **Features**

- Proprietary Operation Mode for Flyback ZVS

- High Efficiency, High Power Density

- Adaptive Gate Voltage Control

- Slope Detection to Prevent SR False Trigger

- 130V DSEN Pin to Directly Sense DRAIN Voltage of SR MOS

- Power Saving Mode to Improve Light Load Efficiency

- Dual Channel Supply for Applications with very Low Output Voltage

### **Applications**

- USB PD, Fast Charger

- Adaptor

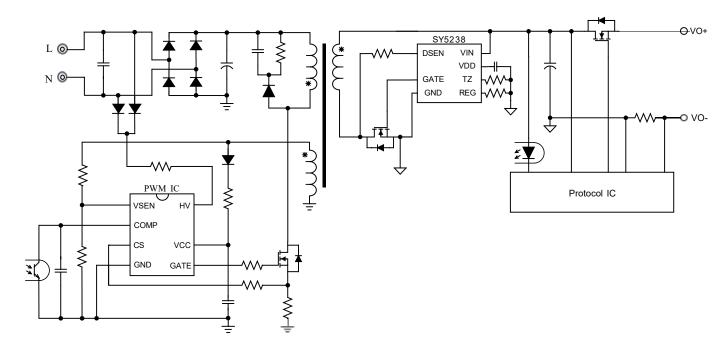

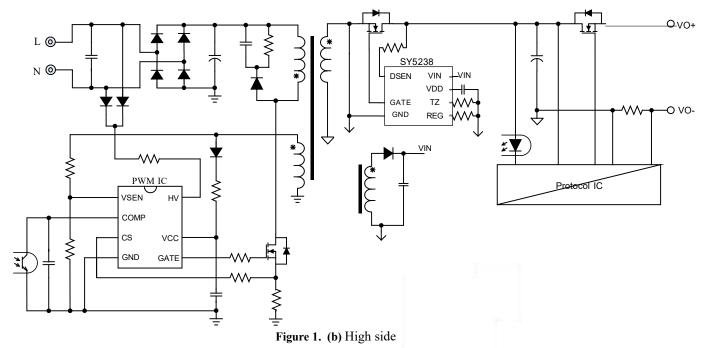

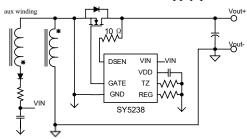

### **Typical Applications**

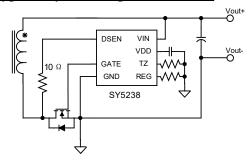

Figure 1. (a) Low side

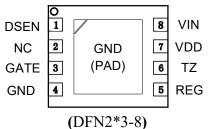

## Pinout (top view)

Top Mark: W7 xyz (device code: W7, x=year code, y=week code, z=lot number code)

| Pin number | Pin Name                           | Pin Description                                |

|------------|------------------------------------|------------------------------------------------|

| 1          | DSEN                               | drain sense input                              |

| 2          | NC                                 | Not connected                                  |

| 3          | GATE                               | Gate drive pin                                 |

| 4          | GND                                | Ground pin                                     |

| 5          | REG                                | Turn on slope threshold set for SR operation   |

| 6          | TZ                                 | Connect a resistor to program ZVS coefficient. |

| 7          | VDD                                | Power supply pin                               |

| 8          | VIN Low voltage power supply input |                                                |

| 9          | 9 GND Ground pin                   |                                                |

# Absolute Maximum Ratings (Note1)

| DSEN                                              | 0.3V ~ 130V          |

|---------------------------------------------------|----------------------|

| VIN                                               | 0.3V ~ 30V           |

| VDD                                               | $0.3V \sim 20V$      |

| GATE                                              | 0.3V $\sim$ VDD+0.3V |

| TZ, REG                                           | 0.3V ~ 4V            |

| Power Dissipation, @ T <sub>A</sub> = 25°C DFN2x3 | 1W                   |

| Package ThFeNrmxat,R098i-s-t-40-c-04No-t-e2)      |                      |

| 4.00C/W                                           |                      |

| 46°C/W<br>DFN2x3, θ <sub>JC</sub>                 | 28°C/W               |

| Maximum Junction Temperature                      | 150°C                |

| Lead Temperature (Soldering, 10 sec.)             |                      |

| Storage Temperature Range                         |                      |

**Electrical Characteristics** (V<sub>IN</sub> = 12V (Note 3), T<sub>A</sub> = 25°C unless otherwise specified)

| $V_{IN} = 12V$ (Note 3), $I_A = 25$ °C Parameter            | Symbol                   | Test Conditions                                | Min | Тур   | Max | Unit |

|-------------------------------------------------------------|--------------------------|------------------------------------------------|-----|-------|-----|------|

| VDD Pin                                                     |                          |                                                |     |       |     | 1    |

| VDD ON Threshold                                            | V <sub>DD_ON</sub>       |                                                |     | 3     |     | V    |

| UVLO Hysteresis                                             | $V_{DD\_HYS}$            |                                                |     | 160   |     | mV   |

| VDD Regulation Voltage when VIN Pin is Active to Supply IC  | V <sub>DD_REG_</sub> VIN |                                                |     | 9     |     | V    |

| VDD Regulation Voltage when DSEN Pin is Active to Supply IC | V <sub>DD_REG_DSEN</sub> | V <sub>DSEN</sub> =100V                        |     | 5     |     | V    |

|                                                             |                          | V <sub>DD</sub> =9V, C <sub>GATE</sub> =2.2nF, |     | 4.9   |     | mA   |

| Operating Current                                           | IDD_OP                   | Vsbwb=25V0,kHzCgate=2.2nF,<br>Fsw=200kHz       |     | 3.1   |     | mA   |

| Quiescent Current                                           | I <sub>DD_</sub> STBY    | Under Standby Mode                             |     | 160   |     | uA   |

| VIN Pin                                                     |                          |                                                |     |       |     |      |

| Threshold of Switching to VIN Supply Channel                | V <sub>IN_INSPY</sub>    | V <sub>IN</sub> is rising                      |     | 4.8   |     | V    |

| Threshold of Switching to DSEN Supply Channel               | V <sub>IN_ DSENSPY</sub> | VIN is falling                                 |     | 4.7   |     | V    |

| REG Pin                                                     |                          |                                                |     |       |     |      |

| Resistor to Program Drain                                   | D                        | Rreg=50k                                       |     | 80    |     | ns   |

| Falling Slope to enable SR                                  | R <sub>REG</sub>         | Rreg=300k                                      |     | 155   |     | ns   |

| TZ Pin                                                      |                          |                                                |     |       |     |      |

| ZVS Time Program Coefficient                                | <b>k</b> tz              |                                                |     | 4.5   |     | 10-9 |

| Operating Voltage Range                                     |                          |                                                |     |       |     |      |

| DSEN Pin                                                    | V <sub>DSEN_OP</sub>     |                                                |     |       | 110 | V    |

| SR Turn on Threshold                                        | V <sub>DS_ON</sub>       |                                                |     | - 100 |     | mV   |

| V <sub>DSEN</sub> Regulation Voltage                        | V <sub>DS_REG</sub>      |                                                |     | -35   |     | mV   |

| SR Turn off Threshold                                       | V <sub>OFF_TH</sub>      |                                                |     | 10    |     | mV   |

| Time Threshold to Trigger Sleep Mode                        | T <sub>TH_</sub> SLP     |                                                |     | 70    |     | us   |

| GATE pin                          |                        |                               |     |     |  |    |

|-----------------------------------|------------------------|-------------------------------|-----|-----|--|----|

| Max. Source Current               | Isource_ max           | CLOAD=2.2nF,Vgs from 1V to 6V | 0.5 |     |  | A  |

| Max. Sink Current                 | I <sub>SINK_ MAX</sub> | Cload=2.2nF,Vgs from 6V to 1V | 1.3 |     |  | A  |

| SR Minimum ON Time                | T <sub>ON_MIN</sub>    |                               |     | 600 |  | ns |

| SR Minimum OFF Time               | T <sub>OFF_MIN</sub>   |                               |     | 600 |  | ns |

| Turn on Delay                     | TDELAY_ ON             | CGATE=2.2nF                   |     | 20  |  | ns |

| Turn off Delay                    | TDELAY_ OFF            | CGATE=2.2nF                   |     | 20  |  | ns |

| ОТР                               |                        |                               |     |     |  |    |

| Thermal Shutdown Temperature      | $T_{SD}$               |                               |     | 150 |  | °C |

| Hysteresis to Resume<br>Operating | Totp_hys               |                               |     | 20  |  | °C |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause perm anent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Note 2: θ<sub>JA</sub> is measured in the natural convection at T<sub>A</sub> = 25°C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

### **Operation Principles**

#### Introduction

The SY5238 is a Flyback SR with proprietary operation mode to achieve flyback ZVS. It supports primary side PWM IC with QR mode, and the maximum valley numbers to turn on must >6. To ensure safety operation, SR control includes turn on/off control, Vds regulation, slope program, etc. The ZVS control logic helps primary side FET turning on at ~0V to reducing switching losses to maximize system efficiency and achieve high power density.

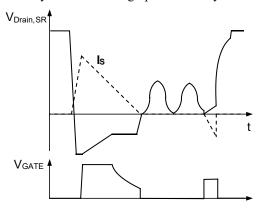

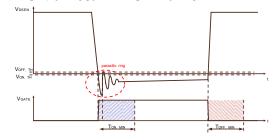

Fig. 1 SR operation diagram

### **SR Turn On**

Traditional method is to set a SR MOSFET turn on threshold Von TH, when DSEN voltage is falling and down to Von TH, then turn on SR MOSFET after a short delay as shown. However, under DCM or QR operating mode, after secondary current decrease to ZERO, a resonant waveform will appear. Sometimes, the amplitude of this resonant waveform can be large enough, which will cause DSEN voltage drops below turn on threshold Von TH. SR MOSFET may be falsely turned on by parasitic resonant.

To solve the above issue, V<sub>DSEN</sub> falling slope rate is detected. When primary MOSFET is turned off, V<sub>DSEN</sub> falling slope rate is very high, SR will turn on; while during resonant phase, VDSEN falling slope rate is relatively low, SR will not turn on.

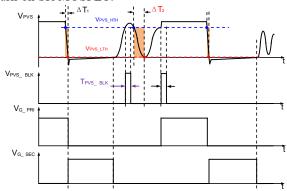

SY5238 use resistor divide circuit to sense the DSEN voltage, the V<sub>PVS</sub> is 0.02 times of V<sub>DSEN</sub>. It set 2 thresholds to indirectly sense V<sub>PVS</sub> falling slope rate, the  $V_{PVS}$  is the time duration ( $\Delta t$ ) when  $V_{PVS}$  is falling between high-level threshold VPVS\_HTH and low-level

threshold V<sub>DSEN LTH</sub> (0mV) is measured, and the falling time duration ( $\triangle t$ ) will be compared with a falling slope ref time threshold T<sub>REF</sub>.

To prevent external noise (for example: ESD noise) false turn on SR MOSFET by making fast V<sub>DSEN</sub> falling slope rate, the DSEN blanking time is adopt. V<sub>PVS</sub> is the resistor divide voltage of V<sub>DSEN</sub>. If V<sub>PVS</sub> is above V<sub>PVS HTH</sub> and lasting for T<sub>PVS BLK</sub> (200nS) and falling slope time  $\Delta t < T_{REF}$ , IC considers this action as primary MOSFET turn off event and then turn on SR MOSFET after a short delay. Otherwise, IC will not turn on SR MOSFET.

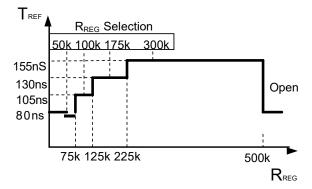

Fig. 2 Time diagram of SR enable strategy V<sub>PVS HTH</sub> is a dynamically adjusted value, it is 0.85 times of DSEN high-level voltage value. The falling slope ref time threshold T<sub>REF</sub> is controlled by REG resistor as below.

| T <sub>REF</sub> setting has 4 steps: |              |                                |  |  |

|---------------------------------------|--------------|--------------------------------|--|--|

| Step                                  | $T_{ m REF}$ | $R_{ m REG} \ ( { m k}\Omega)$ |  |  |

| 1                                     | 80ns         | 50                             |  |  |

| 2                                     | 105ns        | 100                            |  |  |

| 3                                     | 130ns        | 175                            |  |  |

| 4                                     | 155ns        | 300                            |  |  |

Fig. 3 Programmable curve of falling slope ref

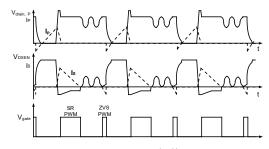

#### **SR Gate Control**

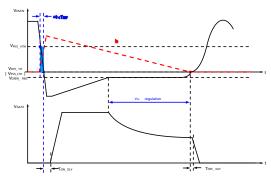

After primary side FET turn off, the inductor current freewheels in SR, the current decreases linearly. When  $V_{DS}$  drops to  $V_{DS\_REG}(-35 \text{mV})$ , the closed loop  $V_{DS}$ regulation circuit will gradually decrease V<sub>GATE</sub> to maintain the  $V_{DS}$  above  $V_{DS\ REG}$ . As SR current becomes smaller, V<sub>GATE</sub> drops near the SR MOSFET turn off threshold, ID\*RDSON cannot be regulated to V<sub>DS\_REG</sub> anymore, V<sub>DS</sub> will increase higher than  $V_{\text{DS}\ \text{REG}}$  . If  $V_{\text{DS}}$  rises and cross  $V_{\text{OFF}\ \text{TH}},$  after a short delay time Toff DLY, GATE voltage will be pulled down to 0V by a large sink current to turn off SR MOSFET.

Fig. 4 SR gate control diagram

#### Min ON time& min OFF time

internal logic circuit false action, a blanking time Toff\_MIN is also applied. During Toff\_MIN, the SR logic can't begin a new switching cycle and the normal gate drive not allowed turning on.

#### **ZVS Operation**

The key function of SY5238 is achieving primary MOS ZVS turn on for high efficiency and high power density. SY5238 is compatible with primary side QR IC to achieve this function.

SY5238 adopts proprietary drive method to increase resonation magnitude of switching node, which pulls  $V_{Drain, P}$  to approximately ~50 V to achieve primary side MOSFET ZVS turns on. The ZVS PWM only active in QR mode within 6 valleys, beyond this range, the ZVS is disabled.

Fig. 6 ZVS control diagram

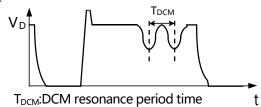

### ZVS coefficient R<sub>TZ</sub> setting

The ZVS performance is affected by transformer's magnetizing inductance (Lm) and the total equivalent capacitance (Csw) of switching node. To tune the best operation efficiency, the resistor value of TZ pin to GND can be adjusted. The resistor set ZVS PWM turn on time coefficient; it is chose as follows.

$$R_{TZ} = \frac{\sqrt{c_{SW} \times L_m}}{4.5 \times 10^{-9}} (k\Omega)$$

method 1, calculate coefficient base on magnetizing inductance and equivalent switching node capacitance capacitor.

$$R_{TZ} = \frac{T_{DCM}}{2\pi} \frac{1}{4.5 \times 10^{-9}} (k\Omega)$$

method 2, calculate coefficient base on DCM resonance period time

The resistor can be adjusted slightly around the calculated value. The resistance range is preferred to be  $20k\Omega$ - $60k\Omega$ , if it is  $<10k\Omega$  or  $>100k\Omega$  range, the ZVS function is disabled.

#### ZVS enable condition

- 1. Power supply: when VIN supply is active, ZVS is enabled. When DSEN supply is active, the ZVS is disabled. (DSEN pin supply power loss is much higher, the extra driving loss may be greater than ZVS affect)

- 2. Input voltage condition: at low line input, the ZVS has little efficiency improvement. So the input voltage range is limited to maximize ZVS effect. Input voltage condition calculation is shown as below with hysteresis:

ZVS enable:  $VIN > N(0.333 \cdot V_{OUT} + 26.5V)$ ZVS disable:  $VIN < N(0.333 \cdot V_{OUT} + 21.5V)$

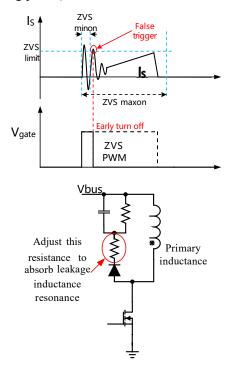

#### **ZVS** protection

To guarantee ZVS logic working correctly, the maximum ZVS on time is limited to 2.5us, so the primary side IC QR detecting timeout time must be greater than 2.5us+Treso. (Treso is the DCM resonating period).

Fig. 7 ZVS limit protection

To prevent ZVS current is to big or primary false turn on, secondary current is limited during ZVS. But primary leakage inductance resonance may trigger ZVS limit, cause ZVS PWM turn off early, add primary inductance resonance absorb resistance is recommend.

#### ZVS performance adjust

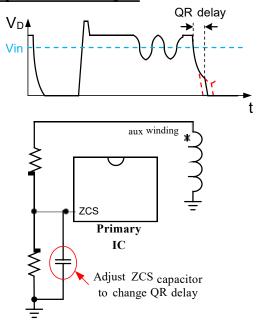

Fig. 8 adjust ZVS performance

To achieve best ZVS performance, primary IC QR delay need slightly adjust. Consider primary IC turn on at DCM resonance valley is the best.

#### **Dual Channel Power Supply**

When the output voltage is as low as 3V, which is not high enough to drive the SR MOSFET, the DSEN pin supply is preferred. When the output voltage is high, the power supply efficiency of DSEN pin is lower than VIN pin, the VIN pin supply is preferred.

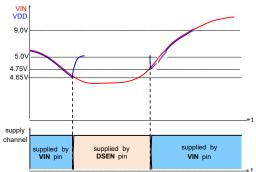

Fig.9 Timing diagram of dual channel supply SY5238 adopts dual channel power supply. Before VDD voltage reaches ON threshold V<sub>VDD</sub> on, SY5238

7

is supplied by DSEN pin. As V<sub>DD</sub> rises and reach ON threshold, VIN pin voltage will be monitored. If VIN voltage is higher than V<sub>IN INSPY</sub>, then power supply channel will switch to VIN pin. As VIN increase higher, VDD will follow  $V_{\rm IN}$  (with about 0.5V voltage drop), finally VDD will be clamped to 9V. As VIN is decreasing and crossing V<sub>DSEN\_VINSPY</sub>, then the power supply channel will switch to DSEN pin and  $V_{\text{DD}}$  will be regulated to 5V. Timing diagram is shown in Fig. 9.

#### **Power Saving Mode**

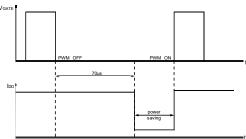

Under light load conditions, SY5238 will enter power saving mode to improve light load efficiency.

During each switching cycle, after SR MOSFET is turned off, a timer will start to count, if the timer has counted to 70us before next SR turn on instant, IC will enter power saving mode, and reduce the power consumption. IC will exit power saving mode by SR MOSFET turn on event.

Fig. 10 timing diagram of power saving mode

#### **OTP**

IC die temperature is always monitored, if the die temperature rises above 150°C, IC will stop driving SR MOS and keep GATE voltage to 0V. When temperature drops below 130°C, IC die will resume normal operating again.

### **Application Information**

#### **Typical System Implementations**

Low side Rectification with Vout supply power

High side Rectification with aux winding supply power

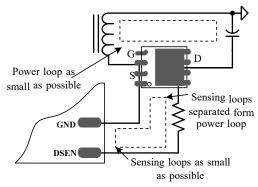

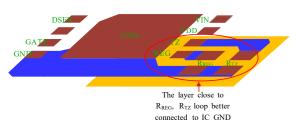

#### Layout Guideline Sensing for DSEN/GND

- 1. Make the sensing connection (DSEN/GND) as close as possible to the MOSFET (drain/source).

- Keep the IC out of the power loop to prevent the 2. sensing loop and power loop from interrupting each

- (a) To achieve better EMI and Efficiency performance, the output connector should be connected to the output cap first, then to the SR Power pin.

- (b) The circuit loop of all switching circuit should be kept small: secondary power loop, secondary RC snubber circuit loop and IC power supply loop.

(c) Due to the high resistance on REG and TZ pin, the layout size and length of each loop should be as small as possible. Meanwhile, the layer directly under these two loops better connected to IC GND to shield switching noise.

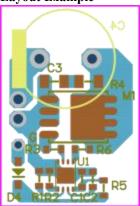

Low side SR layout @bottom view

#### Layout Example

High side SR layout @bottom view

## **Design Notice**

- To achieve better EMI performance and reduce secondary rectifier loss, the circuit loop of secondary winding terminal, the output cap and SR MOSFET should be short. GND pin should be connected to Source of SR MOSFET shortly.

- 2.

- DSEN pin should be connected to Drain of SR MOSFET shortly.

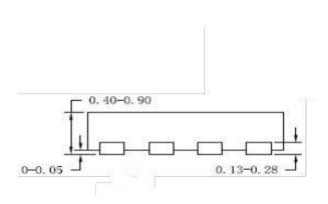

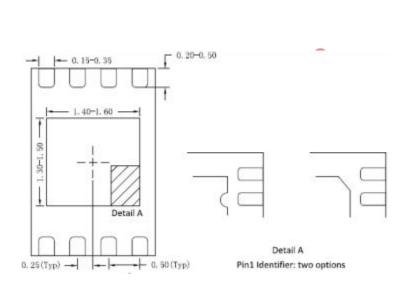

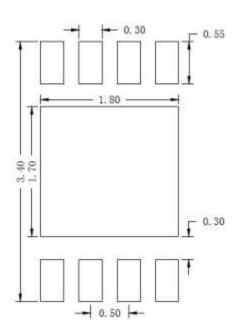

# DFN2x3-8 Package Outline

**Top View**

**Side View**

**Bottom View**

**Recommended PCB layout** (Reference only)

**Notes:** All dimension in millimeter and exclude mold flash & metal burr.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Silergy manufacturer:

Other Similar products are found below:

FAN53610AUC33X FAN53611AUC123X EN6310QA 160215 R3 KE177614 FAN53611AUC12X MAX809TTR AST1S31PUR

NCP81103MNTXG NCP81203PMNTXG NCP81208MNTXG PCA9412AUKZ NCP81109GMNTXG NCP81109JMNTXG MP2161AGJ-Z

NCP81241MNTXG MPQ4481GU-AEC1-P MP8756GD-P MPQ2171GJ-P MPQ2171GJ-AEC1-P MP2171GJ-P NCV1077CSTBT3G

MP28160GC-Z MPM3509GQVE-AEC1-P XDPE132G5CG000XUMA1 MP5461GC-P IR3888AMTRPBFAUMA1 MPQ4409GQBE-AEC1-P S-19903DA-A8T1U7 S-19903CA-A6T8U7 S-19903CA-S8T1U7 S-19902BA-A6T8U7 S-19902CA-A6T8U7 AP7361EA-SPR-13

AP7361EA-33DR-13 S-19902AA-A6T8U7 S-19903AA-A6T8U7 S-19902AA-S8T1U7 S-19902BA-A8T1U7 AU8310 LMR36503R5RPER

LMR36503RFRPER LMR54406DBVR XC9110C301MR-G XC9141A50CMR-G XCL206F083CR-G XCL210A111GR-G

LTM4663EV#PBF LD5537B1GL