**Application Notes: AN\_SY7060**

Typical 0.7V minimum input voltage

18uA quiescent current

Adjustable output voltage from 1.8V to

Pass-through function during shutdown

Low R<sub>DS(ON)</sub> (main switch/synchronous

switch) at 3.3V output: 0.45/0.80ohm

Output over-voltage protection

#### 0.7V Minimum Input and 5.25V Maximum Output Synchronous Boost Converter

**Features**

5.25V

# **General Description**

SY7060 is a high efficiency, low input voltage, stepup synchronous boost converter designed for singlecell or dual-cell alkaline, NiMH, or NiCd batterypowered applications. It can receive an input voltage as low as 0.7V. It adopts NMOS for the main switch and PMOS for the synchronous switch.

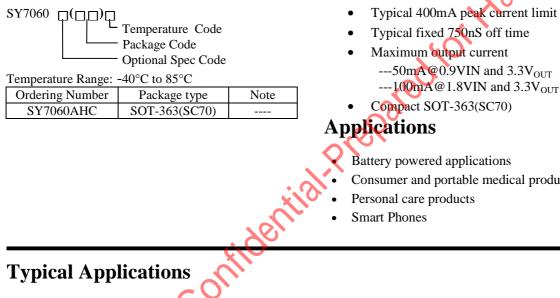

### **Ordering Information**

Ľ1 6.8uH

LX

OUT

FB

Figure 1. Schematic Diagram

$R_2$

1ΜΩ

R<sub>1</sub> 181kC

IN

ΕN

GND

Battery powered applications

V<sub>OUT</sub>: 3.3V

$C_4$

22uF/6.3V

Consumer and portable medical products

V<sub>IN</sub>. 0.7~3∨

C<sub>2</sub> <u>-</u> 10uF/6.3V

K

R<sub>3</sub>

1MΩ

IN 1 6 EN FB 2 5 LX GND 3 4 OUT

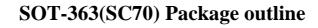

(SOT-363)

Top mark: GYxyz (Device code: GY, x=year code, y=week code, z= lot number code)

| Pin Name      | Pin Number    | Pin Description                                                 |

|---------------|---------------|-----------------------------------------------------------------|

| P III INallie | PIII Nullibel | Pin Description                                                 |

| IN            | 1             | Input pin. Decouple this pin to GND pin with 4.70F ceramic cap. |

|               |               | Feedback pin. Connect a resistor R1 between OUT and FB, and a   |

| FB            | 2             | resistor R2 between FB and GND to program the output voltage.   |

|               |               | $V_{OUT}=0.505V^{*}(R2/R1+1)$                                   |

| GND           | 3             | Ground pin.                                                     |

| OUT           | 4             | Output pin. Decouple this pin to GND pin with two 10uF ceramic  |

|               |               | caps.                                                           |

| LX            | 5             | Inductor node. Connect an inductor between IN pin and LX pin.   |

| EN            | 6             | Enable pin. Pull it high to turn on. Do not float.              |

|               |               |                                                                 |

### Absolute Maximum Ratings (Note)

|                                           | 5.5V          |

|-------------------------------------------|---------------|

| Power Dissipation, PD @ TA = 25°C SOT-363 | 0.6W          |

| Package Thermal Resistance (Note 2)       |               |

| θ JA                                      | 161°C/W       |

| θ.ιc                                      | 130°C/W       |

| Junction Temperature Range                | 125°C         |

| Lead Temperature (Soldering, 10 sec.)     | 260°C         |

| Storage Temperature Range                 | 65°C to 150°C |

|                                           |               |

# Recommended Operating Conditions (Note 3)

| IN.OUT                     | 0.7V to 5.0V                 |

|----------------------------|------------------------------|

| EN                         | 0V to V <sub>OUT</sub> +0.3V |

| All other pins             | 0-5 0V                       |

| Junction Temperature Range | 40°C to 125°C                |

| Ambient Temperature Range  |                              |

| Amount remperature Range   |                              |

sileroy

#### **Electrical Characteristics**

(VIN =1.2V,  $V_{OUT}$ =3.3V,  $I_{OUT}$ =10mA, TA = 25°C unless otherwise specified)

| Parameter                                       | Symbol               | Test Conditions                               | Min   | Тур   | Max      | Unit |

|-------------------------------------------------|----------------------|-----------------------------------------------|-------|-------|----------|------|

| Input Voltage                                   | V <sub>IN</sub>      |                                               | 0.7   |       | 5.0      | V    |

| Minimum V <sub>IN</sub> at start-up             | V <sub>START</sub>   |                                               |       | 0.75  |          | V    |

| Output Voltage Range                            | V <sub>OUT</sub>     |                                               | 1.8   |       | 5.25     | V    |

| Quiescent V <sub>IN</sub>                       | IQ                   | $Io=0mA, V_{EN}=V_{IN}=1.2V,$                 |       | 0.5   | 0.9      | μA   |

| Current V <sub>OUT</sub>                        |                      | $V_{OUT}=3.3V$                                |       | 18    |          |      |

| Shut Down Current                               | I <sub>SHDN</sub>    | $V_{EN}=0V, V_{IN}=1.2V,$                     |       |       | 1        | μA   |

|                                                 |                      | $V_{OUT} > V_{IN}$                            |       |       |          |      |

| EN Rising Threshold                             | V <sub>ENH</sub>     |                                               | 0.7   |       | 4        | V    |

| EN Falling Threshold                            | V <sub>ENL</sub>     |                                               |       |       | 0.3      | V    |

| Low Side Main FET R <sub>ON</sub>               | R <sub>DS(ON)1</sub> | V <sub>OUT</sub> =3.3V                        |       | 0.45  | <u>}</u> | Ω    |

| Synchronous FET R <sub>ON</sub>                 | R <sub>DS(ON)2</sub> | V <sub>OUT</sub> =3.3V                        |       | 0.80  |          | Ω    |

| Main FET Current Limit                          | I <sub>LIM1</sub>    |                                               |       | 400   |          | mA   |

| Reference Voltage                               | V <sub>REF</sub>     |                                               | 0.490 | 0.505 | 0.520    | V    |

| Synchronous FET On Time                         | T <sub>OFF</sub>     |                                               |       | 750   |          | nS   |

| Thermal Shutdown Temperature                    | T <sub>SD</sub>      | .0                                            | 5     | 150   |          | °C   |

| Thermal Shutdown Hysteresis                     | T <sub>HYS</sub>     |                                               |       | 20    |          | °C   |

| Output Over Voltage Protection                  | V <sub>OVP</sub>     | <u>, , , , , , , , , , , , , , , , , , , </u> |       | 6     |          | V    |

| Under Voltage Lockout Threshold<br>For Turn Off | V <sub>UVLO</sub>    | 0184                                          |       | 0.65  |          | V    |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2**:  $\theta$  JA is measured in the natural convection at  $T_A = 25^{\circ}$ C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3: The device is not guaranteed to function outside its operating conditions.

## AN\_SY7060

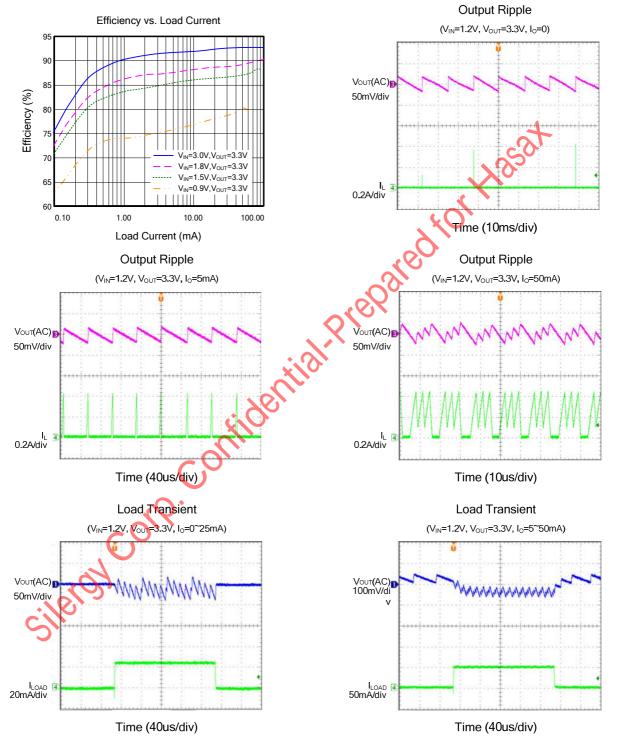

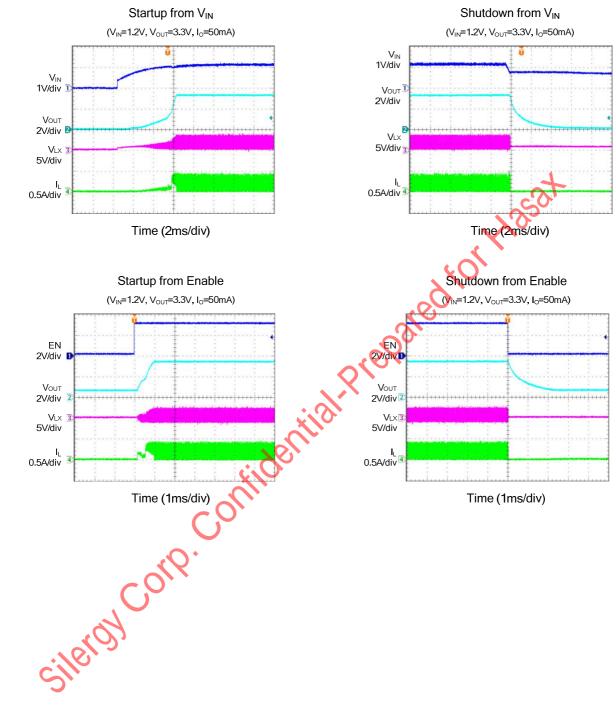

### **Typical Performance Characteristics**

AN\_SY7060 Rev. 0.9 Silergy Corp. Confidential- Prepared for Customer Use Only 4

# AN\_SY7060

### AN\_SY7060

#### **Applications Information**

SY7060 is a high efficiency, low input voltage, step-up synchronous boost converter designed for single-cell or dual-cell alkaline, NiMH, or NiCd battery-powered applications. It adopts NMOS for the main switch and PMOS for the synchronous switch.

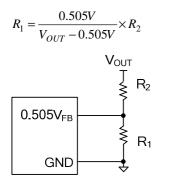

#### Feedback resistor dividers R1 and R2:

Choose R1 and R2 to program the proper output voltage. To minimize the power consumption under light loads, it is desirable to choose large resistance values for both R1 and R2. If  $V_{OUT}$  is 3.3V, R2=1Meg is chosen, using following equation, then R1 can be calculated to be 181k:

#### **Input capacitor CIN:**

To minimize the potential noise problem, place a typical X5R or better grade ceramic capacitor really close to the IN and GND pins. Care should be taken to minimize the loop area formed by CIN, and IN/GND pins. In this case, a 100F low ESR ceramic capacitor is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit.

#### **Output capacitor Cour:**

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. For the best performance, it is recommended to use X5R or better grade ceramic capacitor with 6.3V rating and greater than 10uF capacitance.

#### **Inductor L:**

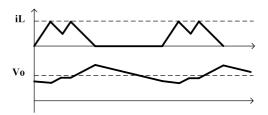

SY7060 controls output voltage directly through FB pin. And the typical peak current limit is about 400mA. If inductor current reaches the peak current limit preset value, IC will turn off the low side FET and turn on the high side FET. After the fixed off time delay, IC will turn off high side FET and turn on low side FET again. If the FB pin voltage reaches the reference voltage, IC will go into sleep mode for the low quiescent current purpose design.

If the inductor is designed large, IC can afford more output current. But the output ripple will be large. So we need to optimize the inductor design for the different cell battery input applications.

For the detailed application schematic, please refer to our BOM list proposal solutions.

#### **Recommended PCB Layout:**

For the best efficiency and minimum noise problems, we should place the following components close to the IC: CIN, COUT, L, R1 and R2.

1) It is desirable to maximize the PCB copper area connecting to GND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

## **SY7060**

OUT

GND

2) COUT must be close to Pins OUT and GND. The loop area formed by COUT and GND must be minimized.

3) The PCB copper area associated with LX pin must be minimized to avoid the potential noise problem.

4) Feedback resistor R1, R2, and the trace connecting to the FB pin must not be adjacent to the LX net on the PCB layout to avoid the noise problem.

5) If the system chip interfacing with the EN pin has a

battery, it is desirable to add a pull down 1Mohm resistor between the EN and GND pins to prevent the noise from falsely turning on the regulator at shutdown mode.

L

IN

GND

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Silergy manufacturer:

Other Similar products are found below :

NCP1218AD65R2G\_NCP1244BD065R2G\_NCP1336ADR2G\_NCP6153MNTWG\_NCP81101BMNTXG\_NCP81205MNTXG\_SJE6600 AZ7500BMTR-E1\_SG3845DM\_NCP1250BP65G\_NCP4204MNTXG\_NCP6132AMNR2G\_NCP81102MNTXG\_NCP81206MNTXG NCP1240AD065R2G\_NCP1240FD065R2G\_NCP1361BABAYSNT1G\_NCP1230P100G\_NX2124CSTR\_SG2845M\_NCP1366BABAYDR2G NCP81101MNTXG\_NCP81174NMNTXG\_NCP4308DMTTWG\_NCP4308AMTTWG\_NCP1366AABAYDR2G\_NCP1251FSN65T1G NCP1246BLD065R2G\_MB39A136PFT-G-BND-ERE1\_NCP1256BSN100T1G\_LV5768V-A-TLM-E\_NCP1365BABCYDR2G NCP1365AABCYDR2G\_NCP1246ALD065R2G\_AZ494AP-E1\_CR1510-10\_NCP4205MNTXG\_XRP6141ELTR-F\_RY8017\_LP6260SQVF LP6298QVF\_ISL6121LIB\_ISL6225CA\_ISL6244HRZ\_ISL6268CAZ\_ISL6315IRZ\_ISL6420AIAZ-TK\_ISL6420AIRZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL6420IAZ\_ISL64