## **General Description**

SILERGY

SY7066 is a high efficiency synchronous boost regulator that converts down to 1.8V input and up to 5.5V output voltage. It adopts NMOS for the main switch and PMOS for the synchronous switch. It can disconnect the output from input during the shutdown mode

### **Ordering Information**

Temperature Range: -40°C to 85°C

| 1 0             |              |      |

|-----------------|--------------|------|

| Ordering Number | Package type | Note |

| SY7066QMC       | QFN2X2-10    |      |

### **Features**

- 1.8V Minimum input voltage

- Adjustable output voltage from 2.5V to 5. 5V

- 6A peak current limit

- Input under voltage lockout

- Load disconnect during shutdown

- Output over voltage protection

- Input battery voltage monitor

- Low R<sub>DS(ON)</sub> (main switch/synchronous switch) at 5.0V output: 25/45mohm

- Compact package: QFN2x2-10

## **Applications**

All Single Cell Li or Dual Cell Battery

Operated Products as MP-3 Player, PDAs, and

Other Portable Equipment.

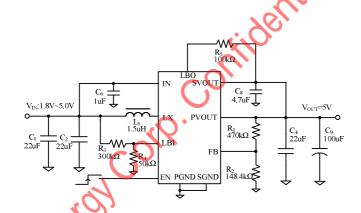

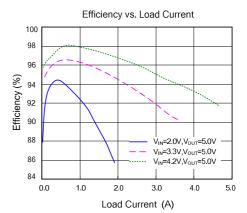

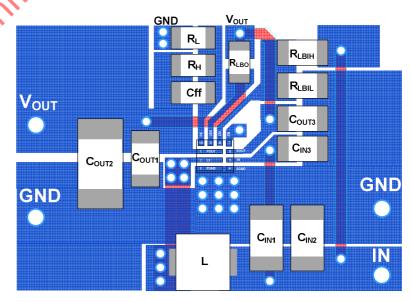

### **Typical Applications**

Figure 1. Schematic Diagram

Figure 2. Efficiency Figure

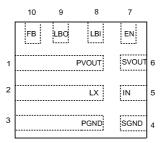

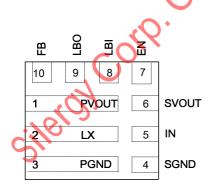

## **Pinout (top view)**

(QFN2X2-10)

Top mark: MGxyz (Device code: MG.,  $x=year\ code$ ,  $y=week\ code$ ,  $z=lot\ number\ code$ )

| Name  | QFN2X2-8 | Description                                                                                                                                                                             |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVOUT | 1        | Power output pin. Decouple this pin to GND pin with at least 22uF ceramic cap.                                                                                                          |

| SVOUT | 6        | Signal output pin. Decouple this pin to GND pin with at least 4.7uF ceramic cap for noise immunity consideration.                                                                       |

| LX    | 2        | Inductor node. Connect an inductor between IN pin and LX pin.                                                                                                                           |

| PGND  | 3        | Power ground pin.                                                                                                                                                                       |

| SGND  | 4        | Signal ground pin.                                                                                                                                                                      |

| IN    | 5        | Signal input pin.                                                                                                                                                                       |

| EN    | 7        | Enable pin. Internal integrated with 1Mohm pull down resistor.                                                                                                                          |

| LBI   | 8        | Low battery comparator input.                                                                                                                                                           |

|       |          | Feedback pin. Connect a resistor R1 between OUT and FB, and a resistor R2 between FB and GND to program the output voltage. V <sub>OUT</sub> =1.2V*(R <sub>1</sub> /R <sub>2</sub> +1). |

| LBO   | 9        | Low battery comparator output (open drain).                                                                                                                                             |

**Absolute Maximum Ratings** (Note 1)

| EN                                                                 | V <sub>OUT</sub> +0.3V |

|--------------------------------------------------------------------|------------------------|

| Other Pins                                                         |                        |

| Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> =25°C QFN2x2-10 | TBD                    |

| Power Dissipation, $P_D$ @ $T_A$ =25°C QFN2x2-10                   |                        |

| θ JA                                                               | TBD                    |

| θ ιc                                                               | TBD                    |

| Junction Temperature Range                                         | 125°C                  |

| Lead Temperature (Soldering, 10 sec.)                              | 260°C                  |

| Storage Temperature Range                                          |                        |

# **Recommended Operating Conditions** (Note 3)

| 11                         | 1.0 V to 3.23 V              |

|----------------------------|------------------------------|

| PVOUT, SVOUTEN             | 2.5V to 5.5V                 |

| 1,001,0001                 |                              |

| EN                         | 0V to V <sub>OUT</sub> +0.3V |

| All other pins             | 0-5 5V                       |

|                            |                              |

| Junction Temperature Range | 40°C to 125°C                |

| Ambient Temperature Range  | 40°C to 85°C                 |

| Ambient Temperature Kange  | 40 C 10 83 C                 |

### **Electrical Characteristics**

$(V_{IN} = 2.4V, V_{OUT} = 5V, I_{OUT} = 500mA, T_A = 25$ °C unless otherwise specified)

| Parameter                         | Symbol               | Test Conditions              | Min   | Тур | Max   | Unit         |

|-----------------------------------|----------------------|------------------------------|-------|-----|-------|--------------|

| Input Voltage                     | $V_{IN}$             |                              | 1.8   |     | 5.25  | V            |

| Output Voltage Range              | V <sub>OUT</sub>     |                              | 2.5   |     | 5.5   | V            |

| Quiescent Current V <sub>IN</sub> | IQ                   | $Io=0A, V_{EN}=V_{IN}=1.8V,$ |       | 10  |       | μA           |

| $V_{ m OUT}$                      |                      | $V_{OUT}=5.0V$               |       | 27  |       | μA           |

| Shutdown Current                  | $I_{SHDN}$           | $V_{EN} = 0V, V_{IN} = 2.4V$ |       | 0.1 | 1     | μA           |

| Linear charge current             | I <sub>CHARGE</sub>  | $V_{OUT} \le 1V$             |       | 1.2 |       | A            |

|                                   |                      | $1V < V_{OUT} < 90\% V_{IN}$ |       | 1.0 |       |              |

| Soft-start time                   | Tss                  |                              |       | 1   | 1     | ms           |

| Input Vin UVLO threshold          | $V_{UVLO}$           |                              |       |     | 1.78  | V            |

| Vin UVLO hysteresis               | $V_{HYS}$            |                              |       | 0.1 | 0     | V            |

| EN Rising Threshold               | $V_{ENH}$            |                              | 1.2   | 10  | ).    | V            |

| EN Falling Threshold              | V <sub>ENL</sub>     |                              |       |     | 0.4   | V            |

| LBI Voltage Threshold             | $V_{LBI}$            |                              | 490   | 500 | 510   | mV           |

| LBI Input Hysteresis              | $V_{LBI\_HYS}$       |                              | 4.0   | 10  |       | mV           |

| Low Side Main FET R <sub>ON</sub> | R <sub>DS(ON)1</sub> | $V_{OUT}=5.0V$               |       | 25  |       | mΩ           |

| Synchronous FET R <sub>ON</sub>   | R <sub>DS(ON)2</sub> | $V_{OUT}=5.0V$               |       | 45  |       | mΩ           |

| Main FET Current Limit            | $I_{LIM1}$           |                              | 6.0   |     |       | A            |

| Switching Frequency               | fsw                  |                              |       | 500 |       | kHz          |

| Feedback Reference Voltage        | $V_{REF}$            | 0                            | 1.182 | 1.2 | 1.218 | V            |

| Output over voltage protection    | V <sub>OVP</sub>     | 101                          |       | 5.9 |       | V            |

| Minimum on time                   | T <sub>ON_MIN</sub>  | 0                            |       | 100 |       | ns           |

| Minimum off time                  | T <sub>OFF_MIN</sub> |                              |       | 100 |       | ns           |

| Max on time                       | T <sub>ON_MAX</sub>  |                              |       | 2   |       | μs           |

| Thermal Shutdown Temperature      | $T_{SD}$             | */0                          |       | 150 |       | $^{\circ}$ C |

| Thermal Shutdown hysteresis       | T <sub>HYS</sub>     |                              |       | 20  |       | $^{\circ}$ C |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2:  $\theta$  JA is measured in the natural convection at  $T_A = 25$ °C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3: The device is not guaranteed to function outside its operating conditions.

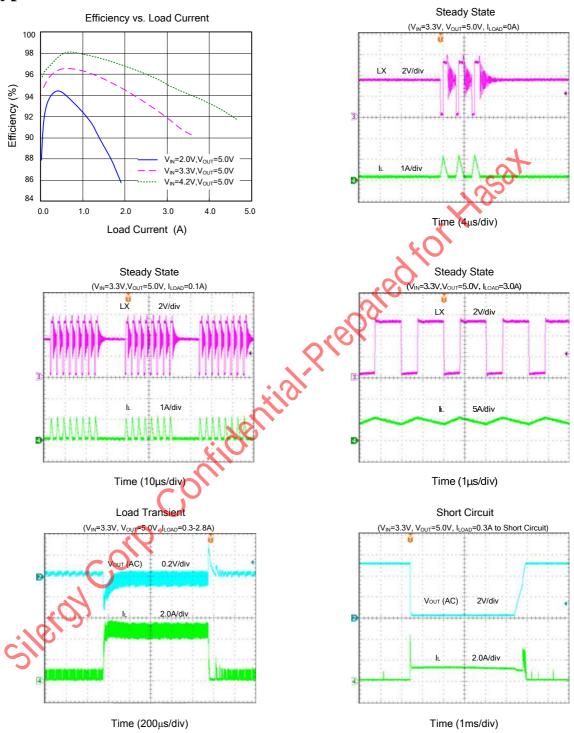

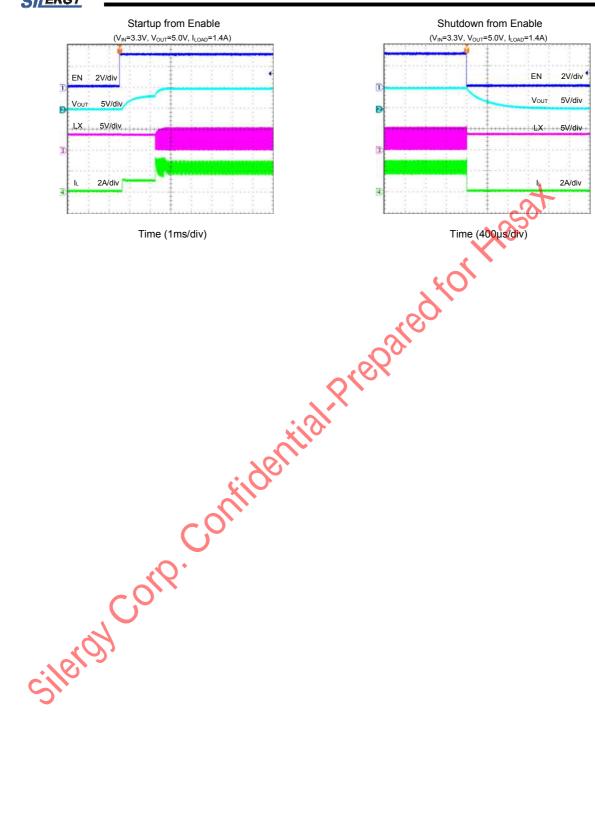

## **Typical Performance Characteristics**

### **Applications Information**

Because of the high integration for SY7066, only input capacitor  $C_{IN}$ , output capacitor  $C_{OUT}$ , inductor L and feedback resistors ( $R_1$  and  $R_2$ ) need to be selected for the targeted applications specifications.

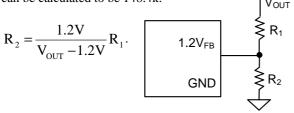

#### Feedback resistor dividers R1 and R2:

Choose  $R_1$  and  $R_2$  to program the proper output voltage. To minimize the power consumption under light loads, it is desirable to choose large resistance values for both  $R_1$  and  $R_2$ . A value of between 10k and 1M is recommended for both resistors. If  $V_{OUT}$  is 5.0V,  $R_1$ =470k is chosen, using following equation, then  $R_2$  can be calculated to be 148.4k:

#### Input capacitor CIN:

The ripple current through input capacitor is calculated as:

$$I_{\text{CIN\_RMS}} = \frac{V_{\text{IN}} \cdot (V_{\text{OUT}} - V_{\text{IN}})}{2\sqrt{3} \cdot L \cdot F_{\text{SW}} \cdot V_{\text{OUT}}}$$

The intput capacitor is selected to handle the input ripple noise requirements. For the best performance, it is recommended to use X5R or better grade ceramic capacitor with 6.3V rating and greater than 22uF capacitance.

#### Output capacitor Cout:

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. Care should be taken to minimize the loop area formed by Cout, and OUT/GND pins. It's recommended to use a X5R or better grade ceramic capacitor with 10V rating and great than 22uF capacitance to decouple the high frequency current. And also a tantalum capacitor with 16V rating and great than 100uF capacitance is recommended for the stability consideration.

#### **Output inductor L:**

There are several considerations in choosing this inductor.

1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the maximum output current. The inductance is calculated as:

$$L = (\frac{V_{_{IN}}}{V_{_{OUT}}})^2 \frac{(V_{_{OUT}} - V_{_{IN}})}{F_{_{SW}} \times I_{_{OUT,MAX}} \times 40\%}$$

where  $F_{SW}$  is the switching frequency and  $I_{OUT,MAX}$  is the maximum load current.

The SY7066 regulator IC is quite tolerant of different ripple current amplitude. Consequently, the final choice of inductance can be slightly off the calculation value without significantly impacting the performance.

2) The saturation current rating of the inductor must be selected to be greater than the peak inductor current under full load conditions.

$$I_{\text{SAT-MIN}} > \left(\frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times I_{\text{OUT, MAX}} + \frac{V_{\text{IN}}}{V_{\text{OUT}}} \frac{(V_{\text{OUT}} - V_{\text{IN}})}{2 \times F_{\text{SW}} \times L}$$

The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<50mohm to achieve a good overall efficiency.

#### **Enable Operation**

Pulling the EN pin low (<0.4V) will shut down the device. During shutdown mode, the SY7066 shutdown current drops to lower than 1uA, driving the EN pin high (> 1.2V) will turn on the IC again.

#### **Low Battery Detector Function-LBI/LBO**

The low-battery detector function is used to monitor the battery voltage and to generate an error flag when the battery voltage drops below a user-set threshold voltage.

The function is active only when the device is enabled. When the device is disabled, LBO stays at high impedance. The detection threshold is 500mV at LBI. During normal operation, LBO stays at high impedance when the voltage applied at LBI is above the threshold. It is active low when the voltage at LBI goes below 500mV.

The battery voltage, at which the detection circuit switches, can be programmed with a resistive divider

connected to LBI pin. The resistive divider scales down the battery voltage to a voltage level of 500mV, which is then compared to LBI threshold voltage. The LBI pin has a built-in hysteresis of 10mV. If the low-battery detection circuit is not used, the LBI pin should be connected to GND (or to VBAT) and the LBO pin can be left unconnected. Do not let the LBI pin float.

$R_3$  and  $R_4$  are designed to program the proper low battery threshold voltage. The voltage across  $R_4$  is equal to the LBI voltage threshold that is generated on-chip, which has a value of 500mV. The value of resistor  $R_3$ , depending on the desired minimum battery voltage VBAT, can be calculated as:

$$R_{3} = \frac{VBAT - 500mV}{500mV} R_{4}$$

$$R_{4}$$

$$R_{3} = \frac{VBAT \circ R_{3}}{SO0mV}$$

$$R_{4}$$

The output of the low battery monitor is a simple opendrain output that goes active low if the dedicated battery voltage drops below the programmed threshold voltage on LBI. The output requires a pull up resistor with a recommended value of  $100k\Omega$ . The maximum voltage which is used to pull up the LBO outputs should not exceed the output voltage of the DC/DC converter. If not used, the LBO pin can be left floating or tied to GND.

#### **Layout Design:**

The layout design of SY7066 regulator is relatively simple. For the best efficiency and minimum noise problems, we should place the following components close to the IC:  $C_{IN}$ ,  $C_{OUT}$ , L,  $R_1$  and  $R_2$ .

- 1) It is desirable to maximize the PCB copper area connecting to PGND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly recommended.

- 2)  $C_{OUT}$  must be close with Pins PVOUT and PGND. The loop area formed by  $C_{OUT}$  and GND must be minimized.

- 3) To minimize the output decouple loop area, LX trace is recommended to be routed on bottom or middle layer through via.

- 4) SVOUT is the power supply pin for the internal control circuit. Don't connect to PVOUT pin directly. A 4.7uF ceramic cap is strongly recommended to decouple SVOUT pin to SGND pin. Please use a jump wire to connect SVOUT pin to output capacitor side.

- 5) The PCB copper area associated with LX pin must be minimized to avoid the potential noise problem.

- 6) The components  $R_1$  and  $R_2$ , and the trace connecting to the FB pin must not be adjacent to the LX net on the PCB layout to avoid the noise problem.

**PCB Layout Suggestion**

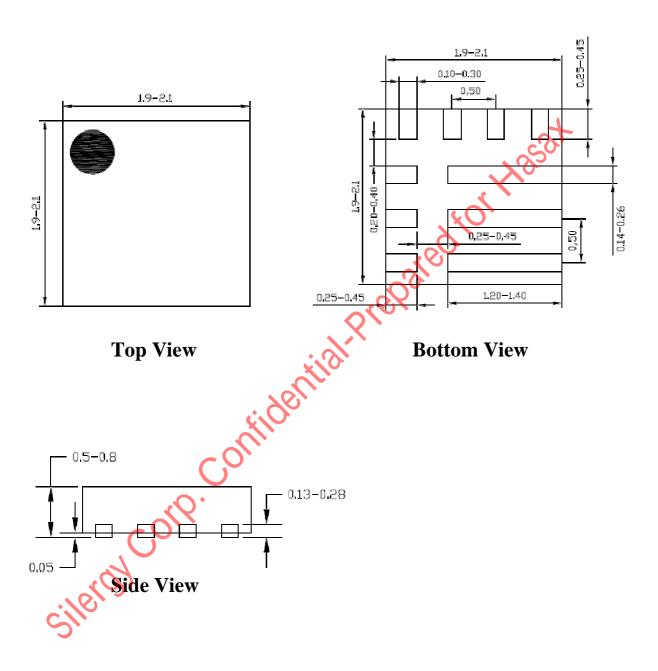

# QFN2x2-10L FC Package Outline

Notes: All dimension in MM and exclude mold flash & metal burr

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Silergy manufacturer:

Other Similar products are found below:

FAN53610AUC33X FAN53611AUC123X EN6310QA 160215 R3 KE177614 FAN53611AUC12X MAX809TTR AST1S31PUR

NCP81103MNTXG NCP81203PMNTXG NCP81208MNTXG PCA9412AUKZ NCP81109GMNTXG NCP81109JMNTXG MP2161AGJ-Z

NCP81241MNTXG MPQ4481GU-AEC1-P MP8756GD-P MPQ2171GJ-P MPQ2171GJ-AEC1-P MP2171GJ-P NCV1077CSTBT3G

MP28160GC-Z MPM3509GQVE-AEC1-P XDPE132G5CG000XUMA1 MP5461GC-P IR3888AMTRPBFAUMA1 MPQ4409GQBE-AEC1-P S-19903DA-A8T1U7 S-19903CA-A6T8U7 S-19903CA-S8T1U7 S-19902BA-A6T8U7 S-19902CA-A6T8U7 AP7361EA-SPR-13

AP7361EA-33DR-13 S-19902AA-A6T8U7 S-19903AA-A6T8U7 S-19902AA-S8T1U7 S-19902BA-A8T1U7 AU8310 LMR36503R5RPER

LMR36503RFRPER LMR54406DBVR XC9110C301MR-G XC9141A50CMR-G XCL206F083CR-G XCL210A111GR-G

LTM4663EV#PBF LD5537B1GL