# DIFFERENTIAL OUTPUT SILICON OSCILLATOR

#### **Features**

- Quartz-free, MEMS-free, and PLL-free all-silicon oscillator

- Any output frequencies from 0.9 to 200 MHz

- Short lead times

- Excellent temperature stability (±20 ppm)

- Highly reliable startup and operation

- High immunity to shock and vibration

- Low jitter: <1.5 ps rms

- 0 to 85 °C operation includes 10-year aging in hot environments

- Footprint compatible with industrystandard 3.2 x 5.0 mm XOs

- CMOS, SSTL, LVPECL, LVDS, and HCSL versions available

- Driver stopped, tri-state, or powerdown operation

- RoHS compliant

- 1.8, 2.5, or 3.3 V options

- Low power

- More than 10x better fit rate than competing crystal solutions

### **Specifications**

| Parameters             | Condition                                              | Min  | Тур | Max  | Units |

|------------------------|--------------------------------------------------------|------|-----|------|-------|

| Frequency Range        |                                                        | 0.9  | _   | 200  | MHz   |

|                        | Temperature stability,<br>0 to +70 °C                  | _    | ±10 | _    | ppm   |

| Frequency Stability    | Temperature stability,<br>0 to +85 °C                  | _    | ±20 | _    | ppm   |

| Frequency Stability    | Total stability,<br>0 to +70 °C operation <sup>1</sup> |      |     | ±150 | ppm   |

|                        | Total stability,<br>0 to +85 °C operation <sup>2</sup> | _    | _   | ±250 | ppm   |

| Operating Temperature  | Commercial                                             | 0    | _   | 70   | °C    |

| Operating reinperature | Extended commercial 0                                  |      | _   | 85   | °C    |

| torage Temperature     |                                                        | -55  | _   | +125 | °C    |

|                        | 1.8 V option                                           | 1.71 | _   | 1.98 | V     |

| Supply Voltage         | 2.5 V option                                           | 2.25 |     | 2.75 | V     |

|                        | 3.3 V option                                           | 2.97 | _   | 3.63 | V     |

#### Notes:

- 1. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, first-year aging at 25 °C, shock, vibration, and one solder reflow.

- 2. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, ten-year aging at 85 °C, shock, vibration, and one solder reflow.

- **3.** See "AN409: Output Termination Options for the Si500S and Si500D Silicon Oscillators" for further details regarding output clock termination recommendations.

- **4.**  $V_{TT} = .5 \times V_{DD}$ .

- **5.**  $V_{TT} = .45 \times V_{DD}$ .

| Parameters                                                 | Condition                                                      | Min                         | Тур                        | Max                         | Units           |

|------------------------------------------------------------|----------------------------------------------------------------|-----------------------------|----------------------------|-----------------------------|-----------------|

|                                                            | LVPECL                                                         | _                           | 34.0                       | 36.0                        | mA              |

|                                                            | Low Power LVPECL                                               | _                           | 19.3                       | 22.2                        | mA              |

|                                                            | LVDS                                                           | _                           | 14.9                       | 16.5                        | mA              |

|                                                            | HCSL                                                           | _                           | 25.3                       | 29.3                        | mA              |

|                                                            | Differential CMOS(3.3 V option, 10 pF on each output, 200 MHz) | _                           | 33                         | 36                          | mA              |

| Supply Current                                             | Differential CMOS(3.3 V option, 1 pFon each output, 40 MHz)    | _                           | 16                         | _                           | mA              |

|                                                            | Differential SSTL-3.3                                          | _                           | 24.5                       | 27.7                        | mA              |

|                                                            | Differential SSTL-2.5                                          | _                           | 24.3                       | 26.7                        | mA              |

|                                                            | Differential SSTL-1.8                                          | _                           | 22.2                       | 25                          | mA              |

|                                                            | Tri-State                                                      | _                           | 9.7                        | 10.7                        | mA              |

|                                                            | Powerdown                                                      | _                           | 1.0                        | 1.9                         | mA              |

| Output Symmetry                                            | V <sub>DIFF</sub> = 0                                          | 46 – 13 ns/T <sub>CLK</sub> | _                          | 54 + 13 ns/T <sub>CLK</sub> | %               |

|                                                            | LVPECL/LVDS                                                    | _                           | _                          | 460                         | ps              |

| Rise and Fall Times (20/80%) <sup>3</sup>                  | HCSL/Differential SSTL                                         | _                           | _                          | 800                         | ps              |

|                                                            | Differential CMOS, 15 pF, ≥80 MHz                              | _                           | 1.1                        | 1.6                         | ns              |

| LVPECL Output Option                                       | Mid-level                                                      | V <sub>DD</sub> – 1.5       | _                          | V <sub>DD</sub> – 1.34      | V               |

| (DC coupling, 50 $\Omega$ to $V_{DD} - 2.0 \text{ V})^3$   | Diff swing                                                     | .720                        | _                          | .880                        | $V_{PK}$        |

| Low Power LVPECL Output Option                             | Mid-level                                                      | _                           | N/A                        | _                           | V               |

| (AC coupling, 100 $\Omega$ Differential Load) <sup>3</sup> | Diff swing                                                     | .68                         | _                          | .95                         | V <sub>PK</sub> |

| LVDS Output Option (2.5/3.3 V)                             | Mid-level                                                      | 1.15                        | _                          | 1.26                        | V               |

| $(R_{TERM} = 100 \Omega \text{ diff})^3$                   | Diff swing                                                     | 0.25                        | _                          | 0.45                        | $V_{PK}$        |

| LVDS Output Option (1.8 V)                                 | Mid-level                                                      | 0.85                        | _                          | 0.96                        | V               |

| $(R_{TERM} = 100 \Omega \text{ diff})^3$                   | Diff swing                                                     | 0.25                        | _                          | 0.45                        | $V_{PK}$        |

|                                                            | Mid-level                                                      | 0.35                        | _                          | 0.425                       | V               |

| HCSL Output Option <sup>3</sup>                            | Diff swing                                                     | 0.65                        | _                          | 0.82                        | $V_{PK}$        |

|                                                            | DC termination per pad                                         | 45                          | _                          | 55                          | Ω               |

| CMOS Output Voltage <sup>3</sup>                           | V <sub>OH</sub> , sourcing 9 mA                                | V <sub>DD</sub> – 0.6       | _                          | _                           | V               |

| CiviOS Output voltage                                      | V <sub>OL</sub> , sinking 9 mA                                 | _                           | _                          | 0.6                         | V               |

| SSTL-1.8 Output Voltage <sup>4</sup>                       | V <sub>OH</sub>                                                | V <sub>TT</sub> + 0.375     | _                          | _                           | V               |

| SSTL-1.8 Output voltage                                    | V <sub>OL</sub>                                                | _                           | _                          | V <sub>TT</sub> – 0.375     | \ \             |

| SSTL-2.5 Output Voltage <sup>4</sup>                       | V <sub>OH</sub>                                                | V <sub>TT</sub> + 0.48      | _                          | _                           |                 |

| 551L-2.5 Output Voltage                                    | V <sub>OL</sub>                                                | _                           | _                          | V <sub>TT</sub> – 0.48      | V               |

| SSTL-3.3 Output Voltage <sup>5</sup>                       | V <sub>OH</sub>                                                | V <sub>TT</sub> + 0.48      | _                          | _                           | .,              |

| SSTE-3.3 Output voltage                                    | V <sub>OL</sub>                                                | _                           | _                          | V <sub>TT</sub> – 0.48      | V               |

| Powerup Time                                               | From time V <sub>DD</sub> crosses min spec 2                   |                             |                            | ms                          |                 |

| OE Deassertion to Clk Stop                                 | — — 250 + 3 x T <sub>C</sub>                                   |                             | 250 + 3 x T <sub>CLK</sub> | ns                          |                 |

| Return from Output Driver Stopped<br>Mode                  |                                                                | _                           | _                          | 250 + 3 x T <sub>CLK</sub>  | ns              |

| Return From Tri-State Time                                 |                                                                | _                           | _                          | 12 + 3 x T <sub>CLK</sub>   | μs              |

| Notes:                                                     |                                                                |                             | l                          | OLK                         |                 |

### Notes:

- 1. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, first-year aging at 25 °C, shock, vibration, and one solder reflow.

- 2. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, ten-year aging at 85 °C, shock, vibration, and one solder reflow.

- **3.** See "AN409: Output Termination Options for the Si500S and Si500D Silicon Oscillators" for further details regarding output clock termination recommendations.

- **4.**  $V_{TT} = .5 \times V_{DD}$ .

- **5.**  $V_{TT} = .45 \times V_{DD}$ .

2 Rev. 1.1

| Parameters                 | Condition                                                     | Min | Тур | Max | Units     |

|----------------------------|---------------------------------------------------------------|-----|-----|-----|-----------|

| Return From Powerdown Time |                                                               | _   | _   | 2   | ms        |

| Period Jitter (1-sigma)    | Non-CMOS                                                      | _   | 1   | 2   | ps<br>RMS |

| r enou sitter (1-sigma)    | CMOS, C <sub>L</sub> = 7 pF                                   | _   | 1   | 3   | ps<br>RMS |

| Integrated Phase Jitter    | 1.0 MHz – min(20 MHz,<br>0.4 x F <sub>OUT</sub> ),non-CMOS    | _   | 0.6 | 1   | ps<br>RMS |

| integrated i nase sitter   | 1.0 MHz – min(20 MHz,<br>0.4 x F <sub>OUT</sub> ),CMOS format | _   | 0.7 | 1.5 | ps<br>RMS |

### Notes:

- 1. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, first-year aging at 25 °C, shock, vibration, and one solder reflow.

- 2. Inclusive of 25 °C initial frequency accuracy, operating temperature range, supply voltage change, output load change, ten-year aging at 85 °C, shock, vibration, and one solder reflow.

- 3. See "AN409: Output Termination Options for the Si500S and Si500D Silicon Oscillators" for further details regarding output clock termination recommendations.

- **4.**  $V_{TT} = .5 \times V_{DD}$ . **5.**  $V_{TT} = .45 \times V_{DD}$ .

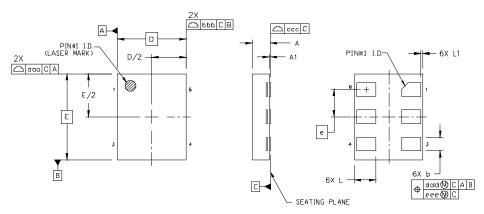

## **Package Specifications**

**Table 1. Package Diagram Dimensions (mm)**

| Dimension | Min       | Nom  | Max  |

|-----------|-----------|------|------|

| А         | 0.80      | 0.85 | 0.90 |

| A1        | 0.00      | 0.03 | 0.05 |

| b         | 0.59      | 0.64 | 0.69 |

| D         | 3.20 BSC. |      |      |

| е         | 1.27 BSC. |      |      |

| E         | 4.00 BSC. |      |      |

| L         | 0.95      | 1.00 | 1.05 |

| Dimension | Min  | Nom  | Max  |

|-----------|------|------|------|

| L1        | 0.00 | 0.05 | 0.10 |

| aaa       | _    | _    | 0.10 |

| bbb       | _    | _    | 0.10 |

| ccc       | _    | _    | 0.08 |

| ddd       | _    | _    | 0.10 |

| eee       | _    | _    | 0.05 |

**Table 2. Pad Connections**

| 1 | OE                                         |  |

|---|--------------------------------------------|--|

| 2 | NC—Make no external connection to this pin |  |

| 3 | GND                                        |  |

| 4 | Output                                     |  |

| 5 | Complementary Output                       |  |

| 6 | VDD                                        |  |

Table 3. Tri-State/Powerdown/Driver Stopped **Function on OE (3rd Option Code)**

|            | Α             | В             | С              | D              | E                 | F                 |

|------------|---------------|---------------|----------------|----------------|-------------------|-------------------|

| Open       | Active        | Active        | Active         | Active         | Active            | Active            |

| 1<br>Level | Active        | Tri-<br>State | Active         | Power-<br>down | Active            | Driver<br>Stopped |

| 0<br>Level | Tri-<br>State | Active        | Power-<br>down | Active         | Driver<br>Stopped | Active            |

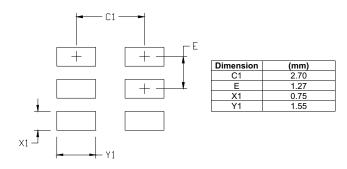

Figure 1. Recommended Land Pattern

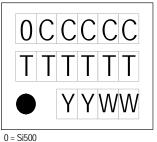

CCCCC = mark code TTTTTT = assembly manufacturing code YY = year

WW = work week

Figure 2. Top Mark

4 Rev. 1.1

### **Environmental Compliance**

| Parameter                    | Conditions/Test Method            |

|------------------------------|-----------------------------------|

| Mechanical Shock             | MIL-STD-883, Method 2002.4        |

| Mechanical Vibration         | MIL-STD-883, Method 2007.3 A      |

| Resistance to Soldering Heat | MIL-STD-202, 260 C° for 8 seconds |

| Solderability                | MIL-STD-883, Method 2003.8        |

| Damp Heat                    | IEC 68-2-3                        |

| Moisture Sensitivity Level   | J-STD-020, MSL 3                  |

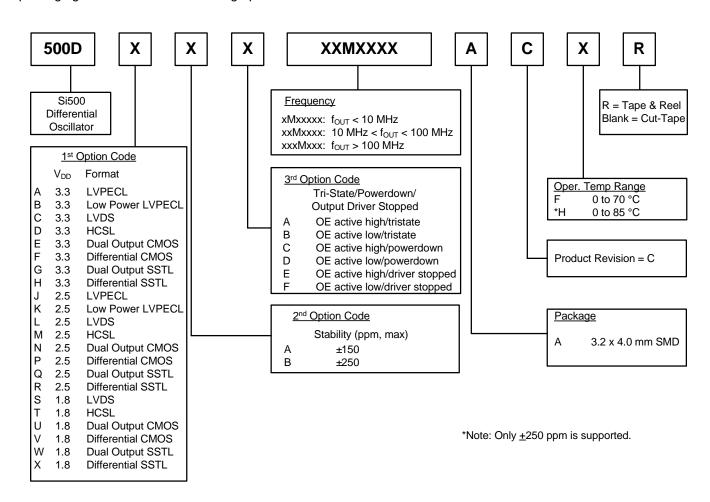

## **Ordering Information**

The Si500D supports a variety of options including frequency, output format, supply voltage, and tristate/powerdown. Specific device configurations are programmed into the Si500D at time of shipment. Configurations are specified using the figure below. Silicon Labs provides a web-based part number utility that can be used to simplify part number configuration. Refer to <a href="https://www.silabs.com/SiliconXOPartnumber">www.silabs.com/SiliconXOPartnumber</a> to access this tool. The Si500D XO series is supplied in a ROHS-compliant, Pb-free, 6-pad, 3.2 x 4.0 mm package. Tape and reel packaging is available as an ordering option.

Rev. 1.1 5

# **Si500D**

## **DOCUMENT CHANGE LIST**

## Revision 0.2 to Revision 0.3

- Revision B to Revision C updated in Ordering Information

- 0 to 85 C° Operating Temperature Range option added

### Revision 0.3 to Revision 1.0

- Clarified SSTL specifications.

- Revised Differential CMOS supply current values.

- Clarified Differential CMOS supply current loading conditions.

### **Revision 1.0 to Revision 1.1**

- Updated Ordering information for ±250 ppm from 0 to

- Updated jitter from 1.5 ps to 1.5 ps rms.

- Updated operating temperature to include extended commercial at 0 to +85 °C.

- Updated features to include LVPECL, LVDS, and HCSL.

Notes:

## **Si500D**

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

8 Rev. 1.1

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Standard Clock Oscillators category:

Click to view products by Silicon Labs manufacturer:

Other Similar products are found below:

EP1400SJTSC-125.000M 601137 601252 CSX750FBC-24.000M-UT CSX750FBC-33.333M-UT CSX750FCC-3.6864M-UT F335-12 F335-25 F535L-50 DSC506-03FM2 ASA-20.000MHZ-L-T ASA-25.000MHZ-L-T ASA-27.000MHZ-L-T ASV-20.000MHZ-L-T ECS-2018-160-BN-TR EL13C7-H2F-125.00M MXO45HS-2C-66.6666MHZ NBXDBB017LN1TAG NBXHBA019LN1TAG SiT1602BI-22-33E-50.000000E SIT8003AC-11-33S-2.04800X SiT8256AC-23-33E-156.250000X SIT8918AA-11-33S-50.000000G SM4420TEV-40.0M-T1K SMA4306-TL-H F335-24 F335-40 F335-50 F535L-10 F535L-12 F535L-16 F535L-24 F535L-27 F535L-48 PE7744DW-100.0M CSX750FBC-20.000M-UT CSX-750FBC33333000T CSX750FBC-4.000M-UT CSX750FBC-7.3728M-UT CSX750FBC-8.000M-UT CSX-750FCC14745600T CSX750FCC-16.000M-UT CSX-750FCC40000000T CSX750FCC-4.000M-UT ASA-22.000MHZ-L-T ASA-26.000MHZ-L-T ASA-40.000MHZ-L-T ASA-48.000MHZ-L-T ASA-60.000MHZ-L-T ASF1-3.686MHZ-N-K-S