# 32 KHz-100 MHz CMEMS® OSCILLATOR

### **Features**

- Wide frequency range: 32 kHz to 100 MHz

- Contact Silicon Labs for frequencies above 100 MHz

- Si501 single frequency w/ OE

- Si502 dual frequency w/ OE/FS

- Si503 quad frequency w/ FS

- ±20/30/50 ppm frequency stability including 10-year aging

- LVCMOS output

- Low period jitter

- Low power

- Continuous supply voltage range: +1.71 V to +3.63 V

- User selectable tRise/tFall options

- Glitchless start and stop

- Excellent short-term stability, longterm aging

- Industry standard footprints: 2x2.5, 2.5x3.2, 3.2x5 mm

- RoHS compliant, Pb-free

- Short lead times: <2 weeks

- -20 to +70 °C: Extnd commercial

- -40 to +85 °C: Industrial

- The Si50x family also includes the Si504 for in-circuit programmability (See the Si504 Data Sheet)

### **Applications**

- Storage (SATA/SAS/PCIe)

- General purpose processors

- Industrial controllers

- Embedded controllers

- Motor control

- Flow control

- Office/Home automation

- IP cameras/surveillance

- Display and control panels

- Outdoor electronics

- Multi-function printers

- Office equipment

Patents pending

### **Description**

The Si501/2/3 CMEMS oscillator family provides monolithic, MEMS-based IC replacements for traditional crystal oscillators. Silicon Laboratories' CMEMS technology combines standard CMOS + MEMS in a single, monolithic IC to provide integrated, high-quality and high-reliability oscillators. Each device is factory tested and configured for guaranteed performance to data sheet specifications across voltage, process, temperature, shock, vibration, and aging.

Additional information on the Si50x CMEMS oscillator architecture and CMEMS technology is available in white papers on the Silicon Labs website at www.siliconlabs.com/cmems.

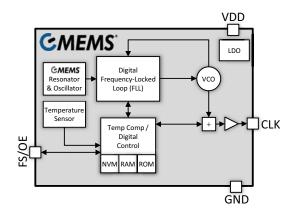

### **Functional Block Diagram**

# Si501/2/3

# TABLE OF CONTENTS

| <u>Section</u>                                        | <u>Page</u> |

|-------------------------------------------------------|-------------|

| 1. Electrical Specifications                          | 3           |

| Descriptions                                          |             |

| 2.1. Si501/2 Applications Circuits                    |             |

| 2.2. Si501/2 AC Waveforms and Functional Descriptions |             |

| 2.3. Si503 Applications Circuits                      |             |

| 2.4. Si503 AC Waveform and Functional Description     |             |

| 3. Functional Description                             |             |

| 3.1. OE Enable and Disable States                     |             |

| 3.2. Output Rise and Fall settings                    |             |

| 4. Pin Descriptions                                   | 13          |

| 5. Ordering Guide                                     | 14          |

| 5.1. Si501 Ordering Guide and Part Number Syntax      | 14          |

| 5.2. Si502 Ordering Guide and Part Number Syntax      | 15          |

| 5.3. Si503 Ordering Guide and Part Number Syntax      |             |

| 6. Package Dimensions and Land Patterns               |             |

| 6.1. Package Outline: 3.2 x 5 mm 4-pin DFN            |             |

| 6.2. Package Outline: 2.5 x 3.2 mm 4-pin DFN          |             |

| 6.3. Package Outline: 2 x 2.5 mm 4-pin DFN            |             |

| 7. Top Markings                                       |             |

| 7.1. 3.2 x 5 mm Top Marking                           |             |

| 7.2. 3.2 x 5 mm Top Marking Explanation               |             |

| 7.3. 2.5 x 3.2 mm Top Marking                         |             |

| 7.4. 2.5 x 3.2 mm Top Marking Explanation             |             |

| 7.5. 2 x 2.5 mm Top Marking                           |             |

| 7.6. 2 x 2.5 mm Top Marking Explanation               |             |

| Document Change List                                  |             |

| Contact Information                                   | 27          |

# 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

$V_{DD}$ =1.71 to 3.63 V,  $T_A$ = -40 to 85 °C, unless otherwise specified

| Parameter                    | Symbol           | Test Condition                                                                           | Min                       | Тур | Max                       | Unit |

|------------------------------|------------------|------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| Supply Voltage <sup>1</sup>  | $V_{DD}$         |                                                                                          | 1.71                      | _   | 3.63                      | V    |

| Supply Current               | I <sub>DD1</sub> | C <sub>L</sub> =4 pF, 3.3 V <sub>DD</sub> , F <sub>CLK</sub> =1.0 MHz, low power option  | _                         | 1.7 | 2.5                       | mA   |

|                              |                  | C <sub>L</sub> =4 pF, 3.3 V <sub>DD</sub> , F <sub>CLK</sub> =100 MHz, low power option  | _                         | 5.3 | 6.5                       | mA   |

|                              |                  | C <sub>L</sub> =4 pF, 3.3 V <sub>DD</sub> , F <sub>CLK</sub> =1.0 MHz, low jitter option | _                         | 3.9 | 4.9                       | mA   |

|                              |                  | C <sub>L</sub> =4 pF, 3.3 V <sub>DD</sub> , F <sub>CLK</sub> =100 MHz, low jitter option | _                         | 7.6 | 8.9                       | mA   |

| Static Supply<br>Current     | I <sub>DD2</sub> | Mode=Stop <sup>2</sup> , low power option F <sub>CLK</sub> =1 MHz                        | _                         | 1.7 | 2.5                       | mA   |

|                              |                  | Mode=Stop <sup>2</sup> , low jitter option F <sub>CLK</sub> =1 MHz                       | _                         | 3.9 | 4.9                       | mA   |

|                              |                  | Mode=Doze <sup>2</sup>                                                                   | _                         | 670 | 890                       | μA   |

|                              |                  | Mode=Sleep <sup>2</sup>                                                                  | _                         | 0.3 | 1                         | μA   |

| Input High Voltage           | V <sub>IH</sub>  | FS/OE pin                                                                                | 0.70 x<br>V <sub>DD</sub> | _   | _                         | V    |

| Input Low Voltage            | V <sub>IL</sub>  | FS/OE pin                                                                                | _                         | _   | 0.30 x<br>V <sub>DD</sub> | V    |

| OE Internal Pull<br>Resistor | R <sub>I</sub>   | Ordering option                                                                          | 40                        | 50  | 60                        | kΩ   |

| Operating                    | T <sub>A</sub>   | Extended commercial grade                                                                | -20                       | _   | 70                        | °C   |

| Temperature                  |                  | Industrial grade                                                                         | -40                       | _   | 85                        | °C   |

### Notes:

- 1. The supply voltage range is continuous from 1.71 to 3.63 V.

- **2.** Si501 and Si502 only. Si503 has FS only and does not support Stop, Doze, or Sleep. See Section 3. Functional Description for more information on operational modes.

### **Table 2. Output Clock Characteristics**

$V_{DD}$ =1.71 to 3.63 V,  $T_{A}$ = -40 to 85 °C, unless otherwise specified.

| Parameter                                  | Symbol                | Test Condition                                             | Min    | Тур | Max                            | Unit |

|--------------------------------------------|-----------------------|------------------------------------------------------------|--------|-----|--------------------------------|------|

| Frequency<br>Range                         | F <sub>CLK</sub>      |                                                            | 0.032  | _   | 100                            | MHz  |

| Clock Period                               | T <sub>CLK</sub>      | 1/F <sub>CLK</sub>                                         | 31,250 | _   | 10                             | ns   |

| Total Stability <sup>1</sup>               | F <sub>STAB</sub>     |                                                            | -20    | _   | +20                            | ppm  |

|                                            |                       |                                                            | -30    | _   | +30                            | ppm  |

|                                            |                       |                                                            | -50    | _   | +50                            | ppm  |

| Initial<br>Accuracy                        | F <sub>I</sub>        | Measured at 25 °C at the time of shipping                  | _      | ±2  | _                              | ppm  |

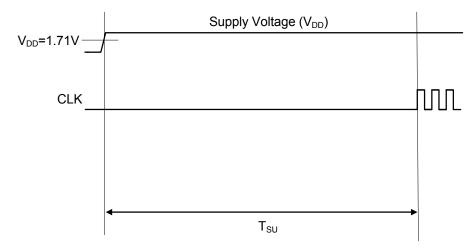

| Startup Time <sup>2</sup>                  | T <sub>SU</sub>       | From V <sub>DD</sub> crossing 1.71 V to first clock output | _      | 2.5 | 4                              | ms   |

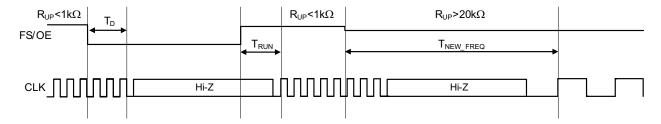

| Resume                                     | $T_{RUN}$             | From Sleep mode                                            | _      | 2.5 | 5                              | ms   |

| Time <sup>3,4</sup>                        |                       | From Doze mode                                             | _      | 1.7 | 2.55                           | ms   |

|                                            |                       | From Stop mode <sup>5</sup>                                | _      | _   | 1.5 x T <sub>CLK</sub> +<br>35 | ns   |

| Output Disable<br>Time <sup>3,4</sup>      | T <sub>D</sub>        | To Sleep/Doze mode, from output running                    | _      | —   | 225                            | μs   |

|                                            |                       | To Stop, from output running                               | _      | _   | 1.5 x T <sub>CLK</sub> +<br>35 | ns   |

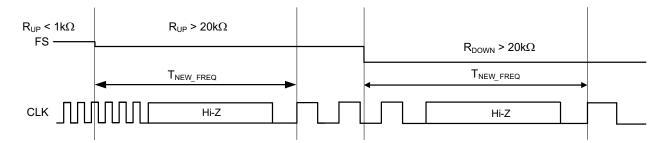

| Frequency<br>Update<br>Time <sup>4,6</sup> | T <sub>NEW_FREQ</sub> |                                                            | _      | _   | 5                              | ms   |

### Notes:

- 1. Orderable option. Stability budget consists of initial tolerance, operating temperature range, rated power supply voltage change, load change, 10-year aging, shock, and vibration.

- 2. Hold FS/OE high (strong or weak) during powerup for fastest time to clock.

- 3. Si501 and Si502 only. Si503 has FS only and does not support Stop, Doze, or Sleep.

- **4.** Asserted FS/OE actions must be held stable for the maximum duration of the invoked FS/OE event (e.g., T<sub>RUN</sub>, T<sub>NEW FREQ</sub>, T<sub>D</sub>, etc).

- 5. If the Si502 frequency is switched while the device is in Stop mode, the frequency prior to Stop will be output briefly until the glitchless switch to the other frequency. Doze mode and Sleep mode do not have this behavior.

- 6. Si502 and Si503 only. Si501 is a single frequency device with OE only.

Table 3. Output Clock Levels and Symmetry

$V_{DD}$  = 1.71 to 3.63 V,  $T_A$  = -40 to 85 °C unless otherwise indicated.

| Parameter                      | Symbol          | Test Condition                                                                           | Min                       | Тур              | Max                       | Unit |

|--------------------------------|-----------------|------------------------------------------------------------------------------------------|---------------------------|------------------|---------------------------|------|

| Output High Voltage            | V <sub>OH</sub> | 1st ordering option code: A and H I <sub>OH</sub> =–4 mA                                 | 0.90 x<br>V <sub>DD</sub> | _                | _                         | V    |

| Output Low Voltage             | V <sub>OL</sub> | 1st ordering option code: A and H I <sub>OH</sub> =+4 mA                                 | _                         | _                | 0.10 x<br>V <sub>DD</sub> | V    |

| Rise/Fall<br>Time <sup>1</sup> | tRise<br>/tFall | $1^{st}$ ordering option code <sup>2</sup> : A and H $Z_0$ =25 $\Omega$ @ 3.3 V          | 0.4                       | 0.7 <sup>2</sup> | 1.2                       | ns   |

|                                |                 | ${\rm 1^{st}}$ ordering option code: B and J ${\rm Z_0}$ = 50 $\Omega$ @ 3.3 V           | 1                         | 1.3              | 1.6                       | ns   |

|                                |                 | ${\rm 1^{st}}$ ordering option code: C and K ${\rm Z_0}$ = 50 $\Omega$ @ 2.5 V           | 1                         | 1.3              | 1.6                       | ns   |

|                                |                 | ${\sf Z}_0^{\rm st}$ ordering option code: D and L ${\sf Z}_0$ = 50 $\Omega$ @ 1.8 V     | 1                         | 1.3              | 1.6                       | ns   |

|                                |                 | ${\rm 1^{st}}$ ordering option code: E and M ${\rm Z_0}$ = 110 $\Omega$ @ 3.3 V          | 2                         | 3                | 4                         | ns   |

|                                |                 | ${\rm 1^{st}}$ ordering option code: F and N ${\rm Z_0}$ =220 $\Omega$ @ 3.3 ${\rm V^3}$ | 4                         | 5                | 7                         | ns   |

|                                |                 | $1^{st}$ ordering option code: G and P $Z_0$ =440 $\Omega$ @ 3.3 $V^3$                   | 7                         | 8                | 11                        | ns   |

| Duty Cycle                     | DC              | Drive strength selected such that tRise/tFall (20% to 80%)<10% of period                 | 45                        | 50               | 55                        | %    |

### Notes:

- C<sub>L</sub>=15 pF, tRise/tFall (20% to 80%), 3.3 V, unless otherwise stated.

Recommended series termination resistor (R<sub>S</sub>) = 24.9 Ω for Z<sub>0</sub>=50 Ω.

Ordering options F, N, G, and P are not recommended for F<sub>CLK</sub> > 5 MH<sub>2</sub>.

# Si501/2/3

**Table 4. Output Clock Jitter and Phase Noise**

$V_{DD}$  = 1.71 to 3.63 V,  $T_A$  = -40 to 85 °C unless otherwise indicated.

| Parameter                 | Symbol             | Test Condition                                                                               | Min | Тур | Max | Unit     |

|---------------------------|--------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|----------|

| Cycle-to-Cycle Jitter     | J <sub>CCPP</sub>  | 100 MHz, Low Jitter Option<br>1 <sup>st</sup> ordering option code: H                        | _   | 14  | 25  | ps pk-pk |

|                           |                    | 100 MHz, Low Power Option 1st ordering option code: A                                        | _   | 16  | 26  | ps pk-pk |

| Period Jitter             | J <sub>PRMS</sub>  | 100 MHz, Low Jitter Option 1st ordering option code: H                                       | _   | 1   | 1.6 | ps rms   |

|                           |                    | 100 MHz, Low Power Option<br>1 <sup>st</sup> ordering option code: A                         |     | 1.3 | 1.9 | ps rms   |

| Period Jitter Pk-Pk       | J <sub>PPKPK</sub> | Low Jitter Option<br>10k samples<br>1 <sup>st</sup> ordering option code: H                  | _   | 9   | 13  | ps pk-pk |

|                           |                    | Low Power Option<br>10k samples<br>1 <sup>st</sup> ordering option code: A                   | _   | 10  | 16  | ps pk-pk |

| Phase Jitter <sup>1</sup> | ф                  | 75 MHz F <sub>OFFSET</sub> =900 kHz to 7.5 MHz Low Jitter Option 1st ordering option code: H | _   | 1   | 1.3 | ps rms   |

|                           |                    | 75 MHz F <sub>OFFSET</sub> =900 kHz to 7.5 MHz Low Power Option 1st ordering option code: A  | _   | 2.5 | 3.2 | ps rms   |

### Notes:

<sup>1.</sup> Integrated phase jitter exceeds the requirements of some high-performance data communications systems. See AN783 for additional information.

**Table 5. Environmental Compliance and Package Information**

| Parameter                 | Test Condition                               |

|---------------------------|----------------------------------------------|

| Mechanical Shock          | MIL-STD-883, Method 2002, Cond B. (1,500 g)  |

| Mechanical Shock High g   | MIL-STD-883, Method 2002, Cond E. (10,000 g) |

| Mechanical Vibration      | MIL-STD-883, Method 2007                     |

| Solderability             | MIL-STD-883, Method 2003                     |

| Temperature Cycle         | JESD22, Method A104                          |

| Resistance to Solder Heat | MIL-STD-883, Method 2036                     |

| Contact Pads              | Gold over Nickel/Palladium                   |

### **Table 6. Thermal Conditions**

| Parameter         | Symbol        | Test Condition        | Value | Unit |

|-------------------|---------------|-----------------------|-------|------|

| Thermal Impedance | $\theta_{JA}$ | 3.2x5 mm, still air   | 187   | 0000 |

|                   |               | 2.5x3.2 mm, still air | 239   | °C/W |

|                   |               | 2x2.5 mm, still air   | 241   |      |

### Table 7. Absolute Maximum Limits<sup>1</sup>

| Parameter                                                          | Symbol            | Rating                           | Unit |

|--------------------------------------------------------------------|-------------------|----------------------------------|------|

| Maximum Operating Temperature                                      | T <sub>MAX</sub>  | 85                               | °C   |

| Storage Temperature                                                | T <sub>S</sub>    | -55 to +125                      | °C   |

| Supply Voltage                                                     | V <sub>DD</sub>   | -0.5 to +3.8                     | V    |

| Input Voltage                                                      | V <sub>IN</sub>   | -0.5 to V <sub>DD</sub><br>+0.3V | V    |

| ESD Sensitivity (JESD22-A114)                                      | НВМ               | 2000                             | V    |

| ESD Sensitivity (CDM)                                              | CDM               | 500                              | V    |

| Soldering Temperature (Pb-free profile) <sup>2</sup>               | T <sub>PEAK</sub> | 260                              | °C   |

| Soldering Time at T <sub>PEAK</sub> (PB-free profile) <sup>2</sup> | T <sub>P</sub>    | 20–40                            | S    |

| Junction Temperature                                               | T <sub>J</sub>    | 125                              | °C   |

### Notes

- 1. Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2. The device is compliant with JEDEC J-STD-020.

8

# 2. Si501/2/3 Typical Applications Circuits, AC Waveforms, and Functional Descriptions

The Si501/2/3 family has various applications circuits and ac waveforms depending on the selected device and ordering configuration options. Pay careful attention when reading the following section to be sure you refer to the correct diagrams.

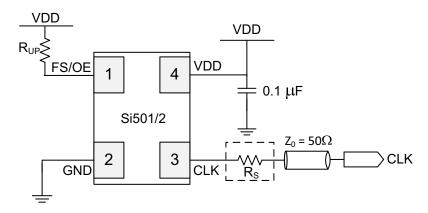

### 2.1. Si501/2 Applications Circuits

Figure 1. Si501/2 Applications Circuit with Optional Output Series Resistor

**Note:** The dotted line box in Figure 1 is an optional component depending on tRise/tFall configuration option. This diagram applies to all Si50x product drive strength configuration options. See Table 3 for R<sub>S</sub> recommendations. See Section 5. "Ordering Guide" for configuration options.

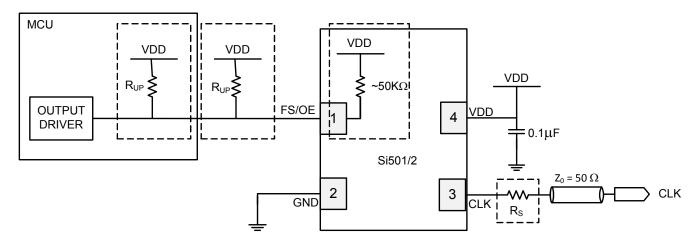

**Note:** The dotted line boxes in Figure 2 show resistor options depending on MCU pull-up resistors configuration and the Si501/2 internal resistor configuration options. See Section 5. "Ordering Guide" for configuration options. Users should design only one of the pin 1 dotted-line options. The series resistor (R<sub>S</sub>) on pin 3 is also optional. See Table 3 for R<sub>S</sub> recommendations.

Figure 2. Si501/2 Applications Circuit with MCU Configuration Options

Table 8. Si502 FS/OE States and Resistor Values

| FS/OE Pin State | R <sub>UP</sub>                            | Clock Output |

|-----------------|--------------------------------------------|--------------|

| Strong High     | $0 \Omega \le R_{UP} \le 1 k\Omega$        | Frequency 1  |

| Weak High       | 20 kΩ $\leq$ R <sub>UP</sub> $\leq$ 200 kΩ | Frequency 2  |

| Low             | _                                          | Hi-Z         |

### Notes:

- 1. If the Si502 internal pull-up resistor configuration option is not selected, an MCU internal pull-up resistor or an external pull-up resistor should be used.

- 2. The parallel combination of all pull-up resistors on the FS/OE pin, including the optional internal device pull-up resistor must be > 20 k $\Omega$  to select the Weak High state.

- **3.** If the Si502 internal pull-up resistor is enabled with no other external FS/OE connections, the FS/OE state will be detected as `Weak High' which selects the Frequency 2 output by default.

### 2.2. Si501/2 AC Waveforms and Functional Descriptions

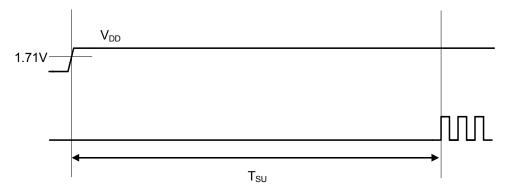

Figure 3. Si501/2 Power On Time (refer to Table 2)

Figure 4. Si501/2 AC Waveform (refer to Table 2)

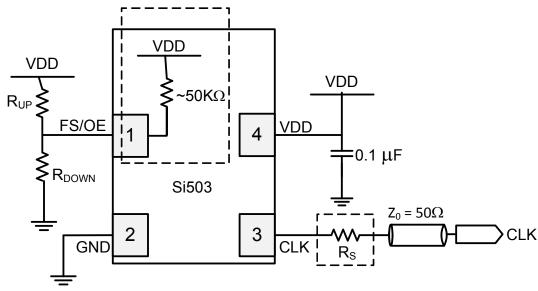

### 2.3. Si503 Applications Circuits

**Note:** The dotted line boxes show optional components depending on tRise/tFall and internal pull up resistor configuration options. See Section 5. "Ordering Guide" for configuration options. See Table 3 for R<sub>S</sub> recommendations.

Figure 5. Si503 Applications Circuit with Configuration Options

Table 9. Si503 Frequency Select with External Resistor Options

| FS/OE Pin State | R <sub>UP</sub>                                                  | R <sub>DOWN</sub>                                  | Clock Output |

|-----------------|------------------------------------------------------------------|----------------------------------------------------|--------------|

| Strong High     | $0 \Omega \le R_{UP} \le 1 k\Omega$                              | Do not populate                                    | Frequency 1  |

| Weak High       | $20 \text{ k}\Omega \leq R_{\text{UP}} \leq 200 \text{ k}\Omega$ | Do not populate                                    | Frequency 2  |

| Weak Low        | Do not populate                                                  | 20 k $\Omega$ ≤ R <sub>DOWN</sub> ≤ 200 k $\Omega$ | Frequency 3  |

| Strong Low      | Do not populate                                                  | $0 \Omega \le R_{DOWN} \le 1 k\Omega$              | Frequency 4  |

**Note:** If the Si503 internal pull-up resistor is enabled with no other external FS/OE connections, the FS/OE state will be detected as 'Weak High' which selects the Frequency 2 output by default.

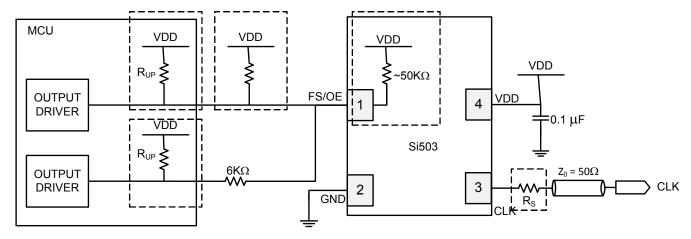

**Note:** The dotted line boxes in Figure 6 show resistor options depending on MCU pull-up resistors configuration and the Si503 internal resistor configuration options. See Section 5. "Ordering Guide" for configuration options. Users should design only one of the pin 1 dotted-line options. The series resistor (R<sub>S</sub>) on pin 3 is also optional. See Table 3 for R<sub>S</sub> recommendations.

Figure 6. Si503 Applications Circuit with MCU and Configuration Options

| FS/OE Pin State | MCU Output 1 | MCU Output 2 | Clock Output |

|-----------------|--------------|--------------|--------------|

| Strong High     | High         | Hi-Z         | Frequency 1  |

| Weak High       | Hi-Z         | Hi-Z         | Frequency 2  |

| Weak Low        | Hi-Z         | Low          | Frequency 3  |

| Strong Low      | Low          | Hi-Z         | Frequency 4  |

Table 10. Si503 Frequency Select

**Note:** If the Si50x internal pull-up resistor is enabled with no other external OE connections, the OE state will be detected as `Weak High' which selects the Frequency 2 output by default.

### 2.4. Si503 AC Waveform and Functional Description

Figure 7. Si503 Power On Time (refer to Table 2)

Figure 8. Si503 AC Waveform (refer to Table 2)

### 3. Functional Description

The Si50x series oscillator family includes four base devices. All devices are configurable according to the Section 5. "Ordering Guide". The four devices each support a single clock output frequency at any one time and are segmented according to the number of clock frequencies they store in on-chip memory.

The Si501 supports a single stored frequency, enabled with the OE functionality. The Si502 stores two frequencies that can be selected with FS and enabled/disabled with OE functionality. The Si503 stores four frequencies, selected with FS functionality. The Si503 does not support OE functionality. The Si501/2/3 are covered in this data sheet.

The Si504 is a programmable oscillator, controlled through a single pin interface (C1D). It is covered in its own Si504 data sheet available at <a href="https://www.siliconlabs.com/cmems">www.siliconlabs.com/cmems</a>.

All devices in the Si50x CMEMS series employ a cost-optimized, power-efficient, digital FLL architecture to produce a highly accurate and stable output clock from a passively compensated MEMS resonator reference frequency.

The architecture uses the MEMS resonator as its reference frequency along with a divided signal from an on-chip, digitally-controlled VCO to drive a frequency comparator for the FLL's digital loop filter. The digital loop filter accumulates and further processes the frequency error values to produce the target output frequency.

The architecture also uses a high-resolution, low-noise temperature sensor and temperature compensation algorithm to offset any temperature drift of the passively compensated MEMS resonator. Each device is calibrated for temperature and MEMS-resonator frequency pairs and derives a device-specific compensation polynomial. As the temperature changes, this compensation circuitry offsets any frequency drift.

This tightly coupled system is extremely accurate and fast because the MEMS resonator and CMOS compensation circuitry are in a single, monolithic chip, and, therefore, separated by a few microns.

The complete system process occurs many thousands of times per second, providing excellent frequency accuracy and stability across temperature changes, including any fast temperature transients. The oscillator also supports a low-power version that reduces the sampling cycle to a longer period, reducing power consumption for applications that can tolerate relaxed jitter specifications of approximately 1 ps RMS to reduce power by approximately 2-3 mA. See Table 1 for exact specifications.

### 3.1. OE Enable and Disable States

The Si50x CMEMS series supports four operational output states via the FS/OE configuration pin. If enabled, the Si50x is in Run mode, the clock is output and power is as specified in Table 1. The disable modes are Stop, Sleep, and Doze. Each of these states has a different power consumption profile as specified in Table 1.

### 3.1.1. Stop Mode

The Si50x output in Stop mode is high-impedance, also known as High-Z (Hi-Z) or Tri-State. Stop mode disables the output driver, but the digital core and MEMS resonator remain enabled for fast transition to Run mode. The output is stopped and held at High-Z after completing the last cycle glitch-free. No other power saving measure is taken in Stop mode.

### 3.1.2. Doze Mode

The Si50x output in Doze mode is high-impedance, also known as High-Z (Hi-Z) or Tri-State. Doze mode disables the output driver, the VCO, and the MEMS resonator, but the digital core remains enabled. The output is stopped and is held at High-Z after completing the last cycle glitch-free.

### 3.1.3. Sleep Mode

The Si50x output in Sleep mode is high-impedance, also known as High-Z (Hi-Z) or Tri-State. Sleep mode disables power to all circuitry except for low-leakage circuitry that retains the last device configuration. The output is stopped and is held at High-Z after completing the last cycle glitch-free.

### 3.2. Output Rise and Fall Settings

The Si50x clock output is programmable. This enables reduction of electromagnetic interference (EMI) radiation from the clock output. The amount of EMI reduction is dependent on the output frequency, the harmonic of interest, and the board layout. Lab results using a 50 MHz FOUT and changing the clock tRise/tFall time from 0.7 ns to 8 ns show up to 14 dB of EMI reduction.

The tRise/tFall feature also allows the Si50x to match competing devices' rise and fall times. Crystal oscillator tRise/tFall behavior is largely dependent on the supply voltage. In crystal-based oscillators, a higher supply voltage will generally drive a more rapid tRise/tFall time. The Si50x configuration options allow the user to match the tRise/tFall to the supply voltage. The Si50x also provides a specified tRise/tFall with a given supply voltage and a 50  $\Omega$  trace impedance. See Table 3 for Si50x tRise/tFall specifications.

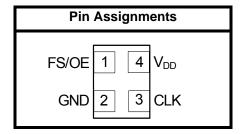

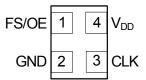

### 4. Pin Descriptions

Figure 9. Si501/2/3

**Table 11. Pin Description**

| Pin | Name            | Function                                                                                           |

|-----|-----------------|----------------------------------------------------------------------------------------------------|

| 1   | FS/OE           | FS=Frequency Select. Si502 and Si503 only. OE=Output Enable. Si501 and Si502 only.                 |

| 2   | GND             | Ground.                                                                                            |

| 3   | CLK             | Output clock.                                                                                      |

| 4   | V <sub>DD</sub> | Power supply. Bypass with a $0.1 \mu F$ capacitor placed as close to the $V_{DD}$ pin as possible. |

### 5. Ordering Guide

The Si50x family of CMEMS oscillators are highly configurable. Each orderable part number must be specified according to the guidelines below. Each customized part's performance is guaranteed to operate within the data sheet specifications. An on-line configuration and ordering tool is available at <a href="https://www.siliconlabs.com/cmems">www.siliconlabs.com/cmems</a>.

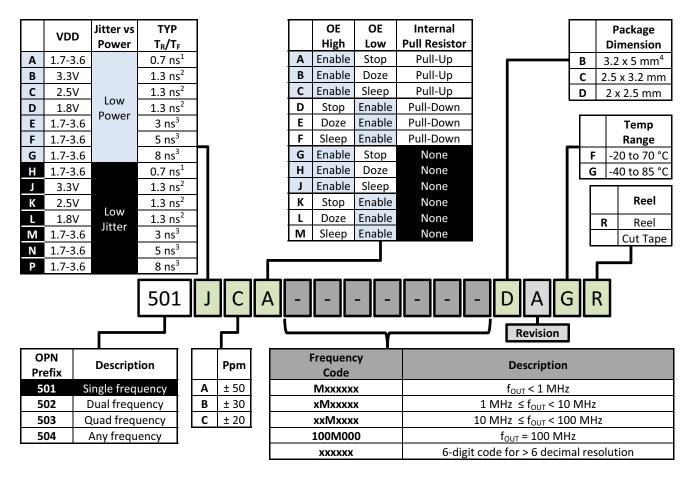

### 5.1. Si501 Ordering Guide and Part Number Syntax

### Note:

- 1. Series termination resistor (R<sub>S</sub>) is recommended for this configuration. See Table 3 and Section 2.

- 2. Series termination resistor is not needed for this configuration. Output impedance is 50  $\Omega$  for the indicated supply condition.

- 3. Series termination resistor is not needed for this configuration. Reduced EMI setting.

- **4.** Silicon Labs 3.2 x 5 mm package is delivered as 3.2 x 4 mm and accommodates the industry-standard 3.2 x 5 mm footprint.

Figure 10. Si501 Part Number Syntax

#### TYP OE Internal Jitter vs **Package** VDD Low<sup>5</sup> **Pull Resistor Power** $T_R/T_F$ Dimension 1.7-3.6 0.7 ns<sup>1</sup> Stop Pull-Up В 3.2 x 5 mm<sup>4</sup> В Pull-Up 1.3 ns<sup>2</sup> Doze 3.3V 2.5 x 3.2 mm C Pull-Up C 2.5V 1.3 ns<sup>2</sup> Sleep D 2 x 2.5 mm Low None D 1.8V 1.3 ns<sup>2</sup> D Stop Power Doze 3 ns<sup>3</sup> Ε None Ε 1.7-3.6 Temp 1.7-3.6 $5 \text{ ns}^3$ Sleep None Range G 1.7-3.6 8 ns<sup>3</sup> -20 to 70 °C 1.7-3.6 0.7 ns<sup>1</sup> G -40 to 85 °C 3.3V 1.3 ns<sup>2</sup> Reel Κ 2.5V 1.3 ns<sup>2</sup> Low 1.8V 1.3 ns<sup>2</sup> Reel Jitter M 1.7-3.6 3 ns<sup>3</sup> Cut Tape 1.7-3.6 5 ns<sup>3</sup> 1.7-3.6 8 ns<sup>3</sup> 502 Revision OPN Frequency Description Ppm Description **Prefix** Code 501 Single frequency Α ± 50 6-digit code from Silicon Labs xxxxx В 502 **Dual frequency** ± 30 503 Quad frequency C ± 20

### 5.2. Si502 Ordering Guide and Part Number Syntax

### Note:

504

Any frequency

- 1. Series termination resistor (R<sub>S</sub>) is recommended for this configuration. See Table 3 and Section 2.

- 2. Series termination resistor is not needed for this configuration. Output impedance is 50  $\Omega$  for the indicated supply condition.

- 3. Series termination resistor is not needed for this configuration. Reduced EMI setting.

- **4.** Silicon Labs 3.2 x 5 mm package is delivered as 3.2 x 4 mm and accommodates the industry-standard 3.2 x 5 mm footprint.

- 5. The Si502 OE pin has three (3) states: OE High = Freq 1; OE Weak High = Freq 2; OE Low is configurable.

Figure 11. Si502 Part Number Syntax

#### Jitter vs **TYP** Internal **Package VDD Power** $T_R/T_F$ **Pull Resistor** Dimension 0.7 ns1 Α Pull-Up 1.7-3.6 3.2 x 5 mm<sup>4</sup> В В 3.3V 1.3 ns<sup>2</sup> None C 2.5 x 3.2 mm 2.5V $1.3 \text{ ns}^2$ D 2 x 2.5 mm Low 1.3 ns<sup>2</sup> D 1.8V Power Ε 1.7-3.6 $3 \text{ ns}^3$ Temp 1.7-3.6 5 ns<sup>3</sup> Range **G** 1.7-3.6 8 ns<sup>3</sup> -20 to 70 °C 1.7-3.6 0.7 ns<sup>1</sup> -40 to 85 °C G 3.3V 1.3 ns<sup>2</sup> Reel K $1.3 \text{ ns}^2$ 2.5V Low 1.8V 1.3 ns<sup>2</sup> Reel Jitter M 1.7-3.6 $3 \, ns^3$ **Cut Tape** N 1.7-3.6 $5 \text{ ns}^3$ 1.7-3.6 8 ns<sup>3</sup> 503 Revision OPN Frequency Description Ppm Description **Prefix** Code 501 Single frequency Α ± 50 6-digit code from Silicon Labs XXXXXX

### 5.3. Si503 Ordering Guide and Part Number Syntax

### Note:

502

503

504

**Dual frequency**

Quad frequency

Any frequency

В

C

± 30

± 20

- 1. Series termination resistor (R<sub>S</sub>) is recommended for this configuration. See Table 3 and Section 2.

- 2. Series termination resistor is not needed for this configuration. Output impedance is 50  $\Omega$  for the indicated supply condition.

- 3. Series termination resistor is not needed for this configuration. Reduced EMI setting.

- **4.** Silicon Labs 3.2 x 5 mm package is delivered as 3.2 x 4 mm and accommodates the industry-standard 3.2 x 5 mm footprint.

Figure 12. Si503 Part Number Syntax

# 6. Package Dimensions and Land Patterns

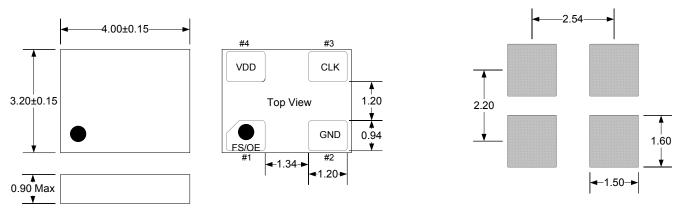

### 6.1. Package Outline: 3.2 x 5 mm 4-pin DFN

Note: Layout and pin-compatible with industry-standard 3.2 x 5 mm footprint.

Figure 13. 3.2 x 5 mm 4-pin DFN

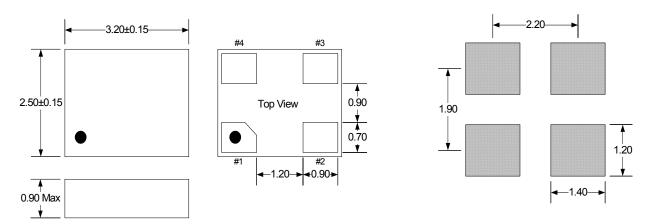

### 6.2. Package Outline: 2.5 x 3.2 mm 4-pin DFN

Figure 14. 2.5 x 3.2 mm 4-pin DFN

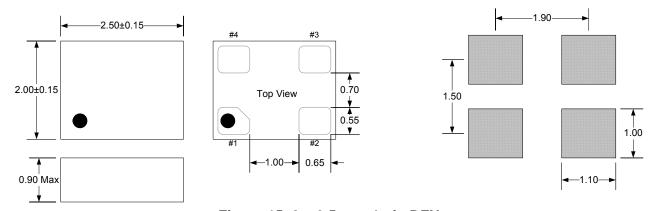

### 6.3. Package Outline: 2 x 2.5 mm 4-pin DFN

Figure 15. 2 x 2.5 mm 4-pin DFN

# 7. Top Markings

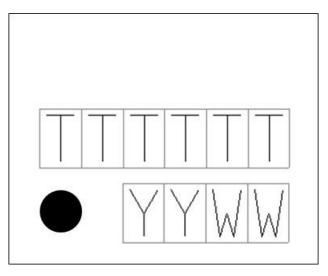

# 7.1. 3.2 x 5 mm Top Marking

# 7.2. 3.2 x 5 mm Top Marking Explanation

| Mark Method:    | Laser                                       |                                                                                                |

|-----------------|---------------------------------------------|------------------------------------------------------------------------------------------------|

| Font Size:      | 0.60 mm<br>Right-Justified                  |                                                                                                |

| Line 1 Marking: | TTTTTT=Trace Code                           | Manufacturing Code from the Assembly Purchase Order form.                                      |

| Line 2 Marking  | Circle=0.5 mm<br>Diameter<br>Left-Justified | Pin 1 Indicator                                                                                |

|                 | YY=Year<br>WW=Work Week                     | Assigned by the Assembly House.<br>Corresponds to the year and work<br>week of the build date. |

# 7.3. 2.5 x 3.2 mm Top Marking

# 7.4. 2.5 x 3.2 mm Top Marking Explanation

| Mark Method:    | Laser                                    |                                                                                                |

|-----------------|------------------------------------------|------------------------------------------------------------------------------------------------|

| Font Size:      | 0.50 mm<br>Right-Justified               |                                                                                                |

| Line 1 Marking: | TTTTT=Trace Code                         | Manufacturing Code from the Assembly Purchase Order form.                                      |

| Line 2 Marking: | Circle=0.3 mm Diameter<br>Left-Justified | Pin 1 Indicator                                                                                |

|                 | Y=Year<br>WW=Work Week                   | Assigned by the Assembly House.<br>Corresponds to the year and work<br>week of the build date. |

# 7.5. 2 x 2.5 mm Top Marking

# 7.6. 2 x 2.5 mm Top Marking Explanation

| Mark Method:    | Laser                                    |                                                                                                |

|-----------------|------------------------------------------|------------------------------------------------------------------------------------------------|

| Font Size:      | 0.50 mm<br>Right-Justified               |                                                                                                |

| Line 1 Marking: | TTTT=Trace Code                          | Manufacturing Code from the Assembly Purchase Order form.                                      |

| Line 2 Marking: | Circle=0.3 mm Diameter<br>Left-Justified | Pin 1 Indicator                                                                                |

|                 | Y=Year<br>WW=Work Week                   | Assigned by the Assembly House.<br>Corresponds to the year and work<br>week of the build date. |

### **DOCUMENT CHANGE LIST**

### Revision 0.2 to Revision 0.3

- Combined Si501/2/3 data sheets.

- Modified title page.

- Modified Table 2.

- Modified Table 4.

- Modified Section 2.

- Modified Section 3.

- Modified Section 4.

- Modified Section 5.

### Revision 0.3 to Revision 0.4

- Modified title page.

- Modified Table 1.

- Modified Table 2.

- Modified Table 3.

- Modified Table 4.

- Modified Table 5.

- Modified Table 6.

- Modified Table 7.

- Modified Section 2.

- Modified Section 4.

- Modified Section 5.

- Modified Section 6.

### **Revision 0.4 to Revision 0.41**

■ Modified Table 4.

### Revision 0.41 to Revision 0.7

- Revised supported frequency range.

- Added MIN/MAX figures to all relevant tables.

### **Revision 0.7 to Revision 0.71**

- Revised Table 3.

- Revised Section 5.

### Revision 0.71 to Revision 0.72

- Revised Table 1.

- Revised Table 2.

- Revised Table 3.

- Revised Table 5.

- Modified Section 2.

- Added Section 3.

- Modified Section 4.

### **Revision 0.72 to Revision 1.0**

- Updated Table 3.

- Updated Section 6.

### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Standard Clock Oscillators category:

Click to view products by Silicon Labs manufacturer:

Other Similar products are found below:

EP1400SJTSC-125.000M 601137 601252 CSX750FBC-24.000M-UT CSX750FBC-33.333M-UT CSX750FCC-3.6864M-UT F335-12 F335-25 DSC506-03FM2 ASA-20.000MHZ-L-T ASA-25.000MHZ-L-T ASA-27.000MHZ-L-T ASV-20.000MHZ-LR-T ECS-2018-160-BN-TR EL13C7-H2F-125.00M MXO45HS-2C-66.6666MHZ SiT1602BI-22-33E-50.000000E SIT8003AC-11-33S-2.04800X SiT8256AC-23-33E-156.250000X SIT8918AA-11-33S-50.000000G SM4420TEV-40.0M-T1K SMA4306-TL-H F335-24 F335-40 F335-50 F535L-10 F535L-12 F535L-16 F535L-27 F535L-48 PE7744DW-100.0M CSX750FBC-20.000M-UT CSX-750FBC333333000T CSX750FBC-4.000M-UT CSX750FBC-7.3728M-UT CSX750FBC-8.000M-UT CSX-750FCC14745600T CSX750FCC-16.000M-UT CSX-750FCC40000000T CSX750FCC-4.000M-UT ASA-22.000MHZ-L-T ASA-26.000MHZ-L-T ASA-40.000MHZ-L-T ASA-48.000MHZ-L-T ASA-60.000MHZ-L-T ASA-60.000MHZ-L-T ASF1-3.686MHZ-N-K-S XLH735025.000JU418 XLP725125.000JU618 XO37CTECNA10M XO57CRECNA16M