# Si3474 Data Sheet

# Up to four 802.3bt or eight 802.3at Ethernet Port PoE PSE Controllers

The Si3474 is a fully programmable, 50 to 57 V power management controller for IEEE 802.3af, 802.3at, and 802.3bt compliant Power Sourcing Equipment (PSE). Designed for use in PSE endpoints (switches), the Si3474 integrates eight independent ports, each with the IEEE-required powered device (PD) detection and classification functionality. When used in 802.3af/802.3at (two-pair power) mode each PSE port supports one Ethernet connection, for a total of eight PoE Ethernet connections. 802.3bt operation (four-pair power) uses two PSE ports per Ethernet connection, for a total of four PoE Ethernet connections.

In addition, the Si3474 features a fully-programmable architecture that enables powered device (PD) disconnect using dc-sense algorithms, a robust multipoint detection algorithm, software configurable per-port current and voltage monitoring, and programmable current limits to support the IEEE 802.3af, 802.3at, and 802.3bt standards. Intelligent protection circuitry includes input undervoltage detection, output current limit, and short-circuit protection. The Si3474 operates autonomously or by host processor control through a two wire, I<sup>2</sup>C compatible serial interface. An interrupt pin is used to alert the host processor of various status and fault conditions.

#### **Applications**

- IEEE 802.3af, 802.3at, and 802.3bt Power Sourcing Equipment (PSE)

- · Power over Ethernet Switches

- · IP Phone Systems

- · Smartgrid Switches

- · Ruggedized and Industrial Switches

#### **KEY FEATURES**

- Octal-Port Power Sourcing Equipment (PSE) controller

- IEEE 802.3af, 802.3at, and 802.3bt compliant

- Autonomous or I<sup>2</sup>C host interface

- Emergency Shutdown support with port priority control

- Adds enhanced features for maximum design flexibility:

- · Per-port current and voltage monitoring

- · Multi-point detection

- Programmable power MOSFET gate drive control

- Configurable watchdog timer enables failsafe operation

- · Maskable interrupt pin

- Comprehensive fault protection circuitry includes:

- · Power undervoltage lockout

- Output current limit and short-circuit protection

- · Thermal overload detection

- Extended operating temp range: –40 to +85 °C

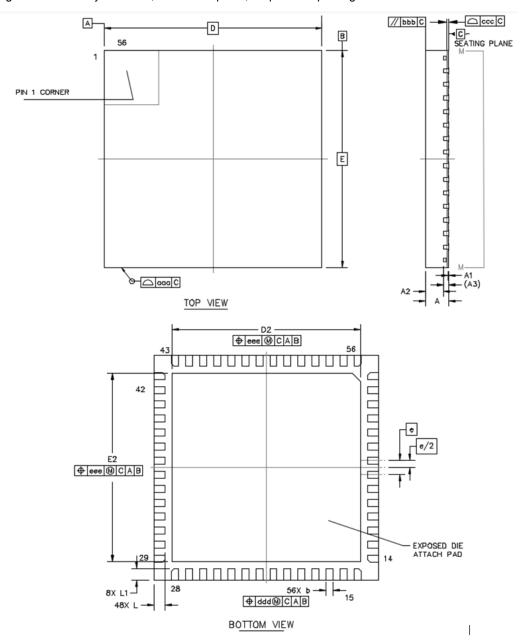

- 56-pin, 8 x 8 mm QFN package (RoHScompliant)

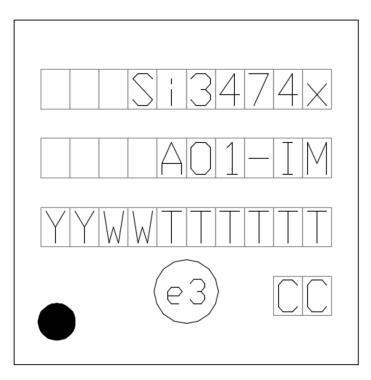

# 1. Ordering Guide

Table 1.1. Si3474 Ordering Guide

| Ordering<br>Part Number <sup>1</sup> | Product Revision | Current Sense<br>Resistor <sup>2</sup> | Package                                | Temperature Range (Ambient) |

|--------------------------------------|------------------|----------------------------------------|----------------------------------------|-----------------------------|

| Si3474A-A01-IM                       | A01              | 255 mΩ                                 | 56-pin, 8 x 8 mm QFN<br>RoHS-compliant | –40 to 85 °C                |

| Si3474B-A01-IM                       | A01              | 200 mΩ                                 | 56-pin, 8 x 8 mm QFN<br>RoHS-compliant | –40 to 85 °C                |

## Note:

- 1. Add an "R" to the end of the part number for tape and reel option (e.g., Si3474A or Si3474A-A01-IMR).

- 2. Options include industry-standard 255 m $\Omega$  or more thermally efficient 200 m $\Omega$  sense resistor.

# **Table of Contents**

| 1. | Ordering Guide                                                       |   |  |  | . 2 |

|----|----------------------------------------------------------------------|---|--|--|-----|

| 2. | Functional Description                                               |   |  |  | . 6 |

|    | 2.1 Overview                                                         |   |  |  | . 6 |

|    | 2.2 Functional Block Diagram                                         |   |  |  | . 6 |

|    | 2.3 Operational Modes                                                |   |  |  |     |

|    | 2.3.1 Autonomous Mode                                                |   |  |  |     |

|    | 2.3.3 Manual Mode                                                    |   |  |  |     |

|    | 2.4 Host Interface                                                   |   |  |  | . 8 |

|    | 2.5 Reset and Initialization                                         |   |  |  | . 9 |

|    | 2.6 Semi-Auto Detection, Connection Check, and Class Probe           |   |  |  | .10 |

|    | 2.7 Powering Up                                                      |   |  |  | .12 |

|    | 2.7.1 Power Demotion                                                 |   |  |  |     |

|    | 2.7.2 Final Detection, Connection Check, and Class Probe             |   |  |  |     |

|    | 2.8 Powered States                                                   |   |  |  |     |

|    | 2.8.1 FET On Status                                                  |   |  |  | .15 |

|    | 2.8.2 Inrush Period                                                  |   |  |  |     |

|    | 2.8.4 Autoclass                                                      |   |  |  |     |

|    | 2.8.5 Current Limit and Voltage Foldback                             |   |  |  |     |

|    | 2.9 Event Handling                                                   |   |  |  | .19 |

|    | 2.10 Autonomous Operation                                            |   |  |  |     |

|    | 2.10.1 AUTO Pin Autonomous Mode                                      |   |  |  |     |

|    | 2.10.2 I <sup>2</sup> C Autonomous Mode                              |   |  |  |     |

|    | 2.11 OSS Operation                                                   |   |  |  |     |

|    | 2.12 I <sup>2</sup> C Interface                                      |   |  |  |     |

|    | 2.12.1 I <sup>2</sup> C Protocol                                     |   |  |  |     |

|    | 2.13 Bootloader                                                      |   |  |  | .24 |

|    | 2.13.1 Updating Si3474 Flash                                         |   |  |  | .24 |

| 3. | Typical Application Example                                          |   |  |  | 26  |

| 4. | Register Map                                                         |   |  |  | 27  |

|    | 4.1 INTERRUPT Register (Address 0x00)                                |   |  |  | .34 |

|    | 4.2 INTERRUPT_MASK Register (Address 0x01)                           |   |  |  | .35 |

|    | 4.3 Event Registers                                                  |   |  |  | .37 |

|    | 4.4 POWER Event and POWER Event CoR (Address 0x02, 0x03)             |   |  |  | .38 |

|    | 4.5 CLASS_DETECT_EVENT and CLASS_DETECT_EVENT CoR (0x04, 0x05)       |   |  |  | .39 |

|    | 4.6 DISCONNECT PCUT FAULT and DISCONNECT PCUT FAULT CoR (0x06, 0x07) | _ |  |  | 40  |

| 4.7 ILIM_START_FAULT and ILIM_START_FAULT COR (0x08, 0x09)                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------|

| 4.8 SUPPLY_EVENT and SUPPLY_EVENT CoR (0x0A, 0x0B)                                                                             |

| 4.9 POWER_ON_FAULT and POWER_ON_FAULT CoR (0x24, 0x25)                                                                         |

| 4.10 CLASS_DETECT_STATUS Registers (0x0C-0x0F)                                                                                 |

| 4.11 PORT_POWER_STATUS Register (0x10)                                                                                         |

| 4.12 PORT_MODE (0x12)                                                                                                          |

| 4.13 DISCONNECT_ENABLE (0x13)                                                                                                  |

| 4.14 DETECT_CLASS_ENABLE (0x14)                                                                                                |

| 4.15 POWER_PRIORITY_PCUT_DISABLE (0x15)                                                                                        |

| 4.16 TIMING_CONFIG (0x16)                                                                                                      |

| 4.17 MISC (0x17)                                                                                                               |

| 4.18 PB_DETECT_CLASS (0x18)                                                                                                    |

| 4.19 PB_POWER_ENABLE (0x19)                                                                                                    |

| 4.20 PB_RESET (0x1A)                                                                                                           |

| 4.21 VENDOR_ID (0x1B), FIRMWARE_REVISION (0x41), CHIP_REVISION (0x43)                                                          |

| 4.22 AUTOCLASS_CONNECTION_CHECK (0x1C)                                                                                         |

| 4.23 PORT1_POLICE_2P to PORT4_POLICE_2P, PORT12_POLICE_4P, PORT34_POLICE_4P (0x1E – 0x21, 0x2A, 0x2B)                          |

| 4.24 PORT_REMAP (0x26)                                                                                                         |

| 4.25 PORTn_MULTIBIT_PRIORITY (0x27, 0x28)                                                                                      |

| 4.26 POWER_ALLOCATION (0x29)                                                                                                   |

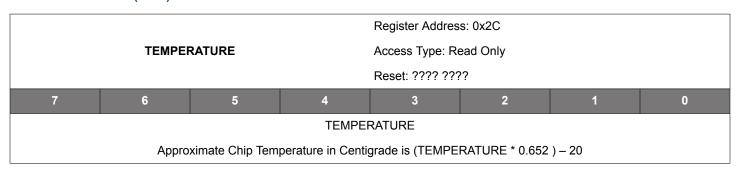

| 4.27 TEMPERATURE (0x2C)                                                                                                        |

| 4.28 ILIM_PCUT_DISCONNECT_4P (0x2D)                                                                                            |

| 4.29 Parametric Measurement Registers (0x2E – 0x3F)                                                                            |

| 4.30 VPWR, PORT1_VOLTAGE, PORT2_VOLTAGE, PORT3_VOLTAGE, PORT4_VOLTAGE (0x2E/ 0x2F, 0x32/0x33, 0x36/0x37, 0x3A/0x3B, 0x3E/0x3F) |

| 4.31 PORT1_CURRENT, PORT2_CURRENT, PORT3_CURRENT, PORT4_CURRENT (0x30/0x31, 0x34/0x35, 0x38/0x39, 0x3C/0x3D)                   |

| 4.32 MAX_ILIM_MANUAL_POLICE (0x40)                                                                                             |

| 4.33 I2C_WATCHDOG (0x42)                                                                                                       |

| 4.34 DETECT_RESISTANCE (0x44 - 0x47)                                                                                           |

| 4.35 DETECT_CAPACITANCE (0x48 – 0x4B)                                                                                          |

| 4.36 CLASS_RESULTS (0x4C - 0x4F)                                                                                               |

| 4.37 AUTOCLASS_CONTROL (0x50)                                                                                                  |

| 4.38 PORT1_AUTOCLASS_RESULTS, PORT2_AUTOCLASS_RESULTS, PORT3_AUTOCLASS_RESULTS, PORT4_AUTOCLASS_RESULTS (0x51 - 0x54)          |

| 4.39 ALTERNATIVE_FOLDBACK (0x55)                                                                                               |

| 4.40 FLASH REGISTERS (0x5F – 0x63)                                                                                             |

| Flectrical Characteristics Si3474                                                                                              |

| 6. Pin Descriptions  |          |     |    |    |  |  |  |  | • |  |  |  |  |  |  |  | 76 |

|----------------------|----------|-----|----|----|--|--|--|--|---|--|--|--|--|--|--|--|----|

| 7. Package Outline:  | 56-      | Pin | QF | -N |  |  |  |  |   |  |  |  |  |  |  |  | 79 |

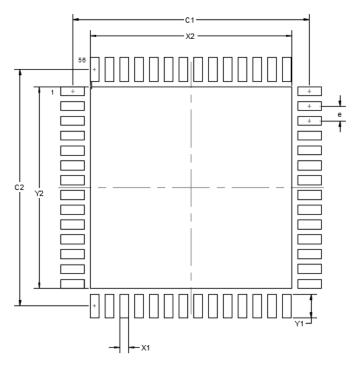

| 8. Land Pattern .    |          |     |    |    |  |  |  |  |   |  |  |  |  |  |  |  | 8′ |

| 9. Top Marking       |          |     |    |    |  |  |  |  |   |  |  |  |  |  |  |  | 83 |

| 10. Revision History | <i>ı</i> |     |    |    |  |  |  |  |   |  |  |  |  |  |  |  | 84 |

#### 2. Functional Description

#### 2.1 Overview

Integrating a high-performance microcontroller with high-resolution A/D and D/A capabilities, along with eight independent, high-voltage PSE port interfaces, the Si3474 enables an extremely flexible solution for virtually any PoE switch application. The Si3474 integrates all PSE controller functions needed for an octal-port PoE design.

The Si3474 includes many additional features that can be individually enabled or disabled by programming the extended register set appropriately.

- · Per-port current / voltage monitoring and measurement

- · Multipoint detection algorithms

- · Programmable gate drive for external MOSFETs

- Watchdog timer (WDT)

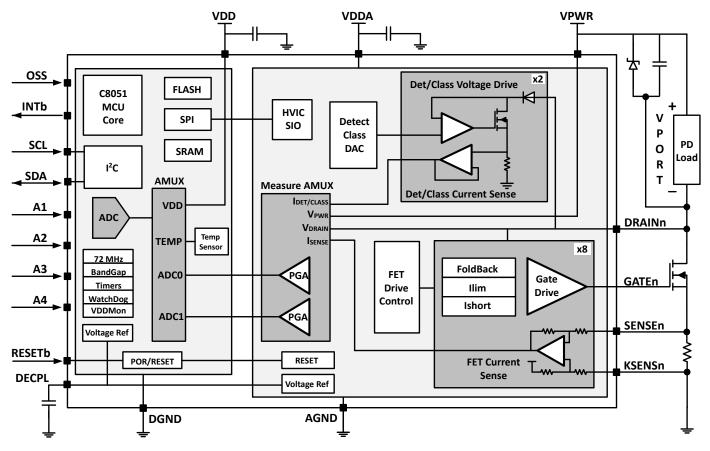

#### 2.2 Functional Block Diagram

Figure 2.1. Si3474 Functional Block Diagram

## 2.3 Operational Modes

The Si3474 has three different operating modes: Autonomous, Semi-Autonomous, and Manual, plus one non-operating mode, Shutdown. The appropriate operating mode can be chosen depending on system requirements, such as whether the PSE system is power-constrained, whether the PSE system has a power manager host, or whether the PSE system must identify any power-non-conforming PD loads.

#### 2.3.1 Autonomous Mode

Autonomous Mode should only be used in PSE systems where there is enough power to power all ports simultaneously to their total allocated power. In other words, Autonomous Mode can only be used in non-power constrained PSE systems. In Autonomous mode, the Si3474 will automatically detect, classify and power on ports that present a valid PD signature without any external host interaction.

There are two methods to place the Si3474 into Autonomous mode. One method is to configure the AUTO pin using an external voltage and power cycling the Si3474. The following types of systems are suitable for AUTO pin Autonomous Mode:

- Homogenous ports configuration. For each Si3474, all ports must be configured as either four-pair powered ports (4P) or all ports configured as two-pair powered ports (2P).

- · Each port must have the same Power Allocation setting.

- PSE system must be able to supply sufficient VPWR current to all ports under maximum loading.

The second method is to an external host processor to configure and start the Autonomous Mode through the I<sup>2</sup>C registers. For systems whose ports are not homogenous or if the ports are to have different power allocations, use I<sup>2</sup>C Autonomous Mode instead of the AUTO pin. Whether Autonomous Mode is invoked by the AUTO pin or by the I<sup>2</sup>C interface, the I<sup>2</sup>C register interface remains active so an external host processor can poll the event registers, for example, to control indicator LEDs.

For more details on autonomous operation, refer to 2.10.1 AUTO Pin Autonomous Mode and 2.10.2 I<sup>2</sup>C Autonomous Mode.

#### 2.3.2 Semi-Autonomous Mode

In PSE systems with high port counts, rarely is there a PSE system power supply that is capable of powering all ports to their maximum load simultaneously. The Si3474 I<sup>2</sup>C register interface is designed to accommodate a host processor to act as a power manager that can choose or deny PD power requests as new PD loads are attached. In these systems, the Si3474 controller performs low level PoE protocols with the PD loads and provides real-time fault monitoring and power consumption measurements required by the external host processor to perform power management. For these hosted, power-constrained systems, the Si3474 operates in Semi-Autonomous mode.

#### 2.3.3 Manual Mode

Manual mode is special case of Semi-Autonomous mode where the external host processor forces a condition on the port(s) that bypasses the low-level PoE protocol. For example, forcing a port to power on a PD load immediately without exercising detection and classification protocol. As such, manual mode should be used for diagnostic or debug purposes only.

#### 2.4 Host Interface

The Si3474 communicates with the host processor through an I<sup>2</sup>C interface using:

- Registers

- Events

- Pushbuttons

In this data sheet, register names, fields and bits are listed in all capitals. Some have prefixes such as PORTn\_ or PORTnm\_. The PORTn\_ describes attributes that are associated with 2P ports. The prefix PORTnm\_ applies to attributes associated with 4P ports. Some registers are global to the entire Si3474. Some registers are associated with one set of four 2P ports (quad). The Si3474 has two quads and the second set of four 2P ports are accessed in the same register but through the alternate I<sup>2</sup>C address. Refer to 4. Register Map for a complete listing of registers.

During operation, the Si3474 monitors global conditions such as temperature and supply voltage, and some conditions that are associated with the individual PoE ports. When an event occurs, the Si3474 will drive the INTb pin low. The host processer will then read the INTERRUPT register and decode what event has occurred. The Si3474 drives the INTb low until the appropriate Clear-on-Read (CoR) register is read by the host processor.

There are some events in which cause the Si3474 to take immediate action without instructions from the host, and there are some that are intended to be indicators to allow the host processor to take desired actions as its role being the PSE system power manager. Once the host receives notification of an event, it is expected to act upon that event. The details and mechanics of event handling is described in 2.9 Event Handling.

The host processor can instruct the Si3474 to take certain actions through a Pushbutton (PB) command. All write-only registers are Pushbutton registers. A register designated as Pushbutton will always return as zero when read. Some read-write registers can also act as pushbuttons depending on the context as described in .

Each Si3474 port can be in one of four operational modes, controlled by the PORT\_MODE register. PORTn\_PORT\_MODE can be set to:

- SHUTDOWN

- MANUAL

- SEMI AUTO

- AUTO

The AUTO mode is most applicable to a non-hosted PSE system. The MANUAL mode is used primarily for diagnostic and debug purposes. For hosted PSE systems, SHUTDOWN and SEMI\_AUTO port modes are the most important. When PORTn\_PORT\_MODE is set to SHUTDOWN, that port is in an idle state, ready to be configured by the host.

A port enters SHUTDOWN by:

- A hard reset (power on reset or by deasserting RESETb pin)

- Setting RESET QUAD in PB RESET register sets all ports in that quad to SHUTDOWN

- Setting individual PORTn\_RESET\_PORT in PB\_RESET register. Each port has a dedicated bit

- · Any SUPPLY\_EVENT sets all ports to SHUTDOWN

- An I<sup>2</sup>C WATCHDOG event is equivalent to a RESET\_QUAD that sets all ports to SHUTDOWN

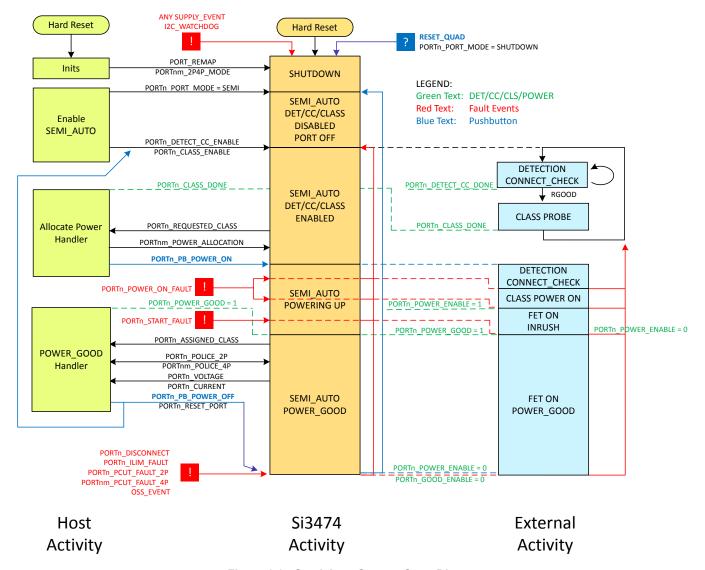

A port in SEMI\_AUTO mode, when combined with PORTn\_DETECT\_CC\_ENABLE and PORTn\_CLASS\_ENABLE, instructs the Si3474 to actively look for connected PDs on a port. In a power-managed, hosted PSE system, the figure below describes the key interactions and events between the power manager host and the PoE port conditions in the Si3474. The following sections describe the control flow of a Semi-Auto PSE.

Figure 2.2. Semi-Auto System State Diagram

#### 2.5 Reset and Initialization

Hard resets are invoked by either cycling power (Power on Reset or PoR) and/or deasserting RESETb input. After a hard reset, all registers are set to default values. A PoR will always set all registers to default values. Invoking a hard reset by deasserting the RESETb input will set all registers to default values except the upper nibble of SUPPLY\_EVENT to default values. The upper nibble is sticky until the condition that is causing the global event is cleared. For specific information, refer to 4.8 SUPPLY\_EVENT and SUPPLY\_EVENT COR (0x0A, 0x0B).

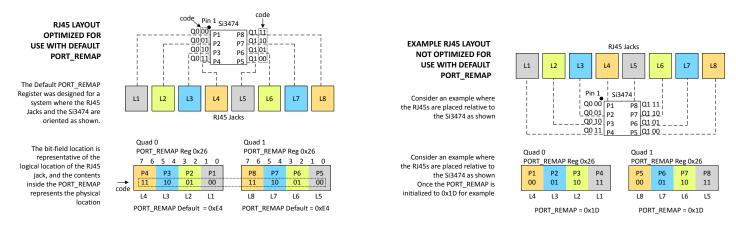

Immediately after a hard reset, the host must initialize at least two registers, the PORT\_REMAP register and the PORTnm\_2P4P\_MODE field in POWER\_ALLOCATION register. These registers must be set to match the hardware configuration, ex. how the ports are wired, of the PSE system. For specifics, refer 4.24 PORT\_REMAP (0x26) and 4.26 POWER\_ALLOCATION (0x29). These two registers once written to, are locked until a hard reset of the Si3474 to unlock them again.

During the initialization, the host can set other global registers as needed.

#### 2.6 Semi-Auto Detection, Connection Check, and Class Probe

The host instructs the Si3474 to start detecting attached PDs by setting:

- PORTn PORT MODE = SEMI AUTO

- PORTn DETECT CC ENABLE and PORTn CLASS ENABLE in DETECT CLASS ENABLE

Prior to driving the detection waveform, the Si3474 performs a check that the port's external FET is properly off and is not damaged. The first test is a current measurement across the external sense resistor and the second test is a voltage measurement at the DRAINx pin. If excessive current detected or an unexpected drain voltage, PORTn\_DETECTION\_STATUS will indicate a MOSFET\_FAULT and detection is aborted.

The Si3474 detects a PD by making a differential resistance measurement by driving 4 V to 8 V and back to 4 V on each enabled port through the DRAINx pin, while measuring current at each step. The results are used to calculate measured detection resistance, also known as the PD Signature Resistance, which is nominally 25 k $\Omega$ . The Si3474 reports the detection results in the PORTn\_DETECTION STATUS field of the PORTn\_DETECT CLASS\_STATUS registers.

During detection the Si3474 monitors the voltage driven for evidence of a contention with another PSE driving the same line. If the measured voltage deviates significantly from the driven voltage, PORTn\_DETECTION\_STATUS will report a PSE to PSE fault. The Si3474 also uses the voltage/current measurements taken during the detection waveform to determine if the PD Signature Resistance measures too capacitive and reports in the PORTn\_DETECTION\_STATUS.

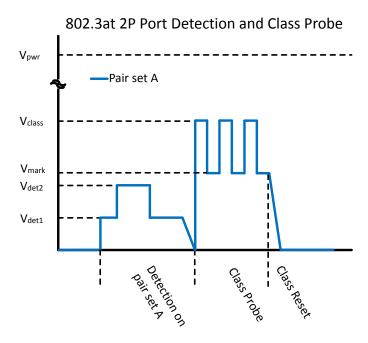

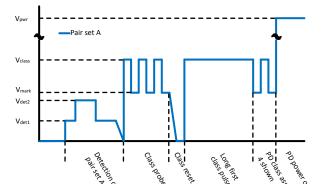

If the port is configured as a 2P port, a DETECT\_CC\_DONE event will be reported to the host after the detection sequence. If the detection result is RGOOD, the Si3474 begins a class probe to determine the PD's class signature. A class probe will always consist of three class fingers to determine the PD requested power followed by a class reset. The following figure shows the expected waveform for a 2-Pair powered PD.

Figure 2.3. Semi-Auto DET/CLASS 2-Pair Waveform

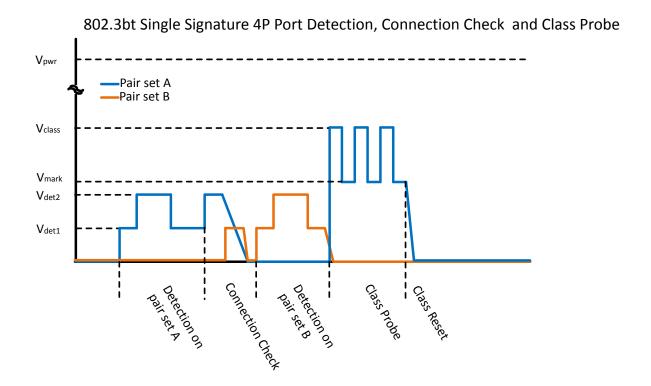

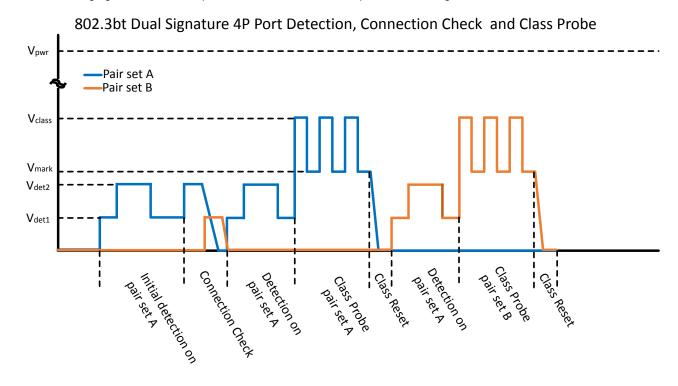

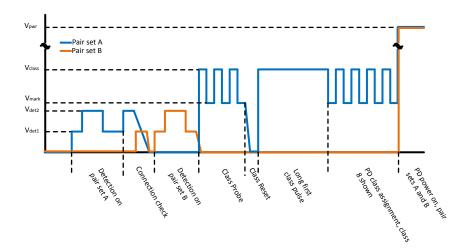

The sequence changes if the port is configured to be a 4P port. After one of the two ports that comprise a 4P port detects a valid PD detection signature, a connection check (CC) is performed to determine if the attached PD is a single-signature PD or a dual signature PD. If the connection check indicates a single-signature PD, then Si3474 indicates a DETECT\_CC\_DONE and continues onto class probe on the primary pairset that detected the valid PD detection signature. The following figure shows the expected waveform for a 4-Pair powered single signature PD.

Figure 2.4. Semi-Auto DET/CC/CLASS 4-Pair Single-Signature Waveform

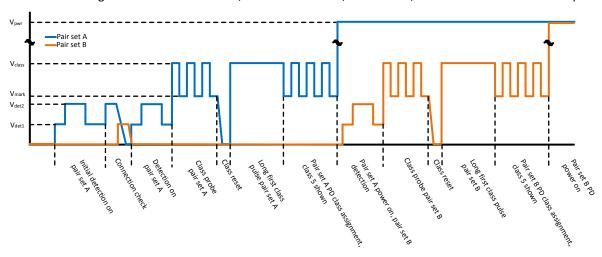

If the connection check indicates a dual-signature PD, the Si3474 detects and class probes on both the primary and secondary pairsets. The following figure shows the expected waveform for a 4-Pair powered dual-signature PD.

Figure 2.5. Semi-Auto DET/CC/CLASS 4-Pair Dual-Signature Waveform

Upon class probe completion, the Si3474 will report a PORTn\_CLASS\_DONE event and place the requested power in the PORTn\_CLASS\_STATUS field of the PORTn\_DETECT\_CLASS\_STATUS register and in the PORTn\_REQUESTED\_CLASS field in the PORTn\_CLASS\_RESULTS register.

#### 2.7 Powering Up

A port is ready to be powered on after the PORTn\_CLASS\_DONE event is reported. The host can examine the results of the PORTn\_CLASS\_STATUS to discover the PD's requested class. The host can then set or adjust the PORTnm\_POWER\_ALLOCATION as needed, followed by setting the PORTn\_PB\_POWER\_ON for the port.

The Si3474 goes through the sequence of events described in the following subsections.

#### 2.7.1 Power Demotion

Upon powering on a port, the host knows how much power the PD has requested by reading the PD's requested class. If the host determines that it has the requested power available, it will typically set PORTnm\_POWER\_ALLOCATION so that the PD receives the power it has requested. If the host knows it does not have the full power available, it can choose to set the PORTnm\_POWER\_ALLOCATION such that the assigned class will be less than the requested class; this is known as Power Demotion.

A power-demoted PD can request more power at any time through the Ethernet Link-Layer protocol (LLDP). Through LLDP, if the PD requests additional power (and if the PSE has more power to spare at that time), it can then grant the additional power. The host communicates the allowable additional power to the Si3474 by updating the PORTn\_POLICE\_2P or PORTnm\_POLICE\_4P registers without needing to put the port in SHUTDOWN and perform another PORTn\_PB\_POWER\_ON sequence.

When putting a PD in Power Demotion, there are some considerations. There is a risk of encountering a PORTn\_POWER\_ON\_FAULT "Insufficient Power Allocation" in a dual-signature 4P Port if one pair-set consumes all of the power in a way that prevents supplying additional power to the other pair-set. The other nuance is that, when a Class 4 to Class 8 PD is only provided Class 3 power, the PSE can only send one classification finger to the PD. In this case, the Si3474 will supply Class 3 power and communicate report "Class 4+ Type 1 Limited" in PORTn\_CLASS\_STATUS. PORTn\_ASSIGNED\_CLASS will show Class 3, and the PORTn\_REQUESTED\_CLASS shows the result of the Class Probe, which will show Class 4 to Class 8.

#### 2.7.2 Final Detection, Connection Check, and Class Probe

When PORTn\_PB\_POWER\_ON is received by the Si3474, it is likely that it is performing a DET/CC/CLASS PD discovery sequence that is unrelated to the port receiving the PB\_POWER\_ON pushbutton. The Si3474 allows those started sequences to complete before executing the Pushbutton command for the specified port. PB\_POWER\_ON consists of a final set of Detection, Connection Check (for 4P Ports), and Class Power On for the ports that the host wants to power on.

The PB\_POWER\_ON detection sequence is similar to that performed by Semi-Auto Detection, Connection Check and Class Probe, with some slight differences. If the detection results are anything other than RGOOD for the ports being powered up, the PORTn\_POW-ER\_ON\_FAULT event is set to *Invalid Detection*. If the PB\_POWER\_ON is issued to a 4P Port, a connection check will be performed the same way. The Si3474 then performs another Class Probe to reconfirm the PD's requested class followed by a Class Reset.

#### 2.7.3 Class Power On

Unlike Class Probe, Class Power On intends to power on the PD afterwards. The other important factor to consider is that, with Class Power On, the number of classification fingers is significant as the PD will count them so as to learn what power it has been allocated by the Si3474. For example, a Class 4 PD learns it has been power demoted and is allocated only 15.5 W of power if the PSE presents a single classification finger. But, a Class 4 PD learns it may draw the full 30 W if the PSE presents it with two fingers during the Class Power On.

If, during Class Power On, an overcurrent or an invalid classification occurs, the PORTn\_POWER\_ON\_FAULT event is set to *Classification Error*. Another error that will trigger a PORTn\_POWER\_ON\_FAULT event is *Insufficient power allocation*. This can occur when a one pair-set of a dual-signature PD consumes the remaining power allocation and, therefore, there is no power available for the other pair-set. *Insufficient power allocation* is also reported if the host issues a PB\_POWER\_ON to only one pair-set of a Single Signature port and the attached PD requested Class 5 or higher power.

Class Power On results are stored in PORTn\_ASSIGNED\_CLASS. However, PORTn\_CLASS\_STATUS can contain additional information. In the case of a Power Demotion where a Class 4 or higher PD is demoted to Class 3, PORTn\_CLASS\_STATUS will report Class 4+ Type 1 Limited, whereas the PORTn\_ASSIGNED\_CLASS will report Class 3. Refer to Table 4.2 Classification Event Timing on page 67 in 4.36 CLASS\_RESULTS (0x4C - 0x4F) for a comprehensive list of class codes and when they are updated.

The Si3474 sends out a long class pulse on the first finger during Class Power On for two purposes. First, a long first classification finger communicates to the PD that the Si3474 supports Short Maintain Power Signature (MPS) to save more power when in standby. Second, with the initial long class pulse, it is possible to detect if the PD supports Autoclass. Refer to 2.8.4 Autoclass for details.

After Class Power On has completed, the FET is turned on, and the Inrush period begins. The following figure show the entire expected waveforms for a PORTn PB POWER ON for 2P, 4P Single Signature, and 4P Dual Signature PDs.

802.3at 2P Port Detection, Class Probe, Class Power On and Power Up

Figure 2.6. 2P Port Detection Waveform

802.3bt Single Signature 4P Port Detection, Connection Check, Class Probe, Class Power On and Power Up

Figure 2.7. 4P Single-Signature Port Detection Waveform

802.3bt Dual Signature 4P Port Detection, Connection Check, Class Probe, Class Power On and Power Up

Figure 2.8. 4P Dual-Signature Port Detection Waveform

#### 2.8 Powered States

There are two states for which the FET is ON:

- 1. Inrush Period

- 2. Power Good State

#### 2.8.1 FET On Status

Each pair set has the PORTn\_POWER\_ENABLE and PORTn\_POWER\_GOOD status information suitable for tracking the general state of the Si3474 after a PORTn\_PB\_POWER\_ON.

| PORTn_POWER_ENABLE | PORTn_POWER_GOOD | FET State | After PORTn_PB_POWER_ON |

|--------------------|------------------|-----------|-------------------------|

|                    |                  |           | Final Detection         |

|                    |                  | OFF       | Connection Check        |

| 0                  | 0                | OFF       | Class Probe             |

|                    |                  |           | Class Power             |

| 1                  | 0                | ON        | Inrush Period           |

| 1                  | 1                | ON        | Power Good              |

| 0                  | 1                | _         | Invalid                 |

The corresponding events PORTn\_POWER\_ENABLE\_CHANGE and PORT\_POWER\_GOOD\_CHANGE events in the POW-ER\_EVENT register track the changes in the POWER\_ENABLE and the POWER\_GOOD fields in the POWER\_STATUS register.

Changes to PORTn\_POWER\_GOOD and PORTn\_POWER\_ENABLE affects the corresponding events PORTn\_POWER\_GOOD\_CHANGE and PORTn\_POWER\_ENABLE\_CHANGE. These events can be used by the host to check the POWER\_STATUS register to check the most up-to-date port status.

PORTn\_POWER\_GOOD and PORTn\_POWER\_ENABLE elicit changes to the PORTn\_POWER\_GOOD\_CHANGE and PORTn\_POWER\_ENABLE\_CHANGE event bits. Once set, the PORTn\_POWER\_GOOD\_CHANGE and PORTn\_POWER\_ENABLE\_CHANGE bits are typically cleared by reading the POWER\_CHANGE CoR register. In addition, PORTn\_POWER\_GOOD\_CHANGE and PORTn\_POWER\_ENABLE\_CHANGE events are cleared when PORTn\_RESET\_PORT is set, PORTn\_PB\_POWER\_OFF is set, and when a port is turned off as a result of an OSS Event.

#### 2.8.2 Inrush Period

Immediately after the FET is turned on, the Si3474 enters the Inrush Period. The Inrush Period is a fixed time period defined by  $t_{\text{INRUSH}}$ , During the Inrush Period, the Si3474 performs a voltage-foldback function for currents higher than 425 mA in order to limit the current drawn from the VPWR rail. The Si3474 also has a proprietary short-circuit FET protection circuit intended to protect the FET from damage.

The terms "start" and "inrush" are used interchangeably in this document. The Inrush Period is the initial part of a power-on in which the PSE is expected to supply current to the PD's bulk capacitors. As is normal with any capacitor, if permitted, it will consume as much current as the PSE can supply. During the Inrush Period, a port implements a 425 mA current limit, with a 30 V Foldback, during a t<sub>START</sub> or t<sub>INRUSH</sub> time period.

After t<sub>INRUSH</sub>, the port should no longer be in a current-limited state. If the port is still in a current-limited state, the port is powered off, and the PORTn\_START\_FAULT event is raised. Otherwise, the port reaches a POWER\_GOOD state, and the Si3474 begins monitoring the port.

See 2.8.5 Current Limit and Voltage Foldback for an illustration of how current limiting and voltage foldback work.

#### 2.8.3 Power Good State

When a port is in a POWER GOOD state, three things are monitored:

- 1. Disconnection

- 2. ILIM / Current Limit

- 3. PCUT / Power Overload

Of these three things monitored, the Disconnection monitoring is to check if the PD is drawing too little current.

For the next two items, the Si3474 is monitoring for "too much current". The difference between these two over-current monitors is the speed of the action taken.

For ILIM / Current Limit events are considered to be fast, high current events. As such, Si3474 circuits aim to limit the current by reducing port voltage. Under extremely high current conditions, the Si3474 shuts off the port completely to protect the FET from damage.

On the other hand, a PCUT does not involve FETs operating in current-limited state. But rather, the Si3474 is monitoring the port voltage and port current, then comparing them against the POLICE register limits.

#### 2.8.3.1 Disconnection

While in the POWER\_GOOD state, the Si3474 checks whether or not the PD is still connected to the port. A connected PD is obligated to draw a minimum amount of current. To keep the PSE from declaring a disconnection, the PD must meet a "Maintain Power Signature" for time duration of t<sub>MPDO</sub>. If the PD does not meet these MPS requirements, the PSE may choose to power down the port.

When the Si3474 determines that the PD is no longer present, it sets the PORTn DISCONNECTION event.

#### 2.8.3.2 ILIM / Current Limit

Depending on the PD Class, the Si3474 chooses a current-limit template designed to allow normal PD currents to flow, while also setting a peak current threshold to begin a voltage foldback. Ostensibly, the Si3474 implements a number of current limit templates. The current limit template is a 2-dimensional function that defines a current limit against the drain voltage. At low drain voltages, the current limit is set at its maximum.

Whenever the measured port current exceeds these current limits, a feedback circuit then adjusts the gate voltage of the FET to fold-back the voltage. The speed at which the gate voltage is adjusted is a function of the difference between the current limit threshold at the drain voltage against the sensed port current.

The foldback mechanism is done automatically, while the drain voltage is monitored to check for evidence of a current-limited state. The device implements a counter that counts up by 1 whenever the FET is in an over-current state. For every subsequent non-overcurrent event is encountered, the counter is then decreased by 1/16. This allows current limited events to self-clear if it is a transient event. This prevents nuisance disconnections while also allowing disconnecting a port based on the severity of the event.

As a simple example, if the device continuously detects overcurrent for time  $t_{LIM}$  time periods, it will be considered an ILIM fault and remove power from the port.

In addition to the programmable current-limit foldback voltage templates, the Si3474 also implements a separate short circuit monitor so that if the difference between the measured current and the current limit is very large, the FET is turned off. In a certain sense, turning off a FET is a form of "extreme foldback". This is implemented this way as it intends to protect the FET in the case of an unexpected short-circuit.

Current Limit faults are reported through the PORTn\_ILIM\_FAULT in the ILIM\_START\_FAULT register.

2.8.5 Current Limit and Voltage Foldback shows an illustration of how current limiting and voltage foldback works.

## 2.8.3.3 PCUT Faults

After the Class Power On, both the PSE and PD would have a mutual understanding of the power that the PSE is obligated to supply, as well as an understanding by the PD on how much power it is entitled to receive. Once the Port has reached a POWER\_GOOD state, the Si3474 enforces this mutual power agreement through the various police registers.

The power values represented in the various police registers represents the power level consistent with what the PSE is obligated to supply, at the very minimum. Based on these values, the actual police limits internal to the Si3474 are slightly higher, to err on the side of supplying power to the PD.

There are generally two kinds of police registers PORTn\_POLICE\_2P and PORTnm\_POLICE\_4P.

The PORTn\_POLICE\_2P defines the power limits for each pair set, independently of each other. PORTnm\_POLICE\_4P is used also for 4P Ports. The PORTnm\_POLICE\_4P takes the total power of the two pair sets forming the 4P Port and compares against the power thresholds implied by the PORTnm\_POLICE\_4P.

At the completion of the Class Power On, the Assigned Class is determined based on the value of PORTnm\_POWER\_ALLOCATION, PORTnm\_2P4P\_MODE, PORTnm\_CONNECTION\_CHECK\_RESULTS and the PORTn\_REQUESTED\_CLASS. For each pair set, the PORTn\_ASSIGNED\_CLASS is converted into a minimum power threshold and is stored in the applicable PORTn\_POLICE\_2P. For 4P Ports, there are two PORTn\_POLICE\_2P registers that are initialized, and in addition, the PORTnm\_POLICE\_4P.

For Single Signature 4P Ports, Autoclass can be enabled in the Si3474, and if the PD also supports Autoclass, then the PD will draw its expected maximum power during the first two to three seconds of being powered, allowing the Si3474 to know exactly how much power the PD would use. As such, the various police registers are initialized based on the Autoclass results, rather than using the Assigned Classification. Autoclass is discussed separately in 2.8.4 Autoclass.

In summary, the Si3474, upon reaching the POWER\_GOOD state will have an initialized police register set. These police registers are the basis of checking for PCUT events. The Si3474 implements an algorithm that monitors compliance against the police registers.

After the initialization of the police registers, the host can make adjustments to the various police registers once it has more accurately determined the actual usage either through long term checking of the pertinent PORTn\_VOLTAGE and PORTn\_CURRENT, or through LLDP link-layer messaging.

PCUT faults are reported in PORTn\_PCUT\_FAULT\_2P if the fault is associated with the PORTn\_POLICE\_2P. PORTnm\_PCUT\_FAULT\_4P events are reported in the case where the PCUT faults are associated with PORTnm\_POLICE\_4P.

#### 2.8.4 Autoclass

Autoclass is a protocol that only affects Single Signature 4P Ports. When automatic Autoclass is enabled, the Si3474 monitors the first long class finger of the Class Power On to detect if the PD is Autoclass-capable. If the Si3474 detects the PD acknowledgement, the PORTn\_AUTOCLASS\_DETECTED bit is set on that pair set. The Si3474 then takes voltage and current measurements when the pair sets reach POWER GOOD state. Both the two PORTn\_POLICE\_2P registers and the PORTnm\_POLICE\_4P registers will be initialized based on measured power plus margin. If PORTn\_AUTO\_AUTOCLASS is set, the corresponding PORTn\_POLICE\_2P and/or PORTnm\_POLICE\_4P are updated using the information in PORTn\_AUTOCLASS\_POWER information, plus some power margin.

The host may also initiate a Manual Autoclass by setting PORTn\_MANUAL\_AUTOCLASS (both pair sets must be set) in the AUTO-CLASS\_CONTROL register. The manual autoclass feature is typically used in conjunction with the LLDP-initiated autoclass procedure. As such, the host is expected to initiate a Manual Autoclass when the PD is drawing its maximum power. The Si3474 stores the computed Autoclass power results in the PORTn\_AUTOCLASS\_POWER (one for each pair set). Once the results are written into PORTn\_AUTOCLASS\_POWER fields, the Si3474 clears the PORTn\_MANUAL\_AUTOCLASS bits. When both PORTn\_MANUAL\_AUTOCLASS bits are cleared, the host can use this as an indication that the information is ready. The host may then overwrite the results of the police registers based on the power information supplied by the two PORTn\_AUTOCLASS\_POWER registers.

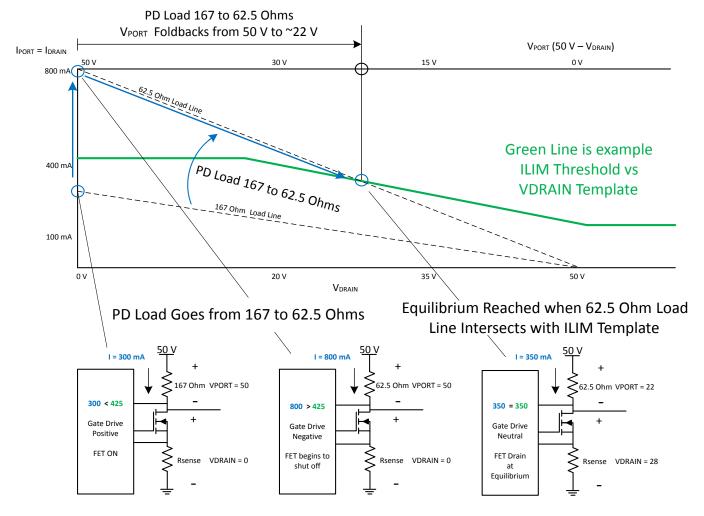

#### 2.8.5 Current Limit and Voltage Foldback

The figure below illustrates how current limiting works. Consider an initial condition where the FET is ON, with the PD appearing like 167  $\Omega$  load. Let's say that suddenly, the load changes from 167  $\Omega$  to 62.5  $\Omega$ . The initial point condition is below the Green Line, which represents an ILIM Threshold vs VDRAIN template that the Si3474 is maintaining. Any difference between the actual current and this threshold results in whether or not current is flowing into the gate of the FET, or if it is flowing into the gate. The magnitude of the gate current is proportional to the difference between where the actual current through the sense resistor, relative to the set point.

When the load initially changes from 167  $\Omega$  to 62.5  $\Omega$ , the sensed current is higher than the ILIM Threshold at that VDRAIN voltage, and as such, the current is removed from the gate, leading to the FET shutting down slightly, leading to the VDRAIN increasing.

Eventually, the VDRAIN will increase high enough so that it meets the 62.5  $\Omega$ , where the gate drive becomes zero since the sensed current is at the green line. In this example, when the PD Load decreases from 167  $\Omega$  to 62.5  $\Omega$ , the port voltage folds back from 50 V down to around 22 V.

Note that the example does not show the intermediate steps, only the starting points and end points. This is a feedback circuit and this illustration cannot show the fact that the speed by which the VDRAIN increases is in proportion to the magnitude difference between the sensed current and the ILIM curve.

Some things to note include:

- 1. The FET power in the current limited state is 28 V \* 350 mA = 9.8 W. To prevent damage, the Si3474 limits the time the FET spends in this condition.

- 2. The DRAIN Voltage is high. The Si3474 can measure this, and magnitude of the DRAIN Voltage, when taking the ILIM Template into account, is a good clue of the power level being experienced by the FET.

Figure 2.9. Current Limiting and Voltage Feedback

#### 2.9 Event Handling

The host can communicate with the Si3474 at any time since the host is an I<sup>2</sup>C Master. For the Si3474 to communicate vital information to the host, it can only do so by asserting the INTb pin, and wait for the host to service the Si3474. However, it is not known when the host will service the Si3474. Therefore, there needs to be a way to have a way of communicating information without losing any of it if the host does not service the Si3474 immediately.

When the Si3474 wants attention from the host, it does so by setting an event in the event register map. The event bits map into a corresponding bit in the INTERRUPT register. If the corresponding INTERRUPT\_MASK bit is also set, then this will cause INTb to assert.

Whenever the host receives an interrupt, the host should first read the INTERRUPT register from every I<sup>2</sup>C address. If there is a bit set, the host should then check the fields associated with that interrupt.

Refer to the figure below. The events are color-coded to have the same color as the associated bits in the INTERRUPT register. For example, when the host reads INTERRUPT, it sees the DISCONNECT\_BIT set only. Note the color coding of DISCONNECT. The DISCONNECTION field and the OSS\_EVENT fields are of the same color. In this case, the host would know to read DISCONNECT\_PCUT\_FAULT register SUPPLY\_EVENT register as those are where the DISCONNECTION field and OSS\_EVENT fields are located at.

Once the DISCONNECT\_PCUT\_FAULT\_COR (0x07) and SUPPLY\_EVENT\_COR (0x0B) are read, the Si3474 will clear the DISCONNECT\_BIT in the INTERRUPT register. If the DISCONNECT\_BIT is the only bit that is set, then the INTb pin will negate.

It is important to note that each Si3474 contains two Quads. So, INTb will assert whenever there is an unserved interrupt in either Quad.

It is also important to note that if the host reads all the COR registers, it is not a guarantee that the INTb would negate. The reason being that a new event may have occurred after the COR register was read to clear the event. The host should take care to only service the events that it reads from the COR register as this is how the Si3474 knows that the host has picked up the event and had cleared it by reading the COR register.

It is important to note that PORTn\_POWER\_ON\_FAULT is slightly different from the other event registers. When a PORTn\_POW-ER\_ON\_FAULT event is reported, the corresponding PORTn\_START\_FAULT is also set. To service a PORTn\_POWER\_ON\_FAULT, both the ILIM\_START\_FAULT COR register and the POWER\_ON\_FAULT COR register must be read to clear the START\_EVENT\_BIT in the INTERRUPT Register.

| Address | Name                  | Access | 7            | 6               | 5              | 4           | 3              | 2          | 1                 | 0                   |

|---------|-----------------------|--------|--------------|-----------------|----------------|-------------|----------------|------------|-------------------|---------------------|

| INTERR  | UPT REGISTERS         |        |              |                 |                |             |                |            |                   |                     |

| 0x00    | INTERRUPT             | RO     | SUPPLY_EVENT | START_EVENT     | P_I_FAULT      | CLASS_DONE  | DETECT_CC_DONE | DISCONNECT | POWER_GOOD_CHANGE | POWER_ENABLE_CHANGE |

| 0x01    | INTERRUPT_MASK        | R/W    | SUPPLI_EVENT | START_EVENT     | F_I_FAOL1      | CLASS_DONE  | DETECT_CC_DONE | DISCONNECT | FOWER_GOOD_CHANGE | POWER_ENABLE_CHANGE |

| EVENT   | REGISTER BITS ASS     | OCIAT  | ED WITH IN   | ITERRUPT RE     | GISTER         |             |                |            |                   |                     |

| 0x02    | POWER_EVENT           | RO     |              | POWER GO        | OOD CHANGE     |             |                | POWER      | ENABLE CHANGE     |                     |

| 0x03    | . onex_even           | CoR    |              | 10000           | /OD_011/11/OE  |             |                | TOWER      |                   |                     |

| 0x04    | CLASS_DETECT_EVENT    | RO     |              | CI 499          | S DONE         |             |                | DETE       | ECT CC DONE       |                     |

| 0x05    | CEASS_BETECT_EVENT    | CoR    |              | OLAGO           | 3_DONE         |             |                | DET        | _C1_CC_DONE       |                     |

| 0x06    | DISCONNECT_PCUT_FAULT | RO     |              | DISCON          | INECTION       |             |                | P.C.I      | JT FAULT 2P       |                     |

| 0x07    | DISCONNECT_FCCT_FACET | CoR    |              | DISCON          | INECTION       |             |                | FO         | DI_I AOLI_ZP      |                     |

| 0x08    | ILIM_START_FAULT      | RO     |              | II IM           | FAULT          |             |                | 61         | ADT FALLT         |                     |

| 0x09    | ILIM_START_FAULT      | CoR    |              | ILIW_           | FAULT          |             |                | 31         | ART_FAULT         |                     |

| 0x0A    | CUPPLY EVENT          | RO     | OVED TEMP    | VDD HV/I O FAII | VDD HVI O WADN | VDWD LIVILO | DODT DOUT      | FAULT 4D   | OCC EVENT         |                     |

| 0x0B    | SUPPLY_EVENT          | CoR    | OVER_TEMP    | VDD_UVLO_FAIL   | VDD_UVLO_WARN  | VPWR_UVLO   | PORTnm_PCUT    | _FAULI_4P  | OSS_EVENT         | ı                   |

| 0x24    | DOWED ON FAULT        | RO     | DORTA DOM    | /ER ON FAULT    | PORT3 POWER    | ON FAULT    | PORT2 POWER    | ON FAULT   | DORT1 DOW         | ED ON FAULT         |

| 0x25    | POWER_ON_FAULT        | CoR    | FUR14_PUW    | ALIN_OIN_FAULT  | FOR 13_FOWER   | _ON_FAULT   | FORTZ_FOWER    | CON_FAULT  | PORTI_POW         | ER_ON_FAULT         |

#### 2.10 Autonomous Operation

If it can be assumed that the total PD load can be supplied by the system VPWR, then it is suitable to use one of the two autonomous operations.

The two autonomous modes will be described as "virtual register settings", so as to leverage much of the prior discussion with typical use case when using Semi Auto and Pushbutton Power On.

#### 2.10.1 AUTO Pin Autonomous Mode

A voltage divider is needed on the AUTO pin. A 15 k $\Omega$  resistor is needed from VDD to the AUTO pin, and the following resistors can be populated from the AUTO pin to GND.

| Lower<br>Resistor | 2P / 4P Port | Class                            | Power     | Equivalent Register Setting POWER_ALLOCATION |

|-------------------|--------------|----------------------------------|-----------|----------------------------------------------|

| None              |              | Hosted I <sup>2</sup> C          | Operation |                                              |

| 124 kΩ            | 2P           | Class 3                          | 15 W      | 0x00                                         |

| 61.9 kΩ           | 2P           | Class 4                          | 30 W      | 0x33                                         |

| 35.7 kΩ           | 4P           | SS Class 4, DS Class 3 + Class 3 | 30 W      | 0xBB                                         |

| 22.6 kΩ           | 4P           | SS Class 5, DS Class 4 + Class 3 | 45 W      | 0xCC                                         |

| 15.8 kΩ           | 4P           | SS Class 6, DS Class 4 + Class 4 | 60 W      | 0xDD                                         |

| 11 kΩ             | 4P           | SS Class 7, DS Class 5 + Class 4 | 75 W      | 0xEE                                         |

| 7.68 kΩ           | 4P           | SS Class 8, DS Class 5 + Class 5 | 90 W      | 0xFF                                         |

The operation of AUTO Pin Autonomous Mode is identical to setting the following in both Quads:

- 1. PORT REMAP = 0xE4 (no remapping)

- 2. POWER ALLOCATION = AS SHOWN ABOVE

- 3. INTERRUPT MASK = 0xE4 (faults enabled)

- 4. PORT MODE = 0xFF (all ports in AUTO Mode)

- 5. PORT\_DETECT\_CLASS\_ENABLE = 0xFF (all ports DETECT\_CC\_ENABLE = 1 and CLASS\_ENABLE = 1)

#### 2.10.2 I<sup>2</sup>C Autonomous Mode

When the PORTn\_MODE is set to AUTO instead of SEMI\_AUTO, as long as the PORTn\_DETECT\_CC\_ENABLE and PORTn\_CLASS\_ENABLE is also set, then the operation is similar to SEMI\_AUTO.

The main difference between SEMI\_AUTO and AUTO is that when a PD successfully classifies, in SEMI\_AUTO, the Si3474 keeps repeating Detection/Connection Check/Class Probe, whereas in AUTO Mode, the Si3474 acts as though it immediately received a PORTn PB POWER ON, and proceeds with a Final Detection, Connection Check and Class Power On before powering up the port.

If a fault were to occur at any time, the Si3474 will go back into Continuous Detection / Connection Check / Class Probe and repeats the process over again. In summary, the Si3474 will simply "keep trying".

Placing the Si3474 in I<sup>2</sup>C Autonomous Mode requires the following register settings to both Quads:

- 1. PORT REMAP = 0xE4 (no remapping)

- 2. POWER\_ALLOCATION = This depends on your system

- 3. INTERRUPT\_MASK = 0xE4 (faults enabled)

- 4. PORT MODE = 0xFF (all ports in AUTO Mode)

- 5. PORT DETECT CLASS ENABLE = 0xFF (all ports DETECT CC ENABLE = 1 and CLASS ENABLE = 1)

The setting of the POWER\_ALLOCATION consists of setting the PORTnm\_2P4P\_MODE as well as the PORTnm\_POWER\_ALLOCATION registers. Refer to 4.26 POWER\_ALLOCATION (0x29) for more details.

#### 2.11 OSS Operation

#### 2.11.1 Emergency Shutdown Feature

The Si3474 supports two kinds of Emergency Shutdown procedures, both of which are controlled by the host via the OSS pin (pin 36). If MULTIBIT\_PRIORITY\_ENABLE = 0 (in MISC register), then 2.11.1.1 1-Bit Shutdown Priority describes the Emergency Shutdown behavior. Otherwise, if MULTIBIT\_PRIORITY\_ENABLE = 1 (in MISC register), then 2.11.1.2 Multi-Bit Shutdown Priority describes the Emergency Shutdown behavior.

#### 2.11.1.1 1-Bit Shutdown Priority

If MULTIBIT\_PRIORITY\_ENABLE = 0, then PORTn\_PORT\_POWER\_PRIORITY bit in each port defines the port Shutdown priority. PORTn\_PORT\_POWER\_PRIORITY bits are found in the POWER\_PRIORITY\_PCUT\_DISABLE register. If PORTn\_PORT\_POWER\_PRIORITY is set, then the associated port is tagged as a "Low Priority" ports. "High Priority" ports are unaffected by an OSS event.

A positive-going edge on pin 36 (OSS), will shut down powered lower priority ports. All powered lower priority ports will be shut down within 50 µs. Refer to the PORTn\_PB\_POWER\_OFF description for all event and register bits that are cleared. Since PORTn\_CLASS\_ENABLE and PORTn\_DETECT\_CC\_ENABLE are among one of the many bits that are cleared, no detection, connection check, or classification activity will occur until the PORTn\_CLASS\_ENABLE and PORTn\_DETECT\_CC\_ENABLE are set again. As such, all events and associated measurement data are cleared. For as long as OSS is asserted high, low priority ports cannot be powered on.

#### 2.11.1.2 Multi-Bit Shutdown Priority

If MULTIBIT PRIORITY ENABLE is set, then PORTn MULTIBIT PRIORITY defines the port priority and OSS action.

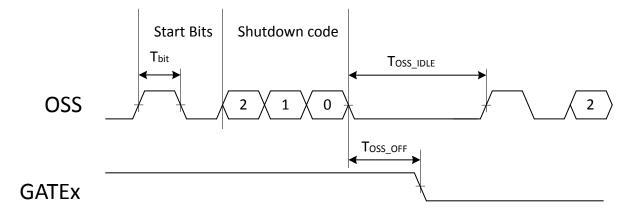

The figure below shows the operation and timing diagram of the OSS pin in multi-bit mode.

- The priority of each port is defined by a 3-bit value in PORTn\_MULTIBIT\_PRIORITY for each port.

- · A port whose priority setting is "000" has the highest priority; priority setting of "111" has the lowest priority.

- · When the host system wants certain priority ports to be shut down, it will transmit the "Shutdown code" over the OSS pin.

- · Ports whose port priority settings are greater than or equal to the received Shutdown code will be turned off.

- For example, a received OSS Shutdown code of "101" will shut down ports whose port priority settings are "101", "110" or "111".

Figure 2.10. OSS Pin in Multi-Bit Mode

The following table describes the timing parameters associated with the OSS pin in multi-priority bit mode.

Table 2.1. Description of Timing Parameters Associated with the OSS Pin In Multi-Bit Mode

| Parameter        | Description                                                                         | Min | Тур | Max | Units |

|------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>bit</sub> | Bit Period                                                                          | 24  | 25  | 26  | μs    |

| Toss_off         | Maximum time between receiving Shut-<br>down code and shutting down of the<br>ports | _   | _   | 50  | μs    |

| Toss_IDLE        | Idle time between consecutive Shutdown code transmission in multi-bit mode          | 125 | _   | _   | μs    |

#### 2.12 I<sup>2</sup>C Interface

#### 2.12.1 I<sup>2</sup>C Protocol

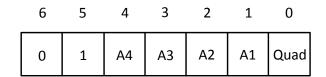

Communicating with the Si3474 is accomplished through a 2-wire I<sup>2</sup>C compatible serial interface. An I<sup>2</sup>C transaction begins with a START condition and concludes with a STOP condition. Technically speaking, the interface to the Si3474 is better described as SMBus instead of I<sup>2</sup>C. SMBus transactions consist of I<sup>2</sup>C accesses in a manner that resembles a register map. The Si3474 registers are described in Table 4.1 Si3474 Registers<sup>1</sup> on page 27. Note that the Register Map describes the operation of a quad (four ports). Each Si3474 has two quads. As such the Si3474 responds to two I<sup>2</sup>C Addresses, one for each quad.

#### 2.12.1.1 Slave Address

The I<sup>2</sup>C Slave Addresses, for which the Si3474 responds to, are dependent on the following:

- · A1, A2, A3 and A4 pin strapping

- Quad

As mentioned previously, each Si3474 responds to two I<sup>2</sup>C Addresses since there are two quads in each Si3474.

The 7-bit Slave Address is effectively constructed as this bit pattern:

Figure 2.11. 7-bit I<sup>2</sup>C Address Bit Pattern

The following table outlines the I<sup>2</sup>C Addresses that the Si3474 will respond to, based on the A1, A2, A3 and A4 pin strapping as well as which quad the host intends to access:

Table 2.2. Si3474 I<sup>2</sup>C Slave Address

| <b>A</b> 4 | A3 | A2 | A1 | Quad 0 l <sup>2</sup> C<br>Address | Quad 1 I <sup>2</sup> C<br>Address |

|------------|----|----|----|------------------------------------|------------------------------------|

| 0          | 0  | 0  | 0  | 0x20                               | 0x21                               |

| 0          | 0  | 0  | 1  | 0x22                               | 0x23                               |

| 0          | 0  | 1  | 0  | 0x24                               | 0x25                               |

| 0          | 0  | 1  | 1  | 0x26                               | 0x27                               |

| 0          | 1  | 0  | 0  | 0x28                               | 0x29                               |

| 0          | 1  | 0  | 1  | 0x2A                               | 0x2B                               |

| 0          | 1  | 1  | 0  | 0x2C                               | 0x2D                               |

| 0          | 1  | 1  | 1  | 0x2E                               | 0x2F                               |

| 1          | 0  | 0  | 0  | 0x30                               | 0x31                               |

| 1          | 0  | 0  | 1  | 0x32                               | 0x33                               |

| 1          | 0  | 1  | 0  | 0x34                               | 0x35                               |

| 1          | 0  | 1  | 1  | 0x36                               | 0x37                               |

| 1          | 1  | 0  | 0  | 0x38                               | 0x39                               |

| 1          | 1  | 0  | 1  | 0x3A                               | 0x3B                               |

| 1          | 1  | 1  | 0  | 0x3C                               | 0x3D                               |

| 1          | 1  | 1  | 1  | 0x3E                               | 0x3F                               |

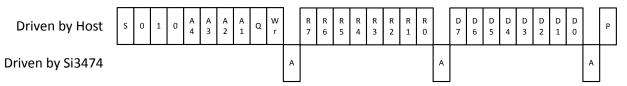

#### 2.12.1.2 Available I<sup>2</sup>C Transfer Types

All Si3474 registers are accessible using 8-bit Writes and 8-bit Reads.

In addition, 16-bit Port Parametric Measurement Registers must be read using a 16-bit Read address in order to guarantee that the MSB and LSB of the Voltage or Current measurement belong to each other. The 16-bit Read Register Address should be pointing to the least significant byte so that the burst-read will end with the MSB.

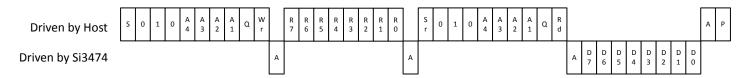

#### Legend

| S | Start Bit |

|---|-----------|

|   |           |

|   |           |

|   |           |

Sr Repeated Start Bit

P Stop Bit

A1...A4 Si3474 A1, A2, A3, A4 pin strapping

Q Si3474 Quad Selection (virtual 'A0')

R0...R7 Si3474 Register Address

D0...D7 Si3474 Register Data LSB

D8...D15 Si3474 Register Data MSB

Wr Write Bit

Rd Read Bit

A ACK bit

N No ACK bit

Figure 2.12. 8-Bit Write

Figure 2.13. 8-Bit Read

Figure 2.14. 16-Bit Read

#### 2.13 Bootloader

#### 2.13.1 Updating Si3474 Flash

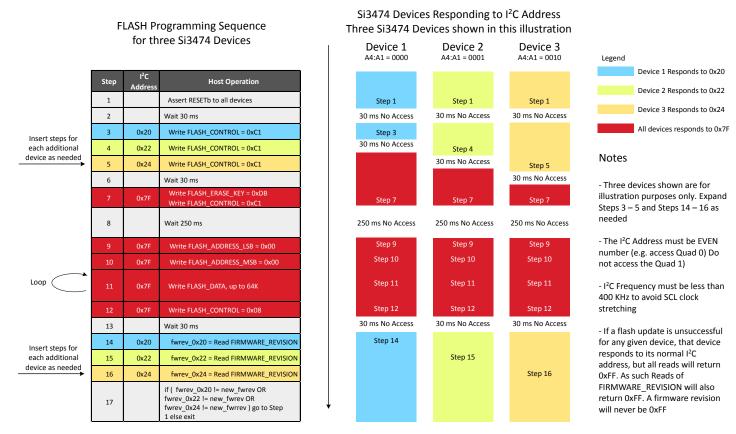

The Si3474 Firmware can be updated through the I<sup>2</sup>C interface. The Si3474 firmware is roughly separated into the 'Application' firmware and a 'Bootloader' firmware. To ensure that the flash loading process never results in a non-communicating device, only the 'Application' part of the firmware is capable of being updated; the Bootloader cannot be updated.

The registers FLASH\_CONTROL, FLASH\_ERASE\_KEY\_FLASH\_ADDRESS\_LSB, FLASH\_ADDRESS\_MSB, FLASH\_DATA work together to implement the flash update process. The figure above illustrates the flash loading sequence.

As a general rule, the flash update must always begin with checking the FIRMWARE\_REVISION to see if a flash update is necessary or not. It is recommended to double-check that the Si3474 does not already have the latest firmware and that it does not need to be reflashed.

Once it has been determined that the device is to be updated, start the flash update procedure with a device reset.

Figure 2.15. Flash Loading Sequence

The chip reset is illustrated in Step 1. After a RESET, wait 30 ms before starting communication, as the device is booting. After the 30 ms wait period, the devices should be able to communicate through I<sup>2</sup>C, via the standard I<sup>2</sup>C Address based on the A1-A4 pin strapping.

In Step 3, Step 4 and Step 5, the host will individually command each device to enter its bootload state (FLASH\_CONTROL=0xC1). Note that the host must access each device individually through its normal I<sup>2</sup>C address. It is also important to note that the host must access only the Quad 0. Quad 0 of each device has an even I<sup>2</sup>C Address. After each device receives its FLASCH\_CONTROL=0xC1 command, each device will reset into a special state where the device will now respond to the Global Address 0x7F.

Once the host has send FLASH\_CONTROL=0xC1 through each individual I<sup>2</sup>C Address it should delay an additional 30 ms in order to allow the last device to be ready. This 30 ms delay is illustrated in Step 6. After this final delay, the host can then proceed to Step 7, where the host would send another FLASH\_CONTROL=0xC1 command. However, this time, the host will use the Global Address 0x7F. In addition, FLASH\_ERASE\_KEY=0xDB is sent prior to the FLASH\_CONTROL=0xC1. This is illustrated on Step 7.

Upon receiving the FLASH\_ERASE\_KEY=0xDB and FLASH\_CONTROL=0xC1 in Step 7, each device will begin to erase the Application FLASH area. This process takes 250 ms, and the host should not initiate communication during this time. This is illustrated on Step 8.

After the 250 ms delay, the host should then write 0x00 to both the FLASH\_ADDRESS\_LSB and FLASH\_ADDRESS\_MSB registers to indicate the starting address. This is illustrated in Steps 9 and 10.

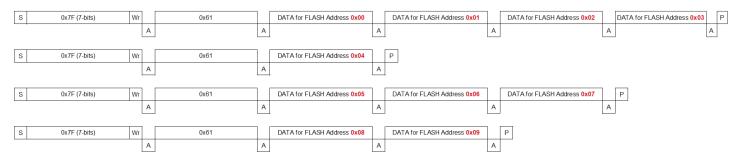

The host then sends the contents of the new firmware by writing to the FLASH\_DATA continuously. For accessing FLASH\_DATA, in addition to the standard I<sup>2</sup>C Register Byte Write method, the Si3474 also supports burst writes in order to increase the throughput of the flash update. The burst write is illustrated in the figure below:

Figure 2.16. Burst Write

To complete the flash update, the host then writes FLASH\_CONTROL=0x08 using the Global Address 0x7F. This is illustrated in Step 12. When each Si3474 device receives the FLASH\_CONTROL=0x08 command, it completes the flash update process and computes the Flash CRC. Normally, the Si3474 reboots, and the FIRMWARE\_REVISION Register can be checked using the normal non-global addresses to make sure that the firmware revision has been updated.

As previously mentioned, there is a separate Bootloader from the 'Application' firmware. As such, the Bootloader doesn't know what the FIRMWARE\_REVISION is, that's why the check for the proper firmware revision needs to be done using the normal, non-global I<sup>2</sup>C Addresses.

If in the event something goes wrong with the flash update, the host will receive a response of 0xFF response to a FIRMWARE\_REVISION read. The host will receive 0xFF for all registers if the firmware update procedure fails. If this happens, the host should simply restart the entire process from the very beginning.

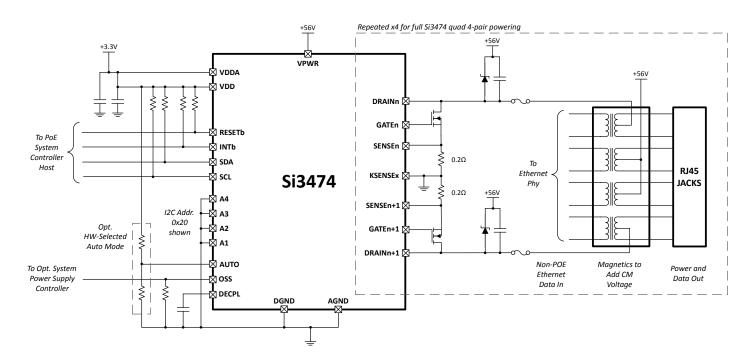

# 3. Typical Application Example

Figure 3.1. Si3474 Typical Application Circuit

# 4. Register Map

Table 4.1. Si3474 Registers<sup>1</sup>

| Addr            | Name                                    | Access  | Reset State | 7            | 9                                          | 2                  | 4            |              | 2                      | -             | 0                  |

|-----------------|-----------------------------------------|---------|-------------|--------------|--------------------------------------------|--------------------|--------------|--------------|------------------------|---------------|--------------------|

| Interrupt       | Interrupt Registers                     |         |             |              |                                            |                    |              |              |                        |               |                    |

| 0000            | INTERRUPT                               | RO      | 1000 0000   | SUPPLY       | START                                      | _<br>_             | CLASS        | DETECT_      | DISCON-                | POWER         | POWER              |

| 0x01            | INTERRUPT_MASK                          | R/W     | 1000 0000   | EVENT        | EVENT                                      | FAÜLT              | DONE         | DONE         | NECT                   | CHANGE        | ENABLE_<br>CHANGE_ |

| Event Registers | gisters                                 |         |             |              |                                            |                    |              |              |                        |               |                    |

| 0x02            | FNEW                                    | SA<br>S | 0000        |              | משואית                                     | מעאדו מי           | Ü            |              |                        |               | Ц                  |

| 0x03            |                                         | CoR     | 0000        |              | DD   Y   M   M   M   M   M   M   M   M   M |                    | Ш            |              | POWER_EINABLE_OIIAIVGE |               | Ц                  |

| 0x04            | CLASS DETECT EVENT                      | RO      | 0000 0000   |              | 000                                        | DONE DONE          |              |              | DETECT                 | ETECT CO DONE |                    |

| 0x05            |                                         | CoR     | 0000        |              |                                            |                    |              |              |                        |               |                    |

| 90x0            | DISCONNECT BCIT EAIILT                  | RO      | 0000 0000   |              | 17000                                      | NOIFOEINICOSIO     |              |              | ) TIOG                 | 00 T II V     |                    |

| 0x07            | DISCONINECT_TOOL_TAGE                   | CoR     | 0000        |              |                                            |                    |              |              |                        | 1001_1A0E1_2F |                    |

| 0x08            | THING TABLE                             | S       | 0000        |              | Z                                          | F                  |              |              | CTABT                  | T     V       |                    |

| 60x0            | ILIM_S IARI_TAULI                       | CoR     | 0000        |              | -<br> <br> -<br> -                         |                    |              |              | האוט                   | SIAN _ PAULI  |                    |

| 0x0A            | F 7 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | RO      |             | OVER         | VDD_                                       | VDD                | VPWR         | PORT         | nn                     | SSO           |                    |

| 0x0B            |                                         | CoR     | 0000 > > 0  | TEMP         | UVLO_<br>FAIL_                             | WARN               | ONFO         | PCUT_FAULT_  | AULT_4P                | EVENT         | l                  |

| 0x24            | DOWED ON FALLT                          | RO      | 0000 0000   | PORT4_POWER_ | OWER_                                      | PORT3_             | PORT3_POWER_ | PORT2_POWER_ | OWER_                  | PORT1_POWER_  | OWER_              |

| 0x25            |                                         | CoR     | 0000 0000   | ON_FAULT     | AULT                                       | ON_F               | ON_FAULT     | ON_FAULT     | AULT                   | ON_FAULT      | AULT               |

| Main Sta        | Main Status Registers                   |         |             |              |                                            |                    |              |              |                        |               |                    |

| 0x0C            | PORT1_CLASS_<br>DETECT_STATUS           | RO      | 0000 0000   | ā            | ORT1_CLA                                   | PORT1_CLASS_STATUS | S            | POF          | PORT1_DETECTION_STATUS | TION_STAT     | Sn                 |

| 0x0             | PORT2_CLASS_<br>DETECT_STATUS           | RO      | 0000 0000   | ā            | ORT2_CLA                                   | PORT2_CLASS_STATUS | S            | POF          | PORT2_DETECTION_STATUS | TION_STAT     | Sn                 |

| 0x0E            | PORT3_CLASS_<br>DETECT_STATUS           | RO      | 0000 0000   | ā            | ORT3_CLA                                   | PORT3_CLASS_STATUS | S            | POF          | PORT3_DETECTION_STATUS | TION_STAT     | Sn                 |

| 0x0F            | PORT4_CLASS_<br>DETECT_STATUS           | RO      | 0000 0000   | ā            | ORT4_CLA                                   | PORT4_CLASS_STATUS | S            | POF          | PORT4_DETECTION_STATUS | TION_STAT     | Sn                 |

|                 |                                         |         |             |              |                                            |                    |              |              |                        |               |                    |

|                              | Name                            | Access | Reset<br>State | 2                  | 9                       | 5                                 | 4                                           | 8                | 2                                 | -                | 0       |

|------------------------------|---------------------------------|--------|----------------|--------------------|-------------------------|-----------------------------------|---------------------------------------------|------------------|-----------------------------------|------------------|---------|

| POWE                         | POWER_STATUS                    | RO     | 0000 0000      |                    | POWER                   | POWER_GOOD                        |                                             |                  | POWER_                            | POWER_ENABLE     |         |

| All                          | PIN_STATUS                      | RO     | 0aaa adoo      | I                  | PIN_A4                  | PIN_A3                            | PIN_A2                                      | PIN_A1           | QUAD                              | I                | I       |

| Main Configuration Registers | Registers                       |        |                |                    |                         |                                   |                                             |                  |                                   |                  |         |

| PC                           | PORT_MODE                       | R/W    | 0000 0000      |                    | RT_MODE                 | PORT4_PORT_MODE   PORT3_PORT_MODE | RT_MODE                                     |                  | PORT2_PORT_MODE   PORT1_PORT_MODE | PORT1_PC         | RT_MODE |

| DISCON                       | DISCONNECT_ENABLE               | R/W    | 0000 1111      |                    | I                       | ı                                 |                                             |                  | DISCONNECT_ENABLE                 | CT_ENABLE        |         |

| DET                          | DETECT_CLASS_<br>ENABLE         | R/W    | 0000 0000      |                    | CLASS                   | CLASS_ENABLE                      |                                             |                  | DETECT_C                          | DETECT_CC_ENABLE |         |

| POWI                         | POWER_PRIORITY_<br>PCUT_DISABLE | R/W    | 0000 0000      | <u>а</u>           | ORT_POWE                | PORT_POWER_PRIORITY               | >-                                          |                  | DISABLE                           | DISABLE_PCUT     |         |

| TIM                          | TIMING_CONFIG                   | R/W    | 0000 0000      | 1                  | TLIM                    | TST                               | TSTART                                      | TO               | TOVLD                             | TMF              | TMPDO   |

|                              | MISC                            | R/W    | 1000 0000      | INT_PIN_<br>ENABLE | CAP_<br>MEAS_<br>ENABLE | l                                 | MULTI-<br>BIT_<br>PRIORI-<br>TY_ENA-<br>BLE | CLASS_<br>CHANGE | DETECT_<br>CHANGE                 | l                | I       |

| Pushbuttons                  |                                 |        |                |                    |                         |                                   |                                             |                  |                                   |                  |         |

| PB_I                         | PB_DETECT_CLASS                 | MO     | 0000 0000      |                    | RESTAR                  | RESTART_CLASS                     |                                             |                  | RESTART_DETECT                    | DETECT           |         |

| PB_P(                        | PB_POWER_ENABLE                 | MO     | 0000 0000      |                    | PB_POM                  | PB_POWER_OFF                      |                                             |                  | PB_POW                            | PB_POWER_ON      |         |

| ш.                           | PB_RESET                        | MO     | 0000 0000      | CLEAR_<br>ALL_INTS | CLEAR_<br>INT_PIN       | I                                 | RESET_<br>QUAD                              |                  | RESET_PORT                        | PORT             |         |

|               |                                    |        | <b>+</b> 0000 |         |               |                         |                  |             |           |                          |

|---------------|------------------------------------|--------|---------------|---------|---------------|-------------------------|------------------|-------------|-----------|--------------------------|

| Addr          | Name                               | Access | State         | 7       | 9             | လ                       | 4                | က           | 7         | 1 0                      |

| Miscellaneous | snoəu                              |        |               |         |               |                         |                  |             |           |                          |

| 0x1B          | VENDOR_ID                          | 8      | 0100 0101     |         | MAN           | MANUFACTURER_ID         | Z_ID             |             |           | IC_ID                    |

| 0x1C          | AUTOCLASS_<br>CONNECTION_CHECK     | RO     | 0000 0000     | ◀       | NUTOCLASS     | AUTOCLASS_DETECTED      |                  | CON         | NECTION_C | CONNECTION_CHECK_RESULTS |

| 0x1D          | Reserved                           | R/W    | 0000 0000     |         |               |                         | Reserved         | rved        |           |                          |

| 0x1E          | PORT1_POLICE_2P                    | R/W    | 1111 1111     |         |               |                         | PORT1_POLICE_2P  | OLICE_2P    |           |                          |

| 0x1F          | PORT2_POLICE_2P                    | R/W    | 1111 1111     |         |               |                         | PORT2_POLICE_2P  | OLICE_2P    |           |                          |

| 0x20          | PORT3_POLICE_2P                    | RW     | 1111 1111     |         |               |                         | PORT3_POLICE_2P  | OLICE_2P    |           |                          |

| 0x21          | PORT4_POLICE_2P                    | R/W    | 1111 1111     |         |               |                         | PORT4_POLICE_2P  | OLICE_2P    |           |                          |