# Si834x Data Sheet

# Isolated Smart Switch

The Si834x provides four isolated high-side or low-side switches with low R<sub>ON</sub>. These switches are ideal for driving resistive and inductive loads like solenoids, relays, and lamps commonly found in industrial control systems like Programmable Logic Controllers (PLC). Each switch is galvanically isolated for safety using Skyworks' groundbreaking CMOS-based isolation technology, offering better reliability and performance than the traditional optocoupler-based isolation, including high Common-Mode Transient Immunity (CMTI) over 100 kV/µs.

The logic interface supports low-power 2.25 V MCUs, while the switches offer a wide supply range of 9 V - 32 V ideal for industrial voltage levels. The switches are capable of providing 0.7 A depending on load conditions. Each switch offers complete fault protection. An innovative multi-voltage clamp efficiently handles an unlimited amount of demagnetization energy (E\_AS). The over-current protection includes an Inrush Current Mode to drive loads like lamps. Additionally, the device power supplies are monitored, and the switches are safely constrained or shutdown on faults.

Eight diagnostics are reported through the logic interface, offering an unprecedented level of details and control. Diagnostics are configured, monitored, and cleared via the Serial Peripheral Interface (SPI) or exposed on active-low, open-drain indicator pins for easy access and combination. Diagnostic communication is independent of switch control signals, with separate isolation channels and constant error checking, ensuring long-term reliability.

# **Applications**

- · Programmable logic controllers

- · Industrial data acquisition

- · Motion controllers

- · Smart solid-state relays

# Safety Approvals (Pending)

- UL 1577 recognized: Up to 1500 Vrms for 1 minute

- CSA certified under: IEC 60950-1, 62368-1

- VDE certification conformity: VDE 0884-10

- CQC certification approval: GB4943.1

# KEY FEATURES

- · High-side or low-side switch

- Logic Supply: 2.25 V 5.5 V

- Switch Supply: 9 V 32 V

- Fast (10 µs) update rate

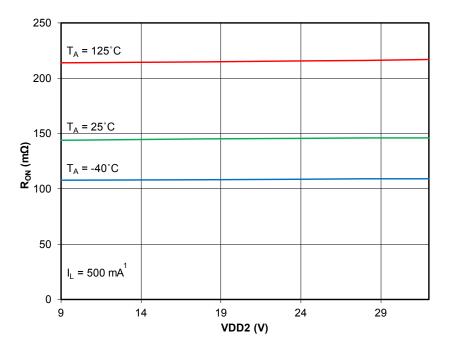

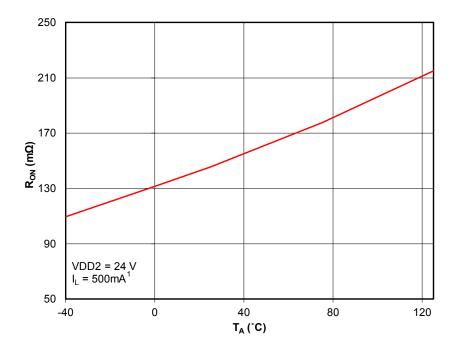

- High continuous current (700 mA) and low  $R_{ON}$  (145 m $\Omega$ )

- · Unique multi-voltage output clamp

- Unlimited demagnetization (EAS)

- · Efficient and fast turn-OFF

- · Inrush Current Mode: 8 A for 20 ms

- · Current-limited overload protection

- · Over-temperature protection

- · Undervoltage protected supplies

- Up to 8 different diagnostics

- · Multiple power supply reports

- · Over-current, over-temperature

- · Open-circuit warning

- · Communication error

- · Channel status indicators

- Dedicated fault indicator

- · Disable outputs asynchronously

- Control 128 channels via SPI

- 1.5 kV<sub>RMS</sub> safety rated isolation

- Transient immunity > 100 kV/µs

- · Compliant to IEC 61131-2

- Compact 9x9 DFN-32 package

- 5 kV ESD Protection

- -40 125 °C operating temperature

# 1. Ordering Guide

Table 1.1. Si834x Ordering Guide

| Ordering Part<br>Number | Output <sup>1</sup><br>Switch<br>Type | Input <sup>2</sup><br>Interface | Output<br>Channels | Continuous<br>Output<br>Current | Channel<br>Status<br>Indicators | Low<br>Voltage<br>Indicator | Open<br>Channel<br>Indicator | Clear<br>Fault<br>Input | Iso.<br>Rating |       |

|-------------------------|---------------------------------------|---------------------------------|--------------------|---------------------------------|---------------------------------|-----------------------------|------------------------------|-------------------------|----------------|-------|

| Products Availab        | le Now                                |                                 |                    |                                 |                                 |                             |                              | ,                       |                |       |

| Si83404AAA-IF           |                                       | Parallel                        |                    |                                 | Vaa                             | Yes                         | No                           | No                      |                |       |

| Si83408ADA-IF           | Sourcing                              | SPI                             | 4                  | 0.7 A                           | Yes                             | No                          | No                           | No                      |                |       |

| Si83408AFA-IF           | 3                                     | Parallel/<br>SPI                | •                  | -                               | No                              | No                          | No                           | No                      | 1.5            |       |

| Si83414AAA-IF           |                                       | Parallel                        |                    |                                 |                                 | \/                          | Yes                          | No                      | No             | kVrms |

| Si83418ADA-IF           | Sinking                               | SPI                             | 4                  | 0.7 A                           | Yes                             | No                          | No                           | No                      |                |       |

| Si83418AFA-IF           |                                       | Parallel/<br>SPI                |                    |                                 | No                              | No                          | No                           | No                      |                |       |

| Contact Skywork         | s Sales for                           | These Option                    | ns                 |                                 |                                 |                             |                              | ı                       | 1              |       |

| Si83404ABA-IF           | 0                                     | Danallal                        | 4                  | 0.7.4                           | V                               | No                          | Yes                          | No                      |                |       |

| Si83404ACA-IF           | Sourcing Parallel                     |                                 | 4                  | 0.7 A                           | Yes                             | No                          | No                           | Yes                     | 1.5            |       |

| Si83414ABA-IF           | Sinking Darallal                      | 4                               | 0.7.4              | \/                              | No                              | Yes                         | No                           | kVrms                   |                |       |

| Si83414ACA-IF           | Sinking                               | Sinking Parallel                | 4                  | 0.7 A                           | Yes                             | No                          | No                           | Yes                     |                |       |

- 1. Output switch can source current in a high-side, open-source configuration or sink current in a low-side, open-drain configuration.

- 2. SPI provides access to all diagnostic, configuration, and channel status information. Devices without a parallel interface allow output channel control through the SPI as well.

- 3. "Si" and "SI" are used interchangeably.

- 4. An "R" at the end of the Ordering Part Number indicates tape and reel option.

# **Table of Contents**

| 1. | Ordering Guide                                                       | . 2 |

|----|----------------------------------------------------------------------|-----|

| 2. | System Overview                                                      | . 5 |

| 3. | Device Operation                                                     | . 7 |

|    | 3.1 Truth Tables                                                     | . 7 |

|    | 3.2 Switch Timing Behavior                                           | .12 |

|    | 3.3 Switch Types                                                     | .13 |

|    | 3.4 Switch Protection                                                |     |

|    | 3.4.1 Demagnetization Energy Protection                              |     |

|    | 3.4.2 Over-Current Protection with Inrush Current Mode               |     |

|    | 3.4.4 Power Supply Protection                                        |     |

|    | 3.5 Diagnostics and Monitoring                                       |     |

|    | 3.5.1 Power Supply Diagnostics.                                      |     |

|    | 3.5.2 Over-Temperature Diagnostics                                   |     |

|    | 3.5.3 Over-Current Diagnostics                                       |     |

|    | 3.5.4 Open-Circuit Diagnostics                                       |     |

|    | 3.5.6 Channel Status Monitoring                                      |     |

|    | 3.6 Serial Peripheral Interface                                      |     |

|    | 3.6.1 SPI Register Map                                               |     |

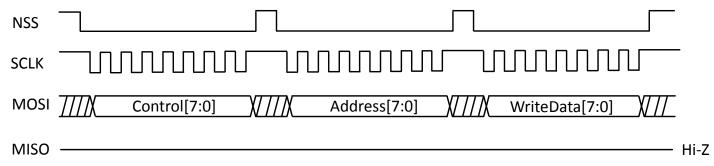

|    | 3.6.2 SPI Communication Transactions                                 |     |

|    | 3.6.3 SPI Read Operation                                             |     |

|    | 3.6.4 SPI Write Operation                                            |     |

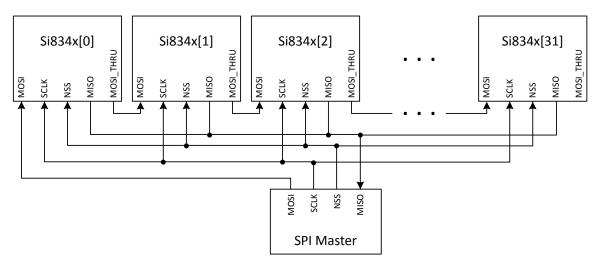

|    | 3.6.5 SPI Daisy Chain Organization                                   |     |

| _  |                                                                      |     |

|    | Application Information                                              |     |

|    | 4.1 Recommended Application Circuits                                 |     |

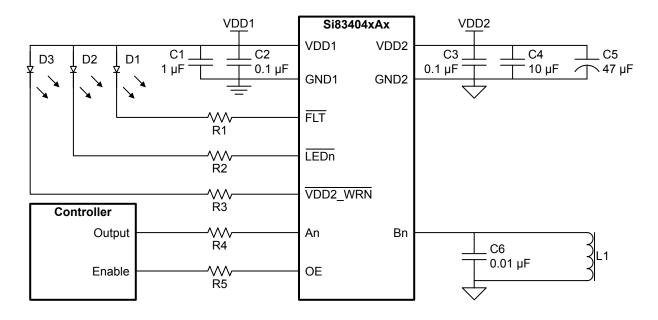

|    | 4.1.1 Isolated Switch with Parallel Inputs and Diagnostic Indicators |     |

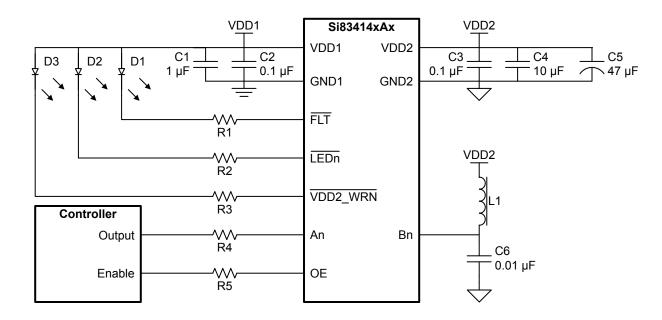

|    | 4.1.3 Isolated High-Side Switch with SPI                             |     |

|    | 4.2 Layout Considerations                                            |     |

|    | 4.3 Power Dissipation Considerations                                 |     |

| 5. |                                                                      | 44  |

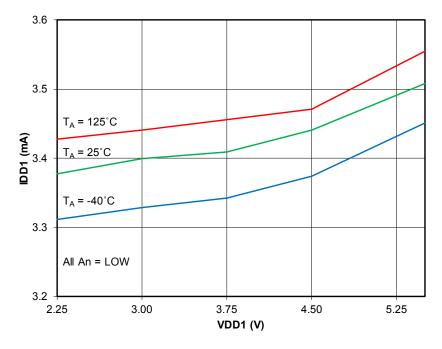

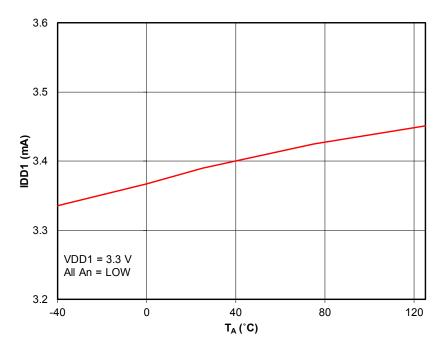

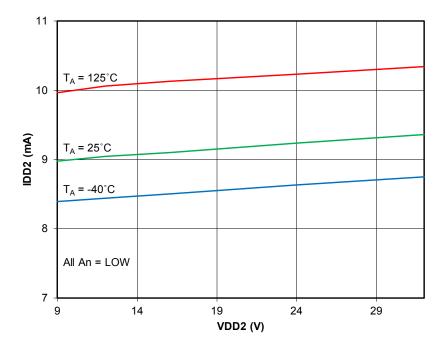

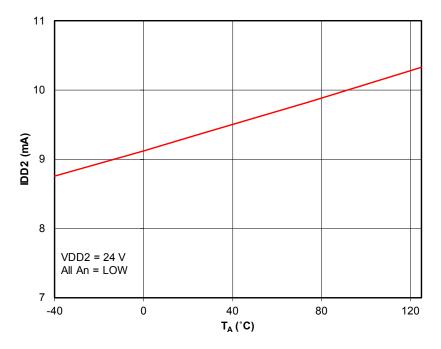

|    | 5.1 Typical Operating Characteristics                                |     |

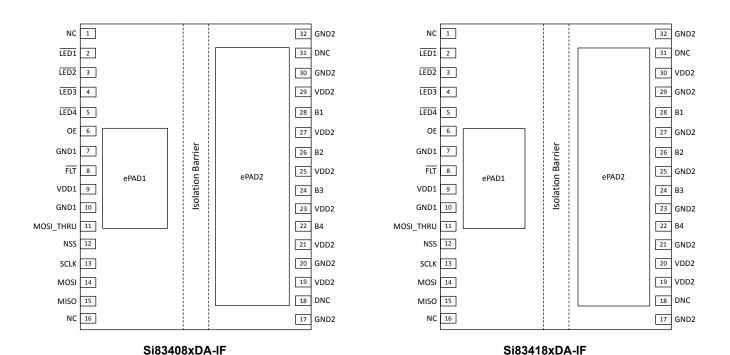

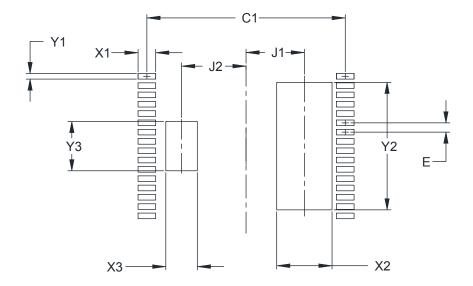

| 6  | Pin and Package Descriptions                                         |     |

| Ο. | 6.1 Pin Descriptions                                                 |     |

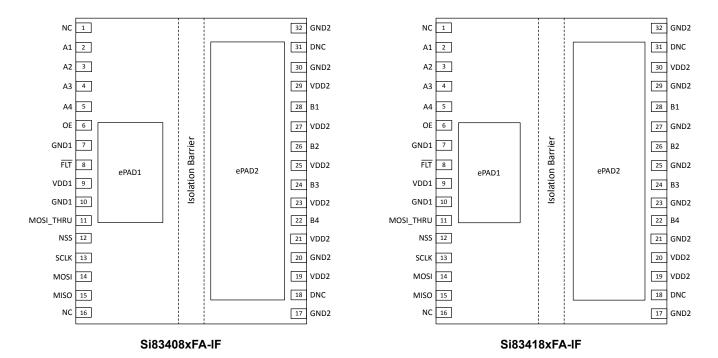

|    | 6.2 Package Drawing                                                  |     |

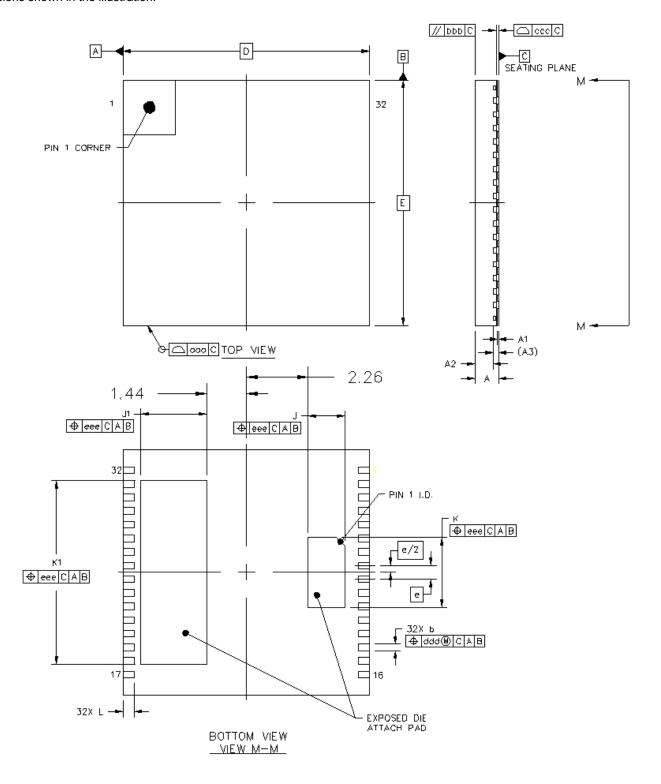

|    | 6.3 Land Pattern.                                                    |     |

|    |                                                                      |     |

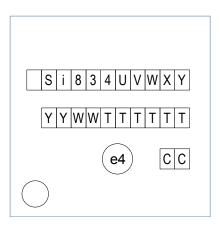

|    | 6.4 Top Marking                                                      | .00 |

| 7. | <b>Revision History</b> |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 67 |

|----|-------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|

|    | 7.1 Pavision 0.5        |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 6. |

# 2. System Overview

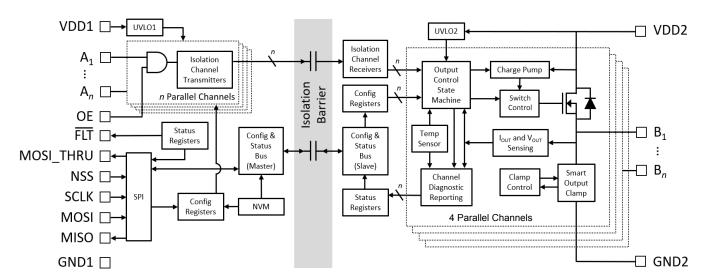

A single channel of the Si834x Isolated Smart Switch is analogous to that of an optocoupler and a relay driver, except that an RF carrier is modulated across the isolation barrier instead of light. This simple architecture provides a robust isolation path and requires no special considerations or initialization at startup. The RF carrier is modulated using methods that optimize fault tolerance and propagation delay across the isolation barrier.

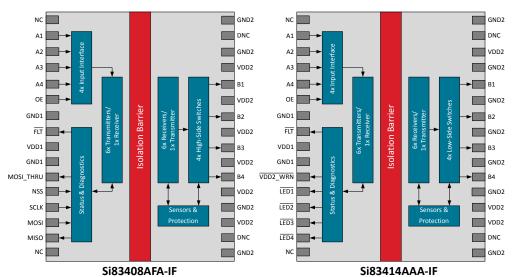

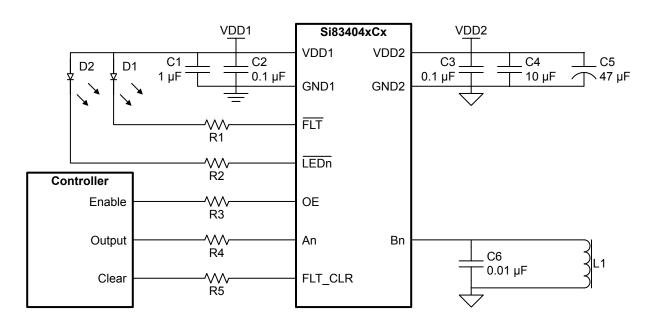

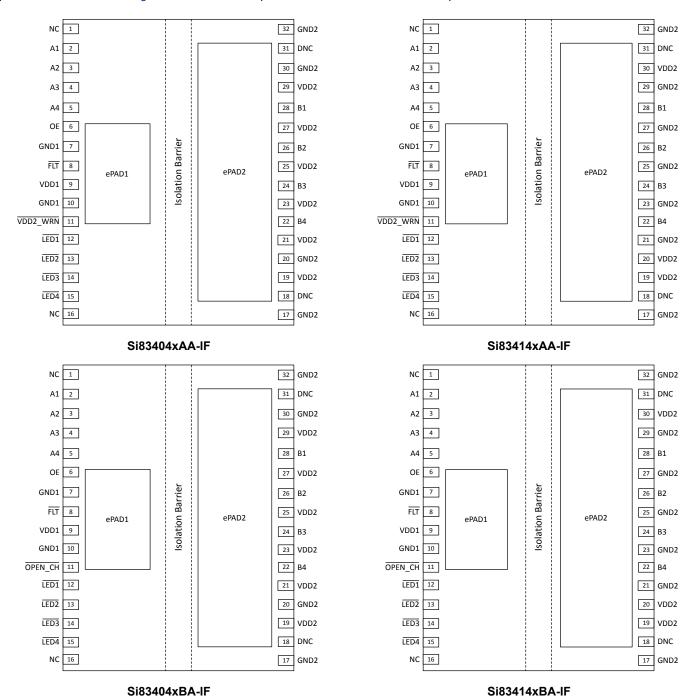

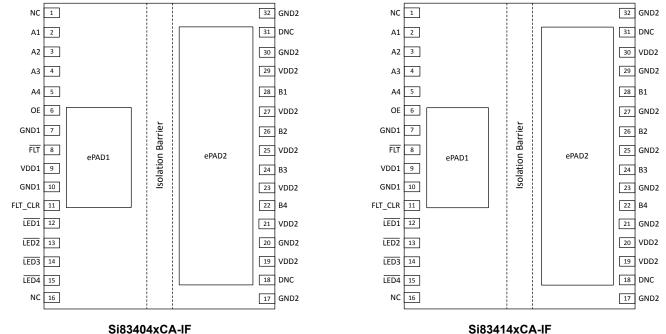

Figure 2.1. Parallel/SPI Sourcing Device System Diagram

The fundamental channel structure described above is augmented using a number of innovative technologies. The output switch is a low ON-State Resistance (R<sub>ON</sub>) device capable of driving inductive and resistive loads at continuous currents of 700 mA. It includes precise voltage, current, and temperature sensors that continuously monitor the switch and load conditions, protecting the device by reducing driver performance or forcing a controlled shutdown when necessary.

The switch uses a sophisticated multi-voltage output clamp, called a "smart output clamp", that both protects the switch from harmful inductive kickback voltage (or back EMF) while still offering fast demagnetization of inductors to reduce contact arcing and increase switching speed.

Four identical channels are packaged together into an Si834x device, each with its own set of sensors. Switches are controlled using dedicated isolation channels which increase reliability and timing performance. A bidirectional, fault-tolerant isolation channel is also implemented between the switch and logic interface, allowing the host controller to configure, monitor, and diagnose the switches and their loads.

The logic interface offers dedicated parallel input channels and an asynchronous output enable (OE) pin for high speed switch control as well as a rich SPI for diagnostics and monitoring. Eight different diagnostic reports are available in the device status registers accessed via SPI which provide a complete picture of device and load condition. See Diagnostics and Monitoring for more information on the available reports.

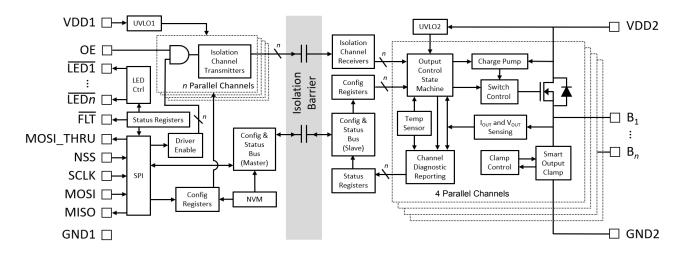

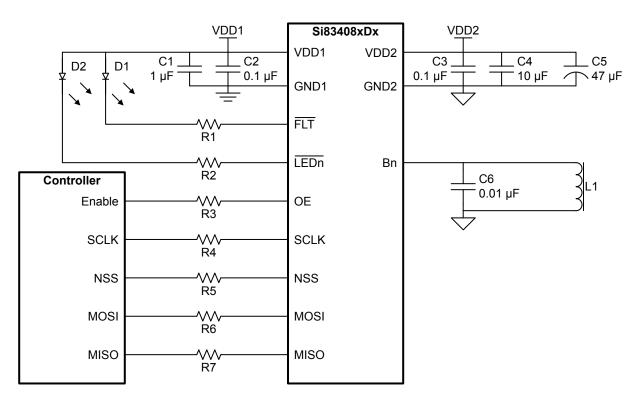

Figure 2.2. SPI Sourcing Device System Diagram

The true status of each switch output is communicated across the isolation barrier to the logic interface and can be monitored by the controller through the status registers. On some product options, such as the one depicted in the figure above, the channel status is also indicated by open-drain, active-low LED output pins that can quickly provide end-user feedback on switch status.

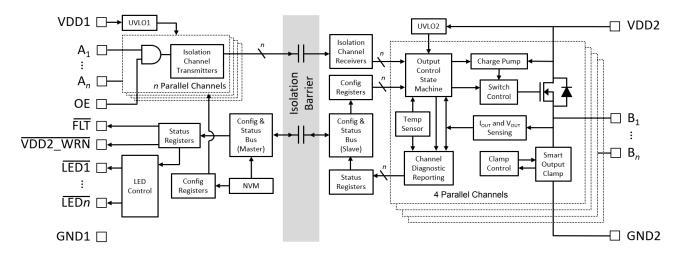

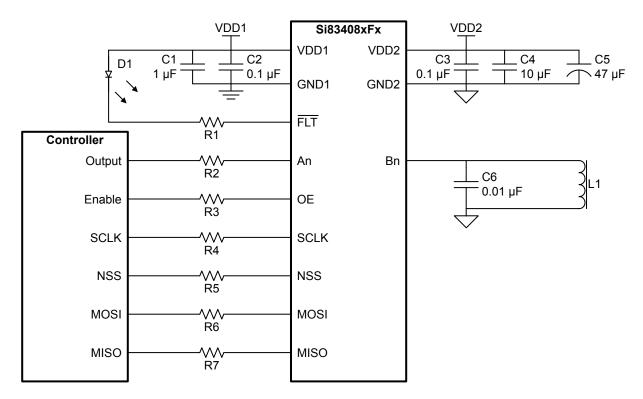

Figure 2.3. Parallel Interface Device System Diagram

The Si834x is also offered without the SPI to simplify designs and provide an easy migration path from existing optocoupler-based solutions, as illustrated in the figure above. Depending on the device selection, different switch diagnostics are exposed using additional indicator pins, such as a switch supply voltage low indicator (VDD2 WRN\).

# 3. Device Operation

This section describes the capabilities of the Si834x Isolated Smart Switch devices and how they should be used to achieve different goals within a design. Refer to the Ordering Guide and Recommended Application Circuits for information on each device and how they are designed into different applications.

# 3.1 Truth Tables

The following tables describe the logical behavior of the Si834x Isolated Smart Switch devices. Use these tables to determine the state of a specific channel's outputs on a specific Si834x device, based on the device's current and past state, and its current inputs. The state of other device channels also impacts some channel output states. When applicable, this is described in the table's footnotes.

Inputs<sup>1</sup> State<sup>2</sup> **Outputs** Mode VDD2<sub>Q-1</sub><sup>4</sup> An OE VDD1<sub>0</sub><sup>3</sup> VDD2<sub>Q</sub><sup>4</sup> Fault<sub>Q</sub><sup>5</sup> VDD2\_WRN\6,7 FLT\6 LEDn\6 Bn<sup>8</sup> Χ Χ NP **OFF** U **OFF OFF** Χ Χ Ρ NP NP **OFF** ON **OFF OFF** D Χ Χ Ρ D OFF OFF Fault NP W ON ON Х Χ Ρ D W ON ON OFF9 OFF9 Χ Χ Ρ Ρ D **OFF** ON OFF9 OFF<sup>9</sup> L Χ Ρ W ND ON **OFF** OFF **OFF** Х L Ρ W ND ON OFF OFF **OFF** Н Н Ρ W ON **OFF** ON ND ON Normal L Х Ρ Ρ ND **OFF** OFF **OFF OFF** Х L Ρ Ρ ND **OFF OFF OFF OFF** Н Н Ρ Ρ ND **OFF** OFF ON ON

Table 3.1. Si834xxxAx Truth Table

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the device state.

- 2. "NP" is the "not powered" state, "P" is the "powered" state, "W" is the "warning" state, "ND" is the "not detected" state, "D" is the detected state, and "—" is an irrelevant state. The current state (Q) and the previous state (Q-1) of the device, as well as the current inputs to the device, define the current outputs of the device.

- 3. "Not powered" (NP) state is defined as VDD1 < VDD1<sub>UV</sub>. "Powered" (P) state is defined as VDD1 > VDD1<sub>UV</sub>. Logic inputs can power VDD1 through an internal diode if its source has adequate current. See Power Supply Characteristics for details.

- 4. "Not powered" (NP) state is defined as VDD2 < VDD2<sub>UV9</sub>. "Warning" (W) state is defined as VDD2<sub>UV9</sub> < VDD2 < VDD2<sub>UV18</sub>. "Powered" (P) state is defined as VDD2 > VDD2<sub>UV18</sub>. See Power Supply Characteristics and Protection and Diagnostics for details.

- 5. The VDD2<sub>Q</sub> "not powered" (NP) state forces a Fault<sub>Q</sub> "detected" state. Fault<sub>Q</sub> state automatically changes to "not detected" (ND) when all fault conditions are removed. Faults are defined in Diagnostics and Monitoring.

- 6. "Undetermined" (U) can be any value within the absolute maximum rating of the output. The output is both active-low and open-drain. See Recommended Application Circuits for more information.

- 7. VDD2 must remain within a state long enough to be measured for this output to change. If VDD2 changes states sufficiently quickly, this output will remain unchanged. See Diagnostics and Monitoring for more information.

- 8. The electrical characteristics for ON and OFF vary based on device selection, switch protection conditions, and switch supply conditions. See Switch Types and Switch Protection for more information.

- 9. If an Over-Temperature Constraint fault is detected while the output is ON, the output will not immediately shut-down. If an Over-Temperature Constraint fault is detected while the output is OFF, the output will be prevented from turning ON. If an Overvoltage Constraint fault is detected, the output will operate normally. See Switch Protection for more information.

Table 3.2. Si834xxxBx Truth Table

| Mada   | Inp | uts <sup>1</sup> |                                |                                | S                                | itate <sup>2</sup>              |                      |                        | Outputs     |                   |                   |                  |  |  |  |

|--------|-----|------------------|--------------------------------|--------------------------------|----------------------------------|---------------------------------|----------------------|------------------------|-------------|-------------------|-------------------|------------------|--|--|--|

| Mode   | An  | OE               | VDD1 <sub>Q</sub> <sup>3</sup> | VDD2 <sub>Q</sub> <sup>4</sup> | VDD2 <sub>Q-1</sub> <sup>4</sup> | Fault <sub>Q</sub> <sup>5</sup> | Bn Load <sub>Q</sub> | Bn Load <sub>Q-1</sub> | OPEN_CH\6,7 | FLT\ <sup>6</sup> | LEDn <sup>6</sup> | Bn <sup>8</sup>  |  |  |  |

|        | Х   | Х                | NP                             | _                              | _                                | _                               | _                    | _                      | OFF         | U                 | OFF               | OFF              |  |  |  |

|        | Х   | Х                | Р                              | NP                             | NP                               | D                               | _                    | _                      | OFF         | ON                | OFF               | OFF              |  |  |  |

| Fault  | Х   | Х                | Р                              | NP                             | Р                                | D                               | _                    | ND                     | ON          | ON                | OFF               | OFF              |  |  |  |

|        | Х   | Х                | Р                              | Р                              | _                                | D                               | ND                   | _                      | ON          | ON                | OFF <sup>9</sup>  | OFF <sup>9</sup> |  |  |  |

|        | Х   | Х                | Р                              | Р                              | _                                | D                               | D                    | _                      | OFF         | ON                | OFF <sup>9</sup>  | OFF <sup>9</sup> |  |  |  |

|        | L   | Х                | Р                              | Р                              | _                                | ND                              | ND                   | _                      | ON          | OFF               | OFF               | OFF              |  |  |  |

|        | Х   | L                | Р                              | Р                              | _                                | ND                              | ND                   | _                      | ON          | OFF               | OFF               | OFF              |  |  |  |

| Normal | L   | Х                | Р                              | Р                              | _                                | ND                              | D                    | _                      | OFF         | OFF               | OFF               | OFF              |  |  |  |

|        | Х   | L                | Р                              | Р                              | -                                | ND                              | D                    | _                      | OFF         | OFF               | OFF               | OFF              |  |  |  |

|        | Н   | Н                | Р                              | Р                              | _                                | ND                              | _                    | _                      | OFF         | OFF               | ON                | ON               |  |  |  |

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the device state.

- 2. "NP" is the "not powered" state, "P" is the "powered" state, "ND" is the "not detected" state, "D" is the detected state, and "-" is an irrelevant state. The current state (Q) and the previous state (Q-1) of the device, as well as the current inputs to the device, define the current outputs of the device.

- 3. "Not powered" (NP) state is defined as VDD1 < VDD1<sub>UV</sub>. "Powered" (P) state is defined as VDD1 > VDD1<sub>UV</sub>. Logic inputs can power VDD1 through an internal diode if its source has adequate current. See Power Supply Characteristics for details.

- 4. "Not powered" (NP) state is defined as VDD2 < VDD2<sub>UV9</sub>. "Powered" (P) state is defined as VDD2 > VDD2<sub>UV9</sub>. See Power Supply Characteristics for details.

- 5. The VDD2<sub>Q</sub> "not powered" (NP) state forces a Fault<sub>Q</sub> "detected" state. Fault<sub>Q</sub> state automatically changes to "not detected" (ND) when all fault conditions are removed. Faults are defined in Diagnostics and Monitoring.

- 6. "Undetermined" (U) can be any value within the absolute maximum rating of the output. The output is both active-low and open-drain. See Recommended Application Circuits for more information.

- 7. All channels are assumed to have the same load state. A "not detected" (ND) load state on any channel will turn ON this output. The load must remain within a state long enough to be measured for this output to change. If the load changes state sufficiently quickly, this output will remain unchanged. See Diagnostics and Monitoring for more information.

- 8. The electrical characteristics for ON and OFF vary based on device selection, switch protection conditions, and switch supply conditions. See Switch Types and Switch Protection for more information.

- 9. If an Over-Temperature Constraint fault is detected while the output is ON, the output will not immediately shut-down. If an Over-Temperature Constraint fault is detected while the output is OFF, the output will be prevented from turning ON. If an Overvoltage Constraint fault is detected, the output will operate normally. See Switch Protection for more information.

Table 3.3. Si834xxxCx Truth Table

| Mode   |    | Input | s <sup>1</sup> |                     | Sta                            | nte <sup>2</sup>                |                                   | Outputs           |                    |                  |  |  |

|--------|----|-------|----------------|---------------------|--------------------------------|---------------------------------|-----------------------------------|-------------------|--------------------|------------------|--|--|

| Mode   | An | OE    | FLT_CLR        | VDD1 <sub>Q</sub> 3 | VDD2 <sub>Q</sub> <sup>4</sup> | Fault <sub>Q</sub> <sup>5</sup> | Fault <sub>Q-1</sub> <sup>5</sup> | FLT\ <sup>6</sup> | LEDn\ <sup>6</sup> | Bn <sup>7</sup>  |  |  |

|        | Х  | Х     | Х              | NP                  | _                              | _                               | _                                 | U                 | OFF                | OFF              |  |  |

| Fault  | Х  | Х     | Х              | Р                   | NP                             | D                               | -                                 | ON                | OFF                | OFF              |  |  |

|        | Х  | Х     | Х              | Р                   | Р                              | D                               | -                                 | ON                | OFF <sup>8</sup>   | OFF <sup>8</sup> |  |  |

|        | L  | Х     | L              | Р                   | Р                              | ND                              | D                                 | ON                | OFF                | OFF              |  |  |

|        | Х  | L     | L              | Р                   | Р                              | ND                              | D                                 | ON                | OFF                | OFF              |  |  |

|        | Н  | Н     | L              | Р                   | Р                              | ND                              | D                                 | ON                | ON <sup>9</sup>    | ON <sup>9</sup>  |  |  |

|        | L  | Х     | Н              | Р                   | Р                              | ND                              | D                                 | OFF               | OFF                | OFF              |  |  |

| Normal | Х  | L     | Н              | Р                   | Р                              | ND                              | D                                 | OFF               | OFF                | OFF              |  |  |

|        | Н  | Н     | Н              | Р                   | Р                              | ND                              | D                                 | OFF               | ON                 | ON               |  |  |

|        | L  | Х     | Х              | Р                   | Р                              | ND                              | ND                                | OFF               | OFF                | OFF              |  |  |

|        | Х  | L     | Х              | Р                   | Р                              | ND                              | ND                                | OFF               | OFF                | OFF              |  |  |

|        | Н  | Н     | Х              | Р                   | Р                              | ND                              | ND                                | OFF               | ON                 | ON               |  |  |

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the device state.

- 2. "NP" is the "not powered" state, "P" is the "powered" state, "ND" is the "not detected" state, "D" is the detected state, and "—" is an irrelevant state. The current state (Q) and the previous state (Q-1) of the device, as well as the current inputs to the device, define the current outputs of the device.

- 3. "Not powered" (NP) state is defined as VDD1 < VDD1<sub>UV</sub>. "Powered" (P) state is defined as VDD1 > VDD1<sub>UV</sub>. Logic inputs can power VDD1 through an internal diode if its source has adequate current. See Power Supply Characteristics for details.

- 4. "Not powered" (NP) state is defined as VDD2 < VDD2<sub>UV9</sub>. "Powered" (P) state is defined as VDD2 > VDD2<sub>UV9</sub>. See Power Supply Characteristics for details.

- 5. The "detected" (D) state will persist as a previous state (Q-1) until the current fault state (Q) is "not detected" (ND) and the FLT\_CLR input is high. Faults are defined in Diagnostics and Monitoring.

- 6. "Undetermined" (U) can be any value within the absolute maximum rating of the output. The output is both active-low and open-drain. See Recommended Application Circuits for more information.

- 7. The electrical characteristics for ON and OFF vary based on device selection, switch protection conditions, and switch supply conditions. See Switch Types and Switch Protection for more information.

- 8. If an Over-Temperature Constraint fault is detected while the output is ON, the output will not immediately shut-down. If an Over-Temperature Constraint fault is detected while the output is OFF, the output will be prevented from turning ON. If an Overvoltage Constraint fault is detected, the output will operate normally. See Switch Protection for more information.

- 9. If a Communication Error Shutdown fault was previously detected and is currently reported, the output will be prevented from turning ON. See Diagnostics and Monitoring for more information.

Table 3.4. Si834xxxDx Truth Table

| Mode   | Inputs <sup>1</sup>   |    |                                | State <sup>3</sup>             |                                 | Outputs              |                   |                   |  |  |

|--------|-----------------------|----|--------------------------------|--------------------------------|---------------------------------|----------------------|-------------------|-------------------|--|--|

| Mode   | SW_EN[n] <sup>2</sup> | OE | VDD1 <sub>Q</sub> <sup>4</sup> | VDD2 <sub>Q</sub> <sup>5</sup> | Fault <sub>Q</sub> <sup>6</sup> | FLT\ <sup>7, 8</sup> | LEDn\8            | Bn <sup>9</sup>   |  |  |

|        | Х                     | Х  | NP                             | _                              | _                               | U                    | OFF               | OFF               |  |  |

| Fault  | Х                     | Х  | Р                              | NP                             | D                               | ON                   | OFF               | OFF               |  |  |

|        | Х                     | Х  | Р                              | Р                              | D                               | ON                   | OFF <sup>10</sup> | OFF <sup>10</sup> |  |  |

|        | L                     | Х  | Р                              | Р                              | ND                              | OFF                  | OFF               | OFF               |  |  |

| Normal | Х                     | L  | Р                              | Р                              | ND                              | OFF                  | OFF               | OFF               |  |  |

|        | Н                     | Н  | Р                              | Р                              | ND                              | OFF                  | ON                | ON                |  |  |

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the device state.

- 2. This input is supplied via the SPI from the SW\_EN register. Bit addresses are zero indexed such that channel 1 (output B1) is supplied from the SW\_EN[0] bit.

- 3. "NP" is the "not powered" state, "P" is the "powered" state, "ND" is the "not detected" state, "D" is the detected state, and "-" is an irrelevant state. The current state (Q) and the previous state (Q-1) of the device, as well as the current inputs to the device, define the current outputs of the device.

- 4. "Not powered" (NP) state is defined as VDD1 < VDD1<sub>UV</sub>. "Powered" (P) state is defined as VDD1 > VDD1<sub>UV</sub>. Logic inputs can power VDD1 through an internal diode if its source has adequate current. See Power Supply Characteristics for details.

- 5. "Not powered" (NP) state is defined as VDD2 < VDD2<sub>UV9</sub>. "Powered" (P) state is defined as VDD2 > VDD2<sub>UV9</sub>. See Power Supply Characteristics for details.

- 6. The VDD2<sub>Q</sub> "not powered" (NP) state forces a Fault<sub>Q</sub> "detected" (D) state. Fault<sub>Q</sub> state automatically changes to "not detected" (ND) when all fault conditions are removed. Faults are defined in Diagnostics and Monitoring.

- 7. The default behavior shown here can be modified through the SPI. See Serial Peripheral Interface for details.

- 8. "Undetermined" (U) can be any value within the absolute maximum rating of the output. The output is both active-low and open-drain. See Recommended Application Circuits for more information.

- 9. The electrical characteristics for ON and OFF vary based on device selection, switch protection conditions, and switch supply conditions. See Switch Types and Switch Protection for more information.

- 10. If an Over-Temperature Constraint fault is detected while the output is ON, the output will not immediately shut-down. If an Over-Temperature Constraint fault is detected while the output is OFF, the output will be prevented from turning ON. If an Overvoltage Constraint fault is detected, the output will operate normally. See Switch Protection for more information.

Table 3.5. Si834xxxFx Truth Table

| Mode   | Inp | uts <sup>1</sup> |                                | State <sup>2</sup>             | Outputs                         |                   |                  |

|--------|-----|------------------|--------------------------------|--------------------------------|---------------------------------|-------------------|------------------|

| Mode   | An  | OE               | VDD1 <sub>Q</sub> <sup>3</sup> | VDD2 <sub>Q</sub> <sup>4</sup> | Fault <sub>Q</sub> <sup>5</sup> | FLT\ <sup>6</sup> | Bn <sup>7</sup>  |

|        | Х   | Х                | NP                             | _                              | _                               | U                 | OFF              |

| Fault  | Х   | Х                | Р                              | NP                             | D                               | ON                | OFF              |

|        | Х   | Х                | Р                              | Р                              | D                               | ON                | OFF <sup>8</sup> |

|        | L   | Х                | Р                              | Р                              | ND                              | OFF               | OFF              |

| Normal | Х   | L                | Р                              | Р                              | ND                              | OFF               | OFF              |

|        | Н   | Н                | Р                              | Р                              | ND                              | OFF               | ON               |

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Logic values listed in this table are assumed to transition at the same time as the device state.

- 2. "NP" is the "not powered" state, "P" is the "powered" state, "ND" is the "not detected" state, "D" is the detected state, and "-" is an irrelevant state. The current state (Q) and the previous state (Q-1) of the device, as well as the current inputs to the device, define the current outputs of the device.

- 3. "Not powered" (NP) state is defined as VDD1 < VDD1<sub>UV</sub>. "Powered" (P) state is defined as VDD1 > VDD1<sub>UV</sub>. Logic inputs can power VDD1 through an internal diode if its source has adequate current. See Power Supply Characteristics for details.

- 4. "Not powered" (NP) state is defined as VDD2 < VDD2<sub>UV9</sub>. "Powered" (P) state is defined as VDD2 > VDD2<sub>UV9</sub>. See Power Supply Characteristics for details.

- 5. The VDD2<sub>Q</sub> "not powered" (NP) state forces a Fault<sub>Q</sub> "detected" (D) state. Fault<sub>Q</sub> state automatically changes to "not detected" (ND) when all fault conditions are removed. Faults are defined in Diagnostics and Monitoring.

- 6. "Undetermined" (U) can be any value within the absolute maximum rating of the output. The output is both active-low and open-drain. See Recommended Application Circuits for more information. It's default behavior shown here can be modified through the SPI. See Serial Peripheral Interface for details.

- 7. The electrical characteristics for ON and OFF vary based on device selection, switch protection conditions, and switch supply conditions. See Switch Types and Switch Protection for more information.

- 8. If an Over-Temperature Constraint fault is detected while the output is ON, the output will not immediately shut-down. If an Over-Temperature Constraint fault is detected while the output is OFF, the output will be prevented from turning ON. If an Overvoltage Constraint fault is detected, the output will operate normally. See Switch Protection for more information.

# 3.2 Switch Timing Behavior

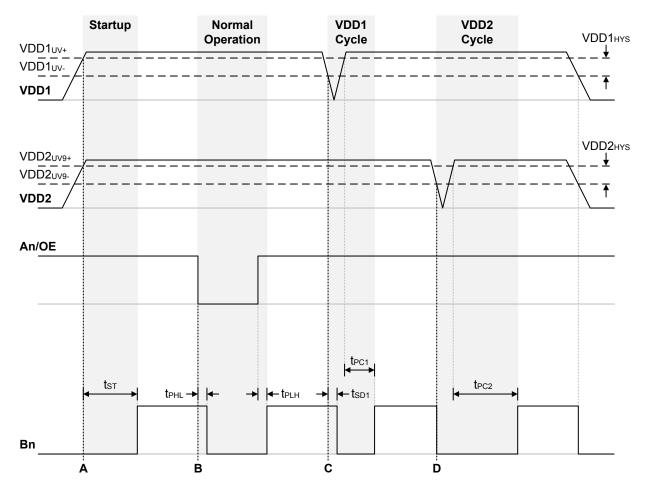

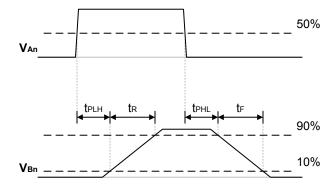

The Si834x exhibits different timing behavior depending on the state of the power supplies, as well as the switch inputs. In the figure below, the analog power supply voltages are plotted against the digital input and output state of the device, with relevant device timings listed. It is important to note that the analog behavior of the Si834x device changes based on the switch type selected. See Switch Types for details.

Figure 3.1. Switch Timing Behavior

At marker A in the figure above, both power supplies, though unpowered initially, exceed the undervoltage threshold (VDD1<sub>UV</sub> and VDD2<sub>UV9</sub>). At this point, the device begins to start up. Until the Device Startup Time ( $t_{ST}$ ) elapses, the output remains off. After  $t_{ST}$ , the output state begins to track the input state. Note that the analog timing behavior from device input to device output is depicted in Figure 5.1 on page 47.

At marker B, the input control signal is turned off. After the Turn OFF Propagation Delay ( $t_{PHL}$ ) elapses, the output will turn off. When the input is turned back on, an additional Turn ON Propagation Delay ( $t_{PLH}$ ) must elapse before the output returns to the ON state.

At marker C, the logic interface power supply is turned completely off to begin a power cycle. When VDD1 drops below VDD1 $_{UV}$ , the device begins to shutdown. After the Logic Interface Shutdown Time ( $t_{SD1}$ ) elapses, the output is turned off. When VDD1 exceeds the VDD1 $_{UV}$  threshold again, the Logic Interface Power Cycle Time ( $t_{PC1}$ ) must elapse before the output will again track the input and turn back on.

At marker D, the switch power supply is turned completely off to begin a power cycle. When VDD2 drops below VDD2 $_{UV9}$ , the output immediately turns off. When VDD2 exceeds VDD2 $_{UV9}$  again, the Switch Power Cycle Time ( $t_{PC2}$ ) must elapse before the output will again track the input and turn back on.

# 3.3 Switch Types

The Si834x Isolated Smart Switch is available in two switch configurations to meet a broad range of application requirements.

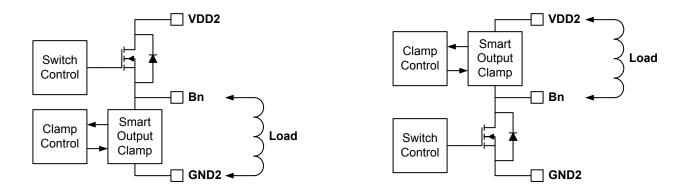

Figure 3.2. Sourcing Device

Figure 3.3. Sinking Device

As shown in the figures above, the sourcing configuration operates as an open-source output for high-side switching. It connects to VDD2 when the switch is turned ON. The sinking configuration uses an open-drain output for low-side switching. It connects to GND2 when the switch is turned ON. Both the sourcing and sinking output configurations are IEC61131-2 compliant. Each switch can source or sink 700 mA of continuous current.

Additionally, the Si834x devices offer an Inrush Current Mode which can briefly provide up to 8 A of current. This is ideal for driving loads with low startup impedance like lamps. To reliably achieve continuous currents of 700 mA, follow the circuit design and layout recommendations in this document. See Layout Considerations and Recommended Application Circuits for details on how to design for high continuous current devices.

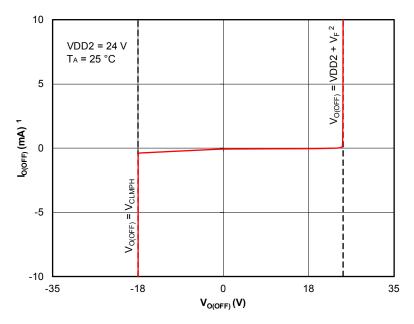

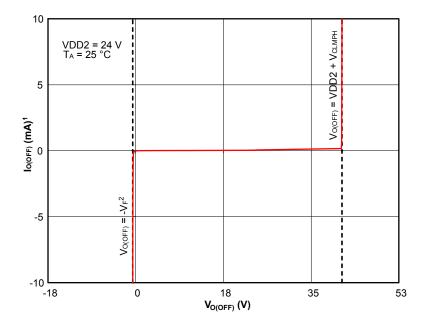

All switches include a smart clamp output to quickly and safely demagnetize inductive loads, as well as advanced over-current protection, over-temperature protection, and open-circuit detection. When the switch is OFF, the output can be considered high impedance (Hi-Z). However, the demagnetization clamp will engage in the OFF state if the voltage on the output pin exceeds the Demagnetization Clamp High Voltage (V<sub>CLMPH</sub>) specification. Also, there will be some OFF state current (I<sub>O(OFF)</sub>) to facilitate open circuit detection. See Figure 5.10 on page 57 and Figure 5.11 on page 58 for details on the output behavior when the switch is OFF.

#### 3.4 Switch Protection

The Si834x Isolated Smart Switch contains sophisticated protection technology. It is designed to operate for decades driving a broad range of loads. It can seamlessly recover from faults ranging from a simple switch supply overvoltage, to a dead short on a driven output channel. The following sections detail individual methods of protection, and how they behave in common scenarios.

# 3.4.1 Demagnetization Energy Protection

The Si834x Isolated Smart Switch includes a high efficiency, multi-voltage "smart" output clamp used to protect the switch from harsh demagnetization voltage, commonly referred to as back EMF, flyback voltage, inductive voltage "kick-back", or sometimes just as a "voltage kick." The smart clamp is actively controlled based on the current through the switch, the switch supply voltage, and the switch temperature. By dynamically adjusting the clamp voltage based on device and load conditions, the Si834x balances safety with performance. It limits device power dissipation to safe levels, while still delivering fast turn-off performance that allows inductors to switch quickly and reduces arcing and arc welding failures in relays.

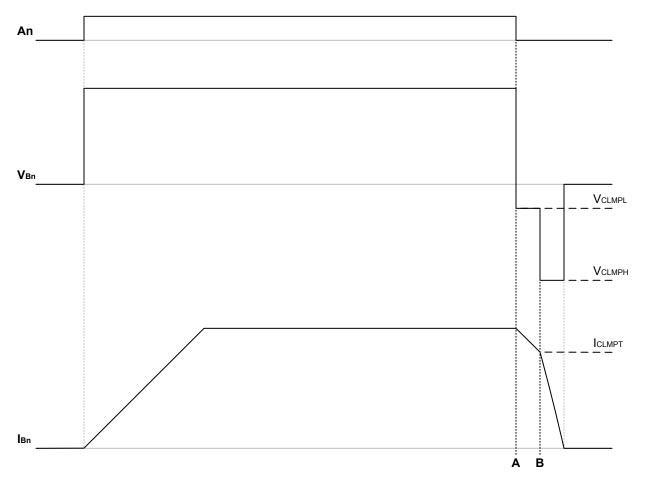

Figure 3.4. Demagnetization Protection Behavior

The figure above illustrates the behavior of a high-side (sourcing) Si834x switch when driving an inductor at the switches' typical ON State Load Current ( $I_{O(ON)}$ ) and under normal operating conditions. It plots the digital input to the switch (An) as well as the output voltage ( $V_{Bn}$ ) and output current ( $I_{Bn}$ ) from the switch where n is a specific channel number.

At marker A, the switch, driving a fully charged inductor, is turned off. The inductor resists a change in current by generating a very large negative voltage at the switch output (Bn) and across the smart output clamp. Initially, because the current through the smart clamp exceeds the Demagnetization Clamp Current Threshold (I<sub>CLMPT</sub>), the clamp voltage is constrained to the Demagnetization Clamp Low Voltage (V<sub>CLMPL</sub>). At this clamp voltage, demagnetization occurs slowly, but power dissipation in the channel is limited to a safe level.

At marker B, current through the clamp falls below  $I_{CLMPT}$  and the clamp voltage is changed to Demagnetization Clamp High Voltage ( $V_{CLMPH}$ ). The higher clamp voltage will rapidly demagnetize the inductor. The increased power dissipation during this phase of protection will cause a small temperature rise in the channel, but with inductor current sufficiently constrained below  $I_{CLMPT}$ , this rise is easily tolerated by the Si834x device.

This two-step approach when turning off an inductor gives the Si834x the ability to demagnetize an unlimited amount of energy from a single turn-off pulse, on a single channel (E<sub>AS(1CH)</sub>). See Table 5.12 on page 53 for maximum energy dissipation under other conditions.

#### 3.4.2 Over-Current Protection with Inrush Current Mode

The Si834x Isolated Smart Switch includes short-circuit-proof, over-current protection with automated restart. Unlike other over-current-protected switches, the Si834x rapidly samples current through the switch, disabling the output while an over-current condition remains present, rather than depending on an increased switch resistance and thermal protection alone to limit current through the switch. This approach drastically reduces the power dissipation through the switch during an over-current condition, eliminating the need for thermal independence of separate channels, increasing the lifespan of the switch, simplifying the thermal requirements of the end-system, and still ensuring safe operation of the switch even with a dead short present for an indefinite amount of time.

The Si834x devices also include an Inrush Current Mode, which enables them to drive loads with low startup impedance like lamps by providing a brief high current when the channel is initially turned on.

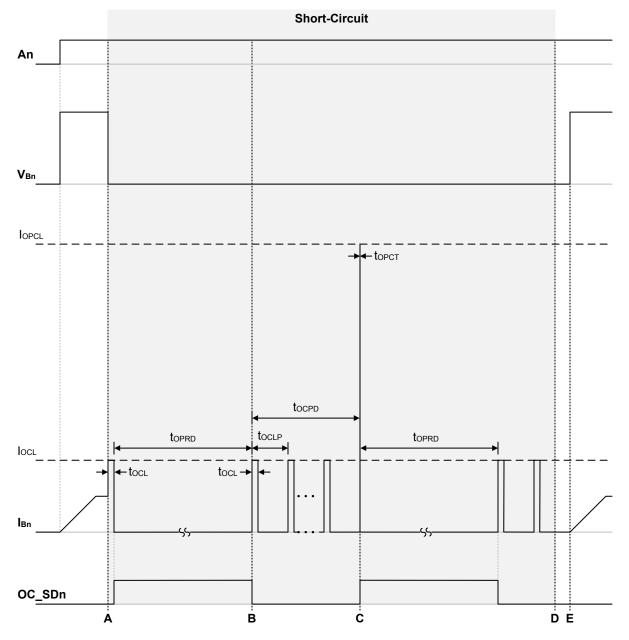

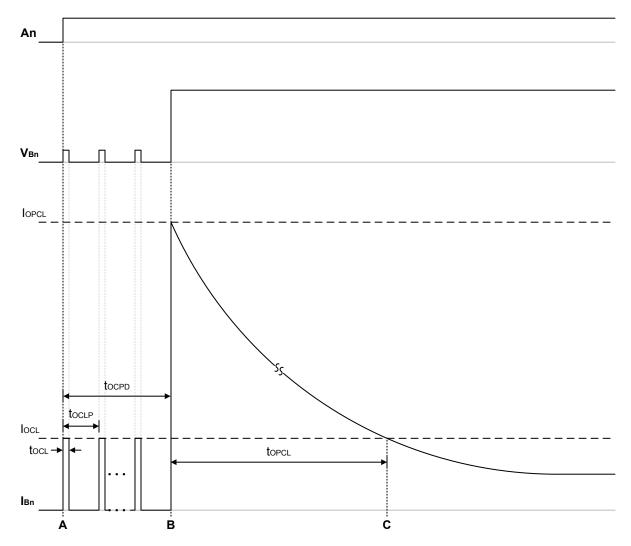

Figure 3.5. Over-Current Shutdown Behavior

The figure above illustrates the behavior of a high-side (sourcing) Si834x switch when driving an inductor at the switches' typical ON State Load Current ( $I_{O(ON)}$ ) under normal operating conditions initially, but then experiencing a short-circuit. Note that marker B depicts the Si834x switches' behavior when it is turned on in a short-circuit state. The figure plots the digital input to the switch (An) as well as the output voltage ( $V_{Bn}$ ) and output current ( $I_{Bn}$ ) from the switch where n is a specific channel number. It also illustrates the Over-Current Shutdown diagnostic register value for the channel (OC\_SDn) when the enable mask for auto-clearing of diagnostics (ACLR\_EN) is set to true. This is the default diagnostic report clearing behavior.

Initially, the switch channel is turned on and the load inductor is fully charged. The current must exceed the Output Current Limit Threshold ( $I_{OCLT}$ ), which is similar to the Output Current Limit ( $I_{OCL}$ ) in the figure above, for the switch to detect an over-current condition and engage its over-current protection. At marker A, a dead short (0  $\Omega$  resistance) is placed on the output to the switch channel which causes an immediate voltage drop and current rise well above  $I_{OCLT}$ . The Si834x device will immediately engage its over-current protection and limits the current to the Output Current Limit ( $I_{OCL}$ ) by altering the resistance of the switch. If the over-current condition is not removed within the Output Current Limit Pulse time ( $I_{OCL}$ ), the output is immediately shutdown and OC SDn is set to true. The channel will remain shutdown for the duration of the Over-Current Protection Retry Delay ( $I_{OPRD}$ ).

At marker B, after the Over-Current Protection Retry Delay has expired, OC\_SDn is set to false, and the channel is turned on again. If the over-current condition is once again detected on the output, the resistance of the switch will once again be altered to limit the current to  $I_{OCL}$  for no longer then  $t_{OCL}$ , at which point the channel will shut down again, protecting itself from high power dissipation. The switch will attempt to turn on again in the same way, multiple times, at a retry period equal to Output Current Limit Period ( $t_{OCLP}$ ), and for up to the Over-Current Protection Duration ( $t_{OCPD}$ ). If the over-current condition is no longer detected at any time during an Over Current Limit Pulse, the switch resistance is immediately reduced to normal ON-State Output Resistance ( $R_{ON}$ ).

At marker C, the Si834x tests the load to determine if it requires high inrush current for normal operation. The current limit is increased to Output Peak Current Limit (I<sub>OPCL</sub>), and the pulse time is reduced to Output Peak Current Test Pulse (t<sub>OPCT</sub>). See the figure below for details on switch behavior when driving a load that requires a high inrush current. In the case of a short-circuit or other over-current condition that cannot be resolved with high inrush current, after t<sub>OPCT</sub> passes, the output is shutdown again for t<sub>OPRD</sub>, and OC\_SDn is set to true. This cycle will repeat indefinitely as long as the over-current condition remains detected.

At marker D, the dead short is removed. However, during the time the channel is shutdown, no changes in the over-current condition are detected. This is true for any period of time the channel is shutdown. Therefore, the channel remains shutdown until  $t_{OCLP}$  expires, at which time the channel is turned on, and normal operation resumes.

Figure 3.6. Inrush Current Mode Behavior

The figure above illustrates the behavior of a high-side (sourcing) Si834x switch when driving a load that requires a high inrush current such as an incandescent lamp. The figure plots the digital input to the switch (An) as well as the output voltage ( $V_{Bn}$ ) and output current ( $I_{Bn}$ ) from the switch where n is a specific channel number.

At marker A, the channel is turned on and the current through the switch is immediately detected above the Output Current Limit Threshold ( $I_{OCLT}$ ), which engages the over-current protection and limits the current to the Output Current Limit ( $I_{OCL}$ ). See Figure 3.5 on page 15 for details on typical over-current protection.

At marker B, similar to the over-current condition depicted in Figure 3.5 on page 15, the Si834x switch alters its resistance to allow for a higher Output Peak Current Limit ( $I_{OPCL}$ ). Unlike the over-current condition, if the current through the switch remains less than  $I_{OPCL}$ , the switch will maintain the increased current limit for a time up to the Output Peak Current Limit Pulse ( $t_{OPCL}$ ). The current through the switch must reduce to a level below  $I_{OCLT}$ , which is similar to  $I_{OCL}$  depicted in the figure above, before  $t_{OPCL}$  passes. Otherwise, the channel is deemed to be in an over-current state, at which time it is shutdown and Over-Current Shutdown diagnostic register (OC\_SDn) is set to true.

#### 3.4.3 Over-Temperature Protection

The Si834x Isolated Smart Switch includes independent over-temperature protection for each channel. It has two levels of protection that balance device safety with switch performance. The Si834x will continue to operate safely with reduced performance when individual channels are over-temperature, only shutting down channels when all channels are detected to be over-temperature.

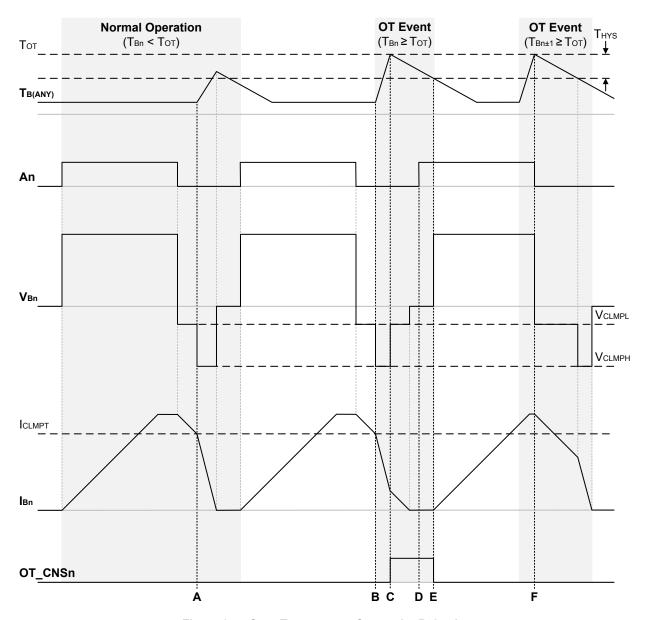

Figure 3.7. Over-Temperature Constraint Behavior

The figure above illustrates the behavior of a high-side (sourcing) Si834x switch when driving an inductor at the switches' typical ON State Load Current ( $I_{O(ON)}$ ), but then experiencing two different over-temperature events (OT Event). The "Normal Operation" section is identical to Figure 3.4 on page 14 and is included for reference. The figure plots the digital input to the switch (An), the temperature of any output channel ( $I_{B(ANY)}$ ), as well as the output voltage ( $I_{B(ANY)}$ ) and output current ( $I_{B(ANY)}$ ) from the switch where  $I_{B(ANY)}$  is a specific channel number. It also illustrates the Over-Temperature Constraint diagnostic register value for the channel (OT\_CNSn) when the enable mask for auto-clearing of diagnostics (ACLR\_EN) is set to true. This is the default diagnostic report clearing behavior.

Under normal conditions where ambient temperature is limited to the Derated Ambient ( $T_{AD}$ ), calculated in Power Dissipation Considerations, the most likely cause of over-temperature is demagnetizing a large inductor ( $E_{AS}$ ). Specifically, when the smart clamp is set to the Demagnetization Clamp High Voltage ( $V_{CLMPH}$ ) and power dissipation is at its peak. This temperature rise is illustrated in the figure above at marker A for an  $E_{AS}$ , which falls below the maximum specification of the device. See Table 5.12 on page 53 for more details on the absolute maximum specifications.

Marker B illustrates the switch behavior when the dissipated  $E_{AS}$  is too large for the current ambient temperature. When the Si834x smart clamp transitions to  $V_{CLMPH}$ , the switch temperature rises quickly until it reaches the Over-Temperature Threshold ( $T_{OT}$ ) at marker C. At this point, the smart clamp for each Si834x channel is constrained to the Demagnetization Clamp Low Voltage ( $V_{CLMPL}$ ), and OT\_CNSn is set to true. This protects the device by reducing power dissipation and forcing all inductors attached to the Si834x to demagnetize more slowly.

While the Si834x is over-temperature on any channel, all channels are prevented from turning on in order to further reduce power dissipation and recover quickly, as illustrated at marker D. Note that a channel in inrush current mode, or experiencing an Over-Current Shutdown will also have it's retry attempts suppressed during its Over-Current Protection Duration ( $t_{OCPD}$ ) period. Once the temperature of the channel falls below the Over-Temperature Hysteresis ( $T_{HYS}$ ) level, as illustrated by marker E, OT\_CNSn is set to false, and all channels resume normal operation.

It is important to note that an over-temperature condition on any channel will cause all channels to be constrained in the manner described above, not just the channel with the over-temperature diagnostic report. This is illustrated at marker F where a different channel, not illustrated, exceeds  $T_{OT}$ , forcing the illustrated channel to remain at  $V_{CLMPL}$  and constraining its demagnetization performance.

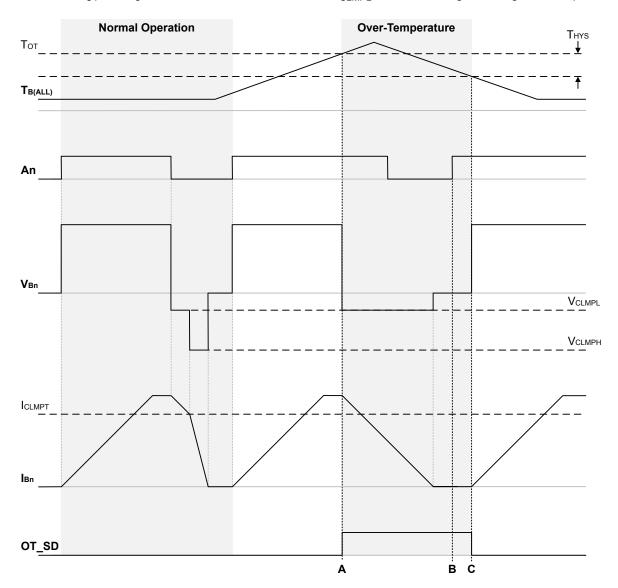

Figure 3.8. Over-Temperature Shutdown Behavior

If ambient temperature is not limited to  $T_{AD}$ , or if  $E_{AS}$  is much larger than the specified maximum, it is possible that the temperature of all channels ( $T_{B(ALL)}$ ) will exceed  $T_{OT}$ , as illustrated in the figure above. In this event, as illustrated at marker A, all channels are immediately shutdown, and the Over-Temperature Shutdown register (OT\_SD) will be set to true. If a channel is driving an inductor, the smart clamp will be constrained to  $V_{CLMPL}$  and demagnetization time will be increased to help reduce power dissipation. All channels will be prevented from turning on (marker B) until the temperature of all channels falls below  $T_{HYS}$ , as depicted at marker C, at which time the OT\_SD register will be set to false and all channels will resume normal operation.

# 3.4.4 Power Supply Protection

The Si834x Isolated Smart Switch monitors both the logic interface and switch power supplies, protecting the device and load when the power supplies are out of specification. Like the over-temperature protection, the Si834x balances performance with safety by constraining switch performance under some power supply conditions, and safely shutting down under others.

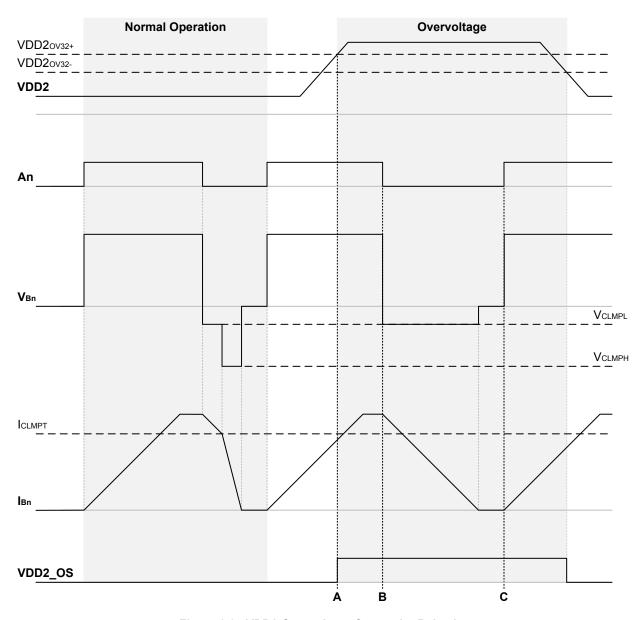

Figure 3.9. VDD2 Overvoltage Constraint Behavior

The figure above illustrates the behavior of a high-side (sourcing) Si834x switch when driving an inductor at the switches' typical ON State Load Current ( $I_{O(ON)}$ ), but then experiences an overvoltage condition on the switch power supply (VDD2). The "Normal Operation" section is identical to Figure 3.4 on page 14 and is included for reference. The figure plots the digital input to the switch (An), the VDD2 supply voltage (VDD2), as well as the output voltage ( $I_{Bn}$ ) and output current ( $I_{Bn}$ ) from the switch where  $I_{Bn}$  is a specific channel number. It also illustrates the VDD2 Out of Specification register value (VDD2\_OS) when the enable mask for auto-clearing of diagnostics (ACLR\_EN) is set to true. This is the default diagnostic report clearing behavior.

At marker A, VDD2 exceeds the VDD2 Overvoltage Threshold (VDD2 $_{OV32}$ ). In order to reduce power dissipation to a safe level, the smart clamp for each channel is constrained to Demagnetization Clamp Low Voltage (V $_{CLMPL}$ ), and the VDD2 $_{CLMPL}$ OS register is set to true. While the smart clamp for each channel is limited to V $_{CLMPL}$ , demagnetization performance is constrained and all inductive loads turn off more slowly, as illustrated at marker B. Unlike an Over-Temperature Constraint, the output channels are not prevented from turning on (marker C). Once VDD2 falls below VDD2 $_{OV32}$  again, the smart clamp returns to "Normal Operation", and the VDD2 $_{CLMPL}$ OS register is set back to false.

It is important to note that overvoltage is not prevented from damaging the device if VDD2 remains above VDD2 $_{OV32}$  or exceeds the absolute maximum specification. It only protects the device from higher power dissipation when demagnetizing an inductive load at higher voltages, and generates a diagnostic report. If VDD2 exceeds the VDD2 ESD Clamp Threshold (VDD2 $_{CLMP}$ ), the VDD2 ESD clamp will engage, damaging the device.

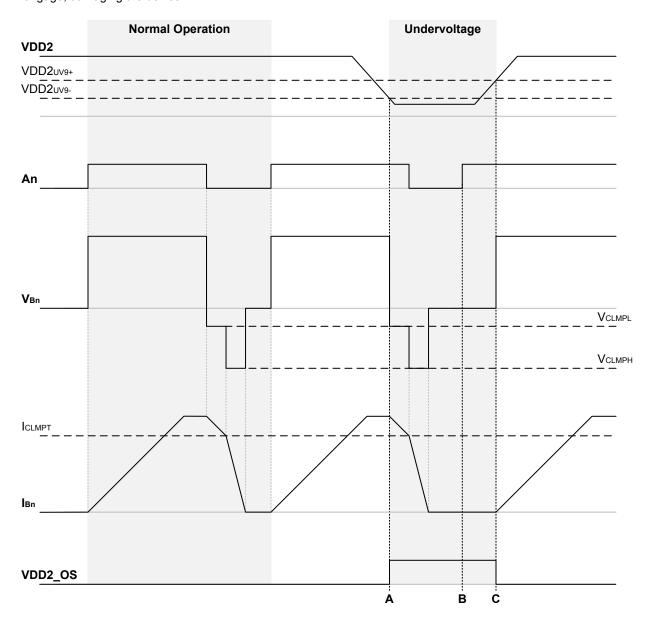

Figure 3.10. VDD2 Undervoltage Shutdown Behavior

The switch is protected against a VDD2 undervoltage condition in a very similar manner to VDD2 overvoltage conditions, as illustrated by the figure above. At marker A, VDD2 falls below the VDD2 Undervoltage Threshold (VDD2<sub>UV9</sub>). All channels are immediately shutdown, and the VDD2\_OS register is set to true. Note that the smart clamp operates normally during shutdown. While VDD2 is undervoltage, all channels are prevented from turning on (marker B). Only after VDD2 rises above VDD2<sub>UV9</sub> again will all channels be allowed to return to normal operation, and the VDD2 OS register set back to false, as illustrated at marker C.

It is important to note that VDD2 must remain powered to offer undervoltage protection in the manner described above. If VDD2 is completely unpowered (0 V), the smart clamp voltage is not well defined. Also, the Master Diagnostic register (MASTER\_DIAG) may not accurately report the VDD2 state. In this condition, if the switch is undamaged, the Communication Error register value (COMM\_ERR) will be set to true, denoting a loss of communication with the unpowered switch. Finally, when power is restored to VDD2, the device must wait for VDD2 Switch Power Cycle Time (t<sub>PC2</sub>) to pass before normal operation will resume. See Switch Timing Behavior for details.

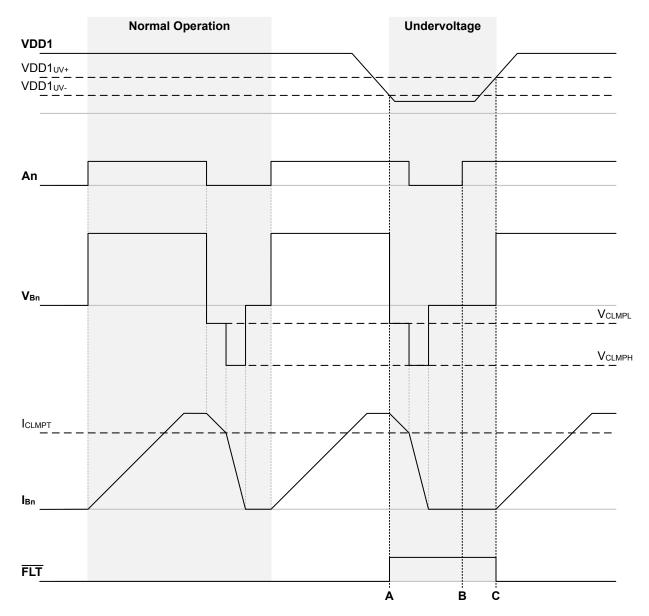

Figure 3.11. VDD1 Undervoltage Shutdown Behavior

The logic interface is also protected against a VDD1 undervoltage condition in the same way as VDD2, illustrated by the figure above. Unlike the VDD2 undervoltage condition, the VDD1 undervoltage condition is only reported on the FLT\ pin, not through a diagnostic register. Like the VDD2 undervoltage protection, all channels are immediately shutdown when VDD1 falls below VDD1 Undervoltage Threshold (VDD1<sub>UV</sub>), as illustrated at marker A. All channels are prevented from turning on while VDD1 remains undervoltage (marker B), and normal operation immediately resumes when VDD1 rises above VDD1<sub>UV</sub>, as illustrated by marker C.

Like VDD2 undervoltage protection, VDD1 must remain powered to offer undervoltage protection in the manner described above. If VDD1 is completely unpowered (0 V), the FLT\ pin may be in an undetermined state and may show a logic high value if connected to VDD1 through a pull-up resistor. When power is restored to VDD1, the device must wait for VDD1 Logic Interface Cycle Time (t<sub>PC1</sub>) to pass before normal operation will resume. See Switch Timing Behavior for details.

#### 3.5 Diagnostics and Monitoring

The Si834x Isolated Smart Switch communicates rich diagnostic and monitoring information to the host controller including the condition of the load, power supplies, and built-in protection. Eight separate diagnostic reports are available, as well as channel status reports.

Table 3.6. Diagnostics Overview

| Scope        | Diagnostic          | Severity <sup>1</sup> | Description                                                                     |

|--------------|---------------------|-----------------------|---------------------------------------------------------------------------------|

|              | Open-Circuit        | Warning               | Channel has no load detected. Output is operating normally.                     |

| Per Channel  | Over-Current        | Shutdown              | Channel is overloaded. Output is immediately turned off.                        |

|              | Over Temperature    | Constraint            | Channel is too hot. Inductors demagnetize slowly. Output will not turn back on. |

|              | Over-Temperature    | Shutdown              | All channels are too hot. All outputs are immediately turned off.               |

|              | VDD2 Low-Voltage    | Warning               | VDD2 is under VDD2 <sub>UV18</sub> . All outputs operating normally.            |

| All Channels | VDD2 Overvoltage    | Constraint            | VDD2 is over VDD2 <sub>OV32</sub> . Inductors demagnetize slowly.               |

| All Channels | VDD2 Undervoltage   | Shutdown              | VDD2 is over VDD2 <sub>UV9</sub> . All outputs are turned off.                  |

|              | VDD1 Undervoltage   | Shutdown              | VDD1 is under VDD1 <sub>UV</sub> . All outputs are turned off.                  |

|              | Communication Error | Shutdown              | Communication across the isolation barrier is lost. All outputs are turned off. |

#### Note:

1. Diagnostics with a severity of "Constraint" or "Shutdown" are defined as faults and exposed on the FLT\ output. The configuration for FLT\ can be modified using the SPI, if available. See Serial Peripheral Interface for details.

Diagnostics and monitoring information is reported in different ways depending on the device selected (see the Ordering Guide for device options.) Devices with the SPI allow access to all diagnostic and monitoring information via diagnostic registers. One active-low, open-drain indicator pin (FLT\) is available on SPI devices and provides immediate diagnostic report feedback to the user, or can be used as a fast diagnostic interrupt for the controller. The diagnostic reports exposed on this indicator pin are configurable via the SPI. By setting a true value in the Fault Enable Mask (FLT\_EN) register at the desired diagnostic's bit field, the indicator pin will be turned ON when the corresponding diagnostic report is true. See Serial Peripheral Interface for more details.

Devices without the SPI have a fixed configuration and expose diagnostics and monitoring information on active-low, open-drain indicator pins only. These pins can drive an LED to provide end-user feedback, they can be combined with a pull-up resistor and read by the controller, or multiple pins can be combined to simplify diagnostics and monitoring across devices. Like SPI devices, an FLT\ indicator pin is always provided. It is configured to report any diagnostic which represents an abnormal switch behavior. This is also the default configuration for SPI devices. Contact Skyworks for custom device configurations not available in the Ordering Guide.

A diagnostic report can be cleared from the Si834x device once the condition that caused the report is removed from the device. If a report is cleared while the condition remains, a new report will be automatically generated. See Switch Protection for details on the conditions that cause diagnostic reports.

For SPI devices, all diagnostics are set to have their reports automatically cleared when the conditions that caused the report are removed. However, this can be controlled for each diagnostic, except for the VDD1 Undervoltage Shutdown diagnostic, through the Automatic Diagnostic Clear Enable Mask (ACLR\_EN) register. If a bit field in this enable mask is set to false, the corresponding diagnostic report will remain until it is cleared by setting a true value in the Clear Diagnostic (CLR\_DIAG) register at the corresponding diagnostic's bit field.

It is important to note that the operation of an output channel is not affected by the presence of a diagnostic report. For example, if the device is not configured to automatically clear a diagnostic report, then the diagnostic report will persist after the condition that caused the report is removed. Once the condition that caused the report is removed, the channel will resume normal operation regardless of diagnostic report state. The Communication Error diagnostic is an exception to this behavior. See Communication Error Diagnostic for details.

For parallel interface only devices, a device with a Clear Fault Input pin (Si834xxxCx) is required to manually clear diagnostic reports on the FLT\ pin. It operates the same way as setting a true value in the CLR\_DIAG register for all diagnostics. All other parallel interface only devices are configured to automatically clear diagnostic reports when the conditions that caused the report are removed.

#### 3.5.1 Power Supply Diagnostics

The Si834x Isolated Smart Switch offers complete power supply diagnostics for both power supplies, including overvoltage, low-voltage, and undervoltage conditions.

Table 3.7. Switch Power Supply Diagnostics

|                             |                                                    |                   | VDD2              | MASTER_D       | IAG[5:4]       | Output Behavior <sup>4</sup> |                                        |

|-----------------------------|----------------------------------------------------|-------------------|-------------------|----------------|----------------|------------------------------|----------------------------------------|

| Diagnostic                  | Supply Voltage <sup>1</sup>                        | FLT\ <sup>2</sup> | WRN\ <sup>3</sup> | VDD2_OS        | VDD2_<br>LOW   | Switch                       | Clamps                                 |

| VDD2 Voltage OK             | VDD2 <sub>UV18</sub> < VDD2 < VDD2 <sub>OV32</sub> | _                 | OFF               | 0              | 0              | Normal                       | Normal                                 |

| VDD2 Low-Voltage Warning    | VDD2 <sub>UV9</sub> < VDD2 < VDD2 <sub>UV18</sub>  | _                 | ON                | 0              | 1              | Normal                       | Normal                                 |

| VDD2 Overvoltage Constraint | VDD2 > VDD2 <sub>OV32</sub>                        | ON                | OFF               | 1              | 0              | Normal                       | V <sub>CLMP</sub> = V <sub>CLMPL</sub> |

| VDD2 Undervoltage Shutdown  | VDD2 < VDD2 <sub>UV9</sub>                         | ON                | ON <sup>5</sup>   | 1 <sup>5</sup> | 1 <sup>5</sup> | Turns OFF                    | Normal                                 |

# Note:

- 1. Supply voltage must remain within this voltage range long enough to be measured for a change to be reported. If supply voltage changes sufficiently quickly, the diagnostic state will remain unchanged.

- 2. The output is both active-low and open-drain. "—" denotes that this diagnostic does not turn on the output, but other diagnostics might. The default configuration for FLT\ is depicted, but can be modified using the SPI, if available. See Serial Peripheral Interface for details.

- 3. The output is both active-low and open drain. It is only available on specific product offerings. See the Ordering Guide for more details.

- 4. Behavior assumes only the defined diagnostic condition is present. Exceptions to normal behavior due to a fault are defined here. See Switch Protection for more information. Clamp behavior applies to all smart output clamps, for all channels.

- 5. If the supply is unpowered, this value may not be accurately reported. Assuming there is no damage to the device, a COMM\_ERR (MASTER\_DIAG bit 7 = 1) will also be reported when VDD2 is unpowered and can be queried via the SPI. See Switch Protection for more information.

The table above describes the switch power supply diagnostic reports, where they are reported by default, and provides a brief overview of how the output behavior changes with each report. Note that the two bit fields in the Master Diagnostic register (MASTER\_DIAG[5:4]) can be read separately or as a two-bit field. If read separately, bit 5 reports when VDD2 voltage is out of device specifications and the output behavior is abnormal. Bit 4 simply reports a warning when VDD2 voltage is low. If read as a two-bit field, all four possible power supply states can be discerned.

Table 3.8. Logic Interface Power Supply Diagnostics

| Diagnostic                 | Supply Voltage              | FLT\ <sup>2</sup> | Output Behavior <sup>3</sup> |        |  |  |  |

|----------------------------|-----------------------------|-------------------|------------------------------|--------|--|--|--|

| Diagnostic                 | Supply Voltage <sup>1</sup> | FLIV              | Switch                       | Clamps |  |  |  |

| VDD1 Voltage OK            | VDD1 > VDD1 <sub>UV</sub>   | -                 | Normal                       | Normal |  |  |  |

| VDD1 Undervoltage Shutdown | VDD1 < VDD1 <sub>UV</sub>   | ON                | Turns OFF                    | Normal |  |  |  |

- 1. Supply voltage must remain within this voltage range long enough to be measured for a change to be reported. If supply voltage changes sufficiently quickly, the diagnostic state will remain unchanged.

- 2. The output is both active-low and open-drain. "—" denotes that this diagnostic does not turn on the output, but other diagnostics might.

- 3. Behavior assumes only the defined diagnostic condition is present. Exceptions to normal behavior due to a fault are defined here. See Switch Protection for more information. Clamp behavior applies to all smart output clamps, for all channels.

The table above describes the undervoltage shutdown diagnostic report for the logic interface power supply, where it is reported, and provides a brief overview of how the output behavior changes with the report. A VDD1 Undervoltage Shutdown is only reported on the FLT\ pin and has no corresponding SPI register entry. If VDD1 is completely unpowered (0 V), the FLT\ output is in an unknown state. A short glitch may be observed on the FLT\ pin when it is connected to VDD1 via a pull-up resistor, until the logic interface is powered. See Switch Protection for more details.

# 3.5.2 Over-Temperature Diagnostics

The Si834x Isolated Smart Switch reports over-temperature in different levels of severity allowing the controller to take different actions depending on how the switch output behavior is changing.

Table 3.9. Over-Temperature Diagnostics

| Diagnostic                  | Switch                            | Channels     | ELT\2 | OT_SD | OT CNSn <sup>3</sup> | Out       | put Behavior <sup>4</sup>              |

|-----------------------------|-----------------------------------|--------------|-------|-------|----------------------|-----------|----------------------------------------|

| Diagnostic                  | Temperature <sup>1</sup>          | Gilainicis   |       | 01_05 | 01_011311            | Switch    | Clamps                                 |

| Temperature OK              | T <sub>Bn</sub> < T <sub>OT</sub> | Any Channel  | _     | 0     | 0                    | Normal    | Normal                                 |

| Over-Temperature Constraint | T- > T                            | Any Channel  | ON    | 0     | 1                    | Stays OFF | V <sub>CLMP</sub> = V <sub>CLMPL</sub> |

| Over-Temperature Shutdown   | $T_{Bn} > T_{OT}$                 | All Channels | ON    | 1     | 1                    | Turns OFF | V <sub>CLMP</sub> = V <sub>CLMPL</sub> |

### Note:

- 1. Channel must remain above this temperature long enough to be measured for a change to be reported. If the temperature changes sufficiently quickly, the diagnostic state will remain unchanged.

- 2. The output is both active-low and open-drain. "-" denotes that this diagnostic does not turn on the output, but other diagnostics might. The default configuration for FLT\ is depicted, but can be modified using the SPI, if available. See Serial Peripheral Interface for details.

- 3. Reported in Diagnostic registers (DIAG), depending on the channel. See Serial Peripheral Interface for details.

- 4. Behavior assumes only the defined diagnostic condition is present. Exceptions to normal behavior due to a fault are defined here. See Switch Protection for more information. Clamp behavior applies to all smart output clamps, for all channels.

The table above describes the over-temperature diagnostic reports, where they are reported by default, and provides a brief overview of how the output behavior changes with each report. An Over-Temperature Constraint is reported in the Diagnostic (DIAG) registers on a per-channel basis where n, in OT\_CNSn, describes the specific channel that has exceeded the Over-Temperature Threshold ( $T_{OT}$ ). An Over-Temperature Shutdown is reported in the MASTER\_DIAG SPI register in bit field OT\_SD when all channels have exceeded  $T_{OT}$ .

# 3.5.3 Over-Current Diagnostics

The Si834x Isolated Smart Switch reports over-current diagnostics on a per-channel basis so the controller can take action on a specific channel without disrupting operation on other channels.

Table 3.10. Over-Current Diagnostics

| Diagnostic            | An or                 | Output Current                      | FLT\ <sup>2</sup> | OC_SDn <sup>3</sup> | Output Behavior <sup>4</sup> |        |  |  |

|-----------------------|-----------------------|-------------------------------------|-------------------|---------------------|------------------------------|--------|--|--|

| Diagnostic            | SW_EN[n] <sup>1</sup> | Output Gurrent                      | FLI\-             | 00_3011             | Switch                       | Clamp  |  |  |

| Current OK            | L                     | _                                   | _                 | 0                   | Normal                       | Normal |  |  |

| Current OK            | Н                     | I <sub>Bn</sub> < I <sub>OCLT</sub> | _                 | 0                   | Normal                       | Normal |  |  |

| Over-Current Shutdown | Н                     | I <sub>Bn</sub> > I <sub>OCLT</sub> | ON                | 1                   | Turns OFF                    | Normal |  |  |

# Note:

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Bit addresses are zero-indexed such that channel 1 (output B1) is enabled by the SW\_EN[0] bit.

- 2. The output is both active-low and open-drain. "-" denotes that this diagnostic does not turn on the output, but other diagnostics might. The default configuration for FLT\ is depicted, but can be modified using the SPI, if available. See Serial Peripheral Interface for details.

- 3. Reported in Diagnostic registers (DIAG), depending on the channel. See Serial Peripheral Interface for details.

- 4. Behavior assumes only the defined diagnostic condition is present. Exceptions to normal behavior due to a fault are defined here. See Switch Protection for more information.

The table above describes the over-current diagnostic report, where it is reported by default, and provides a brief overview of how the output behavior changes with the report. An Over-Current Shutdown can only be reported when the channel input is high (true). Over-Current Shutdown is reported in the Diagnostic (DIAG) registers on a per-channel basis where n, in OC\_SDn, describes the specific channel that has exceeded the Output Current Limit Threshold ( $I_{OCLT}$ ).

# 3.5.4 Open-Circuit Diagnostics

The Si834x Isolated Smart Switch can detect and report an open-circuit on each switch channel allowing the controller to easily detect the condition of individual loads.

Table 3.11. Open-Circuit Diagnostic

| Diagnostic              | An or                 | Load                               | OPEN_CH\3 | OPEN_WRNn <sup>4</sup> | Output Behavior <sup>5</sup> |        |

|-------------------------|-----------------------|------------------------------------|-----------|------------------------|------------------------------|--------|

| Diagnostic              | SW_EN[n] <sup>1</sup> | Resistance <sup>2</sup>            | OPEN_CH(  | OPEN_WRNII             | Switch                       | Clamp  |

| Onen Circuit Undetected | Н                     | _                                  | OFF       | 0                      | Normal                       | Normal |

| Open-Circuit Undetected | L                     | $R_L < R_{LMAX}$                   | OFF       | 0                      | Normal                       | Normal |

| Open-Circuit Warning    | L                     | R <sub>L</sub> > R <sub>LMAX</sub> | ON        | 1                      | Normal                       | Normal |

# Note:

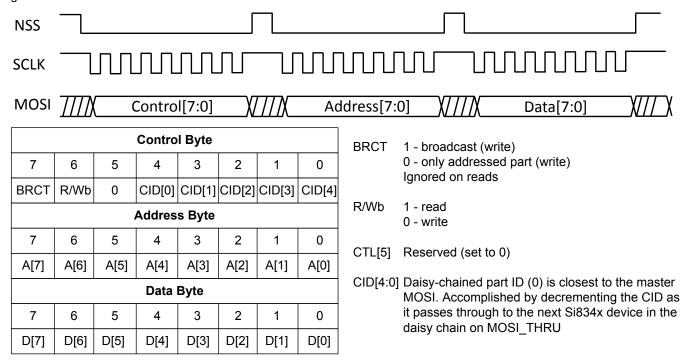

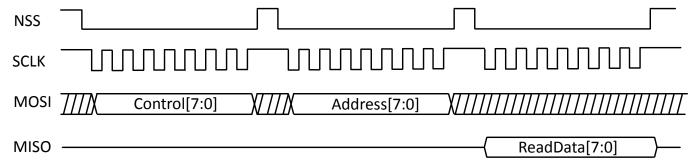

- 1. "X" is any logic value, "H" is a logic high (true) value, and "L" is a logic low (false) value. Logic pins should always be connected to either logic high or low. Bit addresses are zero-indexed such that channel 1 (output B1) is enabled by the SW\_EN[0] bit.